# iCE40™ LP/HX/LM Family Handbook

HB1011 Version 01.2, November 2013

# iCE40 LP/HX/LM Family Handbook Table of Contents

#### October 2013

| Section I. iCE40 LP/HX Family Data Sheet                 |      |

|----------------------------------------------------------|------|

| Introduction                                             |      |

| Features                                                 |      |

| Introduction                                             | 1-2  |

| Architecture                                             |      |

| Architecture Overview                                    |      |

| PLB Blocks                                               |      |

| Routing                                                  |      |

| Clock/Control Distribution Network                       |      |

| sysCLOCK Phase Locked Loops (PLLs)                       | 2-4  |

| sysMEM Embedded Block RAM Memory                         | 2-5  |

| sysIO                                                    | 2-7  |

| sysIO Buffer                                             | 2-8  |

| Non-Volatile Configuration Memory                        | 2-9  |

| Power On Reset                                           | 2-10 |

| Programming and Configuration                            | 2-10 |

| Power Saving Options                                     | 2-10 |

| DC and Switching Characteristics                         |      |

| Absolute Maximum Ratings                                 | 3-1  |

| Recommended Operating Conditions                         |      |

| Power Supply Ramp Rates                                  |      |

| Power-On-Reset Voltage Levels                            |      |

| ESD Performance                                          |      |

| DC Electrical Characteristics                            |      |

| Static Supply Current – LP Devices                       |      |

| Static Supply Current – HX Devices                       |      |

| Programming NVCM Supply Current – LP Devices             |      |

| Programming NVCM Supply Current – HX Devices             |      |

| Peak Startup Supply Current – LP Devices                 |      |

| Peak Startup Supply Current – HX Devices                 |      |

| sysIO Recommended Operating Conditions                   |      |

| sysIO Single-Ended DC Electrical Characteristics         |      |

| sysIO Differential Electrical Characteristics            |      |

| LVDS25                                                   |      |

| subLVDS                                                  |      |

| LVDS25E Emulation                                        |      |

| SubLVDS Emulation                                        |      |

| Typical Building Block Function Performance – LP Devices |      |

| Pin-to-Pin Performance (LVCMOS25)                        |      |

| Register-to-Register Performance                         |      |

| Typical Building Block Function Performance – HX Devices |      |

| Pin-to-Pin Performance (LVCMOS25)                        |      |

| · · · · · · · · · · · · · · · · · · ·                    |      |

| Register-to-Register Performance                         |      |

| Derating Logic Timing                                    |      |

| Maximum sysIO Buffer Performance                         |      |

| iCE40 Family Timing Adders                               |      |

| iCE40 External Switching Characteristics – LP Devices    |      |

| iCE40 External Switching Characteristics – HX Devices    |      |

© 2013 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| sysCLOCK PLL Timing                                                     | 3-16 |

|-------------------------------------------------------------------------|------|

| SPI Master or NVCM Configuration Time                                   |      |

| sysCONFIG Port Timing Specifications                                    |      |

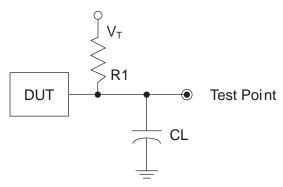

| Switching Test Conditions                                               |      |

| Pinout Information                                                      |      |

| Signal Descriptions                                                     | 4-1  |

| Pin Information Summary                                                 |      |

| Pin Information Summary, Continued                                      |      |

| Ordering Information                                                    |      |

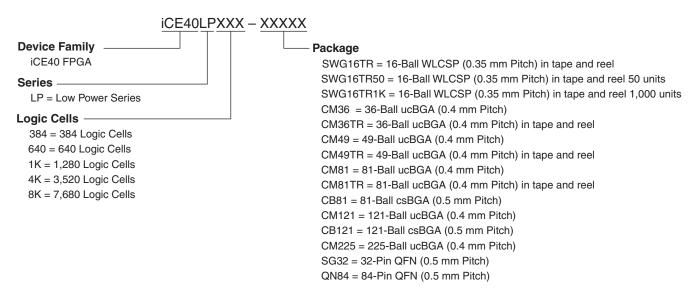

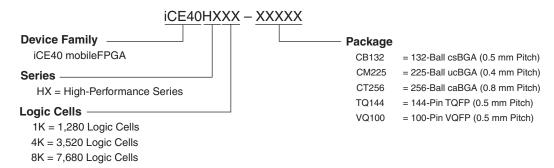

| iCE40 Part Number Description                                           | 5-1  |

| Ultra Low Power (LP) Devices                                            |      |

| High Performance (HX) Devices                                           |      |

| Ordering Information                                                    |      |

| Ultra Low Power Industrial Grade Devices, Halogen Free (RoHS) Packaging |      |

| Supplemental Information                                                | 0 2  |

| For Further Information                                                 | 6-1  |

| Revision History                                                        |      |

| Section II. iCE40LM Family Data Sheet                                   |      |

| · · · · · · · · · · · · · · · · · · ·                                   |      |

| Introduction General Description                                        | 0.4  |

| ·                                                                       |      |

| Features                                                                |      |

| Applications                                                            |      |

| Introduction                                                            | 8-2  |

| Architecture                                                            | 0.4  |

| Architecture Overview                                                   |      |

| PLB Blocks                                                              |      |

| Routing                                                                 |      |

| Clock/Control Distribution Network                                      |      |

| sysCLOCK Phase Locked Loops (PLLs) - NOT SUPPORTED on the 25-Pin WLCSP  |      |

| sysMEM Embedded Block RAM Memory                                        |      |

| sysIO Buffer Banks                                                      |      |

| sysIO Buffer                                                            |      |

| On-Chip Strobe Generators                                               |      |

| User I <sup>2</sup> C IP                                                |      |

| User SPI IP                                                             |      |

| High Drive I/O Pins                                                     |      |

| Power On Reset                                                          |      |

| iCE40LM Configuration                                                   |      |

| Power Saving Options                                                    | 9-11 |

| DC and Switching Characteristics                                        | 40.  |

| Absolute Maximum Ratings                                                |      |

| Recommended Operating Conditions                                        |      |

| Power Supply Ramp Rates                                                 |      |

| Power-On-Reset Voltage Levels                                           |      |

| Power Up Sequence                                                       |      |

| ESD Performance                                                         |      |

| DC Electrical Characteristics                                           |      |

| Supply Current                                                          |      |

| User I <sup>2</sup> C Specifications                                    |      |

| User SPI Specifications                                                 |      |

| sysIO Recommended Operating Conditions                                  |      |

| sysIO Single-Ended DC Electrical Characteristics                        |      |

| Typical Building Block Function Performance                             |      |

| Pin-to-Pin Performance (LVCMOS25)                                       | 10-4 |

| Register-to-Register Performance                                                        |       |

|-----------------------------------------------------------------------------------------|-------|

| Derating Logic Timing                                                                   |       |

| Maximum sysIO Buffer Performance                                                        |       |

| iCE40LM Family Timing Adders                                                            |       |

| iCE40LM External Switching Characteristics                                              |       |

| sysCLOCK PLL Timing – Preliminary                                                       |       |

| SPI Master Configuration Time                                                           |       |

| sysCONFIG Port Timing Specifications                                                    |       |

| Switching Test Conditions                                                               | 10-9  |

| Pinout Information                                                                      |       |

| Signal Descriptions                                                                     |       |

| Pin Information Summary                                                                 | 11-3  |

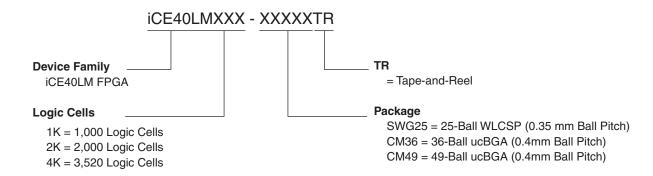

| Ordering Information                                                                    |       |

| iCE40LM Part Number Description                                                         |       |

| Ordering Part Numbers                                                                   | 12-1  |

| Supplemental Information                                                                |       |

| For Further Information                                                                 | 13-1  |

| Revision History                                                                        |       |

| Section III. iCE40 LP/HX/LM Family Technical Notes                                      |       |

| iCE40 Programming and Configuration                                                     |       |

| Introduction                                                                            | 15-1  |

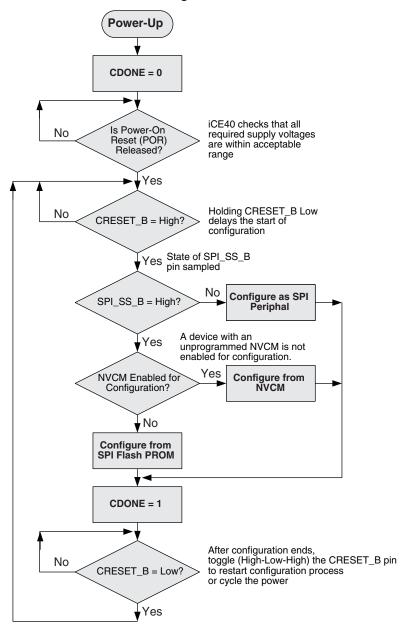

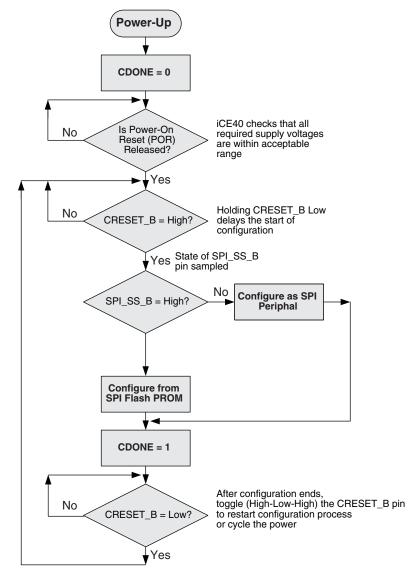

| Configuration Overview                                                                  |       |

| Configuration Mode Selection                                                            |       |

| Mode Selection for iCE40 LP and iCE40 HX                                                |       |

| Mode Selection for iCE40LM                                                              |       |

| Nonvolatile Configuration Memory (NVCM) (Applies to iCE40 LP and iCE40 HX Devices Only) |       |

| NVCM Programming                                                                        |       |

| Configuration Control Signals                                                           |       |

| Internal Oscillator                                                                     |       |

| Internal Device Reset                                                                   |       |

| Power-On Reset (POR)                                                                    |       |

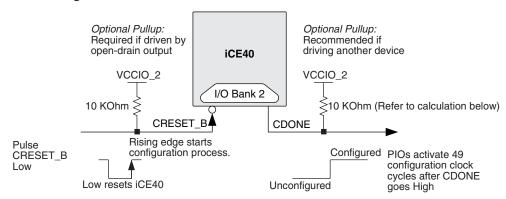

| CRESET B Pin                                                                            |       |

| sysCONFIG Port                                                                          |       |

| sysCONFIG Pins                                                                          |       |

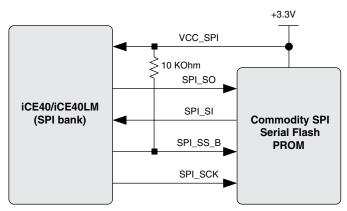

| SPI Master Configuration Interface                                                      |       |

| SPI PROM Requirements                                                                   |       |

| Enabling SPI Configuration Interface                                                    |       |

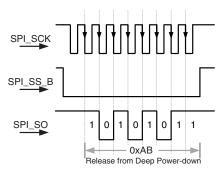

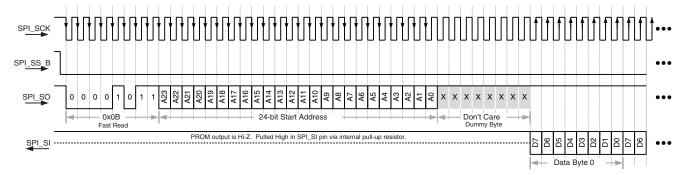

| SPI Master Configuration Process                                                        |       |

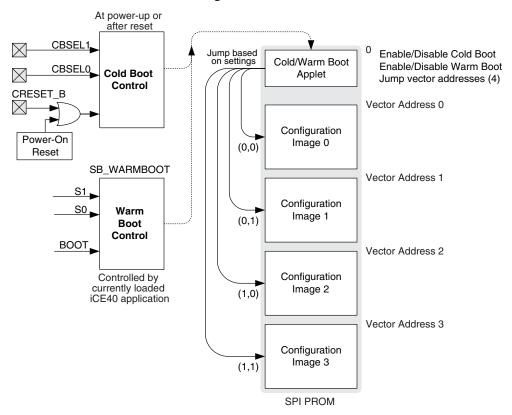

| Cold Boot Configuration Option (Applies to iCE40 LP and iCE40 HX Devices Only)          |       |

| Warm Boot Configuration Option (Applies to iCE40 LP and iCE40 HX Devices Only)          |       |

| Time-Out and Retry                                                                      |       |

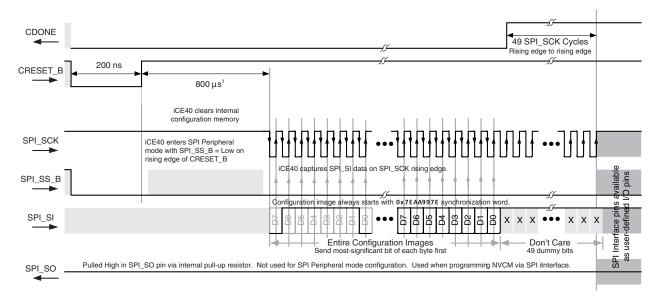

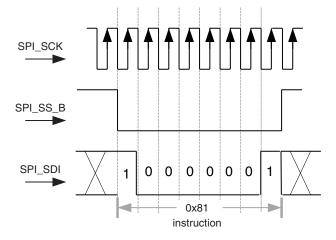

| SPI Slave Configuration Interface                                                       |       |

| Enabling SPI Configuration Interface                                                    |       |

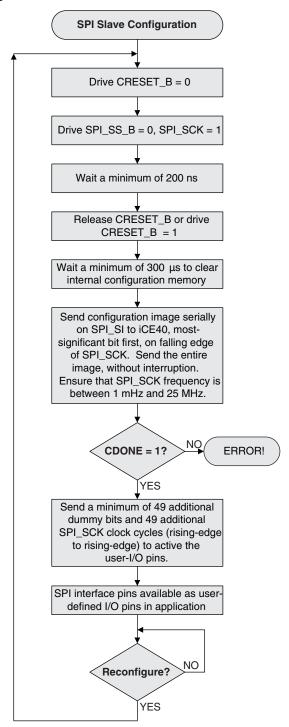

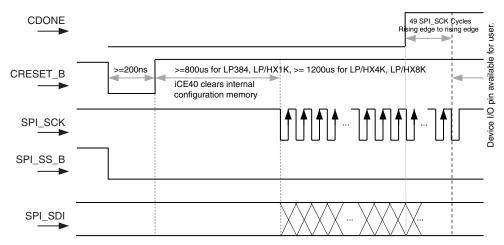

| SPI Slave Configuration Process                                                         |       |

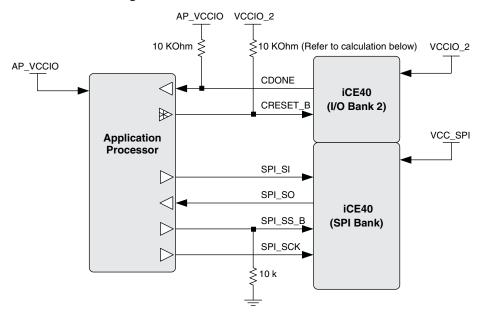

| Voltage Compatibility                                                                   |       |

| Technical Support Assistance                                                            |       |

| Revision History                                                                        |       |

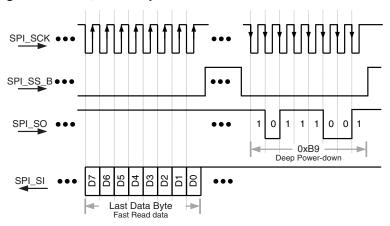

| Appendix A. SPI Slave Configuration Procedure                                           |       |

| CPU Configuration Procedure                                                             |       |

| Configuration Waveforms                                                                 |       |

| · · · · · · · · · · · · · · · · · · ·                                                   |       |

| Pseudo Code                                                                             | 15-23 |

| Memory Usage Guide for iCE40 Devices Introduction                                       | 16 1  |

| Memories in iCE40 Devices                                                               |       |

|                                                                                         | 10-1  |

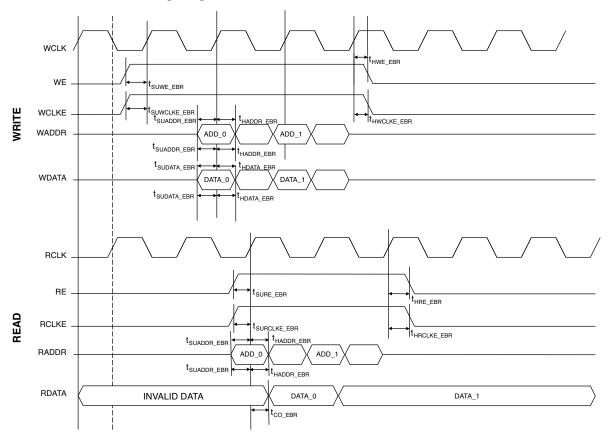

| iCE40 sysMEM Embedded Block RAM                                             | 16-2 |

|-----------------------------------------------------------------------------|------|

| Signals                                                                     | 16-3 |

| Timing Diagram                                                              |      |

| Write Operations                                                            | 16-4 |

| Read Operations                                                             |      |

| EBR Considerations                                                          |      |

| iCE40 sysMEM Embedded Block RAM Memory Primitives                           | 16-5 |

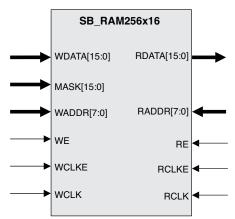

| SB_RAM256x16                                                                |      |

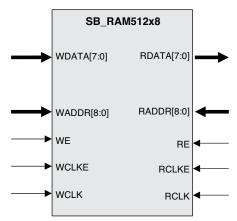

| SB RAM512x8                                                                 |      |

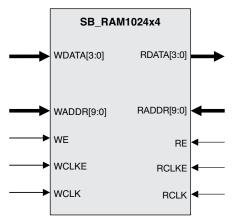

| SB RAM1024x4                                                                |      |

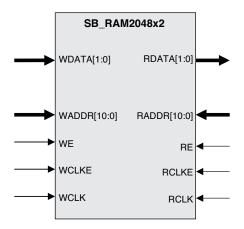

| SB RAM2048x2                                                                |      |

| SB_RAM40_4K                                                                 |      |

| EBR Utilization Summary in iCEcube2 Design Software                         |      |

| Technical Support Assistance                                                |      |

| Revision History                                                            |      |

| Appendix A. Standard HDL Code References                                    |      |

| Single-Port RAM                                                             |      |

| Dual Port Ram                                                               |      |

| iCE40 sysCLOCK PLL Design and Usage Guide                                   |      |

| Introduction                                                                | 17-1 |

| Global Routing Resources                                                    |      |

| Verilog Instantiation                                                       |      |

| VHDL Instantiation                                                          |      |

| iCE40 sysCLOCK PLL                                                          |      |

| iCE40 sysCLOCK PLL Features                                                 |      |

| Signals                                                                     |      |

| Clock Input Requirements                                                    |      |

| PLL Output Requirements                                                     |      |

| Functional Description                                                      |      |

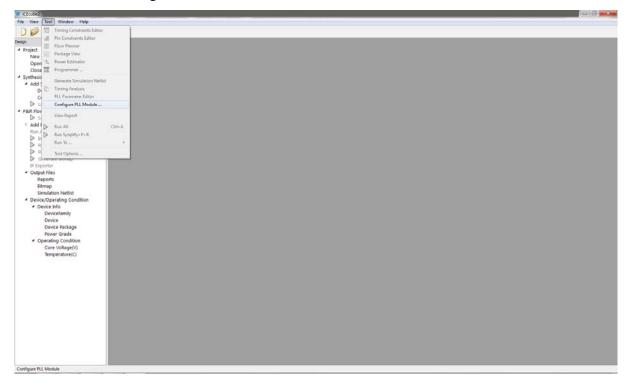

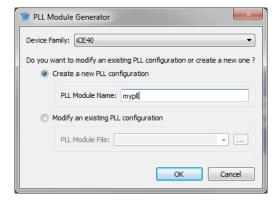

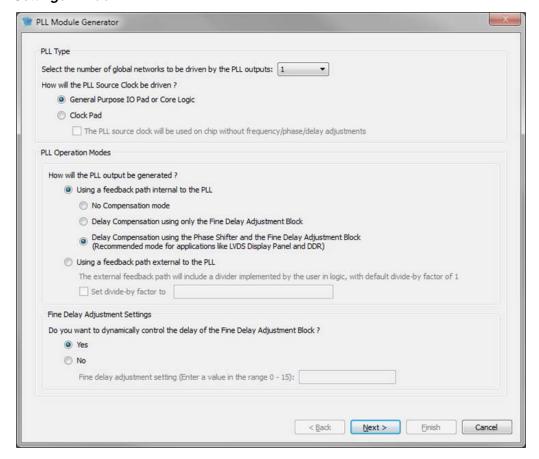

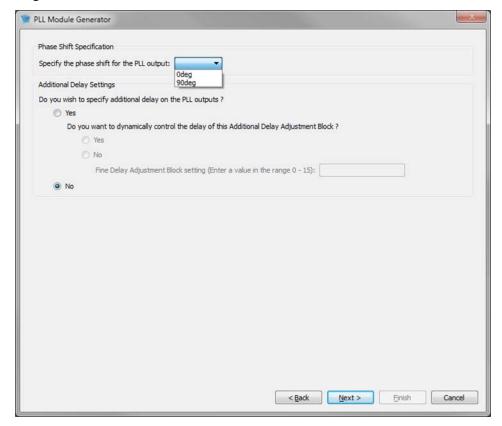

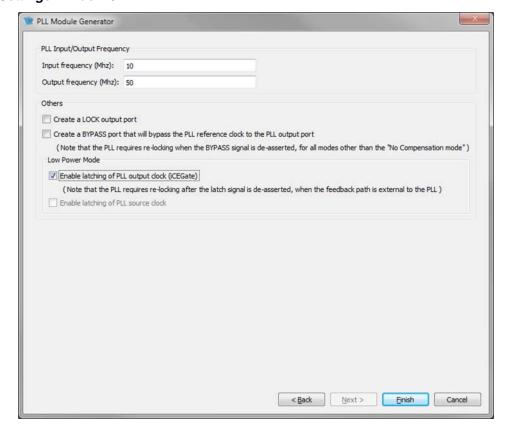

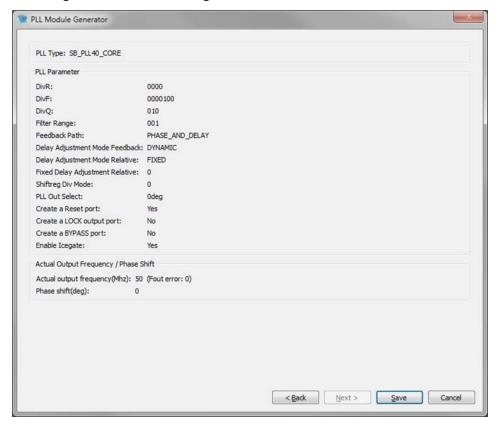

| Generating iCE40 PLL Using PLL Module Generator in iceCube2 Design Software |      |

| PLL Module Generator Output                                                 |      |

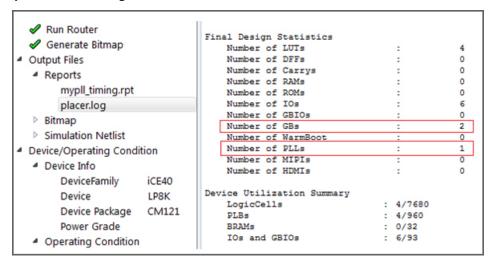

| iCEcube2 Design Software Report File                                        |      |

| Hardware Design Considerations                                              |      |

| PLL Placement Rules.                                                        |      |

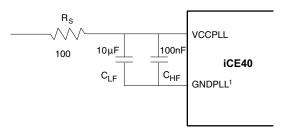

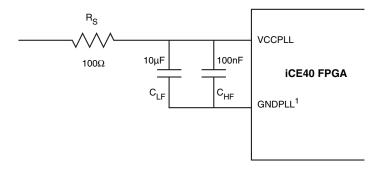

| Analog Power Supply Filter for PLL                                          |      |

| Technical Support Assistance                                                |      |

| Revision History                                                            |      |

| iCE40 Hardware Checklist                                                    |      |

| Introduction                                                                | 18-1 |

| Power Supply                                                                |      |

| Analog Power Supply Filter for PLL                                          |      |

| Configuration Considerations                                                |      |

| SPI Flash Requirement in Master SPI Mode                                    |      |

| LVDS Pin Assignments (For iCE40LP/HX Devices Only)                          |      |

| Checklist                                                                   |      |

| Technical Support Assistance                                                |      |

| Revision History                                                            |      |

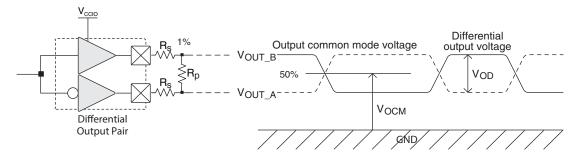

| Using Differential I/O                                                      |      |

| (LVDS, Sub-LVDS)                                                            |      |

| in iCE40 LP/HX Devices                                                      |      |

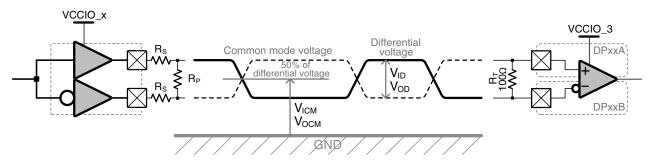

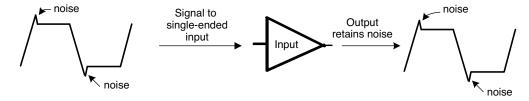

| Introduction                                                                | 19-1 |

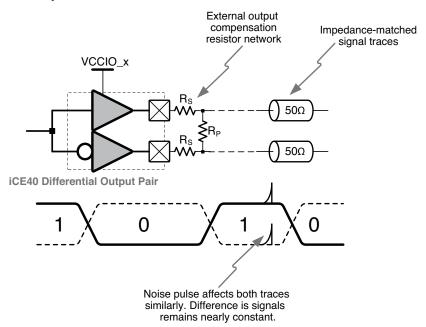

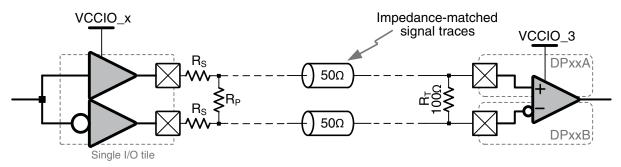

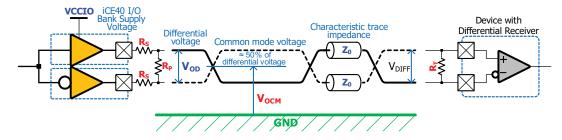

| Differential Outputs                                                        |      |

| Differential Inputs                                                         |      |

| LVDS and Sub-LVDS Termination                                               |      |

| Input Termination Resistor (RT)                                   | 19-4                 |

|-------------------------------------------------------------------|----------------------|

| Output Parallel Resistor (RP)                                     |                      |

| Output Series Resistor (RS)                                       |                      |

| Using the Companion iCE40 Differential I/O Calculator Spreadsheet |                      |

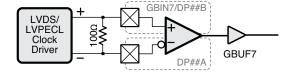

| Differential Clock Input                                          |                      |

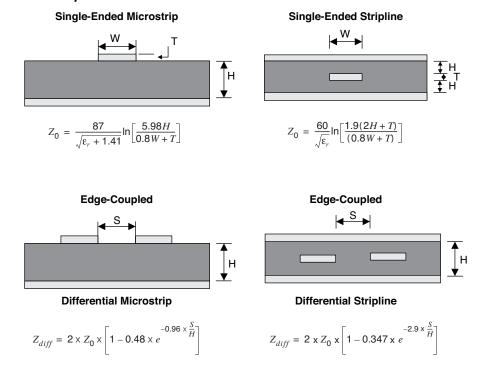

| iCE40 Differential Signaling Board Layout Requirements            |                      |

| Layout Recommendations to Minimize Reflection                     |                      |

| EMI and Noise Cancellation                                        |                      |

| Reducing EMI Noise                                                |                      |

| Defining Differential I/O                                         |                      |

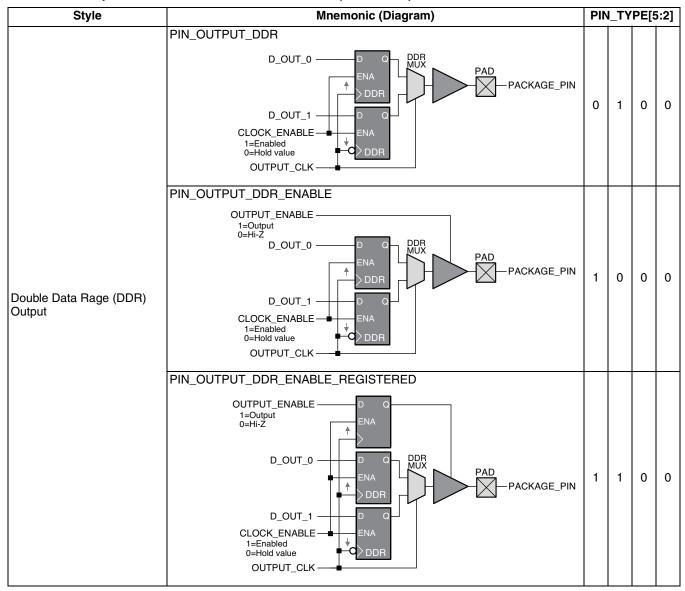

| SB IO Primitive                                                   |                      |

| SB_GB_IO Primitive                                                | 19-9                 |

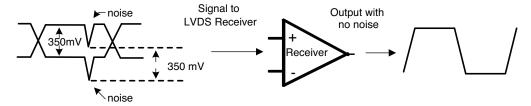

| PIN_TYPE Parameter                                                | 19-9                 |

| IO_STANDARD Parameter                                             | 19-13                |

| NEG_TRIGGER Parameter                                             | 19-14                |

| HDL Implementation Example                                        | 19-14                |

| VHDL Component Declaration                                        | 19-14                |

| Differential Clock Input                                          | 19-14                |

| Differential Input                                                |                      |

| Differential Output Pair                                          |                      |

| Applications                                                      | 19-17                |

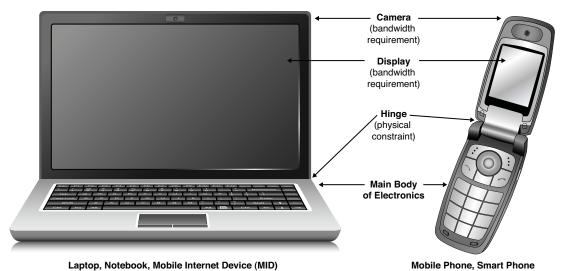

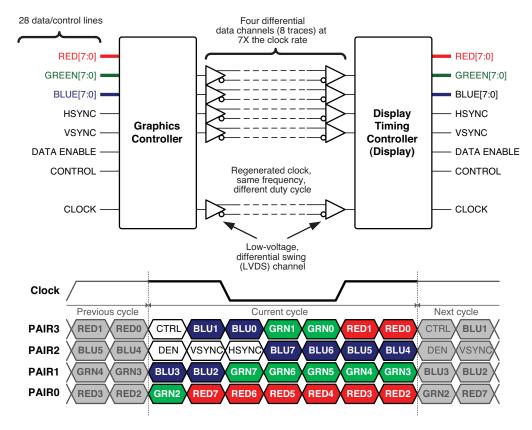

| Graphic Displays                                                  |                      |

| Cameras and Imagers                                               | 19-19                |

| Summary                                                           | 19-19                |

| References                                                        | 19-19                |

| Technical Support Assistance                                      | 19-19                |

| Revision History                                                  | 19-20                |

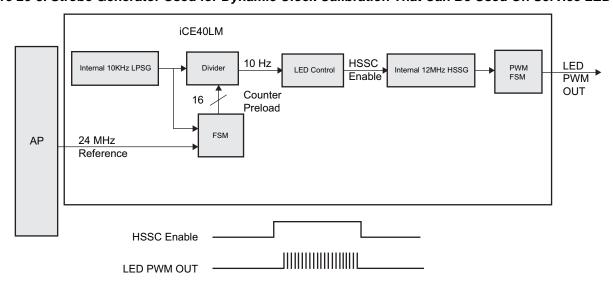

| CE40LM On-Chip                                                    |                      |

| Strobe Generator Usage Guide                                      |                      |

| Introduction                                                      |                      |

| Key Features                                                      |                      |

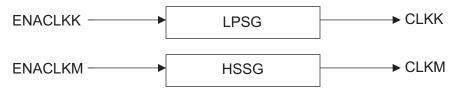

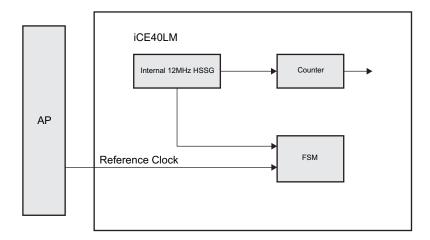

| On-Chip Strobe Generator Overview                                 |                      |

| I/O Port Description                                              |                      |

| Connectivity Guideline                                            |                      |

| Power Management Options                                          |                      |

| Technical Support Assistance                                      |                      |

| Revision History                                                  |                      |

| Appendix: Design Entry                                            |                      |

| LSOSC (LPSG) Usage with VHDL                                      |                      |

| LSOSC(LPSG) Usage with Verilog                                    |                      |

| HSOSC(HSSG) Usage with VHDL                                       |                      |

| HSOSC(HSSG) Usage with Verilog (route through fabric)             | 20-4                 |

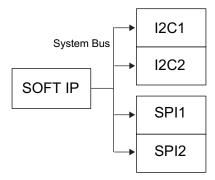

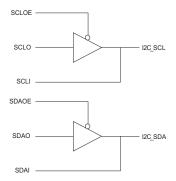

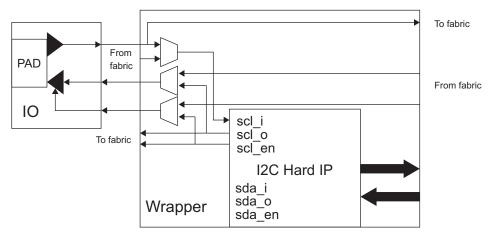

| CE40LM SPI/I2C Hardened IP                                        |                      |

| Usage Guide                                                       |                      |

| Introduction                                                      |                      |

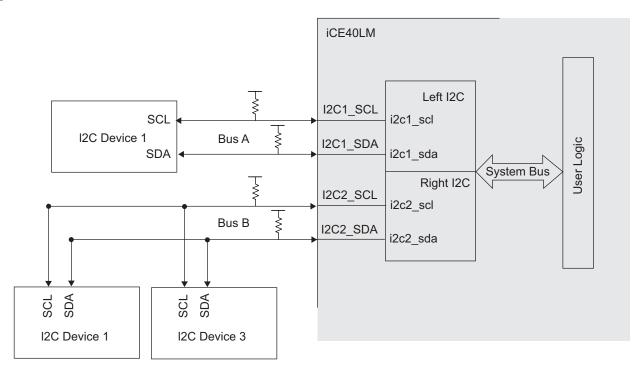

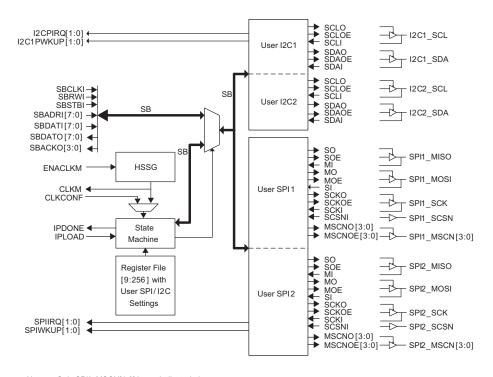

| I2C IP Core Overview                                              |                      |

| Key Features                                                      |                      |

| I2C Usage with Module Generation                                  |                      |

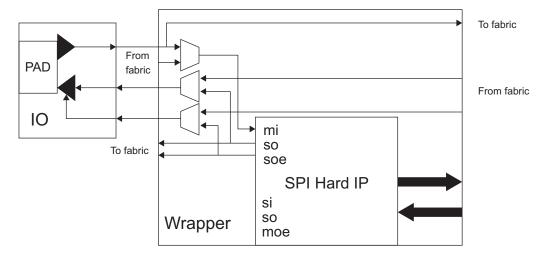

| SB_I2C Hard IP Macro Ports and Wrapper Connections                |                      |

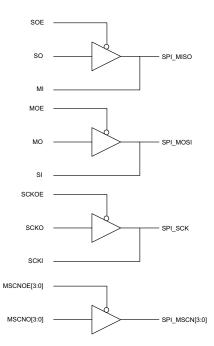

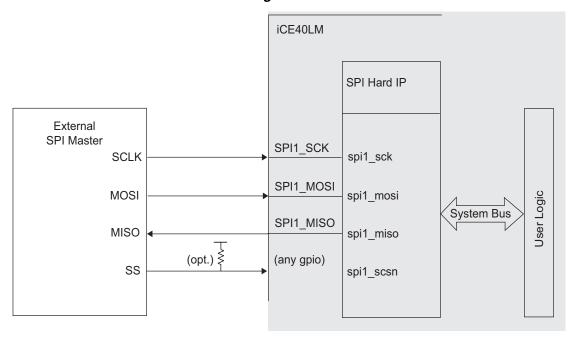

| iCE40LM I2C Usage Cases SPI IP Core Overview                      | 21-6                 |

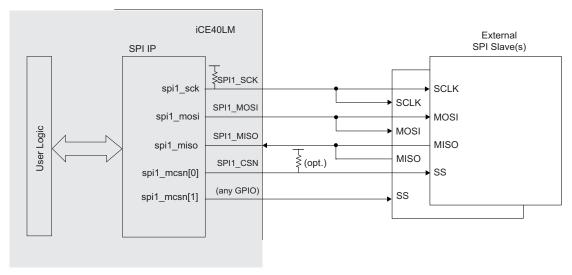

| S DI ID I OTO I MONIONI                                           |                      |

|                                                                   | 21-7                 |

| Key Features                                                      | 21-7<br>21-7         |

|                                                                   | 21-7<br>21-7<br>21-8 |

| ICE40LM SPI Usage Cases                                     | 21-12 |

|-------------------------------------------------------------|-------|

| Module Generator                                            |       |

| Key Features                                                | 21-14 |

| Technical Support Assistance                                |       |

| Revision History                                            |       |

| Advanced iCE40LM SPI/I2C                                    |       |

| Hardened IP Usage Guide                                     |       |

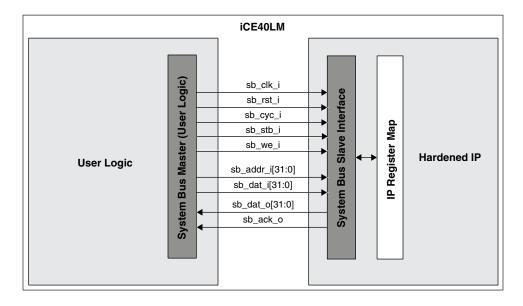

| Introduction                                                | 22-1  |

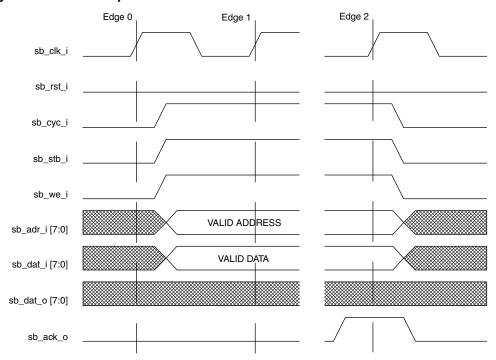

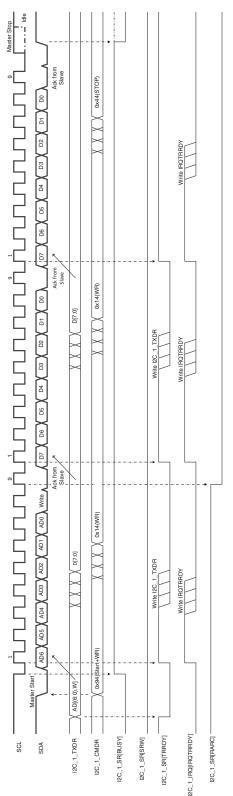

| System Bus Interface                                        |       |

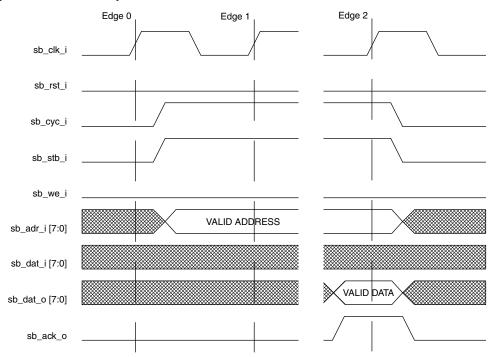

| System Bus Write Cycle                                      |       |

| System Bus Read Cycle                                       |       |

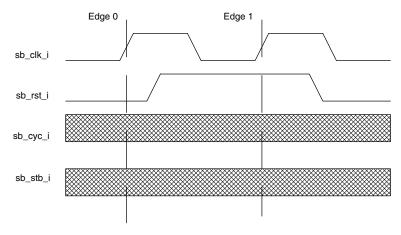

| System Bus Reset Cycle                                      |       |

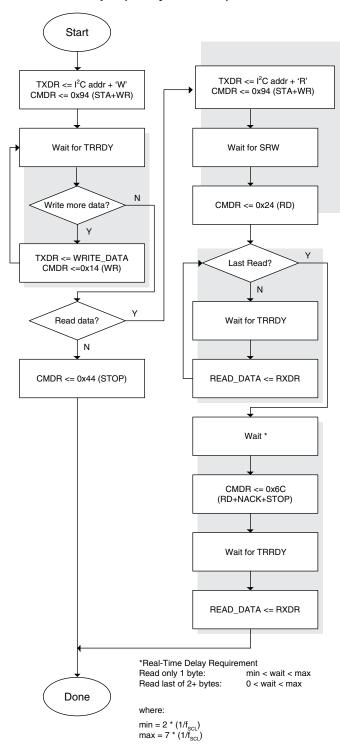

| Hardened I2C IP Cores                                       |       |

| I2C Registers                                               |       |

| I2C Read/Write Flow Chart                                   |       |

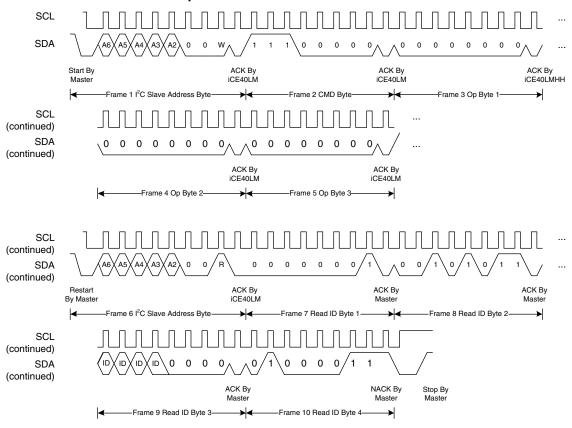

| I2C Framing                                                 |       |

| I2C Functional Waveforms                                    |       |

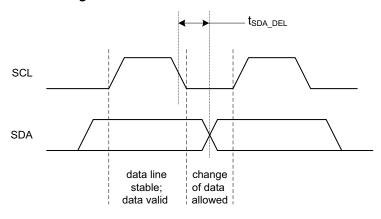

| I2C Timing Diagram                                          |       |

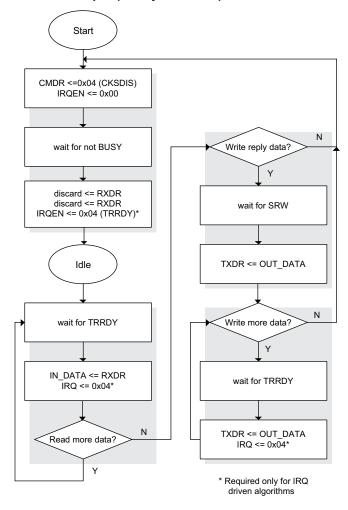

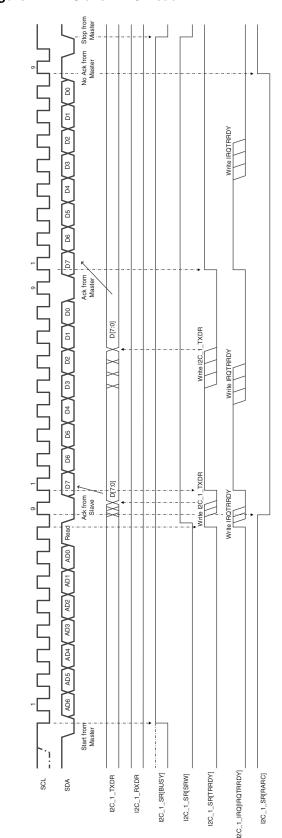

| Hardened SPI IP Core                                        |       |

| SPI Registers                                               |       |

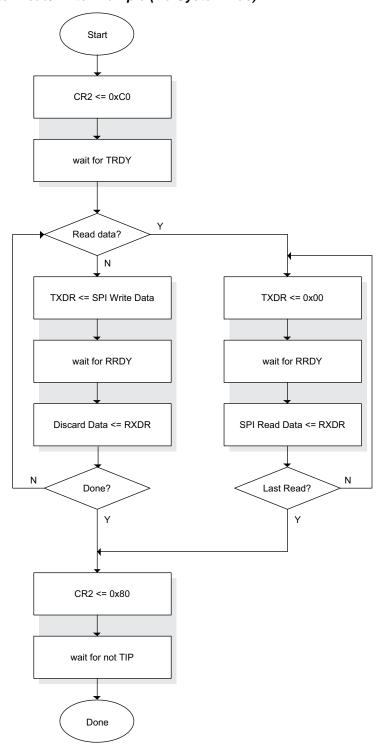

| SPI Read/Write Flow Chart                                   |       |

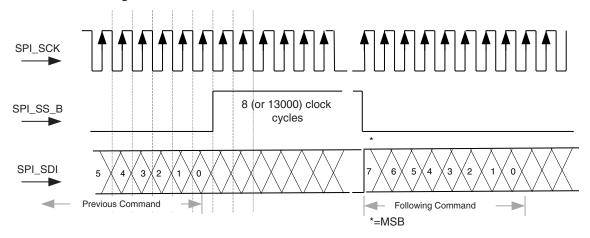

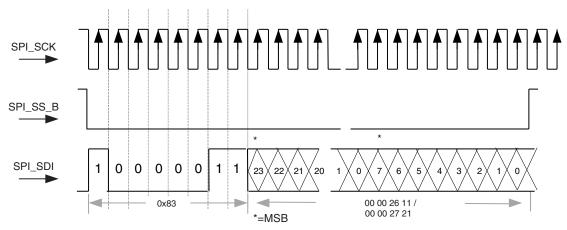

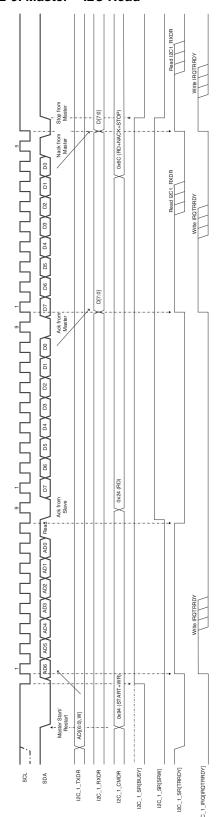

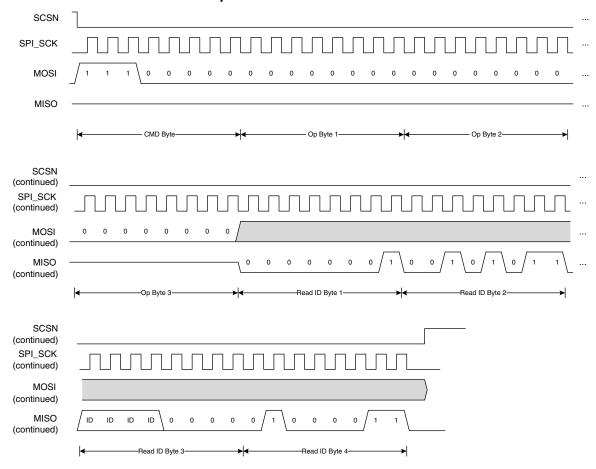

| SPI Framing                                                 |       |

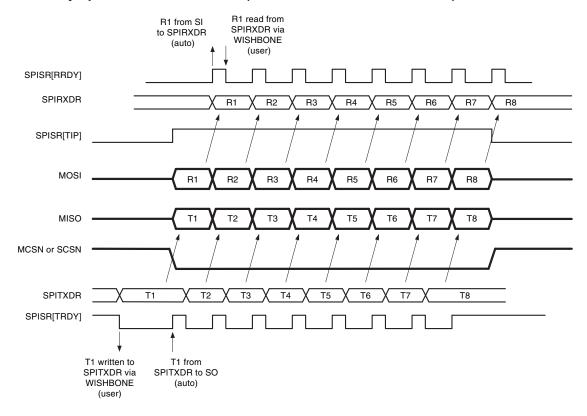

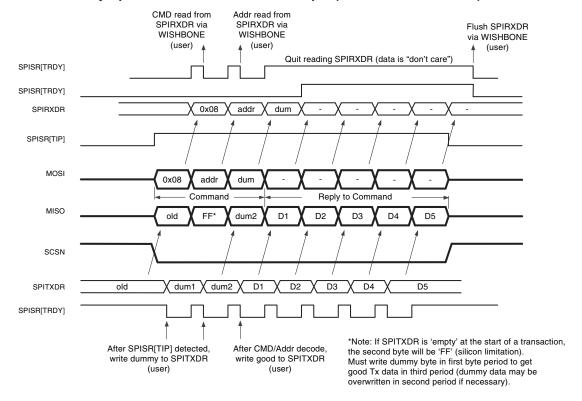

| SPI Functional Waveforms                                    |       |

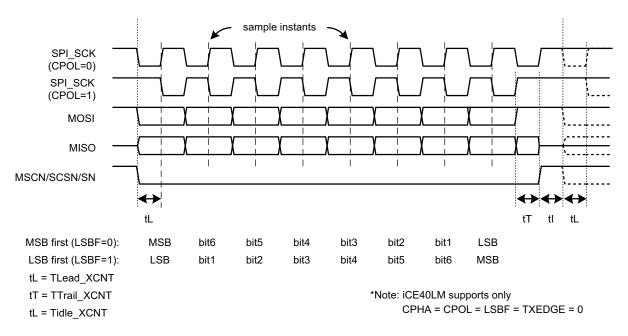

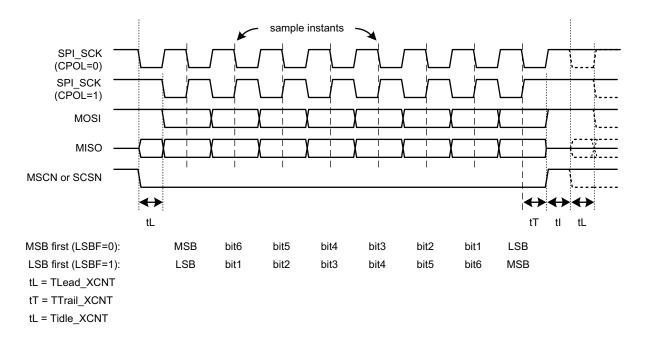

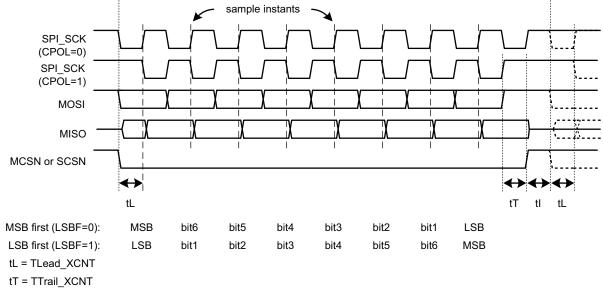

| SPI Timing Diagrams                                         |       |

| Technical Support Assistance                                |       |

| Revision History                                            |       |

| Section IV. iCE40 LP/HX/LM Family Handbook Revision History |       |

| ,                                                           | 00.4  |

| Revision History                                            | 23-   |

## Section I. iCE40 LP/HX Family Data Sheet

DS1040 Version 02.7, October 2013

# iCE40 LP/HX Family Data Sheet Introduction

October 2013 Data Sheet DS1040

## **Features**

### ■ Flexible Logic Architecture

Five devices with 384 to 7,680 LUT4s and 10 to 206 I/Os

#### ■ Ultra Low Power Devices

- Advanced 40 nm low power process

- As low as 21 μW standby power

- Programmable low swing differential I/Os

### **■** Embedded and Distributed Memory

Up to 128 Kbits sysMEM<sup>™</sup> Embedded Block RAM

## ■ Pre-Engineered Source Synchronous I/O

• DDR registers in I/O cells

## ■ High Performance, Flexible I/O Buffer

- Programmable sysIO<sup>™</sup> buffer supports wide range of interfaces:

- LVCMOS 3.3/2.5/1.8

- LVDS25E, subLVDS

- Schmitt trigger inputs, to 200 mV typical hysteresis

- Programmable pull-up mode

## ■ Flexible On-Chip Clocking

- Eight low-skew global clock resources

- Up to two analog PLLs per device

## ■ Flexible Device Configuration

- SRAM is configured through:

- Standard SPI Interface

- Internal Nonvolatile Configuration Memory (NVCM)

## ■ Broad Range of Package Options

- WLCSP, QFN, VQFP, TQFP, ucBGA, caBGA, and csBGA package options

- · Small footprint package options

- As small as 1.40x1.48mm

- · Advanced halogen-free packaging

Table 1-1. iCE40 Family Selection Guide

| Part Number                         |        | LP384         | LP640 | LP1K               | LP4K                  | LP8K                  | HX1K           | HX4K  | HX8K  |

|-------------------------------------|--------|---------------|-------|--------------------|-----------------------|-----------------------|----------------|-------|-------|

| Logic Cells (LUT + Flip-Flop        | )      | 384           | 640   | 1,280              | 3,520                 | 7,680                 | 1,280          | 3,520 | 7,680 |

| RAM4K Memory Blocks                 |        | 0             | 8     | 16                 | 20                    | 32                    | 16             | 20    | 32    |

| RAM4K RAM bits                      |        | 0             | 32K   | 64K                | 80K                   | 128K                  | 64K            | 80K   | 128K  |

| Phase-Locked Loops (PLLs)           | )      | 0             | 0     | 1 <sup>1</sup>     | <b>2</b> <sup>2</sup> | <b>2</b> <sup>2</sup> | 1 <sup>1</sup> | 2     | 2     |

| Maximum Programmable I/C            | ) Pins | 63            | 25    | 95                 | 167                   | 178                   | 95             | 95    | 206   |

| Maximum Differential Input F        | Pairs  | 8             | 3     | 12                 | 20                    | 23                    | 11             | 12    | 26    |

| High Current LED Drivers            |        | 0 3 3 0 0 0 0 |       |                    |                       | 0                     |                |       |       |

| Package                             | Code   |               |       | Programn           | nable I/O: I          | Max Inputs            | (LVDS25)       |       |       |

| 16 WLCSP<br>(1.40 x 1.48mm, 0.35mm) | SWG16  |               | 10(0) | 10(0)              |                       |                       |                |       |       |

| 32 QFN<br>(5 x 5mm, 0.5mm)          | SG32   | 21(3)         |       |                    |                       |                       |                |       |       |

| 36 ucBGA<br>(2.5 x 2.5mm, 0.4mm)    | СМ36   | 25(3)         |       | 25(3) <sup>1</sup> |                       |                       |                |       |       |

| 49 ucBGA<br>(3 x 3mm, 0.4mm)        | CM49   | 37(6)         |       | 35(5) <sup>1</sup> |                       |                       |                |       |       |

| 81 ucBGA<br>(4 x 4mm, 0.4mm)        | CM81   | 55(3)         |       | 63(8)              | 63(9) <sup>2</sup>    | 63(9) <sup>2</sup>    |                |       |       |

| 81 csBGA<br>(5 x 5mm, 0.5mm)        | CB81   |               |       | 62(9) <sup>1</sup> |                       |                       |                |       |       |

© 2013 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Table 1-1  | iCE40 Famil   | v Salaction | Guide | (continued)   |

|------------|---------------|-------------|-------|---------------|

| iable i-i. | IUE4U Fallill | v Selection | Guiue | (COIIIIIIuea) |

| 84 QFN<br>(7 x 7mm, 0.5mm)           | QN84  |  | 67(7) <sup>1</sup> |         |         |                    |         |         |

|--------------------------------------|-------|--|--------------------|---------|---------|--------------------|---------|---------|

| 100 VQFP<br>(14 x 14mm, 0.5mm)       | VQ100 |  |                    |         |         | 72(9) <sup>1</sup> |         |         |

| 121 ucBGA<br>(5 x 5mm, 0.4mm)        | CM121 |  | 95(12)             | 93(13)  | 93(13)  |                    |         |         |

| 121 csBGA<br>(6 x 6mm, 0.5mm)        | CB121 |  | 92(12)             |         |         |                    |         |         |

| 132 csBGA<br>(8 x 8mm, 0.5mm)        | CB132 |  |                    |         |         | 95(11)             | 95(12)  | 95(12)  |

| 144 TQFP<br>(20 x 20mm, 0.5mm)       | TQ144 |  |                    |         |         | 96(12)             | 107(14) |         |

| 225 ucBGA<br>(7 x 7mm, 0.4mm)        | CM225 |  |                    | 178(23) | 178(23) |                    |         | 178(23) |

| 256-ball caBGA<br>(14 x 14mm, 0.8mm) | CT256 |  |                    |         |         |                    |         | 206(26) |

- 1. No PLL available on the 16 WLCSP, 36 ucBGA, 81 csBGA, 84 QFN and 100 VQFP packages.

- 2. Only one PLL available on the 81 ucBGA package.

- 3. High Current I/Os only available on the 16 WLCSP package.

### Introduction

The iCE40 family of ultra-low power, non-volatile FPGAs has five devices with densities ranging from 384 to 7680 Look-Up Tables (LUTs). In addition to LUT-based, low-cost programmable logic, these devices feature Embedded Block RAM (EBR), Non-volatile Configuration Memory (NVCM) and Phase Locked Loops (PLLs). These features allow the devices to be used in low-cost, high-volume consumer and system applications. Select packages offer High-Current drivers that are ideal to drive three white LEDs, or one RGB LED.

The iCE40 devices are fabricated on a 40 nm CMOS low power process. The device architecture has several features such as programmable low-swing differential I/Os and the ability to turn off on-chip PLLs dynamically. These features help manage static and dynamic power consumption, resulting in low static power for all members of the family. The iCE40 devices are available in two versions – ultra low power (LP) and high performance (HX) devices.

The iCE40 FPGAs are available in a broad range of advanced halogen-free packages ranging from the space saving 1.40x1.48mm WLCSP to the PCB-friendly 20x20 mm TQFP. Table 1-1 shows the LUT densities, package and I/O options, along with other key parameters.

The iCE40 devices offer enhanced I/O features such as pull-up resistors. Pull-up features are controllable on a "per-pin" basis.

The iCE40 devices also provide flexible, reliable and secure configuration from on-chip NVCM. These devices can also configure themselves from external SPI Flash or be configured by an external master such as a CPU.

Lattice provides a variety of design tools that allow complex designs to be efficiently implemented using the iCE40 family of devices. Popular logic synthesis tools provide synthesis library support for iCE40. Lattice design tools use the synthesis tool output along with the user-specified preferences and constraints to place and route the design in the iCE40 device. These tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) modules, including a number of reference designs, licensed free of charge, optimized for the iCE40 FPGA family. By using these configurable soft core IP cores as standardized blocks, users are free to concentrate on the unique aspects of their design, increasing their productivity.

# iCE40 LP/HX Family Data Sheet Architecture

October 2013 Data Sheet DS1040

## **Architecture Overview**

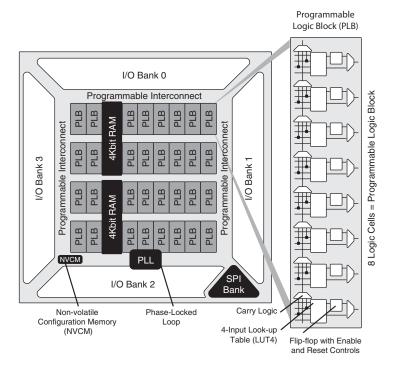

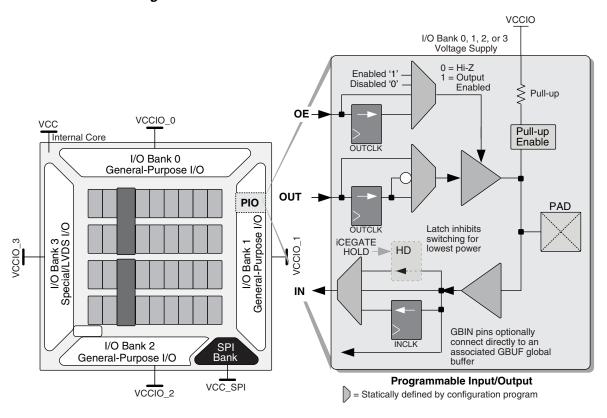

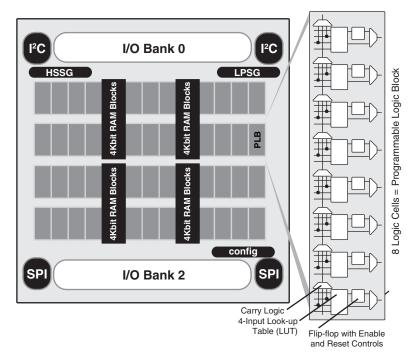

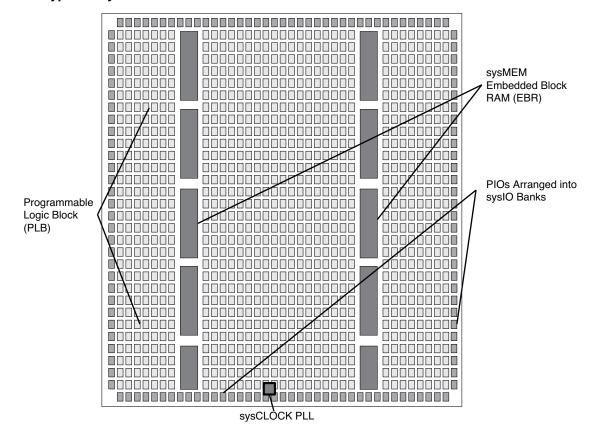

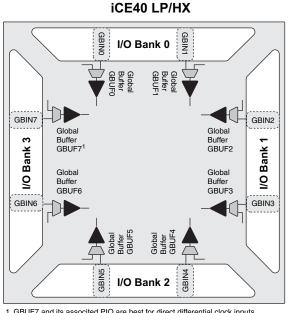

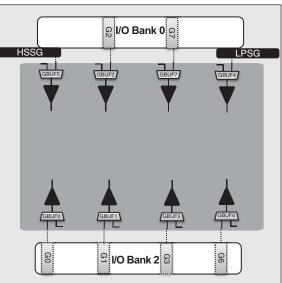

The iCE40 family architecture contains an array of Programmable Logic Blocks (PLB), sysCLOCK™ PLLs, Non-volatile Programmable Configuration Memory (NVCM) and blocks of sysMEM™ Embedded Block RAM (EBR) surrounded by Programmable I/O (PIO). Figure 2-1 shows the block diagram of the iCE40LP/HX1K device.

Figure 2-1. iCE40LP/HX1K Device, Top View

The logic blocks, Programmable Logic Blocks (PLB) and sysMEM EBR blocks, are arranged in a two-dimensional grid with rows and columns. Each column has either logic blocks or EBR blocks. The PIO cells are located at the periphery of the device, arranged in banks. The PLB contains the building blocks for logic, arithmetic, and register functions. The PIOs utilize a flexible I/O buffer referred to as a sysIO buffer that supports operation with a variety of interface standards. The blocks are connected with many vertical and horizontal routing channel resources. The place and route software tool automatically allocates these routing resources.

In the iCE40 family, there are up to four independent sysIO banks. Note on some packages  $V_{CCIO}$  banks are tied together. There are different types of I/O buffers on the different banks. Refer to the details in later sections of this document. The sysMEM EBRs are large 4 Kbit, dedicated fast memory blocks. These blocks can be configured as RAM, ROM or FIFO.

The iCE40 architecture also provides up to two sysCLOCK Phase Locked Loop (PLL) blocks. The PLLs have multiply, divide, and phase shifting capabilities that are used to manage the frequency and phase relationships of the clocks.

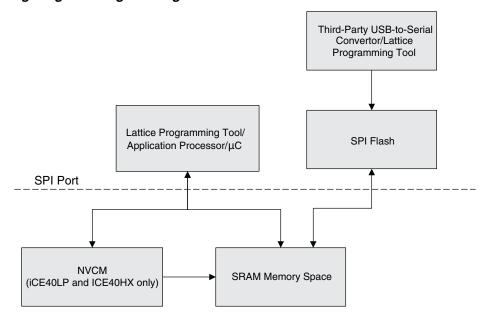

Every device in the family has a SPI port that supports programming and configuration of the device. The iCE40 includes on-chip, Nonvolatile Configuration Memory (NVCM).

© 2013 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### **PLB Blocks**

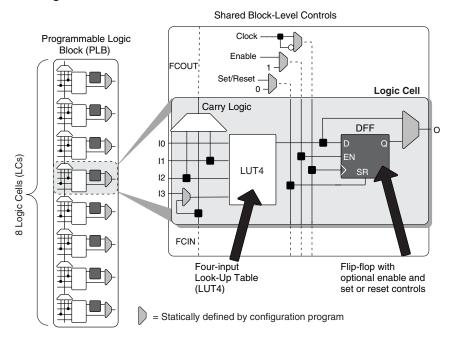

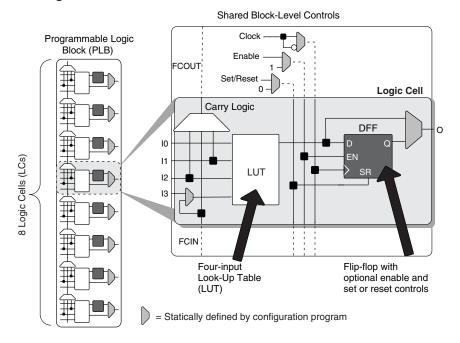

The core of the iCE40 device consists of Programmable Logic Blocks (PLB) which can be programmed to perform logic and arithmetic functions. Each PLB consists of eight interconnected Logic Cells (LC) as shown in Figure 2-2. Each LC contains one LUT and one register.

Figure 2-2. PLB Block Diagram

#### **Logic Cells**

Each Logic Cell includes three primary logic elements shown in Figure 2-2.

- A four-input Look-Up Table (LUT4) builds any combinational logic function, of any complexity, requiring up to four inputs. Similarly, the LUT4 element behaves as a 16x1 Read-Only Memory (ROM). Combine and cascade multiple LUT4s to create wider logic functions.

- A 'D'-style Flip-Flop (DFF), with an optional clock-enable and reset control input, builds sequential logic functions. Each DFF also connects to a global reset signal that is automatically asserted immediately following device configuration.

- Carry Logic boosts the logic efficiency and performance of arithmetic functions, including adders, subtracters, comparators, binary counters and some wide, cascaded logic functions.

Table 2-1. Logic Cell Signal Descriptions

| Function | Туре             | Signal Names           | Description                                                                                                          |

|----------|------------------|------------------------|----------------------------------------------------------------------------------------------------------------------|

| Input    | Data signal      | 10, 11, 12, 13         | Inputs to LUT4                                                                                                       |

| Input    | Control signal   | Enable                 | Clock enable shared by all LCs in the PLB                                                                            |

| Input    | Control signal   | Set/Reset <sup>1</sup> | Asynchronous or synchronous local set/reset shared by all LCs in the PLB.                                            |

| Input    | Control signal   | Clock                  | Clock one of the eight Global Buffers, or from the general-purpose interconnects fabric shared by all LCs in the PLB |

| Input    | Inter-PLB signal | FCIN                   | Fast carry in                                                                                                        |

| Output   | Data signals     | 0                      | LUT4 or registered output                                                                                            |

| Output   | Inter-PFU signal | FCOUT                  | Fast carry out                                                                                                       |

<sup>1.</sup> If Set/Reset is not used, then the flip-flop is never set/reset, except when cleared immediately after configuration.

## Routing

There are many resources provided in the iCE40 devices to route signals individually with related control signals. The routing resources consist of switching circuitry, buffers and metal interconnect (routing) segments.

The inter-PLB connections are made with three different types of routing resources: Adjacent (spans two PLBs), x4 (spans five PLBs) and x12 (spans thirteen PLBs). The Adjacent, x4 and x12 connections provide fast and efficient connections in the diagonal, horizontal and vertical directions.

The design tool takes the output of the synthesis tool and places and routes the design.

### **Clock/Control Distribution Network**

Each iCE40 device has eight global inputs, two pins on each side of the device. Note that not all GBINs are available in all packages.

These global inputs can be used as high fanout nets, clock, reset or enable signals. The dedicated global pins are identified as GBIN[7:0] and the global buffers are identified as-GBUF[7:0]. These eight inputs may be used as general purpose I/O if they are not used to drive the clock nets. Global buffer GBUF7 in I/O Bank 3 also provides an optional direct LVDS25 or subLVDS differential clock input.

Table 2-2 lists the connections between a specific global buffer and the inputs on a PLB. All global buffers optionally connect to the PLB CLK input. Any four of the eight global buffers can drive logic inputs to a PLB. Even-numbered global buffers optionally drive the Set/Reset input to a PLB. Similarly, odd-numbered buffers optionally drive the PLB clock-enable input.

Table 2-2. Global Buffer (GBUF) Connections to Programmable Logic Blocks

| Global Buffer | LUT Inputs      | Clock | Clock Enable | Reset |

|---------------|-----------------|-------|--------------|-------|

| GBUF0         |                 | ✓     | ✓            |       |

| GBUF1         |                 | ✓     |              | ✓     |

| GBUF2         |                 | ✓     | ✓            |       |

| GBUF3         | Yes, any 4 of 8 | ✓     |              | ✓     |

| GBUF4         | GBUF Inputs     | ✓     | ✓            |       |

| GBUF5         |                 | ✓     |              | ✓     |

| GBUF6         |                 | ✓     | ✓            |       |

| GBUF7         |                 | ✓     |              | ✓     |

The maximum frequency for the global buffers are shown in the iCE40 External Switching Characteristics tables later in this document.

#### **Global Hi-Z Control**

The global high-impedance control signal, GHIZ, connects to all I/O pins on the iCE40 device. This GHIZ signal is automatically asserted throughout the configuration process, forcing all user I/O pins into their high-impedance state.

#### **Global Reset Control**

The global reset control signal connects to all PLB and PIO flip-flops on the iCE40 device. The global reset signal is automatically asserted throughout the configuration process, forcing all flip-flops to their defined wake-up state. For PLB flip-flops, the wake-up state is always reset, regardless of the PLB flip-flop primitive used in the application.

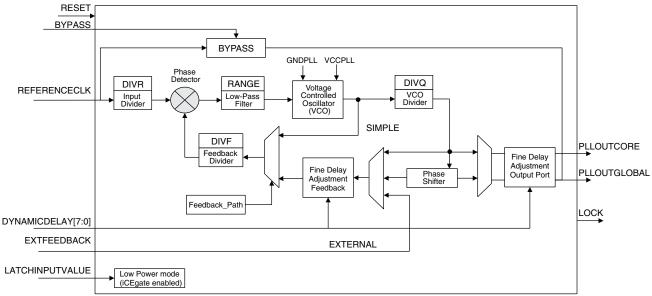

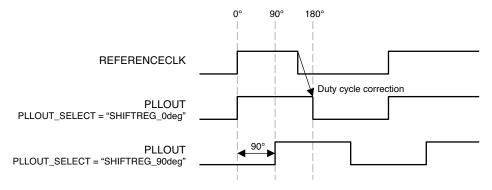

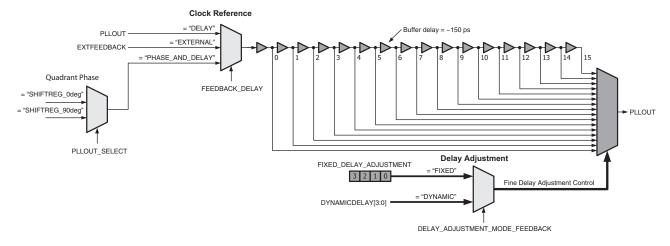

## sysCLOCK Phase Locked Loops (PLLs)

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. The iCE40 devices have one or more sys-CLOCK PLLs. REFERENCECLK is the reference frequency input to the PLL and its source can come from an external I/O pin or from internal routing. EXTFEEDBACK is the feedback signal to the PLL which can come from internal routing or an external I/O pin. The feedback divider is used to multiply the reference frequency and thus synthesize a higher frequency clock output.

The PLLOUT output has an output divider, thus allowing the PLL to generate different frequencies for each output. The output divider can have a value from 1 to 6. The PLLOUT outputs can all be used to drive the iCE40 global clock network directly or general purpose routing resources can be used.

The LOCK signal is asserted when the PLL determines it has achieved lock and de-asserted if a loss of lock is detected. A block diagram of the PLL is shown in Figure 2-3.

The timing of the device registers can be optimized by programming a phase shift into the PLLOUT output clock which will advance or delay the output clock with reference to the REFERENCECLK clock. This phase shift can be either programmed during configuration or can be adjusted dynamically. In dynamic mode, the PLL may lose lock after a phase adjustment on the output used as the feedback source and not relock until the t<sub>LOCK</sub> parameter has been satisfied.

For more details on the PLL, see TN1251, iCE40 sysCLOCK PLL Design and Usage Guide.

Figure 2-3. PLL Diagram

Table 2-3 provides signal descriptions of the PLL block.

Table 2-3. PLL Signal Descriptions

| Signal Name       | Direction | Description                                                                                                                                                                                 |

|-------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFERENCECLK      | Input     | Input reference clock                                                                                                                                                                       |

| DVDAGG            | Input     | When FEEDBACK_PATH is set to SIMPLE, the BYPASS control selects which clock signal connects to the PLLOUT output.                                                                           |

| BYPASS            | Input     | 0 = PLL generated signal<br>1 = REFERENCECLK                                                                                                                                                |

| EXTFEEDBACK       | Input     | External feedback input to PLL. Enabled when the FEEDBACK_PATH attribute is set to EXTERNAL.                                                                                                |

| DYNAMICDELAY[3:0] | Input     | Fine delay adjustment control inputs. Enabled when DELAY_ADJUSTMENT_MODE is set to DYNAMIC.                                                                                                 |

| LATCHINPUTVALUE   | Input     | When enabled, forces the PLL into low-power mode; PLL output is held static at the last input clock value. Set ENABLE ICEGATE_PORTA and PORTB to '1' to enable.                             |

| PLLOUTGLOBAL      | Output    | Output from the Phase-Locked Loop (PLL). Drives a global clock network on the FPGA. The port has optimal connections to global clock buffers GBUF4 and GBUF5.                               |

| PLLOUTCORE        | Output    | Output clock generated by the PLL, drives regular FPGA routing. The frequency generated on this output is the same as the frequency of the clock signal generated on the PLLOUTLGOBAL port. |

| LOCK              | Output    | When High, indicates that the PLL output is phase aligned or locked to the input reference clock.                                                                                           |

| RESET             | Input     | Active low reset.                                                                                                                                                                           |

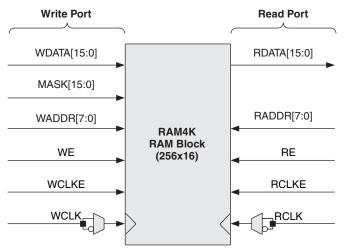

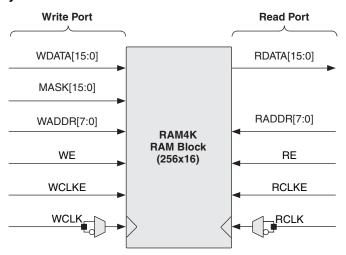

## sysMEM Embedded Block RAM Memory

Larger iCE40 device includes multiple high-speed synchronous sysMEM Embedded Block RAMs (EBRs), each 4 Kbit in size. This memory can be used for a wide variety of purposes including data buffering, and FIFO.

#### sysMEM Memory Block

The sysMEM block can implement single port, pseudo dual port, or FIFO memories with programmable logic resources. Each block can be used in a variety of depths and widths as shown in Table 2-4.

Table 2-4. sysMEM Block Configurations<sup>1</sup>

| Block RAM<br>Configuration                                           | Block RAM<br>Configuration<br>and Size | WADDR Port<br>Size (Bits) | WDATA Port<br>Size (Bits) | RADDR Port<br>Size (Bits) | RDATA Port<br>Size (Bits) | MASK Port<br>Size (Bits) |

|----------------------------------------------------------------------|----------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--------------------------|

| SB_RAM256x16<br>SB_RAM256x16NR<br>SB_RAM256x16NW<br>SB_RAM256x16NRNW | 256x16 (4K)                            | 8 [7:0]                   | 16 [15:0]                 | 8 [7:0]                   | 16 [15:0]                 | 16 [15:0]                |

| SB_RAM512x8<br>SB_RAM512x8NR<br>SB_RAM512x8NW<br>SB_RAM512x8NRNW     | 512x8 (4K)                             | 9 [8:0]                   | 8 [7:0]                   | 9 [8:0]                   | 8 [7:0]                   | No Mask Port             |

| SB_RAM1024x4<br>SB_RAM1024x4NR<br>SB_RAM1024x4NW<br>SB_RAM1024x4NRNW | 1024x4 (4K)                            | 10 [9:0]                  | 4 [3:0]                   | 10 [9:0]                  | 4 [3:0]                   | No Mask Port             |

| SB_RAM2048x2<br>SB_RAM2048x2NR<br>SB_RAM2048x2NW<br>SB_RAM2048x2NRNW | 2048x2 (4K)                            | 11 [10:0]                 | 2 [1:0]                   | 11 [10:0]                 | 2 [1:0]                   | No Mask Port             |

<sup>1.</sup> For iCE40 EBR primitives with a negative-edged Read or Write clock, the base primitive name is appended with a 'N' and a 'R' or 'W' depending on the clock that is affected.

### **RAM Initialization and ROM Operation**

If desired, the contents of the RAM can be pre-loaded during device configuration.

By preloading the RAM block during the chip configuration cycle and disabling the write controls, the sysMEM block can also be utilized as a ROM.

Note the sysMEM Embedded Block RAM Memory address 0 cannot be initialized.

#### **Memory Cascading**

Larger and deeper blocks of RAM can be created using multiple EBR sysMEM Blocks.

#### **RAM4k Block**

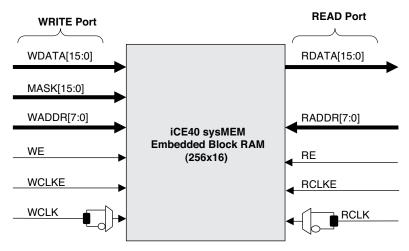

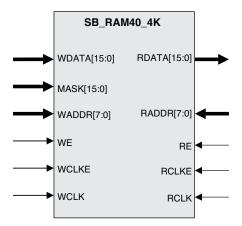

Figure 2-4 shows the 256x16 memory configurations and their input/output names. In all the sysMEM RAM modes, the input data and addresses for the ports are registered at the input of the memory array.

Figure 2-4. sysMEM Memory Primitives

Table 2-5. EBR Signal Descriptions

| Signal Name | Direction | Description                                                                               |

|-------------|-----------|-------------------------------------------------------------------------------------------|

| WDATA[15:0] | Input     | Write Data input.                                                                         |

| MASK[15:0]  | Input     | Masks write operations for individual data bit-lines.  0 = write bit; 1 = don't write bit |

| WADDR[7:0]  | Input     | Write Address input. Selects one of 256 possible RAM locations.                           |

| WE          | Input     | Write Enable input.                                                                       |

| WCLKE       | Input     | Write Clock Enable input.                                                                 |

| WCLK        | Input     | Write Clock input. Default rising-edge, but with falling-edge option.                     |

| RDATA[15:0] | Output    | Read Data output.                                                                         |

| RADDR[7:0]  | Input     | Read Address input. Selects one of 256 possible RAM locations.                            |

| RE          | Input     | Read Enable input.                                                                        |

| RCLKE       | Input     | Read Clock Enable input.                                                                  |

| RCLK        | Input     | Read Clock input. Default rising-edge, but with falling-edge option.                      |

For further information on the sysMEM EBR block, please refer to TN1250, Memory Usage Guide for iCE40 Devices.

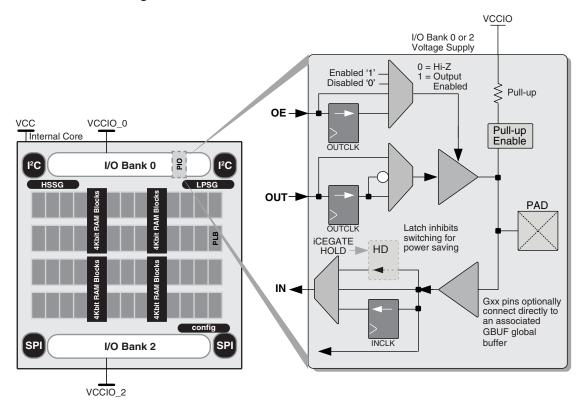

## sysIO

#### **Buffer Banks**

iCE40 devices have up to four I/O banks with independent Vccio rails with an additional configuration bank  $V_{CC\_SPI}$  for the SPI I/Os.

#### Programmable I/O (PIO)

The programmable logic associated with an I/O is called a PIO. The individual PIO are connected to their respective sysIO buffers and pads. The PIOs are placed on all four sides of the device.

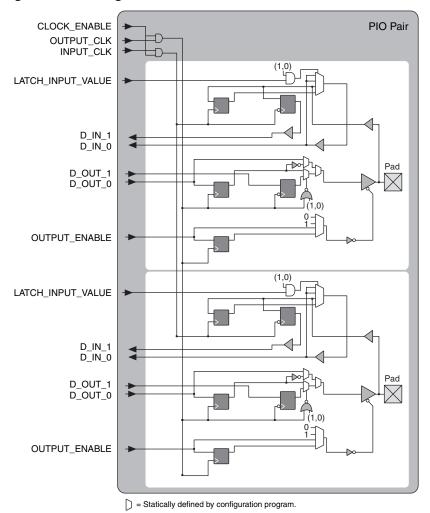

Figure 2-5. I/O Bank and Programmable I/O Cell

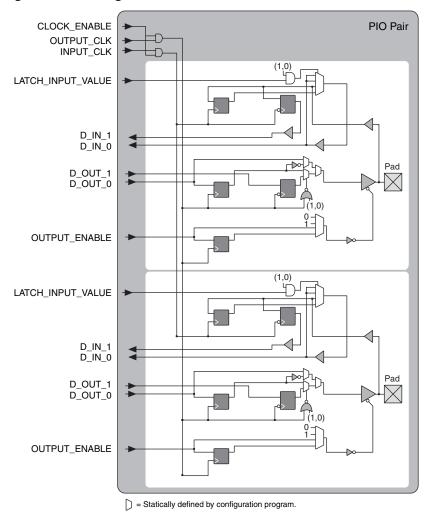

The PIO contains three blocks: an input register block, output register block iCEgate<sup>™</sup> and tri-state register block. To save power, the optional iCEgate<sup>™</sup> latch can selectively freeze the state of individual, non-registered inputs within an I/O bank. Note that the freeze signal is common to the bank. These blocks can operate in a variety of modes along with the necessary clock and selection logic.

### Input Register Block

The input register blocks for the PIOs on all edges contain registers that can be used to condition high-speed interface signals before they are passed to the device core. In Generic DDR mode, two registers are used to sample the data on the positive and negative edges of the system clock signal, creating two data streams.

### **Output Register Block**

The output register block can optionally register signals from the core of the device before they are passed to the syslO buffers. In Generic DDR mode, two registers are used to capture the data on the positive and negative edge of the system clock and then muxed creating one data stream.

Figure 2-6 shows the input/output register block for the PIOs.

Figure 2-6. iCE I/O Register Block Diagram

Table 2-6. PIO Signal List

| Pin Name          | I/O Type | Description                   |

|-------------------|----------|-------------------------------|

| OUTPUT_CLK        | Input    | Output register clock         |

| CLOCK_ENABLE      | Input    | Clock enable                  |

| INPUT_CLK         | Input    | Input register clock          |

| OUTPUT_ENABLE     | Input    | Output enable                 |

| D_OUT_0/1         | Input    | Data from the core            |

| D_IN_0/1          | Output   | Data to the core              |

| LATCH_INPUT_VALUE | Input    | Latches/holds the Input Value |

## sysIO Buffer

Each I/O is associated with a flexible buffer referred to as a sysIO buffer. These buffers are arranged around the periphery of the device in groups referred to as banks. The sysIO buffers allow users to implement a wide variety of standards that are found in today's systems including LVCMOS and LVDS25.

High Current LED Drivers combine three sysIO buffers together. This allows for programmable drive strength. This also allows for high current drivers that are ideal to drive three white LEDs, or one RGB LED. Each bank is capable of supporting multiple I/O standards including single-ended LVCMOS buffers and differential LVDS25E output buf-

fers. Bank 3 additionally supports differential LVDS25 input buffers. Each sysIO bank has its own dedicated power supply.

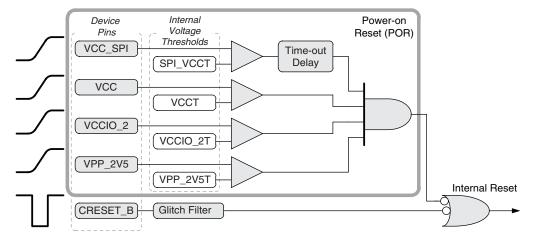

#### Typical I/O Behavior During Power-up

The internal power-on-reset (POR) signal is deactivated when  $V_{CC}$ ,  $V_{CCIO\_2}$ ,  $V_{PP\_2V5}$ , and  $V_{CC\_SPI}$  have reached the level defined in the Power-On-Reset Voltage table in the DC and Switching Characteristics section of this data sheet. After the POR signal is deactivated, the FPGA core logic becomes active. It is the user's responsibility to ensure that all  $V_{CCIO}$  banks are active with valid input logic levels to properly control the output logic states of all the I/O banks that are critical to the application. The default configuration of the I/O pins in a device prior to configuration is tri-stated with a weak pull-up to  $V_{CCIO}$ . The I/O pins will maintain the pre-configuration state until  $V_{CC}$  and  $V_{CCIO}$  (for I/O banks containing configuration I/Os) have reached levels, at which time the I/Os will take on the software user-configured settings only after a proper download/configuration. Unused IOs are automatically blocked and the pullup termination is disabled.

#### **Supported Standards**

The iCE40 sysIO buffer supports both single-ended and differential input standards. The single-ended standard supported is LVCMOS. The buffer supports the LVCMOS 1.8, 2.5, and 3.3V standards. The buffer has individually configurable options for bus maintenance (weak pull-up or none).

Table 2-7 and Table 2-8 show the I/O standards (together with their supply and reference voltages) supported by the iCE40 devices.

Table 2-7. Supported Input Standards

| Input Standard          | V <sub>CCIO</sub> (Typical) |      |      |  |  |

|-------------------------|-----------------------------|------|------|--|--|

| iliput Stalldard        | 3.3V                        | 2.5V | 1.8V |  |  |

| Single-Ended Interfaces |                             |      |      |  |  |

| LVCMOS33                | ✓                           |      |      |  |  |

| LVCMOS25                |                             | ✓    |      |  |  |

| LVCMOS18                |                             |      | ✓    |  |  |

| Differential Interfaces | •                           |      |      |  |  |

| LVDS25 <sup>1</sup>     |                             | ✓    |      |  |  |

| subLVDS <sup>1</sup>    |                             |      | ✓    |  |  |

<sup>1.</sup> Bank 3 only.

Table 2-8. Supported Output Standards

| Output Standard         | V <sub>CCIO</sub> (Typical) |

|-------------------------|-----------------------------|

| Single-Ended Interfaces |                             |

| LVCMOS33                | 3.3                         |

| LVCMOS25                | 2.5                         |

| LVCMOS18                | 1.8                         |

| Differential Interfaces |                             |

| LVDS25E <sup>1</sup>    | 2.5                         |

| subLVDSE <sup>1</sup>   | 1.8                         |

<sup>1.</sup> These interfaces can be emulated with external resistors in all devices.

## **Non-Volatile Configuration Memory**

All iCE40 devices provide a Non-Volatile Configuration Memory (NVCM) block which can be used to configure the device.

For more information on the NVCM, please refer to TN1248, iCE40 Programming and Configuration Usage Guide.

#### **Power On Reset**

iCE40 devices have power-on reset circuitry to monitor  $V_{CC}$ ,  $V_{CCIO\_2}$ ,  $V_{PP\_2V5}$ , and  $V_{CC\_SPI}$  voltage levels during power-up and operation. At power-up, the POR circuitry monitors  $V_{CC}$ ,  $V_{CCIO\_2}$ ,  $V_{PP\_2V5}$ , and  $V_{CC\_SPI}$  (controls configuration) voltage levels. It then triggers download from the on-chip NVCM or external Flash memory after reaching the power-up levels specified in the Power-On-Reset Voltage table in the DC and Switching Characteristics section of this data sheet. Before and during configuration, the I/Os are held in tri-state. I/Os are released to user functionality once the device has finished configuration.

## **Programming and Configuration**

This section describes the programming and configuration of the iCE40 family.

#### **Device Programming**

The NVCM memory can be programmed through the SPI port.

### **Device Configuration**

There are various ways to configure the Configuration RAM (CRAM) including:

- 1. Internal NVCM Download

- 2. From a SPI Flash (Master SPI mode)

- 3. System microprocessor to drive a Serial Slave SPI port (SSPI mode)

The image to configure the CRAM can be selected by the user on power up (Cold Boot) or once powered up (Warm Boot).

For more details on programming and configuration, see TN1248, iCE40 Programming and Configuration Usage Guide.

## **Power Saving Options**

iCE40 devices are available in two options for maximum flexibility: LP and HX devices. The LP devices have ultra low static and dynamic power consumption. HX devices are designed to provide high performance. Both the LP and the HX devices operate at 1.2V  $V_{\rm CC}$ .

iCE40 devices feature iCEGate and PLL low power mode to allow users to meet the static and dynamic power requirements of their applications. While these features are available in both device types, these features are mainly intended for use with iCE40 LP devices to manage power consumption.

Table 2-9. iCE40 Power Saving Features Description

| Device Subsystem | Feature Description                                                                                                                                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | When LATCHINPUTVALUE is enabled, forces the PLL into low-power mode; PLL output held static at last input clock value.                                                                                                          |

|                  | To save power, the optional iCEgate latch can selectively freeze the state of individual, non-registered inputs within an I/O bank. Registered inputs are effectively frozen by their associated clock or clock-enable control. |

# iCE40 LP/HX Family Data Sheet DC and Switching Characteristics

October 2013 Data Sheet DS1040

## **Absolute Maximum Ratings**<sup>1, 2, 3, 4</sup>

|                                                              | iCE40 LP/HX    |

|--------------------------------------------------------------|----------------|

| Supply Voltage V <sub>CC</sub>                               | 0.5 to 1.42V   |

| Output Supply Voltage V <sub>CCIO,</sub> V <sub>CC_SPI</sub> | 0.5 to 3.60V   |

| NVCM Supply Voltage V <sub>PP_2V5</sub>                      | 0.5 to 3.60V   |

| PLL Supply Voltage V <sub>CCPLL</sub>                        | 0.5 to 1.30V   |

| I/O Tri-state Voltage Applied.                               | 0.5 to 3.60V   |

| Dedicated Input Voltage Applied                              | 0.5 to 3.60V   |

| Storage Temperature (Ambient)                                | -65°C to 150°C |

| Junction Temperature (T <sub>J</sub> )                       | -55°C to 125°C |

<sup>1.</sup> Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

- 2. Compliance with the Lattice Thermal Management document is required.

- 3. All voltages referenced to GND.

- IOs can support a 200mV Overshoot above the Recommend Operating Conditions V<sub>CCIO</sub> (Max) and -200mV Undershoot below V<sub>IL</sub> (Min).

Overshoot and Undershoot is permitted for 25% duty cycle but must not exceed 1.6ns.

## Recommended Operating Conditions<sup>1</sup>

| Symbol                               | Parameter                                                         |                          |      | Max. | Units |

|--------------------------------------|-------------------------------------------------------------------|--------------------------|------|------|-------|

| V <sub>CC</sub> <sup>1</sup>         | Core Supply Voltage                                               |                          | 1.14 | 1.26 | V     |

|                                      |                                                                   | Slave SPI Configuration  | 1.71 | 3.46 | V     |

| V                                    | V <sub>PP 2V5</sub> NVCM Programming and                          | Master SPI Configuration | 2.30 | 3.46 | V     |

| V <sub>PP_2V5</sub>                  | V <sub>PP_2V5</sub> NVCM Programming and Operating Supply Voltage | Configure from NVCM      | 2.30 | 3.46 | V     |

|                                      |                                                                   | NVCM Programming         | 2.30 | 3.00 | V     |

| V <sub>PP_FAST</sub> <sup>4</sup>    | Optional fast NVCM programming supply. Leave unconnected.         |                          | N/A  | N/A  | V     |

| V <sub>CCPLL</sub> <sup>5, 6</sup>   | PLL Supply Voltage                                                |                          | 1.14 | 1.26 | V     |

| 1, 2, 3                              | I/O Driver Supply Voltage                                         | V <sub>CCIO0-3</sub>     | 1.71 | 3.46 | V     |

| V <sub>CCIO</sub> <sup>1, 2, 3</sup> | 1/O Driver Supply voltage                                         | V <sub>CC_SPI</sub>      | 1.71 | 3.46 | V     |

| t <sub>JIND</sub>                    | Junction Temperature Industrial Operation                         |                          | -40  | 100  | °C    |

| t <sub>PROG</sub>                    | Junction Temperature NVCM Programming                             |                          | 10   | 30   | °C    |

|                                      |                                                                   |                          |      |      |       |

Like power supplies must be tied together. For example, if V<sub>CCIO</sub> and V<sub>CC\_SPI</sub> are both the same voltage, they must also be the same supply.

<sup>2.</sup> See recommended voltages by I/O standard in subsequent table.

<sup>3.</sup>  $V_{CCIO}$  pins of unused I/O banks should be connected to the  $V_{CC}$  power supply on boards.

V<sub>PP\_FAST</sub>, used only for fast production programming, must be left floating or unconnected in applications, except CM36 and CM49 packages MUST have the V<sub>PP\_FAST</sub> ball connected to V<sub>CCIO\_0</sub> ball externally.

<sup>5.</sup> No PLL available on the iCE40LP384 and iCE40LP640 device.

<sup>6.</sup>  $V_{CCPLL}$  is tied to  $V_{CC}$  internally in packages without PLLs pins.

# Power Supply Ramp Rates<sup>1, 2</sup>

| Symbol            | Parameter       |                                                                                               | Min. | Max. | Units |

|-------------------|-----------------|-----------------------------------------------------------------------------------------------|------|------|-------|

|                   |                 | All configuration modes. No power supply sequencing.                                          | 0.40 | 10   | V/ms  |

|                   |                 | Configuring from Slave SPI. No power supply sequencing,                                       | 0.01 | 10   | V/ms  |

| <sup>t</sup> RAMP | power supplies. | Configuring from NVCM. $V_{CC}$ and $V_{PP\_2V5}$ to be powered 0.25ms before $V_{CC\_SPI}$ . | 0.01 | 10   | V/ms  |

|                   |                 | Configuring from MSPI. $V_{CC}$ and $V_{PP\_SPI}$ to be powered 0.25ms before $V_{PP\_2V5}$ . | 0.01 | 10   | V/ms  |

<sup>1.</sup> Assumes monotonic ramp rates.

## Power-On-Reset Voltage Levels<sup>1</sup>

| Symbol             | Device                         | Parameter                                                                                                            |         | Min. | Max. | Units |

|--------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------|---------|------|------|-------|

| V <sub>PORUP</sub> | iCE40LP384                     |                                                                                                                      | VCC     | 0.67 | 0.99 | V     |

|                    |                                | (band gap based circuit monitoring VCC, VCCIO_2, VCC_SPI and                                                         | VCCIO_2 | 0.70 | 1.59 | V     |

|                    |                                | VPP_2V5)                                                                                                             | VCC_SPI | 0.70 | 1.59 | V     |

|                    |                                | ,                                                                                                                    | VPP_2V5 | 0.70 | 1.59 | V     |

|                    | iCE40LP640,                    | K, (band gap based circuit monitoring VCC, VCCIO_2, VCC_SPI and VPP_2V5)                                             | VCC     | 0.55 | 0.75 | V     |

|                    | iCE40LP/HX1K,<br>iCE40LP/HX4K, |                                                                                                                      | VCCIO_2 | 0.86 | 1.29 | V     |

|                    | iCE40LP/HX8K                   |                                                                                                                      | VCC_SPI | 0.86 | 1.29 | V     |

|                    |                                |                                                                                                                      | VPP_2V5 | 0.86 | 1.33 | V     |

| V <sub>PORDN</sub> | iCE40LP384                     | Power-On-Reset ramp-down trip<br>point (band gap based circuit moni-<br>toring VCC, VCCIO_2, VCC_SPI<br>and VPP_2V5) | VCC     | -    | 0.64 | V     |

|                    |                                |                                                                                                                      | VCCIO_2 | -    | 1.59 | V     |

|                    |                                |                                                                                                                      | VCC_SPI | -    | 1.59 | V     |

|                    |                                |                                                                                                                      | VPP_2V5 | -    | 1.59 | V     |

|                    | iCE40LP640,                    | Power-On-Reset ramp-down trip                                                                                        | VCC     | -    | 0.75 | V     |

|                    | iCE40LP/HX1K, iCE40LP/HX4K,    | point (band gap based circuit monitoring VCC, VCCIO_2, VCC_SPI and VPP_2V5)                                          | VCCIO_2 | -    | 1.29 | V     |

|                    | iCE40LP/HX8K                   |                                                                                                                      | VCC_SPI | -    | 1.29 | V     |

|                    |                                |                                                                                                                      | VPP_2V5 | -    | 1.33 | V     |

<sup>1.</sup> These POR trip points are only provided for guidance. Device operation is only characterized for power supply voltages specified under recommended operating conditions.

## **ESD Performance**

Please refer to the <u>iCE40 Product Family Qualification Summary</u> for complete qualification data, including ESD performance.

<sup>2.</sup> iCE40LP384 requires  $V_{CC}$  to be greater than 0.7V when  $V_{CCIO}$  and  $V_{CC\_SPI}$  are above GND.

## **DC Electrical Characteristics**

## **Over Recommended Operating Conditions**

| Symbol                          | Parameter                                       | Condition                                                                                | Min. | Тур. | Max.  | Units |

|---------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------|------|------|-------|-------|

| ·-, ···                         | Input or I/O Leakage                            | $0V < V_{\text{IN}} < V_{\text{CCIO}} + 0.2V$                                            | _    | _    | +/-10 | μΑ    |

| C <sub>1</sub> <sup>6, 7</sup>  | I/O Capacitance <sup>2</sup>                    | $V_{CCIO} = 3.3V, 2.5V, 1.8V$<br>$V_{CC} = Typ., V_{IO} = 0 \text{ to } V_{CCIO} + 0.2V$ | _    | 6    |       | pf    |

| C <sub>2</sub> <sup>6, 7</sup>  | Global Input Buffer<br>Capacitance <sup>2</sup> | $V_{CCIO} = 3.3V, 2.5V, 1.8V$<br>$V_{CC} = Typ., V_{IO} = 0 \text{ to } V_{CCIO} + 0.2V$ | _    | 6    |       | pf    |

| V <sub>HYST</sub>               | Input Hysteresis                                | V <sub>CCIO</sub> = 1.8V, 2.5V, 3.3V                                                     | _    | 200  |       | mV    |

| I <sub>PU</sub> <sup>6, 7</sup> | Internal PIO Pull-up                            | $V_{CCIO} = 1.8V, 0 = < V_{IN} < = 0.65 V_{CCIO}$                                        | -3   | _    | -31   | μΑ    |

|                                 | Current                                         | V <sub>CCIO</sub> = 2.5V, 0= <v<sub>IN&lt;=0.65 V<sub>CCIO</sub></v<sub>                 | -8   | _    | -72   | μΑ    |

|                                 |                                                 | $V_{CCIO} = 3.3V, 0 = < V_{IN} < = 0.65 V_{CCIO}$                                        | -11  | _    | -128  | μΑ    |

- 1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Internal pull-up resistors are disabled.

- 2. T<sub>.1</sub> 25°C, f = 1.0 MHz.

- 3. Please refer to V<sub>IL</sub> and V<sub>IH</sub> in the sysIO Single-Ended DC Electrical Characteristics table of this document.

- 4. Only applies to IOs in the SPI bank following configuration.

- 5. Some products are clamped to a diode when  $V_{IN}$  is larger than  $V_{CCIO}$ .

- 6. High current IOs has three sysIO buffers connected together.

- 7. The iCE40640KLP and iCE401KLP SWG16 package has CDONE and a sysIO buffer are connected together.

## Static Supply Current - LP Devices<sup>1, 2, 3, 4, 7</sup>

| Symbol                                 | Parameter                                                  | Device      | Typ. V <sub>CC</sub> ⁴ | Units |

|----------------------------------------|------------------------------------------------------------|-------------|------------------------|-------|

|                                        |                                                            | iCE40LP384  | 21                     | μΑ    |

|                                        |                                                            | iCE40LP640  | 100                    | μΑ    |

| I <sub>CC</sub>                        | Core Power Supply                                          | iCE40LP1K   | 100                    | μΑ    |

|                                        |                                                            | iCE40LP4K   | 360                    | μΑ    |

|                                        |                                                            | iCE40LP8K   | 360                    | μΑ    |

| I <sub>CCPLL</sub> <sup>5, 6</sup>     | PLL Power Supply                                           | All devices | 10                     | μΑ    |

| I <sub>PP_2V5</sub>                    | NVCM Power Supply                                          | All devices |                        | μΑ    |

| I <sub>CCIO,</sub> I <sub>CC_SPI</sub> | Bank Power Supply <sup>4</sup><br>V <sub>CCIO</sub> = 2.5V | All devices |                        | μΑ    |

<sup>1.</sup> Assumes blank pattern with the following characteristics: all outputs are tri-stated, all inputs are configured as LVCMOS and held at V<sub>CCIO</sub> or GND, on-chip PLL is off. For more detail with your specific design, use the Power Calculator tool. Power specified with master SPI configuration mode. Other modes may be up to 25% higher.

- 2. Frequency = 0 MHz.

- 3.  $T_{.1} = 25$ °C, power supplies at nominal voltage.

- 4. Does not include pull-up.

- 5. No PLL available on the iCE40LP384 and iCE40LP640 device.

- 6.  $V_{CCPLL}$  is tied to  $V_{CC}$  internally in packages without PLLs pins. 7. iCE40LP4K/iCE40LP8K status is Advanced.

# Static Supply Current – HX Devices<sup>1, 2, 3, 4, 6</sup>