# **MachXO Family Handbook**

HB1002 Version 02.7, October 2011

# MachXO Family Handbook Table of Contents

October 2011

| Section I. MachXO Family Data Sheet                    |      |

|--------------------------------------------------------|------|

| Introduction                                           | 4.4  |

| Features Introduction                                  |      |

| Architecture                                           |      |

| Architecture Architecture Overview                     | 2.1  |

| PFU Blocks                                             |      |

| Slice                                                  |      |

| Routing                                                |      |

| Clock/Control Distribution Network                     |      |

| sysCLOCK Phase Locked Loops (PLLs)                     |      |

| sysMEM Memory                                          |      |

| PIO Groups                                             |      |

| PIO                                                    |      |

| sysIO Buffer                                           |      |

| sysiO Buffer Banks                                     |      |

| Hot Socketing                                          |      |

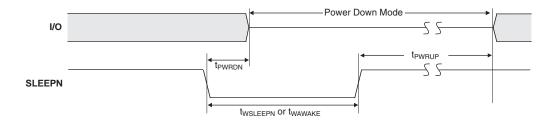

| Sleep Mode                                             |      |

| SLEEPN Pin Characteristics                             |      |

| Oscillator                                             |      |

| Configuration and Testing                              |      |

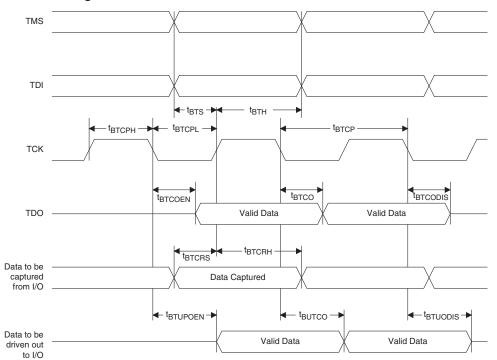

| IEEE 1149.1-Compliant Boundary Scan Testability        |      |

| Device Configuration                                   |      |

| Density Shifting                                       |      |

| DC and Switching Characteristics                       |      |

| Absolute Maximum Ratings                               | 3-1  |

| Recommended Operating Conditions <sup>1</sup>          |      |

| MachXO256 and MachXO640 Hot Socketing Specifications   |      |

| MachXO1200 and MachXO2280 Hot Socketing Specifications |      |

| DC Electrical Characteristics                          |      |

| Supply Current (Sleep Mode)                            |      |

| Supply Current (Standby)                               |      |

| Initialization Supply Current                          |      |

| Programming and Erase Flash Supply Current             |      |

| sysIO Recommended Operating Conditions                 |      |

| sysIO Single-Ended DC Electrical Characteristics       |      |

| sysIO Differential Electrical Characteristics          |      |

| LVDS                                                   | 3-8  |

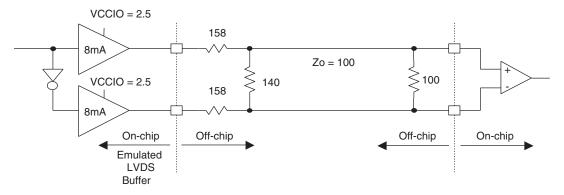

| LVDS Emulation                                         |      |

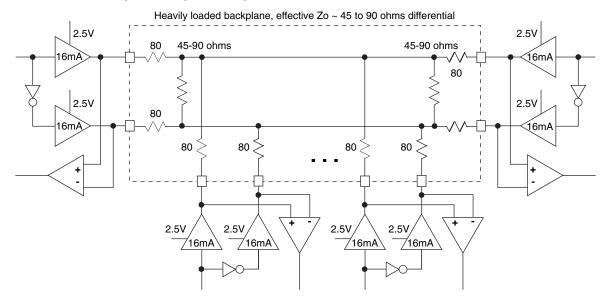

| BLVDS                                                  |      |

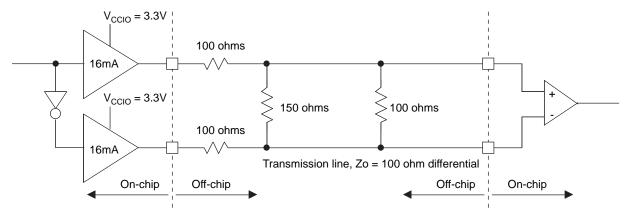

| LVPECL                                                 | 3-10 |

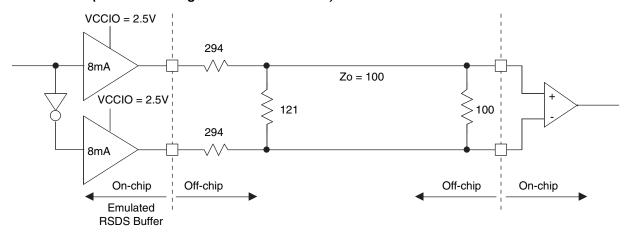

| RSDS                                                   |      |

| Typical Building Block Function Performance            |      |

| Register-to-Register Performance                       |      |

| Derating Logic Timing                                  |      |

| MachXO External Switching Characteristics              |      |

| MachXO Internal Timing Parameters                      |      |

| MachXQ Family Timing Adders                            | 3-15 |

© 2011 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| sysCLOCK PLL Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.40              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Flash Download Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |

| JTAG Port Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |

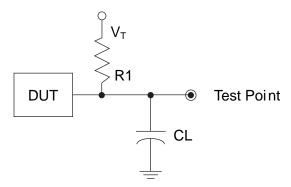

| Switching Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |

| Pinout Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-19              |

| Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-1               |

| Pin Information Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

| Power Supply and NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |

| Power Supply and NC (Cont.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

| LCMXO256 and LCMXO640 Logic Signal Connections: 100 TQFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |

| LCMXO1200 and LCMXO2280 Logic Signal Connections: 100 TQFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |

| LCMXO256 and LCMXO640 Logic Signal Connections: 100 csBGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |

| LCMXO640, LCMXO1200 and LCMXO2280 Logic Signal Connections: 132 csBGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |

| LCMXO640, LCMXO1200 and LCMXO2280 Logic Signal Connections: 144 TQFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |

| LCMXO640, LCMXO1200 and LCMXO2280 Logic Signal Connections: 256 caBGA / 256 ftBGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-20              |

| LCMXO2280 Logic Signal Connections: 324 ftBGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-26              |

| Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| For Further Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-36              |

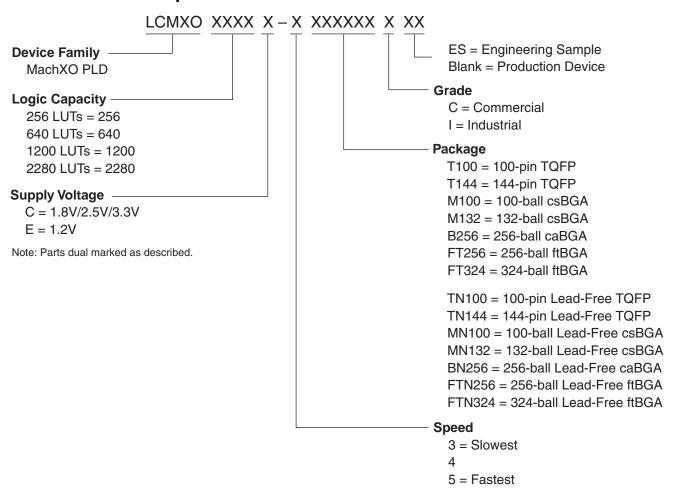

| Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |

| Part Number Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

| Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |

| Conventional Packaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

| Conventional Packaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

| Lead-Free Packaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |

| Lead-Free Packaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-10              |

| Cunniamantal Intermetian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |

| Supplemental Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |

| For Further Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6-1               |

| For Further Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

| For Further Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

| For Further Information  MachXO Family Data Sheet Revision History  Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |

| For Further Information  MachXO Family Data Sheet Revision History  Revision History  Section II. MachXO Family Technical Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |

| For Further Information  MachXO Family Data Sheet Revision History  Revision History  Section II. MachXO Family Technical Notes  MachXO sysIO Usage Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7-1               |

| For Further Information  MachXO Family Data Sheet Revision History Revision History  Section II. MachXO Family Technical Notes  MachXO sysIO Usage Guide Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7-1               |

| For Further Information  MachXO Family Data Sheet Revision History Revision History  Section II. MachXO Family Technical Notes  MachXO syslO Usage Guide Introduction  syslO Buffer Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7-1<br>8-1<br>8-1 |

| For Further Information  MachXO Family Data Sheet Revision History Revision History  Section II. MachXO Family Technical Notes  MachXO sysIO Usage Guide Introduction  sysIO Buffer Overview Supported sysIO Standards sysIO Banking Scheme                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

| For Further Information  MachXO Family Data Sheet Revision History Revision History  Section II. MachXO Family Technical Notes  MachXO sysIO Usage Guide Introduction  sysIO Buffer Overview Supported sysIO Standards sysIO Banking Scheme                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

| For Further Information  MachXO Family Data Sheet Revision History Revision History  Section II. MachXO Family Technical Notes  MachXO sysIO Usage Guide Introduction  sysIO Buffer Overview  Supported sysIO Standards  sysIO Banking Scheme  V <sub>CCIO</sub> (1.2V/1.5V/1.8V/2.5V/3.3V)                                                                                                                                                                                                                                                                                                                                                                |                   |

| For Further Information  MachXO Family Data Sheet Revision History Revision History  Section II. MachXO Family Technical Notes  MachXO sysIO Usage Guide Introduction  sysIO Buffer Overview Supported sysIO Standards sysIO Banking Scheme                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

| For Further Information  MachXO Family Data Sheet Revision History Revision History  Section II. MachXO Family Technical Notes  MachXO sysIO Usage Guide Introduction  sysIO Buffer Overview  Supported sysIO Standards  sysIO Banking Scheme  V <sub>CCIO</sub> (1.2V/1.5V/1.8V/2.5V/3.3V)  V <sub>CCAUX</sub> (3.3V)                                                                                                                                                                                                                                                                                                                                     |                   |

| For Further Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

| For Further Information  MachXO Family Data Sheet Revision History Revision History  Section II. MachXO Family Technical Notes  MachXO sysIO Usage Guide Introduction  sysIO Buffer Overview  Supported sysIO Standards  sysIO Banking Scheme  V <sub>CCIO</sub> (1.2V/1.5V/1.8V/2.5V/3.3V)  V <sub>CCAUX</sub> (3.3V)  Mixed Voltage Support in a Bank  sysIO Standards Supported in Each Bank                                                                                                                                                                                                                                                            |                   |

| For Further Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

| For Further Information  MachXO Family Data Sheet Revision History Revision History  Section II. MachXO Family Technical Notes  MachXO syslO Usage Guide Introduction syslO Buffer Overview Supported syslO Standards syslO Banking Scheme V <sub>CCIO</sub> (1.2V/1.5V/1.8V/2.5V/3.3V) V <sub>CCAUX</sub> (3.3V) Mixed Voltage Support in a Bank syslO Standards Supported in Each Bank LVCMOS Buffer Configurations Programmable PULLUP/PULLDOWN/BUSKEEPER Programmable Drive Programmable Slew Rate                                                                                                                                                     |                   |

| For Further Information  MachXO Family Data Sheet Revision History Revision History  Section II. MachXO Family Technical Notes  MachXO sysIO Usage Guide Introduction  sysIO Buffer Overview Supported sysIO Standards sysIO Banking Scheme  V <sub>CCIO</sub> (1.2V/1.5V/1.8V/2.5V/3.3V)  V <sub>CCAUX</sub> (3.3V)  Mixed Voltage Support in a Bank sysIO Standards Supported in Each Bank  LVCMOS Buffer Configurations  Programmable PULLUP/PULLDOWN/BUSKEEPER Programmable Drive Programmable Slew Rate Open-Drain Control.                                                                                                                           |                   |

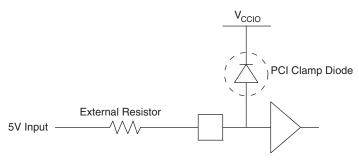

| For Further Information  MachXO Family Data Sheet Revision History Revision History  Section II. MachXO Family Technical Notes  MachXO sysIO Usage Guide Introduction sysIO Buffer Overview Supported sysIO Standards sysIO Banking Scheme V <sub>CCIO</sub> (1.2V/1.5V/1.8V/2.5V/3.3V) V <sub>CCAUX</sub> (3.3V) Mixed Voltage Support in a Bank sysIO Standards Supported in Each Bank  LVCMOS Buffer Configurations Programmable PULLUP/PULLDOWN/BUSKEEPER Programmable Drive Programmable Slew Rate Open-Drain Control Programmable PCICLAMP                                                                                                           |                   |

| For Further Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

| For Further Information  MachXO Family Data Sheet Revision History Revision History  Section II. MachXO Family Technical Notes  MachXO sysIO Usage Guide Introduction  sysIO Buffer Overview Supported sysIO Standards sysIO Banking Scheme  V <sub>CCIO</sub> (1.2V/1.5V/1.8V/2.5V/3.3V)  V <sub>CCAUX</sub> (3.3V)  Mixed Voltage Support in a Bank sysIO Standards Supported in Each Bank  LVCMOS Buffer Configurations  Programmable PULLUP/PULLDOWN/BUSKEEPER Programmable Drive Programmable Slew Rate Open-Drain Control Programmable PCICLAMP 5V Input Interface Using the PCI Clamp Diode  Software sysIO Attributes                              |                   |

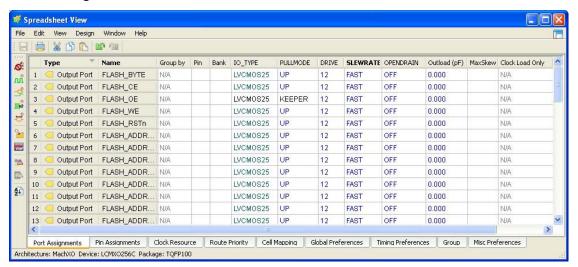

| For Further Information  MachXO Family Data Sheet Revision History Revision History  Section II. MachXO Family Technical Notes  MachXO sysIO Usage Guide Introduction sysIO Buffer Overview Supported sysIO Standards sysIO Banking Scheme V <sub>CCIO</sub> (1.2V/1.5V/1.8V/2.5V/3.3V) V <sub>CCAUX</sub> (3.3V) Mixed Voltage Support in a Bank sysIO Standards Supported in Each Bank LVCMOS Buffer Configurations Programmable PULLUP/PULLDOWN/BUSKEEPER Programmable Drive Programmable Slew Rate Open-Drain Control Programmable PCICLAMP 5V Input Interface Using the PCI Clamp Diode  Software sysIO Attributes IO_TYPE                            |                   |

| For Further Information  MachXO Family Data Sheet Revision History Revision History  Section II. MachXO Family Technical Notes  MachXO syslO Usage Guide Introduction syslO Buffer Overview Supported syslO Standards syslO Banking Scheme V <sub>CCIO</sub> (1.2V/1.5V/1.8V/2.5V/3.3V) V <sub>CCAUX</sub> (3.3V) Mixed Voltage Support in a Bank syslO Standards Supported in Each Bank LVCMOS Buffer Configurations Programmable PULLUP/PULLDOWN/BUSKEEPER Programmable Drive Programmable Slew Rate Open-Drain Control Programmable PCICLAMP 5V Input Interface Using the PCI Clamp Diode  Software syslO Attributes IO_TYPE OPENDRAIN                  |                   |

| For Further Information  MachXO Family Data Sheet Revision History Revision History  Section II. MachXO Family Technical Notes  MachXO syslO Usage Guide Introduction syslO Buffer Overview Supported syslO Standards syslO Banking Scheme V <sub>CCIO</sub> (1.2V/1.5V/1.8V/2.5V/3.3V) V <sub>CCAUX</sub> (3.3V) Mixed Voltage Support in a Bank syslO Standards Supported in Each Bank  LVCMOS Buffer Configurations Programmable PULLUP/PULLDOWN/BUSKEEPER Programmable Drive Programmable Slew Rate Open-Drain Control Programmable PCICLAMP 5V Input Interface Using the PCI Clamp Diode  Software syslO Attributes IO_TYPE OPENDRAIN DRIVE           |                   |

| For Further Information  MachXO Family Data Sheet Revision History Revision History  Section II. MachXO Family Technical Notes  MachXO syslO Usage Guide Introduction  syslO Buffer Overview Supported syslO Standards syslO Banking Scheme V <sub>CCIO</sub> (1.2V/1.5V/1.8V/2.5V/3.3V) V <sub>CCAUX</sub> (3.3V) Mixed Voltage Support in a Bank syslO Standards Supported in Each Bank LVCMOS Buffer Configurations Programmable PULLUP/PULLDOWN/BUSKEEPER Programmable Drive Programmable Slew Rate Open-Drain Control Programmable PCICLAMP 5V Input Interface Using the PCI Clamp Diode.  Software syslO Attributes IO_TYPE OPENDRAIN DRIVE PULLMODE |                   |

| For Further Information  MachXO Family Data Sheet Revision History Revision History  Section II. MachXO Family Technical Notes  MachXO syslO Usage Guide Introduction syslO Buffer Overview Supported syslO Standards syslO Banking Scheme V <sub>CCIO</sub> (1.2V/1.5V/1.8V/2.5V/3.3V) V <sub>CCAUX</sub> (3.3V) Mixed Voltage Support in a Bank syslO Standards Supported in Each Bank  LVCMOS Buffer Configurations Programmable PULLUP/PULLDOWN/BUSKEEPER Programmable Drive Programmable Slew Rate Open-Drain Control Programmable PCICLAMP 5V Input Interface Using the PCI Clamp Diode  Software syslO Attributes IO_TYPE OPENDRAIN DRIVE           |                   |

| LOC                                                                   | 8-10  |

|-----------------------------------------------------------------------|-------|

| Design Considerations and Usage                                       | 8-10  |

| Banking Rules                                                         |       |

| Zero Hold Time                                                        |       |

| Fast Output Path                                                      | 8-10  |

| Dedicated Pins                                                        |       |

| Differential I/O Implementation                                       |       |

| Technical Support Assistance                                          |       |

| Revision History                                                      |       |

| Appendix A. HDL Attributes for Synplify® and Precision® RTL Synthesis |       |

| VHDL Synplify/Precision RTL Synthesis                                 |       |

| Verilog Synpilfy                                                      |       |

| Verilog Precision RTL Synthesis                                       |       |

| Appendix B. sysIO Attributes Using the ispLEVER Preference Editor or  |       |

| Diamond Spreadsheet View                                              | 8-17  |

| Appendix C. sysIO Attributes Using Preference File (ASCII File)       | 8-19  |

| IOBUF                                                                 |       |

| LOCATE                                                                |       |

| Memory Usage Guide for MachXO Devices                                 |       |

| Introduction                                                          | 9-1   |

| MachXO Device Memories                                                |       |

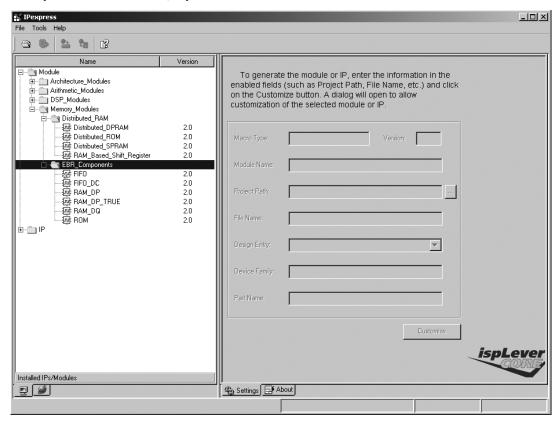

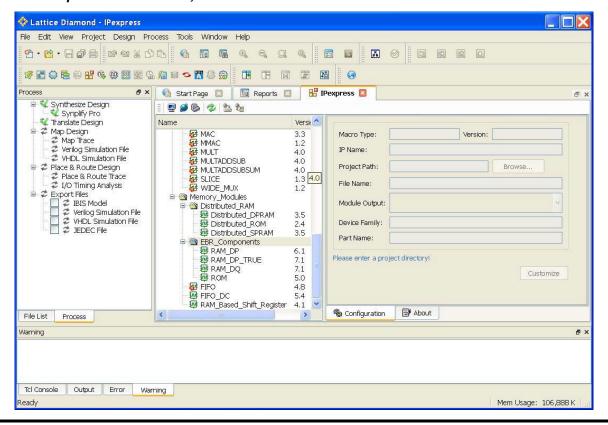

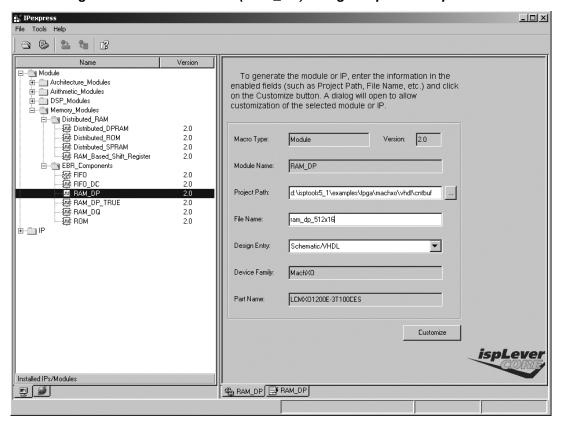

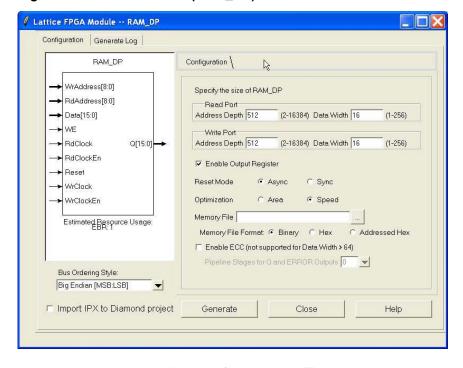

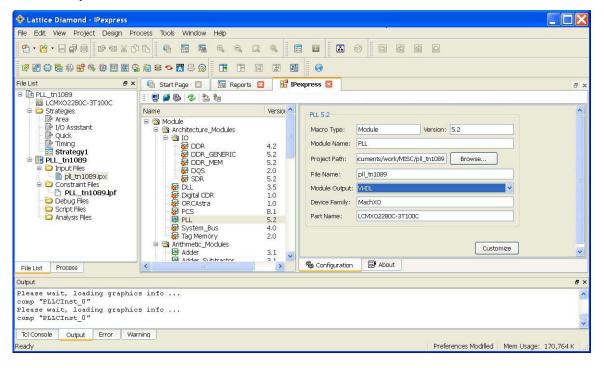

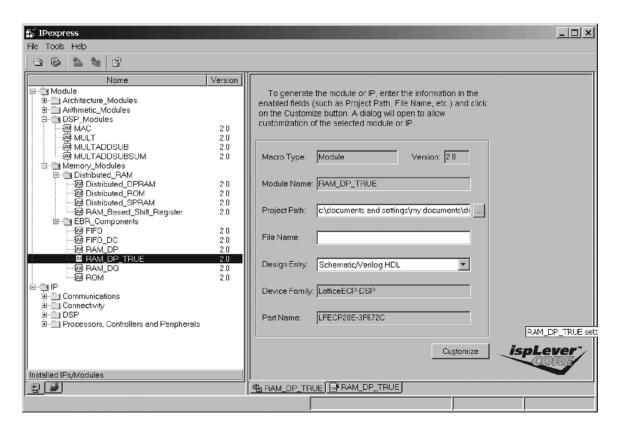

| Utilizing IPexpress                                                   |       |

| IPexpress Flow                                                        |       |

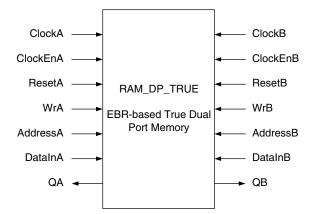

| True Dual Port RAM (RAM_DP_TRUE) - EBR Based                          |       |

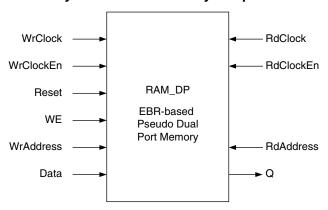

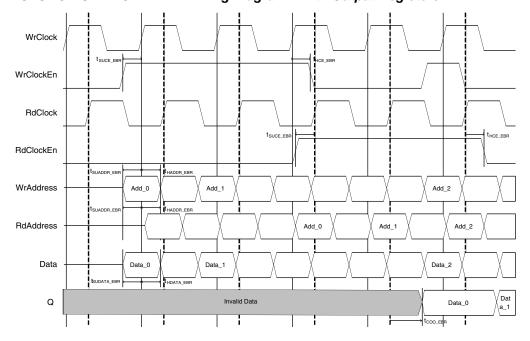

| Pseudo Dual Port RAM (RAM_DP)- EBR Based                              |       |

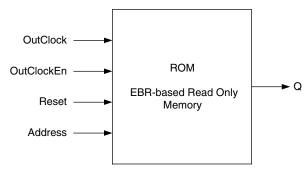

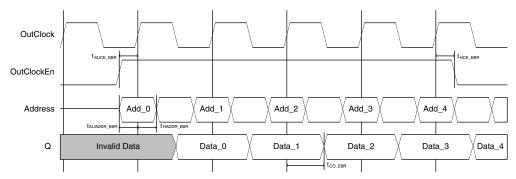

| Read Only Memory (ROM) – EBR Based                                    |       |

| First In First Out (FIFO, FIFO_DC) - EBR Based                        |       |

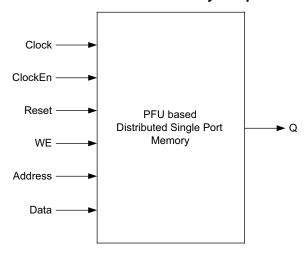

| Distributed Single Port RAM (Distributed_SPRAM) - PFU Based           |       |

| Distributed Dual Port RAM (Distributed_DPRAM) – PFU Based 32          |       |

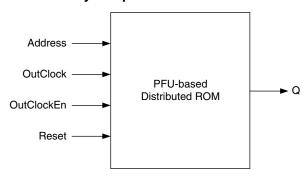

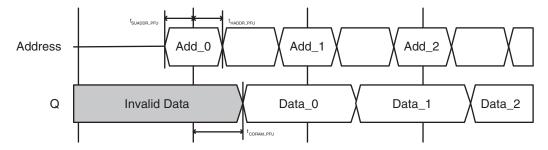

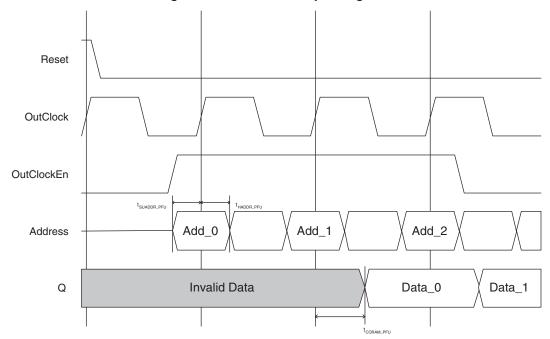

| Distributed ROM (Distributed_ROM) – PFU Based                         | 9-35  |

| Initializing Memory                                                   |       |

| Initialization File Formats                                           |       |

| Technical Support Assistance                                          |       |

| Revision History                                                      |       |

| Appendix A. Attribute Definitions                                     |       |

| MachXO sysCLOCK Design and Usage Guide                                |       |

| Introduction                                                          | 10-1  |

| MachXO Top Level View                                                 |       |

| sysCLOCK PLL                                                          |       |

| Features                                                              |       |

| Functional Description                                                | 10-2  |

| PLL Divider and Delay Blocks                                          |       |

| PLL Inputs and Outputs                                                |       |

| Dynamic Delay Control I/O Ports                                       |       |

| PLL Attributes                                                        |       |

| MachXO PLL Primitive Definitions                                      | 10-4  |

| PLL Attributes Definitions                                            |       |

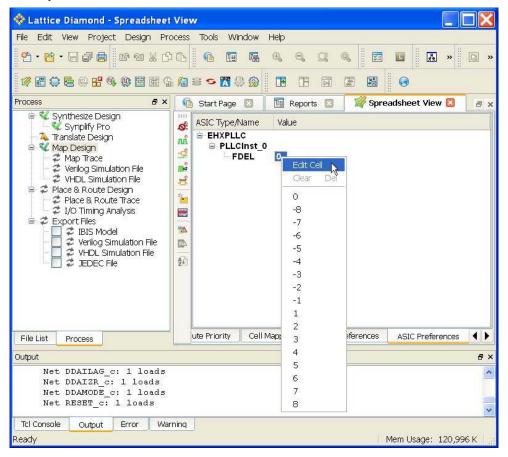

| Dynamic Delay Adjustment                                              |       |

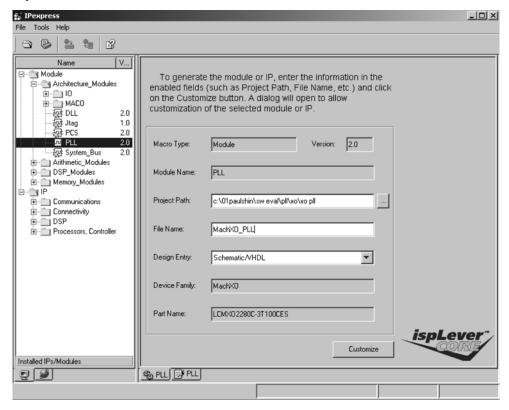

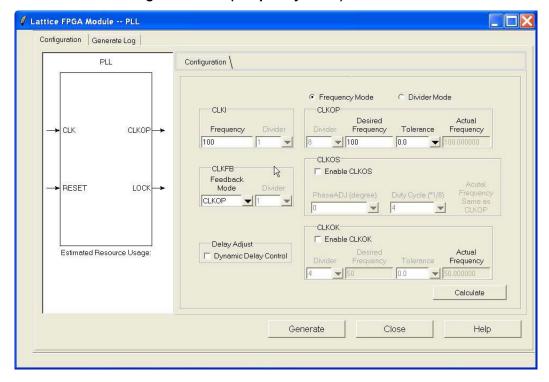

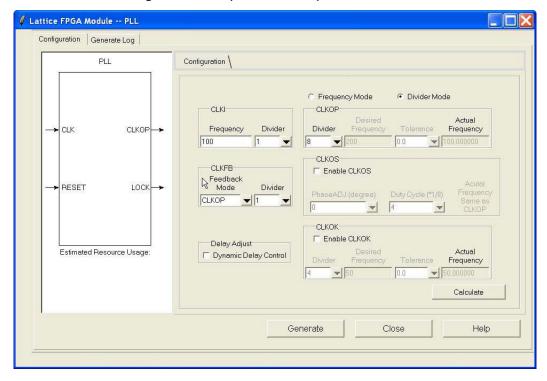

| MachXO PLL Usage in IPexpress                                         |       |

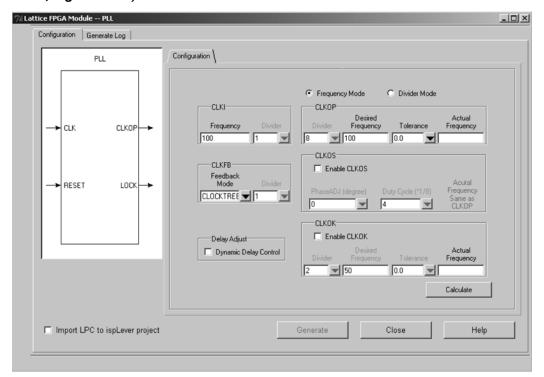

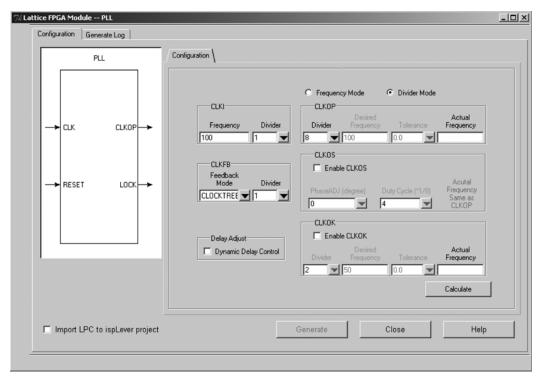

| Configuration Tab                                                     |       |

| Mode                                                                  |       |

| Frequency Programming in Divider Mode for Advanced Users              |       |

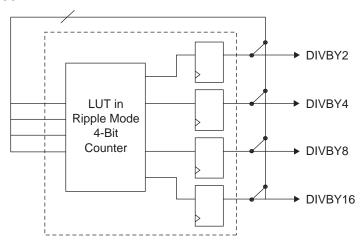

| Oscillator (OSCC)                                                     |       |

|                                                                       |       |

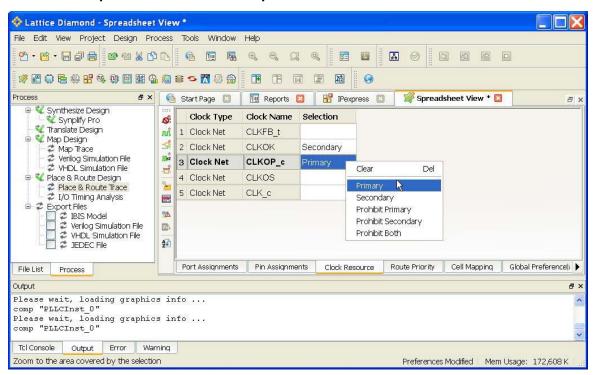

| Clock/Control Distribution Network                                    | 10-13 |

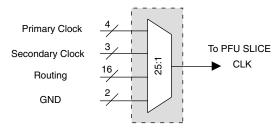

| Primary Clock Mux Connectivity                                      | 10-14 |

|---------------------------------------------------------------------|-------|

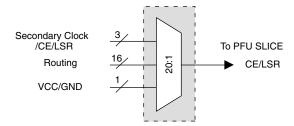

| Secondary Clock/CE/LSR Mux Connectivity                             | 10-15 |

| Primary Clock and Secondary Clock/CE/LSR Distribution Network       | 10-15 |

| Maximum Number of Secondary Clocks Available                        | 10-16 |

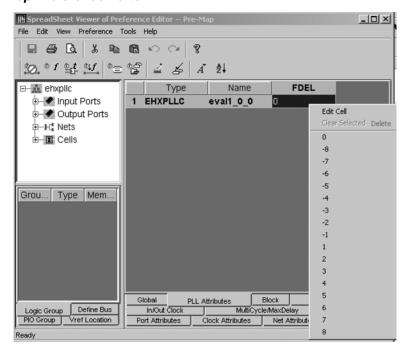

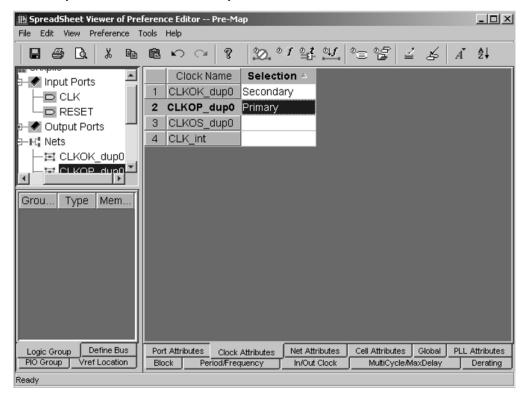

| Post Map Preference Editor Usage                                    | 10-16 |

| Technical Support Assistance                                        | 10-17 |

| Revision History                                                    | 10-17 |

| Appendix A. Lattice Diamond Design Software Screen Shots            | 10-18 |

| Power Estimation and Management for MachXO Devices                  |       |

| Introduction                                                        |       |

| Power Supply Sequencing and Hot Socketing                           | 11-1  |

| Recommended Power-up Sequence                                       | 11-1  |

| Power Calculator Hardware Assumptions                               | 11-1  |

| Power Calculator                                                    | 11-1  |

| Power Calculator Equations                                          | 11-1  |

| Power Calculations                                                  | 11-2  |

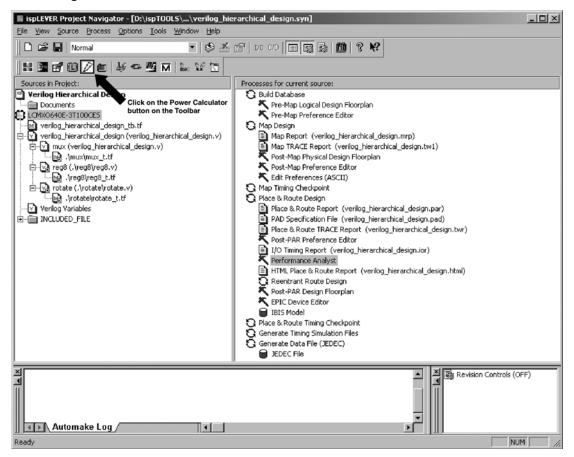

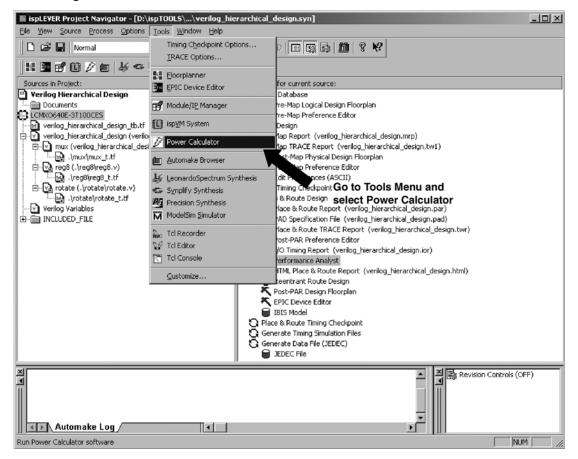

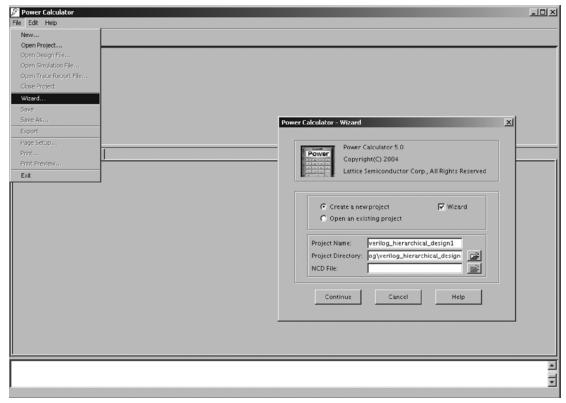

| Starting the Power Calculator                                       | 11-3  |

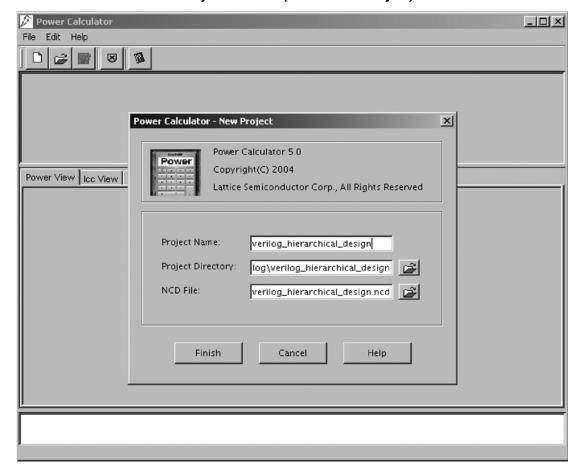

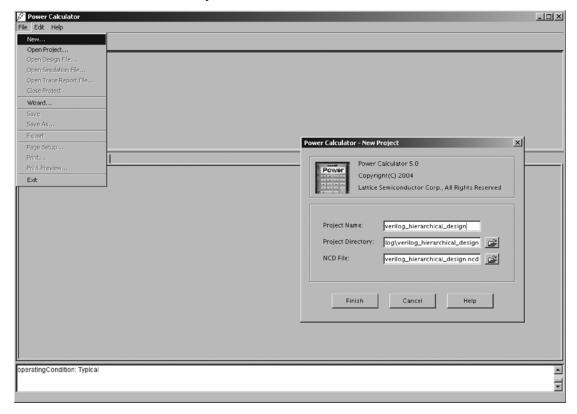

| Creating a Power Calculator Project                                 | 11-4  |

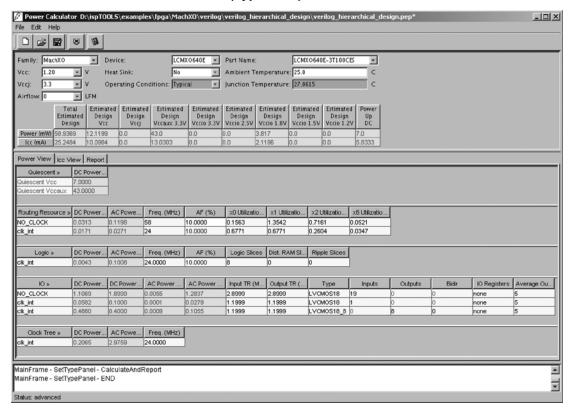

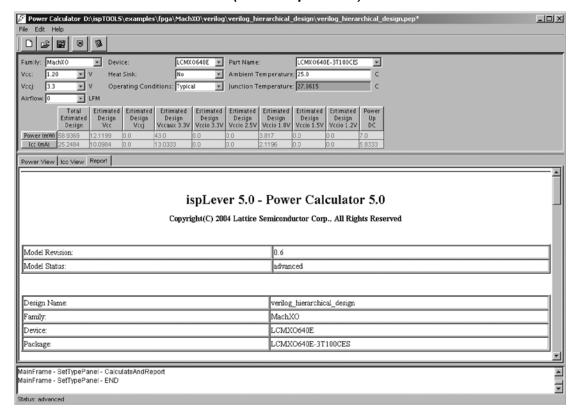

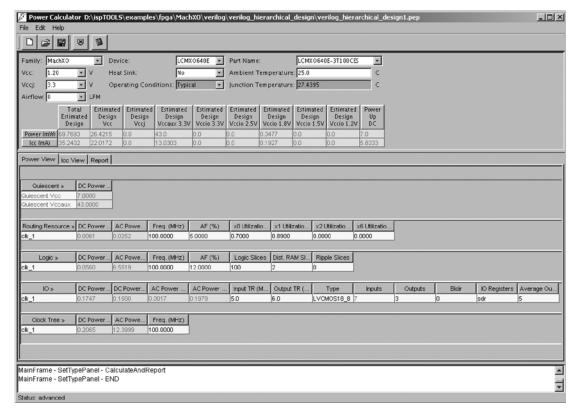

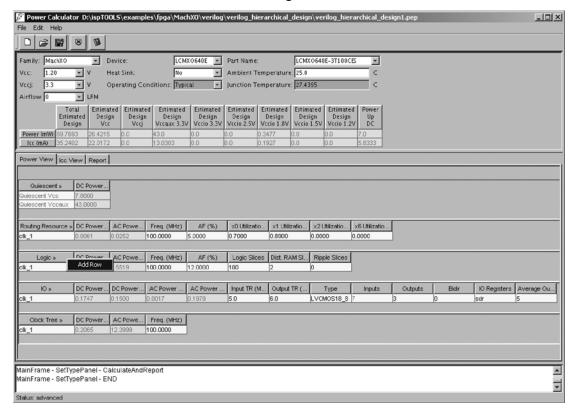

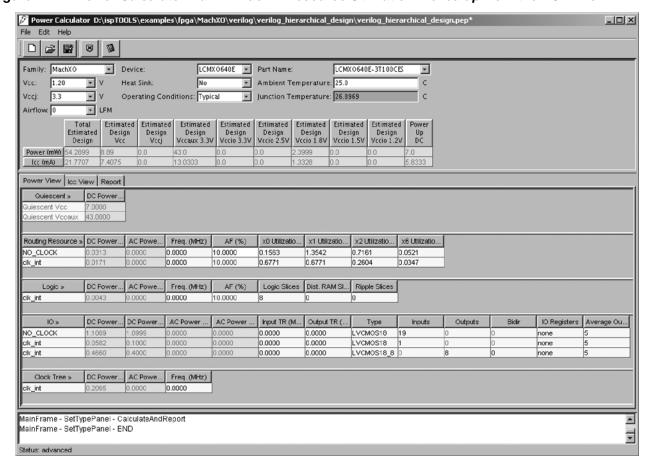

| Power Calculator Main Window                                        |       |

| Power Calculator Wizard                                             |       |

| Power Calculator - Creating a New Project Without the NCD File      |       |

| Power Calculator - Creating a New Project with the NCD File         |       |

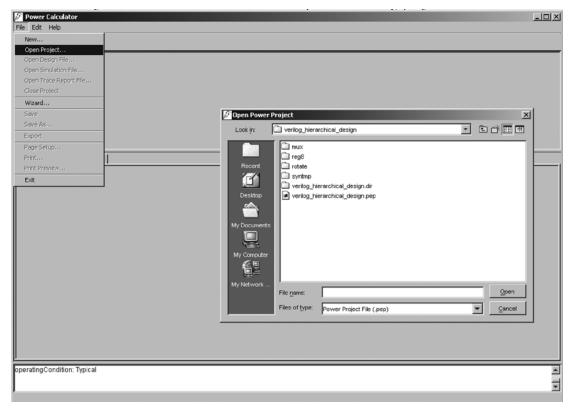

| Power Calculator - Open Existing Project                            |       |

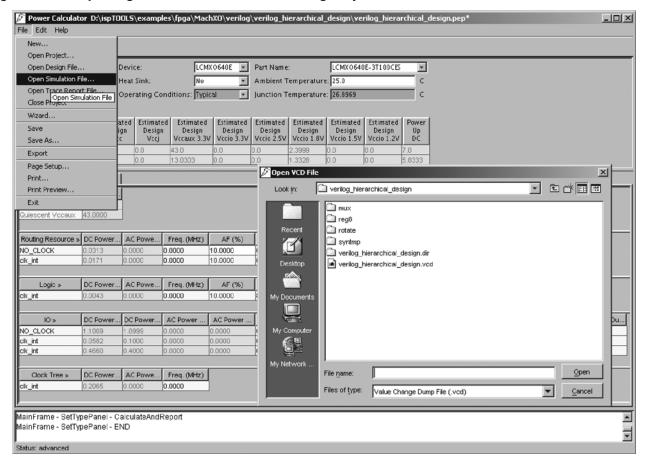

| Power Calculator - Importing Simulation File (VCD) to the Project   |       |

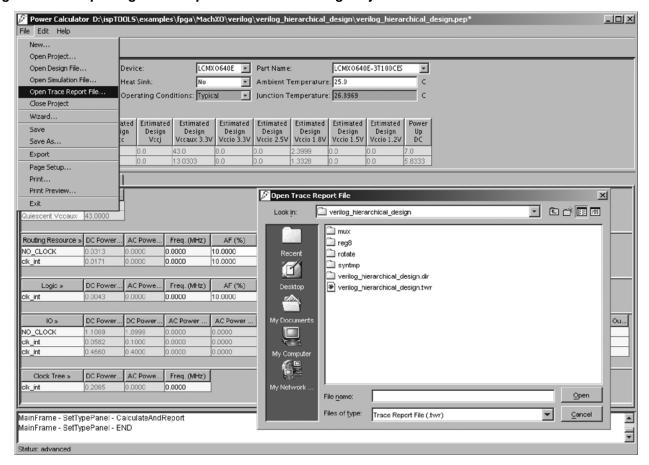

| Power Calculator - Importing Trace Report File (TWR) to the Project |       |

| Activity Factor and Toggle Rate                                     |       |

| Ambient and Junction Temperature and Airflow                        |       |

| Managing Power Consumption                                          |       |

| Power Calculator Assumptions                                        |       |

| Technical Support Assistance                                        |       |

| Revision History                                                    |       |

| MachXO JTAG Programming and Configuration User's Guide              |       |

| Introduction                                                        | 12-1  |

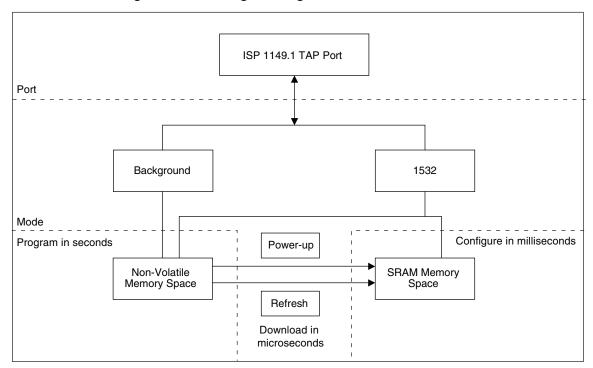

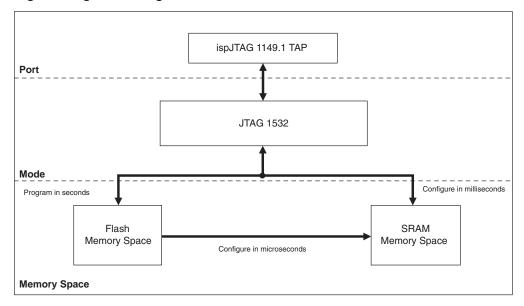

| Programming Overview                                                |       |

| ispJTAG                                                             |       |

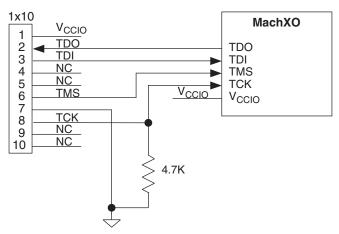

| TDO                                                                 |       |

|                                                                     | 12-2  |

| TMS                                                                 |       |

| TCK                                                                 |       |

| V <sub>CC</sub> Supply for JTAG                                     |       |

| Download Cable Pinout                                               |       |

| BSDL Files                                                          |       |

| Device Wake Up                                                      |       |

| Software Options                                                    |       |

| Preference Options                                                  |       |

| Configuring SRAM or Programming Flash                               |       |

| Technical Support Assistance                                        |       |

| Revision History                                                    |       |

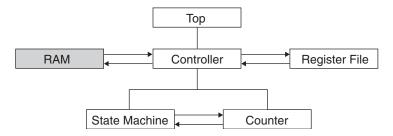

| HDL Synthesis Coding Guidelines for Lattice Semiconductor FPGAs     | 12 0  |

| Introduction                                                        | 10_1  |

| General Coding Styles for FPGA                                      |       |

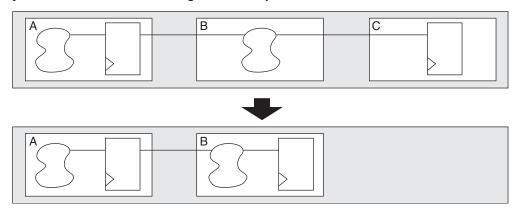

| Hierarchical Coding                                                 |       |

| Design Partitioning                                                 |       |

| State Encoding Methodologies for State Machines                     |       |

| Otate Encounty Methodologies for State Machines                     | 13-3  |

| Coding Styles for FSM                                                         | 13-5  |

|-------------------------------------------------------------------------------|-------|

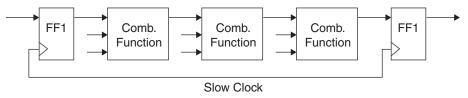

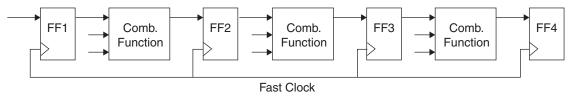

| Using Pipelines in the Designs                                                |       |

| Comparing IF statement and CASE statement                                     | 13-7  |

| Avoiding Non-intentional Latches                                              |       |

| HDL Design with Lattice Semiconductor FPGA Devices                            | 13-8  |

| Lattice Semiconductor FPGA Synthesis Library                                  | 13-8  |

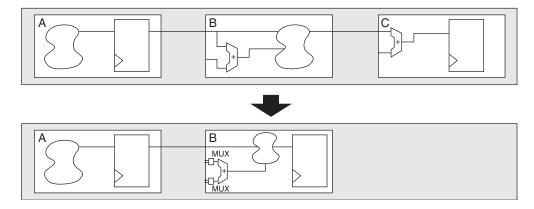

| Implementing Multiplexers                                                     | 13-10 |

| Clock Dividers                                                                | 13-10 |

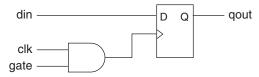

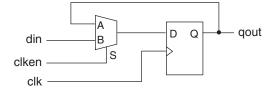

| Register Control Signals                                                      | 13-12 |

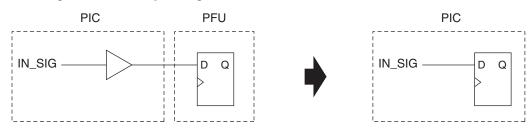

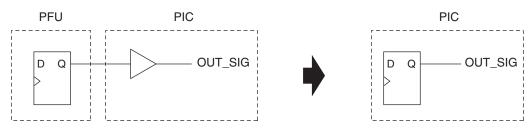

| Use PIC Features                                                              | 13-14 |

| Implementation of Memories                                                    | 13-16 |

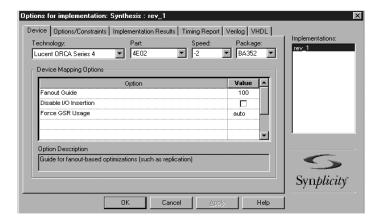

| Preventing Logic Replication and Limited Fanout                               | 13-16 |

| Use ispLEVER Project Navigator Results for Device Utilization and Performance | 13-17 |

| Technical Support Assistance                                                  |       |

| PCB Layout Recommendations for BGA Packages                                   |       |

| Introduction                                                                  | 14-1  |

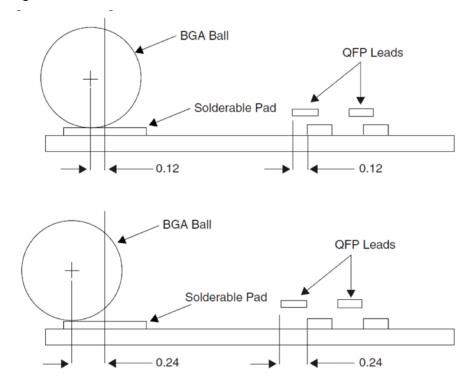

| BGA Board Layout Recommendations                                              |       |

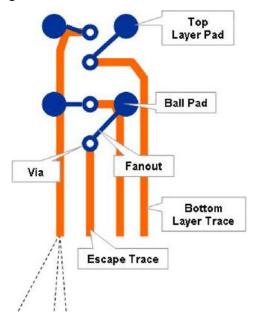

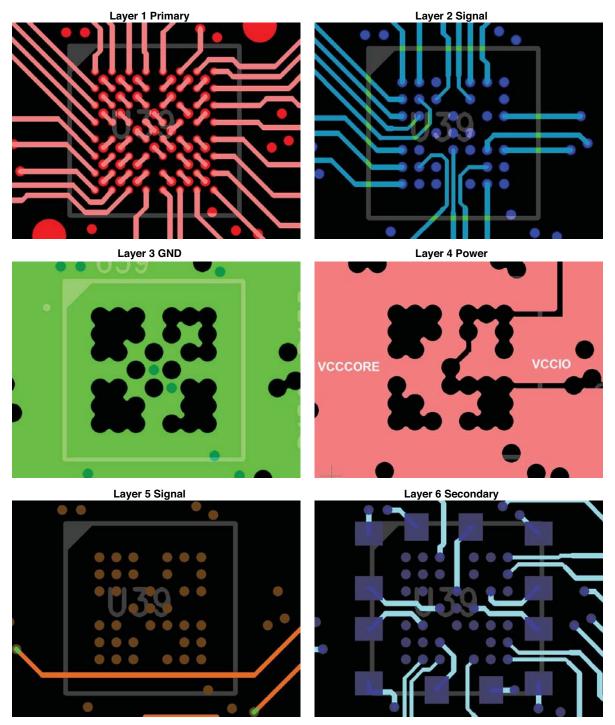

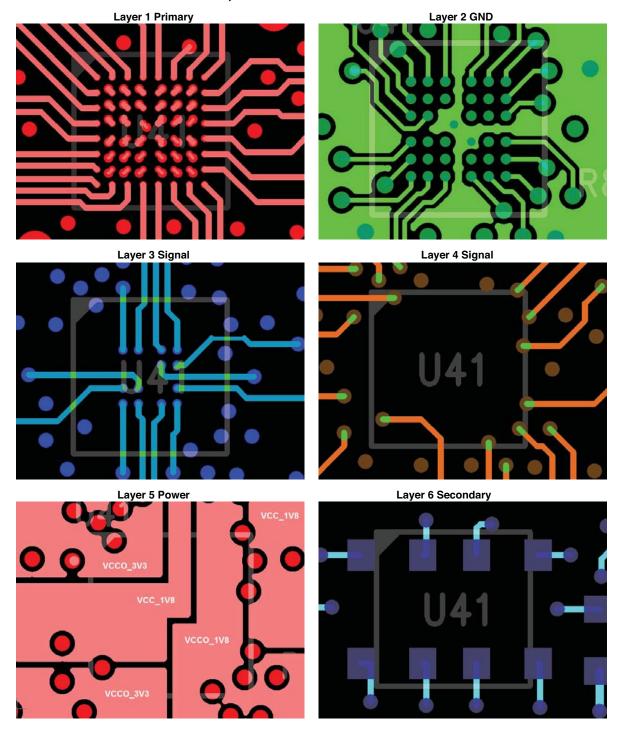

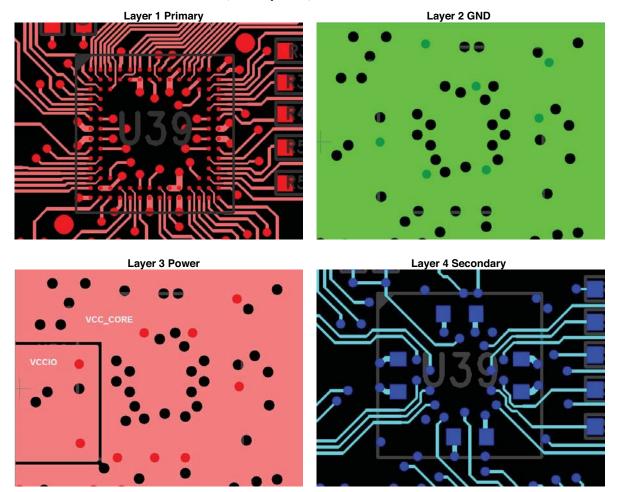

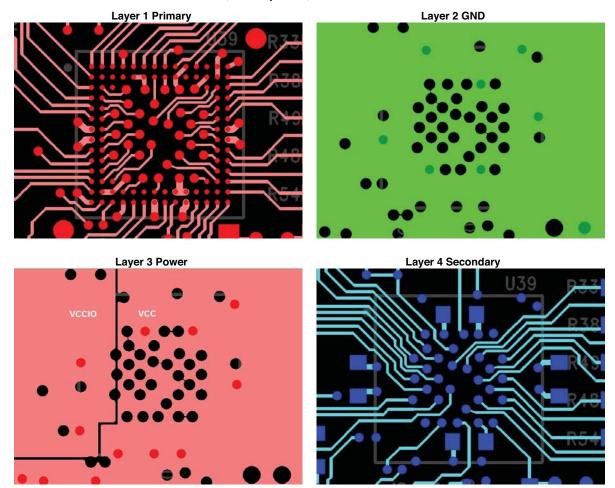

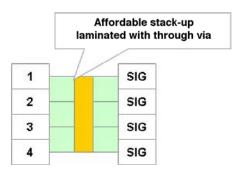

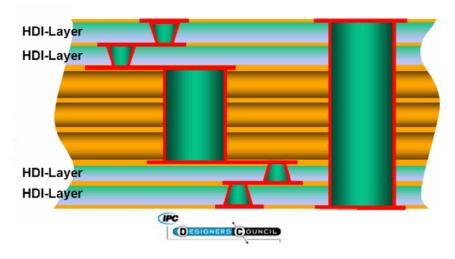

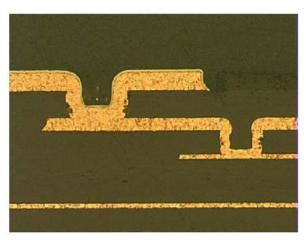

| BGA Breakout and Routing Examples                                             | 14-2  |

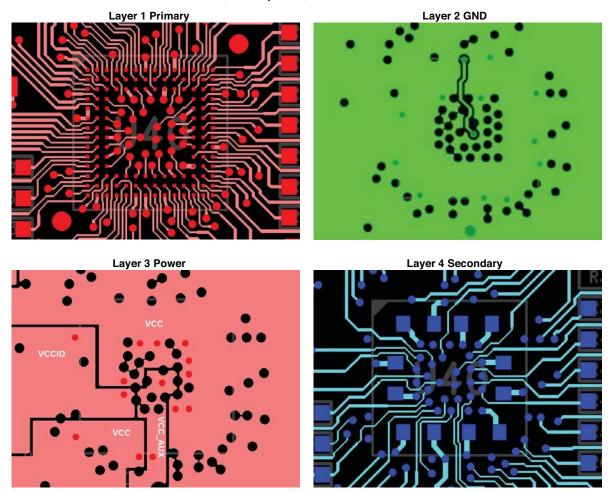

| 64-ball csBGA BGA Breakout and Routing Example                                | 14-4  |

| 64-ball ucBGA BGA Breakout and Routing Example                                | 14-5  |

| 100-ball csBGA BGA Breakout and Routing Examples                              | 14-6  |

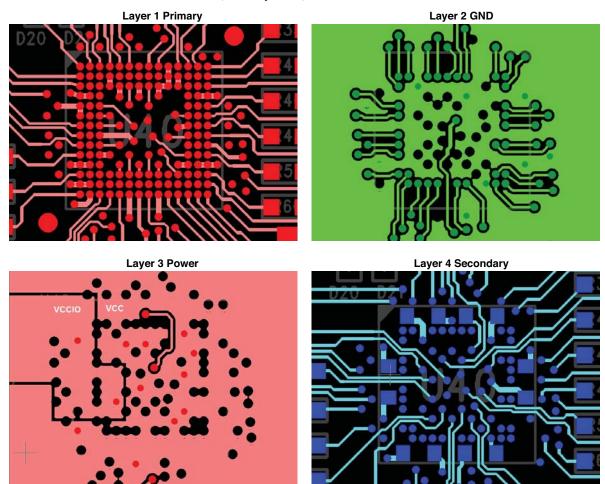

| 132-ball csBGA BGA Breakout Examples                                          |       |

| 144-ball csBGA BGA Breakout Examples                                          |       |

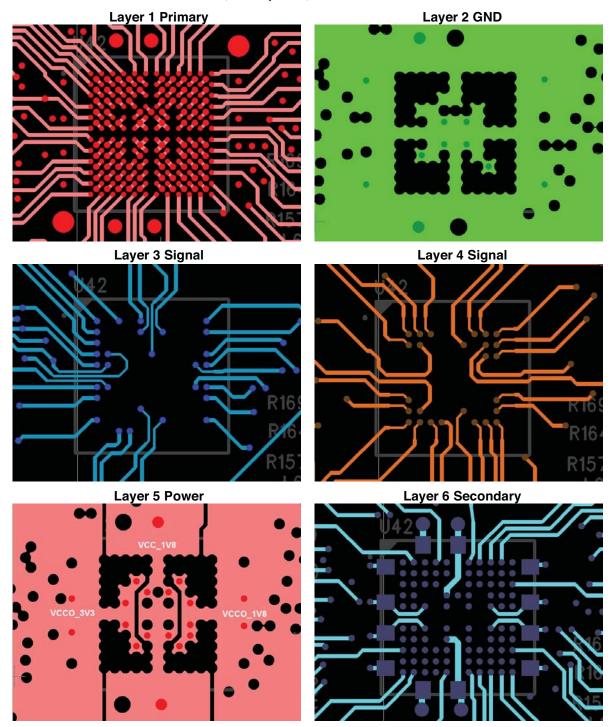

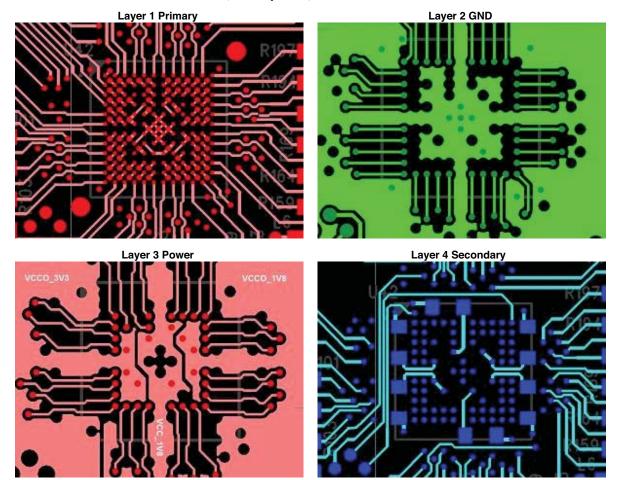

| 256-ball caBGA BGA Breakout Examples                                          | 14-12 |

| PCB Fabrication Cost and Design Rule Considerations                           | 14-13 |

| Advantages and Disadvantages of BGA Packaging                                 | 14-14 |

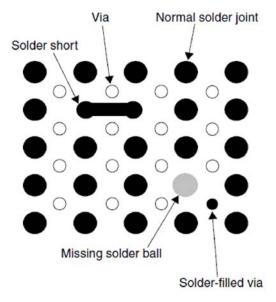

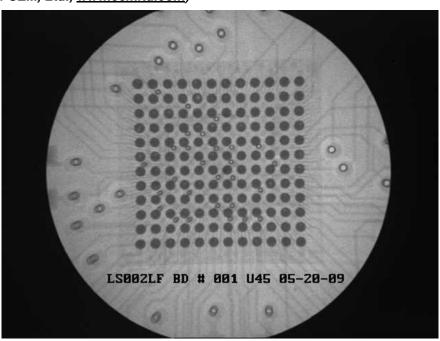

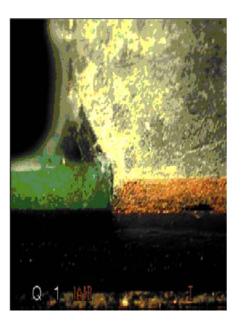

| BGA Package Test and Assembly                                                 | 14-15 |

| PCB Design Support                                                            | 14-18 |

| Technical Support Assistance                                                  | 14-18 |

| Revision History                                                              | 14-19 |

| ·                                                                             |       |

| Section III. MachXO Family Handbook Revision History                          |       |

| Revision History                                                              |       |

| Revision History                                                              | 15-1  |

# **Section I. MachXO Family Data Sheet**

DS1002 Version 02.9, July 2010

# MachXO Family Data Sheet Introduction

June 2009 Data Sheet DS1002

# **Features**

# ■ Non-volatile, Infinitely Reconfigurable

- Instant-on powers up in microseconds

- Single chip, no external configuration memory required

- Excellent design security, no bit stream to intercept

- · Reconfigure SRAM based logic in milliseconds

- SRAM and non-volatile memory programmable through JTAG port

- Supports background programming of non-volatile memory

### ■ Sleep Mode

• Allows up to 100x static current reduction

# ■ TransFR<sup>™</sup> Reconfiguration (TFR)

• In-field logic update while system operates

# ■ High I/O to Logic Density

- 256 to 2280 LUT4s

- 73 to 271 I/Os with extensive package options

- Density migration supported

- Lead free/RoHS compliant packaging

### Embedded and Distributed Memory

- Up to 27.6 Kbits sysMEM<sup>™</sup> Embedded Block RAM

- Up to 7.7 Kbits distributed RAM

- Dedicated FIFO control logic

#### ■ Flexible I/O Buffer

- Programmable syslO<sup>™</sup> buffer supports wide range of interfaces:

- LVCMOS 3.3/2.5/1.8/1.5/1.2

- LVTTL

- PCI

- LVDS, Bus-LVDS, LVPECL, RSDS

# ■ sysCLOCK<sup>™</sup> PLLs

- Up to two analog PLLs per device

- · Clock multiply, divide, and phase shifting

### ■ System Level Support

- IEEE Standard 1149.1 Boundary Scan

- Onboard oscillator

- Devices operate with 3.3V, 2.5V, 1.8V or 1.2V power supply

- IEEE 1532 compliant in-system programming

# Introduction

The MachXO is optimized to meet the requirements of applications traditionally addressed by CPLDs and low capacity FPGAs: glue logic, bus bridging, bus interfacing, power-up control, and control logic. These devices bring together the best features of CPLD and FPGA devices on a single chip.

Table 1-1. MachXO Family Selection Guide

| Device                              | LCMXO256         | LCMXO640         | LCMXO1200        | LCMXO2280        |

|-------------------------------------|------------------|------------------|------------------|------------------|

| LUTs                                | 256              | 640              | 1200             | 2280             |

| Dist. RAM (Kbits)                   | 2.0              | 6.1              | 6.4              | 7.7              |

| EBR SRAM (Kbits)                    | 0                | 0                | 9.2              | 27.6             |

| Number of EBR SRAM Blocks (9 Kbits) | 0                | 0                | 1                | 3                |

| V <sub>CC</sub> Voltage             | 1.2/1.8/2.5/3.3V | 1.2/1.8/2.5/3.3V | 1.2/1.8/2.5/3.3V | 1.2/1.8/2.5/3.3V |

| Number of PLLs                      | 0                | 0                | 1                | 2                |

| Max. I/O                            | 78               | 159              | 211              | 271              |

| Packages                            | <u> </u>         |                  |                  |                  |

| 100-pin TQFP (14x14 mm)             | 78               | 74               | 73               | 73               |

| 144-pin TQFP (20x20 mm)             |                  | 113              | 113              | 113              |

| 100-ball csBGA (8x8 mm)             | 78               | 74               |                  |                  |

| 132-ball csBGA (8x8 mm)             |                  | 101              | 101              | 101              |

| 256-ball caBGA (14x14 mm)           |                  | 159              | 211              | 211              |

| 256-ball ftBGA (17x17 mm)           |                  | 159              | 211              | 211              |

| 324-ball ftBGA (19x19 mm)           |                  |                  |                  | 271              |

The devices use look-up tables (LUTs) and embedded block memories traditionally associated with FPGAs for flexible and efficient logic implementation. Through non-volatile technology, the devices provide the single-chip, high-security, instant-on capabilities traditionally associated with CPLDs. Finally, advanced process technology and careful design will provide the high pin-to-pin performance also associated with CPLDs.

The ispLEVER® design tools from Lattice allow complex designs to be efficiently implemented using the MachXO family of devices. Popular logic synthesis tools provide synthesis library support for MachXO. The ispLEVER tools use the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the MachXO device. The ispLEVER tool extracts the timing from the routing and back-annotates it into the design for timing verification.

# MachXO Family Data Sheet Architecture

February 2007 Data Sheet DS1002

# **Architecture Overview**

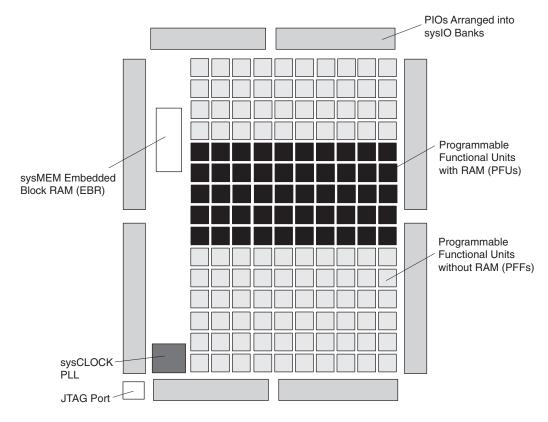

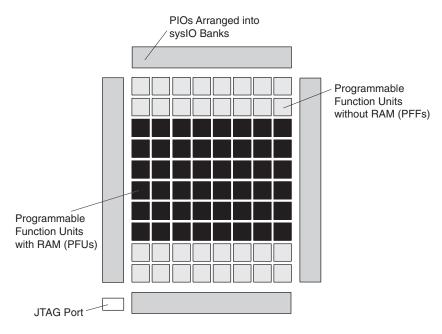

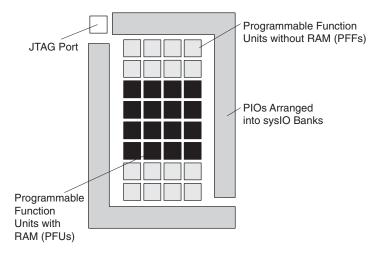

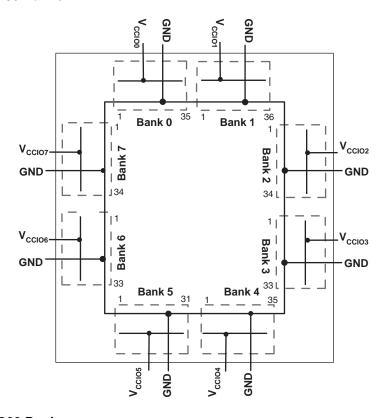

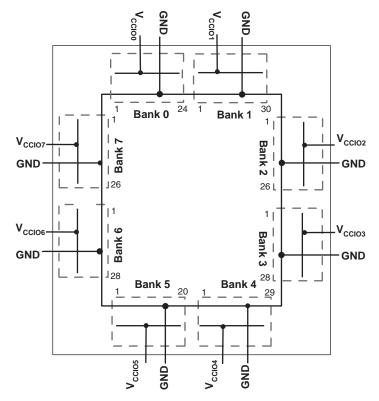

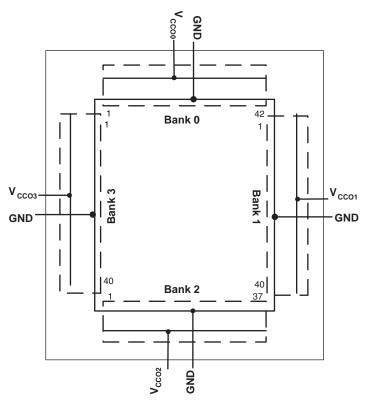

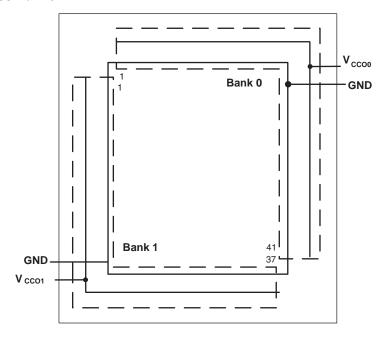

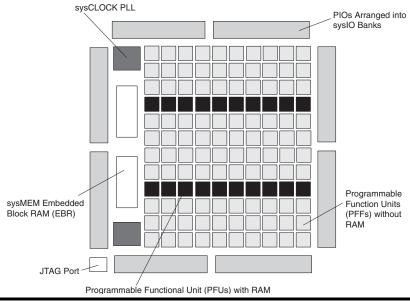

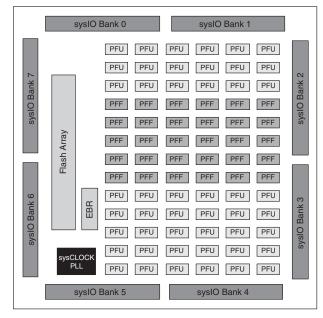

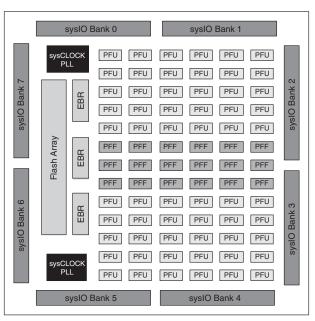

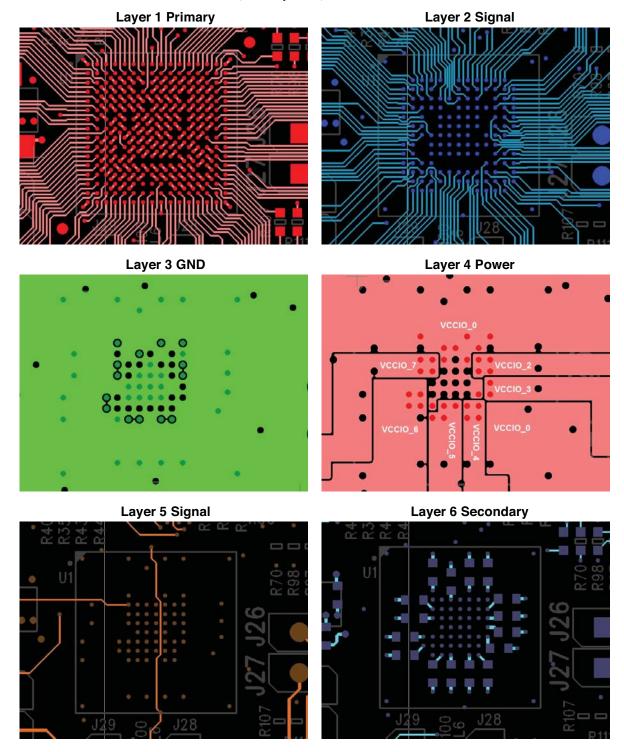

The MachXO family architecture contains an array of logic blocks surrounded by Programmable I/O (PIO). Some devices in this family have sysCLOCK PLLs and blocks of sysMEM™ Embedded Block RAM (EBRs). Figures 2-1, 2-2, and 2-3 show the block diagrams of the various family members.

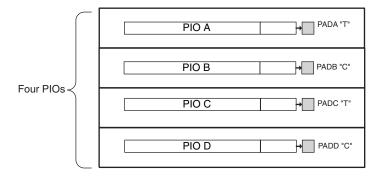

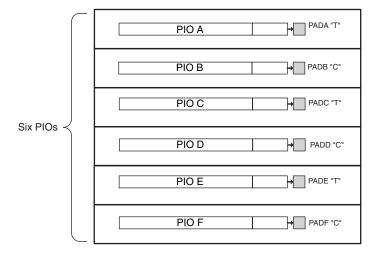

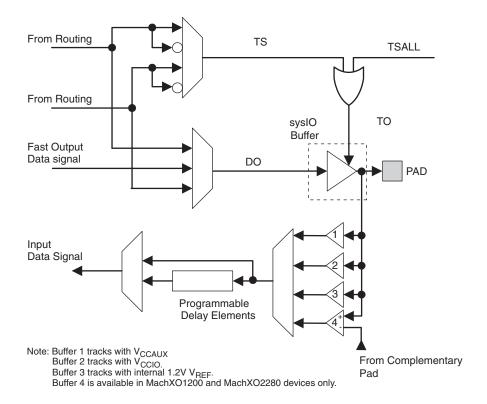

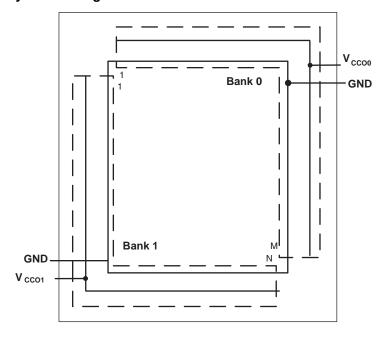

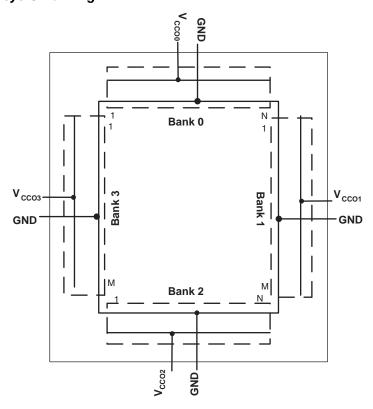

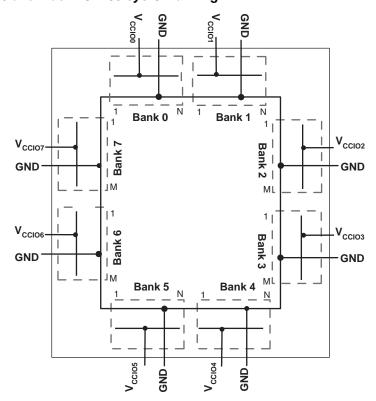

The logic blocks are arranged in a two-dimensional grid with rows and columns. The EBR blocks are arranged in a column to the left of the logic array. The PIO cells are located at the periphery of the device, arranged into Banks. The PIOs utilize a flexible I/O buffer referred to as a sysIO interface that supports operation with a variety of interface standards. The blocks are connected with many vertical and horizontal routing channel resources. The place and route software tool automatically allocates these routing resources.

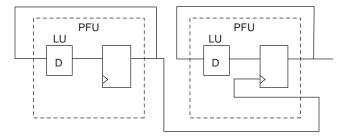

There are two kinds of logic blocks, the Programmable Functional Unit (PFU) and the Programmable Functional unit without RAM (PFF). The PFU contains the building blocks for logic, arithmetic, RAM, ROM, and register functions. The PFF block contains building blocks for logic, arithmetic, ROM, and register functions. Both the PFU and PFF blocks are optimized for flexibility, allowing complex designs to be implemented quickly and effectively. Logic blocks are arranged in a two-dimensional array. Only one type of block is used per row.

In the MachXO family, the number of sysIO Banks varies by device. There are different types of I/O Buffers on different Banks. See the details in later sections of this document. The sysMEM EBRs are large, dedicated fast memory blocks; these blocks are found only in the larger devices. These blocks can be configured as RAM, ROM or FIFO. FIFO support includes dedicated FIFO pointer and flag "hard" control logic to minimize LUT use.

The MachXO architecture provides up to two sysCLOCK™ Phase Locked Loop (PLL) blocks on larger devices. These blocks are located at either end of the memory blocks. The PLLs have multiply, divide, and phase shifting capabilities that are used to manage the frequency and phase relationships of the clocks.

Every device in the family has a JTAG Port that supports programming and configuration of the device as well as access to the user logic. The MachXO devices are available for operation from 3.3V, 2.5V, 1.8V, and 1.2V power supplies, providing easy integration into the overall system.

Figure 2-1. Top View of the MachXO1200 Device<sup>1</sup>

1. Top view of the MachXO2280 device is similar but with higher LUT count, two PLLs, and three EBR blocks.

Figure 2-2. Top View of the MachXO640 Device

Figure 2-3. Top View of the MachXO256 Device

### **PFU Blocks**

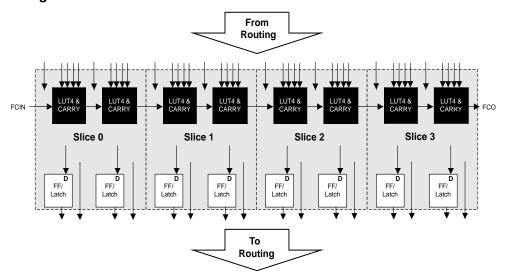

The core of the MachXO devices consists of PFU and PFF blocks. The PFUs can be programmed to perform Logic, Arithmetic, Distributed RAM, and Distributed ROM functions. PFF blocks can be programmed to perform Logic, Arithmetic, and Distributed ROM functions. Except where necessary, the remainder of this data sheet will use the term PFU to refer to both PFU and PFF blocks.

Each PFU block consists of four interconnected Slices, numbered 0-3 as shown in Figure 2-4. There are 53 inputs and 25 outputs associated with each PFU block.

Figure 2-4. PFU Diagram

## Slice

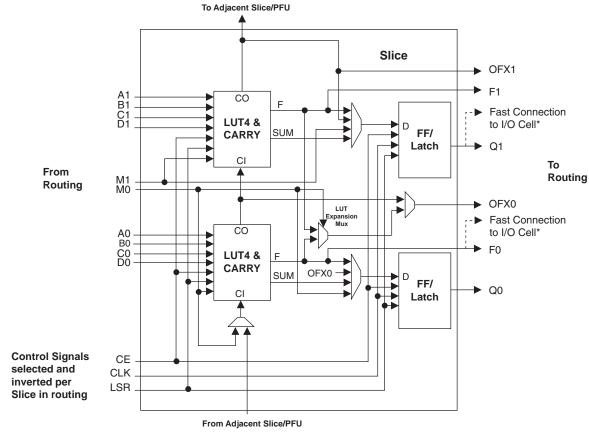

Each Slice contains two LUT4 lookup tables feeding two registers (programmed to be in FF or Latch mode), and some associated logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7, and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/asynchronous), clock select, chip-select, and wider RAM/ROM functions. Figure 2-5 shows an overview of the internal logic of the Slice. The registers in the Slice can be configured for positive/negative and edge/level clocks.

There are 14 input signals: 13 signals from routing and one from the carry-chain (from the adjacent Slice/PFU). There are 7 outputs: 6 to the routing and one to the carry-chain (to the adjacent Slice/PFU). Table 2-1 lists the signals associated with each Slice.

Figure 2-5. Slice Diagram

Notes:

Some inter-Slice signals are not shown.

Table 2-1. Slice Signal Descriptions

| Function | Туре             | Signal Names   | Description                                              |

|----------|------------------|----------------|----------------------------------------------------------|

| Input    | Data signal      | A0, B0, C0, D0 | Inputs to LUT4                                           |

| Input    | Data signal      | A1, B1, C1, D1 | Inputs to LUT4                                           |

| Input    | Multi-purpose    | M0/M1          | Multipurpose Input                                       |

| Input    | Control signal   | CE             | Clock Enable                                             |

| Input    | Control signal   | LSR            | Local Set/Reset                                          |

| Input    | Control signal   | CLK            | System Clock                                             |

| Input    | Inter-PFU signal | FCIN           | Fast Carry In <sup>1</sup>                               |

| Output   | Data signals     | F0, F1         | LUT4 output register bypass signals                      |

| Output   | Data signals     | Q0, Q1         | Register Outputs                                         |

| Output   | Data signals     | OFX0           | Output of a LUT5 MUX                                     |

| Output   | Data signals     | OFX1           | Output of a LUT6, LUT7, LUT82 MUX depending on the Slice |

| Output   | Inter-PFU signal | FCO            | Fast Carry Out <sup>1</sup>                              |

- 1. See Figure 2-4 for connection details.

- 2. Requires two PFUs.

<sup>\*</sup> Only PFUs at the edges have fast connections to the I/O cell.

#### **Modes of Operation**

Each Slice is capable of four modes of operation: Logic, Ripple, RAM, and ROM. The Slice in the PFF is capable of all modes except RAM. Table 2-2 lists the modes and the capability of the Slice blocks.

Table 2-2. Slice Modes

|           | Logic              | Ripple                | RAM     | ROM          |

|-----------|--------------------|-----------------------|---------|--------------|

| PFU Slice | LUT 4x2 or LUT 5x1 | 2-bit Arithmetic Unit | SP 16x2 | ROM 16x1 x 2 |

| PFF Slice | LUT 4x2 or LUT 5x1 | 2-bit Arithmetic Unit | N/A     | ROM 16x1 x 2 |

**Logic Mode:** In this mode, the LUTs in each Slice are configured as 4-input combinatorial lookup tables (LUT4). A LUT4 can have 16 possible input combinations. Any logic function with four inputs can be generated by programming this lookup table. Since there are two LUT4s per Slice, a LUT5 can be constructed within one Slice. Larger lookup tables such as LUT6, LUT7, and LUT8 can be constructed by concatenating other Slices.

**Ripple Mode:** Ripple mode allows the efficient implementation of small arithmetic functions. In ripple mode, the following functions can be implemented by each Slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/Subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Ripple mode multiplier building block

- · Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Two additional signals, Carry Generate and Carry Propagate, are generated per Slice in this mode, allowing fast arithmetic functions to be constructed by concatenating Slices.

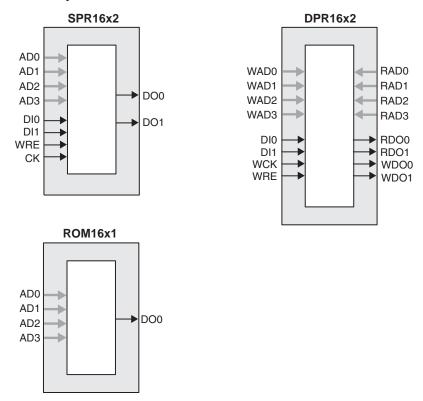

**RAM Mode:** In this mode, distributed RAM can be constructed using each LUT block as a 16x2-bit memory. Through the combination of LUTs and Slices, a variety of different memories can be constructed.

The ispLEVER design tool supports the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of Slices required to implement different distributed RAM primitives. Figure 2-6 shows the distributed memory primitive block diagrams. Dual port memories involve the pairing of two Slices. One Slice functions as the read-write port, while the other companion Slice supports the read-only port. For more information on RAM mode in MachXO devices, please see details of additional technical documentation at the end of this data sheet.

Table 2-3. Number of Slices Required For Implementing Distributed RAM

|                  | SPR16x2 | DPR16x2 |

|------------------|---------|---------|

| Number of Slices | 1       | 2       |

Note: SPR = Single Port RAM, DPR = Dual Port RAM

Figure 2-6. Distributed Memory Primitives

**ROM Mode:** The ROM mode uses the same principal as the RAM modes, but without the Write port. Pre-loading is accomplished through the programming interface during configuration.

### **PFU Modes of Operation**

Slices can be combined within a PFU to form larger functions. Table 2-4 tabulates these modes and documents the functionality possible at the PFU level.

Table 2-4. PFU Modes of Operation

| Logic                      | Ripple            | RAM                        | ROM         |

|----------------------------|-------------------|----------------------------|-------------|

| LUT 4x8 or<br>MUX 2x1 x 8  | 2-bit Add x 4     | SPR16x2 x 4<br>DPR16x2 x 2 | ROM16x1 x 8 |

| LUT 5x4 or<br>MUX 4x1 x 4  | 2-bit Sub x 4     | SPR16x4 x 2<br>DPR16x4 x 1 | ROM16x2 x 4 |

| LUT 6x 2 or<br>MUX 8x1 x 2 | 2-bit Counter x 4 | SPR16x8 x 1                | ROM16x4 x 2 |

| LUT 7x1 or<br>MUX 16x1 x 1 | 2-bit Comp x 4    |                            | ROM16x8 x 1 |

# Routing

There are many resources provided in the MachXO devices to route signals individually or as buses with related control signals. The routing resources consist of switching circuitry, buffers and metal interconnect (routing) segments.

The inter-PFU connections are made with three different types of routing resources: x1 (spans two PFUs), x2 (spans three PFUs) and x6 (spans seven PFUs). The x1, x2, and x6 connections provide fast and efficient connections in the horizontal and vertical directions.

The ispLEVER design tool takes the output of the synthesis tool and places and routes the design. Generally, the place and route tool is completely automatic, although an interactive routing editor is available to optimize the design.

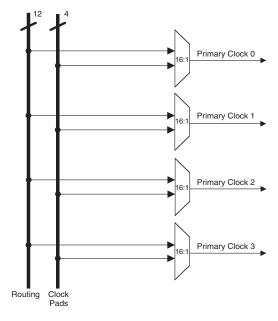

# **Clock/Control Distribution Network**

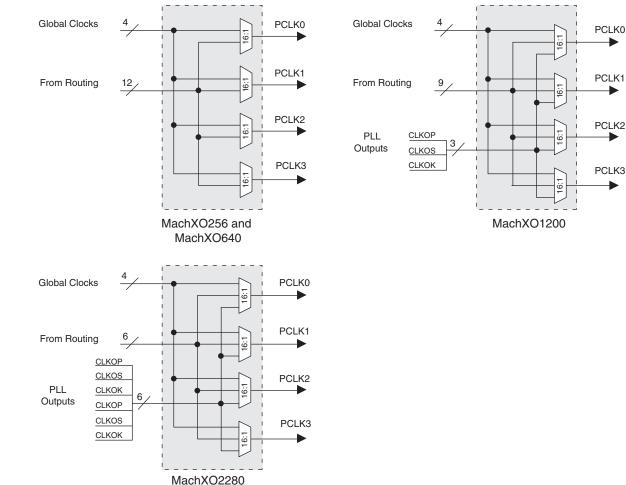

The MachXO family of devices provides global signals that are available to all PFUs. These signals consist of four primary clocks and four secondary clocks. Primary clock signals are generated from four 16:1 muxes as shown in Figure 2-7 and Figure 2-8. The available clock sources for the MachXO256 and MachXO640 devices are four dual function clock pins and 12 internal routing signals. The available clock sources for the MachXO1200 and MachXO2280 devices are four dual function clock pins, up to nine internal routing signals and up to six PLL outputs.

Figure 2-7. Primary Clocks for MachXO256 and MachXO640 Devices

Up to 9

4

Primary Clock 0

Primary Clock 1

16:1

Primary Clock 2

Primary Clock 2

Primary Clock 3

Figure 2-8. Primary Clocks for MachXO1200 and MachXO2280 Devices

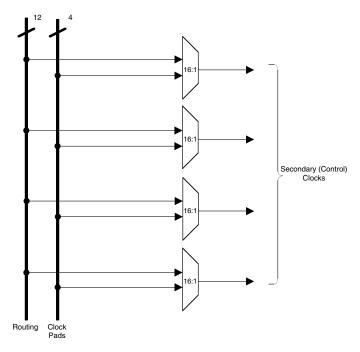

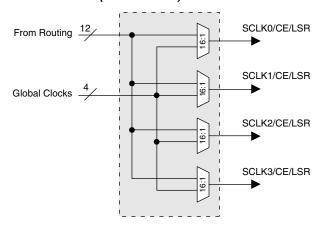

Four secondary clocks are generated from four 16:1 muxes as shown in Figure 2-9. Four of the secondary clock sources come from dual function clock pins and 12 come from internal routing.

Figure 2-9. Secondary Clocks for MachXO Devices

# sysCLOCK Phase Locked Loops (PLLs)

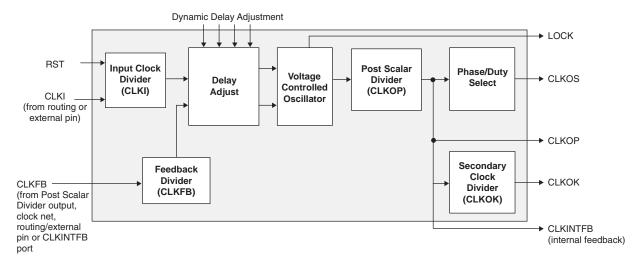

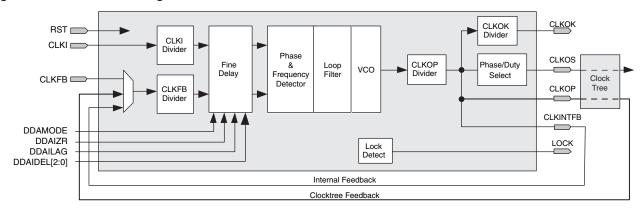

The MachXO1200 and MachXO2280 provide PLL support. The source of the PLL input divider can come from an external pin or from internal routing. There are four sources of feedback signals to the feedback divider: from CLKINTFB (internal feedback port), from the global clock nets, from the output of the post scalar divider, and from the routing (or from an external pin). There is a PLL\_LOCK signal to indicate that the PLL has locked on to the input clock signal. Figure 2-10 shows the sysCLOCK PLL diagram.

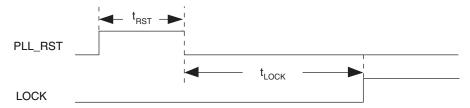

The setup and hold times of the device can be improved by programming a delay in the feedback or input path of the PLL which will advance or delay the output clock with reference to the input clock. This delay can be either programmed during configuration or can be adjusted dynamically. In dynamic mode, the PLL may lose lock after adjustment and not relock until the t<sub>LOCK</sub> parameter has been satisfied. Additionally, the phase and duty cycle block allows the user to adjust the phase and duty cycle of the CLKOS output.

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. Each PLL has four dividers associated with it: input clock divider, feedback divider, post scalar divider, and secondary clock divider. The input clock divider is used to divide the input clock signal, while the feedback divider is used to multiply the input clock signal. The post scalar divider allows the VCO to operate at higher frequencies than the clock output, thereby increasing the frequency range. The secondary divider is used to derive lower frequency outputs.

Figure 2-10. PLL Diagram

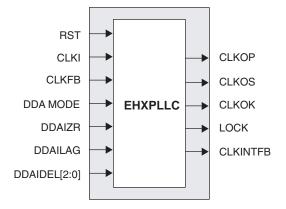

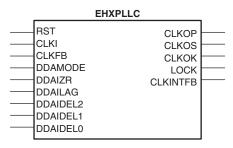

Figure 2-11 shows the available macros for the PLL. Table 2-5 provides signal description of the PLL Block.

Figure 2-11. PLL Primitive

Table 2-5. PLL Signal Descriptions

| Signal       | I/O | Description                                                                                                 |

|--------------|-----|-------------------------------------------------------------------------------------------------------------|

| CLKI         | I   | Clock input from external pin or routing                                                                    |

| CLKFB        | I   | PLL feedback input from PLL output, clock net, routing/external pin or internal feedback from CLKINTFB port |

| RST          | ı   | "1" to reset the input clock divider                                                                        |

| CLKOS        | 0   | PLL output clock to clock tree (phase shifted/duty cycle changed)                                           |

| CLKOP        | 0   | PLL output clock to clock tree (No phase shift)                                                             |

| CLKOK        | 0   | PLL output to clock tree through secondary clock divider                                                    |

| LOCK         | 0   | "1" indicates PLL LOCK to CLKI                                                                              |

| CLKINTFB     | 0   | Internal feedback source, CLKOP divider output before CLOCKTREE                                             |

| DDAMODE      | Į   | Dynamic Delay Enable. "1": Pin control (dynamic), "0": Fuse Control (static)                                |

| DDAIZR       | I   | Dynamic Delay Zero. "1": delay = 0, "0": delay = on                                                         |

| DDAILAG      | ı   | Dynamic Delay Lag/Lead. "1": Lag, "0": Lead                                                                 |

| DDAIDEL[2:0] | !   | Dynamic Delay Input                                                                                         |

For more information on the PLL, please see details of additional technical documentation at the end of this data sheet.

# sysMEM Memory

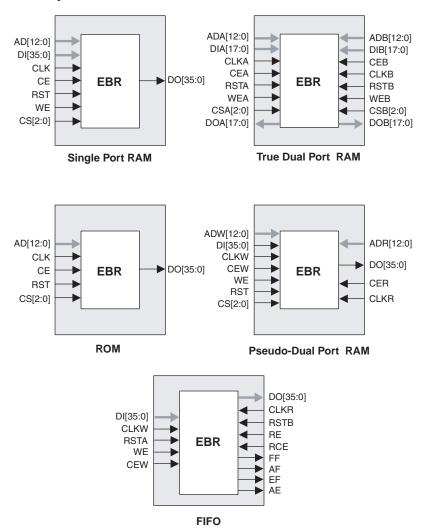

The MachXO1200 and MachXO2280 devices contain sysMEM Embedded Block RAMs (EBRs). The EBR consists of a 9-Kbit RAM, with dedicated input and output registers.

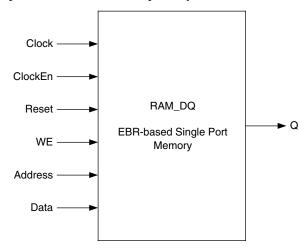

# sysMEM Memory Block

The sysMEM block can implement single port, dual port, pseudo dual port, or FIFO memories. Each block can be used in a variety of depths and widths as shown in Table 2-6.

Table 2-6. sysMEM Block Configurations

| Memory Mode      | Configurations                                                           |

|------------------|--------------------------------------------------------------------------|

| Single Port      | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |

| True Dual Port   | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18             |

| Pseudo Dual Port | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |

| FIFO             | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |

#### **Bus Size Matching**

All of the multi-port memory modes support different widths on each of the ports. The RAM bits are mapped LSB word 0 to MSB word 0, LSB word 1 to MSB word 1 and so on. Although the word size and number of words for each port varies, this mapping scheme applies to each port.

#### **RAM Initialization and ROM Operation**

If desired, the contents of the RAM can be pre-loaded during device configuration. By preloading the RAM block during the chip configuration cycle and disabling the write controls, the sysMEM block can also be utilized as a ROM.

# **Memory Cascading**

Larger and deeper blocks of RAMs can be created using EBR sysMEM Blocks. Typically, the Lattice design tools cascade memory transparently, based on specific design inputs.

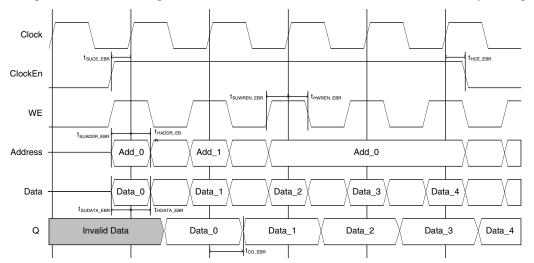

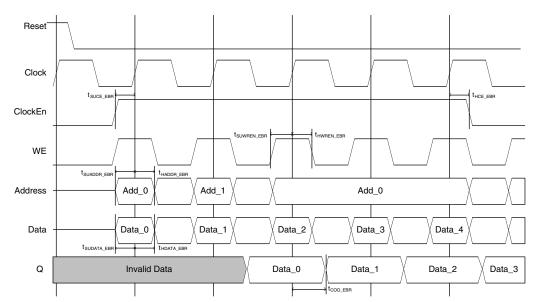

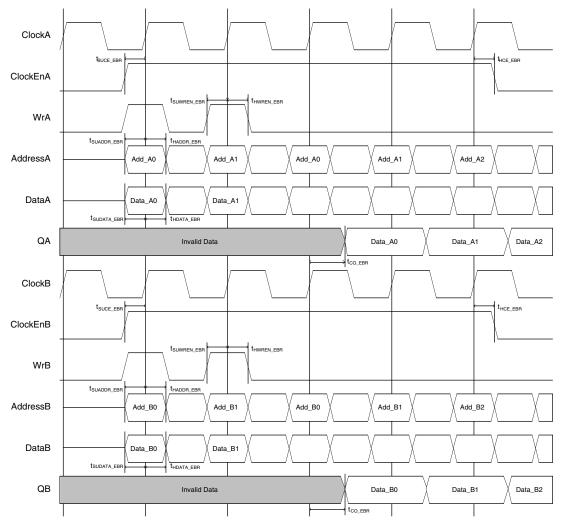

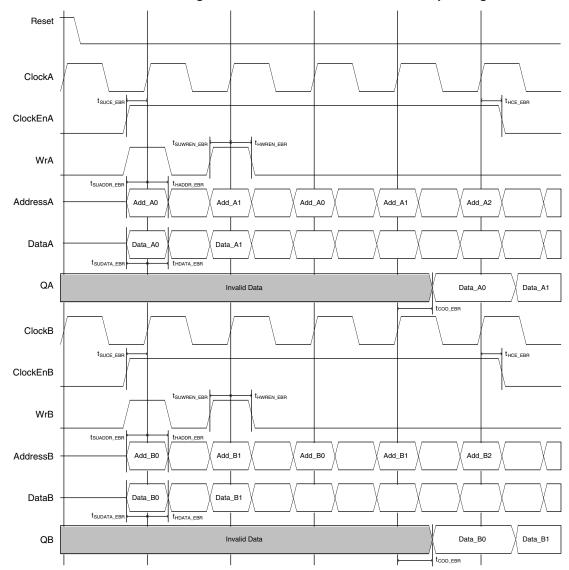

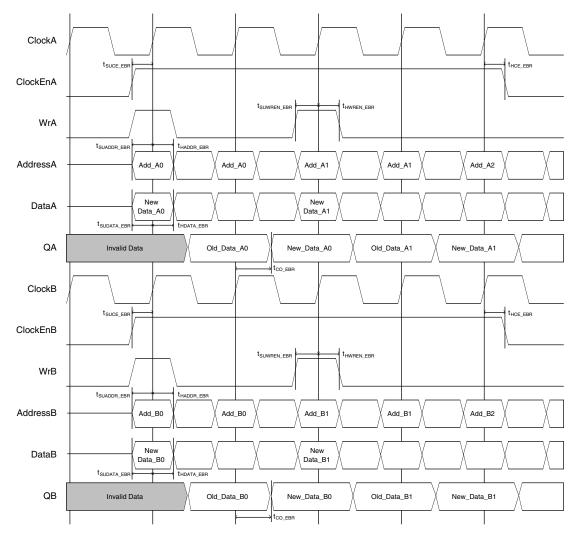

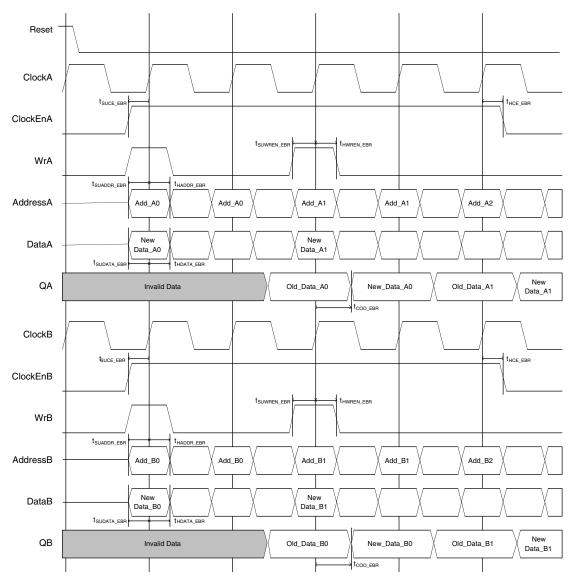

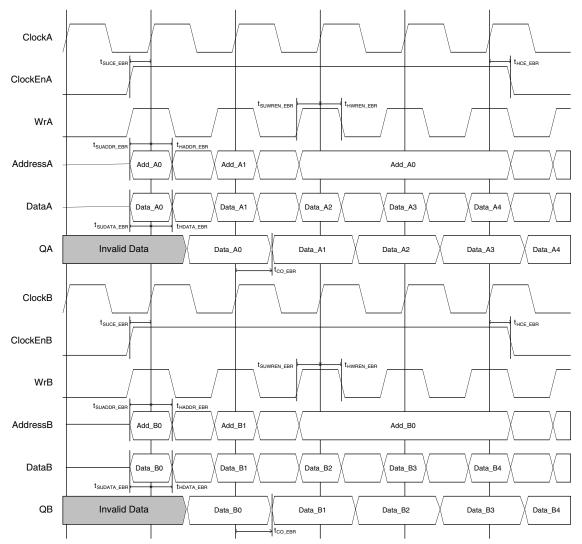

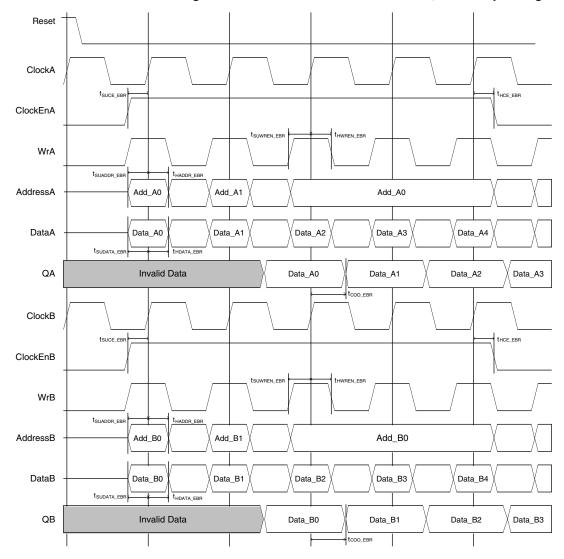

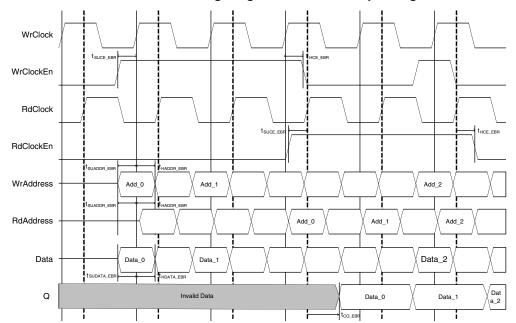

#### Single, Dual, Pseudo-Dual Port and FIFO Modes

Figure 2-12 shows the five basic memory configurations and their input/output names. In all the sysMEM RAM modes, the input data and address for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the memory array output.

Figure 2-12. sysMEM Memory Primitives

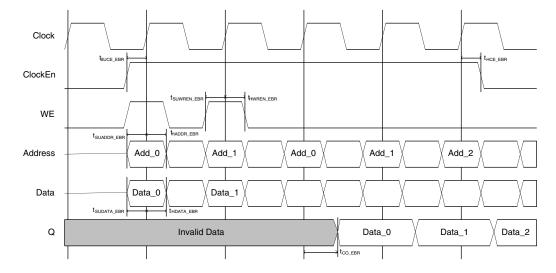

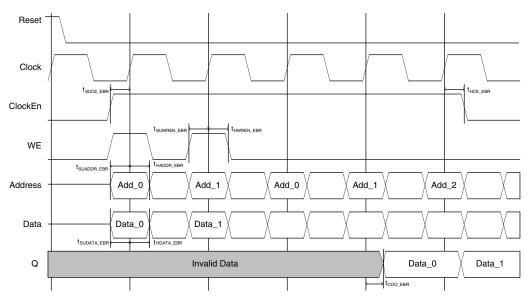

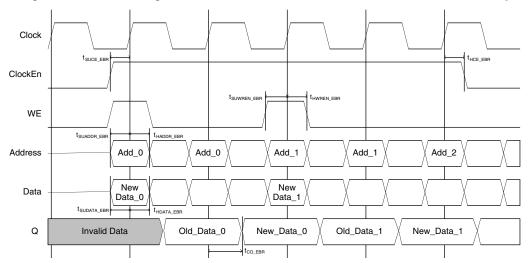

The EBR memory supports three forms of write behavior for single or dual port operation:

- 1. **Normal** data on the output appears only during the read cycle. During a write cycle, the data (at the current address) does not appear on the output. This mode is supported for all data widths.

- 2. **Write Through** a copy of the input data appears at the output of the same port. This mode is supported for all data widths.

- 3. **Read-Before-Write** when new data is being written, the old contents of the address appears at the output. This mode is supported for x9, x18 and x36 data widths.

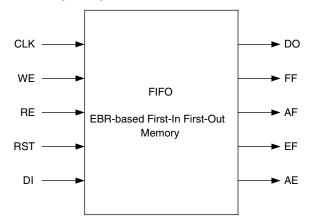

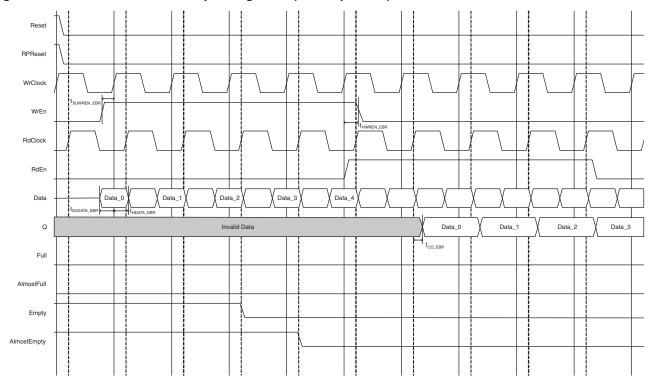

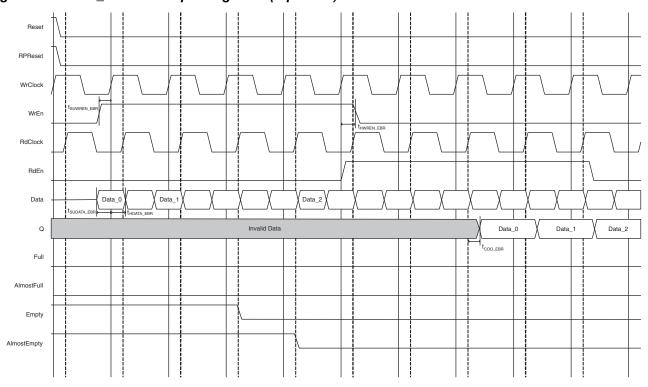

### **FIFO Configuration**

The FIFO has a write port with Data-in, CEW, WE and CLKW signals. There is a separate read port with Data-out, RCE, RE and CLKR signals. The FIFO internally generates Almost Full, Full, Almost Empty and Empty Flags. The Full and Almost Full flags are registered with CLKW. The Empty and Almost Empty flags are registered with CLKR. The range of programming values for these flags are in Table 2-7.

Table 2-7. Programmable FIFO Flag Ranges

| Flag Name         | Programming Range              |

|-------------------|--------------------------------|

| Full (FF)         | 1 to (up to 2 <sup>N</sup> -1) |

| Almost Full (AF)  | 1 to Full-1                    |

| Almost Empty (AE) | 1 to Full-1                    |

| Empty (EF)        | 0                              |

N = Address bit width

The FIFO state machine supports two types of reset signals: RSTA and RSTB. The RSTA signal is a global reset that clears the contents of the FIFO by resetting the read/write pointer and puts the FIFO flags in their initial reset state. The RSTB signal is used to reset the read pointer. The purpose of this reset is to retransmit the data that is in the FIFO. In these applications it is important to keep careful track of when a packet is written into or read from the FIFO.

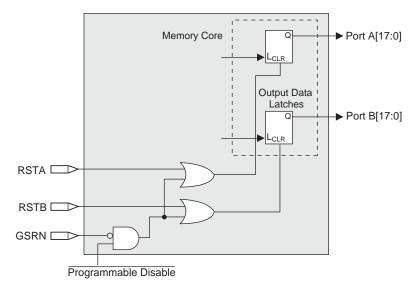

#### **Memory Core Reset**

The memory array in the EBR utilizes latches at the A and B output ports. These latches can be reset asynchronously. RSTA and RSTB are local signals, which reset the output latches associated with Port A and Port B respectively. The Global Reset (GSRN) signal resets both ports. The output data latches and associated resets for both ports are as shown in Figure 2-13.

Figure 2-13. Memory Core Reset

For further information on the sysMEM EBR block, see the details of additional technical documentation at the end of this data sheet.

#### **EBR Asynchronous Reset**

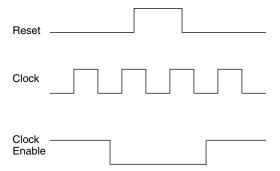

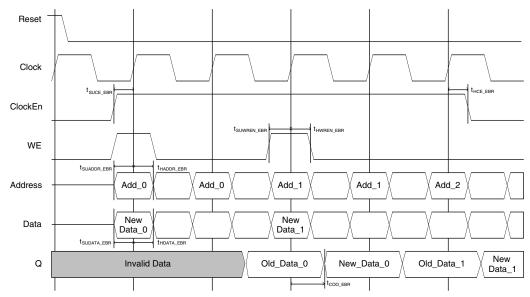

EBR asynchronous reset or GSR (if used) can only be applied if all clock enables are low for a clock cycle before the reset is applied and released a clock cycle after the reset is released, as shown in Figure 2-14. The GSR input to the EBR is always asynchronous.

Figure 2-14. EBR Asynchronous Reset (Including GSR) Timing Diagram

If all clock enables remain enabled, the EBR asynchronous reset or GSR may only be applied and released after the EBR read and write clock inputs are in a steady state condition for a minimum of 1/f<sub>MAX</sub> (EBR clock). The reset release must adhere to the EBR synchronous reset setup time before the next active read or write clock edge.

If an EBR is pre-loaded during configuration, the GSR input must be disabled or the release of the GSR during device Wake Up must occur before the release of the device I/Os becoming active.