# Open-Q<sup>™</sup> 820 (APQ8096) / 820Pro (APQ8096SG) µSOM Development Kit User Guide

[Document: ITC-01RND1239-UG-001 Version: 1.4]

Your use of this document is subject to and governed by those terms and conditions in the Intrinsyc Purchase an Open-Q 820 µSOM Development Kit Based on Snapdragon<sup>TM</sup> 820 Series (APQ8096) Processor and Software License Agreement for the Open-Q 820 µSOM Development Kit, which you or the legal entity you represent, as the case may be, accepted and agreed to when purchasing an Open-Q Development Kit from Intrinsyc Technologies Corporation ("Agreement"). You may use this document, which shall be considered part of the defined term "Documentation" for purposes of the Agreement, solely in support of your permitted use of the Open-Q 820 µSOM Development Kit under the Agreement. Distribution of this document is strictly prohibited without the express written permission of Intrinsyc Technologies Corporation and its respective licensors, which they can withhold, condition or delay in its sole discretion.

Intrinsyc is a trademark of Intrinsyc Technologies Corporation., registered in Canada and other countries.

Qualcomm® and Snapdragon™ are trademarks of Qualcomm® Incorporated, registered in the United States and other countries. Other product and brand names used herein may be trademarks or registered trademarks of their respective owners.

This document contains technical data that may be subject to U.S. and international export, re-export, or transfer ("export") laws. Diversion contrary to U.S. and international law is strictly prohibited.

# **IDENTIFICATION**

Document Title Open-Q™ 820 (APQ8096) / 820Pro (APQ8096SG) µSOM

Development Kit User Guide

Document Number ITC-01RND1239-UG-001

Version 1.4

Date June 7, 2019

# **Revision History**

| REVISION | DATE         | DESCRIPTION                                                                      | PAGES     |

|----------|--------------|----------------------------------------------------------------------------------|-----------|

| 1.0      | Dec 5, 2016  | Initial Draft                                                                    | All       |

| 1.1      | Jan 10, 2017 | Added info on battery charging software Updated figure 16                        | 25, 35    |

| 1.2      | Feb 1, 2017  | Added information on GPS antenna                                                 | 33        |

| 1.3      | Feb 14, 2017 | Added information on WiFi/ BT certification                                      | 16        |

| 1.4      | June 7, 2019 | Update doc to include 820Pro µSOM development kit. Updated USB port descriptions | All<br>19 |

# **Table of Contents**

| 1. | IN  | NTRODUCTION                                  | 5  |

|----|-----|----------------------------------------------|----|

|    | 1.1 | Purpose                                      | 5  |

|    | 1.2 | Scope                                        | 5  |

|    | 1.3 | Intended Audience                            | 5  |

| 2. | D   | OCUMENTS                                     | 6  |

|    | 2.1 | Applicable Documents                         |    |

|    | 2.2 | Reference Documents                          |    |

|    | 2.3 | Terms and Acronyms                           | 6  |

|    | 2.4 | List of Figures                              | 8  |

|    | 2.5 | List of Tables                               | 8  |

| 3. | Oı  | pen-Q 820 µSOM DEVELOPMENT KIT               | 9  |

|    | 3.1 | Introduction                                 | 9  |

|    | 3.2 | Development Platform Notice                  | 9  |

|    | 3.3 | Anti-Static Handling Procedures              | 9  |

|    | 3.4 | Kit Contents                                 |    |

|    | 3.5 | Hardware Identification Label                |    |

|    | 3.6 | System Block Diagram                         |    |

|    | 3.7 | Open-Q 820 / 820Pro μSOM                     |    |

|    | _   | .7.1 µSOM Mechanical Properties              |    |

|    |     | .7.2 μSOM Block Diagram                      | 13 |

|    |     | 7.3 Hardware Specification                   |    |

|    |     | .7.4 µSOM RF Specification for WIFI, BT, GPS |    |

|    | 3.8 | •                                            |    |

|    |     | 8.1 Dip switch S10 Configuration Options     |    |

|    |     | 8.2 Carrier Board Expansion Connectors       |    |

|    |     | 8.4 Battery Header J300                      |    |

|    |     | 8.5 Power Probe Header J86                   |    |

|    | 3.8 | .8.6 Debug Serial UART Header J61            |    |

|    |     | .8.7 Debug Serial UART over USB J22          |    |

|    |     | .8.8 Sensor IO Expansion Header J53          |    |

|    |     | 8.9 Education / GPIO header J54 (EXP2)       |    |

|    |     | .8.10 ANC Headset Jack J27                   |    |

|    |     | 8.11 Audio Inputs Expansion Header J50       |    |

|    |     | .8.12 Audio Outputs Expansion Header J26     |    |

|    |     | 8.14 External and on-Board PCB GPS Antenna   |    |

|    |     | 8.15 Open-Q Display                          |    |

|    |     | 8.16 HDMI Connector J25                      |    |

|    |     | 8.17 Display Connector J2                    |    |

|    |     | .8.18 PCI Express 1X Slot J30                | 39 |

|    | 3.8 | .8.19 Mini PCI Express Connector J72         | 40 |

|    |     | .8.20 Camera Connectors                      | 41 |

|    |     | 8.21 Power Header via 20 Pin Connector J60   |    |

|    | 3.8 | .8.22 Ethernet AVB Expansion Header J73      | 46 |

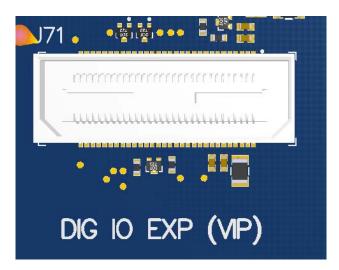

| 3.8.23 | VIP Expansion Header J71      | 47 |

|--------|-------------------------------|----|

|        | USB 2.0 Client Port Operation |    |

|        | USB 2.0 Interface Operation   |    |

|        | USB 3.0 Interface Operation   |    |

## 1. INTRODUCTION

## 1.1 Purpose

The purpose of this user guide is to provide primary technical information on the Open-Q<sup>™</sup> 820 (APQ8096) / 820Pro (APQ8096SG) µSOM Development Kit.

For more background information on this development kit, visit: <a href="www.intrinsyc.com">www.intrinsyc.com</a>

### 1.2 Scope

This document will cover the following items on the Open-Q 820 / 820Pro  $\mu$ SOM Development Kit:

- Block Diagram and Overview

- Hardware Features

- Configuration

- µSOM

- Carrier Board

- Display Board for LCD (Optional)

### 1.3 Intended Audience

This document is intended for users who would like to develop custom applications on the Intrinsyc Open-Q 820 / 820Pro µSOM Development Kit.

# 2. DOCUMENTS

This section lists the supplementary documents for the Open-Q 820/ 820Pro  $\mu$ SOM development kit.

# 2.1 Applicable Documents

| REFERENCE | TITLE                                                                            |  |

|-----------|----------------------------------------------------------------------------------|--|

| A-1       | Intrinsyc Purchase and Software License Agreement for the Open-Q Development Kit |  |

## 2.2 Reference Documents

| REFERENCE | TITLE                                                                          |

|-----------|--------------------------------------------------------------------------------|

| R-1       | Hardware Document Set for the Snapdragon™ APQ8096 based Open-Q Development Kit |

| R-2       | Open-Q 820 / 820Pro Schematics (µSOM, Carrier)                                 |

| R-3       | Open-Q 820 / 820Pro µSOM Carrier Board Design Guide Tech Note 19               |

| R-4       | ITCNFA324 Module Certification OEM Integrator Instructions                     |

# 2.3 Terms and Acronyms

| Term and acronyms                                                               | Definition                                          |  |

|---------------------------------------------------------------------------------|-----------------------------------------------------|--|

| AMIC                                                                            | Analog Microphone                                   |  |

| ANC                                                                             | Audio Noise Cancellation                            |  |

| B2B                                                                             | Board to Board                                      |  |

| Bus access manager Low Speed Peripheral (Serial interfaces like SPI / I2C/ UIM) |                                                     |  |

| BT LE                                                                           | Bluetooth Low Energy                                |  |

| CSI                                                                             | Camera Serial Interface                             |  |

| DSI                                                                             | MIPI Display Serial Interface                       |  |

| EEPROM                                                                          | Electrically Erasable Programmable Read only memory |  |

| eMMC Embedded Multimedia Card                                                   |                                                     |  |

| FCC                                                                             | US Federal Communications Commission                |  |

| FWVGA                                                                           | Full Wide Video Graphics Array                      |  |

| GPS                                                                             | Global Positioning system                           |  |

| HDMI                                                                            | High Definition Media Interface                     |  |

| HSIC High Speed Inter Connect Bus                                               |                                                     |  |

| JTAG Joint Test Action Group                                                    |                                                     |  |

| LNA Low Noise Amplifier                                                         |                                                     |  |

| MIPI                                                                            | Mobile Industry processor interface                 |  |

| MPP                                                                             | Multi-Purpose Pin                                   |  |

| NFC     | Near Field Communication                                                                                              |

|---------|-----------------------------------------------------------------------------------------------------------------------|

| RF      | Radio Frequency                                                                                                       |

| SATA    | Serial ATA                                                                                                            |

| SLIMBUS | Serial Low-power Inter-chip Media Bus                                                                                 |

| μSOM    | micro System On Module                                                                                                |

| SPMI    | System Power Management Interface (Qualcomm® PMIC / baseband proprietary protocol)                                    |

| SSBI    | Single wire serial bus interface (Qualcomm® proprietary mostly PMIC / Companion chip and baseband processor protocol) |

| UART    | Universal Asynchronous Receiver Transmitter                                                                           |

| UFS     | Universal Flash Storage                                                                                               |

| UIM     | User Identity module                                                                                                  |

| USB     | Universal Serial Bus                                                                                                  |

| USB HS  | USB High Speed                                                                                                        |

| USB SS  | USB Super Speed                                                                                                       |

# 2.4 List of Figures

| Figure 1 Assembled Open-Q 820 / 820Pro µSOM Development Kit            | 10            |

|------------------------------------------------------------------------|---------------|

| Figure 2 Open-Q 820 / 820Pro µSOM + Carrier Board Block Diagram        |               |

| Figure 3 Open-Q 820 / 820Pro µSOM                                      |               |

| Figure 4 µSOM Block Diagram                                            | 14            |

| Figure 5 J21 12V DC Power Jack                                         | 22            |

| Figure 6 J300 Battery Header                                           | 23            |

| Figure 7 J86 Power Probe Header                                        | 24            |

| Figure 8 J61 3.3V TTL Debug UART                                       | 24            |

| Figure 9 J22 Debug UART over USB                                       | 25            |

| Figure 10 J53 Sensor Expansion Header                                  | 25            |

| Figure 11 J55 Gen-10 Sensor Connector (Samtec QSH-030 series)          | 27            |

| Figure 12 J54 Education / GPIO header                                  | 28            |

| Figure 13 ANC Headphone Jack                                           | 29            |

| Figure 14 J50 Audio Inputs Expansion Header                            | 30            |

| Figure 15 J26 Audio Outputs Expansion Header                           | 31            |

| Figure 16 On Board PCB Antennas                                        | 33            |

| Figure 17 HDMI Type A Connector                                        | 34            |

| Figure 18 100-Pin Display Connector                                    | 35            |

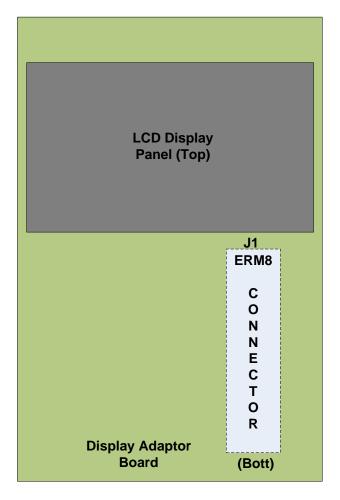

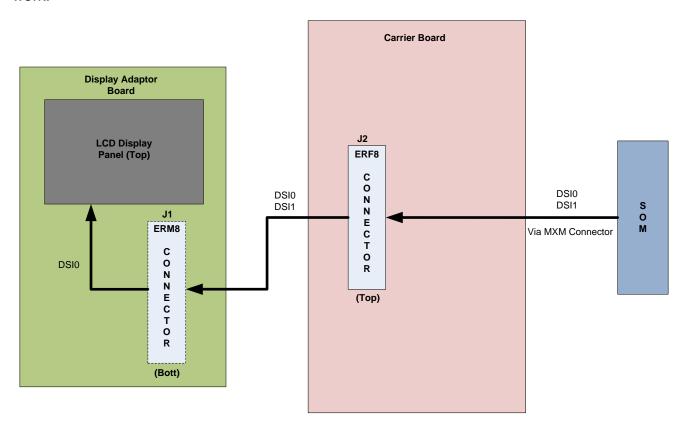

| Figure 19 Display Board Block Diagram                                  | 37            |

| Figure 20 Display Board Default Configuration                          | 38            |

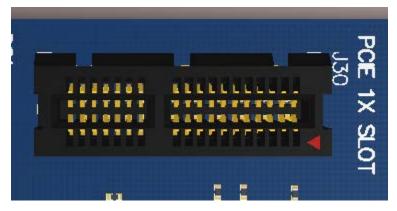

| Figure 21 J30 PCIe Connector                                           | 39            |

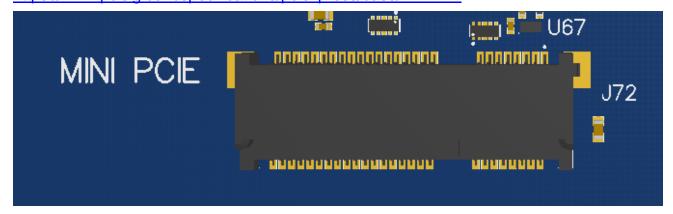

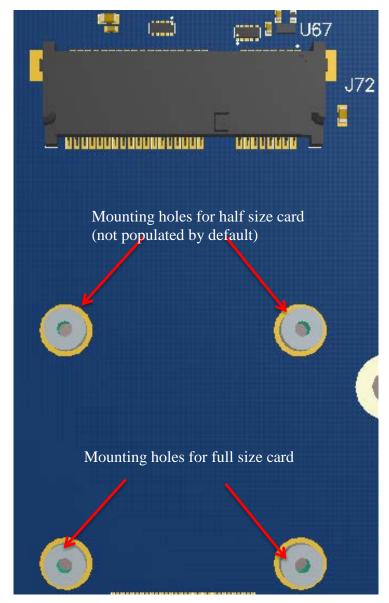

| Figure 22 J72 Mini PCIe Connector                                      | 40            |

| Figure 23 Mounting holes for Mini PCIe Connector                       | 41            |

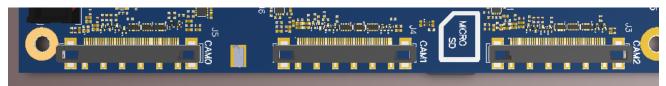

| Figure 24 Camera Connectors (J5, J4, J3)                               | 42            |

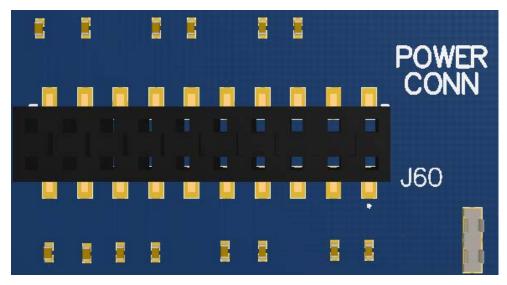

| Figure 25 J60 Power Connector                                          | 45            |

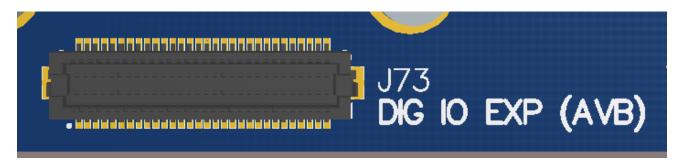

| Figure 26 J73 Ethernet AVB Expansion Header                            | 46            |

| Figure 27 J71 VIP Expansion Header                                     | 47            |

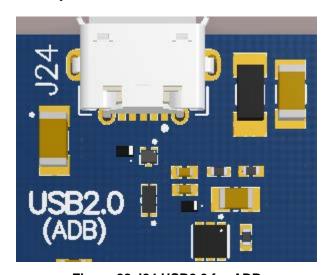

| Figure 28 J24 USB2.0 for ADB                                           | 47            |

| Figure 29 J85 USB1 Connector                                           | 48            |

| Figure 30 S1 Board Configuration Switch (on Bottom of Development Kit) | 48            |

| Figure 31 J23 USB3.0 Host Ports                                        | 49            |

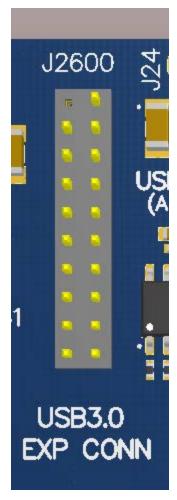

| Figure 32 J2600 USB3.0 Expansion Connector                             | 50            |

|                                                                        |               |

| 2.5 List of Tables                                                     |               |

| Table 3.7-1 Open-Q 820 / 820Pro μSOM Hardware Features                 | 15            |

| Table 3.8-1 Dip Switch HW / SW configuration                           |               |

| Table 3.8-2 Carrier Board Expansion Options and Usage                  |               |

| Table 3.8-3 Sensor Expansion Header J53 Pin out                        | 10<br>つん      |

| Table 3.8-4 Education Connector Expansion Header J54 Pin Out           |               |

| Table 3.8-5 Audio Inputs Expansion Header J50 Pin out                  |               |

| Table 3.8-6 Audio Outputs Expansion Header J26 Pin out                 |               |

| Table 3.8.20-1. MIPI CSI Camera Connector Pinouts (J5,J4,J3)           |               |

| Table 3.8.20-2. MIPI CSI Camera Use Cases                              |               |

| 1 uo 10 0.0.40 4, 17111 1 CD1 Cuincia Cot Caoco                        | <del>++</del> |

# 3. OPEN-Q 820 µSOM DEVELOPMENT KIT

#### 3.1 Introduction

The Open-Q 820 / 820Pro µSOM provides a quick reference or evaluation platform for Qualcomm's latest 820 series - Snapdragon™ 820 processor. This kit is suited for Android / Linux application developers, OEMs, consumer manufacturers, hardware component vendors, video surveillance, robotics, camera vendors, and flash chip vendors to evaluate, optimize, test and deploy applications that can utilize the Qualcomm® Snapdragon™ 820 series technology.

### 3.2 Development Platform Notice

This development platform contains RF/digital hardware and software intended for engineering development, engineering evaluation, or demonstration purposes only and is meant for use in a controlled environment. This device is not being placed on the market, leased or sold for use in a residential environment or for use by the general public as an end user device.

This development platform is not intended to meet the requirements of a commercially available consumer device including those requirements specified in the European Union directives applicable for Radio devices being placed on the market, FCC equipment authorization rules or other regulations pertaining to consumer devices being placed on the market for use by the general public.

This development platform may only be used in a controlled user environment where operators have obtained the necessary regulatory approvals for experimentation using a radio device and have appropriate technical training. The device may not be used by members of the general population or other individuals that have not been instructed on methods for conducting controlled experiments and taking necessary precautions for preventing harmful interference and minimizing RF exposure risks. Additional RF exposure information can be found on the FCC website at http://www.fcc.gov/oet/rfsafety/

# 3.3 Anti-Static Handling Procedures

The Open-Q 820 / 820Pro  $\mu$ SOM Development Kit has exposed electronics and chipsets. Proper anti-static precautions should be employed when handling the kit, including but not limited to:

- Using a grounded anti-static mat

- Using a grounded wrist or foot strap

#### 3.4 Kit Contents

The Open-Q 820 / 820Pro µSOM Development Kit includes the following:

Open-Q 820 µSOM with Snapdragon™ APQ8096 processor or Open-Q 820Pro µSOM with Snapdragon™ APQ8096SG processor

- Mini-ITX form-factor carrier board

- 4.5" FWVGA (480x854) 16.7 M LCD (Additional Accessory)

- o AC power adapter and HDMI cable

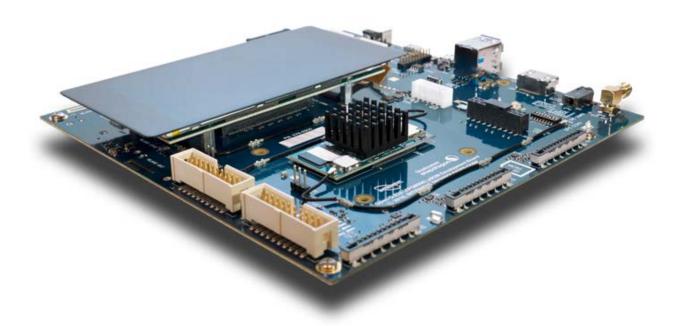

Figure 1 Assembled Open-Q 820 / 820Pro µSOM Development Kit

The development kit comes with Android software pre-programmed on the CPU board (µSOM). Please contact Intrinsyc for availability of camera modules, sensor boards, and other accessories: <a href="mailto:sales@intrinsyc.com">sales@intrinsyc.com</a>

#### 3.5 Hardware Identification Label

Labels are present on the CPU board and the mini-ITX form-factor carrier board. The following information is conveyed on these two boards:

CPU board (µSOM).:

- Serial Number

- WIFI MAC address

Refer to <a href="http://support.intrinsyc.com/account/serialnumber">http://support.intrinsyc.com/account/serialnumber</a> for more details about locating the serial number, as this will be needed to register the development kit. To register a development kit, please visit: <a href="http://support.intrinsyc.com/account/register">http://support.intrinsyc.com/account/register</a>

Mini-ITX form-factor carrier board:

Serial Number

**Note:** Please retain the  $\mu$ SOM and carrier board serial number for warranty purposes.

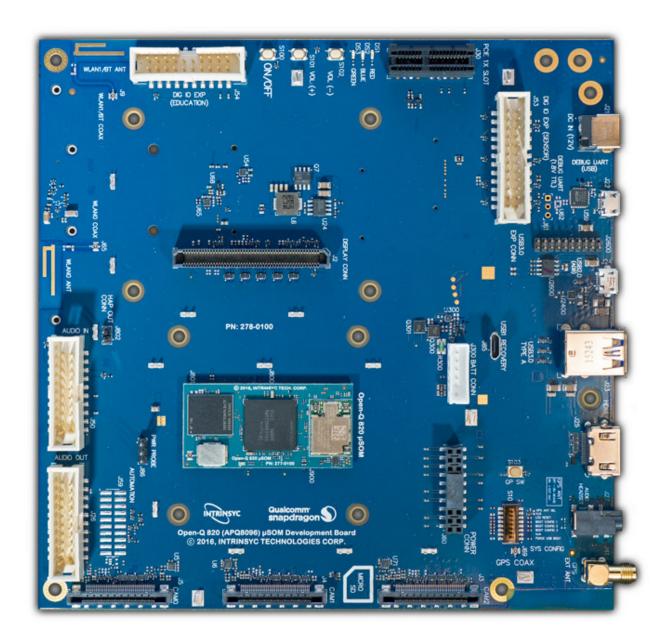

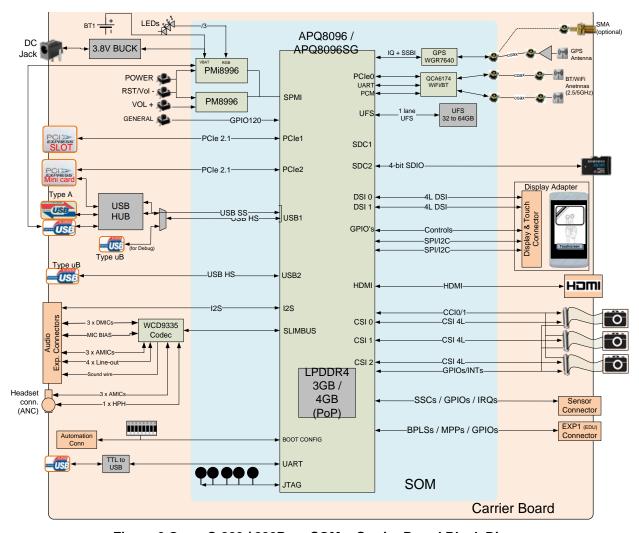

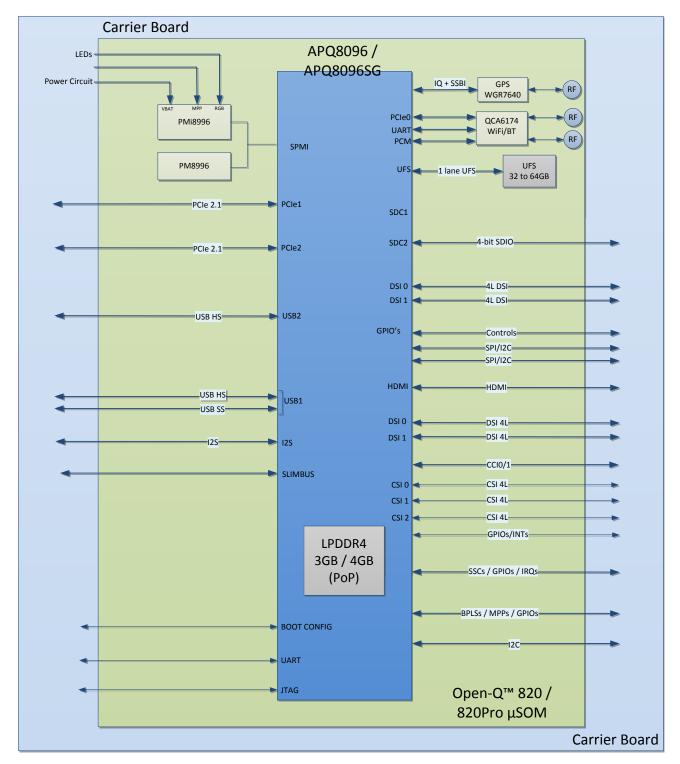

### 3.6 System Block Diagram

The Open-Q 820 / 820Pro µSOM development platform consists of three major components

- Open-Q 820 / 820Pro μSOM

- Carrier board for I/O and connecting with external peripherals

- Display Adapter Board (additional accessory)

The following diagram explains the interconnectivity and peripherals on the development kit.

Figure 2 Open-Q 820 / 820Pro µSOM + Carrier Board Block Diagram

# 3.7 Open-Q 820 / 820Pro µSOM

The µSOM provides the basic common set of features with minimal integration efforts for end users.

It contains the following:

- Snapdragon™ APQ8096 or APQ8096SG main application processor

- LPDDR4 up to 1866MHz 3GB or 4GB RAM (POP)

- PMI8996 + PM8996 PMIC for Peripheral LDOs, Boost Regulators

- QCA6174 Atheros Wi-Fi + BT combo chip over PCIe, UART, PCM

- 32 GB UFS 2.0.

- WGR7640 RF Front End

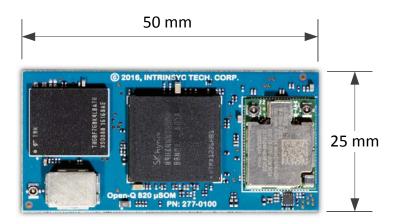

Figure 3 Open-Q 820 / 820Pro µSOM

### 3.7.1 µSOM Mechanical Properties

| Area      | 12.5 cm <sup>2</sup> (25 mm x 50 mm)                                 |

|-----------|----------------------------------------------------------------------|

| Interface | 3 x 100-pins Hirose DF40 connectors (B2B Connector).                 |

| Thermal   | A top side heat sink is installed by default.                        |

| Shielding | A top side shield can for the GPS front end is installed by default. |

## 3.7.2 µSOM Block Diagram

The Open-Q 820 / 820Pro  $\mu$ SOM measuring 25mm x 50mm is where all the processing occurs. It is connected to the carrier via three 100 pin Hirose DF40 connectors. The purpose of these connectors is to bring out essential signals such that other peripherals can be connected to the platform.

Figure 4 µSOM Block Diagram

### 3.7.3 Hardware Specification

The Open-Q 820 / 820Pro µSOM platform encompasses the following hardware features:

Table 3.7-1 Open-Q 820 / 820Pro uSOM Hardware Features

| Subsystem /   | Feature Set                                                           | Q 820 / 820Pro µSOM Hardwar<br>Description                                                                                                                                                   | Specification                                                                                  |

|---------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Connectors    | reature oet                                                           | -                                                                                                                                                                                            | Opecinication                                                                                  |

| Chipset       | APQ8096 or<br>APQ8096SG                                               | Qualcomm® Snapdragon™<br>820 Processor                                                                                                                                                       | Qualcomm® Kyro CPU, quad core, 64-bit ARM V8 compliant processor, 2.2GHz (2.34GHz for 820Pro)  |

|               | PMIC (PM8996 & PMI8996)                                               | Qualcomm® PMIC,<br>Companion PMIC for<br>APQ8096 processor                                                                                                                                   | NA                                                                                             |

| Memory        | 3GB LPDDR4<br>(4GB for 820Pro)                                        | Memory POP                                                                                                                                                                                   | Up to 1866MHz LPDDR4 POP<br>on CPU BGA chip. Supports<br>via 4x16bit channels                  |

|               | 32 GB UFS                                                             | Primary Storage for platform. Mainly used for storing SW applications and user data etc.                                                                                                     | Toshiba UFS on board. Can support up to 256GB                                                  |

| Connectivity  | Wi-Fi 2.4 GHz/<br>5GHz via<br>QCA6174 – SDIO                          | Wi-Fi Atheros QCA6174 Wi-<br>Fi + BT Combo Chip                                                                                                                                              | 802.11a/b/g/n/ac 2.4/5.0 GHz<br>via QCA6174 over PCIe0.<br>Full 2x2 antenna configuration      |

|               | BT 2.4 GHz via<br>QCA6174 – UART<br>/ PCM                             | Wi-Fi Atheros 6174<br>Wi-Fi + BT Combo Chip                                                                                                                                                  | Support BT 4.1 + HS and backward compatible with BT 1.x, 2.x + EDR                             |

|               | GPS via WGR7640  - SSBI Qualcomm® Proprietary Protocol                | GPS Frontend                                                                                                                                                                                 | GPS, GLONASS, COMPASS                                                                          |

| RF Interfaces | 2xWLAN / BT                                                           | Connect to antenna on carrier board via coax cable                                                                                                                                           | 2.4/ 5 GHz                                                                                     |

|               | 1x GPS                                                                | Connect to antenna on carrier board via coax cable                                                                                                                                           | GPS/GLONASS/COMPASS                                                                            |

| Interfaces    | 3 x MIPI CSI                                                          | Camera Connectors<br>CSI0, CSI1, CSI2                                                                                                                                                        | MIPI Alliance Specification v1.0                                                               |

|               | 2 x USB HS & 1 x<br>USB SS                                            | 1 x USB3.1 header, 1 x dual<br>stack type A USB3.0 via USB<br>HUB for front USB (from<br>USB1 line), 1 x USB 2.0 via<br>switch (from USB1 line), 1 x<br>micro AB USB 2.0 (from<br>USB2 line) | USB3.1 & USB2.0                                                                                |

|               | 1 x MIPI DSI (DSI0<br>& DSI1) + Touch<br>100-pin display<br>Connector | 100- pin display connector.<br>Interfaces with Intrinsyc<br>Display Adapter Board                                                                                                            | MIPI Alliance Specification<br>v1.01. MIPI D-PHY<br>Specification v0.65,v0.81,<br>v0.90, v1.01 |

|               | 3 X PCIe                                                              | PCIe 0 PCIe signal to Wi-Fi<br>module. PCIe 1, 2 routed out<br>of µSOM                                                                                                                       | PCI Express Specification, Rev 2.1                                                             |

| Connector     | 3 x board to board connector                                          | Connectors to interface with carrier board                                                                                                                                                   | Hirose DF40C series 100pin connector                                                           |

### 3.7.4 µSOM RF Specification for WIFI, BT, GPS

The µSOM includes the following radio interfaces:

Wi-Fi + BT: ANT1Wi-Fi only: ANT2

WGR7640: For GPS RF Front end

**Antenna 1**: Antenna 1 is used for providing Wi-Fi and Bluetooth connectivity to QCA6174. This antenna is meant to be connected to the carrier board via a coaxial cable. The function of this connector is for extending the dual band capabilities of the Wi-Fi chip; therefore, enabling this antenna to be used simultaneously with Antenna 2. For example, Antenna 2 can be connected to 2.4GHz while Antenna 1 can be connected to 5.1 GHz. To turn on Bluetooth, only Antenna 1 can be used.

**Antenna 2**: Antenna 2 provides Wi-Fi connectivity for QCA6174. This antenna connector is meant to be connected to the carrier board PCB antenna via a coaxial cable. ANT2 is a standard dual band antenna from 2.4 GHz to 5.1 GHz.

The  $\mu$ SOM WiFi/BT module has received regulatory certifications (see FCC ID: 2AFDI-ITCNFA324 for details). Please note that the on-board PCB antennas were not the antennas used for the  $\mu$ SOM WiFi/BT module certification. Refer to the certification documents for the WiFi/BT module (see R-4) for information regarding the test configurations used for certification. Deviating from the documented configuration may trigger the need for re-certification.

For details on connecting the WiFi module to the on-board PCB antennas on the carrier board, refer to section 3.8.13 below.

**WGR7640**: GPS Front End WGR7640 is the primary GPS radio interface used on the Open-Q 820 µSOM development kit. This provides the RF capabilities for GNSS functions. It has both digital and RF interfaces. Digital interface is required for configuration and status of the APQ8096 baseband processor.

The following are the operating frequencies for WGR7640

GPS: 1574.42 MHz – 1576.42 MHz GLONASS: 1598 MHz to 1606 MHz

# 3.8 Open-Q 820 / 820Pro µSOM Carrier Board

The Open-Q 820 / 820Pro  $\mu$ SOM Carrier board is a Mini-ITX form factor board with various connectors used for connecting different peripherals. The following are the mechanical properties of the carrier board:

| Dimensions       | 289 cm <sup>2</sup> (170mm x 170mm)                  |

|------------------|------------------------------------------------------|

| Form Factor      | Mini-ITX                                             |

| Major Interfaces | See <u>section 3.9</u> for details regarding carrier |

|                  | board interfaces                                     |

### 3.8.1 Dip switch S10 Configuration Options

There is a DIP switch S10 on the top side of the Open-Q 820 / 820Pro  $\mu$ SOM carrier board. The 8-bit switch allows the user to control the system configuration and boot options. Table 3.8-1 below outlines the pin outs and connections of this DIP switches.

Table 3.8-1 Dip Switch HW / SW configuration

|                      | DIP    |                                                                                                                                                                                                               |                                                                   |

|----------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Function             | Switch | Description                                                                                                                                                                                                   | Notes                                                             |

| FORCED_USB_BOOT      | S10-1  | Toggles between FORCE USB boot and EDL mode. Enables FORCE USB (GPIO 57) when DIP switch turned on                                                                                                            | Default out of the box configuration is OFF which is the EDL mode |

|                      |        |                                                                                                                                                                                                               | <b>Note:</b> FORCE USB boot option not supported by Intrinsyc     |

| NC                   | S10-2  | N/A                                                                                                                                                                                                           | N/A                                                               |

| BOOT_CONFIG[3]       | S10-3  | Enables APQ boot configuration 3 when DIP switch turned on. Controlled by APQ GPIO104 See schematic for boot configuration options. NOTE: µSOMe boot configurations are not supported on the development kit. | Default out of the box configuration is ON                        |

| BOOT_CONFIG[2]       | S10-4  | Enables APQ boot configuration 2 when DIP switch turned on. Controlled by APQ-GPIO103                                                                                                                         | Default out of the box configuration is OFF                       |

| BOOT_CONFIG[1]       | S10-5  | Enables APQ boot configuration 1 when DIP switch turned on. Controlled by APQ-GPIO 102                                                                                                                        | Default out of the box configuration is OFF                       |

| WATCHDOG<br>_DISABLE | S10-6  | Enables WATCHDOG_DISABLE when DIP switch turned on. Controlled by APQ-GPIO 101                                                                                                                                | Default out of the box configuration is OFF                       |

| N/C                  | S10-7  | NA                                                                                                                                                                                                            | NA                                                                |

| GPS_ANT_SEL          | S10-8  | Option to select which antenna to use for GPS. When DIP switch ON GPS external antenna is being used (SMA connector). When OFF, GPS printed antenna is being used (onboard)                                   | Default out of the box configuration is OFF                       |

**Warning!**: Before making any changes to the dip switch, make sure to note down the previous configuration. The default switch settings are above.

## 3.8.2 Carrier Board Expansion Connectors

The following table lists the connectors, expansions and their usages on the carrier board:

**Table 3.8-2 Carrier Board Expansion Options and Usage**

| Domain                                                      | Description                                                                                                                     | Specification                                                                                    | Usage                                                                                                                |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Power                                                       | AC / Barrel charger                                                                                                             | 12 V DC Power Supply<br>5 A                                                                      | Power Supply                                                                                                         |

|                                                             | Power connector                                                                                                                 | 20 pin header                                                                                    | For providing extra<br>current to camera<br>connectors when<br>needed (ie: when high<br>performance cameras<br>used) |

|                                                             | Battery Connector                                                                                                               | 6 pin header                                                                                     | For Battery operation and charging development                                                                       |

| Debug Serial via USB                                        | Debug Serial UART console over USB for development                                                                              | USB Micro B connector                                                                            | Development Serial<br>Connector for debug<br>output via USB                                                          |

| Buttons                                                     | General Purpose SW button                                                                                                       | SMD Button                                                                                       | Additional button for general purpose (connected to APQ_GPIO120)                                                     |

|                                                             | Power Button                                                                                                                    | SMD Button                                                                                       | Power Button for<br>Suspend / Resume and<br>Power off                                                                |

| Zoom / Volume Keys                                          | Volume + key Volume – key                                                                                                       | SMD Button SMD Button                                                                            | Volume +Key<br>Volume – Key                                                                                          |

| Sensor IO Connector                                         | 24 pin Sensor Expansion<br>Connectors                                                                                           | Support any user sensor card, Standard 24-pin ST Micro PLCC support via optional daughter card   | Available via Intrinsyc optional accessories kit                                                                     |

| GPIO / Education<br>connector Header                        | 20-pin general purpose IO for SPI / I2C / GPIOs/ UIM/ UART functions and other unused GPIOs from PMIC and APQ education header. | Full BLSP1 (SPI/ UART/<br>I2C/ GPIO)<br>APQ GPIOs<br>MPPs<br>Power                               | Useful when user wants to use UART GPIOs pins as BLSP other functions (GPIO/ I2C/ UIM/ SPI).                         |

| Micro SD (on bottom)                                        | Micro SD card                                                                                                                   | 4bit Micro SD card support                                                                       | External Storage                                                                                                     |

| ANC Audio Jack                                              | Audio Jack supported using WCD9335                                                                                              | ANC audio jack providing<br>2lineout and 1 headset<br>drivers (with Qualcomm®<br>ANC technology) | Audio support                                                                                                        |

| 3-Digital Microphone via<br>audio input expansion<br>header | Audio expansion<br>Supported using<br>WCD9335                                                                                   | Digital Audio header                                                                             | For Digital audio input<br>for Digital MIC, I2S<br>codec, Slim bus<br>interface.                                     |

| Domain                                                  | Description                                                         | Specification                                      | Usage                                                                                                                      |

|---------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 3-Analog Microphone via audio input expansion header    | Audio expansion<br>Supported using<br>WCD9335                       | Analog Audio header                                | For Analog audio input<br>for Analog MIC<br>(differential signal)                                                          |

| 2-Loud Speaker via audio output expansion header        | Audio expansion<br>Supported using<br>WCD9335                       | Analog Audio header                                | For loud speaker output after signal has been processed                                                                    |

| Earpiece via audio output expansion header              | Audio expansion<br>Supported using<br>WCD9335                       | Analog Audio header                                | For earpiece output<br>after signal has been<br>processed                                                                  |

| Haptics driver via audio output expansion header        | Audio expansion<br>Supported using<br>WCD9335                       | Analog Audio header                                | For haptics output (ex: vibrator) after signal has been processed                                                          |

| Ultrasound transducer via audio output expansion header | Audio expansion<br>Supported using<br>WCD9335                       | Analog Audio header                                | Ultrasound transducer output                                                                                               |

| HDMI Port                                               | Extended Display ports                                              | HDMI port supports up to 4K without HDCP 1.4A spec | External Display                                                                                                           |

| USB 2.0                                                 | USB 2.0 via the USB2 port                                           | Micro AB connector                                 | USB client mode for<br>ABD (development kit<br>default)<br>USB host mode<br>(requires support from<br>Intrinsyc to enable) |

| USB 3.1                                                 | USB 3.1 via USB1<br>through USB switch and<br>hub                   | Dual Type A connector                              | Host mode transfer data to and from CPU (concurrent use with USB recovery port below is not possible)                      |

| USB Expansion connector                                 | 2 additional USB3.1 ports<br>via USB1 through USB<br>switch and Hub | Samtec TMMH series header                          | Additional USB ports                                                                                                       |

| USB Recovery                                            | USB 2.0 via USB1<br>through USB switch                              | Vertical Micro B connector                         | USB recovery/ debug<br>(for factory purposes<br>only)                                                                      |

| WLAN Antenna                                            | 2X PCB Antenna                                                      | 2.4 – 5.1 GHz                                      | Antenna to µSOM WiFi<br>module                                                                                             |

| Domain                                 | Description                                                           | Specification                                                                                                                                         | Usage                                                                                                                                            |

|----------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| GPS Antenna                            | PCB Antenna                                                           | GPS:<br>1574.42 MHz – 1576.42<br>MHz<br>GLONASS:<br>1587 MHz – 1606 MHz                                                                               | Antenna to µSOM GPS module                                                                                                                       |

| GPS External Antenna via SMA Connector | SMA connector for external GPS antenna                                | Supports active antenna                                                                                                                               | External GPS antenna                                                                                                                             |

| Coin Cell<br>Holder(Optional)          | Coin Cell battery(Optional via stuffing)                              | Coin cell battery for PMIC<br>RTC                                                                                                                     | RTC                                                                                                                                              |

| LED                                    | 3xLED                                                                 | Red : PMIC Driven<br>Green: PMIC Driven<br>Blue: PMIC Driven                                                                                          | Blue : General Purpose<br>Red : Charging<br>Green : Charging<br>complete                                                                         |

| LCD Display and Touch connector        | 100 pin for LCD signals via b2b connector to display adapter board    | 4-lane MIPI DSI0 , DSI1<br>I2C/SPI/GPIO<br>Backlight<br>MIPI Alliance Specification<br>v1.01<br>MIPI D-PHY Specification<br>v0.65,v0.81, v0.90, v1.01 | Can work as one dual<br>DSI or both independent<br>display                                                                                       |

| Gen10 connector                        | Connector for<br>Qualcomm's internal<br>sensor boards                 | 60 pin connector sensor<br>Gen 10                                                                                                                     | To interface with Qualcomm's internal sensor boards (for Intrinsyc internal use only – not supported) Can be used for other purposes.            |

| VIP Extension connector                | Connector for interfacing with Qualcomm® legacy automotive VIP boards | 60 pin connector                                                                                                                                      | To connect to Qualcomm® legacy automotive VIP boards (for Intrinsyc internal use only – not supported) Can be used for other purposes.           |

| Ethernet AVB connector                 | Connector for interfacing with Ethernet AVB standard                  | 60 pin connector                                                                                                                                      | To connect to automotive peripherals via Ethernet AVB standard (for Intrinsyc internal use only – not supported) Can be used for other purposes. |

| PCI Express Slot                       | PCI Express for external peripheral connectivity                      | PCIe1 v2.1<br>Supports half card only<br>Supports 10W card via<br>power supply                                                                        | To connect an Ethernet PCIe card board to support Ethernet.                                                                                      |

| Domain                        | Description                                           | Specification                                                                                                                                                                                                                                                 | Usage                                  |

|-------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|                               |                                                       | Supports 25W card via ATX power supply                                                                                                                                                                                                                        |                                        |

| Mini PCI Express<br>Connector | Mini PCI Express for external peripheral connectivity | PCIe1 v2.1<br>Can support half or full size<br>card                                                                                                                                                                                                           | For external mini PCIe card            |

| WWAN SIM Card (on bottom)     | WWAN SIM card<br>connector (optional)                 | 4bit Mini SIM card support                                                                                                                                                                                                                                    | For WWAN mini PCI express cards        |

| CSI Camera connectors         | 3 x CSI port connector with CLK, GPIOS, CCI           | Supports 3 x Camera interfaces via three separate connectors  • 3 x MIPI-CSI each 4 lane  • External flash driver control  • Support for 3D camera configuration  • Separate I2C / CCI control  MIPI Alliance Specification v1.00 for Camera Serial Interface |                                        |

| Power Probe Header            | 3 pin power probe header                              | Sense lines connected across 0.005 Ohm resistor                                                                                                                                                                                                               | To measure current consumption of μSOM |

| Haptics Connector             | 2 pin haptics driver header                           | Haptics driver output from PMI8996                                                                                                                                                                                                                            | For connecting a 2 pin vibrating motor |

The sections below will provide in depth information on each expansion header and connector on the carrier board. The information listed below is of particular use for those who want to interface other external hardware devices with the Open-Q 820 / 820Pro  $\mu$ SOM. Before connecting anything to the development kit, please ensure the device meets the specific hardware requirements of the processor.

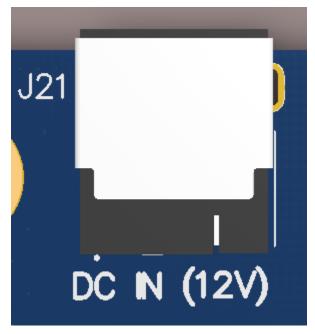

#### 3.8.3 DC Power Input J21

The Open-Q 820 / 820Pro  $\mu$ SOM development kit power source connects to the 12V DC power supply jack J21. Starting from the power jack, the 12V power supply branches off into different voltage rails via step down converters on the carrier board and PMIC on the  $\mu$ SOM. The  $\mu$ SOM is powered by 3.8V via a Texas Instrument step down converter U400 on the

carrier board. To ensure the  $\mu$ SOM is getting powered correctly, user can monitor the current going into the  $\mu$ SOM via the power probe header J86 (see section <u>below</u>).

Figure 5 J21 12V DC Power Jack

The µSOM consists of 2 PMIC modules. Functionalities of the 2 modules are outlined below.

#### PMI8996 PMIC is used for:

- Source various regulated power rails

- Battery charging. Please see section below for additional information on battery support.

- Please note that support for battery charging over external charger is not implemented in the design. Please contact Intrinsyc for such customization.

#### PM8996 PMIC is used for:

- Source various regulated power rails

- Source system clock

### 3.8.4 Battery Header J300

Figure 6 J300 Battery Header

The Open-Q 820 / 820Pro µSOM development platform can also power the µSOM with a single cell Lithium-Ion Polymer (LiPo) battery pack which connects to header J300. The purpose of this header is to be used by the end user to develop a battery charging solution, including battery characterization. Intrinsyc recommends using the AA Portable Power Corp's CU-J479-V2 / 1ICP7/55/85 Lithium ion battery pack. This is a single cell pack with a nominal voltage of 3.8V and a capacity of 3200mAh (11.8 Wh, 5A rate). If user intends to use a different battery, please note the pin outs on this battery header.

| Description                           | Signal                                                        | Pin     | Note                                                                  |

|---------------------------------------|---------------------------------------------------------------|---------|-----------------------------------------------------------------------|

| μSOM Battery positive supply terminal | VBAT Plus (VBAT+)                                             | J300[1] |                                                                       |

| μSOM Battery positive supply terminal | VBAT Plus (VBAT+)                                             | J300[2] |                                                                       |

| N/C                                   | N/C                                                           | J300[3] |                                                                       |

| Internal battery pack temperature     | BATT_THERM (The recommended battery has a 10K Ohm thermistor) | J300[4] | Depopulate R197<br>if battery selected<br>has a 10K ohm<br>thermistor |

| μSOM Battery negative supply terminal | VBAT Minus(VBAT-)                                             | J300[5] |                                                                       |

| μSOM Battery negative supply terminal | VBAT Minus(VBAT-)                                             | J300[6] |                                                                       |

Please note that the battery only powers the  $\mu$ SOM. To ensure proper functionality of the development kit, the 12V power supply must be attached at J21. When a battery is not in use, the TI step down converter U400 is used to power the  $\mu$ SOM.

Note that the software that is shipped with the development kit does NOT support battery charging. Please visit the Intrinsyc support site and follow the instructions for preparing the platform to support battery charging.

#### 3.8.5 Power Probe Header J86

Figure 7 J86 Power Probe Header

The power probe header is used to sense/ monitor the current on the 3.8V power rail going into the µSOM. The table below summarizes the pin outs of header J86.

| Description                            | Signal           | Pin    |

|----------------------------------------|------------------|--------|

| μSOM power positive current sense line | µSOM_PWR_SENSE_P | J86[1] |

| μSOM power negative current sense line | µSOM_PWR_SENSE_N | J86[2] |

| GND                                    | GND              | J86[3] |

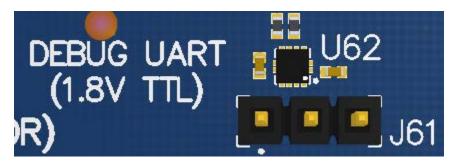

#### 3.8.6 Debug Serial UART Header J61

Figure 8 J61 3.3V TTL Debug UART

The UART header and supporting circuitry does not come preinstalled. To have access to the debug UART, a 3-pin header needs to be installed as well as the supporting circuitry. Please see page 17 of the  $\mu$ SOM carrier board schematic for details on what to install for this header to be functional.

The header consists of TX, RX and GND pins. This is a 3.3V TTL UART header. To get the serial terminal working with a PC, the following cable (or similar) is needed <a href="http://www.digikey.ca/product-detail/en/TTL-232R-RPI/768-1204-ND/4382044">http://www.digikey.ca/product-detail/en/TTL-232R-RPI/768-1204-ND/4382044</a>

| Description         | Signal        | Pin    | FTDI RPI cable connection |

|---------------------|---------------|--------|---------------------------|

| APQ UART RX (GPIO5) | BLSP8_UART_RX | J61[1] | Orange                    |

| APQ UART TX (GPIO4) | BLSP8_UART_TX | J61[2] | Yellow                    |

| GND                 | GND           | J61[3] | Black                     |

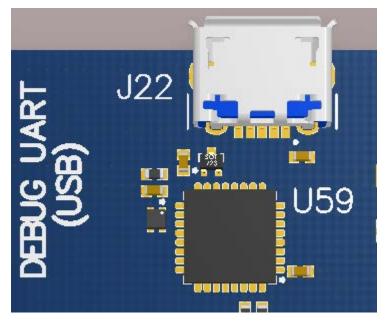

### 3.8.7 Debug Serial UART over USB J22

Figure 9 J22 Debug UART over USB

The UART connection used on the Open-Q 820 / 820Pro  $\mu$ SOM is a USB micro B connector (J22). This debug UART is available over USB via the FTDI FT232RQ chip on the carrier board. To get the serial terminal working with a PC, user needs to ensure that the appropriate FTDI drivers are installed.

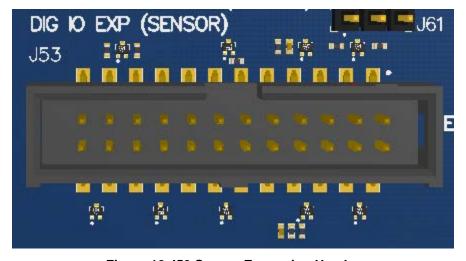

### 3.8.8 Sensor IO Expansion Header J53

Figure 10 J53 Sensor Expansion Header

The sensor expansion header J53 allows for a 24-pin connection to an optional sensor board. If user application does not require a sensor, then this header can be used for other applications that require I2C or GPIO input and output connections.

Following is the pin breakout for sensor expansion header J53.

Table 3.8-3 Sensor Expansion Header J53 Pin out

| Description                                                                      | Signal                  | Pin<br>NO   | Description                                                                                   | Signal             | Pin<br>NO   |

|----------------------------------------------------------------------------------|-------------------------|-------------|-----------------------------------------------------------------------------------------------|--------------------|-------------|

| SSC I2C-3 serial data                                                            | SSC_I2C_3_SDA           | J53[1]      | Acceleromete r interrupt input to processor via GPIO117                                       | ACCEL_INT_N        | J53[2]      |

| SSC I2C-3 serial clock                                                           | SSC_I2C_3_SCL           | J53[3]      | Cap interrupt input to processor via GPIO123                                                  | CAP_INT_N          | J53[4]      |

| Sensor reset signal from processor to sensor via GPIO80                          | MEMS_RESET_N            | J53[5]      | Gyroscope<br>interrupt input<br>to processor<br>via GPIO118                                   | GYRO_INT           | J53[6]      |

| Sensor IO PWR 1.8<br>V<br>VREG_LVS2A_1P<br>8 power supply<br>regulator (Digital) | SENS_IO_PWR             | J53[7]      | Sensor<br>Analog power<br>supply from<br>VREG_L19A<br>2.85V or 3.3V<br>(If R160<br>populated) | SENS_ANA_PWR       | J53[8]      |

| GND                                                                              | GND                     | J53[9]      | GND                                                                                           | GND                | J53[10      |

| HRM interrupt/<br>configurable<br>GPIO122                                        | HRM_INT                 | J53[11<br>] | Touch screen<br>interrupt input<br>from<br>processor via<br>GPIO125                           | TS_INT0            | J53[12<br>] |

| SSC SPI-1 chip<br>select 2                                                       | SSC_SPI_1_CS1_MAG_<br>N | J53[13<br>] | Alternate<br>sensor<br>interrupt input<br>to processor<br>via GPIO120                         | ALSPG_INT_N        | J53[14<br>] |

| NC                                                                               | NC                      | J53[15<br>] | Digital<br>Compass<br>interrupt input<br>to processor<br>via GPIO119                          | MAG_DRDY_INT       | J53[16<br>] |

| NC                                                                               | NC                      | J53[17<br>] | NC                                                                                            | NC                 | J53[18<br>] |

| SSC SPI-1 chip<br>select 1                                                       | SSC_SPI_1_CS_N          | J53[19<br>] | SSC SPI-1<br>data master<br>out/ slave in                                                     | SSC_SPI_1_MOS      | J53[20<br>] |

| SSC SOI-1 clock                                                                  | SSC_SPI_1_CLK           | J53[21<br>] | SSC SPI-1<br>data master<br>in/ slave out                                                     | SSC_SPI_1_MIS<br>O | J53[22<br>] |

| Description | Signal | Pin<br>NO   | Description      | Signal     | Pin<br>NO   |

|-------------|--------|-------------|------------------|------------|-------------|

| NC          | NC     | J53[23<br>] | SSC power enable | SSC_PWR_EN | J53[24<br>] |

In sum, if sensor application is not needed, this expansion header can provide two full BLSP7 and BLSP5 for UART/ SPI/ I2C/ UIM. Please refer to the schematic and consider the power before connecting anything to this header.

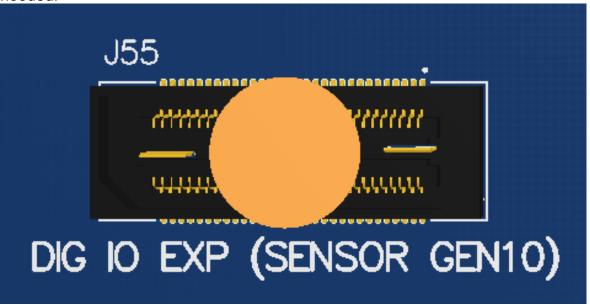

Note that there is an unpopulated Gen-10 connector header (J55) footprint at the bottom of the carrier board. Install the Samtec (part number: QSH-030-01-L-D-A) connector here if needed.

Figure 11 J55 Gen-10 Sensor Connector (Samtec QSH-030 series)

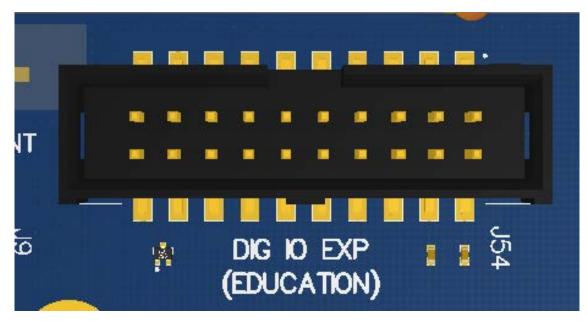

### 3.8.9 Education / GPIO header J54 (EXP2)

Figure 12 J54 Education / GPIO header

Education/ GPIO header expansion J54 is a 20 pin connector that provides access to BLSP1 signals with level shifters. It is ideally used for connecting external peripherals such as microcontrollers and any other devices that are based on I2C, SPI, UART, UIM and GPIO. Please refer to the  $\mu$ SOM carrier board schematic for the level shifter, target voltage and current rating depending on stuffing option. The education expander also supports multiple voltage ratings. The table below outlines the configurations for these settings:

| Voltage Rails       | Resistors to Populate (0 Ohm) |

|---------------------|-------------------------------|

| MB_VREG_3P3 - 3.3 V | R150 (Default)                |

| VREG_S4A_1P8 - 1.8V | R149                          |

| MB_VREG_5P0 - 5.0 V | R151                          |

The following are the detailed pin out information for education header J54.

Table 3.8-4 Education Connector Expansion Header J54 Pin Out

| Description       | Signal                             | Pin NO | Description                                          | Signal       | Pin NO |

|-------------------|------------------------------------|--------|------------------------------------------------------|--------------|--------|

| NC                | NC                                 | J54[1] | VREG_S4A 1.8V<br>voltage regulator max<br>150mA      | VREG_S4A_1P8 | J54[2] |

| BLSP1_3_3P3(3.3V) | BLSP1_SPI_<br>MOSI (APQ-<br>GPIO0) | J54[3] | VDD_EXP2 (Default<br>3.3V Power Supply)<br>max 300mA | VDD_EXP2     | J54[4] |

| BLSP1_2_3P3(3.3V) | BLSP1_SPI_<br>MISO (APQ-<br>GPIO1) | J54[5] | NC                                                   | N/C          | J54[6] |

| Description       | Signal                             | Pin NO  | Description                  | Signal      | Pin NO  |

|-------------------|------------------------------------|---------|------------------------------|-------------|---------|

| BLSP1_1_3P3(3.3V) | BLSP1_SPI_C<br>S_N (APQ-<br>GPIO2) | J54[7]  | PM8996 MPP GPIO4             | PM_MPP04    | J54[8]  |

| BLSP1_0_3P3(3.3V) | BLSP1_SPI_C<br>LK (APQ-<br>GPIO3)  | J54[9]  | NC                           | N/C         | J54[10] |

| NC                | N/C                                | J54[11] | NC                           | N/C         | J54[12] |

| NC                | N/C                                | J54[13] | NC                           | N/C         | J54[14] |

| NC                | N/C                                | J54[15] | NC                           | N/C         | J54[16] |

| GND               | GND                                | J54[17] | NC                           | N/C         | J54[18] |

| NC                | N/C                                | J54[19] | 5V power supply max<br>150mA | MB_VREG_5P0 | J54[20] |

### 3.8.10 ANC Headset Jack J27

Figure 13 ANC Headphone Jack

The ANC headset jack (J27) is a special 3.5mm TRRS jack with ANC capabilities. It is backwards compatible with standard headset jacks. Please contact Intrinsyc at <a href="mailto:sales@intrinsyc.com">sales@intrinsyc.com</a> for compatible ANC headsets.

### 3.8.11 Audio Inputs Expansion Header J50

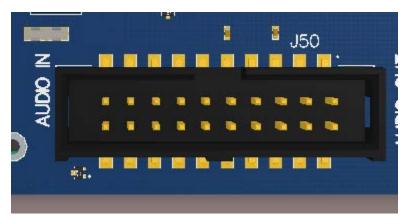

Figure 14 J50 Audio Inputs Expansion Header

This header expansion provides the following audio inputs:

- 1. 3 digital mic inputs (each can support 2 digital microphones)

- 2. 3 analog mics

- 3. Voltage rails to support analog and digital mics

For details on how to connect analog or digital microphones to system, refer to sections 4.1.9 on Open-Q 820 / 820Pro  $\mu$ SOM Development Kit  $\mu$ SOM Technical Note19 (document R-3).

The table below outlines the pin out information of the audio inputs expansion header J50:

Table 3.8-5 Audio Inputs Expansion Header J50 Pin out

| Description                             | Signal            | Pin NO  | Description                                   | Signal        | Pin NO  |

|-----------------------------------------|-------------------|---------|-----------------------------------------------|---------------|---------|

| Analog MIC1 positive differential input | CDC_IN1_P         | J50[1]  | Analog MIC1<br>negative differential<br>input | CDC_IN1_N     | J50[2]  |

| Analog MIC5 positive differential input | CDC_IN5_P         | J50[3]  | Analog MIC5<br>negative differential<br>input | CDC_IN5_N     | J50[4]  |

| MIC bias output voltage 1               | MIC_BIAS1         | J50[5]  | MIC bias output voltage 3                     | MIC_BIAS3     | J50[6]  |

| Analog MIC6 positive differential input | CDC_IN6_P         | J50[7]  | Analog MIC6<br>negative differential<br>input | CDC_IN6_N     | J50[8]  |

| MIC bias output voltage 4               | MIC_BIAS4         | J50[9]  | 3.3V power supply max 500mA                   | MB_VREG_3P3   | J50[10] |

| GND                                     | GND               | J50[11] | GND                                           | GND           | J50[12] |

| Clock for digital MIC 1 and 2           | CDC_DMIC_CL<br>K0 | J50[13] | Clock for digital MIC 3 and 4                 | CDC_DMIC_CLK1 | J50[14] |

| Description                   | Signal             | Pin NO  | Description                   | Signal             | Pin NO  |

|-------------------------------|--------------------|---------|-------------------------------|--------------------|---------|

| Digital MIC 1 and 2 data line | CDC_DMIC_DA<br>TA0 | J50[15] | Digital MIC 3 and 4 data line | CDC_DMIC_DAT<br>A1 | J50[16] |

| 1.8V power supply max 300mA   | VREG_S4A_1P<br>8   | J50[17] | Clock for digital MIC 5 and 6 | CDC_DMIC_CLK2      | J50[18] |

| GND                           | GND                | J50[19] | Digital MIC 5 and 6 data line | CDC_DMIC_DAT<br>A2 | J50[20] |

### 3.8.12 Audio Outputs Expansion Header J26

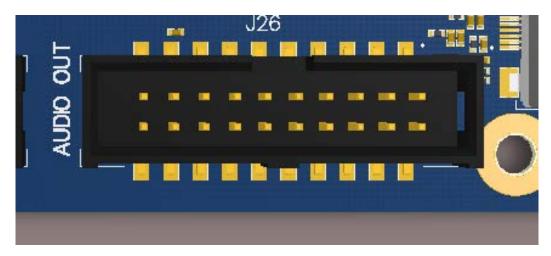

Figure 15 J26 Audio Outputs Expansion Header

This header expansion provides the following audio outputs:

- 1. 2 differential analog audio line out

- 2. 2 single ended analog audio line out

- 3. 1 differential analog earpiece amplifier output (no external amp needed)

- 4. 2 speaker amplifier enable control

- 5. Voltage rails to support analog and digital mics

The table below outlines the pin out information of the audio outputs expansion header J26:

| Description                                           | Signal | Pin NO | Description                                           | Signal          | Pin NO |

|-------------------------------------------------------|--------|--------|-------------------------------------------------------|-----------------|--------|

| Analog audio line out 1, positive differential output |        | J26[1] | Analog audio line out 1, negative differential output | CDC_LINE_OUT1_N | J26[2] |

| Analog audio line out 2, positive differential output |        | J26[3] | Analog audio line out 2, negative differential output | CDC_LINE_OUT2_N | J26[4] |

**Table 3.8-6 Audio Outputs Expansion Header J26 Pin out**

| Description                                                        | Signal            | Pin NO  | Description                                                        | Signal        | Pin NO  |

|--------------------------------------------------------------------|-------------------|---------|--------------------------------------------------------------------|---------------|---------|

| Audio line outputs 3 and 4 GND reference                           | CDC_LINE_RE<br>F  | J26[5]  | 3.3V output power supply                                           | MB_VREG_3P3   | J26[6]  |

| Analog audio line out 3, single ended output                       | CDC_LINE_OU<br>T3 | J26[7]  | Analog audio line out 4, single ended output                       | CDC_LINE_OUT4 | J26[8]  |

| Analog earpiece amplifier out, positive differential output        | CDC_EAR_P         | J26[9]  | Analog earpiece amplifier out, negative differential output        | CDC_EAR_N     | J26[10] |

| GND                                                                | GND               | J26[11] | 3.8V output power supply                                           | MB_VREG_SOM   | J26[12] |

| Digital soundwire data for WSA8810/WSA8815 smart speaker amplifier | CDC_SWR_CL<br>K   | J26[13] | Digital soundwire data for WSA8810/WSA8815 smart speaker amplifier | CDC_SWR_DATA  | J26[14] |

| Speaker amplifier enable 1                                         | SPKR_AMP_EN<br>1  | J26[15] | Speaker amplifier enable 2                                         | SPKR_AMP_EN2  | J26[16] |

| 1.8V output power supply                                           | VREG_S4A_1P<br>8  | J26[17] | 12V output power supply                                            | DC_IN_12V     | J26[18] |

| 5.0V output power supply                                           | MB_VREG_5P0       | J26[19] | GND                                                                | GND           | J26[20] |

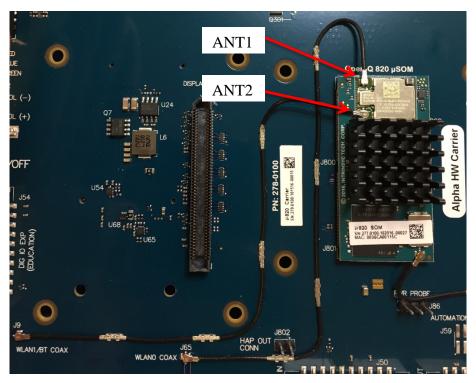

#### 3.8.13 On Board PCB WLAN Antenna

The Open-Q 820 / 820Pro  $\mu$ SOM carrier board has two on board WLAN PCB antennas that connects to the QCA6174 WiFi module on the  $\mu$ SOM via coaxial cables that attaches to MH4L receptacles. These antennas connect to the  $\mu$ SOM in the following configuration:

- WLAN1 on the carrier board connects to ANT2 on the QCA6174 WiFi module

- WLAN0 on the carrier board connects to ANT1 on the QCA6174 WiFi module

Figure 16 On Board PCB Antennas

#### 3.8.14 External and on-Board PCB GPS Antenna

The Open-Q 820 / 820Pro µSOM carrier board allows user the flexibility of using an external (via SMA connector) or an on-board PCB GPS antenna. Depending on which antenna is used, dip switch S10 needs to be configured (see table below for details).

| GPS Antenna Selection                                       | Dip Switch S10 (Position 8) Selection |

|-------------------------------------------------------------|---------------------------------------|

| On Board PCB Antenna                                        | Off Position                          |

| External Antenna (Supports Both Active and Passive Antenna) | On Position                           |

If an external GPS antenna is preferred, Intrinsyc recommends the Laird Technologies hepta-band dipole antenna (manufacture part number: MAF94300). It is important to note that GPS should be used or tested near a window or a location where satellites are easily "seen" by the device.

### 3.8.15 Open-Q Display

The display output options for the Open-Q 820 / 820Pro  $\mu$ SOM Development Kit consists of:

- An HDMI type A connector

- HDMI 2.0 (4K60) or 4K30 Miracast

- A 100-pin display connector J2 that supports:

- o Dual DSI DPHY 1.2 (up to 3840 x 2400 at 60 fps)

- Touch screen capacitive panel via I2C or SPI, and interrupts (up to one device)

- Backlight LED

- Can support external backlight driver control and power

- PMI8996 backlight driver supports three LED strings of up to 30mA each with 28V maximum boost voltage

The Open-Q 820 / 820Pro µSOM development platform can support the following display combinations:

| MIPI DSI | 1 x 4lane DSI0 + 1 x 4lane DSI1                                      |  |  |  |  |

|----------|----------------------------------------------------------------------|--|--|--|--|

|          | 1 x 8 lane combining DIS0 and DSI1 for up to 4K resolution           |  |  |  |  |

|          | 2 x 4-lane DSI DPHY 1.2 and HDMI (4K60) or 4K30 Miracast             |  |  |  |  |

|          | Display 3840 x 2400 at 60fps, 2560 buffer width (10 layers blending) |  |  |  |  |

| HDMI     | V2.0 (4K60)                                                          |  |  |  |  |

#### 3.8.16 HDMI Connector J25

Figure 17 HDMI Type A Connector

The on-board HDMI type A connector enables the Open-Q 820 / 820Pro  $\mu$ SOM development platform to connect to an external HDMI monitor/ television via an HDMI cable. As part of a new feature, the APQ8096 / APQ8096SG can now support up to 4K UHD (3840 x 2400 at 60fps) and HDMI 2.0 (4K60)/ 4K30 Miracast.

Please note that the Open-Q 820 / 820Pro  $\mu$ SOM Development kit is for evaluation purposes only and may not be HDMI compliant.

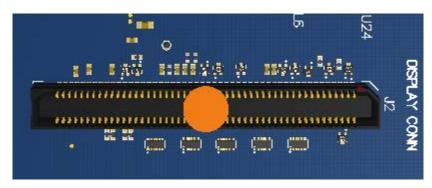

### 3.8.17 Display Connector J2

Figure 18 100-Pin Display Connector

The 100-pin display connector provides the following features/ pin-outs that enables the development kit to connect to a MIPI DSI panel/ device:

Note: Please refer to the carrier schematic and display board tech note when designing a custom display board.

- DSI

- o 2 x 4 lane DSI

- Backlight

- o Built-in backlight WLED driver on PMI8996

- WLED driver supports up to 28.5V output for backlight

- Primary external backlight (BL0)

- Backlight control signals

- External Power

- Display connector LCD/ AMOLED

- PMI8996 programmable display bias output voltage:

- 5V to 6.1V and -1.4V to -6.0V (LCD display)

- 4.6V to 5V and -1.4V to -5.4V (AMOLED display)

- Additional GPIOs for general purposes available

- VREG S4A voltage rail from PM8996

- Required by display for DOVDD

- 300mA current path

- Touch Panel

- Supports one touch screen controller

- Supports I2C or SPI via BLSP12

- o Can chose between I2C or SPI signals in SW U9 via BLSP12

#### Power specifications

The display connector supports the following power domains:

| Display Signal             | Power Domain |

|----------------------------|--------------|

| PM8996 LDO22 (3.3-2.8V)    | up to 150 mA |

| PM8996 LDO14 (1.8V- 2.15V) | up to 150 mA |

| PM8996 LDO15(1.8V – 2.15V) | up to 300 mA |

| PM8996 S4A (1.8V)          | up to 300 mA |

| Carrier 3.3V               | up to 0.5A   |