## IS32LT3957

# HIGH VOLTAGE LED LIGHTING CONTROLLER WITH FAULT PROTECTION

October 2018

#### GENERAL DESCRIPTION

The IS32LT3957 is a current mode PWM controller designed to drive a low side external NMOS FET for wide input/output voltage range and high LED current applications. An external resistor senses the high side output current of the LED string. A high side sense is the most flexible current sensing scheme, since it functions in either boost or buck-boost mode configurations. The controller can be configured with an external resistor to operate between 100kHz~1MHz frequency resulting in small external inductor and capacitors while maintaining high efficiency. A single capacitor is all that is required to set the spread spectrum dither frequency to reduce the radiated peak emission and optimize the system EMI performance.

The IS32LT3957 integrates circuity to detect output open/short, RT/SYNC pin short, VDD short, VCC under voltage lockout and over temperature fault conditions. These failure conditions can be reported by the open drain fault reporting FAULTB pin.

An MCU can be easily interfaced with the IS32LT3957 to perform dimming control and respond to fault report conditions. Dimming can be either analog and/or PWM input. An input DC voltage in the range of 0.1V ~ 1.1V on the ICTRL pin is required for analog dimming. A digital signal with varying duty cycle on the PWM/EN pin will achieve PWM dimming.

The IS32LT3957 is available in an eTSSOP-16 package with an exposed pad for enhanced thermal dissipation. It operates from 5V to 75V over the temperature range of -40°C to +125°C.

#### **FEATURES**

- Wide high voltage input range: 5V to 75V

- Supports boost, buck-boost, SEPIC and buck topology

- ±3.5% output current accuracy over -40°C ~ +125°C temperature

- Adjustable operating frequency range of 100kHz~1MHz

- · Programmable soft start to avoid inrush current

- · Fixed under voltage lockout threshold

- EMI reduction capabilities

- Programmable spread spectrum function

- Operating frequency synchronization with external clock source

- Supports either analog or PWM dimming

- Fault protection with reporting:

- VCC under voltage lockout (not reported)

- Programmable output over voltage protection

- Output short circuit protection

- RT/SYNC pin short protection

- VDD pin short protection

- VDD under voltage lockout (not reported)

- Over temperature protection

- AEC-Q100 Qualified

#### **APPLICATIONS**

- Automotive

- Headlight

- Daytime running light

- Fog light

- Tail light

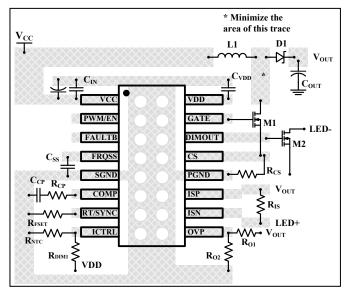

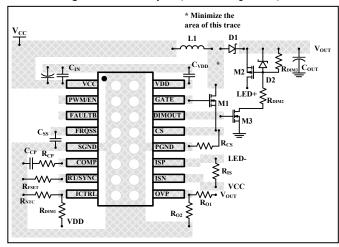

## **TYPICAL APPLICATION CIRCUIT**

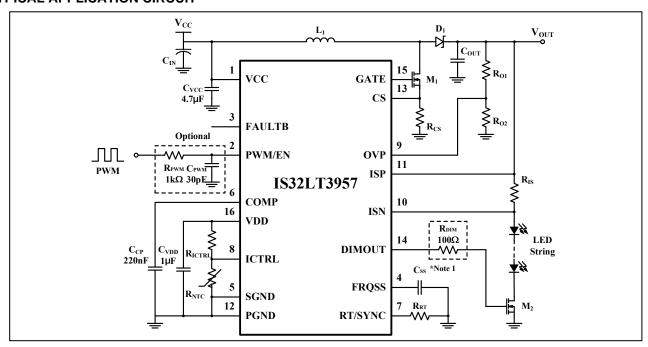

Figure 1 Typical Application Circuit (Boost Configuration)

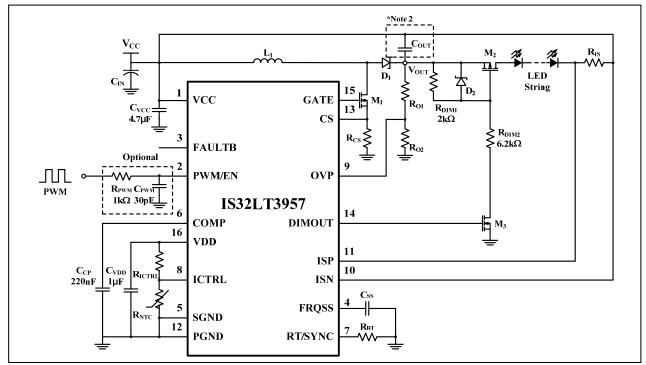

Figure 2 Typical Application Circuit (Buck-Boost Configuration)

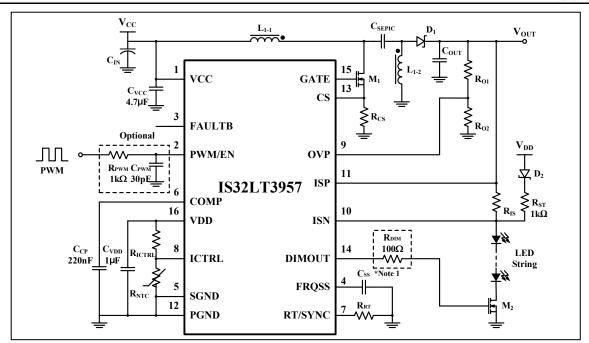

Figure 3 Typical Application Circuit (SEPIC Configuration)

Note 1:  $R_{\text{DIM}}$  is essential for boost and SEPIC configurations; it MUST be a fixed  $100\Omega$ , do not change this value.

Note 2: For buck-boost configuration, C<sub>OUT</sub> MUST be placed close to C<sub>IN</sub>.

Note 3:  $R_{PWM}$  and  $C_{PWM}$  are optional. If PWM dimming is not required, the PWM/EN pin should be tied to VCC or left floating. If PWM dimming is used, this RC filter is recommended and should be placed close to the PWM/EN pin to prevent noise coupling.

## **PIN CONFIGURATION**

| Package   | Pin Configurations (Top View) |  |  |  |  |

|-----------|-------------------------------|--|--|--|--|

| eTSSOP-16 | VCC         1                 |  |  |  |  |

## IS32LT3957

## **PIN DESCRIPTION**

| No. | Pin         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VCC         | The power supply pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2   | PWM/EN      | PWM dimming and enable pin. Internally pulled up to 5V via a $500k\Omega$ resistor. Pull high or leave floating (NC) to enable the IC. Apply an external PWM signal with high level over $V_{IH}$ on this pin to achieve digital dimming. Pulling down below $V_{IL}$ for over $t_{DELAY}$ will force the IC into standby mode.                                                                                                                                            |

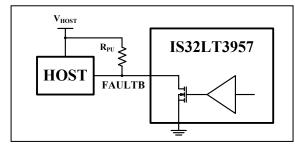

| 3   | FAULTB      | Open drain fault reporting pin. Active low to report a fault condition. Connect a $100 k\Omega$ resistor between this pin and the required logic level voltage.                                                                                                                                                                                                                                                                                                            |

| 4   | FRQSS       | Spread spectrum frequency setting pin. A capacitor from this pin to ground sets the dither frequency. Connect this pin directly to ground to disable this function.                                                                                                                                                                                                                                                                                                        |

| 5   | SGND        | Signal ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6   | COMP        | Error amplifier output for loop regulation. Connect a capacitor to ground to set the soft start speed.                                                                                                                                                                                                                                                                                                                                                                     |

| 7   | RT/SYNC     | An external resistor to ground on this pin sets the operating frequency. This pin can also be used to synchronize two or more IS32LT3957s in the system. Apply an external clock signal to this pin on two or more ICs for frequency synchronization.                                                                                                                                                                                                                      |

| 8   | ICTRL       | Analog dimming voltage input. The analog dimming range is $0.1V\sim1.1V$ . The output is full current when the pin voltage is between $5V>V_{ADIM}>1.1V$ and zero current when $V_{ADIM}<0.1V$ . Analog dimming is achieved when this pin voltage varies between $0.1V It cannot be left floating. Recommend a 10nF X7R type capacitor close to this pin for noise decoupling. When it's connected to VDD, a resistor divider is needed to keep the pin voltage below 5V.$ |

| 9   | OVP         | Over voltage protect. The GATE pin will be pulled low when this pin voltage exceeds $V_{\text{OVP\_TH}}$ (1.34V Typ.). A resistor divider is used for monitoring the output voltage and keeping the pin voltage below $V_{\text{OVP\_TH}}$ .                                                                                                                                                                                                                               |

| 10  | ISN         | The LED current sense amplifier negative input.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11  | ISP         | The LED current sense amplifier positive input.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12  | PGND        | Power ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 13  | CS          | External NMOS switch peak current sense for control loop and over current protection. Connect a resistor from this pin to ground.                                                                                                                                                                                                                                                                                                                                          |

| 14  | DIMOUT      | Buffer of PWM signal for driving LED string disconnect NMOS to achieve better PWM dimming. High voltage level is determined by internal LDO VDD voltage. This pin also serves in the LED string shorted protection function. When $(V_{\text{ISP}}-V_{\text{ISN}})$ exceeds $V_{\text{SENSE\_OC}}$ , this pin will pull to ground to disconnect the circuit. Leave this pin unconnected if not used.                                                                       |

| 15  | GATE        | Gate drive to the external power NMOS. Switches between VDD and GND.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 16  | VDD         | Internal LDO output, needs an external low ESR capacitor (fixed value 1µF) placed close to this pin. This pin is not meant to power any external circuit.                                                                                                                                                                                                                                                                                                                  |

|     | Thermal Pad | MUST be soldered to a large size GND copper plane.                                                                                                                                                                                                                                                                                                                                                                                                                         |

**ORDERING INFORMATION**

Automotive Range: -40°C to +125°C

| Order Part No.                        | Package              | QTY                  |

|---------------------------------------|----------------------|----------------------|

| IS32LT3957-ZLA3-TR<br>IS32LT3957-ZLA3 | eTSSOP-16, Lead-free | 2500/Reel<br>96/Tube |

Copyright © 2018 Lumissil Microsystems. All rights reserved. Lumissil Microsystems reserves the right to make changes to this specification and its products at any time without notice. Lumissil Microsystems assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Lumissil Microsystems does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Lumissil Microsystems receives written assurance to its satisfaction, that:

- a.) the risk of injury or damage has been minimized;

- b.) the user assume all such risks; and

- c.) potential liability of Lumissil Microsystems is adequately protected under the circumstances

## ABSOLUTE MAXIMUM RATINGS

| VCC, PWM/EN, ISP, ISN, FAULTB pins                                                                                    | -0.3V ~ +80V   |

|-----------------------------------------------------------------------------------------------------------------------|----------------|

| GATE, VDD, DIMOUT pins                                                                                                | -0.3V ~ +15V   |

| COMP, RT/SYNC, ICTRL, OVP, CS pins                                                                                    | -0.3V ~ +7V    |

| Operating temperature, T <sub>A</sub> =T <sub>J</sub>                                                                 | -40°C ~ +125°C |

| Maximum operating junction temperature, T <sub>JMAX</sub>                                                             | +150°C         |

| Device storage temperature, T <sub>STG</sub>                                                                          | -65°C ~ +150°C |

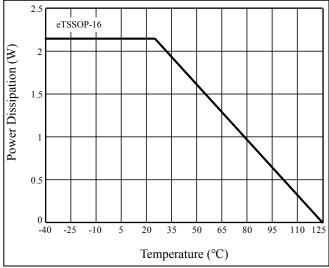

| Maximum power dissipation, P <sub>DMAX</sub>                                                                          | 2.5W           |

| Package thermal resistance, junction to ambient (4 layer standard test PCB based on JESD 51-2A), $\theta_{\text{JA}}$ | 46.4°C/W       |

| Package thermal resistance, junction to thermal PAD (4 layer standard test PCB based on JESD 51-8), $\theta_{\rm JP}$ | 1.617°C/W      |

| ESD (HBM)                                                                                                             | ±2kV           |

| ESD (CDM)                                                                                                             | ±750V          |

Note 4: Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

The specifications are at  $T_J$ = -40°C ~ +125°C,  $V_{CC}$ = 12V, unless otherwise noted. Typical values are at  $T_J$ = 25°C. (Note 5)

| Symbol                 | Parameter                                                           | er Condition           |                                  | Min. | Тур.   | Max. | Unit                   |

|------------------------|---------------------------------------------------------------------|------------------------|----------------------------------|------|--------|------|------------------------|

| V <sub>CC</sub>        | Input voltage range                                                 |                        |                                  | 5    |        | 75   | V                      |

| I <sub>cc</sub>        | Supply current                                                      | V <sub>ICTRL</sub> = 0 | V                                |      | 2      | 3    | mA                     |

| I <sub>STBY</sub>      | Supply current in standby mode                                      | V <sub>PWM/EN</sub> =  | 0V                               |      | 1.2    | 1.5  | mA                     |

| $V_{UVLO_F}$           | Under voltage lock out falling threshold                            |                        |                                  | 3.8  | 4.25   | 4.8  | ٧                      |

| $V_{\text{UVLO}_{R}}$  | Under voltage lock out rising threshold                             |                        |                                  |      |        | 4.98 | V                      |

| V <sub>UVLO_HY</sub>   | Under voltage lock out hysteresis                                   |                        |                                  |      | 250    |      | mV                     |

| $V_{DD}$               | Internal regulator output voltage                                   |                        |                                  | 5.8  | 6.6    | 7.2  | V                      |

| I <sub>MAX_LDO</sub>   | VDD pin maximum drive current                                       | VDD drop               | os to less than 1V               | 20   |        |      | mA                     |

| V <sub>CS_TH</sub>     | Power NMOS current limit threshold                                  |                        |                                  | 160  | 200    | 230  | mV                     |

| \/                     | Output current sense threshold                                      | V <sub>ICTRL</sub> =   | T <sub>J</sub> = 25°C            | 245  | 250    | 255  | mV                     |

| $V_{SENSE}$            | (V <sub>ISP</sub> -V <sub>ISN</sub> )                               | 1.5V                   | T <sub>J</sub> = -40°C~125°C     | 241  | 250    | 259  | IIIV                   |

| Fault Prote            | ction                                                               |                        |                                  |      |        |      |                        |

| $V_{FAULTB\_LOW}$      | FAULTB pull low voltage                                             | Fault con              | idition, sink current            |      | 200    | 400  | mV                     |

| I <sub>FAULTB_LK</sub> | FAULTB pin leakage current                                          |                        | condition, FAULTB<br>d up to 24V |      |        | 1    | μA                     |

| V <sub>SENSE_OC</sub>  | Output over current threshold (V <sub>ISP</sub> -V <sub>ISN</sub> ) | For boost architecture |                                  | 400  | 475    | 550  | mV                     |

| t <sub>SKIP</sub>      | Output over current reset time                                      |                        |                                  |      | 16,000 |      | f <sub>SW</sub> cycles |

| V <sub>OVP_TH</sub>    | Over voltage protection threshold                                   | OVP voltage rising     |                                  | 1.24 | 1.34   | 1.44 | V                      |

| V <sub>OVP_HY</sub>    | Over voltage protection hysteresis                                  |                        |                                  |      | 100    |      | mV                     |

| T <sub>SD</sub>        | Thermal shutdown protection                                         | (Note 6)               |                                  |      | 165    |      | °C                     |

| T <sub>SD_HY</sub>     | Thermal shutdown hysteresis                                         | (Note 6)               |                                  |      | 20     |      | °C                     |

## IS32LT3957

## **ELECTRICAL CHARACTERISTICS (CONTINUE)**

The specifications are at  $T_J$ = -40°C ~ +125°C,  $V_{CC}$ = 12V, unless otherwise noted. Typical value are at  $T_J$ = 25°C. (Note 5)

| Parameter             | Symbol                                                              | Condition                                                                   | Min.     | Тур.   | Max. | Unit                   |

|-----------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------|----------|--------|------|------------------------|

| Gate Driver           |                                                                     |                                                                             | <u> </u> |        |      |                        |

| t <sub>R_GATE</sub>   | GATE pin rise time                                                  | 10%×V <sub>MAX</sub> to 5V,<br>C <sub>GATE</sub> = 3.3nF                    |          | 25     | 60   | ns                     |

| t <sub>F_GATE</sub>   | GATE pin fall time                                                  | 90%×V <sub>MAX</sub> to 10%×V <sub>MAX</sub> ,<br>C <sub>GATE</sub> = 3.3nF |          | 25     | 60   | ns                     |

| t <sub>MIN_ON</sub>   | GATE minimum on time                                                |                                                                             |          | 150    | 230  | ns                     |

| t <sub>R_DIMOUT</sub> | DIMOUT pin rise time                                                | 10%×V <sub>MAX</sub> to 5V,<br>C <sub>DIMOUT</sub> = 1nF                    |          | 200    | 250  | ns                     |

| t <sub>F_DIMOUT</sub> | DIMOUT pin fall time                                                | 90%×V <sub>MAX</sub> to 10%×V <sub>MAX</sub> ,<br>C <sub>DIMOUT</sub> = 1nF |          | 120    | 180  | ns                     |

| Oscillator            |                                                                     |                                                                             |          |        |      |                        |

| $f_{SWR}$             | Operating frequency range                                           |                                                                             | 100      |        | 1000 | kHz                    |

| V <sub>RT/SYNC</sub>  | RT/SYNC pin voltage                                                 |                                                                             |          | 1      |      | V                      |

|                       |                                                                     | $R_{RT}$ = 430k $\Omega$                                                    | 80       | 100    | 110  |                        |

| $f_{SW}$              | Operating frequency                                                 | $R_{RT}$ = 150k $\Omega$                                                    | 220      | 250    | 280  | kHz                    |

|                       |                                                                     | $R_{RT}$ = 33k $\Omega$                                                     | 850      | 1000   | 1150 |                        |

| $D_MAX$               | Maximum operating duty cycle                                        |                                                                             | 88       | 90     |      | %                      |

| $f_{SY}$              | Synchronized PWM frequency                                          |                                                                             | 250      |        | 500  | kHz                    |

| t <sub>SY_OFF</sub>   | Synchronization input minimum off-time                              |                                                                             | 200      |        |      | ns                     |

| t <sub>SY_ON</sub>    | Synchronization input minimum on-time                               |                                                                             | 200      |        |      | ns                     |

| V <sub>SY_H</sub>     | Synchronization input logic high                                    | (Note 6)                                                                    | 2.5      |        |      | V                      |

| V <sub>SY_L</sub>     | Synchronization input logic low                                     | (Note 6)                                                                    |          |        | 0.8  | V                      |

|                       | FRQSS charging current                                              | (Note 6)                                                                    |          | 10     |      |                        |

| I <sub>FRQSS</sub>    | FRQSS discharging current                                           | (Note 6)                                                                    |          | 10     |      | μA                     |

| R <sub>SS</sub>       | Spread spectrum frequency range                                     | (Note 6)                                                                    |          | ±10    |      | %                      |

| Inputs Paraı          | meter                                                               |                                                                             |          |        |      |                        |

| V <sub>IH</sub>       | PWM/EN input logic high                                             |                                                                             | 2.0      |        |      | V                      |

| V <sub>IL</sub>       | PWM/EN input logic low                                              |                                                                             |          |        | 0.8  | V                      |

| t <sub>DELAY</sub>    | The low voltage delay time on PWM/EN pin to enter into standby mode |                                                                             |          | 32,000 |      | f <sub>SW</sub> cycles |

| R <sub>PWM/EN</sub>   | PWM/EN internal pull up resistor                                    |                                                                             |          | 500    |      | kΩ                     |

| $V_{ICTRL}$           | ICTRL analog dimming range                                          | (Note 6)                                                                    | 0.1      |        | 1.1  | V                      |

Note 5: All parts are production tested at  $T_J$  = -40°C ~ +125°C, unless otherwise noted. Other temperature limits are guaranteed by design.

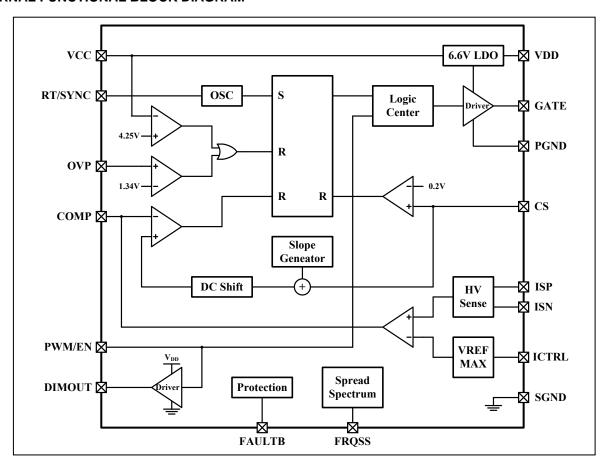

## INTERNAL FUNCTIONAL BLOCK DIAGRAM

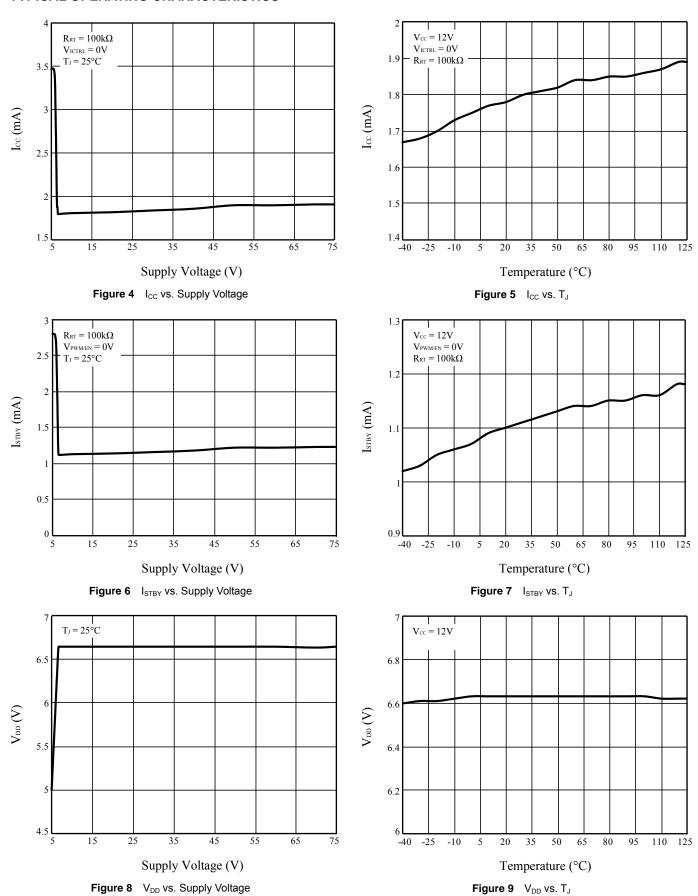

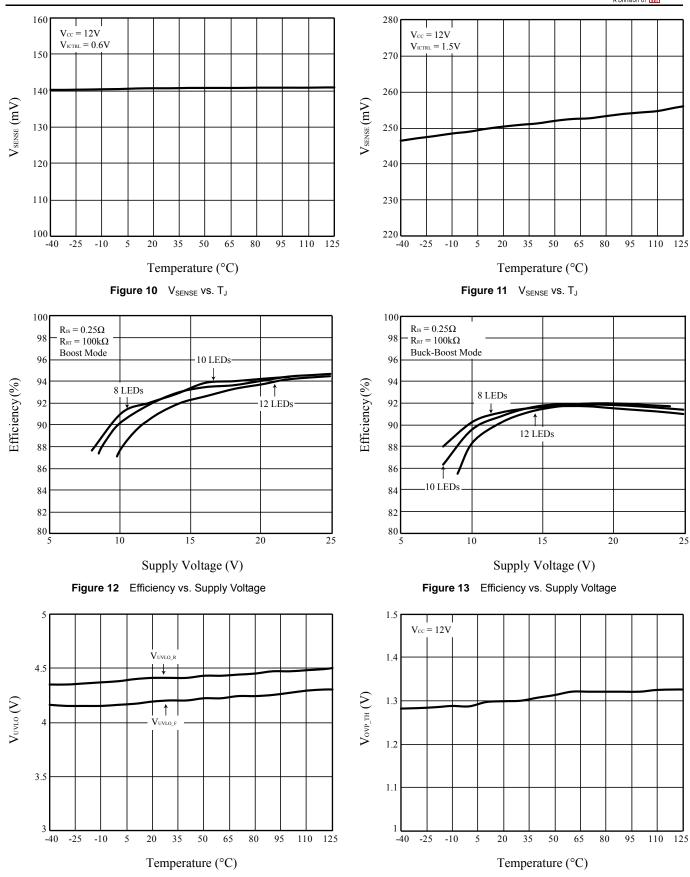

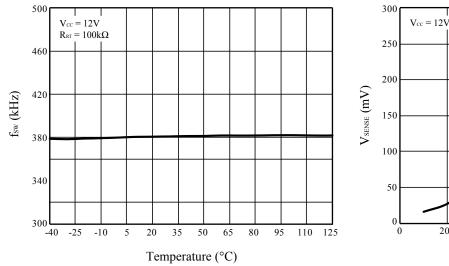

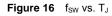

## TYPICAL OPERATING CHARACTERISTICS

Figure 14  $V_{UVLO}$  vs.  $T_J$

Figure 15  $V_{OVP\_TH}$  vs.  $T_J$

## IS32LT3957

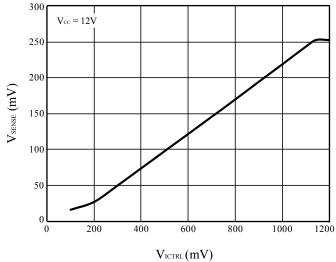

$\textbf{Figure 17} \quad V_{\text{SENSE}} \ vs. \ V_{\text{ICTRL}}$

#### **APPLICATION INFORMATION**

The IS32LT3957 is a constant frequency, current mode PWM controller designed for high current LED applications. The low side gate driver can drive the external NMOS in the 100kHz~1MHz frequency range, which is set by a single resistor connected to RT/SYNC pin. The frequency can be dithered for spread spectrum function by connecting a capacitor from FRQSS pin to GND. The LED current is programmable with one external current sense resistor between ISP and ISN pins. The device supports both analog and PWM dimming methods. The IS32LT3957 is ideal for boost, buck-boost, SEPIC and buck operation.

#### **VCC UVLO**

The device features the under voltage lockout (UVLO) function on VCC pin. It is an internally fixed value of 4.25V and cannot be adjusted. The device is enabled when the VCC voltage rises to exceed  $V_{\text{UVLO}\_R}$ , and disabled when the VCC voltage falls below  $V_{\text{UVLO}}$  F.

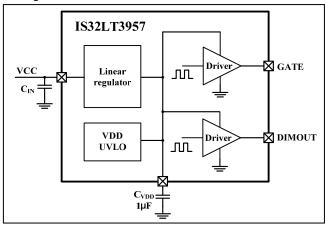

#### LINEAR REGULATOR VDD

The device integrates a linear regulator (VDD) with I<sub>MAX LDO</sub> current capability to power only the GATE and DIMOUT pins and drive the external low side NMOS switches with 6.6V (Typ.). During operation, the external NMOS will draw transient high current from this linear regulator. Therefore, a 1µF low ESR, X7R type ceramic capacitor is necessary from VDD pin to GND; it must be placed as close to VDD pin as possible. VDD is the output of the internal linear regulator and it's not recommended to be driven by an external power supply. This regulator also has the UVLO feature whose voltage threshold is identical with VCC UVLO. When the VDD voltage drops below V<sub>UVLO E</sub>, the GATE and DIMOUT will be turned off and will be turned on once the voltage exceeds V<sub>UVI O R</sub>. This helps protect the external NMOS from excessive power consumption due to insufficient gate driving voltage.

Figure 18 Linear Regulator

An  $I_{\text{MAX\_LDO}}$  current limit on VDD pin protects the IS32LT3957 from excessive power dissipation at high

input voltage. Should the VDD pin be externally pulled below 1.4V, the IS32LT3957 will be disabled and the FAULTB pin will be pulled low to report the fault condition until VDD rises above 1.4V. Most of the VDD current will be supplied to the GATE pin to drive power switching NMOS. The driving current can be calculated from the following Equation (1):

$$I_{GATE} = f_{SW} \times Q_G \tag{1}$$

Where  $f_{SW}$  is operating frequency of IS32LT3957 and  $Q_G$  is the total gate charge of power NMOS.

Choosing a power NMOS with lower  $Q_G$  will improve the efficiency and allow higher switching frequency. It is important to consider the NMOS threshold voltage when operating in the dropout region when the input voltage ( $V_{CC}$ ) is below the VDD regulation level. Recommend a logic level power NMOS with a threshold voltage below 3V when the device is required to operate at an input voltage less than 6V.

VDD can be used to bias external low current circuitry requiring a reference supply, such as in conjunction with the resistor divider to set voltage level for ICTRL pin. However, to ensure stable operation of the IS32LT3957, please do not power any external device with VDD.

#### **SOFT-START**

The IS32LT3957 provides a built-in soft-start function. The function of soft-start is made for suppressing the inrush current to an acceptable value at startup and over voltage protection. During power up, an internal 6µA current source charges the capacitor (220nF Typ.) on the COMP pin causing the COMP pin voltage to gradually ramp up. The current through the external power NMOS depends on the COMP pin voltage, hence, the input peak current gradually ramps up following COMP pin voltage to the regulated level. The soft-start time can be roughly calculated by Equation (2):

$$t_{ss} = \frac{C_{cP} \times 1V}{6\mu A} \tag{2}$$

The  $C_{\text{CP}}$  is the capacitor connected to COMP pin, whose value is in Farad.

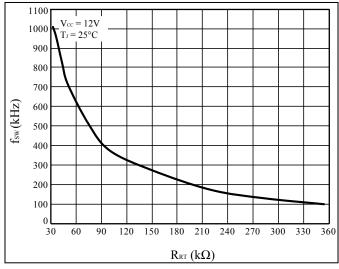

#### **OPERATION FREQUENCY**

The internal oscillator of the device is programmable from 100kHz to 1MHz range using a single resistor  $R_{\rm RT}$  at RT/SYNC pin. Higher frequency operation results in smaller component size but increases the switching losses and power NMOS gate driving current, and may not allow sufficiently high or low duty cycle. Lower frequency gives better performance but results in larger component size. To set a desired frequency, the resistor value can be calculated by following Equation (3):

$$R_{RT} = \frac{37.5 \times 10^9}{f_{sw}}$$

(3)

Where  $R_{\text{RT}}$  is in ohm.  $f_{\text{SW}}$  is the operating frequency in Hertz.

If the RT/SYNC pin is connected to an extremely low value resistor or accidently shorted to ground, the internal oscillation frequency will be over 1MHz. If it exceeds 2.5MHz, the internal circuit will detect it and turn off the power NMOS for protection. When this fault condition is removed so the frequency drops below 2.5MHz, the operation will recovery.

Figure 19 f<sub>SW</sub> vs. R<sub>RT</sub>

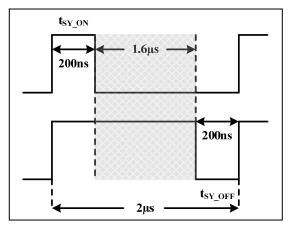

#### FREQUENCY SYNCHRONIZATION

The RT/SYNC pin can also be used as a synchronization input, allowing the IS32LT3957 to operate with an external clock in the range of 250kHz to 500kHz as long as it satisfies the requirements of t<sub>SY ON</sub> and t<sub>SY OFF</sub>. When an external synchronization clock is applied to the RT/SYNC pin, the internal oscillator is over-driven so that each switching cycle begins at the rising edge of external clock. The IS32LT3957 will not be enabled if the RT/SYNC pin is held low during power-up. The IS32LT3957 will start up only when the RT/SYNC pin is tri-stated and allowed to rise to about 1V, or when a synchronization clock is detected, Figure 20 shows the timing for a synchronization clock into the IS32LT3957 at 500kHz. Any pulse with a duty cycle of 10% to 90% at 500kHz can be used to synchronize the IC.

Table 1 Synchronization Duty Cycle Range

| SYNC Clock Frequency(kHz) | Duty Cycle Range (%) |

|---------------------------|----------------------|

| 500                       | 10 ~ 90              |

| 400                       | 8 ~ 92               |

| 300                       | 6 ~ 94               |

| 250                       | 5 ~ 95               |

Figure 20 SYNC Pulse On And Off Time Requirements

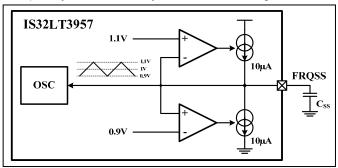

#### SPREAD SPECTRUM

A switch mode controller can be particularly troublesome in applications where EMI is of concern. To optimize EMI performance, the IS32LT3957 includes a spread spectrum feature. The spread spectrum can spread the total electromagnetic emitting energy into a wider range to significantly degrade the peak EMI energy. With spread spectrum, the EMI test can pass with smaller size and lower cost filter circuit.

When a capacitor is connected to FRQSS pin, a triangle waveform is internally generated to modulate the internal oscillator in 90% to 110% of the base frequency which is set by  $R_{RT}$  resistor as Figure 21.

Figure 21 Spread Spectrum Operation

To set the desired modulation frequency, the  $C_{\text{SS}}$  capacitor can be calculated by the following Equation (4):

$$C_{SS} = \frac{10\mu A}{2 \times f_{SS} \times 0.2V} \tag{4}$$

The  $C_{SS}$  is in Farad.  $f_{SS}$  is the modulation frequency in Hertz. A 500Hz frequency is a good starting point to optimize EMI performance. Further adjust this frequency in the actual system to get best EMI performance. Connect FRQSS pin to GND to disable the spread spectrum function.

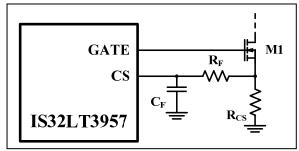

#### **POWER NMOS CURRENT SENSE**

CS is part of the current mode control loop. Connect a resistor  $R_{\text{CS}}$  from the CS pin to ground to regulate the internal oscillator duty cycle and power the NMOS

peak current and achieve input cycle-by-cycle peak current limit protection. In order to provide sufficient current to the external power NMOS for driving the load and prevent this current from exceeding current limit protection, the  $R_{\text{CS}}$  value should be set to a proper level.

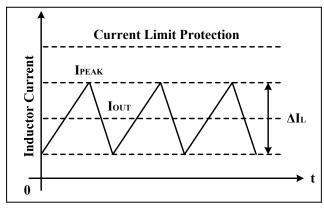

The inductor peak current (I<sub>PEAK</sub>) during normal operation is given by Equation (5):

$$I_{PEAK} = I_L + \frac{\Delta I_L}{2} \tag{5}$$

Where  $I_L$  is the inductor average current in amp.  $\Delta I_L$  is the current ripple of the inductor in amp.

To ensure a reasonable output current ripple and better operating stability, choose  $\Delta I_L$  as follows range:

$$20\% \times I_L \le \Delta I_L \le 100\% \times I_L \tag{6}$$

Figure 22 Inductor Current

The inductor ripple current  $\Delta I_L$  involves trade-offs in performance. Lower  $\Delta I_L$  requires a larger value and bigger size inductor that which will dissipate more power, however it also reduces the peak current in the external power NMOS and the recirculating diode that derate the power dissipation on them.

For boost application, the  $I_L$  is equal to the input average current, so

$$I_{PEAK\_BOOST} = \frac{V_{LED} \times I_{LED}}{\eta \times V_{CC}} + \frac{\Delta I_L}{2}$$

(7)

For buck-boost and SEPIC applications, the  $I_L$  is equal to the input average current plus LED average current, so

$$I_{PEAK\_BUCK-BOOST} = \frac{\left(V_{LED} + V_{CC}\right) \times I_{LED}}{\eta \times V_{CC}} + \frac{\Delta I_L}{2}$$

(8)

Where  $\eta$  is the assumed circuitry efficiency, choose 0.9 for it.  $V_{CC}$  uses the minimum input voltage in volts,  $V_{LED}$  is the maximum total forward voltage of LED string in volts.  $I_{LED}$  is the output LED current in amps.

The current limit protection should be at least 50% greater than the inductor peak current  $I_{\text{PEAK}}$ . The

current sense resistor  $R_{CS}$  is calculated by the following Equation (9):

$$R_{CS} = \frac{V_{CS\_TH}}{1.5 \times I_{PEAK}} \tag{9}$$

Recommend use of ±1% precision type resistor for best accuracy.

The current limit protection is cycle-by-cycle detection. Once the CS pin voltage exceeds the current limit threshold,  $V_{\text{CS\_TH}}$ , the GATE immediately pulls low to turn off the power NMOS until the next switching cycle. The current sense resistor should be placed as close as possible to IS32LT3957 device to ensure stable operation.

Figure 23 CS Filter

An internal blanking circuit prevents power NMOS switching current spike propagation and premature termination of duty cycle by internally shunting the CS input for 150ns after the beginning of the new switching period. For further noise suppression, the use of low pass RC filter on CS pin can be considered. The recommended value of  $R_{\text{F}}$  and  $C_{\text{F}}$  are  $100\Omega$  and 10pF.

#### **INDUCTOR**

Inductor value involves trade-offs in performance. Larger inductance reduces inductor current ripple resulting in smaller output current ripple, however it also brings in unwanted parasitic resistance that degrades performance. Select an inductor with a rating current greater than the input average current and a saturation current greater than the power NMOS current limit set by  $R_{\rm CS}.$  Use the following equations to estimate the approximate inductor value:

For boost application:

$$L_{\text{\tiny BOOST}} = \frac{V_{\text{\tiny CC}} \times (V_{\text{\tiny LED}} - V_{\text{\tiny CC}})}{f_{\text{\tiny SW}} \times \Delta I_{\text{\tiny L}} \times V_{\text{\tiny LED}}}$$

(10)

For buck-boost and SEPIC application:

$$L_{BUCK-BOOST} = \frac{V_{CC} \times V_{LED}}{f_{SW} \times \Delta I_L \times (V_{LED} + V_{CC})}$$

(11)

Where  $V_{\text{CC}}$  uses the minimum input voltage in volts,  $V_{\text{LED}}$  is the maximum total forward voltage of LED string in volts,  $f_{\text{SW}}$  is the operation frequency in hertz. If

the SEPIC inductor is coupled, the equation's result can be used as is. If the SEPIC uses two uncoupled inductors, then each should have an inductance double the result of the equation.

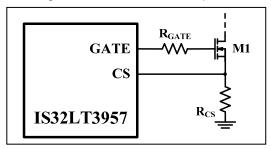

#### **POWER NMOS**

A power NMOS must be chosen with its drain voltage rating V<sub>DS MAX</sub> greater than the over voltage protection voltage (V<sub>OVP</sub>) together with overshoot voltage due to the ringing caused by parasitic inductances and capacitances, therefore keeping 20% safety margin voltage over V<sub>OVP</sub> is necessary.

For boost and buck-boost:

$$V_{DS-MAX} \ge 1.2 \times V_{OVP} \tag{12}$$

For SEPIC:

$$V_{DS-MAX} \ge 1.2 \times (V_{OVP} + V_{IN})$$

(13)

The gate drive current is sourced from the VDD pin whose current capability is limited to protect the device from excessive power dissipation at high input voltage. So low gate charge Q<sub>G</sub> at 7V should be carefully considered (refer to Equation (1)). The consideration of the R<sub>DS(ON)</sub> of power NMOS is usually secondary because the switching loss dominates the power lost, especially at high operating frequency. A power NMOS with lower Q<sub>G</sub> and R<sub>DS(ON)</sub> achieves higher efficiency and lower power losses. The continuous current rating of the selected power NMOS should be higher than the input average current and the maximum current rating should be higher than the current limit protection level.

Figure 24 GATE Buffer Resistor

A buffer resistor can be considered to be added in series with the gate driving that slows down the switching rising and falling edge to minimize EMI. However, it increases the switching loss and degrades the efficiency at the same time. So the value should not be too large; several ten ohm is a good starting point. Please choose a proper value based on the EMI test result.

#### **RECIRCULATING DIODE**

The diode conducts the current during the interval when the power NMOS is turned off. To achieve high efficiency choose a Schottky diode with low forward voltage and fast switching speed. Ensure that the diode's continuous current rating exceeds the output LED current and peak current rating exceeds the

current limit protection level. The diode's reverse breakdown voltage, V<sub>BD</sub>, must be higher than the over voltage protection voltage (V<sub>OVP</sub>) and keep a 20% safety margin.

$$V_{RD} \ge 1.2 \times V_{OVP} \tag{14}$$

The leakage current of the diode is also a critical feature to consider, which increases with the temperature. High leakage current will degrade the efficiency and PWM dimming performance.

#### INPUT CAPACITOR

The input capacitor provides the transient current to the inductor of the converter. An X7R type ceramic capacitor is a good choice for the input bypass capacitor to handle the ripple current since it has a very low equivalent series resistance (ESR) and low equivalent series inductance (ESL) capacitor and good temperature performance. Use the following equation to estimate the approximate capacitance:

For boost application:

$$C_{\scriptscriptstyle IN} \ge \frac{\Delta I_{\scriptscriptstyle L}}{8 \times V_{\scriptscriptstyle DRIME} \times f_{\scriptscriptstyle SW}} \tag{15}$$

For buck-boost and SEPIC application:

$$C_{_{IN}} \ge \frac{I_{_{LED}} \times V_{_{LED}}}{V_{_{RIPPLE}} \times f_{_{SW}} \times (V_{_{LED}} + V_{_{CC}})}$$

(16)

Where, VRIPPLE is the acceptable input voltage ripple in volts. C<sub>IN</sub> is in farads. This input capacitor must be placed close to the IS32LT3957 and the inductor to reduce the ripple. A higher value input capacitor is good for minimizing the input voltage deviation due to the large transient current. An aluminum electrolytic capacitor is recommended to be used in parallel with ceramic capacitors.

#### **OUTPUT CAPACITOR**

The output capacitor is used to filter the LED current ripple to an acceptable level. The equivalent series resistance (ESR), equivalent series inductance (ESL) and capacitance of the capacitor contribute to the output current ripple. Therefore, a low-ESR X7R type ceramic capacitor should be used. Use the following equation to estimate the approximate capacitance:

For boost application:

$$C_{OUT} \ge \frac{I_{LED} \times 2 \times (V_{LED} - V_{CC})}{V_{DEDUC} \times f_{SW} \times V_{LED}}$$

(17)

For buck-boost and SEPIC application:

$$C_{OUT} \ge \frac{I_{LED} \times 2 \times V_{LED}}{V_{RIPPLE} \times f_{SW} \times (V_{LED} + V_{CC})}$$

(18)

Where, V<sub>RIPPLE</sub> is the acceptable output voltage ripple

in volts. C<sub>OUT</sub> is in farads. Based on the above equations. the higher operating frequency proportionally decreases the required output capacitor value which results in smaller capacitor size. The output ceramic capacitor should be placed close to the cathode of D1 for a better filter effect. An aluminum electrolytic capacitor can be used in parallel with the ceramic capacitors to provide bulk energy storage.

#### LED CURRENT CONTROL

The IS32LT3957 regulates the LED current by the external resistor, RIS, in series with LED string and connecting to ISP and ISN. The internal current sense voltage threshold V<sub>SENSE</sub>, which is equal to V<sub>ISP</sub>-V<sub>ISN</sub>, is 0.25V (Typ.). To get best output accuracy, sensing of the output current should be done on the top of the LED string. When the PWM/EN pin is tied to a DC voltage higher than 2.0V and ICTRL voltage is above 1.1V, will result in a full-scale current sense voltage threshold and the LED current can be calculated from Equation (19).

$$I_{LED} = \frac{V_{SENSE}}{R_{IS}}$$

(19)

In order to have an accurate LED current, precision resistors are preferred (±1% recommended). The RIS resistor should be placed as close as possible to the IS32LT3957 device with minimal trace length.

#### **DIMMING CONTROL**

IS32LT3957 can modulate the brightness of LEDs by controlling the PWM signal to the PWM/EN pin or the DC voltage on ICTRL pin.

#### **PWM DIMMING AND ENABLING**

IS32LT3957 offers a PWM/EN pin for pulse-width modulating of the output current.

The DIMOUT pin is a buffered output following the dimming signal on the PWM/EN pin which drives the gate of the dimming MOSFET. When the PWM/EN signal voltage is greater than logic high threshold V<sub>IH</sub>, the device is enabled and the dimming MOSFET is turned on. When the PWM voltage is lower than the logic low threshold V<sub>IL</sub>, the device is disabled and the dimming MOSFET is turned off. The LED string is dimmed by modulating the duty cycle of PWM signal to vary the LED average current. Apply a low PWM signal frequency with a higher device switching frequency will result in best dimming performance.

An external MOSFET driven by the DIMOUT pin (refer to Figure 1 and 2) is recommended for a precise PWM dimming function. The dimming MOSFET will disconnect the LED string during PWM low to prevent the V<sub>OUT</sub> node from discharging which will minimize the recovery time when the PWM goes back high. This shorter recovery time results in better dimming linearity and stable loop regulation during low PWM duty cycles. Both are critical for ensuring control loop regulation

during steady-state operation and to minimize LED current overshoot once PWM returns to high level.

Pulling the PWM/EN pin low for longer than 32,000 switching cycles  $(t_{DELAY})$  will force the device into standby mode. There is a soft start when the PWM/EN is pulled high to enable the device after disabling.

Table 2 PWN/EN Disable Time

| Operating Frequency(kHz) | t <sub>DELAY</sub> (ms) |

|--------------------------|-------------------------|

| 1000                     | 32                      |

| 600                      | 53                      |

| 400                      | 80                      |

| 250                      | 128                     |

| 100                      | 320                     |

An RC filter (1k $\Omega$  resistor and 30pF capacitor) in series with the PWM/EN input is recommended to avoid noise coupling during PWM dimming operation. The PWM/EN pin is internally pulled up to 5V via a  $500k\Omega$ resistor. If PWM dimming is not used, the PWM/EN pin can be either left floating or tied to VCC.

#### **DIMMING MOSFET**

A dimming NMOS (M2) in series with the LED string is essential for PWM dimming application while in boost mode (refer to Figure 1). The NMOS voltage rating should be as high as the power switching NMOS and its maximum continuous current rating should be higher than the maximum LED string current. Choose an NMOS with low total gate charge (Qq) for high frequency turn on and off time to best PWM dimming contrast ratio. Another important NMOS selection parameter is low R<sub>DS(ON)</sub> for high operating efficiency and low power losses. If PWM dimming is not implemented, the dimming NMOS can be removed, the DIMOUT pin left floating and the LED cathode connected directly to GND. However, please note the LED short protection feature will not be functional. Therefore it's recommended to use a dimming NMOS for most applications.

In buck-boost mode (refer to Figure 2), an additional PMOS (M2), zener (D2), and resistors (R<sub>DIM2</sub>, R<sub>DIM3</sub>) are needed as a level shift to disconnect the output during PWM dimming operation. When the NMOS connected to the DIMOUT pin turns on, the R<sub>DIM2</sub> resistor will pull low the PMOS gate to turn it on. When the dimming NMOS turns off, R<sub>DIM1</sub> resistor will pull high the PMOS gate to turn it off. A 7V zener diode (D2) is needed to clamp the  $V_{\text{SG}}$  voltage and protect the PMOS. The PMOS selection should follow the same guideline as the dimming NMOS regarding voltage and current ratings in boost mode. However, the dimming NMOS (M3) in buck-boost mode can be a signal transistor which can be low current capability but the voltage rating should be the same as the power NMOS. If PWM dimming is not implemented, both dimming

PMOS and NMOS can be removed with the DIMOUT pin left floating and LED anode connected directly to  $V_{OUT}$ . The recommended value of  $R_{DIM1}$  and  $R_{DIM2}$  are  $2k\Omega$  and  $6.2k\Omega.$  Too large value of  $R_{\text{DIM1}}$  and  $R_{\text{DIM2}}$  slows down the turn on/off speed of the M2 that degrades the PWM dimming performance. While too low value discharges the output capacitor more quickly that extends the recovery time when the PWM goes back high and degrades the efficiency.

#### ANALOG DIMMING

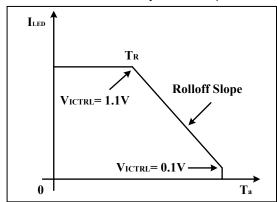

The IS32LT3957 also offers an analog dimming input pin, ICTRL, whose dimming voltage range is 0.1V to 1.1V. The current sense voltage threshold, V<sub>SENSE</sub>, can be regulated by the ICTRL pin voltage. If the ICTRL pin is pulled up above 1.1V, analog dimming is disabled and the output current is given by Equation (19). When the ICTRL voltage is driven below 1.1V, V<sub>ICTRL</sub> will proportionally control the current sense voltage threshold V<sub>SENSE</sub> resulting in a change in the output current as given by Equation (20):

$$I_{LED} = \frac{V_{ICTRL} - 0.1}{1V} \times \frac{V_{SENSE}}{R_{IS}}$$

(20)

The output LED voltage will decrease when the output current decreases. Therefore, it must ensure the output voltage always higher than the input voltage during the dimming in the boost configuration.

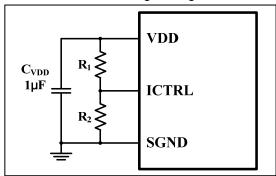

Never leave the ICTRL pin floating. If the analog dimming function is not implemented, connect the ICTRL pin to a voltage level higher than 1.1V and lower than 5V. This voltage can be created with a resistor divider (R1, R2) from the VDD pin. The ICTRL pin cannot be connected directly to the VDD pin because the linear regulator VDD voltage (6.6V) exceeds the maximum voltage rating of the ICTRL pin.

Figure 25 Analog Dimming Unused

The ICTRL can be used to dim the output current to zero, although the relative current accuracy decreases with the decreasing current sense voltage threshold due to the offset of the internal circuit. When the ICTRL voltage is below 0.1V, the output will be turned off. It is recommended to add a 10nF ceramic capacitor from the ICTRL pin to GND to bypass any high frequency noise, especially if the analog voltage level comes from a long copper trace. This 10nF capacitor should

be placed as close to the ICTRL pin as possible.

The ICTRL pin can be used to fine tune the output current during mass-production. LEDs are typically sorted into various bins of different luminous intensity and forward voltage. To correct the brightness deviation during mass-production, the mean output current can be adjusted by adjusting the voltage level on the ICTRL pin. As shown in Figure 25, fix the R2 value and vary the R<sub>1</sub> value to adjust and maintain the same lumen output across different LED bins.

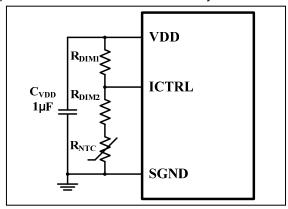

The ICTRL pin can also be used in conjunction with a NTC thermistor to provide over temperature current roll off protection for the LED load or the system.

Figure 26 ICTRL Pin with Thermistor for Roll Off Protection

For example, assume the desired current roll off temperature threshold is T<sub>R</sub> and the NTC thermistor resistance is R<sub>NTCR</sub> at this temperature (R<sub>NTCR</sub> can be found in the NTC thermistor datasheet), then R<sub>DIM1</sub> and R<sub>DIM2</sub> can be calculated by:

$$R_{DIM1} = \frac{(R_{NTCR} + R_{DIM2}) \times (V_{DD} - 1.1V)}{1.1V}$$

(21)

For a given NTC thermistor, the R<sub>DIM1</sub> resistor will adjust the current roll off temperature threshold. The larger R<sub>DIM1</sub> the lower current roll off temperature threshold. The R<sub>DIM2</sub> resistor is optional to be used to adjust current derating slope. The larger R<sub>DIM2</sub> the flatter the current derating slope. If R<sub>DIM2</sub> is not used, tie the NTC thermistor directly to ICTRL pin.

Figure 27 Roll Off Protection

## SETTING THE OVER VOLTAGE PROTECTION

The open LED string protection is achieved using over voltage protection (OVP). In some cases, when the output voltage reaches the programmed OVP voltage ( $V_{\text{OVP}}$ ), the GATE and DIMOUT pins are immediately pulled low and the FAULTB pin is also pulled low to report the fault condition. They remain low until the output voltage drops below the hysteresis voltage. To make sure the chip functions properly, the resistor divider ( $R_{\text{O1}}$ ,  $R_{\text{O2}}$ ) at the OVP pin must be set to 1.2x greater than the output voltage,  $V_{\text{OUT}}$ . For boost and SEPIC applications,  $V_{\text{OUT}}$  is equal to the LED string voltage. For buck-boost applications,  $V_{\text{OUT}}$  is equal to the input voltage ( $V_{\text{CC}}$ ) plus the LED string voltage.

The OVP voltage is calculated using Equation (22).

$$V_{OVP} = \frac{V_{OVP\_TH} \times (R_{O1} + R_{O2})}{R_{O2}} \ge 1.2 \times V_{OUT}$$

(22)

It is recommend to connect a 1nF ceramic capacitor from the OVP pin to GND to avoid unexpected noise coupling into this pin.

Note, the OVP voltage should not be set much higher than  $V_{\text{OUT}}$ , otherwise the power NMOS, the dimming MOS, the recirculating diode and the output capacitor would require higher voltage ratings.

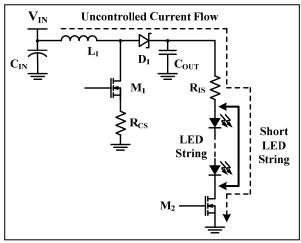

#### SHORT CIRCUIT PROTECTION

In a boost configuration, the short circuit (LED string) protection is implemented by the  $R_{\rm IS}$  over current detection. The ISP and ISN pins have an output over current threshold ( $V_{\rm SENSE\_OC}$ ), which is higher than output current sense threshold ( $V_{\rm SENSE}$ ). If the LED string is shorted the total forward voltage ( $V_{\rm F}$ ) will be lower than the input voltage ( $V_{\rm CC}$ ), resulting in a current path from  $V_{\rm CC}$  through the inductor, recirculating diode,  $R_{\rm IS}$  and power NMOS (M2) to ground. If this fault occurs, the uncontrolled current of this path will rise rapidly. If there is no dimming MOS to disconnect this current path, the huge current may damage the components as well as the power source.

Figure 28 Boost Short LED String

With a dimming MOS, once the uncontrolled current results in the  $R_{\rm IS}$  voltage reaching the threshold  $V_{\rm SENSE\_OC}$  over a delay time (about 2  $f_{\rm SW}$  cycles), the hiccup timer is started and the DIMOUT pin will pull low the gate of dimming MOS M2 for  $t_{\rm SKIP}.$  When the timing is complete, the converter attempts to restart. If the fault condition still persists, the converter shuts down and goes through the cycle again. This on/off cycling of the uncontrolled current flow will result in a low average value. If the fault condition is cleared (due to a momentary output short) the converter will start regulating the output current normally. This prevents the circuitry and power supply from being damaged by an unwanted huge current.

In buck-boost and SEPIC configuration, when the LED string is shorted, there is no uncontrolled current path because in boost configuration the output current remains under control loop regulation. Therefore, an LED short circuit will not cause component damage.

#### THERMAL SHUTDOWN PROTECTION

To protect the IS32LT3957 from damage due to high power dissipation, the temperature of the die is monitored. If the die temperature exceeds the thermal shutdown temperature of 165°C (Typ.) the device will enter standby mode, and the FAULTB pin will be pulled low to report the fault. After a thermal shutdown event, the IS32LT3957 will not try to restart until its die temperature has reduced to less than 145°C (Typ.).

## **FAULT DETECTION AND REPORTING**

For added system reliability, the IS32LT3957 integrates various fault detection and protection circuitry for LED string open/short circuit, VCC and VDD UVLO, power NMOS over current, RT/SYNC and VDD pins short circuit and over temperature conditions. The open drain pin FAULTB can be used as a fault condition flag. When it's monitored by a host, a pull up resistor from the FAULTB pin to the supply of the host is needed. It is pulled low to report the fault conditions. Table 3 briefly describes the typical protection trigger conditions and device behavior.

Figure 29 Host Monitors The Fault Reporting

The ideal value for the FAULTB  $R_{PU}$  range needs to take into account the number of IS32LT3957 devices connected to the same host. The resulting  $R_{PU}$  voltage level should not interfere with the  $V_{IH\_HOST}$  and  $V_{IL\_HOST}$  detection levels of the host. For no-fault detected operation, the sum of the leakage current(s) for the open drain (if more than one device interconnected)

multiplied with the value of  $R_{PU}$  must be greater than  $V_{IH\_HOST}$ . For fault detected operation, the pull down voltage must be below  $V_{IL\_HOST}$ . Then

$$R_{PU\_MAX} = \frac{V_{HOST} - V_{IH\_HOST}}{N \times I_{FAULTB\ LK}}$$

(23)

$$R_{PU\_MIN} = \frac{(V_{HOST} - V_{IL\_HOST}) \times V_{FAULTB\_LOW}}{N \times V_{IL\_HOST} \times I_{OL}}$$

(24)

Where N is the number of IS32LT3957 devices connected to the same host.  $I_{OL}$  is the test condition of FAULTB pin pull down capability. It can be found in the EC table.

**Table 3 Fault Actions**

| Fault Type                       | Fault Condition                         | Device Operation After Fault                                                                                 | FAULTB Pin        | Fault Reset                                      |

|----------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------|

| VCC UVLO                         | V <sub>CC</sub> <v<sub>UVLO_F</v<sub>   | GATE and DIMOUT pull low immediately. IC enters into standby mode and COMP resets to zero.                   | High<br>Impedance | V <sub>CC</sub> >V <sub>UVLO_R</sub>             |

| VDD UVLO                         | V <sub>CC</sub> <v<sub>UVLO_F</v<sub>   | GATE pulls low immediately. IC enters into standby mode and COMP resets to zero.                             | High<br>Impedance | V <sub>CC</sub> >V <sub>UVLO_R</sub>             |

| VDD Pin Short                    | After startup and V <sub>DD</sub> <1.4V | GATE pulls low immediately. IC enters into standby mode and COMP resets to zero.                             | Pull Low          | V <sub>DD</sub> >1.4V                            |

| Over Voltage<br>(LED Open)       | V <sub>OUT</sub> ≥V <sub>OVP</sub>      | GATE pulls low immediately. IC enters into standby mode and COMP resets to zero.                             | Pull Low          | V <sub>OUT</sub> <(V <sub>OVP</sub> -Hysteresis) |

| Power NMOS<br>Current Limit      | V <sub>CS</sub> >V <sub>CS_TH</sub>     | GATE pulls low immediately until the next switching cycle.                                                   | High<br>Impedance | V <sub>CS</sub> <v<sub>CS_TH</v<sub>             |

| LED String Short<br>(Boost Only) | (Visp-Visn)>Vsense_oc                   | GATE and DIMOUT pull low immediately and COMP resets to zero. And retry after 16,000 $f_{\text{SW}}$ cycles. | Pull Low          | (VISP-VISN) <vsense_oc< td=""></vsense_oc<>      |

| RT/SYNC Pin<br>Short             | f <sub>SW</sub> >2.5MHz                 | GATE pulls low immediately.                                                                                  | Pull Low          | f <sub>SW</sub> <2.5MHz                          |

| Thermal<br>Shutdown              | T <sub>J</sub> >165°C                   | GATE pulls low immediately. IC enters into standby mode and COMP resets to zero.                             | Pull Low          | Tյ<145°C                                         |

#### PCB LAYOUT CONSIDERATION

As for all switching power supplies, especially those providing high current and using high switching frequencies, layout is an important design step. If layout is not carefully done, the operation could show instability as well as EMI problems.

The high dV/dt surface and dI/dt loops are big noise emission source. To optimize the EMI performance, keep the area size of all high switching frequency points with high voltage compact. Meantime, keep all traces carrying high current as short as possible to minimize the loops.

Please design the PCB layout according to following considerations.

- (1) Wide and short traces should be used for connection of the high current paths that helps to achieve better efficiency and EMI performance. Such as the traces of power supply, inductor L1, power NMOS M1, recirculating diode D1, LED load, ground.

- (2) Keep the traces of the switching points shorter. The inductor L1, power MOSFET M1 and current recirculating diode D1 should be placed as close to each other as possible and the traces of

connection between them should be as short and wide as possible.

- (3) To avoid the ground jitter, the components of parameter setting, especially the R<sub>IS</sub>, R<sub>CS</sub>, R<sub>RT</sub>, R<sub>O2</sub>, C<sub>CP</sub> should be placed close to the device and keep the traces length to the device pins as short as possible. On the other side, to prevent the noise coupling, the traces of these components should either be far away or be isolated from high-current paths and high-speed switching nodes. These practices are essential for better accuracy and stability.

- (4) The capacitor  $C_{VCC}$  and  $C_{VDD}$  should be placed as close as possible to VCC and VDD pin for good filtering.

- (5) For the boost application, the output capacitor  $C_{\text{OUT}}$  must be placed close to the cathode of D1. For the buck-boost application, the  $C_{\text{OUT}}$  must be placed close to both of the anode of  $C_{\text{IN}}$  and the cathode of D1, otherwise the output current performance will be degraded.

- (6) All thermal pads on the back of IS32LT3957, the recirculating diode and the power NMOS package must be soldered to a sufficient size of copper plane with sufficient vias to conduct the heat to

opposite side PCB for adequate cooling.

#### THERMAL CONSIDERATIONS

The package thermal resistance,  $\theta_{JA}$ , determines the amount of heat that can pass from the silicon die to the surrounding ambient environment. The  $\theta_{JA}$  is a measure of the temperature rise created by power dissipation and is usually measured in degree Celsius per watt (°C/W). The junction temperature,  $T_{J}$ , can be calculated by the rise of the silicon temperature,  $\Delta T$ , the power dissipation, PD, and the package thermal resistance,  $\theta_{JA}$ , as in Equation (25):

$$P_{D} = V_{CC} \times (I_{CC} + f_{SW} \times Q_{G})$$

(25)

and,

$$T_{J} = T_{A} + \Delta T = T_{A} + P_{D} \times \theta_{JA}$$

(26)

Where  $f_{\text{SW}}$  is operation frequency and  $Q_{\text{G}}$  is the total gate charge of power NMOS.

When operating the chip at high ambient temperatures, or when driving maximum load current, care must be taken to avoid exceeding the package power dissipation limits. The maximum power dissipation can be calculated using the following Equation (27):

$$P_{D(MAX)} = \frac{125^{\circ}C - 25^{\circ}C}{\theta_{M}}$$

(27)

So,

$$P_{D(MAX)} = \frac{125^{\circ}C - 25^{\circ}C}{46.4^{\circ}C/W} = 2.16W$$

(28)

for eTSSOP-16 package.

Figure 30, shows the power derating of the IS32LT3957 on a JEDEC boards (in accordance with JESD 51-5 and JESD 51-7) standing in still air.

Figure 30 Dissipation Curve (eTSSOP-16)

Figure 31 PCB Layout (Boost Configuration)

Figure 32 PCB Layout (Buck-Boost Configuration)

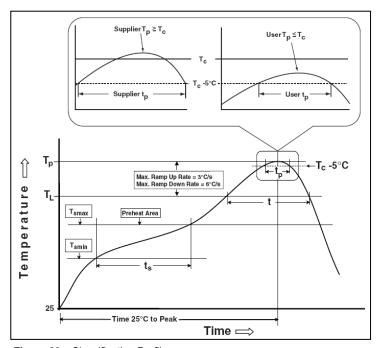

## **CLASSIFICATION REFLOW PROFILES**

| Profile Feature                                                                           | Pb-Free Assembly                 |

|-------------------------------------------------------------------------------------------|----------------------------------|

| Preheat & Soak Temperature min (Tsmin) Temperature max (Tsmax) Time (Tsmin to Tsmax) (ts) | 150°C<br>200°C<br>60-120 seconds |

| Average ramp-up rate (Tsmax to Tp)                                                        | 3°C/second max.                  |

| Liquidous temperature (TL) Time at liquidous (tL)                                         | 217°C<br>60-150 seconds          |

| Peak package body temperature (Tp)*                                                       | Max 260°C                        |

| Time (tp)** within 5°C of the specified classification temperature (Tc)                   | Max 30 seconds                   |

| Average ramp-down rate (Tp to Tsmax)                                                      | 6°C/second max.                  |

| Time 25°C to peak temperature                                                             | 8 minutes max.                   |

Figure 33 Classification Profile

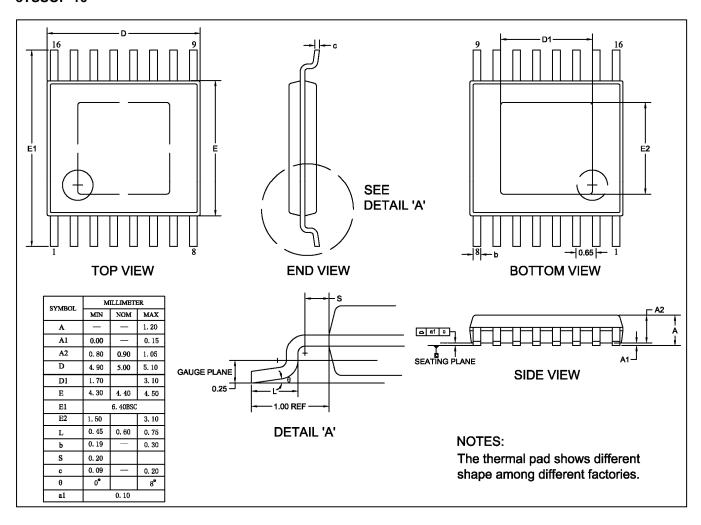

## **PACKAGE INFORMATION**

## eTSSOP-16

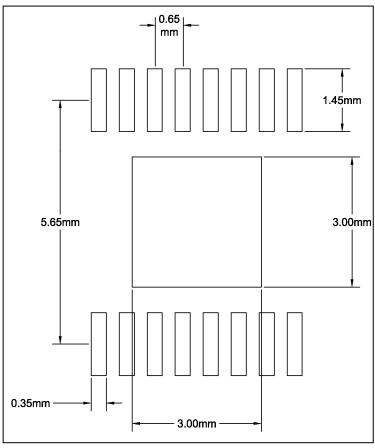

## **RECOMMENDED LAND PATTERN**

## eTSSOP-16

#### Note:

- 1. Land pattern complies to IPC-7351.

- 2. All dimensions in MM.

- 3. This document (including dimensions, notes & specs) is a recommendation based on typical circuit board manufacturing parameters. Since land pattern design depends on many factors unknown (eg. user's board manufacturing specs), user must determine suitability for use.

## IS32LT3957

**REVISION HISTORY**

| Revision | Detail Information | Date       |

|----------|--------------------|------------|

| Α        | Initial release    | 2018.10.23 |

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

ISSI:

IS32LT3957-ZLA3-TR IS32LT3957-ZLA3