#### **16-CHANNEL LED DRIVER**

June 2021

#### **GENERAL DESCRIPTION**

The IS32FL3726A is a serial shift-register-plus latch-type LED driver operating from a 3V to 5V supply. It is comprised of 16 constant-current open drain sinks designed for driving common anode LEDs. The output current value can be set from 5mA to 60mA by using an external resistor. As a result, all outputs will have virtually the same current levels. This driver uses a high-speed 4-wire serial interface of up to 30MHz to drive 16 constant current outputs, a 16-bit shift register, a 16-bit latch and a 16-bit AND-gate circuit. Serial input data appears at the

output OUTn channels after 16 clock cycles. Driving the Latch pin will load the 16-bit of shift-register data into the 16-bit output latch to drive the LEDs ON or OFF. The Enable pin can be used as a PWM input to adjust the LED brightness. The IS32FL3726A operates from a 3V to 5.5V supply, and is specified over the -40°C to +125°C temperature range.

#### **APPLICATIONS**

- Car display panel

- Ambient lighting

- Roof lighting

- Functional lighting

#### **FEATURES**

- Output current capability and number of outputs: 60mA x 16 outputs

- · Current set with external resistor

- Constant current range: 5mA to 60mA

IOUT\_MAX= 45mA @ Vcc= 3.3V

IOUT MAX= 60mA @ Vcc= 5V

- Current accuracy (All output on, I<sub>OUT</sub> = 25.2mA)

- Bit to bit:  $< \pm 5\%$ .

- Device to device: < ±5%.

- 200mV LED Dropout at 25mA

- For common-anode LEDs

- Power supply voltage range, V<sub>CC</sub>= 3.0V to 5.5V

- Serial and parallel data transfer rate: 30MHz (Max. cascade connection)

- Operating temperature range, -40°C ~ +125°C

- Package: eTSSOP-24

- AEC-Q100 Qualified

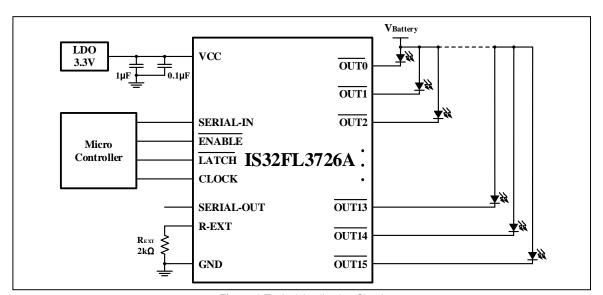

#### TYPICAL APPLICATION CIRCUIT

Figure 1 Typical Application Circuit

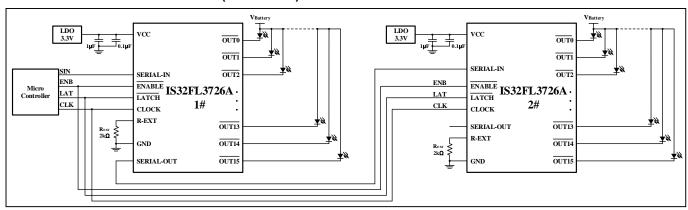

### **TYPICAL APPLICATION CIRCUIT (CONTINUE)**

Figure 2 Typical Application Circuit (Serial Synchronization)

### **PIN CONFIGURATION**

| Package   | Pin Configuration (Top View)                                |     |                                                                                                      |  |  |

|-----------|-------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------|--|--|

| eTSSOP-24 | GND SERIAL-IN CLOCK DUTO OUTO OUTO OUTO OUTO OUTO OUTO OUTO | 1 • | 24 VCC 23 R-EXT 22 SERIAL-OUT 21 ENABLE 20 OUT15 19 OUT14 18 OUT13 17 OUT12 16 OUT10 14 OUT9 13 OUT8 |  |  |

### **PIN DESCRIPTION**

| No.  | Pin         | Description                                                                                                                 |

|------|-------------|-----------------------------------------------------------------------------------------------------------------------------|

| 1    | GND         | GND pin for control logic.                                                                                                  |

| 2    | SERIAL-IN   | Input pin for serial data for data shift register.                                                                          |

| 3    | CLOCK       | Input pin for clock for data shift on rising edge.                                                                          |

| 4    | LATCH       | Input pin for data strobe when the LATCH input is driven low, data is not latched. When it is pulled high, data is latched. |

| 5~20 | OUT0~OUT15  | Constant-current sinks.                                                                                                     |

|      |             | Input pin for output enable.                                                                                                |

| 21   | ENABLE      | All current sinks (OUT0 to OUT15) are turned off, when                                                                      |

|      | LIVADLE     | the ENABLE pin is driven High and are turned on, when this pin is driven Low.                                               |

| 22   | SERIAL-OUT  | Output pin for serial data input on SERIAL-IN terminal.                                                                     |

| 23   | R-EXT       | Input pin connect to an external resistor to regulate the output current.                                                   |

| 24   | VCC         | Supply voltage pin.                                                                                                         |

|      | Thermal Pad | Connect to GND.                                                                                                             |

#### **ORDERING INFORMATION**

Automotive Range: -40°C to +125°C

| Order Part No.      | Package              | QTY/Reel |  |

|---------------------|----------------------|----------|--|

| IS32FL3726A-ZLA3-TR | eTSSOP-24, Lead-free | 2500     |  |

Copyright © 2021 Lumissil Microsystems. All rights reserved. Lumissil Microsystems reserves the right to make changes to this specification and its products at any time without notice. Lumissil Microsystems assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Lumissil Microsystems does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Lumissil Microsystems receives written assurance to its satisfaction, that:

- a.) the risk of injury or damage has been minimized;

- b.) the user assume all such risks; and

- c.) potential liability of Lumissil Microsystems is adequately protected under the circumstances

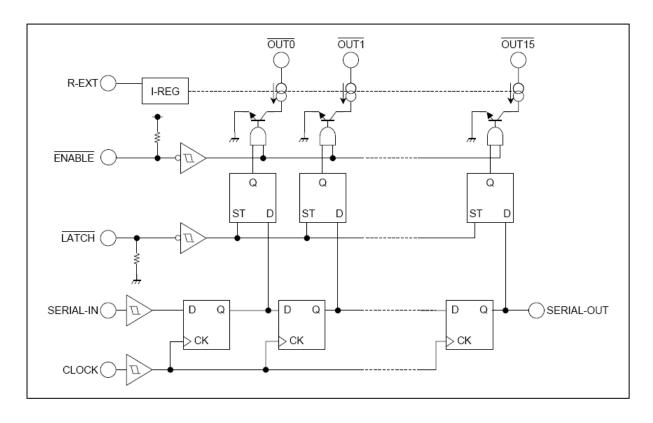

### **FUNCTIONAL BLOCK DIAGRAM**

### **ABSOLUTE MAXIMUM RATINGS**

| Supply voltage, V <sub>CC</sub>                              | -0.3V ~ +6.0V    |

|--------------------------------------------------------------|------------------|

| Voltage at any input pin                                     | -0.3V ~ Vcc+0.2V |

| Maximum junction temperature, T <sub>JMAX</sub>              | +150°C           |

| Storage temperature range, T <sub>STG</sub>                  | -65°C ~ +150°C   |

| Operating temperature range, T <sub>A</sub> =T <sub>J</sub>  | -40°C ~ +125°C   |

| Package thermal resistance, junction to ambient (4 layer     | 28.1°C/W         |

| standard test PCB based on JEDEC standard), θ <sub>JA</sub>  | 28.1 6/1         |

| Package thermal resistance, junction to thermal PAD (4 layer | 8.55°C/W         |

| standard test PCB based on JEDEC standard), θ <sub>JP</sub>  | 0.99 C/VV        |

| Maximum power dissipation, PDMAX                             | 3.56W            |

| ESD (HBM)                                                    | ±2kV             |

| ESD (CDM)                                                    | ±750V            |

**Note 1:** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITION

$V_{CC}$ = 5V,  $T_{A}$ =  $T_{J}$ = -40°C ~ +125°C, unless otherwise noted.

| Symbol             | Characteristic                               | Condition         | Min. | Тур. | Max. | Unit |

|--------------------|----------------------------------------------|-------------------|------|------|------|------|

| Vouт               | Output (headroom) voltage                    |                   |      | 0.7  | 5    | V    |

| f <sub>CLK</sub>   | Clock frequency                              | Cascade connected |      |      | 30   | MHz  |

| twLAT              | LATCH pulse width (Note 2)                   | Cascade connected | 20   |      |      | ns   |

| twclk              | CLOCK pulse width (Note 2)                   |                   | 20   |      |      | ns   |

| twena              | ENABLE pulse width (Note 2, 3)               |                   | 70   |      |      | ns   |

| tsetup1            | SERIAL-IN set-up time for CLOCK pin (Note 2) |                   | 8    |      |      | ns   |

| tHOLD1             | SERIAL-IN Hold time for CLOCK pin (Note 2)   |                   | 8    |      |      | ns   |

| tsetup2            | Set-up time for LATCH pin (Note              |                   | 8    |      |      | ns   |

| t <sub>HOLD2</sub> | Hold time for LATCH pin (Note 2)             |                   | 8    |      |      | ns   |

Note 2: Guaranteed by design.

Note 3: When the pulse of the Low level is input to the ENABLE pin held in the High level.

### **ELECTRICAL CHARACTERISTICS**

$V_{CC}$ = 5V,  $T_{A}$ =  $T_{J}$ = -40°C ~ +125°C, unless otherwise noted.

| Symbol                | Characteristic                           | Condition                                          |                                                     | Min.               | Тур. | Max.               | Unit |  |

|-----------------------|------------------------------------------|----------------------------------------------------|-----------------------------------------------------|--------------------|------|--------------------|------|--|

| Vcc                   | Supply voltage                           | Normal operation                                   |                                                     | 3.0                |      | 5.5                | V    |  |

|                       |                                          | V <sub>OUT</sub> =1V,V <sub>CC</sub> = 3.3V        | R <sub>EXT</sub> = 750Ω                             | 23.4               | 25.2 | 27                 | Л    |  |

| Іоит                  |                                          | Vout=1V,Vcc= 5V                                    | R <sub>EXT</sub> = 750Ω                             | 23.4               | 25.2 | 27                 | mA   |  |

| _                     | Output current error                     | V <sub>OUT</sub> = 1V<br>V <sub>CC</sub> = 3.3V    | R <sub>EXT</sub> = 750Ω<br>I <sub>OUT</sub> =25.2mA | -5                 |      | 5                  | %    |  |

| ΔI <sub>MAT</sub>     | between bits (Note 5)                    | $V_{OUT} = 1V$<br>$V_{CC} = 5V$                    | $R_{EXT} = 750\Omega$<br>$I_{OUT} = 25.2 \text{mA}$ | -5                 |      | 5                  | %    |  |

|                       | Output current error                     | V <sub>OUT</sub> = 1V<br>V <sub>CC</sub> = 3.3V    | $R_{EXT} = 750\Omega$<br>$I_{OUT} = 25.2 \text{mA}$ | -5                 |      | 5                  | %    |  |

| ΔΙουτ                 | between ICs (Note 6)                     | V <sub>OUT</sub> = 1V<br>V <sub>CC</sub> = 5V      | R <sub>EXT</sub> = 750Ω<br>I <sub>OUT</sub> =25.2mA | -5                 |      | 5                  | %    |  |

| V <sub>HR</sub>       | Headroom voltage                         | R <sub>EXT</sub> = 750Ω, I <sub>OUT</sub> = 25.2mA |                                                     |                    | 0.4  | 0.55               | V    |  |

| loz                   | Output leakage current input voltage     | V <sub>OUT</sub> = 5.5V                            |                                                     |                    |      | 1                  | μA   |  |

| $V_{IH}$              | Input voltage                            | Logic high level                                   |                                                     | 0.7V <sub>CC</sub> |      |                    | V    |  |

| $V_{IL}$              | input voitage                            | Logic low level                                    |                                                     |                    |      | 0.3V <sub>CC</sub> |      |  |

| Vol                   |                                          | I <sub>OL</sub> = 1.0mA, V <sub>CC</sub> = 3.3V    |                                                     |                    |      | 0.4                |      |  |

| VOL                   | SERIAL-OUT pin                           | $I_{OL} = 1.0 \text{mA}, V_{CC} = 5 \text{V}$      |                                                     |                    |      | 0.4                | V    |  |

| V <sub>OH</sub>       | voltage                                  | I <sub>OH</sub> = -1.0mA, V <sub>CC</sub> = 3.3V   |                                                     | 2.9                |      |                    |      |  |

| VOH                   |                                          | Iон = -1.0mA, Vcc = 5V                             |                                                     | 4.6                |      |                    |      |  |

| %/Vcc                 | Output current supply voltage regulation | When Vcc is changed 3.3V to 5.5V, IouT= 25.2mA     |                                                     |                    |      | 1.5                | %    |  |

| $R_{(UP)}$            | Pull-up resistor                         | ENABLE pin                                         | ENABLE pin                                          |                    | 500  | 750                | kΩ   |  |

| $R_{(DOWN)}$          | Pull-down resistor                       | LATCH pin                                          |                                                     | 250                | 300  | 730                | N22  |  |

| I <sub>DD(OFF)1</sub> |                                          | V <sub>OUT</sub> = 5V                              | R <sub>EXT</sub> = OPEN                             |                    | 0.3  | 0.6                |      |  |

| I <sub>DD(OFF)2</sub> |                                          | Vout = 5V                                          | $R_{EXT} = 0.75 k\Omega$                            |                    | 2.1  | 2.5                |      |  |

| 100(011)2             | Supply current                           | All outputs off                                    | $R_{EXT} = 1.8k\Omega$                              |                    | 1    | 1.2                | mA   |  |

| I <sub>DD(ON)1</sub>  |                                          | Vout = 0.7V                                        | $R_{EXT} = 0.75k\Omega$                             |                    | 8.6  | 10                 |      |  |

| , ,                   |                                          | All outputs on                                     | $R_{EXT} = 1.8k\Omega$                              |                    | 4.5  | 6                  |      |  |

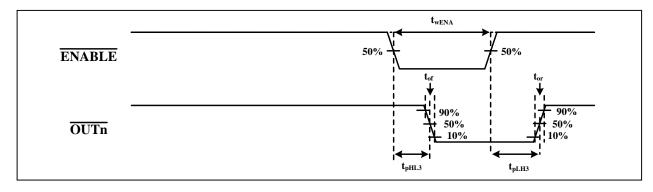

### **SWITCHING CHARACTERISTICS (NOTE 4)**

$V_{CC}$ = 5V,  $T_A$ =  $T_J$ = -40°C ~ +125°C, unless otherwise noted.

| Symbol                  | Characteristic          | Condition                               | Min. | Тур. | Max. | Unit |

|-------------------------|-------------------------|-----------------------------------------|------|------|------|------|

| t <sub>pLH1</sub>       |                         | CLOCK - OUTn, LATCH= "H"<br>ENABLE= "L" |      | 30   | 50   |      |

| t <sub>pLH2</sub>       |                         | LATCH - OUTn, ENABLE =                  |      | 30   | 50   |      |

| t <sub>pLH3</sub>       |                         | ENABLE - OUTn, LATCH=                   |      | 50   | 70   |      |

| <b>t</b> <sub>pLH</sub> | Propagation delay       | CLOCK - SERIAL-OUT                      |      | 20   | 40   | ns   |

| t <sub>pHL1</sub>       | 1 Topagation delay      | CLOCK - OUTn, LATCH= "H"<br>ENABLE= "L" |      | 60   | 100  | 113  |

| t <sub>pHL2</sub>       |                         | LATCH - OUTn, ENABLE =                  |      | 60   | 100  |      |

| t <sub>pHL3</sub>       |                         | ENABLE - OUTn, LATCH=                   |      | 70   | 100  |      |

| t <sub>pHL</sub>        |                         | CLOCK - SERIAL-OUT                      |      | 20   | 40   |      |

| tor                     | Output rise time        | 10%~90% of voltage waveform             |      | 30   | 50   | ns   |

| tof                     | Output fall time        | 90%~10% of voltage waveform             |      | 52   | 80   | ns   |

| tr                      | Maximum CLOCK rise time | When not on DCP (Note 7)                |      |      | 500  | ns   |

| t <sub>f</sub>          | Maximum CLOCK fall time | When not on PCB (Note 7)                |      |      | 500  | ns   |

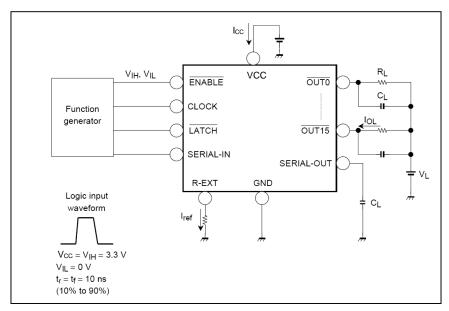

Conditions: (Refer to test circuit.)

$T_{A} = T_{J} = -40^{\circ}C \, \sim \, +125^{\circ}C, \ V_{CC} = V_{IH} = 3.3V \ \text{and} \ 5V, \ V_{IL} = 0V, \ R_{EXT} = 750\Omega, \ V_{L} = 3.0V, \ R_{L} = 60\Omega, \ C_{L} = 10.5 pF$

Note 4: Guaranteed by design.

Note 5:  $I_{OUT}$  mismatch (bit to bit)  $\Delta I_{MAT}$  is calculated:

$$\Delta I_{MAT} = \left(\frac{I_{OUTn}(n = 0 \sim 15)}{\left(\frac{I_{OUT0} + I_{OUT1} + \dots + I_{OUT15}}{16}\right)} - 1\right) \times 100\%$$

Note 6:  $I_{OUT}$  accuracy (device to device)  $\Delta I_{OUT}$  is calculated:

$$\Delta I_{OUT} = \left(\frac{(\frac{I_{OUT0} + I_{OUT1} + ... + I_{OUT15}}{16} - I_{OUT(IDEAL)})}{I_{OUT(IDEAL)}}\right) \times 100\%$$

Where  $I_{OUT(IDEAL)}$ = 10.5mA when  $R_{EXT}$ = 1800 $\Omega$ ,  $I_{OUT(IDEAL)}$ = 25.2mA when  $R_{EXT}$ = 750 $\Omega$ .

#### Note 7:

- 1. If the device is connected in a cascade and tr/tf for the waveform is large, it may not be possible to achieve the timing required for data transfer. Please consider the timings carefully.

- 2. Delay between outputs. The IS32FL3726A has graduated delay circuits between outputs. The fixed delay time is 5ns (typical), OUT1 has 5ns delay, OUT2 has 10ns delay, etc. This delay prevents large inrush currents, which reduce power supply bypass capacitor requirements when the outputs turn on. The delay works during switch on and switch off of each output channel. LEDs that have not turned on before ENABLE is low will still turn on and off at the determined delayed time regardless of the state of ENABLE. Therefore, every LED will be illuminated for the amount of time ENABLE is pulled high.

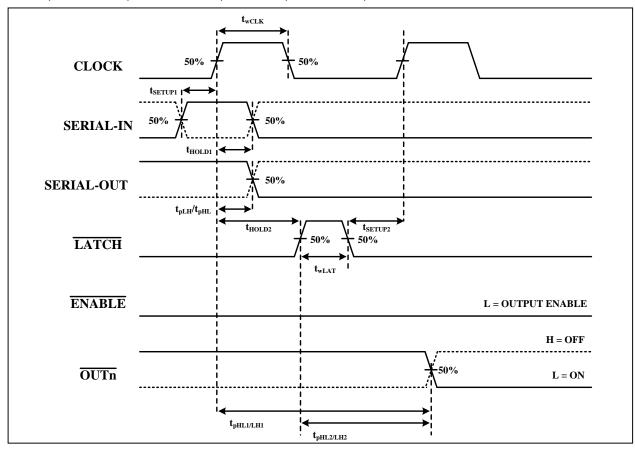

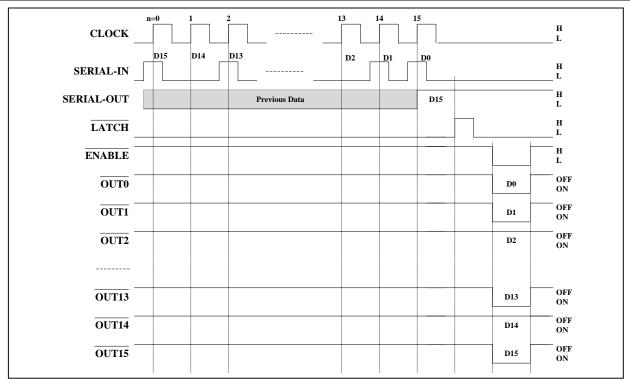

### **TIMING WAVEFORM**

### 1. CLOCK, SERIAL-IN, SERIAL-OUT, LATCH, ENABLE, OUTn

### 2. OUTn

Figure 3 Timing Diagram

Warning: The Latch input is a logic levelit is not an edge triggered latch circuit.

Note 8: The serial-in data (SERIAL-IN) will be clocked into a 16 bit shift register synchronized on the rising edge of the clock (CLOCK). The data "1" means the corresponding current output "ON" for output, the data "0" represents for "OFF". The data will be transferred into the 16 bit latch register when the signal (LATCH) is 'H' (level trigger); otherwise, the data will be latched. The trigger timing of the serial-out data (SERIAL-OUT) will be shifted out on synchronization to the rising edge of the clock. All outputs are turned off while enable terminal (ENABLE) is kept at high level. And they are active when ENABLE turns to low.

#### **Truth Table**

| CLOCK    | LATCH | ENABLE | SERIAL-IN | OUT0OUT7 OUT15 | SERIAL-OUT |

|----------|-------|--------|-----------|----------------|------------|

|          | Н     | L      | Dn        | DnDn-7Dn-15    | Dn-15      |

|          | L     | L      | Dn+1      | No change      | Dn-14      |

|          | Н     | L      | Dn+2      | Dn+2Dn-5Dn-13  | Dn-13      |

| <b>—</b> | X     | L      | Dn+3      | Dn+2Dn-5Dn-13  | Dn-13      |

| <b>—</b> | X     | Н      | Dn+3      | OFF            | Dn-13      |

Warning: The following conditions, ENABLE=0, LATCH=1, SERIAL-IN=1, cannot be configured at the same time when power is on, or IS32FL3726A will behave unpredictably.

**Note 9:** OUT0 to OUT15 =On when Dn = H; OUT0 to OUT15 =Off when Dn = L. In order to ensure that the level of the power supply voltage is correct, an external resistor must be connected between R-EXT and GND.

### TYPICAL TEST CHARACTERISTICS

Figure 4 Test Diagram

# LUMISSIL MICROSYSTEMS A Division of 1531

#### **APPLICATION INFORMATION**

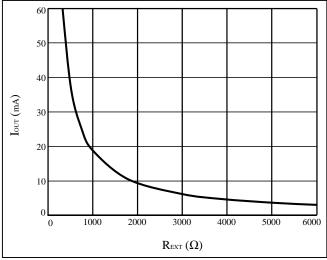

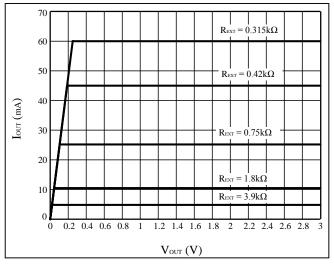

#### **ADJUSTING OUTPUT CURRENT**

The output current of each channel is set by an external resistor  $R_{\text{EXT}}$ , the relationship between  $I_{\text{OUT}}$  and  $R_{\text{EXT}}$  is:

$$I_{OUT} = k \times \frac{V_{REXT}}{R_{EXT}}$$

Where  $V_{REXT}$  is 1.26V, k is 15, so  $I_{OUT}$  is calculated by Equation (1):

$$I_{OUT} = 15 \times \frac{1.26V}{R_{EXT}} \tag{1}$$

As show in the figure below:

Figure 5 I<sub>OUT</sub> vs. R<sub>EXT</sub>

### **CONSTANT CURRENT OUTPUT**

In order to obtain a good performance of constantcurrent output, a suitable output voltage is necessary. Users can get related information about the minimum output voltage below.

Figure 6  $I_{OUT}$  vs.  $V_{OUT}$

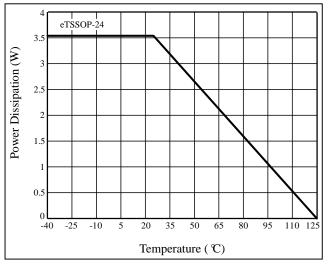

#### THERMAL CONSIDERATIONS

The package thermal resistance,  $\theta_{JA}$ , determines the amount of heat that can pass from the silicon die to the surrounding ambient environment. The  $\theta_{JA}$  is a measure of the temperature rise created by power dissipation and is usually measured in degree Celsius per watt (°C/W).

When operating the chip at high ambient temperatures, or when driving maximum load current, care must be taken to avoid exceeding the package power dissipation limits. The maximum power dissipation can be calculated using the following Equation (2):

$$P_{D(MAX)} = \frac{T_{J(MAX)} - T_A}{\theta_{JA}}$$

(2)

So,

$$P_{D(MAX)} = \frac{125^{\circ}C - 25^{\circ}C}{28.1^{\circ}C/W} \approx 3.56W$$

Figure 7 shows the power derating of the IS32FL3726A on a JEDEC boards (in accordance with JESD 51-5 and JESD 51-7) standing in still air.

Figure 7 Dissipation Curve

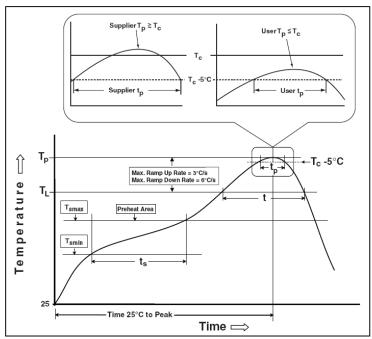

### **CLASSIFICATION REFLOW PROFILES**

| Profile Feature                                                                           | Pb-Free Assembly                 |

|-------------------------------------------------------------------------------------------|----------------------------------|

| Preheat & Soak Temperature min (Tsmin) Temperature max (Tsmax) Time (Tsmin to Tsmax) (ts) | 150°C<br>200°C<br>60-120 seconds |

| Average ramp-up rate (Tsmax to Tp)                                                        | 3°C/second max.                  |

| Liquidous temperature (TL) Time at liquidous (tL)                                         | 217°C<br>60-150 seconds          |

| Peak package body temperature (Tp)*                                                       | Max 260°C                        |

| Time (tp)** within 5°C of the specified classification temperature (Tc)                   | Max 30 seconds                   |

| Average ramp-down rate (Tp to Tsmax)                                                      | 6°C/second max.                  |

| Time 25°C to peak temperature                                                             | 8 minutes max.                   |

Figure 8 Classification Profile

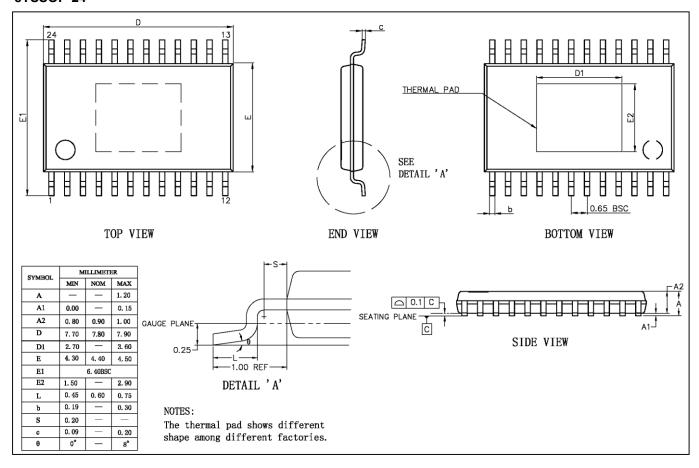

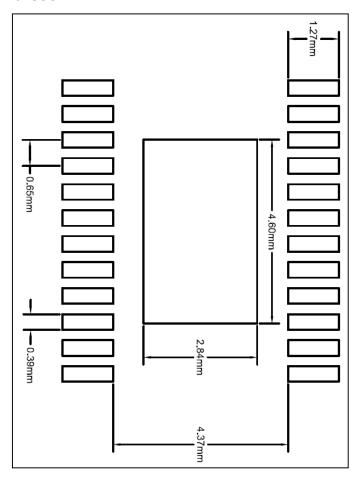

### **PACKAGE INFORMATION**

#### eTSSOP-24

### RECOMMENDED LAND PATTERN

### eTSSOP-24

#### Note:

- 1. Land pattern complies to IPC-7351.

- 2. All dimensions in MM.

- 3. This document (including dimensions, notes & specs) is a recommendation based on typical circuit board manufacturing parameters. Since land pattern design depends on many factors unknown (eg. user's board manufacturing specs), user must determine suitability for use.

### **REVISION HISTORY**

| Revision | Detail Information         | Date       |

|----------|----------------------------|------------|

| 0A       | Initial release            | 2020.09.04 |

| 0B       | Update EC table            | 2020.12.11 |

| Α        | Release to mass production | 2021.02.08 |

| В        | Update AEC-Q100 qualified  | 2021.06.18 |

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

ISSI:

IS32FL3726A-ZLA3-TR