# Single-channel isolated gate-driver ICs in 150 mil DSO package

#### **Description**

EiceDRIVER™ 1EDBx275F is a family of single-channel isolated gate-driver ICs, designed to drive Si, SiC and GaN power switches.

1EDBx275F is available in an 8-pin DSO package with 4 mm input-to-output creepage distance; it provides isolation by means of on-chip coreless transformer (CT) technology.

With tight timing specifications, 1EDBx275F is designed for fast-switching medium-to-high power systems. Excellent common-mode rejection, low part-to-part skew, fast signal propagation and small package size make 1EDBx275F a superior alternative to high-side driving solutions using optocouplers or pulse transformers.

#### **Features**

- · Single-channel isolated gate-driver

- 45 ns input-to-output propagation delay with excellent accuracy (+4/-4 ns)

- Separate low impedance source and sink outputs

- Fast clamping of parasitics-induced output overshoots under UVLO conditions

- Fast start-up times and fast recovery after supply glitches

- Optimized UVLO levels (4 V, 8 V, 13 V) for Si, SiC and GaN transistors

- High common mode transient immunity (CMTI > 300 V/ns)

- Available in 8-pin 150mil DSO package

- Qualified for industrial grade applications

#### **Isolation and safety certificates**

• UL1577 with  $V_{ISO}$  = 3000  $V_{RMS}$  (certification pending)

#### **Potential Applications**

- Server, telecom and industrial Switch-Mode Power Supplies (SMPS)

- EV power modules, motor drives and power tools

- Solar power inverters and Uninterruptable Power Supplies (UPS)

#### Table 1 EiceDRIVER™ 1EDBx275F Portfolio

| Part number | Peak source / sink current                        | UVLO ON / OFF   | Isolation certification              | Package  |

|-------------|---------------------------------------------------|-----------------|--------------------------------------|----------|

| 1EDB7275F   | 5 4 4 / 0 0 4                                     | 4.2 V / 3.9 V   |                                      |          |

| 1EDB8275F   | 5.4  A / 9.8  A<br>(for $V_{DDO} = 15 \text{V}$ ) | 8.0 V / 7.0 V   | UL1577<br>$(V_{ISO} = 3000 V_{RMS})$ | PG-DSO-8 |

| 1EDB9275F   | (101 v <sub>DDO</sub> - 13v)                      | 13.7 V / 12.9 V | (VISO - 3000 VRMS)                   |          |

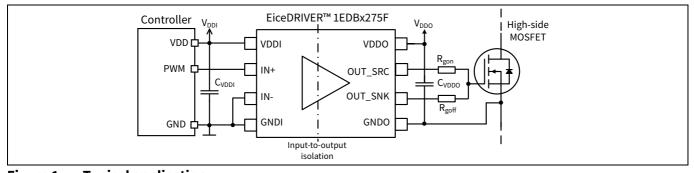

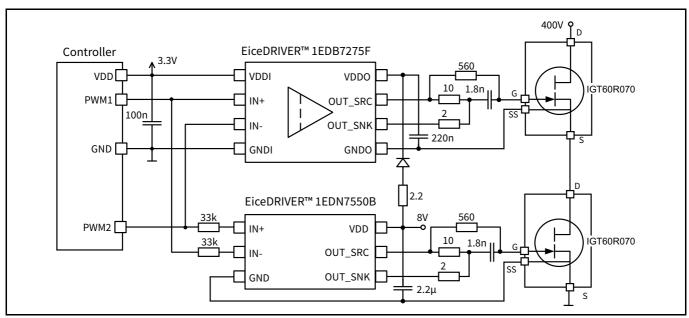

Figure 1 Typical application

# Single-channel isolated gate-driver ICs in 150 mil DSO package

# **Table of Contents**

| 1     | Pin configuration and description                      |

|-------|--------------------------------------------------------|

| 2     | Functional description                                 |

| 2.1   | Block diagram                                          |

| 2.2   | Power supply and Undervoltage Lockout (UVLO)           |

| 2.2.1 | Input supply voltage                                   |

| 2.2.2 | Output supply voltage                                  |

| 2.2.3 | Input stage                                            |

| 2.3   | Driver output                                          |

| 2.4   | Output active clamping                                 |

| 2.5   | CT communication and input to output data transmission |

| 3     | Electrical characteristics and parameters              |

| 3.1   | Absolute maximum ratings                               |

| 3.2   | Thermal characteristics                                |

| 3.3   | Operating range                                        |

| 3.4   | Electrical characteristics                             |

| 3.5   | Isolation specifications                               |

| 4     | Timing diagrams 1                                      |

| 5     | Layout recommendation 1                                |

| 6     | Application notes                                      |

| 6.1   | Driving 600 V CoolGaN <sup>™</sup>                     |

| 6.2   | Driving 650 V CoolSiC <sup>™</sup>                     |

| 7     | Typical characteristics 2                              |

| 8     | Package outline dimensions                             |

| 8.1   | Device numbers and markings                            |

| 8.2   | Package PG-DSO-8 2                                     |

# Single-channel isolated gate-driver ICs in 150 mil DSO package

Pin configuration and description

# 1 Pin configuration and description

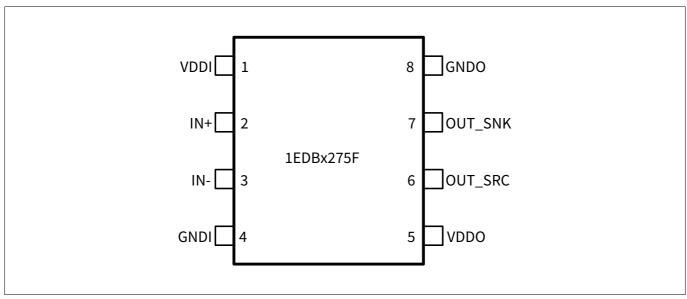

Figure 2 Pin configuration (top side view)

Table 2 Pin description

| Pin | Symbol  | Description                                                                          |

|-----|---------|--------------------------------------------------------------------------------------|

| 1   | VDDI    | Input-side supply voltage (3 V to 15 V)                                              |

| 2   | IN+     | Non-inverting driver input (active high); if IN+ is low or left open, OUT_SNK is low |

| 3   | IN-     | Inverting driver input (active low); if IN- is high or left open, OUT_SNK is low     |

| 4   | GNDI    | Input-side ground reference                                                          |

| 5   | VDDO    | Output-side supply voltage (up to 20 V)                                              |

| 6   | OUT_SRC | Driver output source, low-impedance switch to VDDO                                   |

| 7   | OUT_SNK | Driver output sink, low-impedance switch to GNDO                                     |

| 8   | GNDO    | Output-side ground reference                                                         |

For package drawing details see **Chapter 8 Package outline dimensions**.

**Functional description**

# 2 Functional description

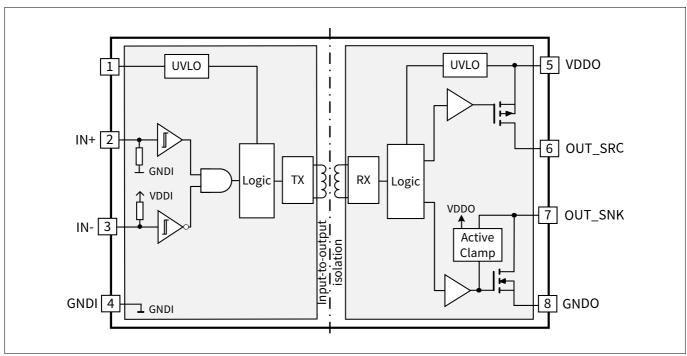

## 2.1 Block diagram

A simplified functional block diagram for the EiceDRIVER™ 1EDBx275F is given in Figure 3.

Figure 3 Block diagram

# 2.2 Power supply and Undervoltage Lockout (UVLO)

Due to the isolation between input and output side, two power domains with independent power management are required. Undervoltage Lockout (UVLO) functions for both input and output supplies ensure a defined startup and robust functionality under all operating conditions.

#### 2.2.1 Input supply voltage

The input die is powered via VDDI and supports a wide supply voltage range from 3 V to 15 V. A ceramic bypass capacitor must be placed between VDDI and GNDI in close proximity to the device; a minimum capacitance of 100 nF is recommended.

Power consumption to some extent depends on switching frequency, as the input signal is converted into a train of repetitive current pulses to drive the coreless transformer. Due to the chosen robust encoding scheme the average repetition rate of these pulses and thus the average supply current depends on the switching frequency,  $f_{\rm sw}$ . However, for  $f_{\rm sw}$  < 500 kHz this effect is very small.

The Undervoltage Lockout function for the input supply VDDI ensures that, as long as VDDI is below UVLO (e.g. in startup), no data is transferred to the output side and the gate driver output is held low (Safety Lock-down at startup). When VDDI exceeds the UVLO level, the PWM input signal is transferred to the output side. If the output side is ready (not in UVLO condition), the output reacts according to the logic input.

# Single-channel isolated gate-driver ICs in 150 mil DSO package

## **Functional description**

#### 2.2.2 **Output supply voltage**

The output die is powered via VDDO (up to 20 V). A ceramic bypass capacitor must be placed between VDDO and GNDO in close proximity to the device. A minimum capacitance of 20 x  $C_{iss}$  (MOSFET input capacitance) is recommended to ensure an acceptable ripple (5% of VDDO) on the supply pin.

The minimum supply voltage is set by the Undervoltage Lockout (UVLO) function. The gate-driver output can be switched only, if the output supply voltage (VDDO) exceeds the output-side UVLO. Thus it can be guaranteed that the switch transistor is not operated, if the driving voltage is too low to achieve a complete and fast transition to the "on" state. Low driving voltage in fact could cause the power MOSFET to enter its saturation (ohmic) region with potentially destructive power dissipation; the output UVLO ensures that the switch transistor always stays within its Safe Operating Area (SOA). Versions with 4 V, 8 V, 13 V UVLO thresholds for the output supply are currently available; Table 3 shows the recommended UVLO levels for different Infineon power switch families.

| Table 3 Recommended 1EDBX215F OVEO levels for typical use-cases |      |                         |     |       |  |  |  |  |

|-----------------------------------------------------------------|------|-------------------------|-----|-------|--|--|--|--|

| Switch far                                                      | nily | Switch part number exam | ple | Recor |  |  |  |  |

| Table 3 | Recommended 1EDBx275F UVLO levels for typical use-cases |

|---------|---------------------------------------------------------|

|---------|---------------------------------------------------------|

| Switch part number example   | Recommended 1EDBx275F                                                                                             |

|------------------------------|-------------------------------------------------------------------------------------------------------------------|

| BSC010N04LS6, BSZ070N08LS5,  | 1EDB7275F (4 V UVLO)                                                                                              |

| BSC040N10NS5, BSZ084N08NS5,  | 1EDB8275F (8 V UVLO)                                                                                              |

| IPP60R099C7, IPB60R600P6,    | 1EDB8275F (8 V UVLO)                                                                                              |

| IMZA65R027M1H, IMW65R107M1H, | 1EDB9275F (13 V UVLO)                                                                                             |

| IGOT60R070D1, IGLD60R070D1,  | 1EDB7275F (4V UVLO)                                                                                               |

|                              | BSC010N04LS6, BSZ070N08LS5,  BSC040N10NS5, BSZ084N08NS5,  IPP60R099C7, IPB60R600P6,  IMZA65R027M1H, IMW65R107M1H, |

#### 2.2.3 Input stage

The logic driver output state is equal to the non-inverted or inverted input signal state at pins IN+ or IN-, respectively. The non-inverting input IN+ is internally pulled down to a logic low voltage and the inverting input is internally pulled up to a logic high voltage. This prevents any switching-on during power-up or in other situations with insufficient supply voltage.

The input is compatible with LV-TTL levels and provide a hysteresis of typically 0.9 V. This hysteresis is independent of the supply voltage  $V_{DDI}$ .

Table 4 shows the IN+, IN- driver logic in case of sufficiently high supply voltage. Otherwise the outputs of the driver are determined by the Undervoltage Lockout (UVLO) and Output Active Clamping functionalities as shown in Table 5.

Table 4 Logic table in case of sufficient bias power

| Inpu | ıts | Supplies                          | Outputs | Note                                         |  |  |

|------|-----|-----------------------------------|---------|----------------------------------------------|--|--|

| IN+  | IN- | $V_{\rm DDI}, V_{\rm DDO}$        | OUT     |                                              |  |  |

| Н    | L   |                                   | Н       | -                                            |  |  |

| Х    | Н   | >UVLO <sub>VDDx,on</sub> (active) | L       | The output is disabled via IN- (active low)  |  |  |

| L    | х   |                                   | L       | The output is disabled via IN+ (active high) |  |  |

#### 2.3 **Driver output**

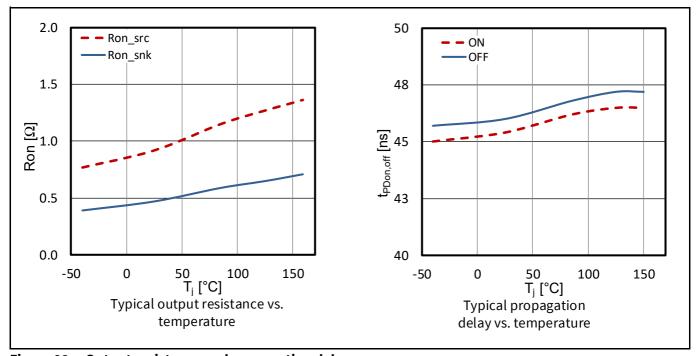

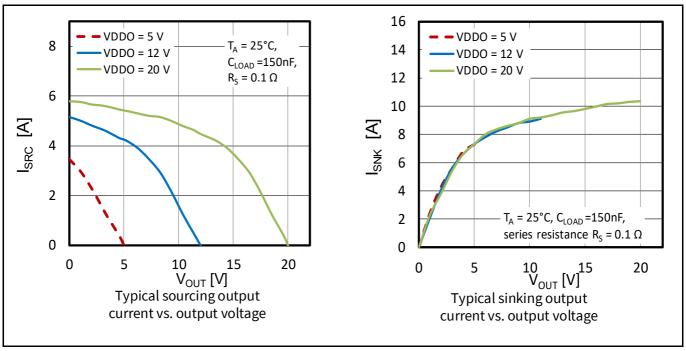

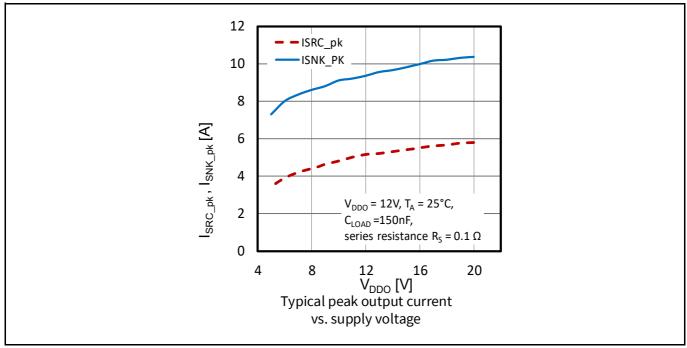

The rail-to-rail output stage realized with complementary MOS transistors is able to provide a typical 5.4 A sourcing and 9.8 A sinking peak current for a 15 V supply. The low on-resistance coming together with high driving current is particularly beneficial for fast switching of very large MOSFETs. With a  $R_{\rm on}$  of 0.95  $\Omega$  for the sourcing pMOS and  $0.48 \Omega$  for the sinking nMOS transistor the driver can in most applications be considered as a nearly ideal switch. The p-channel sourcing transistor enables real rail-to-rail behavior without suffering from the voltage drop unavoidably associated with nMOS source follower stages.

#### Single-channel isolated gate-driver ICs in 150 mil DSO package

## **Functional description**

In case of floating inputs or insufficient supply voltage not exceeding the UVLO thresholds, the driver output is actively clamped to the "low" level (GNDO).

## 2.4 Output active clamping

The Undervoltage Lockout (UVLO) ensures no driver operation for supplies below the UVLO thresholds. However, this is not sufficient to guarantee that the output of the driver is kept low. Transient-induced current on the MOSFETs side may pull-up the output node of the driver and the gate voltage causing an unwanted turn-on of the switch; this is particularly critical in systems using bootstrapping since, during start-up, the supply of the high-side channel is delayed, while the low-side MOSFETs is already switching. In resonant topologies (as LLC), the half-bridge switching node may be pulled up after the turn-off of the low-side switch. When this is turned on again, the dv/dt induced increase of the high-side gate voltage cannot be clamped by the drivers  $R_{\rm DSON, sink}$  if the the boostrap supply is not yet available.

With a fast active clamping circuit in the output stage, EiceDRIVER<sup>TM</sup> 1EDBx275F ensures safe operation in all UVLO situations. This structure allows fast reaction and effective clamping of the output pins (OUT). The exact reaction time depends on the output supply  $(V_{DDO})$  and on the output voltage levels; however, already for very low supply levels (~1 V), the active clamping is able to react in some tens of ns.

Undervoltage Lockout together with the Output Active Clamping ensure that the output is actively held low in case of unsufficient output-side supply voltage.

Table 5 Logic table in case of insufficient supply voltages

| Inputs | Sup                       | Output                                                          |     |

|--------|---------------------------|-----------------------------------------------------------------|-----|

| INx    | $V_{	exttt{DDI}}$         | $V_{	exttt{DDO}}$                                               | OUT |

| Х      | > UVLO <sub>VDDI,on</sub> | $1.2 \text{ V} < V_{\text{DDO}} < \text{UVLO}_{\text{VDDO,on}}$ | L   |

## 2.5 CT communication and input to output data transmission

A coreless transformer (CT) based communication module is used for PWM signal transfer between input and output. A proven high-resolution pulse repetition scheme in the transmitter combined with a watchdog timeout at the receiver side enables recovery from communication fails and ensures safe system shutdown in failure cases.

## Single-channel isolated gate-driver ICs in 150 mil DSO package

**Electrical characteristics and parameters**

# 3 Electrical characteristics and parameters

The absolute maximum ratings are listed in **Table 6**. Stresses beyond these values may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# 3.1 Absolute maximum ratings

Table 6 Absolute maximum ratings

| Parameter                           | Symbol               |                      | Values |                       | Unit         | Note or Test Condition                           |

|-------------------------------------|----------------------|----------------------|--------|-----------------------|--------------|--------------------------------------------------|

|                                     |                      | Min.                 | Тур.   | Max.                  |              |                                                  |

| Input supply voltage                | $V_{	extsf{DDI}}$    | -0.3                 | -      | 17                    | V            | -                                                |

| Output supply voltage               | $V_{ m DDO}$         | -0.3                 | _      | 22                    | V            | -                                                |

| Voltage at pins IN+, IN-            | $V_{IN}$             | -0.3                 | _      | 17                    | ٧            | -                                                |

|                                     |                      | -5                   | _      | _                     | ٧            | transient for 50 ns 1)                           |

| Voltage at pin OUT_SRC              | V <sub>OUT_SRC</sub> | V <sub>DDO</sub> -24 | -      | V <sub>DDO</sub> +0.3 | V            | OUT = low, DC                                    |

|                                     |                      | V <sub>DDO</sub> -24 | -      | V <sub>DDO</sub> +2   | V            | OUT = low,<br>transient for 200 ns <sup>1)</sup> |

| Voltage at pin OUT_SNK              | V <sub>OUT_SNK</sub> | -0.3                 | -      | 24                    | ٧            | OUT = high, DC                                   |

|                                     |                      | -2                   | _      | 24                    | V            | OUT = high,<br>transient for 200 ns 1)           |

| Reverse current peak at pin OUT_SRC | I <sub>SRC_rev</sub> | -5                   | _      | -                     | $A_{\rm pk}$ | transient for 500 ns <sup>2)</sup>               |

| Reverse current peak at pin OUT_SNK | I <sub>SNK_rev</sub> | -                    | -      | 5                     | $A_{\rm pk}$ | transient for 500 ns <sup>2)</sup>               |

| Junction temperature                | $T_{J}$              | -40                  | -      | 150                   | °C           | -                                                |

| Storage temperature                 | $T_{\rm STG}$        | -55                  | _      | 150                   | °C           | -                                                |

| Soldering temperature               | $T_{SOL}$            | _                    | -      | 260                   | °C           | reflow / wave soldering 2)                       |

| ESD capability                      | V <sub>ESD_CDM</sub> | -                    | _      | 0.5                   | kV           | Charged Device Model (CDM) 3)                    |

|                                     | V <sub>ESD_HBM</sub> | -                    | -      | 2                     | kV           | Human Body Model<br>(HBM) <sup>4)</sup>          |

<sup>1)</sup> parameter verified by design, not tested in production

<sup>2)</sup> according to JESD22A111

<sup>3)</sup> according to ANSI/ ESDA/JEDEC JS-002

<sup>4)</sup> according to ANSI/ ESDA/JEDEC JS-001 (discharging 100 pF capacitor through 1.5  $k\Omega$  resistor)

# Single-channel isolated gate-driver ICs in 150 mil DSO package

#### **Electrical characteristics and parameters**

#### 3.2 Thermal characteristics

Table 7 Thermal characteristics at  $T_{\Delta}$  = 25°C

| Parameter                                               | Symbol Values       |      |      |      | Unit | Note or Test Condition |

|---------------------------------------------------------|---------------------|------|------|------|------|------------------------|

|                                                         |                     | Min. | Тур. | Max. |      |                        |

| Thermal resistance junctionambient 1)                   | R <sub>thJA25</sub> | -    | 117  | -    | K/W  | _                      |

| Thermal resistance junction-case (top) <sup>2)</sup>    | R <sub>thJC25</sub> | -    | 54   | -    | K/W  | _                      |

| Thermal resistance junction-board <sup>3)</sup>         | R <sub>thJB25</sub> | -    | 37   | -    | K/W  | _                      |

| Characterization parameter junction-top <sup>4)</sup>   | Ψ <sub>thJT25</sub> | -    | 9    | -    | K/W  | _                      |

| Characterization parameter junction-board <sup>4)</sup> | Ψ <sub>thJB25</sub> | -    | 36   | -    | K/W  |                        |

<sup>1)</sup> obtained by simulating a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a

## 3.3 Operating range

Table 8 Operating range

| Parameter                            | Symbol             | Values |      |      | Unit | Note or Test Condition |

|--------------------------------------|--------------------|--------|------|------|------|------------------------|

|                                      |                    | Min.   | Тур. | Max. |      |                        |

| Input supply voltage                 | $V_{\mathrm{DDI}}$ | 3.0    | -    | 15   | V    | Min. defined by UVLO   |

| Output supply voltage                | $V_{ m DDO}$       | 4.5    | -    | 20   | V    | for 1EDB7275F          |

|                                      |                    | 8.5    | -    | 20   | V    | for 1EDB8275F          |

|                                      |                    | 14.3   | -    | 20   | V    | for 1EDB9275F          |

| Logic input voltage at pins IN+, IN- | V <sub>IN</sub>    | -0.3   | -    | 15   | V    | -                      |

| Junction temperature                 | $T_{J}$            | -40    | -    | 150  | °C   | 1)                     |

| Ambient temperature                  | $T_{A}$            | -40    | -    | 125  | °C   | _                      |

<sup>1)</sup> continuous operation above 125°C may reduce lifetime

<sup>2)</sup> obtained by simulating a cold plate test on the package top. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88

<sup>3)</sup> obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8

<sup>4)</sup> estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $R_{\text{th}}$ , using a procedure described in JESD51-2a (sections 6 and 7)

# Single-channel isolated gate-driver ICs in 150 mil DSO package

## **Electrical characteristics and parameters**

## 3.4 Electrical characteristics

Unless otherwise noted the electrical characteristics are given for  $V_{\rm DDI}$  = 3.3 V,  $V_{\rm DDO}$  = 12 V ( $V_{\rm DDO}$  = 18 V for 1EDB9275F) and no load.

Typical values are given at  $T_J$  = 25°C. Min. and max. values are the lower and upper limits valid within the full operating temperature range.

Table 9 Power supply

| Developer                           | Cumb al            |      | Values |      | Unit | Note ou Took Coundition                              |

|-------------------------------------|--------------------|------|--------|------|------|------------------------------------------------------|

| Parameter                           | Symbol             | Min. | Тур.   | Max. |      | Note or Test Condition                               |

| I <sub>VDDI</sub> quiescent current | I <sub>VDDIq</sub> | _    | 0.85   | 1    | mA   | no switching                                         |

| I <sub>VDDO</sub> quiescent current |                    | 1    | 0.65   | 0.85 | mA   | OUT = low, no switching,<br>V <sub>DDO</sub> = 12 V  |

|                                     | I <sub>VDDOq</sub> | -    | 0.73   | 1.0  | mA   | OUT = low, no switching,<br>V <sub>DDO</sub> = 18 V  |

|                                     |                    | -    | 0.84   | 1.0  | mA   | OUT = high, no switching,<br>V <sub>DDO</sub> = 12 V |

|                                     |                    | -    | 0.97   | 1.1  | mA   | OUT = high, no switching,<br>V <sub>DDO</sub> = 18 V |

Table 10 Undervoltage Lockout V<sub>DDI</sub>

| Davamatav                                                       | Symphol                   |           | Values |      | l lm:4 | Note or               |

|-----------------------------------------------------------------|---------------------------|-----------|--------|------|--------|-----------------------|

| Parameter                                                       | Symbol                    | Min. Typ. |        | Max. | Unit   | <b>Test Condition</b> |

| Undervoltage Lockout (UVLO) turn-on threshold V <sub>DDI</sub>  | UVLO <sub>VDDI,on</sub>   | 2.7       | 2.85   | 3.0  | V      | -                     |

| Undervoltage Lockout (UVLO) turn-off threshold V <sub>DDI</sub> | UVLO <sub>VDDI,off</sub>  | -         | 2.65   | _    | V      | -                     |

| $\overline{\text{UVLO}}$ threshold hysteresis $V_{\text{DDI}}$  | UVLO <sub>VDDI, hys</sub> | 0.15      | 0.2    | 0.25 | V      | _                     |

Table 11 Undervoltage Lockout  $V_{\rm DDO}$  for 1EDB7275F (4 V UVLO option)

| D                                                            | C                         |      | Values |      | 11*4 | Note or<br>Test Condition |

|--------------------------------------------------------------|---------------------------|------|--------|------|------|---------------------------|

| Parameter                                                    | Symbol                    | Min. | Тур.   | Max. | Unit |                           |

| Undervoltage Lockout (UVLO) turn on threshold $V_{\rm DDO}$  | UVLO <sub>VDDO, on</sub>  | 4.0  | 4.2    | 4.4  | V    | -                         |

| Undervoltage Lockout (UVLO) turn off threshold $V_{\rm DDO}$ | UVLO <sub>VDDO, off</sub> | -    | 3.9    | _    | V    | -                         |

| UVLO threshold hysteresis $V_{\rm DDO}$                      | UVLO <sub>VDDO, hys</sub> | 0.2  | 0.3    | 0.4  | V    | -                         |

# Single-channel isolated gate-driver ICs in 150 mil DSO package

# **Electrical characteristics and parameters**

Table 12 Undervoltage Lockout VDDO for 1EDB8275F (8 V UVLO option)

| Parameter                                                    | Symbol                    |      | Values |      | Unit  | Note or        |

|--------------------------------------------------------------|---------------------------|------|--------|------|-------|----------------|

| Parameter                                                    | Symbol                    | Min. | Тур.   | Max. | Oilit | Test Condition |

| Undervoltage Lockout (UVLO) turn on threshold $V_{\rm DDO}$  | UVLO <sub>VDDO, on</sub>  | 7.6  | 8.0    | 8.4  | V     | -              |

| Undervoltage Lockout (UVLO) turn off threshold $V_{\rm DDO}$ | UVLO <sub>VDDO, off</sub> | _    | 7.0    | -    | V     | -              |

| UVLO threshold hysteresis $V_{\rm DDO}$                      | UVLO <sub>VDDO, hys</sub> | 0.7  | 1      | 1.3  | V     | -              |

# Table 13 Undervoltage Lockout VDDO for 1EDB9275F (13 V UVLO option)

| Parameter                                                    | Symbol                    |      | Values |      | Unit | Note or        |

|--------------------------------------------------------------|---------------------------|------|--------|------|------|----------------|

| Parameter                                                    | Symbol                    | Min. | Тур.   | Max. | Unit | Test Condition |

| Undervoltage Lockout (UVLO) turn on threshold $V_{\rm DDO}$  | UVLO <sub>VDDO, on</sub>  | 13.0 | 13.7   | 14.2 | V    | -              |

| Undervoltage Lockout (UVLO) turn off threshold $V_{\rm DDO}$ | UVLO <sub>VDDO, off</sub> | -    | 12.9   | _    | V    | -              |

| UVLO threshold hysteresis V <sub>DDO</sub>                   | UVLO <sub>VDDO, hys</sub> | 0.4  | 0.8    | 1.2  | V    | -              |

# Table 14 Logic inputs IN+, IN-

| D                                              | Completed           |      | Values |      |      | Note or               |

|------------------------------------------------|---------------------|------|--------|------|------|-----------------------|

| Parameter                                      | Symbol              | Min. | Тур.   | Max. | Unit | <b>Test Condition</b> |

| Input voltage threshold for transition LH      | $V_{INH}$           | 1.9  | 2.2    | 2.5  | V    | -                     |

| Input voltage threshold for transition HL      | V <sub>INL</sub>    | 1    | 1.3    | 1.6  | V    | -                     |

| Input voltage threshold hysteresis             | V <sub>IN_hys</sub> | _    | 0.9    | _    | V    | -                     |

| High-level input leakage<br>current at pin IN+ | I <sub>IN+,H</sub>  | _    | 40     | 70   | μΑ   | IN+ tied to VDDI      |

| Low-level input leakage<br>current at pin IN-  | I <sub>IN-,L</sub>  | -55  | -40    | _    | μΑ   | IN- tied to GNDI      |

| Input pull-down resistor                       | $R_{\rm IN,PD}$     | _    | 75     | _    | kΩ   | _                     |

| Input pull-up resistor                         | $R_{\rm IN,PU}$     | -    | 75     | _    | kΩ   | _                     |

# Single-channel isolated gate-driver ICs in 150 mil DSO package

# **Electrical characteristics and parameters**

Table 15 Static output characteristics

| Davameter                                   | Cumbal              | Values |       |      | Unit | Note or                                                                                        |  |

|---------------------------------------------|---------------------|--------|-------|------|------|------------------------------------------------------------------------------------------------|--|

| Parameter                                   | Symbol              | Min.   | Тур.  | Max. | Unit | <b>Test Condition</b>                                                                          |  |

| High-level (sourcing) output resistance     | $R_{\rm on\_SRC}$   | 0.52   | 0.95  | 1.70 | Ω    | I <sub>SNK</sub> = 50 mA                                                                       |  |

| Peak sourcing output current 1)             | 1                   | -      | 5.2   | _    | A    | V <sub>DDO</sub> = 12 V, V <sub>OUT</sub> = 0 V;<br>see <b>Figure 23</b> ,<br><b>Figure 24</b> |  |

|                                             | I <sub>SRC_pk</sub> | _      | 5.6   | _    | A    | $V_{\rm DDO}$ = 18 V, $V_{\rm OUT}$ = 0 V;<br>see <b>Figure 23</b> ,<br><b>Figure 24</b>       |  |

| Low-level (sinking) output resistance       | $R_{ m on\_SNK}$    | 0.31   | 0.48  | 0.88 | Ω    | I <sub>SRC</sub> = 50 mA                                                                       |  |

| Peak sinking output current $^{1)}$ $I_{s}$ |                     | _      | -9.2  | _    | A    | $V_{\rm DDO}$ = 12 V, $V_{\rm OUT}$ = 12 V;<br>see <b>Figure 23</b> ,<br><b>Figure 24</b>      |  |

|                                             | I <sub>SNK_pk</sub> | -      | -10.2 | -    | A    | $V_{\rm DDO}$ = 18 V, $V_{\rm OUT}$ = 18 V;<br>see <b>Figure 23</b> ,<br><b>Figure 24</b>      |  |

<sup>1)</sup> parameter not subject to production test - verified by design / characterization

Table 16 Dynamic characteristics

| Davamatav                                           | Cumhal                      |      | 11   | Note or |      |                                                                           |

|-----------------------------------------------------|-----------------------------|------|------|---------|------|---------------------------------------------------------------------------|

| Parameter                                           | Symbol                      | Min. | Тур. | Max.    | Unit | <b>Test Condition</b>                                                     |

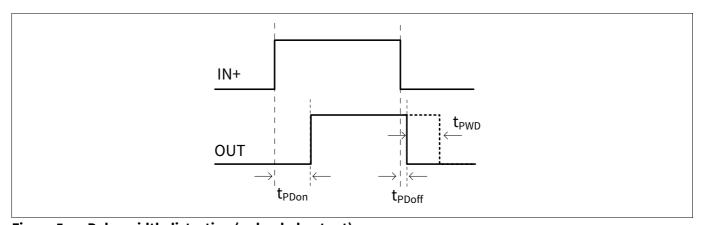

| IN+ /IN- to output propagation delay                | $t_{ m PDon}, t_{ m PDoff}$ | 41   | 45   | 49      | ns   | see <b>Figure 4</b>                                                       |

| Part to part skow                                   | $\Delta t_{PDon,p-p}$       | _    | _    | 2       | ns   | 1)                                                                        |

| Part-to-part skew                                   | $\Delta t_{PDoff,p-p}$      | -    | -    | 2       | ns   | 1)                                                                        |

| Pulse width distortion $ t_{PDoff} - t_{PDon} ^{2}$ | $t_{PWD}$                   | -    | _    | 2       | ns   | see <b>Figure 5</b>                                                       |

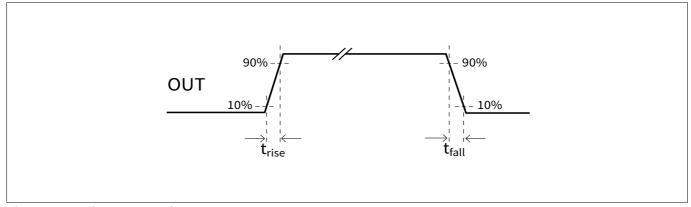

| Rise time <sup>3)</sup>                             | _                           | -    | 6.5  | 12      | ns   | $V_{\rm DDO} = 12 \text{ V}, C_{\rm LOAD} = 1.8 \text{ nF, see Figure 6}$ |

| Rise ume                                            | $t_{rise}$                  | -    | 8.3  | 16      | ns   | $V_{\rm DDO}$ = 18 V, $C_{\rm LOAD}$ = 1.8 nF, see <b>Figure 6</b>        |

| Fall time <sup>3)</sup>                             | 4                           | -    | 4.5  | 8       | ns   | $V_{\rm DDO} = 12 \text{ V}, C_{\rm LOAD} = 1.8 \text{ nF, see Figure 6}$ |

| rall time *                                         | t <sub>fall</sub>           | -    | 5    | 9       | ns   | $V_{\rm DDO} = 18 \text{ V}, C_{\rm LOAD} = 1.8 \text{ nF, see Figure 6}$ |

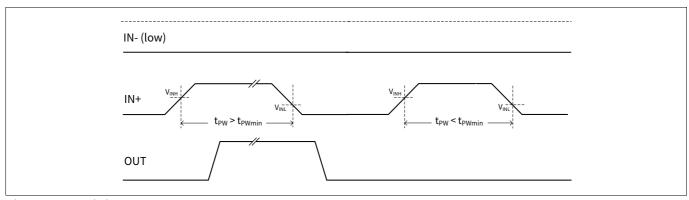

| Minimum input pulse width that changes output state | t <sub>PW</sub>             | 15   | 19   | 23      | ns   | see <b>Figure 7</b>                                                       |

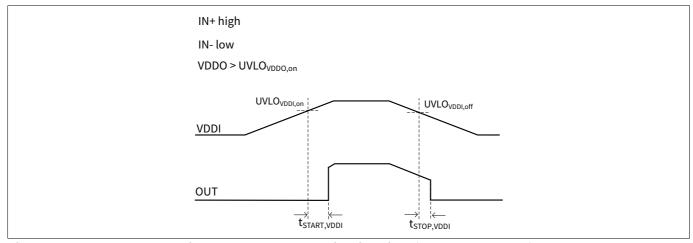

| Input-side start-up time <sup>3)</sup>              | t <sub>START,VDDI</sub>     |      | 3    | -       | μs   | see Figure 8                                                              |

| Input-side deactivation time 3)                     | $t_{STOP,VDDI}$             | -    | 300  | -       | ns   | see Figure 8                                                              |

| Output-side start-up time 3)                        | t <sub>START,VDDO</sub>     | _    | 5    | _       | μs   | see <b>Figure 9</b>                                                       |

#### Single-channel isolated gate-driver ICs in 150 mil DSO package

#### **Electrical characteristics and parameters**

**Table 16 Dynamic characteristics** (cont'd)

| Parameter                                               | Cymphal                |      | Values | l lm:4 | Note or |                       |

|---------------------------------------------------------|------------------------|------|--------|--------|---------|-----------------------|

|                                                         | Symbol                 | Min. | Тур.   | Max.   | Unit    | <b>Test Condition</b> |

| Output-side deactivation time 3)                        | t <sub>STOP,VDDO</sub> | -    | 125    | _      | ns      | see Figure 9          |

| Activation time of output clamping in UVLO condition 3) | t <sub>CLAMP,OUT</sub> | -    | 20     | _      | ns      | see Figure 10         |

<sup>1)</sup> The parameter gives the difference in propagation delay between different samples switching in the same direction under same conditions, including same ambient temperature

Table 17 Common Mode Transient Immunity (CMTI)

| Davamatav                                                  | Symbol                 |     | Values |      | 11                     | 11                                                                                                       | Note or Took Condition |

|------------------------------------------------------------|------------------------|-----|--------|------|------------------------|----------------------------------------------------------------------------------------------------------|------------------------|

| Parameter                                                  |                        |     | Max.   | Unit | Note or Test Condition |                                                                                                          |                        |

| Static Common Mode                                         | CM <sub>Static,H</sub> | 300 | -      | -    | V/ns                   | $V_{\text{CM}} = 1500 \text{ V}$ ; IN- tied to GNDI,<br>IN+ tied to $V_{\text{DDI}}$ (logic high inputs) |                        |

| Transient Immunity 1) 2)                                   | CM <sub>Static,L</sub> | 300 | _      | -    | V/ns                   | $V_{\rm CM}$ = 1500 V; IN- tied to GNDI, IN+ tied to GNDI (logic low inputs)                             |                        |

| Dynamic Common Mode<br>Transient Immunity <sup>1) 3)</sup> | CM <sub>Dynamic</sub>  | 300 | _      | _    | V/ns                   | $V_{\rm CM}$ = 1500 V; IN- tied to GNDI,<br>dynamic IN+ (10 MHz square wave)                             |                        |

<sup>1)</sup> minimum slew rate of a common mode voltage that is able to cause a wrong output signal

<sup>2)</sup> The parameter gives the maximum difference between on and off propagation delay shown from the same sample over the operating temperature range

<sup>3)</sup> parameter not subject to production test - verified by design / characterization

<sup>2)</sup> verified by characterization according to VDE0884-11 standard definitions and test-methods

<sup>3)</sup> verified by characterization with ground reference for the common mode pulse generator connected to the coupler output-side ground to reflect real applications requirements

# Single-channel isolated gate-driver ICs in 150 mil DSO package

## **Electrical characteristics and parameters**

# 3.5 Isolation specifications

Table 18 Input-to-output isolation specifications

|                                    | Parameter                                         | Symbol           | Value | Unit      | Note or Test Condition                                                                                                                                    |

|------------------------------------|---------------------------------------------------|------------------|-------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    | Nominal input-to-output clearance 1)              | CLR              | 4.0   | mm        | Shortest distance in air between any input pin and any output pin                                                                                         |

|                                    | Nominal input-to-output<br>creepage <sup>1)</sup> | CRP              | 4.0   | mm        | Shortest distance over package surface between any input pin and any output pin                                                                           |

| Package<br>characteristics         | Comparative tracking index                        | СТІ              | > 400 | V         | According to DIN EN 60112 (VDE 0303-11)                                                                                                                   |

|                                    | Material group                                    | -                | П     | _         | According to IEC 60112                                                                                                                                    |

|                                    | Overvoltage category                              | -                | I -IV | _         | Rated mains voltage ≤ 150 V <sub>RMS</sub>                                                                                                                |

|                                    |                                                   | _                | 1-111 | _         | Rated mains voltage ≤ 300 V <sub>RMS</sub>                                                                                                                |

|                                    |                                                   | _                | 1-11  | _         | Rated mains voltage ≤ 600 V <sub>RMS</sub>                                                                                                                |

| UL1577 specification <sup>2)</sup> | Input-to-output isolation voltage                 | V <sub>ISO</sub> | 3000  | $V_{RMS}$ | $V_{\text{TEST}} = V_{\text{ISO}}$ for $t = 60$ s (qualification);<br>$V_{\text{TEST}} = 1.2 \times V_{\text{ISO}}$ for $t = 1$ s (100% productive tests) |

<sup>1)</sup> Creepage and clearance requirements depend on the application and related end-equipment isolation standard. Care should be taken to keep the required creepage and clearance value on printed-circuit-board level

<sup>2)</sup> safety certification pending

**Timing diagrams**

# 4 Timing diagrams

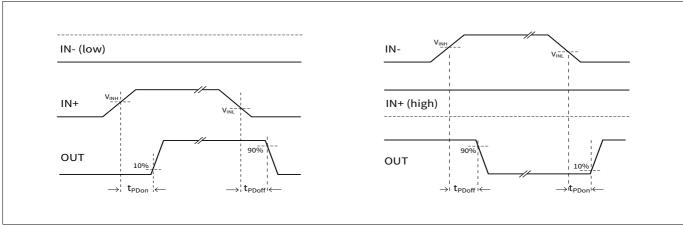

Figure 4 illustrates the input-to-output propagation delays as observed at the capacitively loaded output.

Figure 4 Input-to-output propagation delays (inverting and non-inverting case)

**Figure 6** illustrates the pulse width distortion. It depicts the duty cycle distortion of the signal observed at the driver output due to the mismatch between on and off propagation delay.

Figure 5 Pulse width distortion (unloaded output)

Figure 6 illustrates the rise and fall time as observed at the capacitively loaded output.

Figure 6 Rise and fall times

## Single-channel isolated gate-driver ICs in 150 mil DSO package

## **Timing diagrams**

**Figure 7** illustrates the behavior of the deglitch filter that suppresses input pulses with duration shorter than  $t_{PWmin}$ .

Figure 7 Minimum pulse that changes the output state

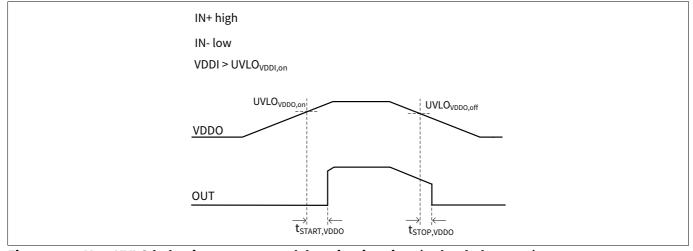

**Figure 8** illustrates the input supply UVLO behavior. It depicts the reaction time to UVLO events when  $V_{\rm DDI}$  crosses the UVLO thresholds during rising or falling transitions (power-up, power-down, supply noise).

Figure 8  $V_{DDI}$  UVLO behavior, start-up and deactivation time (unloaded output)

**Figure 9** illustrates the output supply UVLO behavior. It depicts the reaction time to UVLO events when  $V_{DDO}$  crosses the UVLO thresholds during rising or falling transitions (power-up, power-down, supply noise).

Figure 9  $V_{DDO}$  UVLO behavior, start-up and deactivation time (unloaded output)

# Single-channel isolated gate-driver ICs in 150 mil DSO package

## **Timing diagrams**

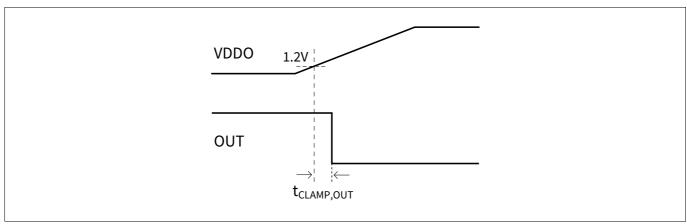

**Figure 10** illustrates  $t_{\text{CLAMP,OUT}}$ , the time required to clamp potential output induced overshoots in UVLO condition ( $V_{\text{DDO}} < \text{UVLO}_{\text{VDDO,on}}$ ).

Figure 10 Activation time of output clamping in UVLO conditions (unloaded output)

#### Single-channel isolated gate-driver ICs in 150 mil DSO package

**Layout recommendation**

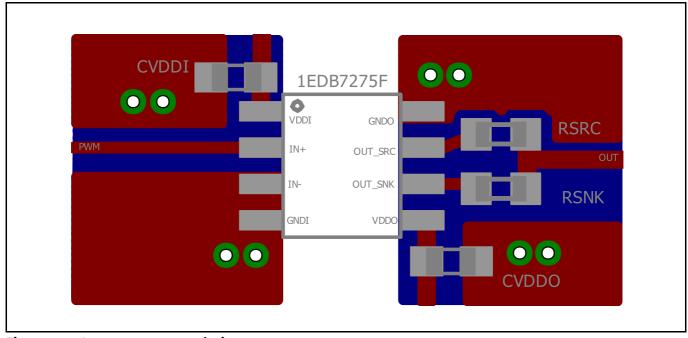

# 5 Layout recommendation

For any fast-switching power system the PCB layout is crucial to achieve optimum performance. Among the many existing rules, recommendations, guidelines, tips and tricks, the ones of highest importance are listed as follow.

- Use low-ESR decoupling capacitances (C<sub>VDDI</sub>, C<sub>VDDO</sub>) and place them as close as possible to the driver to support high peak currents during switching and to ensure stable supply voltages for the driver. The use of PCB planes at ground potential is also recommended to further reduce the inductance to ground.

- Minimize the gate loop inductance by placing the driver as close as possible to the driven transistor and by ensuring that the gate traces are always placed on top of a PCB plane at ground (GNDO) potential. Minimizing the power loop inductance is the key measure to limit voltage overshoots and enable fast switching.

- In case of boostrapping, minimize the boostrap loop inductance to ensure reliable operation and fast bootstrap charge. The boostrap capacitor is, in fact, charged every cycle through the bootstrap diode and the turned-on low-side transistor and the loop is subject to potential high peak charging currents. When this is not possible, use a split bootstrap capacitor with one part placed in some distance of the driver to avoid induced noise; if big enough, this acts as a stable supply for the high-side driver decoupling capacitance (placed close to the driver).

- Pay attention to keep any source of noise (like half-bridge high-current switching traces) away from the driver to avoid any coupling capacitance.

- According to the application requirements, pay attention to keep the needed input-to-output clearance and

creepage on PCB level. To fully benefits from the isolation capabilities of the driver, any trace or plane below

the device must be strictly avoided.

- Connect the driver ground pin to proper PCB planes to reduce the junction-to-board resistance and support the spread of heat outside the driver

A layout recommendation for EiceDRIVER™ 1EDBx275F is given in Figure 11.

Figure 11 Layout recommendation

**Application notes**

# 6 Application notes

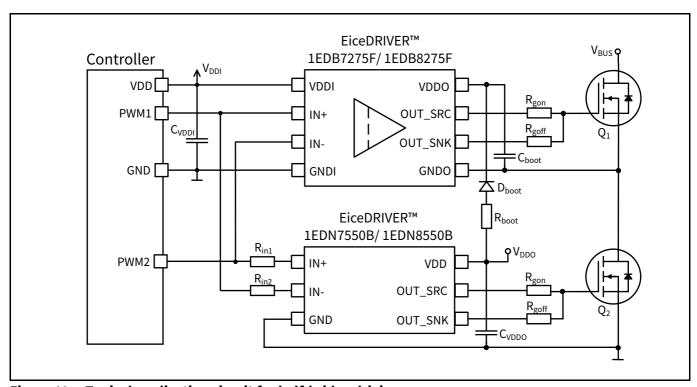

Due to the input-to-output isolation, EiceDRIVER™ 1EDBx275F is best suited for use as high-side driver. In particular, the combination with **EiceDRIVER™ 1EDNx550B** (single-channel gate driver with true differential inputs), is best suited for half-bridge driving due to perfect matching in timing performances and output capability.

By making use of the drivers inverting and non-inverting inputs, shoot-through protection can be implemented as depicted in **Figure 12**; any undesired overlap of low-side and high-side PWM signals is not propagated at the transistors input.

This solution is preferable compared to dual-channel gate drivers in case of high-power or high-frequency designs; here minimizing the gate loop may become a critical requirement that can be more easily fulfilled by using single-channel solutions.

Figure 12 Typical application circuit for half-bridge driving

The high CMTI of 300 V/ns, in conjunction with the ability to drive 4-pin Kelvin source transistors, makes the combination 1EDBx275F, 1EDNx550B ideal to drive GaN and SiC power switches.

# 6.1 Driving 600 V CoolGaN™

**Figure 13** depicts a 1EDB7275F typical use case driving Infineon's 600V GaN power switches (CoolGaN<sup>TM</sup>). The example shows a soft-switching topology; here, due to acceptable switching speed, unipolar driving is possible without risk of false triggering of the devices due to switching induced overshoots.

Details of component dimensioning can be found in the **EiceDRIVER™ 1EDi-GaN** product family datasheet.

## Single-channel isolated gate-driver ICs in 150 mil DSO package

#### **Application notes**

Figure 13 Typical application circuit for 600 V CoolGaN<sup>™</sup> driving

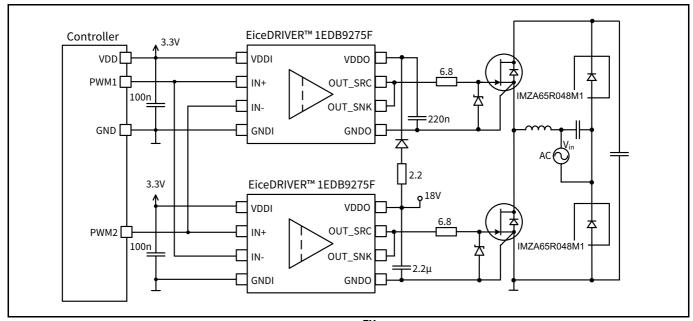

# 6.2 Driving 650 V CoolSiC<sup>TM</sup>

**Figure 14** depicts a typical use case for 600V Infineon's SiC power switches (CoolSiC<sup>TM</sup>) in a so-called "totempole" PFC. It consists of a 48mΩ SiC half-bridge controlled by two 1EDB9275F EiceDRIVER<sup>TM</sup>; the diode functions indicated in the power path are usually realized with low-RDSON MOSFETs operating as synchronous rectifiers. 3.3 kW of power can be handled at very high efficiency (above 99%).

Considering a typical 18 V gate-to-source voltage driving, EiceDRIVER $^{\text{TM}}$  1EDB9275F offers an output UVLO level fitting for 650 V CoolSiC $^{\text{TM}}$ . With a typical UVLO<sub>VDDO,off</sub> of 12.9 V, 1EDB9275F ensures that even in an unsupplied case the transistor (e.g. IMZA65R048M1H in a 3.3kW totem-pole PFC) stays within the Safe Operating Area (SOA) with acceptable power dissipation.

In **Figure 14** a Schottky diode at the CoolSiC<sup>TM</sup> gate is recommended to clamp switching induced undershoots on the gate terminal which may cause a potential drift in the gate threshold voltage  $V_{\rm gs,th}$  over lifetime.

Figure 14 Typical application circuit for 650 V CoolSiC<sup>™</sup> driving

# 7 Typical characteristics

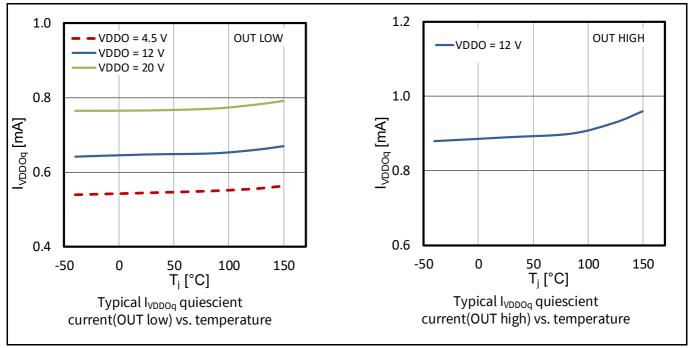

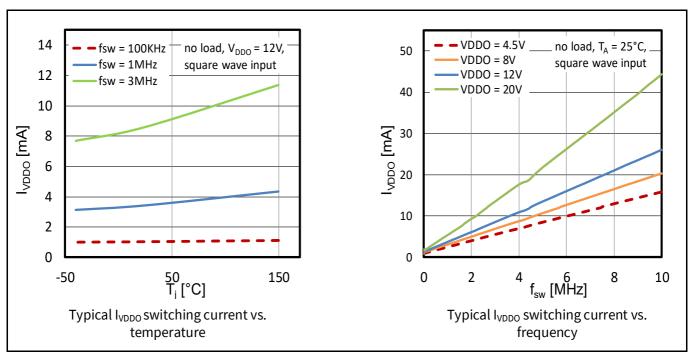

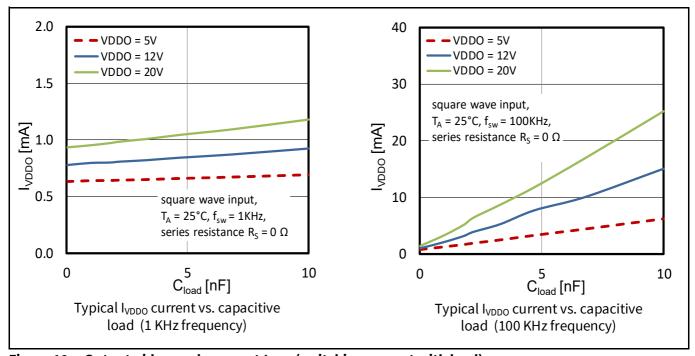

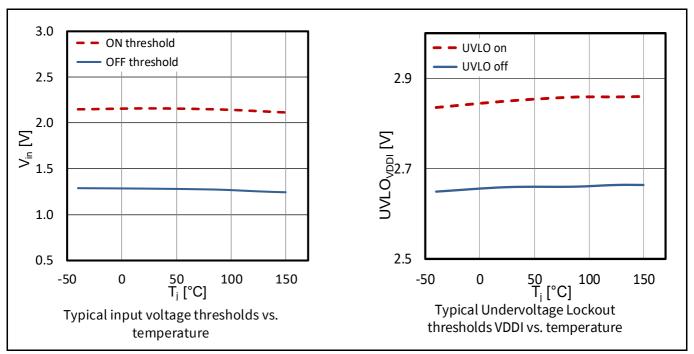

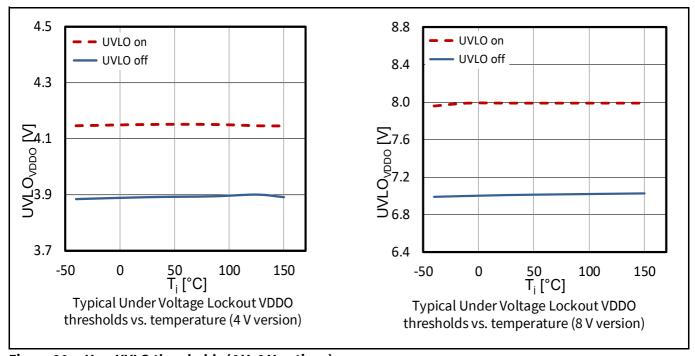

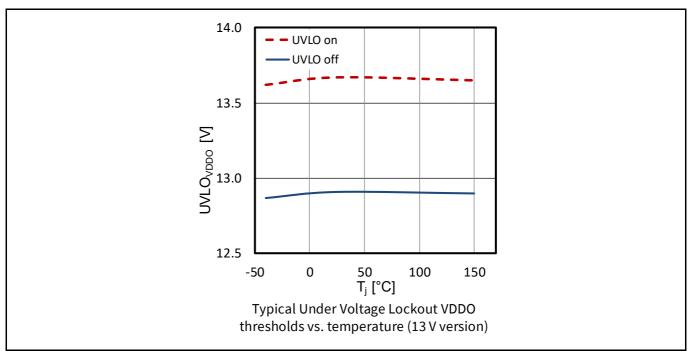

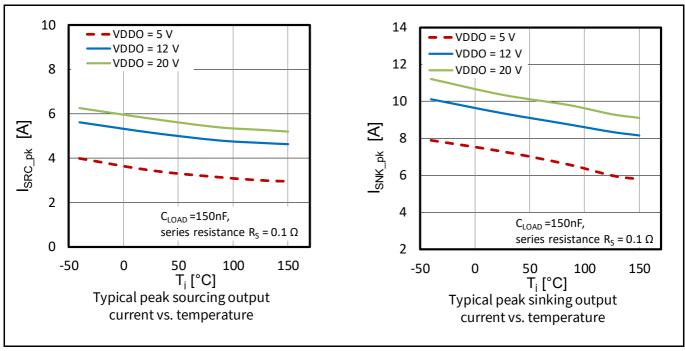

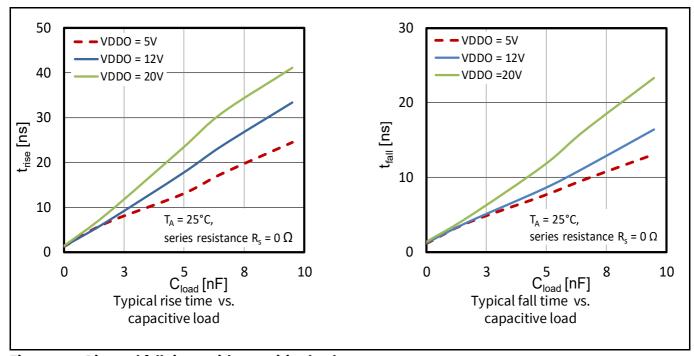

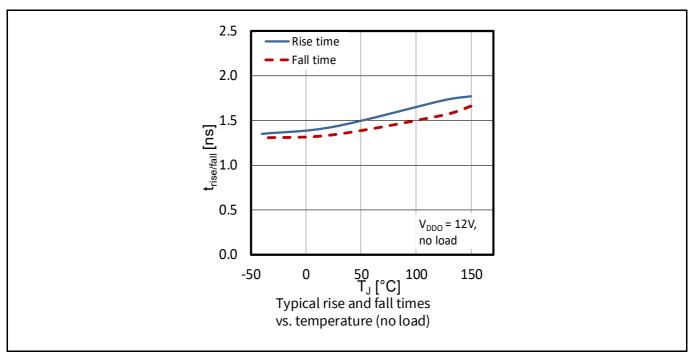

$V_{\rm DDI}$  = 3.3 V,  $V_{\rm DDO}$  = 12 V,  $T_{\rm A}$  = 25°C,  $f_{\rm sw}$ = 1MHz, no load unless otherwise noted.

Figure 15 Input-side supply current I<sub>VDDIq</sub> (quiescent and switching current)

Figure 16 Output-side supply current I<sub>VDDOq</sub> (quiescent current)

Figure 17 Output-side supply current I<sub>VDDO</sub> (switching current without load)

Figure 18 Output-side supply current  $I_{VDDO}$  (switching current with load)

Figure 19 Logic input thresholds and  $V_{\rm DDI}$  UVLO thresholds

Figure 20 V<sub>DDO</sub> UVLO thresholds (4 V, 8 V options)

Figure 21 V<sub>DDO</sub> UVLO thresholds (13 V options)

Figure 22 Output resistance and propagation delay

Figure 23 Source and sink current with output voltage

Figure 24 Peak source and sink current with supply voltage

Peak source and sink current with temperature Figure 25

Figure 26 Rise and fall times with capacitive load

# Single-channel isolated gate-driver ICs in 150 mil DSO package

Figure 27 Rise and fall times with temperature

Package outline dimensions

#### **Package outline dimensions** 8

#### **Device numbers and markings** 8.1

Table 19 **Device numbers and markings**

| Part number | Orderable part number (OPN) | Device marking |

|-------------|-----------------------------|----------------|

| 1EDB7275F   | 1EDB7275FXUMA1              | 1B7275A        |

| 1EDB8275F   | 1EDB8275FXUMA1              | 1B8275A        |

| 1EDB9275F   | 1EDB9275FXUMA1              | 1B9275A        |

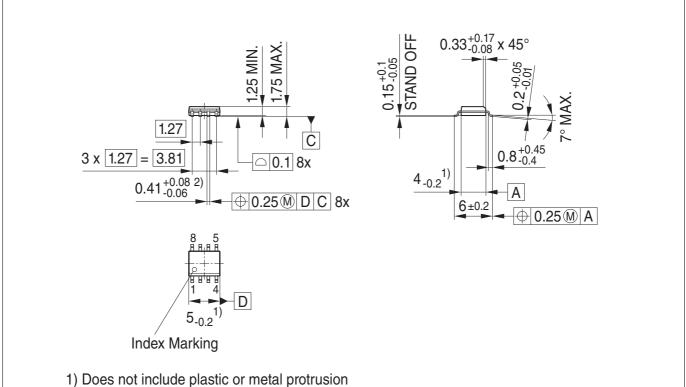

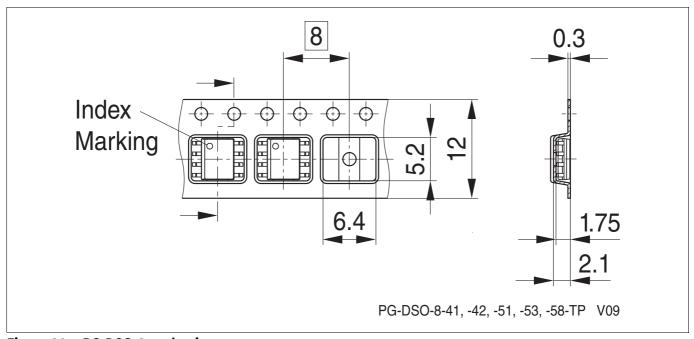

#### Package PG-DSO-8 8.2

- 2) Does not include dambar protrusion of 0.127 max. in excess of the lead width dimension

PG-DSO-8-41, -42, -51, -53, -58-PO V06

Figure 28 PG-DSO-8 outline<sup>1)</sup>

Dimensions in mm

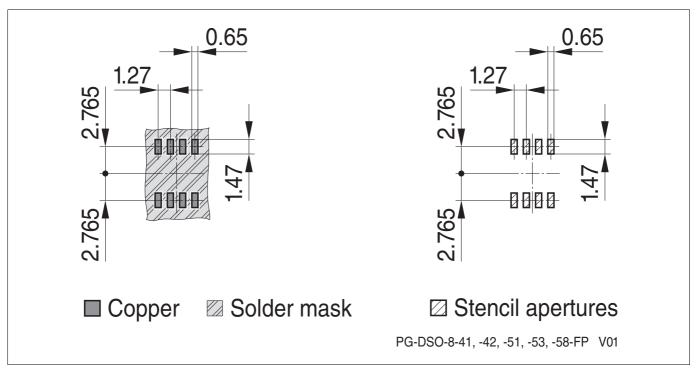

## **Package outline dimensions**

Figure 29 PG-DSO-8 footprint

Figure 30 PG-DSO-8 packaging

#### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pbfree finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

28

#### **Further information on packages**

Final Data Sheet

https://www.infineon.com/packages

# Single-channel isolated gate-driver ICs in 150 mil DSO package

# **Revision history**

| Page or Item         | Subjects (major changes since previous revision) |  |  |  |  |  |

|----------------------|--------------------------------------------------|--|--|--|--|--|

| Rev. 2.0, 2020-04-08 |                                                  |  |  |  |  |  |

|                      | Final datasheet created                          |  |  |  |  |  |

#### **Trademarks of Infineon Technologies AG**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2020-04-08 Published by Infineon Technologies AG 81726 Munich, Germany

© 2020 Infineon Technologies AG. All Rights Reserved.

Do you have a question about any aspect of this document?

Email: erratum@infineon.com

Document reference EiceDRIVER™ 1EDBx275F

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Infineon:

1EDB9275FXUMA1