#### iSSI20R02H, iSSI20R03H, iSSI20R11H, iSSI30R11H, iSSI30R12H Infineon's coreless-transformer advanced solid-state isolators

#### Features

- Solid-state isolators using Infineon's coreless-transformer technology

- No isolated gate bias supply required for gate driving

- Perfect match for CoolMOS<sup>™</sup>, OptiMOS<sup>™</sup>, and TRENCHSTOP<sup>™</sup> IGBT

- Low power, large input voltage range from 2.6 V to 3.5 V (internally clamped)

- High-impedance, CMOS input (buffered variants)

- High output voltage up to 18 V no series or parallel configuration required for powerful gate driving

- High output peak current of 185 µA (direct drive variants) or 400 mA (buffered variants)

- Fast turn-off for safe switches' SOA operation

- Temperature sensor and current sensor protection inputs

- Latch-off in case of a failure event (overcurrent or over-temperature)

- Dynamic Miller clamping protection

- Wide-body package with high creepage and clearance for UL 1577 (planned) and reinforced isolation according to IEC 60747-17 (planned)

#### **Potential applications**

- Solid-state relay AC and DC applications

- Electro-mechanical relay replacements

- Programmable logic control, industrial automation, and controls

- Smart building and home automation systems (thermostat, lighting, heating control)

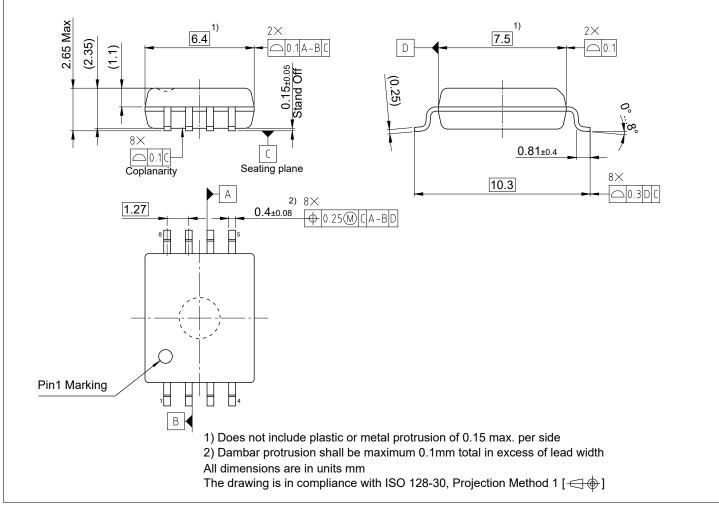

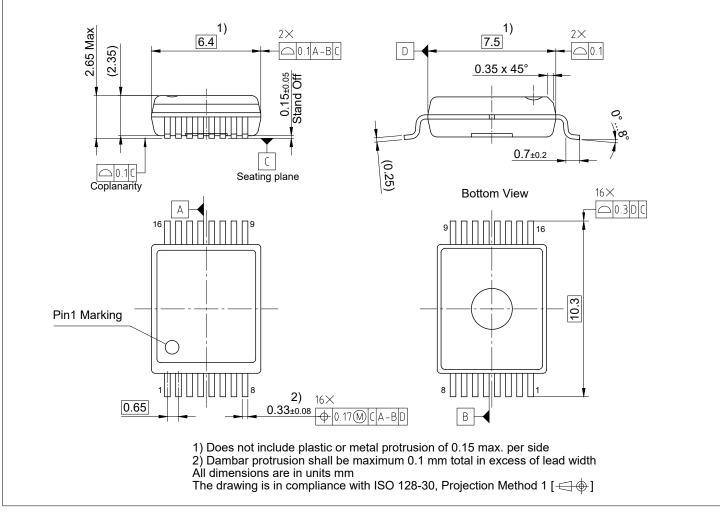

PG-DSO-16-33

#### **Product validation**

Qualified for industrial applications according to relevant tests of JEDEC47/20/22.

#### Description

The iSSI solid-state isolator family provides powerful energy transmission over a galvanic isolation barrier to drive the gates of MOS-controlled power transistors, such as CoolMOS<sup>™</sup>, OptiMOS<sup>™</sup>, TRENCHSTOP<sup>™</sup> IGBT, or CoolSiC<sup>™</sup>. The output side of the iSSI solid-state isolator family does not require a dedicated voltage supply to drive the power transistor's gate. The output side offers advanced control functions such as fast turn-on, fast turn-off, overcurrent protection and over-temperature protection to easily and safely build up solid-state relays for various applications. The iSSI family includes iSSI30R12H which is tailored for CoolMOS<sup>™</sup> S7 T-sense power MOSFETs offering an integrated temperature sensor. Other parts of the family are for use with external PTC resistors. The iSSI family offers precise protection functions for building cost effective systems. The input side of the isolator is 3.3 V compatible and operates with a supply current of typically 16 mA.

The variants iSSI20R02H, iSSI20R03H, and iSSI20R11H come in a DSO-8-66 package while iSSI30R11H and iSSI30R12H come in a DSO-16-33 package.

The isolation is IEC 60747-17 (planned) certified for reinforced isolation and UL 1577 (planned) compliant.

Description

| Product type | <b>Protection features</b> | Fast turn-on | Certification (planned) | Marking | Package      |

|--------------|----------------------------|--------------|-------------------------|---------|--------------|

| iSSI20R02H   | OCP or OTP (PTC), DMC      | No           | IEC 60747-17, UL1577    | I20R02  | PG-DSO-8-66  |

| iSSI20R03H   | OCP, OTP (PTC)             | No           | IEC 60747-17, UL1577    | I20R03  | PG-DSO-8-66  |

| iSSI20R11H   | OCP or OTP (PTC)           | Yes          | IEC 60747-17, UL1577    | I20R11  | PG-DSO-8-66  |

| iSSI30R11H   | OCP, OTP (PTC), DMC        | Yes          | IEC 60747-17, UL1577    | I30R11  | PG-DSO-16-33 |

| iSSI30R12H   | OCP, OTP (diode), DMC      | Yes          | IEC 60747-17, UL1577    | I30R12  | PG-DSO-16-33 |

Table of contents

## **Table of contents**

|       | Features                                                    |

|-------|-------------------------------------------------------------|

|       | Potential applications                                      |

|       | Product validation                                          |

|       | Description                                                 |

|       | Table of contents    3                                      |

| 1     | Block diagrams                                              |

| 2     | Pin configuration                                           |

| 2.1   | Pin configuration                                           |

| 2.2   | Pin description                                             |

| 3     | Electrical characteristics and parameters                   |

| 3.1   | Absolute maximum ratings                                    |

| 3.2   | Operating parameters                                        |

| 3.3   | Electrical characteristics                                  |

| 3.3.1 | IC Supply                                                   |

| 3.3.2 | Logic input (iSSI20R11H, iSSI30R11H, iSSI30R12H) 13         |

| 3.3.3 | Gate drive                                                  |

| 3.3.4 | Fast turn-on (iSSI20R11H, iSSI30R11H, iSSI30R12H)14         |

| 3.3.5 | Dynamic Miller clamping                                     |

| 3.3.6 | Over-temperature protection                                 |

| 3.3.7 | Overcurrent protection                                      |

| 4     | Insulation and safety-related specification16               |

| 4.1   | Safety-limiting values                                      |

| 4.2   | Reinforced insulation according to IEC 60747-17 (planned)16 |

| 5     | Timing diagrams                                             |

| 6     | Functional description                                      |

| 6.1   | Input side                                                  |

| 6.1.1 | Input side supply                                           |

| 6.1.2 | Logic input                                                 |

| 6.2   | Output side                                                 |

| 6.2.1 | Direct gate drive                                           |

| 6.2.2 | Fast turn-on feature    21                                  |

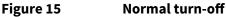

| 6.2.3 | Normal turn-off                                             |

| 6.2.4 | Fast turn-off                                               |

| 6.2.5 | Dynamic Miller clamping (DMC)                               |

| 6.2.6 | Overcurrent protection                                      |

| 6.2.7 | Over-temperature protection                                 |

Table of contents

| 7   | Application information                                       |

|-----|---------------------------------------------------------------|

| 7.1 | Adaptation of the supply voltage                              |

| 7.2 | Grounding reference of current and temperature sensor signals |

| 7.3 | Fast turn-on using iSSI20R11H and iSSI30R1xH 27               |

| 7.4 | Using the overcurrent protection                              |

| 7.5 | Using the dynamic Miller clamping 29                          |

| 7.6 | Inductive energy clamping methods                             |

| 8   | Related products                                              |

| 9   | Package dimensions    32                                      |

| 9.1 | Package outline                                               |

|     | <b>Revision history</b>                                       |

|     | <b>Disclaimer</b>                                             |

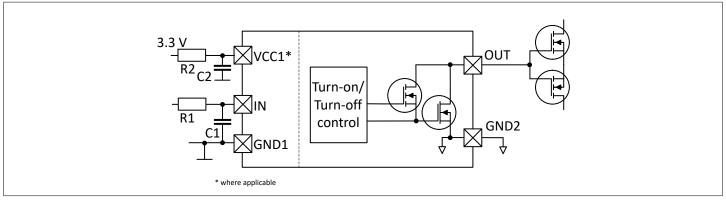

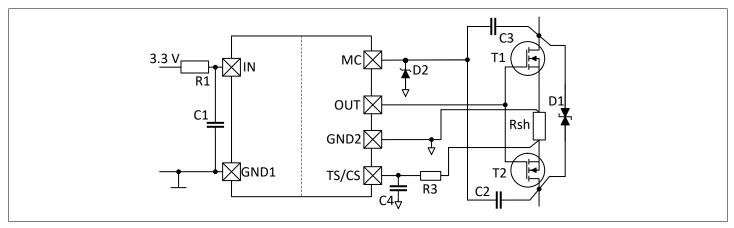

1 Block diagrams

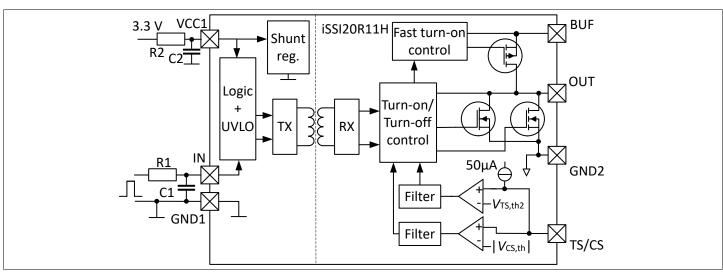

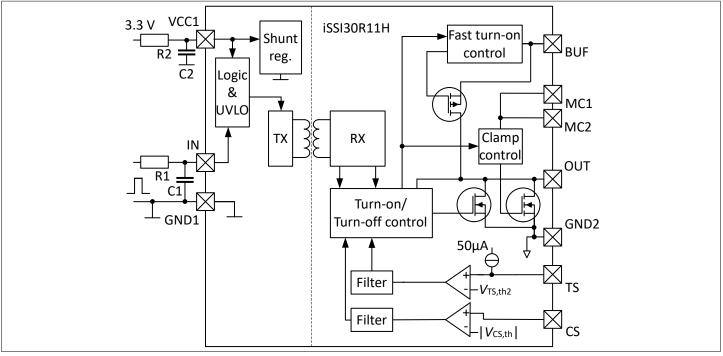

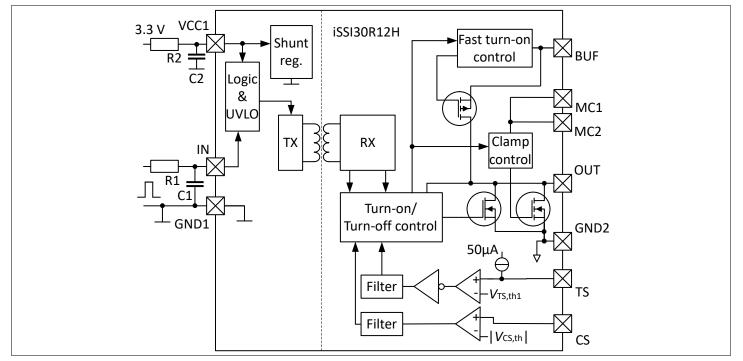

1

## Block diagrams

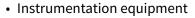

Block diagram of iSSI20R02H

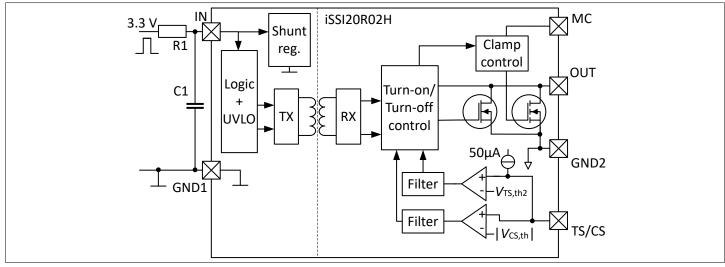

Block diagram of iSSI20R03H

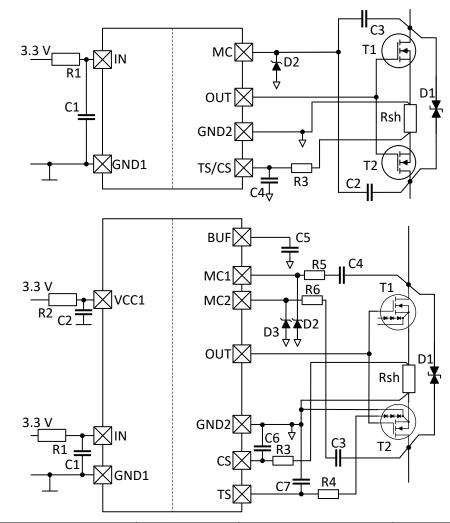

Block diagram of iSSI20R11H

1 Block diagrams

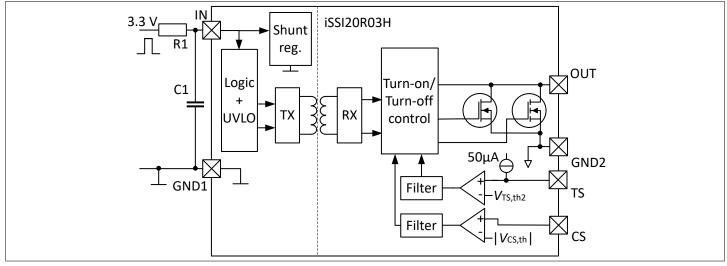

Block diagram of iSSI30R11H

Block diagram of iSSI30R12H

2 Pin configuration

#### **Pin configuration** 2

#### **Pin configuration** 2.1

| 1 | о<br>N.C. | iSSI20R02H | Ουτ   | 8 | 1 | o<br>N.C. | iSSI20R03H               | OUT  | 8        |

|---|-----------|------------|-------|---|---|-----------|--------------------------|------|----------|

| 2 | IN        |            | TS/CS | 7 | 2 | IN        |                          | CS   | 7        |

| 3 | N.C.      |            | мс    | 6 | 3 | N.C.      |                          | TS   | 6        |

| 4 | GND1      |            | GND2  | 5 | 4 | GND1      |                          | GND2 | 5        |

|   | o<br>VCC1 | iSSI20R11H | ουτ   | 8 |   | O<br>GND1 |                          | GND2 | 16       |

| 2 | IN        |            | TS/CS | 7 | 2 | VCC1      |                          | ουτ  | 15       |

| 3 | N.C.      |            | BUF   | 6 | 3 | IN        |                          | CS   | 14       |

| 4 | GND1      |            | GND2  | 5 | 4 | N.C.      |                          | TS   | 13       |

|   | 1         |            |       |   | 5 | N.C.      |                          | BUF  | 12       |

|   |           |            |       |   | 6 | N.C.      |                          | MC1  | 11       |

|   |           |            |       |   | 7 | N.C.      |                          | MC2  | 10       |

|   |           |            |       |   | 8 | GND1      | iSSI30R11H<br>iSSI30R12H | GND2 | <u> </u> |

#### Pin configuration of iSSI family **Figure 6**

| Table 1 | Pino     | onfiguratio | n for iSSI20R02H                                                       |

|---------|----------|-------------|------------------------------------------------------------------------|

| Pin no. | Pin name | Pin type    | Function                                                               |

| 1       | N.C.     | -           | Not connected                                                          |

| 2       | IN       | PWR         | Supply and non-inverting control input                                 |

| 3       | N.C.     | -           | Not connected                                                          |

| 4       | GND1     | PWR         | Reference of control side                                              |

| 5       | GND2     | PWR         | Reference of output side                                               |

| 6       | МС       | I           | Miller clamp input                                                     |

| 7       | TS/CS    | I/O         | Output for temperature sensor bias current and input for sensed signal |

| 8       | OUT      | 0           | Gate drive output                                                      |

2 Pin configuration

| Table 2   Pin configuration for iSSI20R03H |                            |              |                                                                             |  |  |  |

|--------------------------------------------|----------------------------|--------------|-----------------------------------------------------------------------------|--|--|--|

| Pin no.                                    | Pin name Pin type Function |              |                                                                             |  |  |  |

| 1                                          | N.C.                       | -            | Not connected                                                               |  |  |  |

| 2                                          | IN                         | PWR          | Supply and non-inverting control input                                      |  |  |  |

| 3                                          | N.C.                       | -            | Not connected                                                               |  |  |  |

| 4                                          | GND1                       | PWR          | Reference of control side                                                   |  |  |  |

| 5                                          | GND2                       | PWR          | Reference of output side                                                    |  |  |  |

| 6                                          | TS                         | I/o          | Output for temperature sensor bias current and input for temperature signal |  |  |  |

| 7                                          | CS                         | 1            | Input for current-sense signal                                              |  |  |  |

| 8                                          | OUT                        | 0            | Gate drive output                                                           |  |  |  |

| Table 3                                    | Pino                       | configuratio | n for iSSI20R11H                                                            |  |  |  |

| Pin no.                                    | Pin name                   | Pin type     | Function                                                                    |  |  |  |

| 1                                          | VCC1                       | PWR          | Supply input                                                                |  |  |  |

| 2                                          | IN                         | I            | Non-inverting control input                                                 |  |  |  |

|                                            |                            |              |                                                                             |  |  |  |

| N.C.  | -                            | Not connected                                                          |

|-------|------------------------------|------------------------------------------------------------------------|

| GND1  | PWR                          | Reference of control side                                              |

| GND2  | PWR                          | Reference of output side                                               |

| BUF   | I/O                          | Output for buffer charges and input for fast turn-on                   |

| TS/CS | I/O                          | Output for temperature sensor bias current and input for sensed signal |

| OUT   | 0                            | Gate drive output                                                      |

|       | GND1<br>GND2<br>BUF<br>TS/CS | GND1PWRGND2PWRBUFI/OTS/CSI/O                                           |

Table 4

#### Pin configuration for iSSI30R11H and iSSI30R12H

| Pin name | Pin type                                                                                                                           | Function                                                                                                                                                                                                                                                                  |

|----------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND1     | PWR                                                                                                                                | Reference of control side                                                                                                                                                                                                                                                 |

| VCC1     | PWR                                                                                                                                | Supply input                                                                                                                                                                                                                                                              |

| IN       | 1                                                                                                                                  | Non-inverting control input                                                                                                                                                                                                                                               |

| N.C.     | -                                                                                                                                  | Not connected                                                                                                                                                                                                                                                             |

| GND1     | PWR                                                                                                                                | Reference of control side                                                                                                                                                                                                                                                 |

| GND2     | PWR                                                                                                                                | Reference of output side                                                                                                                                                                                                                                                  |

| MC2      | 1                                                                                                                                  | Dynamic Miller clamp input 1                                                                                                                                                                                                                                              |

| MC1      | I                                                                                                                                  | Dynamic Miller clamp input 2                                                                                                                                                                                                                                              |

| BUF      | I/O                                                                                                                                | Output for buffer charges and input for fast turn-on                                                                                                                                                                                                                      |

|          | GND1         VCC1         IN         N.C.         N.C.         N.C.         M.C.         GND1         GND2         MC2         MC1 | GND1         PWR           VCC1         PWR           IN         I           N.C.         -           N.C.         -           N.C.         -           N.C.         -           M.C.         -           M.C.         1           M.C.         1           MC1         I |

#### (table continues...)

2 Pin configuration

| Table 4 | (con     | tinued) Pin                         | configuration for iSSI30R11H and iSSI30R12H                            |

|---------|----------|-------------------------------------|------------------------------------------------------------------------|

| Pin no. | Pin name | Pin type                            | Function                                                               |

| 13      | TS       | I/O                                 | Output for temperature sensor bias current and input for sensed signal |

| 14      | CS       | CS I Input for current sense signal |                                                                        |

| 15      | OUT      | 0                                   | Gate drive output                                                      |

| 16      | GND2     | PWR                                 | Reference of output side                                               |

#### 2.2 **Pin description**

- VCC1: Supply of input side; best operated with 3.3 V; can be shorted to terminal IN; referenced to GND1. •

- *IN*: Logic input for variants iSSI20R11H, iSSI30R11H and iSSI30R12H, can be shorted to *VCC1*. It is the input supply • pin for variants iSSI20R02H and iSSI20R03H. Pin is referenced to GND1

- GND1: Reference pin for VCC1 and IN.

- GND2: Reference pin for MC, MC1, MC2, CS, TS, TS/CS, OUT and BUF.

- *MC*, *MC1*, *MC2*: Input pins for dynamic Miller clamp. Keep these pins unconnected for deactivating the dynamic Miller clamp. Referenced to GND2.

- CS: Current sense input. When unused, it is recommended to connect to GND2. Referenced to GND2.

- TS: Temperature sense input. When unused, it is recommended for variant iSSI30R12H to let the pin float and for all other variants, it is recommended to connect to GND2. Referenced to GND2.

- TS/CS: Pin can be used either as temperature sense input or as current sense input. When unused, it is recommended to connect to GND2. Referenced to GND2.

- OUT: Gate drive output. Referenced to GND2.

- BUF: Gate drive buffer. Typically, a capacitor is connected to implement the fast turn-on feature. Referenced to GND2.

3 Electrical characteristics and parameters

# 3 Electrical characteristics and parameters

### 3.1 Absolute maximum ratings

#### Table 5Absolute maximum ratings

| Parameter                                                         | Symbol                                                  |       | Values | ;    | Unit | Note or condition                                                                                                               |  |

|-------------------------------------------------------------------|---------------------------------------------------------|-------|--------|------|------|---------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                   |                                                         | Min.  | Тур.   | Max. | 1    |                                                                                                                                 |  |

| Input to output offset voltage                                    | V <sub>OFFSET</sub>                                     | -1200 | -      | 1200 | V    | $V_{\text{offset}} =  V_{\text{GND1}} - V_{\text{GND2}} ^{1}$                                                                   |  |

| Input supply voltage                                              | V <sub>IN</sub>                                         | -10   | -      | 4.25 | V    | iSSI20R02H, iSSI20R03H                                                                                                          |  |

|                                                                   | V <sub>VCC1</sub>                                       |       |        |      |      | iSSI20R11H, iSSI30R11H, iSSI30<br>R12H                                                                                          |  |

| Input logic voltage (terminal IN)                                 | V <sub>IN,logic</sub>                                   | -10   | -      | 15   | V    | Reference to GND1                                                                                                               |  |

| Output voltage at terminal OUT                                    | V <sub>OUT</sub>                                        | -0.3  |        | 20   | V    | 2)                                                                                                                              |  |

| Voltage at terminal MC                                            | V <sub>MC</sub>                                         | -0.3  |        | 3.6  | V    | 2)                                                                                                                              |  |

| Voltage at terminals TS, CS or TS/CS (static)                     | V <sub>TS</sub> , V <sub>CS</sub><br>V <sub>TS/CS</sub> | -1.2  |        | 4    | V    | 2)                                                                                                                              |  |

| Voltage at terminals CS, TS and TS/CS (positive signals, dynamic) | V <sub>pin,dyn</sub>                                    | 0     | -      | 6    | V    | <sup>2)</sup> $0 < I_{pin,dyn} < 10$ mA, $t_p < 2$ µs,<br>d < 0.001                                                             |  |

| Voltage at terminals CS, TS and TS/CS (negative signals, dynamic) | V <sub>pin,dyn</sub>                                    | -2    | -      | 0    | V    | <sup>2)</sup> $0 > I_{pin,dyn} > -10$ mA, $t_p < 2 \mu s$ ,<br>d < 0.001                                                        |  |

| Voltage at terminal BUF                                           | V <sub>BUF</sub>                                        | -0.3  |        | 20   | V    | 2)                                                                                                                              |  |

| Input supply current                                              | I <sub>IN</sub><br>I <sub>VCC1</sub>                    | 0     | -      | 120  | mA   | iSSI20R02H, iSSI20R03H<br>iSSI20R11H, iSSI30R11H,<br>iSSI30R12H                                                                 |  |

| Current at terminal OUT (static)                                  | I <sub>OUT</sub>                                        | -10   |        | 10   | mA   | Output deactivated                                                                                                              |  |

| Current at terminal OUT (dynamic)                                 | I <sub>OUT,dyn</sub>                                    | -100  | -      | 100  | mA   | Output deactivated; t <sub>p</sub> < 10 μs<br>for negative current pulses; t <sub>p</sub> <<br>1 μs for positive current pulses |  |

| Current at terminal MC (static)                                   | I <sub>MC</sub>                                         | -6    |        | 6    | mA   | 2)                                                                                                                              |  |

| Current at terminal MC (dynamic)                                  | I <sub>MC,dyn</sub>                                     | -100  |        | 100  | mA   | t <sub>p</sub> < 1 μs; d < 1%                                                                                                   |  |

| Current at terminal TS                                            | I <sub>TS</sub>                                         | -1    |        | 1    | mA   | 2)                                                                                                                              |  |

| Current at terminal CS or TS/CS                                   | I <sub>CS</sub> , I <sub>TS/CS</sub>                    | -1    |        | 1    | mA   | 2)                                                                                                                              |  |

| Current at terminal BUF (static)                                  | I <sub>BUF</sub>                                        | -10   |        | 10   | mA   |                                                                                                                                 |  |

| Current at terminal BUF (dynamic)                                 | I <sub>BUF,dyn</sub>                                    | -1    |        | 1    | A    | t <sub>p</sub> < 1 μs                                                                                                           |  |

| Power dissipation input part                                      | P <sub>DIN</sub>                                        |       |        | 200  | mW   | $T_{\rm A} = 85^{\circ} {\rm C}^{-3/-4}$                                                                                        |  |

| Power dissipation output part                                     | P <sub>DOUT</sub>                                       |       |        | 4.5  | mW   | $T_{\rm A} = 85^{\circ} {\rm C}^{-5/6}$                                                                                         |  |

| Thermal resistance junction-to-<br>ambient                        | R <sub>THJA</sub>                                       |       |        | 140  | K/W  | $T_{\rm A}$ = 85°C, PG DSO-8-66, 2s2p<br>footprint only                                                                         |  |

| (table continues )                                                |                                                         |       |        | 96   |      | $T_{\rm A}$ = 85°C, PG DSO-16-33, 2s2p<br>footprint only                                                                        |  |

(table continues...)

3 Electrical characteristics and parameters

#### Table 5 (continued) Absolute maximum ratings

| Parameter                                          | Symbol               |      | Values |            |     | Note or condition                                                                                                 |

|----------------------------------------------------|----------------------|------|--------|------------|-----|-------------------------------------------------------------------------------------------------------------------|

|                                                    |                      | Min. | Тур.   | Max.       |     |                                                                                                                   |

| Characterization parameter junction-to-package top | $\Psi_{Jtop}$        |      |        | 39.77      | K/W | <i>T</i> <sub>A</sub> = 85°C, PG-DSO-8-66, 2s2p footprint only                                                    |

|                                                    |                      |      |        | 35.30      |     | $T_A = 85^{\circ}$ C, PG-DSO-16-33, 2s2p footprint only                                                           |

| ESD robustness - human body<br>model               | V <sub>ESD,HBM</sub> | 2    |        |            | kV  | 7)                                                                                                                |

| ESD robustness - charged device<br>model           | ESD,CDM              | -    | -      | TC<br>1000 | -   | 8)                                                                                                                |

| Junction temperature                               | TJ                   | -40  |        | 150        | °C  |                                                                                                                   |

| Storage temperature                                | T <sub>ST</sub>      | -55  |        | 150        | °C  |                                                                                                                   |

| Maximum switching frequency                        | f <sub>SW</sub>      | -    | -      | 2          | kHz | $C_{\text{Load}} = 100 \text{ pF}, V_{\text{IN}} = 3.3 \text{ V}, V_{\text{VCC1}}$<br>= 3.3 V (where appropriate) |

1) For functional operation only

2) Reference to GND2.

3) PG-DSO-8-66: derating of power above  $T_i = 122^{\circ}$ C with 7.14 mW/°C, layout 2s2p (JESD 51-5 / JESD 51-7).

4) PG-DSO-16-33: derating of power above  $T_j = 130.8^{\circ}$ C with 10.42 mW/°C, layout 2s2p (JESD 51-5 / JESD 51-7).

5) PG-DSO-8-66: derating of power above  $T_j = 149.3^{\circ}$ C with 7.14 mW/°C, layout 2s2p (JESD 51-5 / JESD 51-7).

6) PG-DSO-16-33: derating of power above  $T_j = 149.5^{\circ}$ C with 10.42 mW/°C, layout 2s2p (JESD 51-5 / JESD 51-7).

7) According to ANSI/ESDA/JEDEC-JS-001-2017 (discharging a 100 pF capacitor through a 1.5 k $\Omega$  series resistor).

8) According to ANSI/ESDA/JEDEC-JS-002-2014 (TC = highest test condition passed according to AEC-Q100-011 Rev D).

|                          |                           | 70 μm as shown on left<br>35 μm 90 % metallization<br>35 μm 90 % metallization<br>70 μm 5% metallization |  |

|--------------------------|---------------------------|----------------------------------------------------------------------------------------------------------|--|

| Solder pads for DSO-8-66 | Solder pads for DSO-16-33 | PCB stack design                                                                                         |  |

Figure 7 Thermal reference design

#### **3.2 Operating parameters**

#### Table 6Operating parameters

| Parameter                                                         | Symbol                                                  |      | Values |      |   | Note or condition |

|-------------------------------------------------------------------|---------------------------------------------------------|------|--------|------|---|-------------------|

|                                                                   |                                                         | Min. | Тур.   | Max. |   |                   |

| Input supply voltage (terminal VCC1<br>(or IN if VCC1 is absent)) | V <sub>VCC1</sub>                                       | 2.85 | 3.3    | 3.5  | V | -                 |

| Voltage at terminals TS, CS, or<br>TS/CS (static)                 | V <sub>TS</sub> , V <sub>CS</sub><br>V <sub>TS/CS</sub> | -0.5 |        | 2.7  | V | 1)                |

(table continues...)

3 Electrical characteristics and parameters

#### Table 6(continued) Operating parameters

| Symbol                |                                                         | Values                                              | •                                                                                   | Unit                                                                                                                        | Note or condition                                                                                                                                               |

|-----------------------|---------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | Min.                                                    | Тур.                                                | Max.                                                                                |                                                                                                                             |                                                                                                                                                                 |

| C <sub>VCC1,ext</sub> | -                                                       | -                                                   | 4.7                                                                                 | nF                                                                                                                          |                                                                                                                                                                 |

| C <sub>TS,ext</sub>   | -                                                       | -                                                   | 1.5                                                                                 | nF                                                                                                                          |                                                                                                                                                                 |

| T <sub>A</sub>        | -40                                                     | -                                                   | 125                                                                                 | °C                                                                                                                          | -                                                                                                                                                               |

| TJ                    | -40                                                     | -                                                   | 125                                                                                 | °C                                                                                                                          | _                                                                                                                                                               |

| dv <sub>CM</sub> /dt  |                                                         |                                                     | 200                                                                                 | V/ns                                                                                                                        |                                                                                                                                                                 |

|                       | C <sub>TS,ext</sub><br>T <sub>A</sub><br>T <sub>J</sub> | $C_{VCC1,ext}$ - $C_{TS,ext}$ - $T_A$ -40 $T_J$ -40 | $C_{VCC1,ext}$ -       - $C_{TS,ext}$ -       - $T_A$ -40       - $T_J$ -40       - | $C_{VCC1,ext}$ -       -       4.7 $C_{TS,ext}$ -       -       1.5 $T_A$ -40       -       125 $T_J$ -40       -       125 | $C_{VCC1,ext}$ -       -       4.7       nF $C_{TS,ext}$ -       -       1.5       nF $T_A$ -40       -       125       °C $T_J$ -40       -       125       °C |

### 3.3 Electrical characteristics

The electrical characteristics include the spread of values over supply voltages and temperatures within the operating parameters. Electrical characteristics are tested in production at  $T_A = 25^{\circ}$ C and the default load at terminal OUT is 100 pF. Typical values represent the median values measured at supply voltage  $V_{IN} = 3.3 \text{ V}$  (or  $V_{VCC1} = 3.3 \text{ V}$  where applicable) and  $T_A = 25^{\circ}$ C. Minimum and maximum characteristics are verified by characterization/design. All voltages are referenced to their respective GND (GND1 for input side pins and GND2 for output side pins). This is valid for all electrical characteristics unless specified otherwise.

### 3.3.1 IC Supply

#### Table 7 IC Supply

| Parameter                                                                | Symbol                                       |           | Values |      | Unit | Note or condition                                                                                                             |

|--------------------------------------------------------------------------|----------------------------------------------|-----------|--------|------|------|-------------------------------------------------------------------------------------------------------------------------------|

|                                                                          |                                              | Min.      | Тур.   | Max. |      |                                                                                                                               |

| UVLO threshold input side (power<br>up)                                  | V <sub>UVLOH1</sub>                          | 2.7       | 2.775  | 2.85 | V    |                                                                                                                               |

| UVLO threshold input side (power<br>down)                                | V <sub>UVLOL1</sub>                          | 2.6       | 2.68   | 2.75 | V    | Reference to GND1                                                                                                             |

| UVLO hysteresis input side                                               | V <sub>HYS1</sub>                            | 89        | -      | -    | mV   | <sup>1)</sup> V <sub>UVLOH1</sub> - V <sub>UVLOL1</sub>                                                                       |

| Supply current input side at<br>terminal IN (or VCC1 where<br>available) | I <sub>IN</sub>                              | 14        | 16     | 19   | mA   | V <sub>IN</sub> = 3.3 V, <i>I</i> <sub>OUT</sub> = 0                                                                          |

| Standby input supply current at<br>terminal VCC1                         | I <sub>IN,STBY</sub>                         | -         | 1.4    | 2.5  | mA   | V <sub>VCC1</sub> = 3.3 V, V <sub>IN</sub> = 0                                                                                |

| Integrated supply bias resistance                                        | R <sub>VCC1,bias</sub>                       | 2.45      |        | 7.14 | Ω    |                                                                                                                               |

| Reverse supply resistance                                                | R <sub>VCC1,rev</sub><br>R <sub>IN,rev</sub> | 1<br>0.17 | -      | -    | MΩ   | iSSI30R11H and<br>iSSI30R12H, V <sub>test</sub> = -2.5 V<br>iSSI20R02H, iSSI20R03H,<br>iSSI20R11H, V <sub>test</sub> = -2.5 V |

| Off-time before turn-on                                                  | t <sub>OFF,IN</sub><br>t <sub>OFF,VCC1</sub> | 25        | -      | -    | μs   | $V_{\rm IN} < V_{\rm UVLOL1}$ (or $V_{\rm VCC1} < V_{\rm UVLOL1}$ where applicable)                                           |

3 Electrical characteristics and parameters

1) Parameter is not subject to production test - verified by design/characterization.

# 3.3.2 Logic input (iSSI20R11H, iSSI30R11H, iSSI30R12H)

#### Table 8Logic input (iSSI20R11H, iSSI30R11H, iSSI30R12H)

| Parameter                             | Symbol              |      | Values |      | Unit | Note or condition                                             |

|---------------------------------------|---------------------|------|--------|------|------|---------------------------------------------------------------|

|                                       |                     | Min. | Тур.   | Max. |      |                                                               |

| IN logic low input threshold voltage  | V <sub>IL</sub>     | 1.0  | 1.2    | -    | V    | Reference to GND1                                             |

| IN logic high input threshold voltage | V <sub>IH</sub>     |      | 2.1    | 2.3  | V    |                                                               |

| IN logic low/high hysteresis          | V <sub>IN,HYS</sub> | 0.7  |        |      | V    |                                                               |

| IN logic pull down resistor           | R <sub>IN,PD</sub>  | 200  | -      | -    | kΩ   | V <sub>IN</sub> = 2.5 V                                       |

| Off-time before turn-on               | t <sub>OFF,IN</sub> | 25   | -      | -    | μs   | <sup>1)</sup> $V_{VCC1} = 3.3 \text{ V}, V_{IN} < V_{IL,min}$ |

1) Parameter is not subject to production test - verified by design/characterization.

### 3.3.3 Gate drive

#### Table 9

Gate drive

| Parameter                                                                                                            | Symbol                    |      | Values | ;    | Unit | Note or condition                                                                          |

|----------------------------------------------------------------------------------------------------------------------|---------------------------|------|--------|------|------|--------------------------------------------------------------------------------------------|

|                                                                                                                      |                           | Min. | Тур.   | Max. |      |                                                                                            |

| Output voltage                                                                                                       | V <sub>OUT</sub>          | 10   | 15     | 20   | V    | <sup>1)</sup> $V_{\rm IN} = 3.3$ V, $I_{\rm OUT} = 0$                                      |

| Output voltage                                                                                                       | V <sub>OUT</sub>          | 10   | 13     | 16   | V    | <sup>1)</sup> $V_{\rm IN} = 2.6$ V, $I_{\rm OUT} = 0$                                      |

| Short circuit output current<br>(iSSI20R02H, iSSI20R03H)                                                             | I <sub>OUT</sub>          | 120  | 185    | -    | μA   | V <sub>IN</sub> = 3.3 V, V <sub>OUT</sub> = 0                                              |

| Short circuit output current<br>(iSSI20R11H, iSSI30R11H,<br>iSSI30R12H)                                              | I <sub>OUT</sub>          | 150  | 325    | 550  | μA   | V <sub>IN</sub> = 3.3 V, V <sub>OUT</sub> = 0                                              |

| Turn-off current                                                                                                     | I <sub>off,sat</sub>      | 50   | 160    | 270  | mA   | <sup>2)</sup> $V_{\rm IN} = 0$ V, $V_{\rm OUT} = 5$ V                                      |

| Fast turn-off transistor saturation current                                                                          | l <sub>off,fast,sat</sub> | 488  | -      | -    | mA   | $^{2)}V_{IN} = 3.3 \text{ V}, V_{CS} = 0.3 \text{ V}, V_{OUT} = 5 \text{ V}$               |

| High-level output resistance                                                                                         | R <sub>OH</sub>           | 60   | 110    | 155  | kΩ   | $V_{\rm IN}$ = 3.3 V, $\Delta V_{\rm OUT}$ = 1 V,<br>iSSI20R02H, iSSI20R03H                |

| High-level output resistance                                                                                         | R <sub>OH</sub>           | 48   | 95     | 135  | kΩ   | $V_{\rm IN}$ = 3.3 V, $\Delta V_{\rm OUT}$ = 1 V,<br>iSSI20R11H, iSSI30R11H,<br>iSSI30R12H |

| Low-level output resistance                                                                                          | R <sub>OL</sub>           | 5    | 8.5    | 12   | Ω    | V <sub>VCC1</sub> = 0, V <sub>OUT</sub> < 0.5 V                                            |

| Turn-on propagation delay terminal<br>IN and VCC1 (where applicable) to<br>terminal OUT or BUF (where<br>applicable) | t <sub>PDON</sub>         | -    | -      | 20   | μs   | V <sub>IN</sub> = 3.3 V, V <sub>VCC1</sub> = 3.3 V (where applicable), no load             |

| Turn-off propagation delay                                                                                           | t <sub>PDOFF</sub>        | 0.3  | 3      | 6    | μs   | V <sub>IN</sub> = 0, no load, V <sub>VCC1</sub> = 3.3 V<br>(where applicable)              |

(table continues...)

3 Electrical characteristics and parameters

#### Table 9(continued) Gate drive

| Parameter | Symbol                              |      | Values |      |    | Note or condition                                                                                                                                                    |

|-----------|-------------------------------------|------|--------|------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |                                     | Min. | Тур.   | Max. |    |                                                                                                                                                                      |

| Rise time | t <sub>r</sub> , t <sub>r,BUF</sub> | -    | 8      | 15   | μs | V <sub>VCC1</sub> = 3.3 V (where<br>appropriate), V <sub>IN</sub> = 3.3 V, no<br>load                                                                                |

| Fall time | t <sub>f</sub>                      | -    | 1.9    | 4    | μs | Supply at VCC1: $V_{VCC1} = 3.3 \text{ V}$ ,<br>$V_{IN} \le 1 \text{ V}$ , $C_{BUF} = 3 \text{ nF}$ , no load<br>Supply at IN: $V_{IN} \le 2.6 \text{ V}$            |

| Fall time | t <sub>f</sub>                      | 1    | 3.2    | 6.5  | μs | Supply at VCC1: $V_{VCC1} = 3.3 \text{ V}$ ,<br>$V_{IN} \le 1 \text{ V}$ , $C_L = 10 \text{ nF}$<br>Supply at IN: $V_{IN} \le 2.6 \text{ V}$ , $C_L = 10 \text{ nF}$ |

1) Reference to GND2.

2) Parameter is not subject to production test - verified by design/characterization.

## 3.3.4 Fast turn-on (iSSI20R11H, iSSI30R11H, iSSI30R12H)

#### Table 10Fast turn-on (iSSI20R11H, iSSI30R11H, iSSI30R12H)

| Parameter                                                     | Symbol                   |      | Values |      | Unit | Note or condition                                                               |

|---------------------------------------------------------------|--------------------------|------|--------|------|------|---------------------------------------------------------------------------------|

|                                                               |                          | Min. | Тур.   | Max. |      |                                                                                 |

| Fast turn-on threshold (power up)                             | V <sub>BUF,th</sub>      | 10.0 | 10.4   | 10.8 | V    | 1)                                                                              |

| Fast turn-on saturation current                               | I <sub>on,fast,sat</sub> | 232  | 400    | -    | mA   | <sup>2)</sup> $V_{OUT} = 5 \text{ V}, V_{BUF} = 10.4 \text{ V}$                 |

| Resistance between terminal BUF<br>and OUT after fast turn-on | R <sub>BUF-OUT</sub>     | 300  | 500    | -    | kΩ   | 2)                                                                              |

| Fast turn-on propagation delay input-to-output                | t <sub>PDON,fast</sub>   | -    | 5      | -    | ms   | $^{2)}C_{BUF} = 33 \text{ nF}, C_{OUT} = 5.6 \text{ nF}, V_{OUT} = 1 \text{ V}$ |

| Fast turn-on rise time                                        | t <sub>r,fast</sub>      | -    | 530    | 1000 | ns   | $^{2)}C_{BUF} = 48 \text{ nF}, C_{OUT} = 10 \text{ nF}$                         |

1) Reference to GND2.

2) Parameter is not subject to production test - verified by design/characterization.

# 3.3.5 Dynamic Miller clamping

### Table 11Dynamic Miller clamping

| Parameter                                                     | Symbol             |      | Values |      | Unit | Note or condition                                                |

|---------------------------------------------------------------|--------------------|------|--------|------|------|------------------------------------------------------------------|

|                                                               |                    | Min. | Тур.   | Max. |      |                                                                  |

| Dynamic Miller clamp saturation current                       | I <sub>CLAMP</sub> | 500  | 1700   | -    | mA   | <sup>1)</sup> $V_{\rm MC} = 2.5  \rm V;  V_{\rm OUT} = 3  \rm V$ |

| Low-level output resistance during<br>dynamic Miller clamping | R <sub>OL,MC</sub> | 0.7  | 1.5    | 3.5  | Ω    | V <sub>MC</sub> = 2.5 V, <i>I</i> <sub>OUT</sub> = 10 mA         |

| Input resistance terminal MC                                  | R <sub>MC</sub>    | 400  | 500    | 600  | Ω    | $V_{\rm VCC1} = 0, V_{\rm MC} = 0.5 \rm V$                       |

1) Parameter is not subject to production test - verified by design/characterization.

3 Electrical characteristics and parameters

### 3.3.6 Over-temperature protection

#### Table 12 Over-temperature protection

| Parameter                                                  | Symbol                                          |             | Values      |              | Unit | Note or condition                                                                                                                                          |

|------------------------------------------------------------|-------------------------------------------------|-------------|-------------|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                            |                                                 | Min.        | Тур.        | Max.         |      |                                                                                                                                                            |

| Temperature sense comparator<br>threshold (iSSI30R12H)     | V <sub>TS,th1</sub>                             | 1.056       | 1.095       | 1.120        | V    | <sup>1)</sup> $V_{\rm IN} = 3.3 \rm V$                                                                                                                     |

| Temperature sense comparator<br>threshold (other variants) | V <sub>TS,th2</sub>                             | 190         | 200         | 210          | mV   | <sup>1)</sup> $V_{\rm IN} = 3.3 \rm V$                                                                                                                     |

| Temperature sense bias current<br>(terminals TS and TS/CS) | I <sub>TS,bias</sub><br>I <sub>TS/CS,bias</sub> | 40          | 50          | 60           | μA   | $V_{\rm IN} = V_{\rm VCC1} = 3.3  {\rm V}$                                                                                                                 |

| Temperature sense protection propagation delay             | t <sub>PD,TS</sub>                              | -           | -           | 5            | μs   | $V_{IN} = 3.3 \text{ V}, C_{Load} \le 100$<br>pF, $V_{TS} = V_{TS,th2} - 20 \text{ mV}$<br>(iSSI30R12H), $V_{TS} = V_{TS,th1} + 20$<br>mV (other variants) |

| Temperature sense filter time                              | t <sub>TS,filter</sub>                          | 1.9<br>0.12 | 2.7<br>0.15 | 3.5<br>0.175 | μs   | $^{2)}V_{VCC1} = 3.3 V, V_{TS} =$<br>$V_{TS,th2} - 20 mV (iSSI30R12H),$<br>$V_{VCC1} = 3.3 V,$<br>$V_{TS} = V_{TS,th1} + 20 mV (other variants)$           |

| Fast turn-off fall time after OTP<br>trigger               | t <sub>f,TS</sub>                               | -           | -           | 725          | ns   | <sup>2)</sup> $C_{OUT}$ = 28 nF, $V_{OUT}$ = 12 V                                                                                                          |

1) Reference to GND2.

2) Parameter is not subject to production test - verified by design/characterization.

### 3.3.7 Overcurrent protection

#### Table 13Overcurrent protection

| Parameter                                    | Symbol                 |      | Values | ;    | Unit | Note or condition                                                                                   |

|----------------------------------------------|------------------------|------|--------|------|------|-----------------------------------------------------------------------------------------------------|

|                                              |                        | Min. | Тур.   | Max. |      |                                                                                                     |

| Overcurrent comparator shut down threshold   | V <sub>CS,th</sub>     | 185  | 200    | 215  | mV   | <sup>1)</sup> $V_{VCC1}$ = 3.3 V; Output is active;                                                 |

| Overcurrent shut-down delay                  | t <sub>CS,off</sub>    | -    | 0.6    | 1    | μs   | V <sub>CS</sub> = 300 mV, V <sub>OUT</sub> = 2.5 V                                                  |

| Overcurrent filter time                      | t <sub>CS,filter</sub> | 120  | 150    | 175  | ns   | $^{2)} v_{\rm CS}  = 0.3  \rm V$                                                                    |

| Fast turn-off fall time after OCP<br>trigger | t <sub>f,CS</sub>      | -    | -      | 725  | ns   | $^{2)}C_{OUT} = 28 \text{ nF}, V_{OUT} = 12 \text{ V},    dv_{CS}/dt  > 480 \text{ mV/}\mu\text{s}$ |

1) Reference to GND2.

2) Parameter is not subject to production test - verified by design/characterization.

4 Insulation and safety-related specification

# 4 Insulation and safety-related specification

### 4.1 Safety-limiting values

Note: safety-limiting values define the operating conditions under which the isolation barrier can be guaranteed to stay unaffected. This corresponds with the maximum allowed junction temperature, as temperature-induced failures might cause significant overheating and eventually damage the isolation barrier.

| Parameter                          | Symbol          | Value                                    | Unit | Note or condition                                                                       |

|------------------------------------|-----------------|------------------------------------------|------|-----------------------------------------------------------------------------------------|

| iSSI20R02H, iSSI20R03H, iSSI20     | R11H            | L. L |      |                                                                                         |

| Maximum ambient safety temperature | T <sub>S</sub>  | 150                                      | °C   |                                                                                         |

| Safety input power dissipation     | Ps              | 200                                      | mW   | Derating required above $T_A = 122^{\circ}C$ with<br>7.14 mW/°C, $T_J = 150 ^{\circ}C$  |

| Safety input supply current        | I <sub>SI</sub> | 50                                       | mA   | Derating required above $T_A = 122$ °C with 1.8 mA/°C, $T_J = 150$ °C                   |

| Safety output power dissipation    | P <sub>SO</sub> | 4.5                                      | mW   | Derating required above $T_A = 149.4^{\circ}$ C with 7.14 mW/°C, $T_J = 150^{\circ}$ C  |

| iSSI30R11H, iSSI30R12H             |                 |                                          |      |                                                                                         |

| Maximum ambient safety temperature | T <sub>S</sub>  | 150                                      | °C   |                                                                                         |

| Safety input power dissipation     | P <sub>SI</sub> | 200                                      | mW   | Derating required above $T_A = 130.8^{\circ}$ C with 10.42 mW/°C, $T_J = 150^{\circ}$ C |

| Safety input supply current        | I <sub>SI</sub> | 50                                       | mA   | Derating required above $T_A = 130.8$ °C with 2.6 mA/°C, $T_J = 150$ °C                 |

| Safety output power dissipation    | P <sub>SO</sub> | 4.5                                      | mW   | Derating required above $T_A = 149.5^{\circ}$ C with 10.42 mW/°C, $T_J = 150^{\circ}$ C |

## 4.2 Reinforced insulation according to IEC 60747-17 (planned)

| Parameter                  | Symbol | Value         | Unit | Note or condition                                                                                                        |

|----------------------------|--------|---------------|------|--------------------------------------------------------------------------------------------------------------------------|

| External clearance         | CLR    | >8            | mm   | Shortest distance in air from any input pin to any output pin according to IEC 60664-1 <sup>1)</sup>                     |

| External creepage          | CRP    | >8            | mm   | Shortest distance over package surface from<br>any input pin to any output pin according to<br>IEC 60664-1 <sup>1)</sup> |

| Comparative tracking index | СТІ    | >400          | V    | According to IEC 60112                                                                                                   |

| Material group             |        | II            |      | According to IEC 60112                                                                                                   |

| Pollution degree           |        | 2             |      | According to IEC 60664-1                                                                                                 |

| Overvoltage category       |        | I - IV        |      | Rated mains voltage ≤ 150 V (rms)                                                                                        |

| (According to IEC 60664-1) |        | I - IV        |      | Rated mains voltage ≤ 300 V (rms)                                                                                        |

|                            |        | 1 - 111       |      | Rated mains voltage ≤ 600 V (rms)                                                                                        |

|                            |        | 1-11          |      | Rated mains voltage ≤ 1000 V (rms)                                                                                       |

| Climatic category          |        | 40/125/<br>21 |      |                                                                                                                          |

4 Insulation and safety-related specification

| Parameter                                       | Symbol            | Value             | Unit             | Note or condition                                                                                  |

|-------------------------------------------------|-------------------|-------------------|------------------|----------------------------------------------------------------------------------------------------|

| Input-to-output isolation accordi               | ng to UL157       | 7 Ed. 5 (plan     | ned)             |                                                                                                    |

| Input-to-output isolation voltage               | V <sub>ISO</sub>  | 5700              | V <sub>rms</sub> | $V_{\text{TEST}} = V_{\text{ISO}}$ for $t = 60$ s (qualification);                                 |

|                                                 |                   |                   |                  | $V_{\text{TEST}} = 1.2 \times V_{\text{ISO}}$ for $t = 1$ s (100% productive tests)                |

| Input-to-output isolation accordi               | ng to IEC 607     | 747-17 (plan      | ned)             |                                                                                                    |

| Maximum rated transient isolation voltage       | V <sub>IOTM</sub> | 8000              | V <sub>pk</sub>  | $V_{\text{TEST}} = V_{\text{IOTM}}$ for $t_{\text{ini}} = 60$ s (type test and sample test)        |

|                                                 |                   |                   |                  | $V_{\text{TEST}} = 1.2 \times V_{\text{IOTM}}$ for $t_{\text{ini}} = 1$ s (routine test)           |

| Maximum rated repetitive peak isolation voltage | V <sub>IORM</sub> | 1200              | V <sub>pk</sub>  | According to Time Dependent Dielectric<br>Breakdown (TDDB) test                                    |

| Apparent charge                                 | q <sub>PD</sub>   | <5                | pC               | Method (b1) (routine test and type test pre-<br>conditioning)                                      |

|                                                 |                   |                   |                  | $V_{\text{PD(ini)},b} = 1.2 \times V_{\text{IOTM}}$ for $t_{\text{ini}} = 1$ s                     |

|                                                 |                   |                   |                  | $V_{\rm PD(m)} = 1.875 \times V_{\rm IORM}$ for $t_{\rm m} = 1$ s                                  |

|                                                 |                   |                   |                  | Method (a) (type test, subgroup 1 final measurements)                                              |

|                                                 |                   |                   |                  | $V_{\text{PD(ini)},a} = V_{\text{IOTM}}$ for $t_{\text{ini}} = 60$ s                               |

|                                                 |                   |                   |                  | $V_{\rm PD(m)} = 1.6 \times V_{\rm IORM}$ for $t_{\rm m} = 10  {\rm s}^{3}$                        |

| Impulse voltage                                 | V <sub>IMP</sub>  | 8000              | V <sub>pk</sub>  |                                                                                                    |

| Maximum surge isolation voltage                 | V <sub>IOSM</sub> | 11000             | V <sub>pk</sub>  | $V_{\text{TEST}} \ge 1.3 \times V_{\text{IMP}} \text{ (type test)}^{4)}$                           |

| Isolation resistance                            | R <sub>IO</sub>   | >10 <sup>12</sup> | Ω                | $V_{\rm IO} = 500 V_{\rm dc}$ for $t = 60$ s, $T_{\rm A} = 25 {}^{\circ}{\rm C}^{5)}$              |

| Isolation resistance                            | R <sub>IO</sub>   | >10 <sup>11</sup> | Ω                | $V_{\rm IO} = 500 V_{\rm dc}$ for $t = 60$ s, $T_{\rm A} = 125 {}^{\circ}{\rm C}^{5)}$             |

| Isolation resistance                            | R <sub>IO_S</sub> | >109              | Ω                | $V_{\rm IO} = 500 V_{\rm dc}$ for $t = 60$ s, $T_{\rm S} = T_{\rm A} = 150 {}^{\circ}{\rm C}^{5)}$ |

| Isolation capacitance                           | C <sub>IO</sub>   | 1.9               | pF               | f=1 MHz <sup>5)</sup>                                                                              |

1) Creepage and clearance requirements depend on the application and related end-equipment isolation standard. Care should be taken to keep the required creepage and clearance value on printed-circuit-board level.

2) Safety certification pending.

3) The partial discharge voltage  $V_{PD(m)}$  applied during productive tests is greater (tbd  $V_{pk} > 1.875 \times V_{IORM}$ ) to include the  $F_4$  factor (1.1) required by end-equipment standards IEC 60664-1, IEC 62368-1, IEC 60950 ( $V_{PD(m)} = F_1 \times F_2 \times F_3 \times F_4 \times V_{IORM} = 1.875 \times F_4 \times V_{IORM}$ ). The  $F_3$  factor (1.25) is also considered for further stress of the insulation.

4) The surge test is performed in insulation oil to determine the intrinsic surge immunity of the insulation barrier.

5) The parameters apply to the product converted in a two terminals device with all terminals on side 1 connected together and all terminals on side 2 connected together.

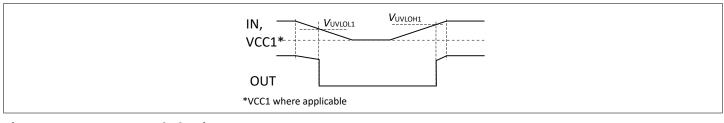

5 Timing diagrams

# 5 Timing diagrams

UVLO behavior

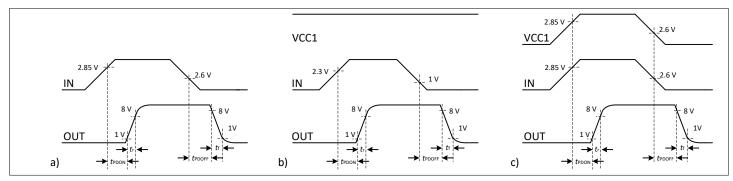

Direct gate drive turn-on and turn-off propagation delay, rise and fall time: a) direct drive turn-on for variants iSSI20R02H and iSSI20R03H, b) separate *VCC1* and *IN* using no buffer capacitor, c) *VCC1* and *IN* shorted using no buffer capacitor

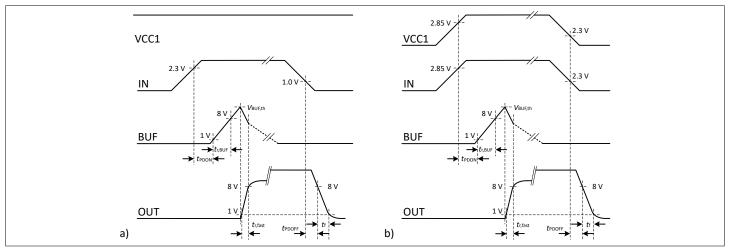

Fast turn-on timing using a buffer capacitor: a) separate VCC1 and IN, b) VCC1 and IN shorted

Figure 11

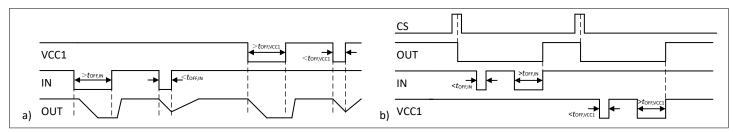

a) Off-time before turn-on, b) off-time after protection (example of overcurrent protection)

5 Timing diagrams

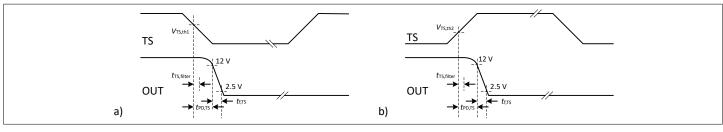

Over-temperature protection timing: a) iSSI30R12H, b) others

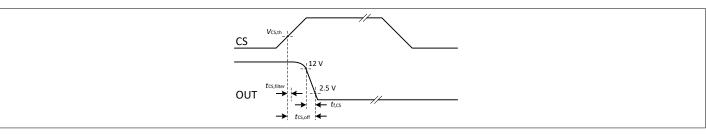

**Overcurrent protection timing**

6 Functional description

# 6 Functional description

### 6.1 Input side

## 6.1.1 Input side supply

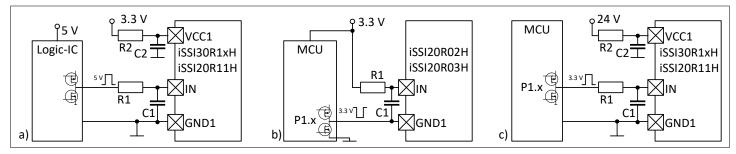

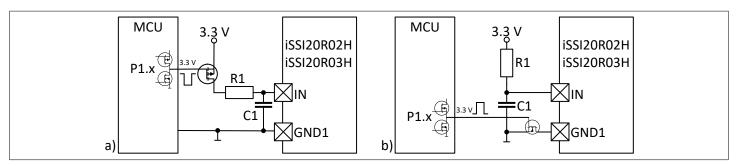

The input side of the iSSI family is 3.3 V compatible and operates best with an input voltage tolerance of 5%. The power-up under-voltage threshold voltage is  $V_{UVLOH1}$ . It ensures sufficient output voltage for operating the output. The power-down under-voltage threshold is  $V_{UVLOL1}$ . The integrated supply is based on a shunt regulator that emulates a diode structure to simplify designs. The device can then be supplied even by any voltage rail that exceeds the operating range by using a current limiting resistor placed in series to the supply terminal *IN* or *VCC1* (where applicable). If no suitable resistor in series to terminal *VCC1* is used for current limitation, then staying within the operating parameters is recommended to avoid unnecessary power dissipation in the IC.

The input side of the IC contains an integrated power supply buffer capacitor. External buffer capacitors for the supply voltage are not necessary, but possible. Such external buffer capacitors should not exceed C<sub>VCC1,ext</sub>.

In addition, the iSSI family provides a strong reverse bias capability for the supply terminals *IN* or *VCC1* (where applicable). This enables all variants to operate in differential operation with respect to their terminals *IN* and *GND1*.

A minimum off-time *t*<sub>OFF,IN</sub> or *t*<sub>OFF,VCC1</sub> is required between the turn-off and turn-on signals to establish a defined "off"-state on the output side of the isolator.

Variants iSSI20R02H and iSSI20R03H use the supply terminal *IN* to perform the reset procedure after the output side latch-off procedure of the protection functions. Variants iSSI20R11H, iSSI30R11H, and iSSI30R12H can perform this reset at either at terminal *VCC1* or at terminal *IN*. In any case of reset of any variant, ensure that the reset time is larger than  $t_{OFF,IN}$  or  $t_{OFF,VCC1}$  before turning on again after a protection event.

### 6.1.2 Logic input

Variants iSSI20R11H, iSSI30R11H, and iSSI30R12H offer separate supply and control terminals. The control logic thresholds  $V_{IL}$  and  $V_{IH}$  at terminal *IN* are 3.3 V CMOS compliant and can be controlled directly from standard CMOS logic outputs. Please note that the signal level at terminal *IN* can be substantially higher than the supply voltage at terminal *VCC1*. For example, it is possible to apply signals on 5 V level while  $V_{VCC1} = 3.3$  V. The output acts in phase with the input control signal at terminal *IN*. Before turning on, a minimum off-time  $t_{OFF,IN}$  has to be considered for resetting the output side. If the equivalent MOSFET's input capacitance is larger than 100 pF longer off-times than  $t_{OFF,IN}$  might be needed.

A new reset procedure has to be performed after a protection triggered turn-off. Variants iSSI20R11H, iSSI30R11H, and iSSI30R12H can perform this reset at either at terminal *VCC1* or at terminal *IN*. In any case of reset of any variant, ensure that the reset time is larger than t<sub>OFF,IN</sub> before turning on again after a protection event.

Applications using the variants iSSI20R11H, iSSI30R11H, and iSSI30R12H can use these isolators with externally shorted terminals *VCC1* and *IN*. In this case, all operating guidelines of variants iSSI20R02H and iSSI20R03H apply.

### 6.2 Output side

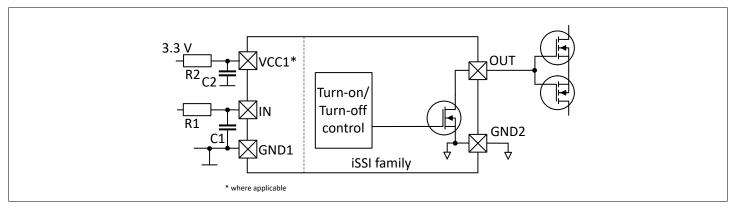

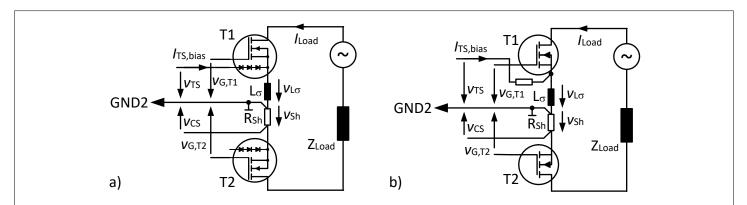

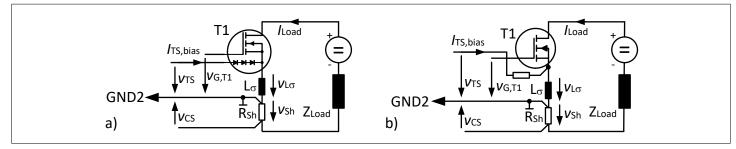

### 6.2.1 Direct gate drive

Terminal *OUT* is the gate drive output. The output voltage *V*<sub>OUT</sub> is sufficient to drive CoolMOS<sup>™</sup>, OptiMOS<sup>™</sup>, or TRENCHSTOP<sup>™</sup> IGBT without additional, external buffers. Variants iSSI20R02 and iSSI20R03 provide the short circuit output current *I*<sub>OUT</sub> directly to the gate. This enables a quick turn-on of MOS-controlled power transistor. Variants iSSI20R11H and iSSI30R1xH can be used in direct drive mode, as well, if the buffer capacitor is not connected.

6 Functional description

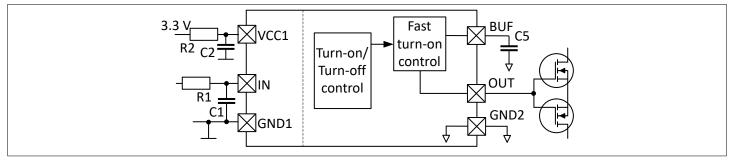

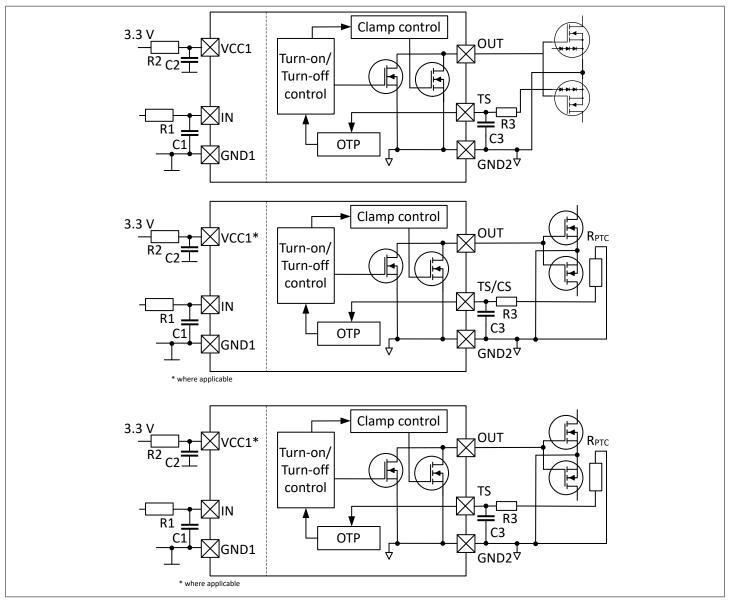

#### 6.2.2 Fast turn-on feature

Variants iSSI20R11H, iSSI30R11H, and iSSI30R12H provide the fast turn-on feature that further enforces the turn-on current by accumulating charge in an external buffer capacitor at terminal BUF. The accumulated charge is released to terminal OUT, if the voltage at terminal BUF equal or higher than the buffer threshold voltage  $V_{\text{BUEth}}$  and a turn-on condition is given on the control side.

# Fast turn-on feature of iSSI20R11H, iSSI30R11H, and iSSI30R12H

#### 6.2.3 Normal turn-off

The normal turn-off feature is implemented in all variants. A turn-off signal from the input side activates the integrated depletion FET. The depletion FET discharges the gate node of the operated power transistor. The iSSI family's sink saturation current I<sub>off,sat</sub> is dimensioned to discharge CoolMOS<sup>™</sup> S7 transistors within a few microseconds.

#### Fast turn-off 6.2.4

Overcurrent or over-temperature events trigger the fast turn-off feature of the iSSI family. The fast turn-off enables the iSSI family to shut down the power transistors inside their safe operating area particularly under high load operations. The iSSI family's fast turn-off sink saturation current Ioff, fast, sat is dimensioned to discharge CoolMOS™ S7 transistors faster than a normal turn-off.

6 Functional description

Figure 16 Fast turn-off

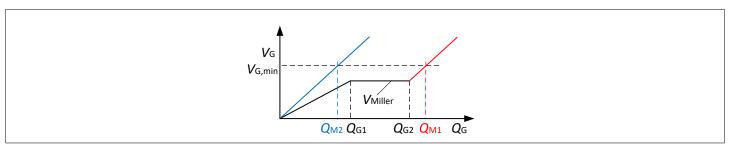

# 6.2.5 Dynamic Miller clamping (DMC)

The dv/dt applied by the connected AC voltage creates capacitive displacement currents through the parasitic capacitances of a power transistor. This can lead to parasitic turn-on of the power switch by increasing the voltage at the gate node of the power switch during its "off"-state. Three major effects can cause dv/dt to occur in installations:

- surge voltages

- fast electric transients (burst)

- dv/dt of line voltage

The dv/dt of line voltage results in a relatively slow dv/dt of 320 V \* 2\*π \* 50 Hz ~ 100 V/ms in 230 V a.c. grids. Many power transistors are robust, by default, against parasitic turn-on under this condition. Surge voltages and fast electric transients result in a much faster dv/dt and power transistors benefit from the dynamic Miller clamping feature.

The dynamic Miller clamping feature ensures that the power switch stays in the "off" state. It is activated by connecting the power switch's drain to terminal *MC*, *MC1*, or *MC2* respectively with a suitable capacitor. The dv/dt appearing at the drain also injects a current into the related terminals *MCx* and activates of the dynamic Miller clamp FET.

Voltage clamping elements at the Miller clamping terminals may be needed to stay within the absolute maximum ratings.

## 6.2.6 Overcurrent protection

Overcurrent protection detects excessive, positive and negative current through the power transistor and uses the voltage drop at an external shunt resistor to trigger a comparator with a fixed threshold  $|V_{CS,th}|$  at terminal *CS* or *TS/CS*. Please note that  $V_{CS,th}$  can be positive or negative. Once triggered, the protection reacts quickly and is able to turn off, for example, CoolMOS<sup>™</sup> IPT60R022S7 in very short time. Thus, it is able to support the AC-15 system tests according to IEC 60947-5-1 under appropriate operating conditions. The integrated noise filter has a filter time of  $t_{CS,filter}$  and can be backed up by an external RC-filter. However, it is recommended to have as little external filtering as possible to get a quick reaction time in case of overcurrent.

The triggering of the overcurrent protection leads to the latched turn-off of the power switch with a sinking current of  $I_{off, fast, sat}$ .

Terminal *TS/CS* sources a bias current for temperature sensing in iSSI20R02H and iSSI20R11H. As the current sensing shunt is usually very low-resistive, the effect of the biasing current  $I_{TS/CS,bias}$  with respect to the shunt signal can be neglected.

The dimensioning of the shunt follows this equation:  $R_{\rm sh} = \frac{|V_{\rm CS, th}|}{I_{\rm pk, max}}$

6 Functional description

### 6.2.7 Over-temperature protection

The over-temperature protection of the iSSI family offers two options to protect against excessive temperatures of the driven power transistor:

- Protection by reading a PTC resistor(iSSI20R02H, iSSI20R03H, iSSI20R11H, and iSSI30R11H)

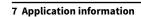

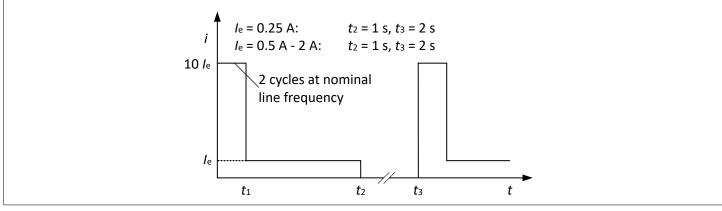

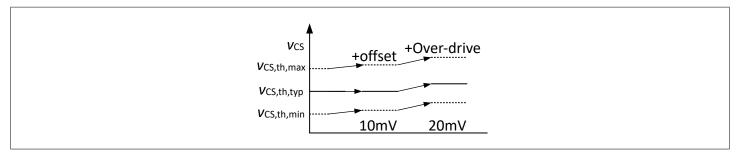

- Protection by reading the threshold voltage of one or several diodes in series (iSSI30R12H, best matching with CoolMOS<sup>™</sup> S7 with temperature sense)