## **Application Note**

#### **About this document**

#### Scope and purpose

The Embedded Power ICs integrate on a single-die a 32-bit microcontroller, non-volatile flash memory, analog and mixed signal peripherals, communication interfaces along with the driving stages needed for either relay, half-bridge or full-bridge DC and BLDC motor applications. The Embedded Power is an industry standard microcontroller processor (32-bit Arm® Cortex®-M core) in leading edge automotive qualified technology (130 nm Smart Power process).

The TLE987x/6x family addresses a wide range of smart 3-phase (TLE987x) and 2-phase (TLE986x) brushless DC motor control applications, like engine cooling fans, auxiliary pumps and fans, sunroof, window lift.

This Application Note provides the reader with detailed descriptions about hardware design guidelines for the external components, using the TLE987x/6x devices.

#### Intended audience

This Application Note is addressed to embedded hardware and software developers, who are going to use the TLE987x/6x devices to design ECU (Electronic Control Unit) for BLDC/PMSM motor control applications.

<sup>\*</sup> Arm and Cortex are registered trademarks of Arm Limited, UK

# **Table of contents**

|                                                                                                                                      | About this document                                                                                                                                                                                                                                                                                    | . 1                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|                                                                                                                                      | Table of contents                                                                                                                                                                                                                                                                                      | . 2                                                      |

| 1.1<br>1.2<br>1.3                                                                                                                    | TLE987x/6x family  TLE987x/6x block diagram  TLE987x/6x family comparison  Application information                                                                                                                                                                                                     | . 4                                                      |

| 2<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5                                                                                                 | Power Supply Generation Unit (PGU)  Block diagram  Input voltage VS, preregulator VPRE and reference voltage VAREF  VDDP: voltage regulator 5.0 V  VDDC: voltage regulator 1.5 V  VDDEXT: voltage regulator 5.0 V                                                                                      | . 9<br>10<br>12<br>12                                    |

| 3.1<br>3.2<br>3.3<br>3.4                                                                                                             | Clock Generation Unit (CGU)  Block diagram  External Input Clock mode  External Crystal mode  Layout recommendations                                                                                                                                                                                   | 14<br>15<br>16                                           |

| 4                                                                                                                                    | LIN transceiver                                                                                                                                                                                                                                                                                        | 18                                                       |

| <b>5</b><br>5.1<br>5.2                                                                                                               | High-voltage monitor input                                                                                                                                                                                                                                                                             | 19                                                       |

| 6<br>6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.2.1<br>6.2.2.2<br>6.2.2.3<br>6.2.2.4<br>6.2.2.5<br>6.2.2.6<br>6.2.2.7<br>6.2.2.8<br>6.2.2.9 | Bridge driver (excluding charge pump)  Application diagram  External components  Overview  Details  Gate resistor  Gate-to-source resistor  Gate-to-drain capacitor  DC link capacitors  Snubber  EMC filter capacitor at the SHx pin  Low-pass filter at the VDH pin  Protection diode at the SHx pin | 20<br>21<br>21<br>21<br>21<br>22<br>22<br>23<br>23<br>23 |

| <b>7</b> 7.1 7.2 7.2.1 7.3 7.3.1                                                                                                     | Charge pump  Application diagram  Charge pump: how it works  ICP load current calculation  Charge pump external capacitors design  Calculation example                                                                                                                                                 | 24<br>24<br>27<br>32                                     |

| <b>8</b><br>8.1                                                                                                                      | Current Sense Amplifier                                                                                                                                                                                                                                                                                |                                                          |

| 8.2    | Functional description                                             | 35 |

|--------|--------------------------------------------------------------------|----|

| 8.2.1  | DC characteristics                                                 | 35 |

| 8.2.2  | AC characteristics                                                 | 37 |

| 8.3    | Application hints                                                  | 40 |

| 8.3.1  | Shunt resistor selection                                           | 40 |

| 8.3.2  | Filter network selection                                           | 44 |

| 8.3.3  | Conclusion                                                         | 47 |

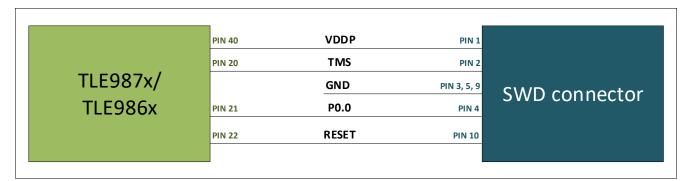

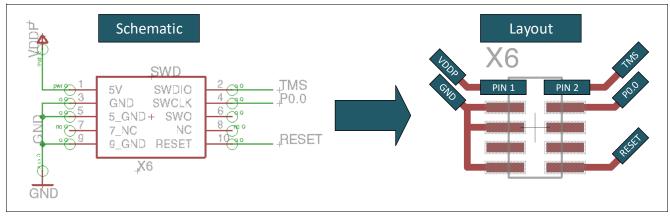

| 9      | SWD (Serial Wire Debug) interface circuitry                        | 49 |

| 9.1    | Description of the SWD interface                                   |    |

| 9.2    | Implementing an SWD interface connection to TLE987x/6x             |    |

| 10     | Unused pins                                                        | 50 |

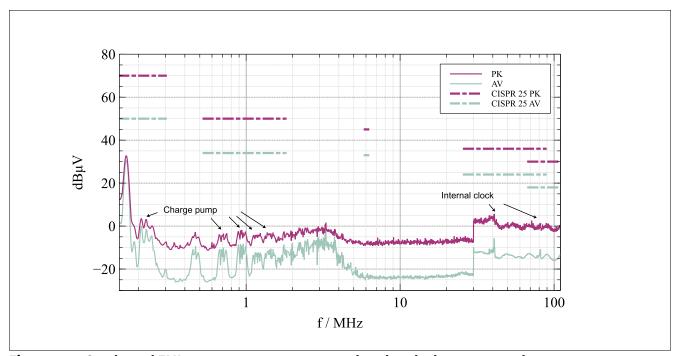

| 11     | EMI recommendation                                                 | 51 |

| 11.1   | Recommendations for optimized PCB layout                           | 51 |

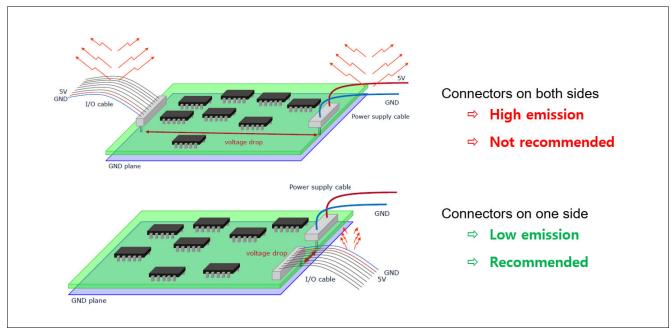

| 11.1.1 | Placement of the connectors                                        | 51 |

| 11.1.2 | Floor-planning the PCB                                             | 51 |

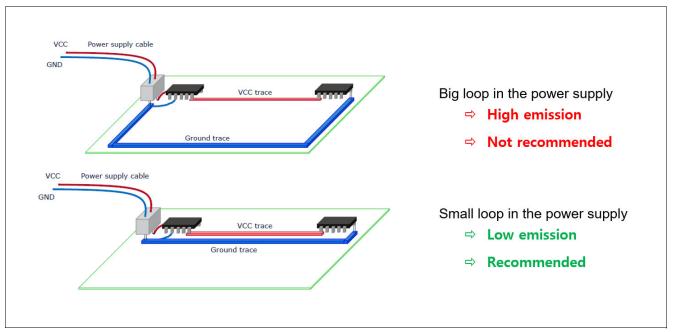

| 11.1.3 | Routing the power supply traces                                    | 52 |

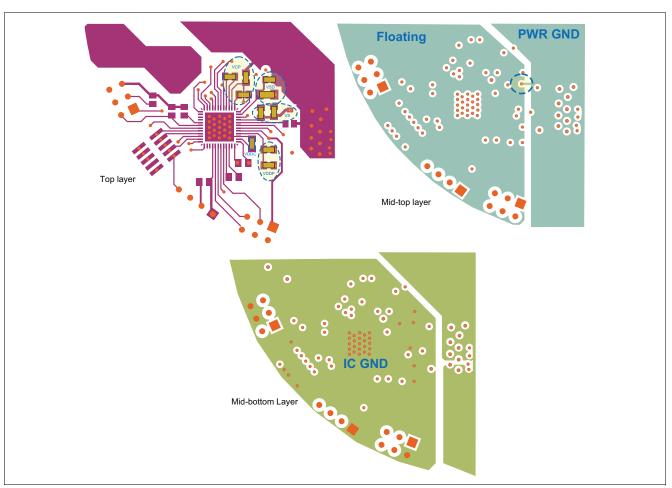

| 11.1.4 | Number of PCB layers                                               | 53 |

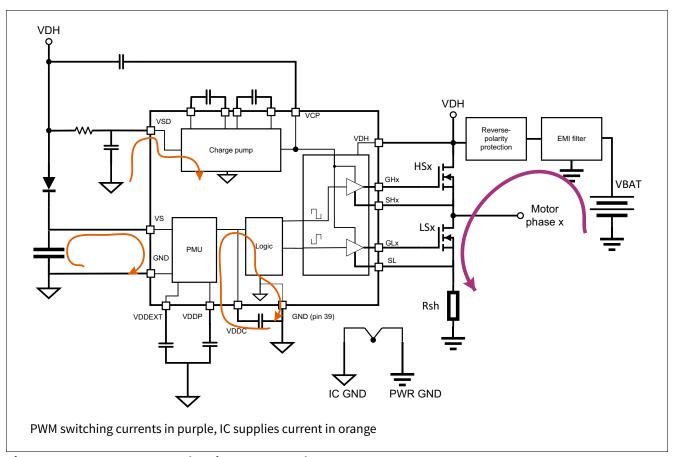

| 12     | Specific PCB design rules for microcontrollers with bridge drivers | 54 |

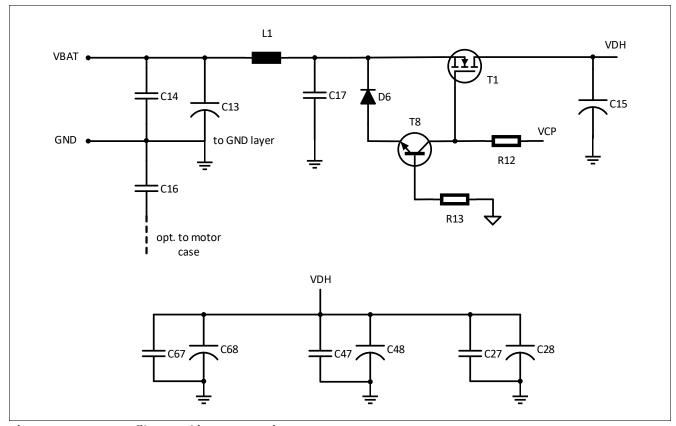

| 12.1   | Input filter                                                       |    |

| 12.1.1 | GND concept                                                        | 56 |

| 12.2   | Bypass capacitors                                                  | 59 |

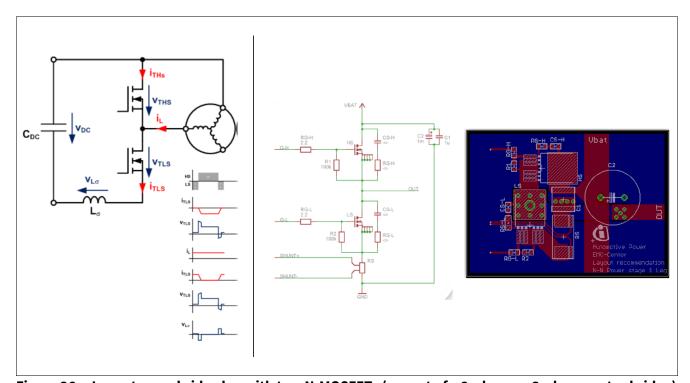

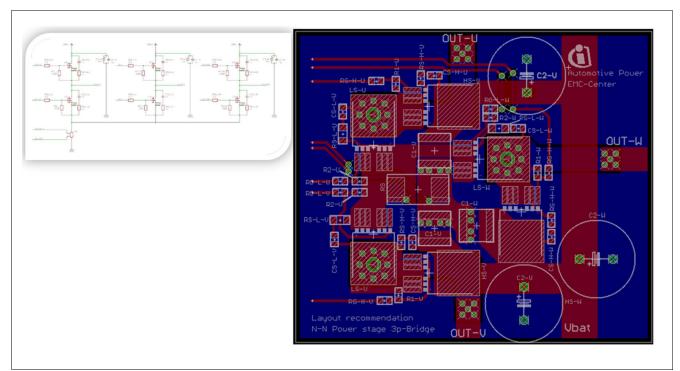

| 12.3   | Layout recommendation for a 3-phase motor bridge                   | 59 |

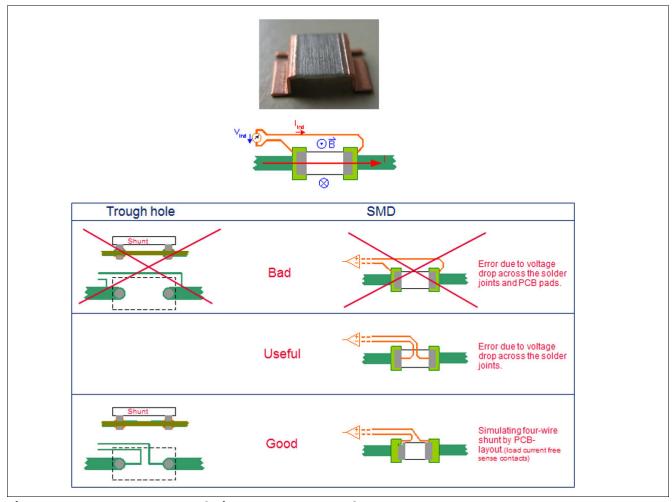

| 12.4   | Layout recommendation for a current sense shunt                    | 61 |

|        | Revision history                                                   | 62 |

|        |                                                                    |    |

TLE987x/6x family

### 1 TLE987x/6x family

The TLE987x/6x is a single-chip 3-phase/2-phase motor driver that integrates the industry standard Arm® Cortex®-M3 core, enabling the implementation of advanced motor control algorithms such as field-oriented control.

It includes six (TLE987x) or four (TLE986x) fully integrated NFET drivers optimized to drive a 3-phase or 2-phase motor via external power NFETs, a charge pump enabling low-voltage operation, and programmable current along with current slope control for optimized EMC behavior. Its peripheral set includes a current sense amplifier, a successive approximation ADC optionally synchronized with the Capture and Compare Unit for PWM control, and 16-bit timers. A LIN transceiver to enable communication with the device and several general-purpose I/O units are also integrated. It includes an on-chip linear voltage regulator to supply external loads.

In addition to other products of the TLE987x product family, TLE9879-2QXA40 incorporates two 14-bit Sigma-Delta ADCs, which provide a reliable interface for an external GMR/TMR sensor.

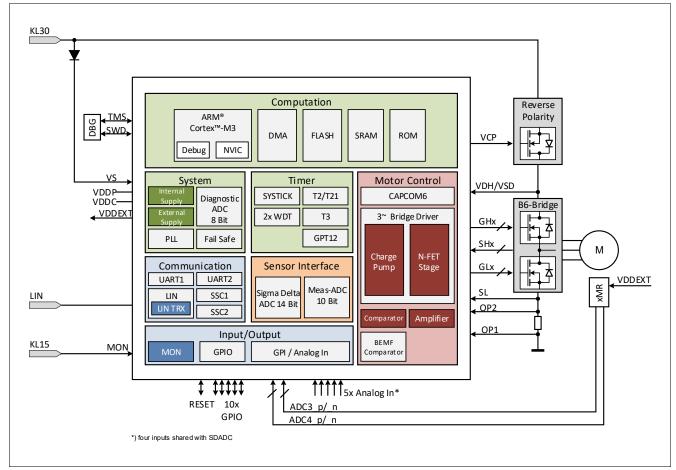

#### 1.1 TLE987x/6x block diagram

**Figure 1** shows the block diagram of the TLE987x. The TLE986x differs from the TLE987x since it integrates two bridge drivers, instead of three.

Figure 1 Block diagram of the TLE987x

In the variants with the Sigma-Delta ADCs, the XTAL1 and XTAL2 pins for the external oscillator are not available.

TLE987x/6x family

## 1.2 TLE987x/6x family comparison

**Table 1** and **Table 2** list the variants available in the TLE987x/6x product family. The versions with the Sigma-Delta ADCs are named using the scheme TLE987x-2Qx.

Table 1 TLE987x product family variants

| Product        | Package | Flash     | RAM     | Max. operating frequency | Interfaces | T <sub>j</sub> max |

|----------------|---------|-----------|---------|--------------------------|------------|--------------------|

| TLE9871QXA20   | VQFN-48 | 36 kByte  | 3 kByte | 24 MHz                   | PWM        | 150°C              |

| TLE9873QXW40   | VQFN-48 | 48 kByte  | 3 kByte | 40 MHz                   | PWM + LIN  | 175°C              |

| TLE9877QXA20   | VQFN-48 | 64 kByte  | 6 kByte | 24 MHz                   | PWM + LIN  | 150°C              |

| TLE9877QXA40   | VQFN-48 | 64 kByte  | 6 kByte | 40 MHz                   | PWM + LIN  | 150°C              |

| TLE9877QXW40   | VQFN-48 | 64 kByte  | 6 kByte | 40 MHz                   | PWM + LIN  | 175°C              |

| TLE9877QTW40   | TQFP-48 | 64 kByte  | 6 kByte | 40 MHz                   | PWM + LIN  | 175°C              |

| TLE9879QXA20   | VQFN-48 | 128 kByte | 6 kByte | 24 MHz                   | PWM + LIN  | 150°C              |

| TLE9879-2QXA40 | VQFN-48 | 128 kByte | 6 kByte | 40 MHz                   | PWM + LIN  | 150°C              |

| TLE9879QXA40   | VQFN-48 | 128 kByte | 6 kByte | 40 MHz                   | PWM + LIN  | 150°C              |

| TLE9879QXW40   | VQFN-48 | 128 kByte | 6 kByte | 40 MHz                   | PWM + LIN  | 175°C              |

| TLE9879QTW40   | TQFP-48 | 128 kByte | 6 kByte | 40 MHz                   | PWM + LIN  | 175°C              |

| TLE9872-2QXA40 | VQFN-48 | 256 kByte | 8 kByte | 40 MHz                   | PWM + LIN  | 150°C              |

| TLE9872QXA40   | VQFN-48 | 256 kByte | 8 kByte | 40 MHz                   | PWM + LIN  | 150°C              |

| TLE9872QTW40   | TQFP-48 | 256 kByte | 8 kByte | 40 MHz                   | PWM + LIN  | 175°C              |

Table 2 TLE986x product family variants

| Product      | Package | Flash     | RAM     | Max. operating frequency | Interfaces | T <sub>j</sub> max |

|--------------|---------|-----------|---------|--------------------------|------------|--------------------|

| TLE9861QXA20 | VQFN-48 | 36 kByte  | 3 kByte | 24 MHz                   | PWM        | 150°C              |

| TLE9867QXA40 | VQFN-48 | 64 kByte  | 6 kByte | 40 MHz                   | PWM + LIN  | 150°C              |

| TLE9867QXA20 | VQFN-48 | 64 kByte  | 6 kByte | 24 MHz                   | PWM + LIN  | 150°C              |

| TLE9867QXW20 | VQFN-48 | 64 kByte  | 6 kByte | 24 MHz                   | PWM + LIN  | 175°C              |

| TLE9868QXB20 | VQFN-48 | 128 kByte | 4 kByte | 20 MHz                   | PWM + LIN  | 150°C              |

| TLE9869QXA20 | VQFN-48 | 128 kByte | 6 kByte | 24 MHz                   | PWM + LIN  | 150°C              |

| TLE9862QXA40 | VQFN-48 | 256 kByte | 8 kByte | 40 MHz                   | PWM + LIN  | 150°C              |

TLE987x/6x family

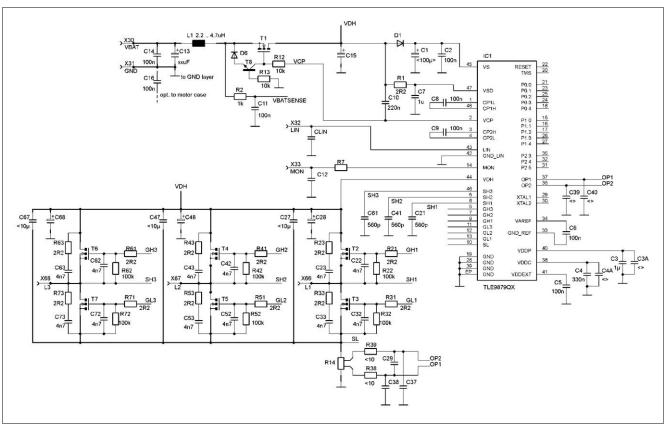

#### 1.3 Application information

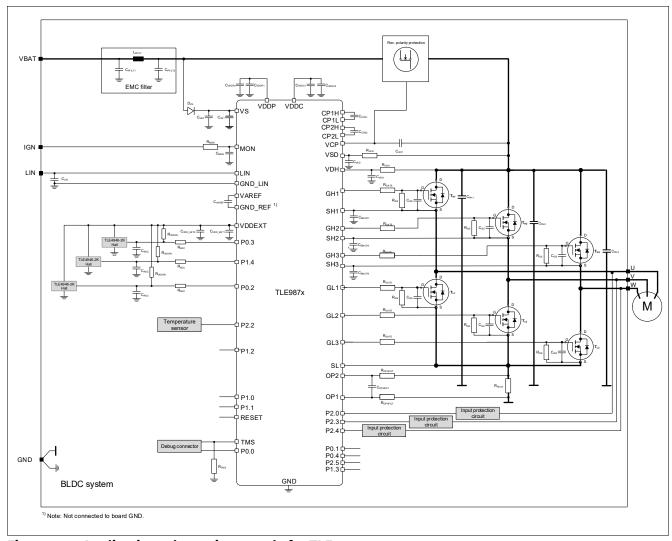

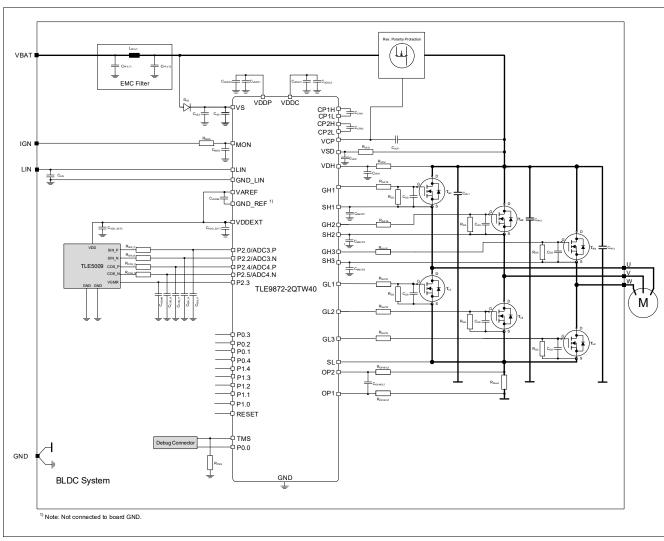

**Figure 2** and **Figure 3** show the TLE987x in an electric-drive application setup controlling a BLDC motor. This is a very simplified example of an application circuit and bill of materials. The function must be verified in the actual application. The TLE986x differs from the TLE987x since it has two bridge drivers, instead of three.

Figure 2 Application schematic example for TLE987x

#### TLE987x/6x family

Figure 3 Application schematic example for TLE987x-2QX

Table 3 **External components (BOM)**

| Symbol                | Function                                                 | Component (typical) |

|-----------------------|----------------------------------------------------------|---------------------|

| $C_{VS1}$             | Filter capacitor at VS pin (TLE987x supply)              | ≥ 100 nF            |

| $C_{VS2}$             | Bulk capacitor at VS pin (TLE987x supply)                | > 2.2 μF            |

| $C_{\text{VDDP}}$     | Output capacitor at VDDP pin (voltage regulator)         | 470 nF + 100 nF     |

| $C_{\text{VDD\_EXT}}$ | Output capacitor at VDD_EXT pin (voltage regulator)      | 100 nF              |

| $C_{\text{VDDC}}$     | Output capacitor at VDDC pin (voltage regulator)         | 470 nF + 100 nF     |

| C <sub>VAREF</sub>    | Filter capacitor at VAREF pin (analog reference)         | 100 nF              |

| $C_{LIN}$             | Filter capacitor at LIN pin                              | 220 pF              |

| $C_{\text{VSD}}$      | Filter capacitor at VSD pin (charge pump supply)         | 1 μF                |

| $C_{\text{CPS1}}$     | Charge pump capacitor (first stage flying capacitor)     | 220 nF              |

| C <sub>CPS2</sub>     | Charge pump capacitor (second stage flying capacitor)    | 220 nF              |

| $C_{\text{VCP}}$      | Charge pump capacitor (output bulk capacitor)            | 470 nF              |

| $C_{\text{MON}}$      | Filter capacitor at MON pin (high-voltage monitor input) | 10 nF               |

## TLE987x/6x family

Table 3 External components (BOM)

| Symbol                                  | Function                                                    | Component (typical) |

|-----------------------------------------|-------------------------------------------------------------|---------------------|

| C <sub>VDH</sub>                        | Filter capacitor at VDH pin (drain high-side MOSFET driver) | 3.3 nF              |

| C <sub>PH1</sub>                        | Filter capacitor at drain high-side FET (phase U)           | 220 μF              |

| C <sub>PH2</sub>                        | Filter capacitor at drain high-side FET (phase V)           | 220 μF              |

| C <sub>PH3</sub>                        | Filter capacitor at drain high-side FET (phase W)           | 220 μF              |

| OPAFILT                                 | Filter capacitor at OP1 and OP2 pins (CSA inputs)           | application related |

| EMCP1                                   | Filter capacitor at SH1 pin (source high-side FET 1)        | 1 nF                |

| EMCP2                                   | Filter capacitor at SH2 pin (source high-Side FET 2)        | 1 nF                |

| EMCP3                                   | Filter capacitor at SH3 pin (source high-side FET 3)        | 1 nF                |

| $C_{PFILT1}, C_{PFILT2}$                | Filter capacitors of the input $\pi$ filter                 | application related |

| O <sub>VS</sub>                         | Reverse-polarity protection diode                           | application related |

| ·PFILT                                  | Filter inductor of the input $\pi$ filter                   | application related |

| R <sub>MON</sub>                        | Filter resistor at MON pin                                  | 3.9 kΩ              |

| R <sub>VSD</sub>                        | Filter resistor at VSD pin                                  | 2 Ω                 |

| $R_{\text{VDH}}$                        | Filter resistor at VDH pin                                  | 1 kΩ                |

| GATE                                    | FET Gate resistor                                           | 2 Ω                 |

| POPAFILT                                | Filter resistor at OP1 and OP2 pins (CSA inputs)            | application related |

| Shunt                                   | Shunt resistor                                              | application related |

| GS                                      | FET gate-source resistor                                    | application related |

| ·GS                                     | FET gate-source resistor                                    | application related |

| R <sub>VDDPU</sub>                      | Pull-up resistor for Hall sensor                            | application related |

| RADC                                    | Filter resistor at ADC1 input                               | application related |

| ADC                                     | Filter capacitor at ADC1 input                              | application related |

| R <sub>TMS</sub>                        | Pull-down resistor at TMS pin (test mode select)            | optional            |

| R <sub>SIN_P</sub> / R <sub>SIN_N</sub> | Filter resistors at ADC3 input pins (Sigma-Delta version)   | 10 kΩ               |

| R <sub>COS_P</sub> / R <sub>COS_N</sub> | Filter resistors at ADC4 input pins (Sigma-Delta version)   | 10 kΩ               |

| C <sub>SIN_P</sub> / C <sub>SIN_N</sub> | Filter capacitors at ADC3 input pins (Sigma-Delta version)  | 68 nF               |

| $C_{\text{COS\_P}} / C_{\text{COS\_N}}$ | Filter capacitors at ADC4 input pins (Sigma-Delta version)  | 68 nF               |

| C <sub>VGMR</sub>                       | Filter capacitor at GPIO input pin (GMR bridge voltage)     | 4.7 nF              |

infineon

**Power Supply Generation Unit (PGU)**

## 2 Power Supply Generation Unit (PGU)

The Power Management Unit (PMU) generates all required voltage supplies for the embedded MCU (VDDC, VDDP) as well as for the external supply (VDDEXT).

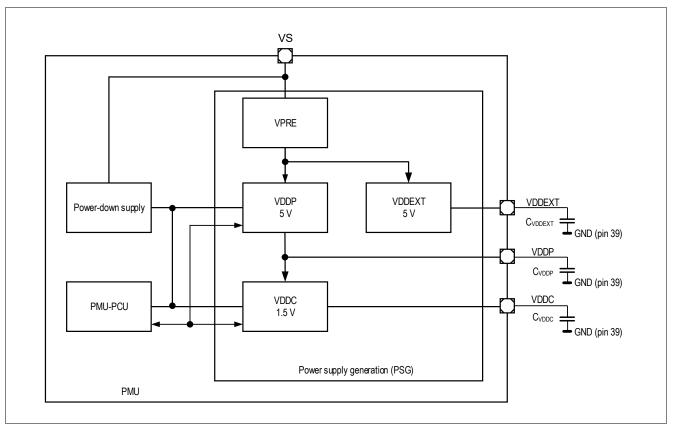

#### 2.1 Block diagram

**Figure 4** shows the structure of the PMU, where the Power Supply Generation Unit (PGU) includes the voltage regulators for the pad supply (VDDP), the core supply (VDDC) and in cascade the voltage regulator to supply external circuits (VDDEXT).

Figure 4 PMU block diagram including the PGU (called PSG in the figure)

The submodules of the PMU are:

- **Power-down supply:** independent analog supply voltage generation for the Power Control Unit logic, for the VDDP regulator, and for the VDDC regulator.

- **VPRE:** analog supply voltage preregulator. This regulator reduces the power dissipation for the following regulator stages.

- **VDDP:** 5-V digital voltage regulator for internal modules and all GPIOs.

- **VDDC:** 1.5-V digital voltage regulator for internal microcontroller modules and core logic.

- VDDEXT: 5-V digital voltage regulator for external circuits.

- **PMU-PCU:** Power Control Unit responsible supervising and controlling the 5-V regulator and the 1.5-V regulator.

**Power Supply Generation Unit (PGU)**

#### 2.2 Input voltage VS, preregulator VPRE and reference voltage VAREF

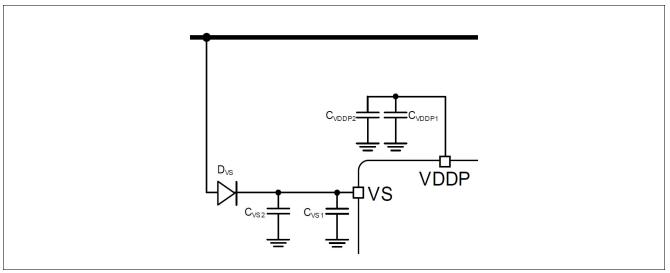

The VS input is the supply voltage of the VPRE preregulator and the power-down supply. VS is derived from the battery voltage (VBAT) and, if necessary, it must be protected against reverse battery connections using a diode ( $D_{VS}$ ) in series to VBAT. The Infineon Application Note "Reverse Polarity Protection for Embedded Power ICs" provides a detailed description of the complete circuit for reverse battery protection.

The  $C_{\rm VS1}$  and  $C_{\rm VS2}$  capacitors, placed before the VS pin, respectively act as a filter and a bulk capacitor for the TLE987x/6x power supply.

Figure 5 Components before the VS pin

If data should be saved in the flash memory at power down, the selection of  $C_{\rm VS2}$  should be done in order to ensure that operations, modifying the content of the flash are never interrupted (for example, in case of power loss). Assuming that at power loss detection all the peripherals are disabled, power is still consumed by the MCU and flash erase or write operations. The size of  $C_{\rm VS2}$  can be calculated using the equation:

(2.1)

$$C_{VS2} \ge \frac{I \times t}{\Delta V}$$

#### where:

- I is the current consumption at power down

- t is the time for which the MCU should stay active after power down

- $\Delta V$  is the difference between the voltage at the time when the loss of power is detected and the reset voltage of the MCU

As reported in the TLE987x/6x product datasheets, the supply voltage in Active mode with reduced functionality (full MCU and flash operation) has a minimum value of 3 V. For example, assuming 10 mA as the current consumption during power down, 20 ms as the time needed to save the flash content, and 3 V as  $\Delta V$ , then  $C_{VS2}$  must be at least 67  $\mu$ F.

**Table 4** shows the recommended components to connect before the VS pin.

#### **Hardware Design Guideline**

**Power Supply Generation Unit (PGU)**

Component selection for the VS pin Table 4

| Symbol           | Function                             | Recommended component                                                                                                  |

|------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| D <sub>VS</sub>  | Diode for reverse battery protection | PN or Schottky diode Voltage and current ratings defined according to the application                                  |

| C <sub>VS1</sub> | Filter capacitor                     | Ceramic capacitor  Min. value 100 nF  Voltage rating and dielectric type defined according to the application          |

| C <sub>vs2</sub> | Bulk capacitor                       | Electrolytic capacitor  Min. value 2.2 μF  Value, voltage rating, and temperature defined according to the application |

The voltage preregulator VPRE generates an internal voltage of about 7 V from the VS input. The output voltage of VPRE is used as input for the internal voltage regulators, and it is not accessible externally.

The  $I_{PRE}$  current is shared between the VDDP and VDDEXT voltage regulators. The table summarizes the maximum currents allowed for each voltage regulator.

| Linear regulator | Maximum current                                       |

|------------------|-------------------------------------------------------|

| VPRE             | I <sub>PRE</sub> = 110 mA                             |

|                  | $I_{PRE} = I_{DDP} + I_{DDEXT}$                       |

| VDDP             | $I_{\text{DDP}} = 90 \text{ mA}$                      |

|                  | $I_{DDP} = 90 \text{ mA}$ $I_{DDEXT} = 20 \text{ mA}$ |

| VDDEXT           | $I_{\text{DDEXT}} = 40 \text{ mA}$                    |

|                  | $I_{\text{DDP}} = 70 \text{ mA}$                      |

| VDDC             | I <sub>DDC</sub> = 40 mA                              |

The voltage VAREF is derived from VPRE and it can be used as 5 V reference voltage for the internal AD converters. The value of the capacitor  $C_{VAREF}$  is in the range of 100 nF up to 1  $\mu$ F.

#### **Hardware Design Guideline**

**Power Supply Generation Unit (PGU)**

#### 2.3 VDDP: voltage regulator 5.0 V

This module represents the 5 V voltage regulator, which provides the pad supply for the parallel port pins and other 5-V analog functions (for example, the LIN transceiver).

#### **Notes**

- 1. The output capacitor  $C_{VDDP}$  is necessary for the stability of the output voltage.

- 2. The values of the  $C_{VDDP}$  capacitors are specified in the table below.

- 3. One single ceramic capacitor can be used, as long as the value is within the recommended range.

- 4. The  $C_{VDDP}$  capacitor should be placed as close as possible to the VDDP pin in the layout.

- 5. For EMC reasons, a ferrite bead can be placed between the VDDP pin and the  $C_{\rm VDDP}$  capacitor.

Table 5 Capacitor selection for VDDP

| Symbol            | Function                 | Recommended component                                         |

|-------------------|--------------------------|---------------------------------------------------------------|

| $C_{\text{VDDP}}$ | Output capacitor at VDDP | Ceramic capacitor                                             |

|                   |                          | Min. value: 470 nF + 1 μF (1.47 μF)                           |

|                   |                          | Max. value: 2.2 μF + 2.2 μF (4.4 μF)                          |

|                   |                          | Voltage rating: 10 V or higher                                |

|                   |                          | Size and dielectric type defined according to the application |

#### 2.4 VDDC: voltage regulator 1.5 V

The 1.5-V voltage regulator provides the power supply for the microcontroller core, the digital peripherals, and other internal analog 1.5-V functions (for example, ADC2) of the chip.

#### **Notes**

- 1. The output capacitor  $C_{VDDC}$  is necessary for the stability of the output voltage.

- 2. The values of the  $C_{VDDC}$  capacitors are specified in the table below.

- 3. One single ceramic capacitor can be used, as long as the value is within the recommended range.

- 4. The  $C_{VDDC}$  capacitor should be placed as close as possible to the VDDC pin in the layout.

- 5. It is NOT possible to place a ferrite bead between the VDDC pin and the  $C_{VDDC}$  capacitor.

- 6. For EMI reasons the ground of the VDDC and the ground of the TLE987x can be separated by placing a ferrite bead between the two ground points.

Table 6 Capacitor selection for VDDC

| Symbol            | Function                 | Recommended component                                         |

|-------------------|--------------------------|---------------------------------------------------------------|

| $C_{\text{VDDC}}$ | Output capacitor at VDDC | Ceramic capacitor                                             |

|                   |                          | Min. value: 100 nF + 330 nF (430 nF)                          |

|                   |                          | Max. value: 1 μF + 1 μF (2 μF)                                |

|                   |                          | Voltage rating: 4 V or higher                                 |

|                   |                          | Size and dielectric type defined according to the application |

#### **Hardware Design Guideline**

**Power Supply Generation Unit (PGU)**

#### 2.5 **VDDEXT: voltage regulator 5.0 V**

The 5-V voltage regulator supplies power to external circuits. It can be used, for example, to supply an external sensor, LEDs, or potentiometers. VDDEXT can be used as the reference for the SDADC (ADC3/4), if available in the product variant.

#### **Notes**

- 1. The output capacitor  $C_{VDDEXT}$  is necessary for the stability of the output voltage.

- 2. The values of the  $C_{VDDEXT}$  capacitors are specified in the table below.

- 3. One single ceramic capacitor can be used, as long as the value is within the recommended limits.

- 4. The  $C_{VDDEXT}$  capacitor should be placed as close as possible to the VDDC pin in the layout.

- 5. In case VDDEXT is not used and disabled, the output capacitor  $C_{\text{VDDEXT}}$  is not needed. The pin VDDEXT can be left open.

**Capacitor selection for VDDEXT** Table 7

| Symbol              | Function                   | Recommended component                                 |

|---------------------|----------------------------|-------------------------------------------------------|

| $C_{\text{VDDEXT}}$ | Output capacitor at VDDEXT | Ceramic capacitor                                     |

|                     |                            | Min. value: 100 nF + 1 μF (1.1 μF)                    |

|                     |                            | Max. value: 2.2 μF + 2.2 μF (4.4 μF)                  |

|                     |                            | Voltage rating: 10 V or higher                        |

|                     |                            | Dielectric type: defined according to the application |

**Clock Generation Unit (CGU)**

### 3 Clock Generation Unit (CGU)

The Clock Generation Unit (CGU) enables flexible clock generation. The frequency can be modified to optimize the ratio of performance to power-consumption. The system clock  $f_{SYS}$  can be generated from one of the following sources:

- Phase-locked loop (PLL) output f<sub>PLL</sub>

- External clock from external crystal oscillator f<sub>OSC</sub>

- External clock from external clock input f<sub>OSC</sub>

- Low-precision clock  $f_{LP CLK}$

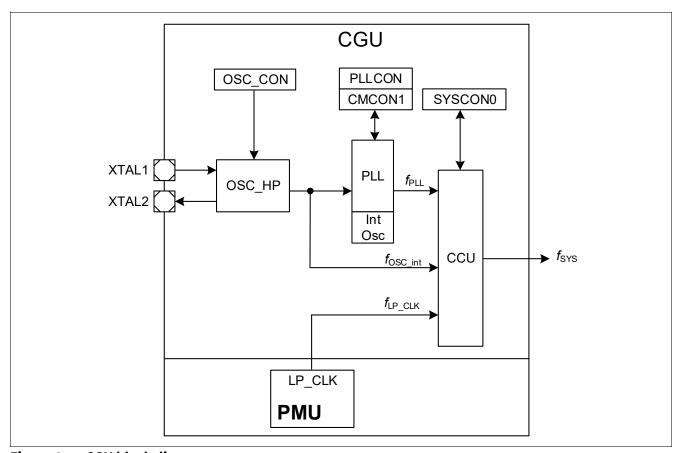

#### 3.1 Block diagram

The CGU consists of a high-precision oscillator circuit (OSC\_HP), a PLL module with an internal oscillator (OSC\_PLL), and a configurable Clock Control Unit (CCU). The CGU can convert a low-frequency input or external clock signal to a high-frequency internal clock.

Figure 6 CGU block diagram

The submodules of the CGU are:

- **High-precision oscillator circuit:** designed to work with either an external crystal oscillator or an external stable clock source, it consists of an inverting amplifier with XTAL1 as the input and XTAL2 as the output.

- **PLL module:** this module generates the clock  $f_{PLL}$  in different modes:

- Prescaler mode (VCO Bypass mode)

- Normal mode

- Freerunning mode

The reference frequency  $f_R$  can be selected to be taken either from the internal oscillator  $f_{INT}$  or from an

#### **Clock Generation Unit (CGU)**

external clock source  $f_{OSC\ INT}$ .

The PLL uses up to three dividers to manipulate the reference frequency in a configurable way. Each of the three dividers can be bypassed corresponding to the PLL operating mode.

• **CCU:** The Clock Control Unit enables the selection of the source for  $f_{SYS}$ .

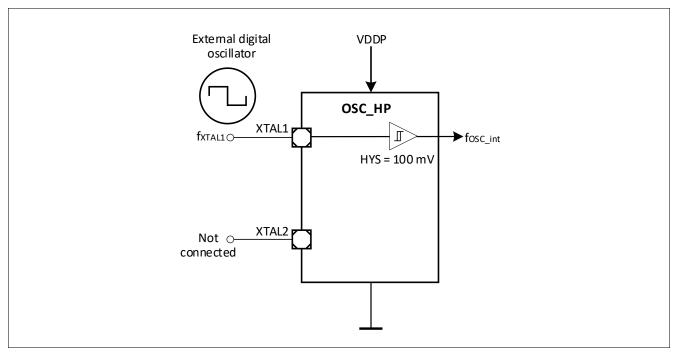

#### 3.2 External Input Clock mode

The External Input Clock mode is used to directly supply the device with an externally generated clock signal in the range from 4 MHz to 16 MHz. In this mode, the high-precision oscillator circuit is bypassed and the external clock signal is fed directly into the PLL module. The input frequency has to be 4 MHz or higher, if the prescaler mode is used.

The external clock input has to be connected to XTAL1, while XTAL2 is left open (not connected). The negative terminal of the external clock input has to be connected to the analog GND (pin 39).

Figure 7 External Input Clock mode

**Clock Generation Unit (CGU)**

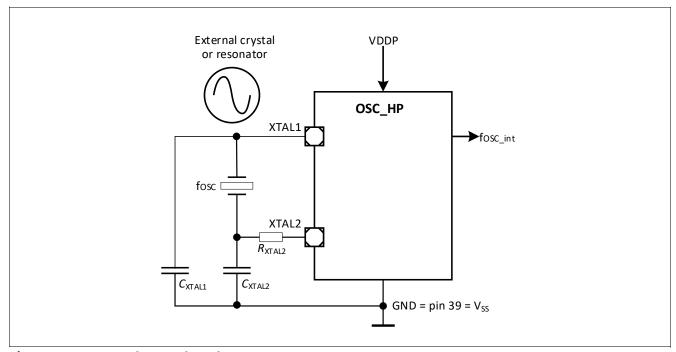

#### 3.3 External Crystal mode

The External Crystal mode is used to supply the device with an external crystal in the range from 4 MHz to 16 MHz. An external oscillator circuitry has to be placed, consisting of two load capacitors connected to XTAL1/GND and XATL2/GND and an optional series damping resistor at XTAL2. The GND pin is in this case the analog GND (pin 39).

Figure 8 External Crystal mode

The values and the corresponding operating ranges depend on the chosen crystal and have to be determined and optimized in correlation with the crystal vendor, using the negative resistance method, which is the most common test for start-up and reliability of the oscillator. This method is about the insertion of a test resistor in series with the quartz crystal and the monitoring of the drive current. Typically, this test does not result in one set of circuitry values which is the 'right one', but it indicates a recommended range. Depending on further system requirements such as XTAL1 amplitude specification or oscillator frequency, the final circuitry values of the oscillator are then selected.

More information about the test method can be found in the Infineon Application Note "Crystal Oscillator Basics AP56002".

| Symbol                                  | Function                                                                                                             | Recommended component                                       |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| C <sub>XTAL1</sub> , C <sub>XTAL2</sub> | Load capacitors for external crystal oscillator forming an LC tank circuit which determines the oscillator frequency | ≥ 10 V ceramic capacitor X7R/X8R<br>(low ESR, 0805 package) |

| R <sub>XTAL2</sub>                      | Serial damping resistor                                                                                              | 0-280 Ω                                                     |

The oscillator can operate for a specified set of crystals with known ESR and parasitic capacitances  $C_{10}$  and  $C_{0}$  up to a specific value.

Choosing different crystals requires detailed consideration of parasitics, external circuitry, frequency range, and quality of the intended crystal. Its proper operation has to be verified by testing.

**Clock Generation Unit (CGU)**

**Recommendation for oscillator load capacitors** Table 8

| f <sub>osc</sub>                | 4 MHz | 8 MHz | 12 MHz | 16 MHz |

|---------------------------------|-------|-------|--------|--------|

| $ESR_{\mathrm{typ}}$ / $\Omega$ | 120   | 90    | 80     | 70     |

| C <sub>IO</sub> / pF            | 3.5   | 3.5   | 3.5    | 3.5    |

| C <sub>O</sub> / pF             | 3     | 3     | 3      | 3      |

| $C_{XTAL1} = C_{XTAL2} / pF$    | 33    | 18    | 12     | 12     |

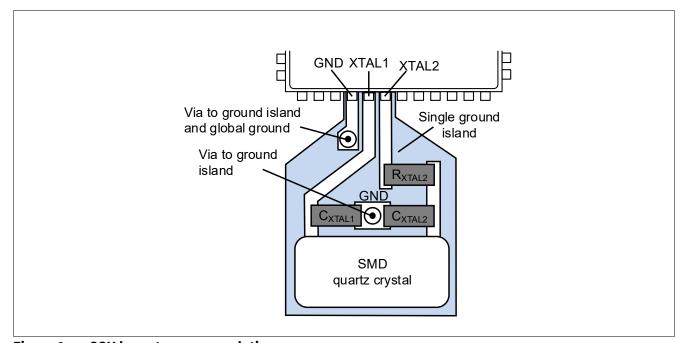

#### **Layout recommendations** 3.4

Figure 9 shows a layout example for an SMD quartz crystal to be used with the TLE987x/6x.

Figure 9 **CGU layout recommendation**

#### LIN transceiver

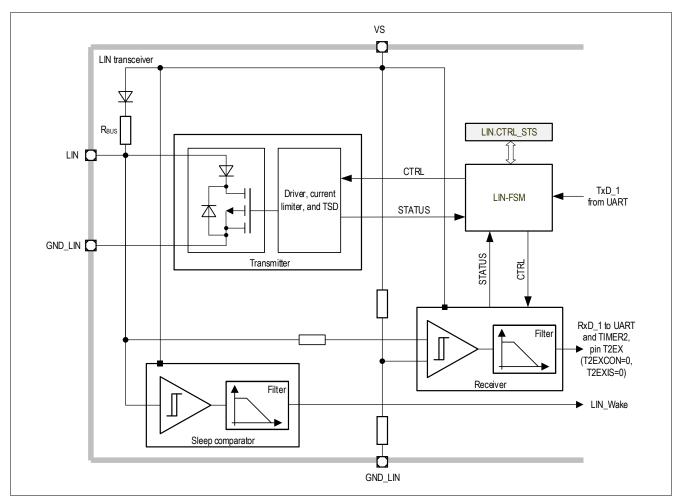

#### 4 LIN transceiver

The LIN module is a transceiver for the Local Interconnect Network (LIN), compliant to the LIN2.2 standard, backward compatible to LIN1.3, LIN2.0 and LIN2.1. It operates as a bus driver between the protocol controller and the physical network. The LIN bus is a single-wire, bidirectional bus, which is typically used for in-vehicle networks, using data rates between 2.4 kBaud and 20 kBaud. Additionally, data rates up to 115.2 kBaud are supported.

Figure 10 LIN transceiver Block Diagram

It is recommended to put a 220 pF capacitor between the LIN input and GND\_LIN pins. This complies with the LIN specification 2.2.

The GND\_LIN pin has to be connected to a global ground net outside the chip.

In order to avoid interferences with the SoC's core voltage, it is recommended to connect GND\_LIN to the same ground net of the power MOSFETs – called power GND.

To reduce digital ground bounce transmitted via LIN, GND\_LIN should not be connected directly to the GND of the TLE987x/6x. It is better to have a slight decoupling by using few millimeters of trace.

The LIN transceiver can be used also with PWM control. In this case, a pull-up resistor between the LIN input and the battery input voltage should be placed. The value of the pull-up resistor is  $\geq 1 \text{ k}\Omega$ .

In case additional filtering is needed because of EMC issues, common mode chokes before the LIN pin are not recommended. A ferrite bead placed at GND\_LIN is preferred.

# infineon

**High-voltage monitor input**

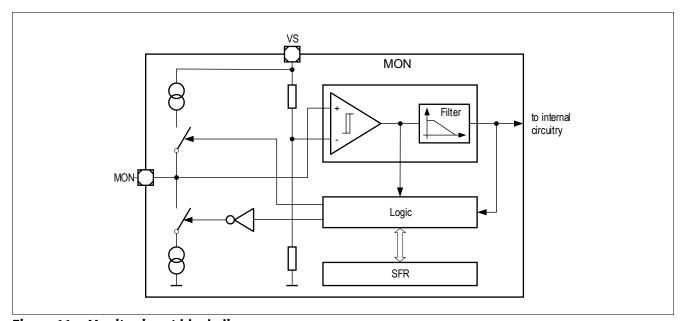

## 5 High-voltage monitor input

This module monitors external voltage to detect levels above or below a specified threshold, or it can be used in Low-Power mode to detect a wake-up event at the high-voltage MON pin.

#### 5.1 Block diagram

Figure 11 Monitor input block diagram

#### 5.2 Application hints

The functional description of the high-voltage monitor input is included in chapter 26 of the TLE987x and TLE986x User Manuals.

A dedicated R-C filter ( $R_{MON}$  and  $C_{MON}$ ) must be placed before the MON pin (**Figure 2**), in order to protect it against reverse polarity connection and voltage transients (ISO pulses), which could violate the absolute maximum ratings of the MON pin. In fact, in a typical use-case the MON pin could be directly connected to the car battery in order to sense the supply voltage, especially during power-down.

**Table 9** shows the recommended  $R_{\text{MON}}$  and  $C_{\text{MON}}$  values. The GND to be used for  $C_{\text{MON}}$  is the analog or digital GND. Since the R-C time constant affects the voltage slope on the MON pin, the  $R_{\text{MON}}$  and  $C_{\text{MON}}$  values should be selected according to the application requirements. Due to potential high peak power during transient tests, the recommended package for  $R_{\text{MON}}$  is 1206 SMD.

Table 9 Component selection for the MON pin

| Symbol           | Function         | Recommended component                                                                                   |

|------------------|------------------|---------------------------------------------------------------------------------------------------------|

| $R_{MON}$        | Filter resistor  | Min. value 1 kΩ                                                                                         |

|                  |                  | $R_{\mathrm{MON}}$ value and size selected according to the application, package 1206 SMD recommended   |

| C <sub>MON</sub> | Filter capacitor | Ceramic capacitor  Min. value 10 nF, typical voltage rating 50 V                                        |

|                  |                  | $C_{\text{MON}}$ value, voltage rating, size, and dielectric type selected according to the application |

Bridge driver (excluding charge pump)

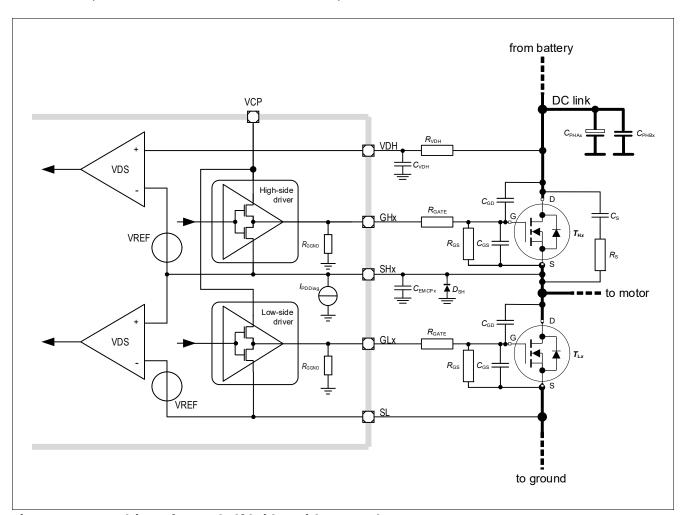

## 6 Bridge driver (excluding charge pump)

The bridge driver is intended to drive external normal-level MOSFETs in bridge configuration. This chapter provides details about external components, which are needed depending on application requirements. Detailed information about the bridge driver functioning and configuration is available in the Infineon Application Note "TLE986x/TLE987x Bridge Driver".

#### 6.1 Application diagram

The following application diagram shows the gate drivers for one half-bridge with the (partially optional) external components, which are described in this chapter.

Figure 12 Gate drivers for one half-bridge with external components

Bridge driver (excluding charge pump)

#### 6.2 **External components**

#### 6.2.1 **Overview**

| Component                        | Short description                                                                                                | Recommended value                      |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| $R_{GATE}$                       | Gate resistor (optional): suppresses potential oscillations between PCB line inductances and MOSFET capacitances | 2 Ω 10 Ω                               |  |

| $R_{GS}$                         | Gate-to-source resistor: terminates the MOSFET gate                                                              | 100 kΩ                                 |  |

| $C_{GS}$                         | Gate-to-source capacitor (optional): linearizes the intrinsic MOSFET gate-to-source capacitor                    | it depends on MOSFET                   |  |

| $C_{\sf GD}$                     | Gate-to-drain capacitor (optional): linearizes the intrinsic MOSFET gate-to-drain capacitor                      |                                        |  |

| $C_{PHAx}$                       | DC link capacitors: A buffers DC link voltage                                                                    | it depends on application requirements |  |

| $C_{PHBx}$                       | DC link capacitors: B suppresses double-digit MHz oscillations                                                   |                                        |  |

| $R_{\rm S}, C_{\rm S}$           | Snubber (optional): reduces voltage peaks and ringing at motor pin                                               |                                        |  |

| C <sub>EMCPx</sub>               | <b>EMC filter capacitor at the SHx pin</b> : suppresses fast transients at SHx                                   | 1 nF                                   |  |

| $R_{\text{VDH}}, C_{\text{VDH}}$ | Low-pass filter at the VDH pin: suppresses high-frequency components of DC link voltage                          | 1 kΩ, 1 nF 3.3 nF                      |  |

| $D_{SH}$                         | <b>Protection diode at the SHx pin (optional)</b> : limits SHx undershoot voltages                               | -                                      |  |

#### 6.2.2 **Details**

#### 6.2.2.1 **Gate resistor**

The optional gate resistor  $R_{\mathsf{GATE}}$  suppresses potential oscillations between PCB line inductances and MOSFET capacitances, which build up an LC oscillator that can be stimulated by fast transients during MOSFET switching. The value of  $R_{\text{GATE}}$  depends on the PCB layout conditions, MOSFET parasitics, and switching speed, but should be as small as possible, preferably in the range from 2  $\Omega$  to 10  $\Omega$ .

#### 6.2.2.2 **Gate-to-source resistor**

The gate-to-source resistor  $R_{GS}$  terminates the gate of the external MOSFET to its source. It should be placed as close as possible to the MOSFET to keep it turned off, for example, in the case of electromagnetic interference (EMI) or broken PCB lines. The recommended value is 100 k $\Omega$ .

#### **Hardware Design Guideline**

Bridge driver (excluding charge pump)

#### 6.2.2.3 Gate-to-source capacitor

The optional gate-to-source capacitor  $C_{GS}$  linearizes the intrinsic MOSFET gate-to-source capacitance and reduces the tolerance of the total gate-to-source capacitance seen by the gate driver. The value of  $C_{GS}$  should be large enough to dominate the intrinsic MOSFET gate-to-source capacitance  $C_{GS\_int}$ . The recommendation is:  $C_{GS} \ge 2 \times C_{GS\_int}$ .

#### **Notes**

- 1. The maximum gate charge  $Q_{tot\_max}$  per MOSFET including the external gate capacitors must not exceed 100 nC.

- 2.  $C_{GS\_int}$  is usually not directly given in MOSFET datasheets, but it can be estimated from parameters like  $C_{iss}$  or  $Q_{as}$ .

#### 6.2.2.4 Gate-to-drain capacitor

The optional gate-to-drain capacitor  $C_{\rm GD}$  linearizes the intrinsic MOSFET gate-to-drain capacitor and reduces the tolerance of the total gate-to-drain capacitance seen by the gate driver. The placement of  $C_{\rm GD}$  is recommended, if it is important for the application to have a well-controlled linear slew rate at the SHx pin:  $\Delta V_{\rm SHx} / \Delta t = I_{\rm GATE} / C_{\rm GD}$ .

#### **Notes**

- 1. The maximum gate charge  $Q_{tot\_max}$  per MOSFET including the external gate capacitors must not exceed 100 nC.

- 2. In order to avoid unintended switch-on of the MOSFET during fast transients, the following condition must be met:  $C_{GD}/C_{GS} \le 1/10$ .

#### 6.2.2.5 DC link capacitors

The DC link capacitors  $C_{\rm PHAx}$  and  $C_{\rm PHBx}$  serve two purposes:

- 1.  $C_{PHAx}$  works as a buffer capacitor.

- 2.  $C_{PHBx}$  suppresses double-digit MHz oscillations on the DC link voltage.

The total value of all DC link capacitors  $C_{\text{PH\_tot}} = \sum (C_{\text{PHAx}} + C_{\text{PHBx}})$  depends on the acceptable DC link voltage ripple caused by PMW operation and on additional application-specific requirements, like having motors operating in generator mode or the need to buffer the motor energy in the case of an emergency shutdown of the MOSFETs.

Note:  $C_{PH\_tot}$  must be large enough to always keep all connected input pins (for example, VDH, VSD) within their absolute maximum ratings.

As a starting point for the value of  $C_{\text{PH\_tot}}$ , a rule of thumb is 230  $\mu\text{F}$  per 10 A of motor current. The bigger part of the capacitance is covered by electrolytic capacitors  $C_{\text{PHAx}}$  and the rest by ceramic capacitors  $C_{\text{PHBx}}$ . It is recommended to choose capacitors with low ESR and low self-inductance and to place them close to their respective high-side MOSFETs, in order to minimize series resistances and inductances in the high-current path.

#### **Hardware Design Guideline**

Bridge driver (excluding charge pump)

#### **6.2.2.6** Snubber

The optional snubber  $R_S$  and  $C_S$  reduces voltage peaks and ringing at the motor pin, which can be caused by PCB parasitics like series inductances. The values for  $R_S$  and  $C_S$  depend on the half-bridge power ratings and on the parasitics of the selected MOSFET.

Starting values for  $R_S$  and  $C_S$  can be derived from the following constraints:

- $R_S \le V_{DClink} / I_{motor}$  in order to keep the voltage across  $R_S$  always smaller than the DC link voltage

- $C_S \ge 2 \times C_{oss}$ , where  $C_{oss}$  is the output capacitance of the MOSFET

#### **Notes**

- 1. For  $R_S$ , a resistor with very low self-inductance should be chosen. The resistor power class can be derived from the maximum energy stored in  $C_S$ .

- 2. For  $C_{S}$ , a capacitor with high peak-current capability should be chosen.

#### 6.2.2.7 EMC filter capacitor at the SHx pin

The EMC filter capacitor  $C_{\rm EMCPx}$  at the SHx pin suppresses fast transients coming from the motor pin. The recommended value is 1 nF. This capacitor should be placed as close as possible to the SHx pin.

#### 6.2.2.8 Low-pass filter at the VDH pin

The low-pass filter  $R_{\rm VDH}$  and  $C_{\rm VDH}$  at the VDH pin suppresses high-frequency components on the DC link voltage. The VDH input serves as the reference voltage of the high-side drain-source comparators and should be stable right after each MOSFET switching event. Therefore, a time constant in the range of a low single-digit  $\mu$ s value should be targeted, for example:  $R_{\rm VDH} = 1~{\rm k}\Omega$  and  $C_{\rm VDH} = 1~{\rm nF}$ .

Note:

R<sub>VDH</sub> performs an additional protection role by limiting the current out of the VDH pin in the case of a reverse-polarity event or other undershoots of the DC link voltage.

#### 6.2.2.9 Protection diode at the SHx pin

The optional protection diode at the SHx pin limits SHx undershoot voltages. This diode is only recommended if undershoots below the absolute maximum ratings may be expected due to unknown application conditions.

**Charge pump**

#### 7 Charge pump

The charge pump is intended to supply the bridge driver integrated in the TLE987x/6x, as well as the Back-EMF comparators. The purpose of this chapter is to provide a design method for the external capacitors, depending on the application requirements.

#### 7.1 **Application diagram**

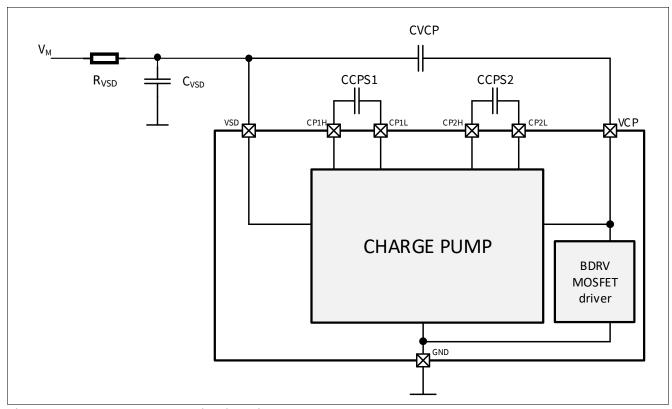

The following application diagram shows the charge pump and its external components, which are the flying capacitors CCPS1 / CCPS2 and the output capacitor CVCP. The input voltage of the charge pump is VSD, while the output voltage is VCP.

$V_{\rm M}$  is the motor voltage after the MOSFET for reverse polarity protection. An RC network can be optionally placed between  $V_{\rm M}$  and VSD.  $C_{\rm VSDM}$  is acting as filter capacitor, while  $R_{\rm VSD}$  limits the current flowing into VSD during voltage transients. The recommended values for  $C_{VSDM}$  and  $R_{VSD}$  are 1  $\mu$ F and 2  $\Omega$ .

Figure 13 Charge pump application diagram

#### 7.2 Charge pump: how it works

The voltage VCP is generated by a 2-stage charge pump, as a multiplying effect of the input voltage VSD using two flying capacitors CCPS1 and CCPS2: ideally, each stage of the charge pump can provide a voltage increase equal to the input voltage. The output capacitor CVCP acts as bulk for the voltage VCP. A detailed description of the behavior of an n-stage charge pump is available in the following literature:

- "On-Chip High-Voltage Generation in Integrated Circuits Using an Improved Multiplier Technique" by J.F. Dickson

- "Theoretical and Experimental Analysis of Dickson Charge Pump Output Resistance" by A. Cabrini, L. Gobbi, and G. Torelli

#### **Charge pump**

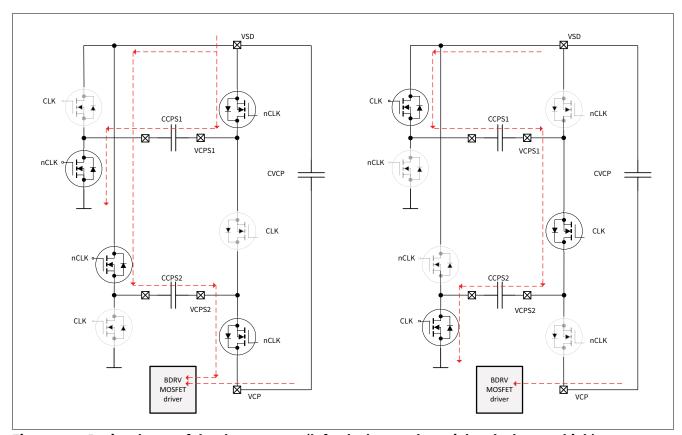

The switches of the charge pump are driven by an internal clock (CLK) with a frequency equal to  $f_{SW}$ , derived from the TLE987x/6x system clock. The following pattern applies (Figure 14):

Clock set to low: the capacitor CCPS1 is charged by VSD, while the energy of CCPS2 is transferred to the output, boosting the voltage VCP of the capacitor CVCP. Considering  $V_{DROP1}$  as the voltage drop of the switches of the first stage and ignoring the load current, the average voltage VCPS1 can be expressed as:

$$VCPS1 = 2 VSD - V_{DROP1}$$

Clock set to high: the energy is transferred from CCPS1 to CCPS2, while the output voltage VCP is buffered by the bulk capacitor CVCP. Considering  $V_{DROP2}$  as the voltage drop of the switches of the first and second stage and ignoring the load current, the average voltages VCPS2 and VCP can be expressed as:

$$VCPS2 = 3 VSD - V_{DROP2}$$

;  $VCP = 3 VSD - V_{DROP}$

where  $V_{DROP}$  is the total voltage drop of the switches of the charge pump.

Basic scheme of the charge pump (left: clock set to low; right: clock set to high) Figure 14

#### **Charge pump**

Including now the load current in the calculation, the output voltage VCP can be expressed as:

(7.1)

$$VCP = 3 VSD-V_{DROP} - R_{OUT AVG} \times ICP$$

where:

- ICP is the average output current, as sum of the bias current of the bridge driver and the total current needed to drive the MOSFETs gates;

- $R_{\text{OUT AVG}}$  is the average output resistance of the charge pump, which can be expressed as:

(7.2)

$$R_{OUT\_AVG} \approx \frac{2}{f_{SW} \times CCPS} + \frac{3}{4 \times f_{SW} \times CVCP}$$

where  $f_{SW}$  is the switching frequency of the charge pump, and CCPS1 and CCPS2 are both equal to CCPS. Considering:

$$V_{DROP} = ICP \times R_{EQ}$$

the **Equation (7.1)** can be rearranged as follows:

(7.3)

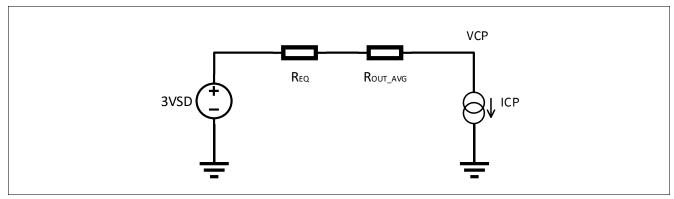

$$VCP = 3 \times VSD - ICP (R_{EQ} + R_{OUT AVG})$$

where  $R_{EO}$  is an average resistance, which takes into account of the total voltage drop  $V_{DROP}$  as soon as it varies with the output current. A value of  $R_{\rm EQ}$  fitting to the TLE987x/6x charge pump is about 100  $\Omega$ . Figure 15 shows the equivalent circuit as expressed by the **Equation (7.3)**.

Figure 15 Charge pump equivalent circuit

#### **Hardware Design Guideline**

#### **Charge pump**

Considering the wide range of the input voltage VSD, the charge pump of the TLE987x limits the output voltage VCP according to the following relations:

$$VCP - VSD \cong \begin{cases} 14 \text{ V} & \text{if } VCP - VSD \ge 14 \text{ V} \\ VCP - VSD & \text{if } VCP - VSD < 14 \text{ V} \end{cases}$$

Important to note is that the above equations are aiming to provide an equivalent model of the charge pump considering average values of the electrical parameters, not RMS (root medium square) values. For this reason, they should not be used straightforward to calculate the power dissipation of the charge pump itself.

#### 7.2.1 ICP load current calculation

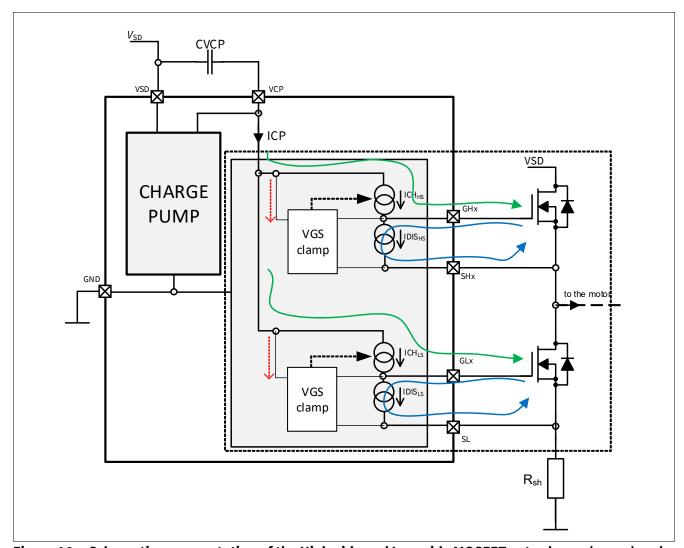

The load current ICP of the charge pump is the sum of the currents supplied to each gate, and the bias current of the bridge driver. In **Figure 16** the gate charge and discharge current paths are shown. Referring to this figure, the following equations can be derived:

(7.4)

$$ICP = N_G \times (ICP_M + I_{BIAS})$$

(7.5)

$$ICP_M = N_M \times f_{PWM} \times Q_M$$

(7.6)

$$Q_M = Q_{MOSFET} + CGS_{ext} \times VGS + CGD_{ext} \times VGD$$

#### where:

- $N_G$  is the number of half-bridge drivers active in one PWM switching period. This value depends on the PWM switching scheme and the control technique used in the application. Considering a 3-phase motor,  $N_G$  is equal to 1 with block commutation, while  $N_G$  is equal to 3 with FOC (Field Oriented Control).

- *ICP*<sub>M</sub> is the current of each half-bridge gate driver.

- I<sub>BIAS</sub> is the bias current of each single half-bridge driver. A typical for I<sub>BIAS</sub> value is about 2 mA.

- N<sub>M</sub> is the number of MOSFETs turned on in one PWM switching period. This value depends on the PWM switching scheme and the control technique used in the application. For block commutation and FOC N<sub>M</sub> is equal to 2.

27

f<sub>PWM</sub> is the PWM switching frequency.

**Application Note**

# infineon

#### **Charge pump**

- Q<sub>M</sub> is the total charge transferred to the High-Side (HS) and/or Low-Side (LS) gate, including the charge of

external capacitors.

- $Q_{MOSFET}$  is the gate charge of the HS (and/or LS) gate present at a certain VGS.

- **CGS**<sub>ext</sub> is the value of the external gate to source capacitance.

- **VGS** is the gate to source voltage.

- CGD<sub>ext</sub> is the value of the external gate to drain capacitance.

- **VGD** is the gate to drain voltage.

Figure 16 Schematic representation of the High-side and Low-side MOSFET gate charge (green) and discharge (blue) currents paths (left). Bias current in red. Each gate driver block is repeated 3× in the TLE987x, while 2× in the TLE986x.

#### **Hardware Design Guideline**

#### **Charge pump**

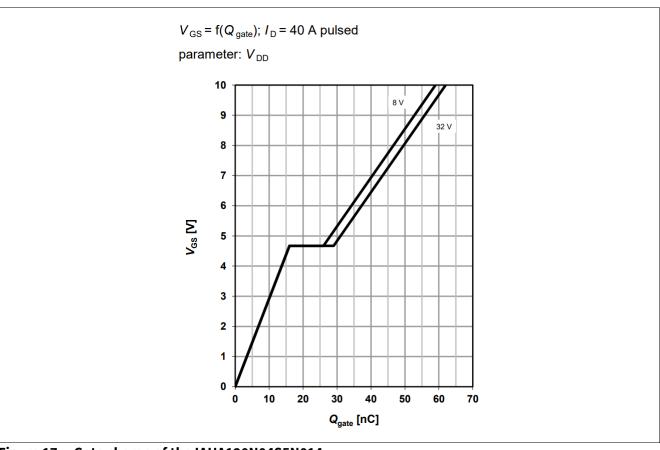

The gate charge  $Q_{MOSFET}$  can be determined from the characteristics of the MOSFET. A typical gate charge graph of an automotive Infineon MOSFET (IAUA120N04S5N014) is shown in the Figure 17.

Figure 17 Gate charge of the IAUA120N04S5N014

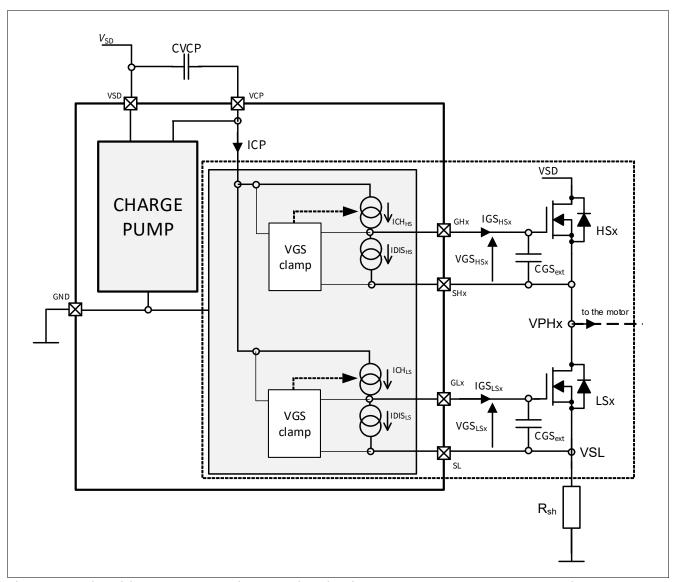

In the bridge driver implementation of the TLE987x/6x, the HS and LS gate source voltages VGS are limited by an internal clamping. In **Figure 18** a simplified schematic of the bridge driver is illustrated. It can be assumed that the MOSFETs ON-resistances and the current sensing resistor  $R_{\rm sh}$  are in the order of magnitude of [m $\Omega$ ]. As a consequence the following approximations can be made:

- When **HSx** is **ON** and **LSx** is **OFF** → VPHx ≅ VSD

- When LSx is ON and HSx is OFF → VPHx ≅ VSL ≅ GND

Taking this into account, the typical average  $VGS_{HS}$  (for the HS) and  $VGS_{LS}$  (for the LS) voltages can be estimated as:

(7.7)

$$VGS_{HS} \cong \begin{cases} 12.5 \text{ V} & \text{if } VCP - VSD \ge 14 \text{ V} \\ VCP - VSD - 1.5 \text{ V} & \text{if } VCP - VSD < 14 \text{ V} \end{cases}$$

$$VGS_{LS} \cong \begin{cases} 12.5 \text{ V} & \text{if } VCP \ge 14 \text{ V} \\ VCP - 1.5 \text{ V} & \text{if } VCP < 14 \text{ V} \end{cases}$$

# infineon

#### **Charge pump**

Figure 18 Simplified BDRV block diagram with highlight on gate-source voltage clamping. Each gate driver block is repeated 3× in the TLE987x, while 2× in the TLE986x.

A calculation example is provided here below, where no capacitors are connected to the MOSFETs gates and FOC control with a 3-phase motor is used. For sake of simplicity, we can assume VGS to have the same value for HS and LS, as well as to be independent from ICP.

• Assumptions:

$N_{M}=2$  ;  $f_{PWM}=20\,kHz$  ;  $Q_{MOSFET}\cong60\,nC$  ;  $VGS=12.5\,V$

#### **Hardware Design Guideline**

#### **Charge pump**

• Considering VGS equal to 12.5 V, the gate charge should be consequently increased, since the 60 nC are estimated for VGS = 10 V.

$$Q_{MOSFET} \cong 60 \text{ nC} \times \frac{12.5 \text{ V}}{10 \text{ V}} = 75 \text{ nC}$$

The current for each gate driver is equal to:

$$ICP_M = N_M \times f_{PWM} \times Q_{MOSFET} \cong 3 \text{ mA}$$

The total ICP current is:

$$ICP = 3 \times (ICP_M + I_{BIAS}) \cong 15 \text{ mA}$$

Another calculation example is provided here below, where a capacitor is placed between gate and source, and no capacitor between gate and drain is connected. The control scheme is always FOC. For sake of simplicity, we can assume VGS and VGD to have the same value for HS and LS, as well as to be independent from ICP.

· Assumptions:

$$N_{M} = 2$$

;  $f_{PWM} = 20 \text{ kHz}$  ;  $Q_{MOSFET} = 60 \text{ nC}$

$VGS = VGD = 12.5 \text{ V}$  ;  $CGS_{ext} = 1 \text{ nF}$

The charge for each gate is then:

$$Q_M = 60 \text{ nC} \times \frac{12.5 \text{ V}}{10 \text{ V}} + 12.5 \text{ V} \times 1 \text{ nF} \cong 88 \text{ nC}$$

• The current for each gate driver is equal to:

$$ICP_M = N_M \times f_{PWM} \times Q_M \cong 3.5 \text{ mA}$$

The total ICP current is:

$$ICP = 3 \times (ICP_M + I_{BIAS}) \cong 16.5 \text{ mA}$$

**Charge pump**

#### 7.3 Charge pump external capacitors design

The flying capacitors CCPS1 and CCPS2 boost the input voltage VSD to generate the output voltage VCP, while the output capacitor CVCP is acting as bulk capacitor. The selection of the values and type should consider the following requirements:

- **VCP voltage in steady state**: as shown in the **Equation (7.1)**, the output voltage depends also on the value of the charge pump capacitors.

- **Voltage ripple**: the ripple of the flying capacitors can be expressed as:

(7.8)

$$V_{ripple} = \frac{ICP}{f_{SW} \times C}$$

where C is the value of the capacitor. The voltage ripple of the output capacitor CVCP is equal to the one of the flying capacitors, but divided by 2.

- **Dynamic response**: the higher the value of the capacitors, the slower will be the start-up time and the response to load changes. In a typical TLE987x/6x application, this requirement is not critical.

- Losses due to ESR (Equivalent Series Resistance): the higher the value of the capacitors, the higher will be the ESR and so the losses. Using ceramic capacitors, the losses can be considered as not relevant in this application.

- **DC bias voltage**: ceramic capacitors exhibit lower capacitance values, when the applied voltage increases. According to the point of load and the desired capacitance value, the voltage rating should be adequately selected. For a typical application, 50 V capacitors are recommended.

Here a method is presented to select the charge pump capacitors:

- 1. Define the type of MOSFETs of the application.

- 2. Define the switching frequency  $f_{PWM}$  of the bridge driver.

- 3. Calculate the load current ICP, as described in the **Equation (7.4)**.

- 4. Calculate the preliminary values of CCPS and CVCP using the **Equation (7.8)**. As a rule, we can consider a maximum ripple of 0.5 V for the flying capacitors CCPS and 0.25 V for CVCP. Moreover, at least 50% higher capacitance should be taken into account of the DC bias.

- 5. Calculate  $R_{\text{OUT AVG}}$  using the **Equation (7.2)**.

- 6. Calculate  $V_{DROP}$  using the **Equation (7.3)**.

- 7. Calculate VCP voltage using the **Equation (7.3)**.

- 8. Calculate the voltage VCP vs. VSD using the **Equation (7.7)**, checking that the gates are driven with a sufficient voltage in the input voltage range VSD, as required by the application.

The recommended values are 220 nF for the flying capacitors (CCPS1 / CCPS2), and 470 nF for the output capacitor (CVCP). These values allow to have a VCP voltage sufficiently high within the nominal working conditions of the charge pump, as well as a low voltage ripple in the load current range.

#### **Hardware Design Guideline**

**Charge pump**

#### 7.3.1 Calculation example

A calculation example is provided here below.

- 1. Identify the MOSFETs, for example: IAUA120N04S5N014.

- 2. Define the switching frequency:

$$f_{PWM} = 20 \text{ kHz}$$

3. Calculate ICP, considering VGS = 12.5 V,  $N_{\rm M}$  = 2, and no external capacitors connected to the gates:

$$ICP \cong 15 \text{ mA}$$

4. Calculate preliminary values for CCPS and CVCP, considering a charge pump frequency of 250 kHz and a voltage ripple of 0.4 V and 0.1 V for CCPS and CVCP respectively.

CCPS =

$$150 \text{ nF} \rightarrow +50\% \rightarrow 220 \text{ nF}$$

CVCP =  $300 \text{ nF} \rightarrow +50\% \rightarrow 470 \text{ nF}$

5. Calculate R<sub>OUT AVG</sub>:

$$R_{OUT\_AVG} = 43 \Omega$$

$ICP \times R_{OUT_{AVG}} \cong 0.65 V$

6. Calculate the voltage drop:

$$V_{DROP} = ICP \times R_{EQ} \cong 1.5 \text{ V}$$

7. Calculate VCP vs. VSD:

$$VCP - VSD \cong 2 \times VSD - 2.2 V$$

8. Considering 8 V – 18 V as VSD voltage range, calculate the voltages VCP vs. VSD,  $VGS_{HS}$  and  $VGS_{LS}$ :

|            | VCP-VSD | VGSHS  | VGSLS  |

|------------|---------|--------|--------|

| /SD = 18 V | 14 V    | 12.5 V | 12.5 V |

| 12 V       | 14 V    | 12.5 V | 12.5 V |

| 10 V       | 14 V    | 12.5 V | 12.5 V |

| 8 V        | 13.8 V  | 12.3 V | 12.5 V |

From the table, the minimum VGS voltage is equal to 12.3 V, so the MOSFETs can be correctly driven in every condition.

**Current Sense Amplifier**

## 8 Current Sense Amplifier

The Current Sense Amplifier (CSA) is an analog circuit capable for amplifying a differential input voltage by a programmable gain *G*.

Despite being actually a voltage amplifier, it is specifically designed for shunt current measurements. For this purpose, the pins OP2 ad OP1 are connected to the terminals of a suitably designed shunt resistor, through which the current to be measured flows, and a filter network.

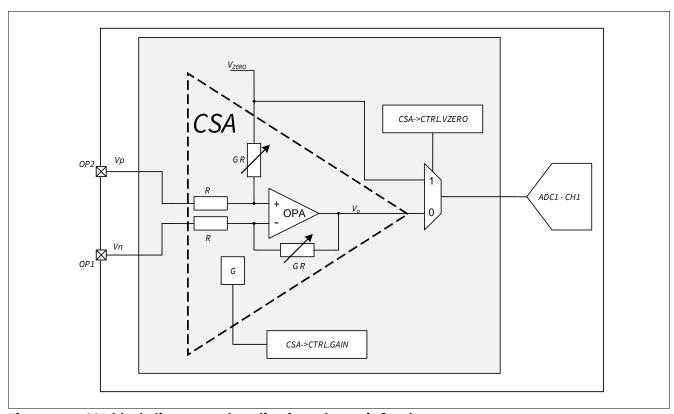

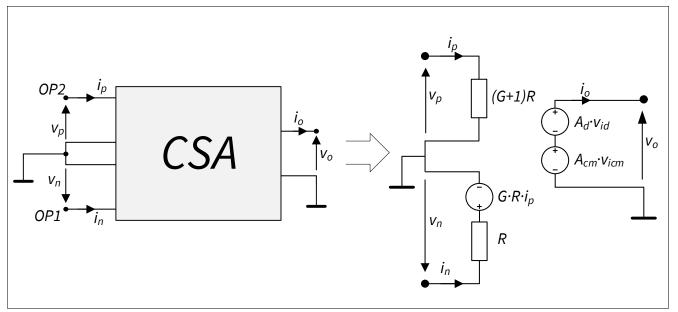

## 8.1 Block diagram

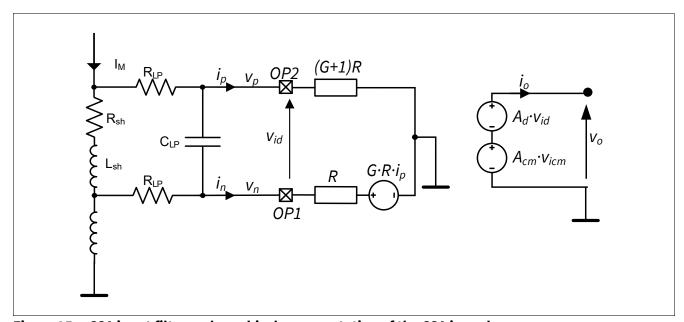

Figure 19 CSA block diagram and application schematic for shunt current measurement

**Current Sense Amplifier**

#### 8.2 Functional description

**Figure 19** shows the block diagram of the CSA together with the registers and logic related to its setup. The amplifier is built around an OPA configured as a differential amplifier with an output voltage offset. The amplifier's output is permanent connected to the ADC1 channel 1, which means it is loaded by a fixed impedance. It is an integrated closed loop amplifier and it can be used only as such. What follows will describe the entire CSA configuration and behavior.

#### 8.2.1 DC characteristics

The differential input voltage is defined as:

(8.1)

$$V_{id} = OP2 - OP1 = V_p - V_n$$

The ideal DC transfer characteristics can be calculated as:

(8.2)

$$V_o = V_{ZERO} + G V_{id}$$

$V_{ZERO} = 0.4 VAREF$

$V_{id} = 0 \rightarrow V_o = V_{ZERO}$

where  $V_{\rm ZERO}$  is the **output voltage offset** and VAREF is the reference voltage of ADC. If, for example, VAREF is generated by the internal reference voltage generator, its nominal value is 5 V. As a consequence  $V_{\rm ZERO}$  = 2 V, which allows the ADC1 channel 1 to measure positive and negative values of  $V_{\rm id}$ .

The **linear output voltage range** of the amplifier is (see P\_13.1.4 of the datasheet):

(8.3)

min, max

$$\{V_o\} = V_{OUT} = V_{ZERO} \pm 1.5 V$$

With the use of the internal VAREF generator,  $V_o$  can assume any value between 0.5 V and 3.5 V.

The  $V_0$  range limits the **differential linear input range**, which also depends on the gain setting according to (see P\_13.1.1 of the datasheet):

(8.4)

$$min, max{V_{id}} = V_{IX} = \pm 1.5 \text{ V/G}$$

Outside these ranges, the CSA characteristics are not linear and therefore undefined.

#### **Hardware Design Guideline**

#### **Current Sense Amplifier**

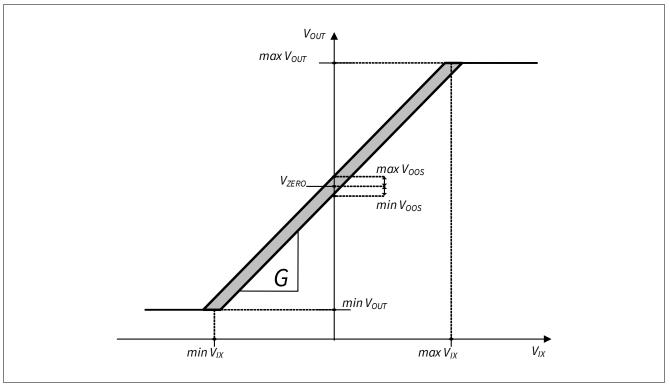

Because it is not an ideal circuit, the OPA exhibits **an input offset**  $V_{OS}$ . Because of this, the output voltage can be expressed by:

(8.5)

$$\begin{aligned} V_{o} &= V_{\rm ZERO} + G \; (V_{\rm id} \pm V_{\rm OS}) \\ V_{\rm id} &= 0 \rightarrow V_{o} = V_{\rm ZERO} \pm G \; V_{\rm OS} = V_{\rm ZERO} \pm V_{\rm OOS} \end{aligned}$$

This implies that the direct measurement of  $V_{\rm ZERO}$  by means of CSA->CTRL.VZERO = 1 will differ from the value of  $V_{\rm o}$  with  $V_{\rm id}$  = 0 with CSA->CTRL.VZERO = 0. This difference equals to the **output offset**  $V_{\rm OOS}$  (see parameter P\_13.1.17). These measurements can be used to calculate this difference in the application software and to compensate the offset.

The **common mode input voltage** is defined as:

(8.6)

$$V_{icm} = \frac{OP2 + OP1}{2} = \frac{V_p + V_n}{2}$$

Considering also the contribution of  $V_{\text{icm}}$  and **the common mode rejection ratio** DC\_CMRR (see parameter P\_13.1.8 for grade 1 in conjunction with P\_13.1.27 for grade 0 devices), the **DC characteristics** can be expressed as:

(8.7)

$$V_{o} = V_{ZERO} \pm V_{OOS} + G (V_{id} + V_{icm} / CMRR_{lin})$$

$$CMRR_{lin} = 10^{\frac{DC CMRR}{20}}$$

**Figure 20** shows a graphical representation of the **differential DC characteristics** and the input/output range.

## **(infineo**

#### **Current Sense Amplifier**

Figure 20 Differential DC characteristics

#### 8.2.2 AC characteristics

The CSA can be modeled as a three-ports network with two input ports and one output port, as shown in **Figure 21**. The two input ports represent OP2 and OP1, while the output port represents  $V_{\text{OUT}}$ . Voltages for all three ports refer to the ground potential GND.

By considering the specific characteristics of the CSA, the three-port network can be expressed as:

(8.8)

$$\begin{cases} v_o = A_d v_{id} + A_{cm} v_{icm} \\ v_p = Z_{pp} i_p + Z_{pn} i_n \\ v_n = Z_{np} i_p + Z_{nn} i_n \end{cases}$$

where:

(8.9)

$$\begin{cases} v_{id} = v_p - v_n \\ v_{icm} = \frac{v_p + v_n}{2} \end{cases}$$

37

#### **Current Sense Amplifier**

The first equation in **Equation (8.8)** represents the output behavior, while the other two represent the input behavior of the CSA. The nominal value of the input impedances can be expressed as:

(8.10)

$$Z_{pp} = \frac{v_p}{i_p}\Big|_{i_n = 0} = (G+1) R \qquad Z_{pn} = \frac{v_p}{i_n}\Big|_{i_p = 0} = 0$$

$$Z_{np} = \frac{v_n}{i_p}\Big|_{i_n = 0} = G R \qquad Z_{nn} = \frac{v_n}{i_n}\Big|_{i_p = 0} = R$$

Figure 21 CSA AC simplified three-ports model

**Figure 21** shows a schematic representation of the input equations and its impedances. This representation together with the equations are necessary to design the external current-sensing and filtering network.

The resistors R have nominal values of 1.25 k $\Omega$  (see P\_13.1.25 of the datasheet), and G changes according the programmed gain.

The closed-loop nature of the CSA ensures the stability is guaranteed in any application condition. The **open-loop transfer function** of the CSA together with its **gain and phase margins** are designed and fixed for each *G* gain configuration. Therefore, only the **closed-loop** transfer functions are described here.

The **DC common mode gain** can be derived from the CMRR as:

(8.11)

$$A_{cm} = \frac{A_d}{CMRR}$$

#### **Hardware Design Guideline**

#### **Current Sense Amplifier**

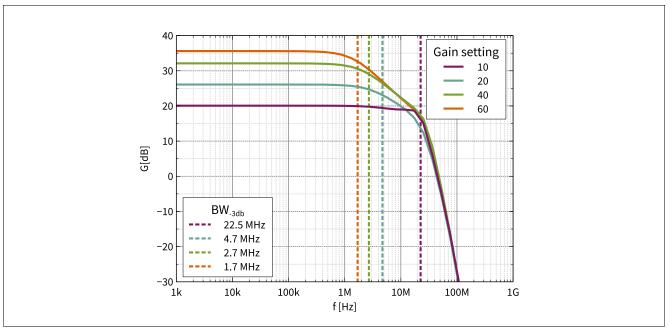

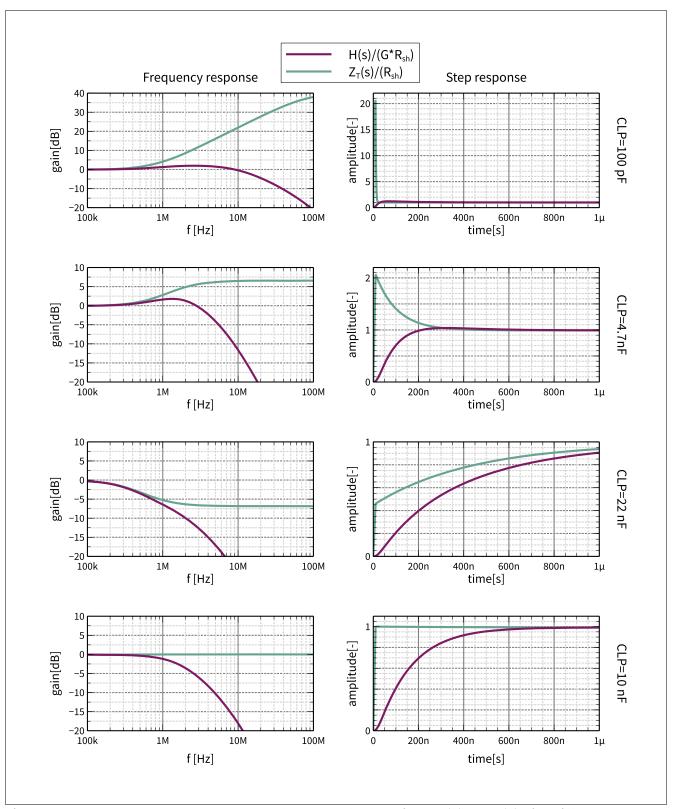

The typical AC differential gain transfer function is shown in Figure 22 and defined as:

(8.12)

$$A_d(s) = \frac{v_o(s)}{v_{id}(s)}$$

A simplified analytical expression for each transfer function can be used in order to identify the typical frequency and time-domain parameters. A dominant-pole approximation of  $A_d(s)$  is:

(8.13)

$$A_d(s) = \frac{v_o(s)}{v_{id}(s)} \approx \frac{G}{\left(\frac{s}{\omega_p} + 1\right)^4}$$

AC differential gain transfer function

The typical values of  $\omega_n$  for each gain setting are shown in **Table 10**. Being a 4<sup>th</sup>-order transfer function, its step response in the time domain has a quite complex analytical expression. However, we can still define the time constant  $\tau_p$  and its relation to the settling time  $T_s$ :

(8.14)

$$\tau_{\rm p} = \frac{1}{\omega_{\rm p}}$$

$T_{\rm s} \approx 9 \, \tau_{\rm p}$

The **settling time**  $T_s$  is defined as the time between the instant when the step is applied at  $V_{id}$  and the instant in which  $V_0$  remains confined within  $\pm 2\%$  of its final value. **Table 10** shows the values of the estimated typical  $T_{\rm s}$  and  $\tau_{\rm p}$  for each gain setting.

#### Hardware Design Guideline

**Current Sense Amplifier**

Table 10 Typical values for gain settings

| Gain [V/V]            | 10  | 20  | 40  | 60  |  |

|-----------------------|-----|-----|-----|-----|--|

| $\omega_{p}$ [Mrad/s] | 50  | 27  | 17  | 12  |  |

| $\tau_p$ [ns]         | 20  | 37  | 57  | 84  |  |

| Settling time [ns]    | 185 | 330 | 520 | 760 |  |

#### 8.3 Application hints

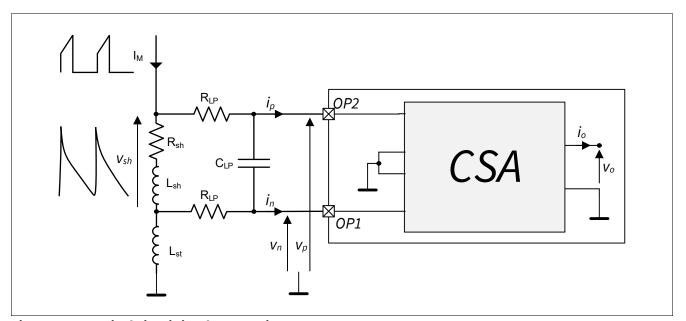

The CSA is designed to measure the differential voltage across a shunt resistor through which the current to be measured flows. A typical circuit implementation of the sensing network is shown in **Figure 23**.

Because of the parasitic inductance introduced by the shunt resistor and the PCB traces, the signal across the shunt resistor presents spikes and ringings. This effect must be compensated by a filtering network as shown in **Figure 23**.

**Chapter 8.3.1** and **Chapter 8.3.2** describe a procedure for designing the shunt resistor and the filter network.

Figure 23 Typical circuit implementation

#### 8.3.1 Shunt resistor selection

In a typical application, the input pins OP2 and OP1 are connected to an external shunt resistor so that:

(8.15)

$$V_{id} = R_{sh}I_{M}$$

$$V_{o} = V_{ZERO} + GR_{sh}I_{M}$$

where  $I_{\rm M}$  is the current to measure, and  $R_{\rm sh}$  is the nominal resistance of the shunt resistor. This equation represents the ideal DC behavior of the CSA, so it is only valid once all the dynamics of the system are eliminated. However, it is still a valid design equation for the choice of  $R_{\rm sh}$  and G.

#### **Hardware Design Guideline**

#### **Current Sense Amplifier**

Indeed, because of the limited output voltage range of the CSA, one has to consider the behavior under maximum current:

(8.16)

$$V_o^{\text{max}} = V_{ZERO} + 1.5 \text{ V} > V_{ZERO} + G R_{\text{sh}} I_M^{\text{max}}$$

This leads to the 1st design equation:

(8.17)

$$R_{sh} < R_{sh}^{max} = \frac{1.5 \text{ V}}{\text{G I}_{M}^{max}}$$

Note: This equation should be used so that  $R_{sh}$  is as close as possible to its maximum limit in order to take the greatest advantage of the  $V_o$  range.

Since the output voltage is eventually measured by the ADC1 channel 1, one has to consider the relation between the current resolution  $\Delta I_{\rm M}$  and the ADC1 resolution  $\Delta V_{\rm O}$ :

(8.18)

$$\Delta V_o = \frac{VAREF}{2^{10}-1} < G R_{sh} \Delta I_M^{min}$$

Using the internal reference leads to  $\Delta V_o \approx 4.5$  mV. From this condition, the **2<sup>nd</sup> design equation** derives:

(8.19)

$$R_{sh} > R_{sh}^{min} = \frac{\Delta V_o}{G \Delta I_M^{min}}$$

Note: This equation should be used so that  $R_{sh}$  is as far as possible to its minimum limit.

Another effect to consider is the power dissipation of the shunt resistor:

(8.20)

$$P_{D_{sh}} = R_{sh}I_{M_{RMS}}^2$$

41

#### **Hardware Design Guideline**

#### **Current Sense Amplifier**

In order to limit the power dissipation to a certain value  $P_{\rm Dsh}^{\rm max}$ , the **3<sup>rd</sup> design equation** should be applied:

(8.21)

$$R_{sh} < R_{sh}^{D} = \frac{P_{D_{sh}}^{max}}{I_{M_{RMS}}^{2}}$$

The following **considerations** are also relevant when selecting a shunt resistor:

- 1. The higher the gain, the lower the bandwidth, as seen in Figure 22.

- 2. The values of commercial current sensing resistors are discrete and limited.

- 3. More shunt resistors in parallel are possible to increase the total maximum power dissipation.

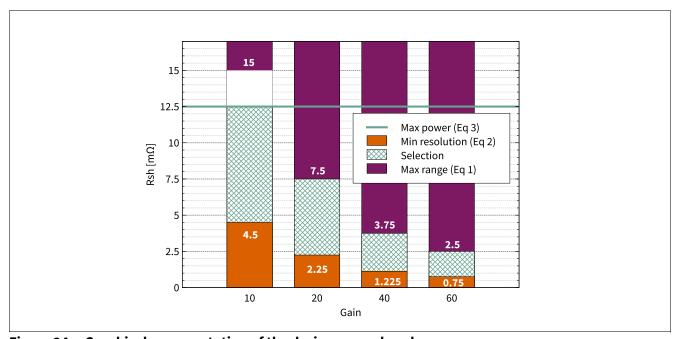

#### Design example: Selecting a shunt resistor

- $I_{M}(t)$  is a square-wave current with:

- $-I_{\rm M}^{\rm max} = 10 {\rm A}$

- $-I_{M}^{min}=0$  A

- Duty cycle = 80%

- VAREF = 5 V (internal)

- $\Delta I_{\rm M}^{\rm min} = 100 \, \rm mA$

- $P_{Dsh}^{max} = 1 \text{ W}$

To find the suboptimal shunt resistance, the best approach is to consider the three design equations for each gain setting  $G = \{10, 20, 40, 60\}$ :

1. From the 1<sup>st</sup> design equation (**Equation (8.17)**):

(8.22)

$$R_{sh} < R_{sh}^{max} = \frac{1.5 \text{ V}}{G \cdot 10 \text{ A}} = \{15; 7.5; 3.75; 2.5\} \text{ m}\Omega$$

2. From the 2<sup>nd</sup> design equation (**Equation (8.19)**):

(8.23)

$$R_{sh} > R_{sh}^{min} = \frac{4.5 \text{ mV}}{G \cdot 100 \text{ mA}} = \{4.5; 2.25; 1.225; 0.75\} \text{ m}\Omega$$

3. From the 3<sup>rd</sup> design equation (Equation (8.21)):

(8.24)

$$R_{sh} < R_{sh}^{D} = \frac{1 \text{ W}}{80 \text{ A}^2} = 12.5 \text{ m}\Omega$$

#### **Hardware Design Guideline**

#### **Current Sense Amplifier**

Figure 24 shows a graphical representation of the design equations above. It shows that any gain setting can fit the case, given that  $R_{\rm sh}$  falls in the selection area.

On the base of this analysis and considerations 1. and 2., a suboptimal choice for this use case would be a 7-m $\Omega$  resistor with a gain setting G = 20. This will lead to the following actual values:

(8.25)

$$V_o^{max} = 2 + 20 \cdot 7 \text{ m}\Omega \cdot 10 \text{ A} = 3.4 \text{ V}$$

$$\Delta I_M = \frac{4.5 \text{ mV}}{20 \cdot 7 \text{ m}\Omega} \approx 32.2 \text{ mA}$$

$$P_{D_{sh}} = 7 \text{ m}\Omega \cdot 80 \text{ A}^2 = 560 \text{ mW}$$

Figure 24 Graphical representation of the design example values

#### **Hardware Design Guideline**

#### **Current Sense Amplifier**

#### Filter network selection 8.3.2

The goal of the filter network design is to shape the dynamics of the CSA input voltage so that it is the best representation of the measured current. In practice, the design goal is to choose the values of the low pass filter components  $R_{LP}$  and  $C_{LP}$  that damp the ringings caused by the parasitic inductance  $L_{sh}$ .

$V_{\rm o}$  as function of  $I_{\rm M}$  needs to be expressed. We could do this in the time domain, but the AC analysis in the frequency domain can simplify the design procedure. The total CSA gain transfer function can be defined as:

(8.26)

$$H_{(s)} = \frac{v_o(s)}{i_M(s)}$$

Further H(s) can be broken down as a function of the CSA differential and common mode gains from the input pins OP2 and OP1 to the input of the ADC1:

(8.27)

$$H_{(s)} = \frac{v_o(s)}{i_M(s)} = \frac{A_d(s)v_{id}(s) + A_{cm}(s)v_{icm}(s)}{i_M(s)} \approx \frac{v_{id}(s)}{i_M(s)}A_d(s)$$

The above simplification is possible because both the common-mode input signal and gain are Note: negligible compared to the differential ones.

In the frequency domain, the design goal mentioned above translates into obtaining a response as flat as possible, ideally a constant response across the whole frequency spectrum. As known  $A_d(s)$  has a flat gain, but within limited bandwidth (see Figure 22 and Table 10), so the effect of the shunt and filter network has to preserve this level of fidelity.

CSA input filter and graphical representation of the CSA impedances Figure 25

#### **Hardware Design Guideline**

#### **Current Sense Amplifier**

In conclusion, the best dynamic performance obtainable (without introducing any additional reactive device) is the one of the CSA. This requires:

(8.28)

$$Z_{T}(s) = \frac{v_{id}(s)}{i_{M}(s)} = R_{sh}$$