#### Features

- Compatible with Infineon's OptiMOS<sup>™</sup>

- Compatible with Infineon's Linear FET

- Wide input voltage range: -6.5 V to -80 V

- Transient withstand: up to -100 V for 500 ms

- Dedicated current and voltage ADCs: 12-bit

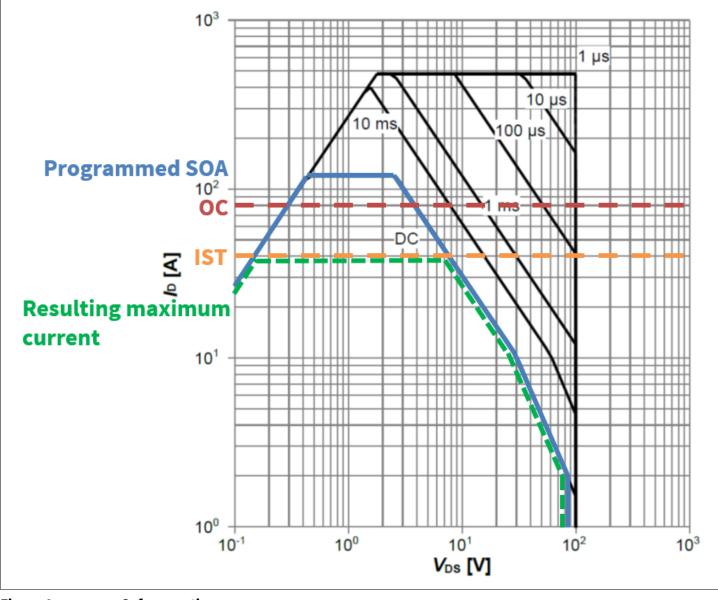

- Programmable and pre-set FET active SOA protection

- Integrated gate driver for external N-Channel MOSFET

- Configurable fast FET's shut down: two step turn-off or 1.5 A pull-down current

- PMBus interface: 1 MHz

- Precision input and output voltage monitoring and reporting: ≤ 0.5%

- Precision FET's current monitoring and reporting: ≤ 1.3% at full ADC range

- Precision input power monitoring and reporting: ≤ 1.8%

- Energy monitoring and reporting

- Programmable input and output OV and UV protections

- Support for external temperature sensor and OT protection

- Sequential turn-on capability

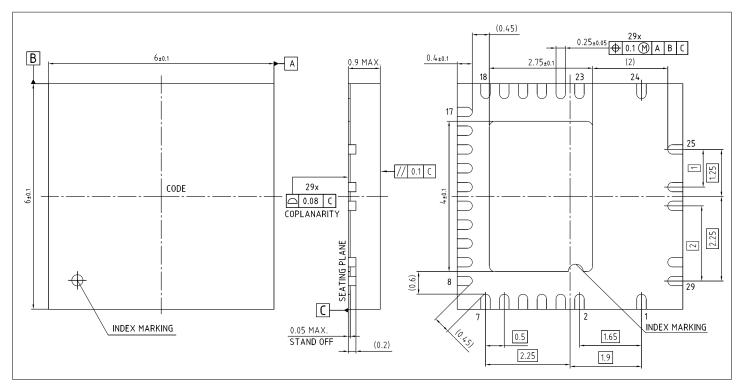

- 29-lead (6 mm x 6 mm) VQFN package

- -40°C to 125°C junction temperature

#### **Potential applications**

- -48 V Pre-Isolated DC/DC Telecom infrastructure

- -24 V/-48 V Industrial systems

- Power distribution systems

- Intelligent e-fuse

- Network router and switches

#### **Product validation**

Qualified for industrial applications according to the relevant tests of JEDEC47/20/22.

#### Description

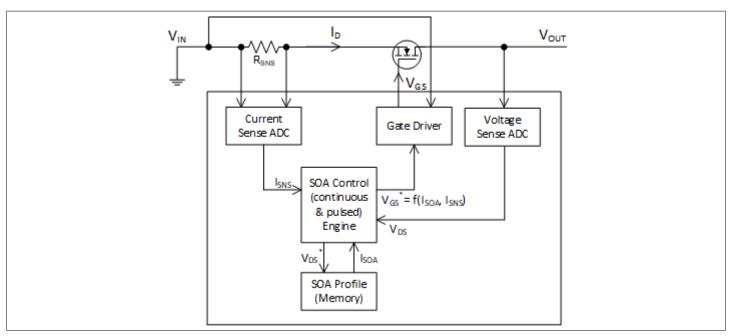

XDP700 is a wide input voltage Hot Swap and System monitoring Controller IC that drives a single or multiple parallel N-Channel MOSFETs. In addition to a controlled turn ON, XDP700 provides continuous system health monitoring and communication to the main MCU via PMBus interface. The high speed communication through PMBus allows system designers to disable the downstream sub-systems fully or partially.

It incorporates an extensive variety of system protections for safety operation and generates various protection responses depending on the severity of the incident. Latch off, reset, system shutdown and retry are some examples of response types. Its SOA protection effectively ensures that the system FET always operates under safe condition.

Please read the sections "Important notice" and "Warnings" at the end of this document

#### XDP700-001 - XDP700-002 Comparison table

The following is a summary of the improvements and features added to XDP700-002

- Support SMBAlert, Connector good disconnect (CGDN) pin feature

- Supports SMBus alert response address (ARA)

- PMBus enable, LED and Restart features added.

- Configurable Vin UV Fault hysteresis.

- More Infineon FETs SOA profiles added.

- Size of turn off control register has been increased to 10-bits to allow more control over FET turn off.

- More options added to Watchdog timer, UV\_EN deglitch timer, SOAD timer and Startup current limit (IST).

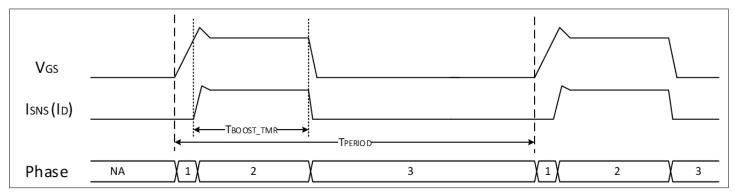

- Modifications to boost mode with addition of full boost feature.

- Programmable multiplication factor for boost mode.

Description

- Minimum regulation current down to 0.25A is achievable.

- Improved telemetry accuracy

Besides these added features, all erratas have been fixed and some features were improved in XDP700-002. For more information please consult XDP7xx-001 - XDP7xx-002 compatibility and migration application note.

İnfineon

Table of contents

## Table of contents

|        | Table of contents                | 3  |

|--------|----------------------------------|----|

| 1      | Block diagram                    | 5  |

| 2      | Pin configuration and package    | 6  |

| 3      | General product characteristics  | 12 |

| 3.1    | Absolute maximum ratings         | 12 |

| 3.2    | Functional range                 |    |

| 3.3    | Thermal characteristics          | 15 |

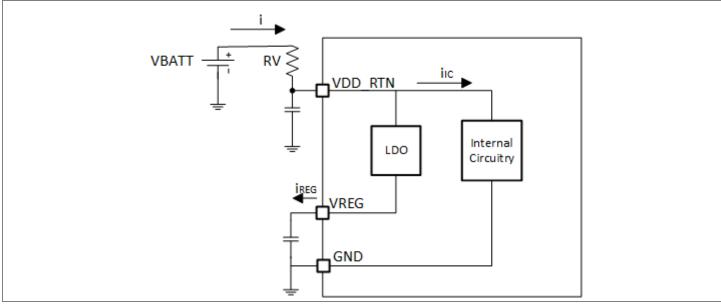

| 3.4    | Current consumption              | 16 |

| 3.5    | ESD robustness                   | 16 |

| 3.6    | Electrical characteristics       | 16 |

| 3.7    | Timing characteristics           | 25 |

| 4      | Product features                 |    |

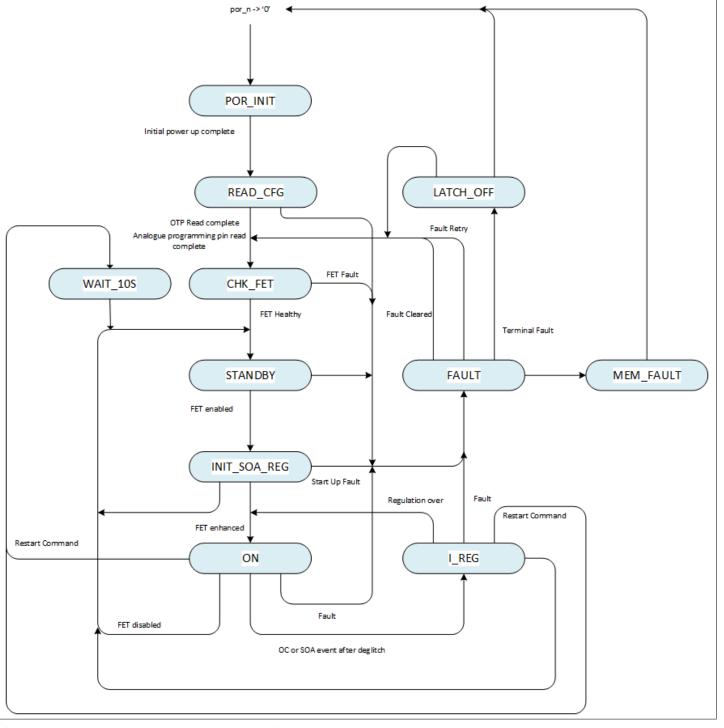

| 4.1    | Functional description           | 32 |

| 4.1.1  | Modes of operation               |    |

| 4.1.2  | Operational states               | 34 |

| 4.1.3  | Enable and disable               |    |

| 4.1.4  | Control of FET's current         |    |

| 4.1.5  | Boost mode power-up              |    |

| 4.1.6  | Power good                       | 45 |

| 4.1.7  | Support of sequential turn-on    | 45 |

| 4.1.8  | Support of OR-ing capability     | 45 |

| 4.1.9  | FET power down                   | 45 |

| 4.1.10 | Restart                          |    |

| 4.2    | Faults                           |    |

| 4.2.1  | Memory fault                     | 49 |

| 4.2.2  | Damaged FET faults               | 49 |

| 4.2.3  | Input voltage faults             |    |

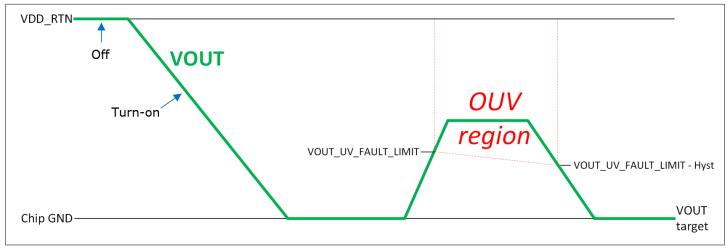

| 4.2.4  | Output voltage faults            | 50 |

| 4.2.5  | Current and temperature faults   |    |

| 4.2.6  | Power-up faults                  | 53 |

| 4.2.7  | Internal protection fault        | 54 |

| 4.3    | Retry                            | 54 |

| 4.4    | Latch-off                        | 54 |

| 4.5    | Warnings                         | 55 |

| 4.5.1  | Damaged FET warning              |    |

| 4.5.2  | Input voltage and power warnings |    |

| 4.5.3  | Output voltage warning           |    |

| 4.5.4  | Current and temperature warnings | 58 |

## XDP700-002 Hot-swap Controller Wide input voltage range (-6.5 V to -80 V) system monitoring and protection IC

#### Table of contents

|       | <b>Disclaimer</b>                                                              |

|-------|--------------------------------------------------------------------------------|

| 7     | <b>Revision history</b>                                                        |

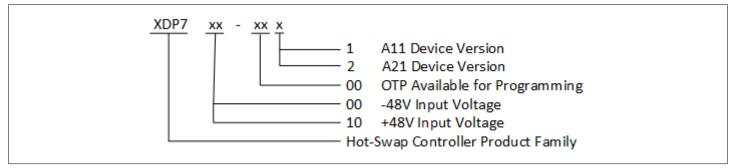

| 6     | Ordering information                                                           |

| 5.10  | Layout guidelines                                                              |

| 5.9.5 | Energy                                                                         |

| 5.9.4 | Temperature                                                                    |

| 5.9.3 | Power                                                                          |

| 5.9.2 | Current                                                                        |

| 5.9.1 | Voltage                                                                        |

| 5.9   | Calculating PMBus direct format limits from "real world" values and vice-versa |

| 5.8   | FET selection considerations                                                   |

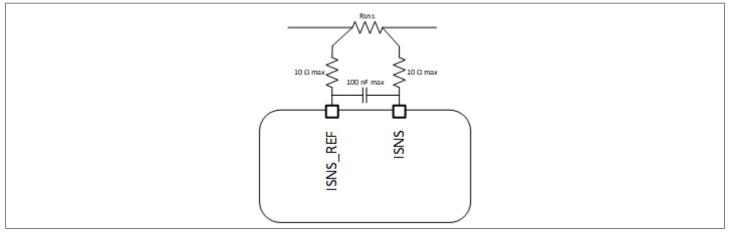

| 5.7   | ISNS input filter                                                              |

| 5.6   | Handling external current at VREG pin77                                        |

| 5.5   | Setting the voltage at ADDR1/0 pins                                            |

| 5.4   | Setting the voltage at MODE1/0 pins in AADM77                                  |

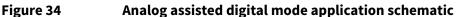

| 5.3   | Setting OV and UV in ACM                                                       |

| 5.2   | Setting loc                                                                    |

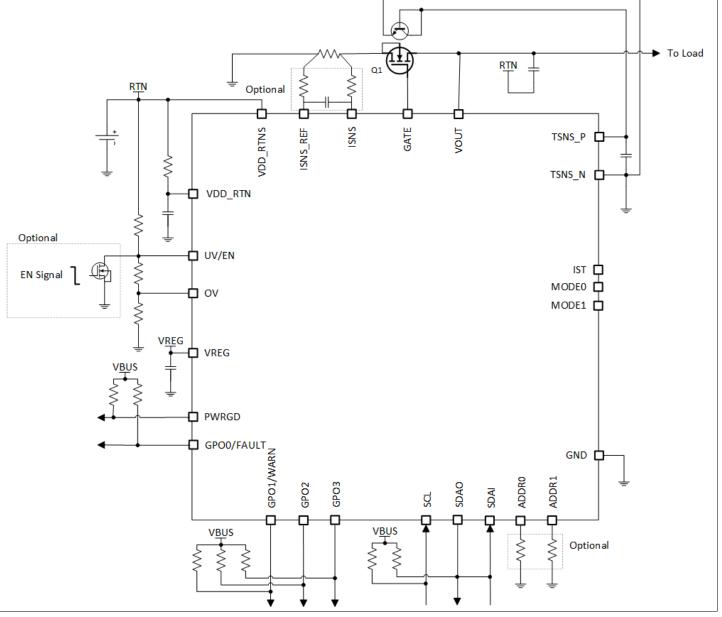

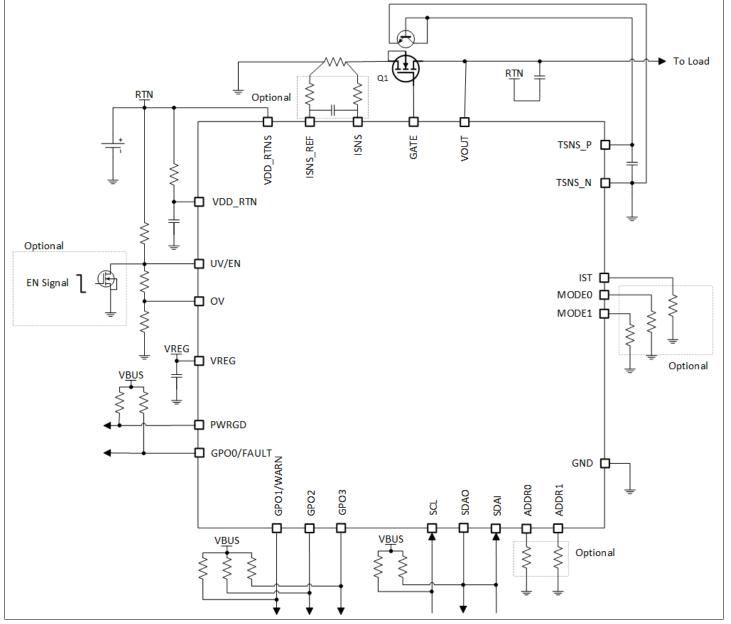

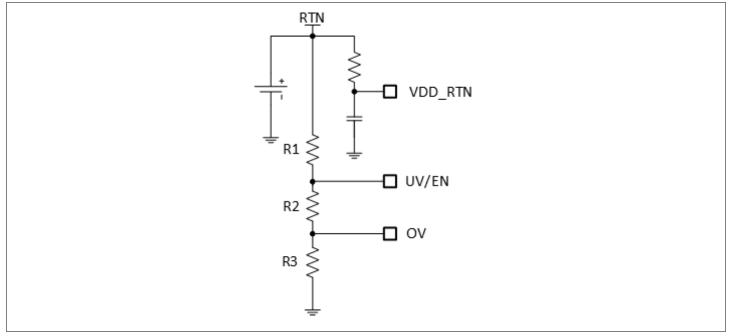

| 5.1   | Typical application schematics                                                 |

| 5     | Application information                                                        |

| 4.8   | Memory                                                                         |

| 4.7.1 | PMBus                                                                          |

| 4.7   | Communication interface                                                        |

| 4.6.7 | Energy calculation                                                             |

| 4.6.6 | Input power calculation                                                        |

| 4.6.5 | RMS current calculation                                                        |

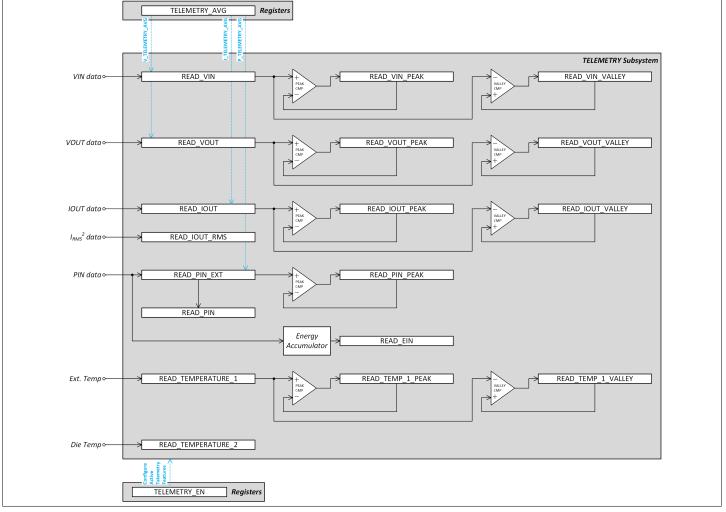

| 4.6.4 | Telemetry via PMBus                                                            |

| 4.6.3 | Peaks and valleys                                                              |

| 4.6.2 | Averaged and instantaneous telemetry61                                         |

| 4.6.1 | Telemetry summary table                                                        |

| 4.6   | Telemetry                                                                      |

| 4.5.5 | Communication warning                                                          |

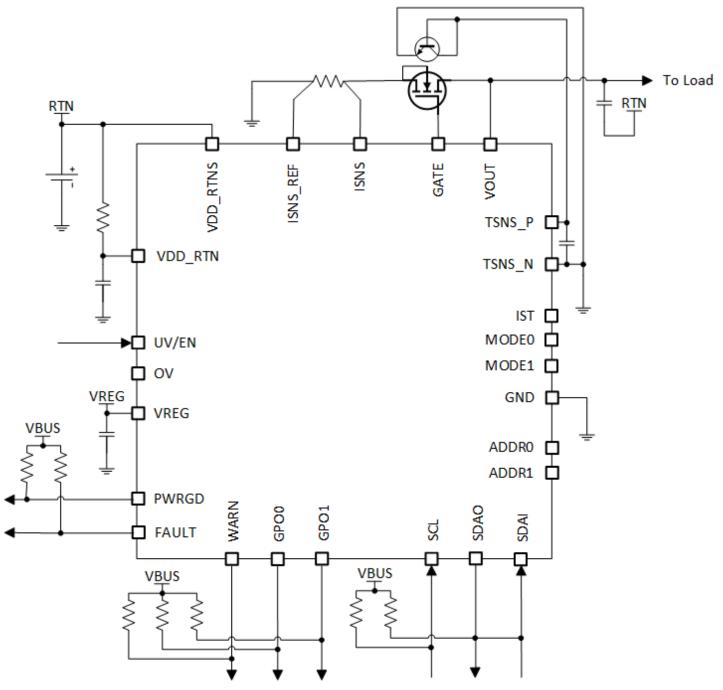

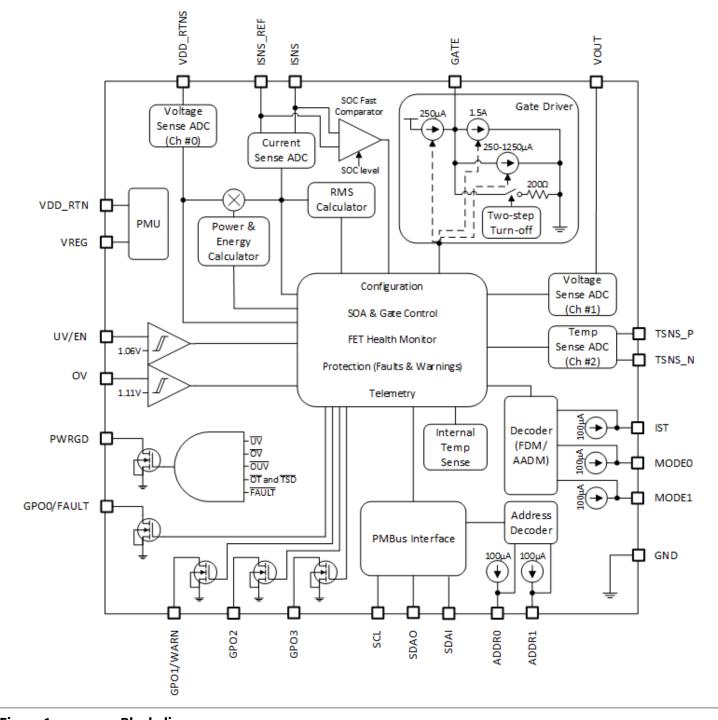

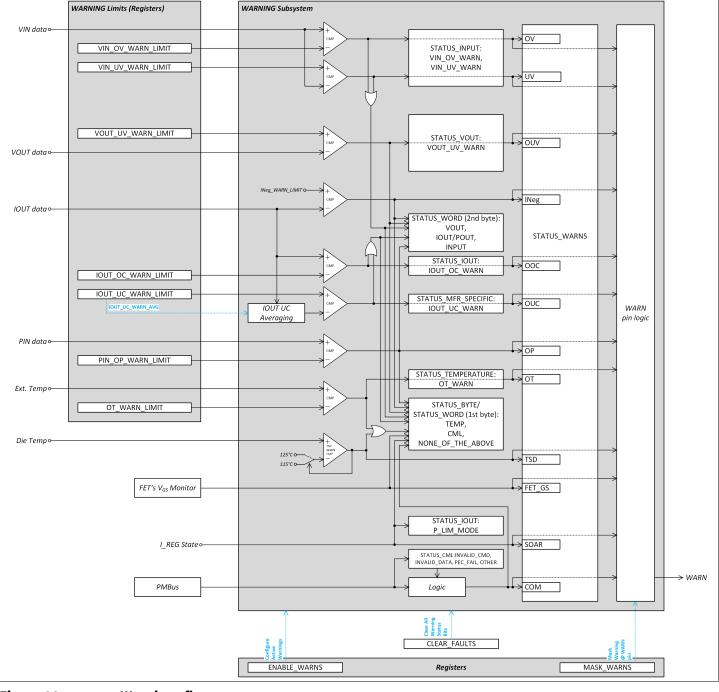

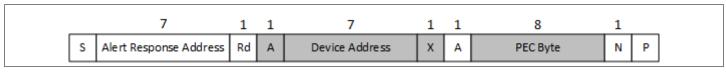

1 Block diagram

1

## Block diagram

XDP700-002 Hot-swap Controller

**Block diagram**

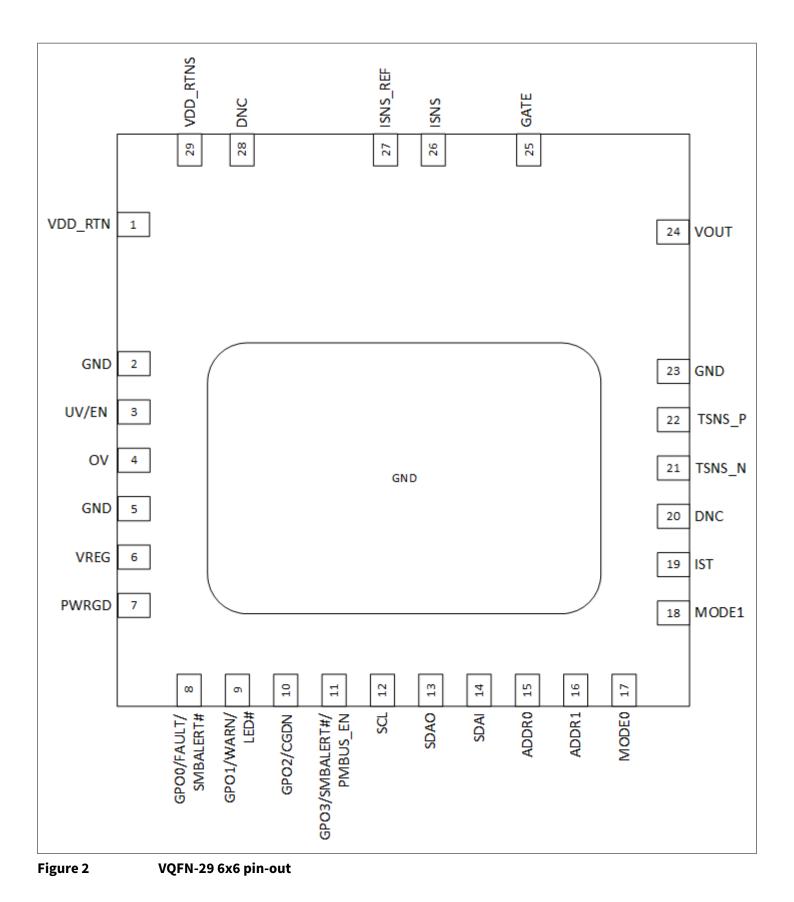

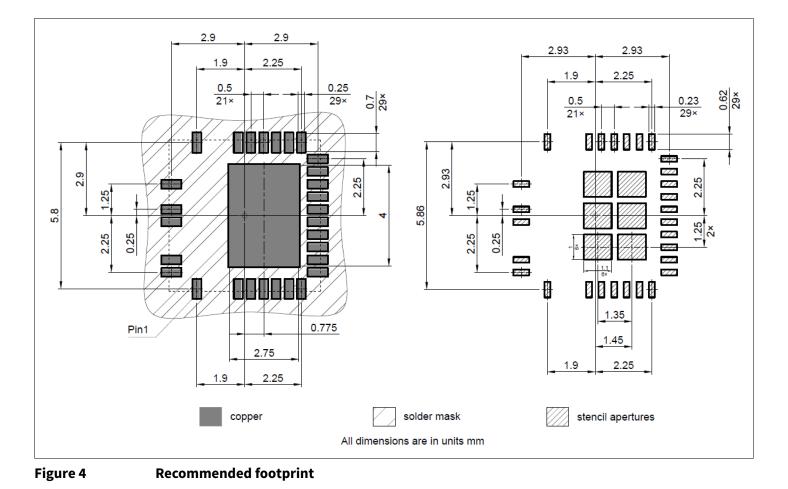

2 Pin configuration and package

# 2 Pin configuration and package

#### Table 1XDP700 pinout

| Pin # | Name                     | I/O | Туре | Description                                                                                                                                                                                                                                                                                                                              | Connection if unused                                      |

|-------|--------------------------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 1     | VDD_RTN                  |     | P    | <b>Return path</b> pin. Power supply. A 100nF capacitor from this pin to GND is strongly recommended.                                                                                                                                                                                                                                    | VDD_RTN                                                   |

| 2     | GND                      |     | G    | <b>Ground</b> reference. Pin must be connected to system negative input.                                                                                                                                                                                                                                                                 | GND                                                       |

| 3     | UV/EN                    | 1   | A    | <b>Undervoltage detection/enable</b> input. A voltage lower than V <sub>UVEN_LTH</sub> on this pin turns off the FET.                                                                                                                                                                                                                    | VREG                                                      |

| 4     | OV                       | 1   | A    | <b>Overvoltage detection</b> input. A voltage higher than V <sub>OV_UTH</sub> on this pin turns off the FET.                                                                                                                                                                                                                             | GND                                                       |

| 5     | GND                      |     | G    | <b>Ground</b> reference. Pin must be connected to system negative input.                                                                                                                                                                                                                                                                 | GND                                                       |

| 6     | VREG                     |     | P    | <b>VREG</b> (internal 5 V regulator) output.<br>Connect a 1 μF capacitor from this pin to<br>GND.                                                                                                                                                                                                                                        | Connect a<br>1 μF<br>capacitor<br>from this pin<br>to GND |

| 7     | PWRGD                    | 0   | D    | <b>Power good open drain</b> output. Pin is<br>asserted when VOUT has reached its<br>final level and steady state, FET is fully<br>enhanced and no faults are detected. Its<br>polarity is configurable.                                                                                                                                 | Open                                                      |

| 8     | GPO0/FAULT/<br>SMBALERT# | 0   | D    | <ul> <li>General-purpose digital output 0. Pin configuration is programmable.</li> <li>Fault open drain output if configured, the pin asserts High/Low (programmable) when a fault occurs. The faults that can trigger the pin can configured.</li> <li>SMBALERT# open drain output if configured, the pin asserts low when a</li> </ul> | Open                                                      |

|       |                          |     |      | fault or warning occurs (depending on<br>configuration). The faults and warnings<br>that can trigger the pin can be configured.                                                                                                                                                                                                          |                                                           |

|       |                          |     |      | <b>Default configuration:</b> FAULT.                                                                                                                                                                                                                                                                                                     |                                                           |

6

2 Pin configuration and package

| Table 1 | (continued) XDP700 pinout       |                                         |      |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                        |  |  |  |  |  |

|---------|---------------------------------|-----------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|--|--|

| Pin #   | Name                            | I/O                                     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                            | Connection<br>if unused                                |  |  |  |  |  |

| 9       | GPO1/<br>WARN/LED#              | 0                                       | D    | <b>General-purpose digital output 1</b> . Pin configuration is programmable.                                                                                                                                                                                                                                                                                                                                           | Open                                                   |  |  |  |  |  |

|         |                                 |                                         |      | Warning open drain output if<br>configured, the pin asserts High/Low<br>(programmable) when a warning occurs.<br>The warnings that can trigger the pin<br>can configured.                                                                                                                                                                                                                                              |                                                        |  |  |  |  |  |

|         |                                 |                                         |      | <ul> <li>LED# open drain output if configured, the pin asserts low when a fault occurs. The faults that can trigger the pin can be configured.</li> <li>Default configuration: WARN.</li> </ul>                                                                                                                                                                                                                        |                                                        |  |  |  |  |  |

| 10      | GPO2/CGDN                       | I/O                                     | D    | General-purpose digital output 2. Pin                                                                                                                                                                                                                                                                                                                                                                                  | Open                                                   |  |  |  |  |  |

| 10      |                                 | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |      | configuration is programmable.<br><b>Connector Good (CGDN)</b> if configured, if<br>this pin is pulled externally low, the<br>controller is allowed to turn on the FET.<br><b>Default configuration:</b> Disabled.                                                                                                                                                                                                     |                                                        |  |  |  |  |  |

| 11      | GPO3/<br>SMBALERT#/<br>PMBUS_EN | 1/0                                     | D    | <ul> <li>General-purpose digital output 3. Pin configuration is programmable.</li> <li>SMBALERT# open drain output if configured, the pin asserts low when a fault or warning occurs (depending on configuration). The faults and warnings that can trigger the pin can be configured.</li> <li>PMBUS_EN: if configured, enabled or disabled PMBus communication.</li> <li>Default configuration: Disabled.</li> </ul> | Open                                                   |  |  |  |  |  |

| 12      | SCL                             | 1                                       | D    | <b>PMBus clock</b> input. The interface is rated to 1 MHz.                                                                                                                                                                                                                                                                                                                                                             | Pull-up to<br>VREG or<br>external<br>voltage<br>source |  |  |  |  |  |

| 13      | SDAO                            | 0                                       | D    | <b>PMBus data output</b> . Open drain pin. The serial data is split into an input and an output for easy use with isolators.                                                                                                                                                                                                                                                                                           | Pull-up to<br>VREG or<br>external<br>voltage<br>source |  |  |  |  |  |

| 14      | SDAI                            | 1                                       | D    | <b>PMBus data input</b> . The serial data is split into an input and an output for easy use with isolators.                                                                                                                                                                                                                                                                                                            | Pull-up to<br>VREG or<br>external<br>voltage<br>source |  |  |  |  |  |

7

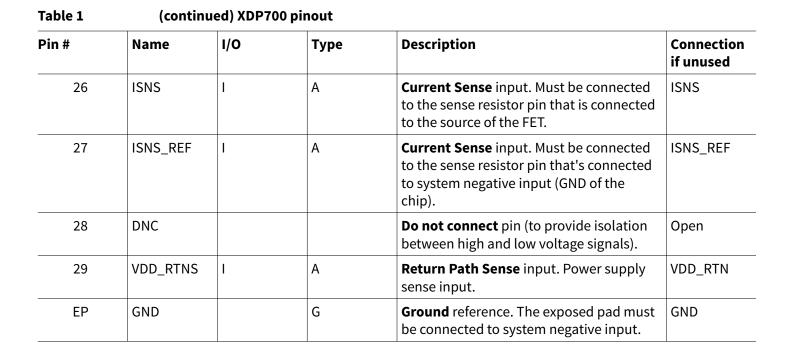

## Table 1 (continued) XDP700 pinout

2 Pin configuration and package

| in #     | Name           | I/O | Туре | Description                                                                                                                                                                                                                                                                     | Connection if unused |

|----------|----------------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 15<br>16 | ADDR0<br>ADDR1 | l   | A A  | <b>Device address configuration 0 and 1</b><br>inputs. These pins can be tied to GND, left<br>open or tied to GND through a resistor<br>for a total of 16 unique PMBus device<br>addresses.                                                                                     | Open                 |

| 17       | MODE0          | 1   | A    | Mode of operation 0 and 1 inputs. These                                                                                                                                                                                                                                         | Open                 |

| 18       | MODE1          | 1   | A    | pins can be tied to GND, left open or tied<br>to GND through a resistor to select<br>between FDM and AADM.<br>Leave both pins open to select FDM.                                                                                                                               |                      |

| 19       | IST            | I   | A    | <b>Start-up Current</b> setting input. A resistor<br>to GND on this pin limits the maximum<br>current allowed at start-up phase. This pin<br>is used in AADM and it is to be kept open in<br>FDM.                                                                               | Open                 |

| 20       | DNC            |     |      | Shall be kept open (unconnected).                                                                                                                                                                                                                                               | Open                 |

| 21       | TSNS_N         | I   | A    | Temperature sense negative terminal.Tie this pin to the emitter of an externalNPN BJT to sense the FET's temperature.Connect a 1nF capacitor from this pin toTSNS_P.This pin must be connected locally toGND.                                                                   | GND                  |

| 22       | TSNS_P         | I   | A    | Temperature sense positive terminal. Tiethis pin to the base and collector of anexternal NPN BJT to sense the FET'stemperature. Connect a 1nF capacitorfrom this pin to TSNS_N.If unused, this pin must be connected toGND.                                                     | GND                  |

| 23       | GND            |     | G    | <b>Ground</b> reference. Pin must be connected to system negative input.                                                                                                                                                                                                        | GND                  |

| 24       | VOUT           | 1   | A    | Output voltage sense input.                                                                                                                                                                                                                                                     | VOUT                 |

| 25       | GATE           | 0   | A    | <b>Gate driver</b> output of single or multiple<br>parallel external N channel FETs, which<br>is/are regulated to a maximum allowed<br>current by regulating the GATE pin<br>voltage. GATE is pulled down when the<br>supply is not within UV and OV limits or<br>fault occurs. | GATE                 |

XDP700-002 Hot-swap Controller Wide input voltage range (-6.5 V to -80 V) system monitoring and protection IC

2 Pin configuration and package

#### Datasheet

## XDP700-002 Hot-swap Controller Wide input voltage range (-6.5 V to -80 V) system monitoring and protection IC

2 Pin configuration and package

Package dimensions

## 3 General product characteristics

## 3.1 Absolute maximum ratings

#### Table 2Absolute maximum ratings

The following operating conditions must not be exceeded in order to ensure correct operation and reliability of the device. All voltage parameters are referenced to GND unless otherwise specified, positive currents are flowing into the pin.

| Parameter                                                                | Symbol                                                                                                       | Values |      |      | Unit | Note or condition                                                                                                                                                                 |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                          |                                                                                                              | Min.   | Тур. | Max. |      |                                                                                                                                                                                   |

| Supply voltage<br>at VDD_RTN pin                                         | VDD_RTN <sub>DC</sub>                                                                                        | -0.3   | -    | 80   | V    |                                                                                                                                                                                   |

| Supply voltage<br>transients at<br>VDD_RTN pin                           | VDD_RTN <sub>AC</sub>                                                                                        | _      | -    | 100  | V    | For 500 ms maximum.                                                                                                                                                               |

| Voltage slew<br>rate at<br>VDD_RTN pin                                   | VDD_RTN <sub>SR</sub>                                                                                        | _      | -    | ±80  | V/µs | The RC filter (i.e. $10 \Omega / 100 \text{ nF}$ , or $100 \Omega / 10 \text{ nF}$ ,<br>etc.) on the pin is recommended, especially for<br>high voltage (i.e. 48 V) applications. |

| Voltage slew<br>rate at<br>VDD_RTNS pin                                  | VDD_RTNS <sub>SR</sub>                                                                                       | _      | -    | ±2   | V/ns | Max is defined by hot plag scenario. The resistor (i.e.10 $\Omega$ ) in series to the pin is recommended if an excessive dV/dt may occur in the application.                      |

| Voltage slew<br>rate at VOUT pin                                         | VOUT <sub>SR</sub>                                                                                           | -      | -    | ±80  | V/µs | An output cap (10 $\mu\text{F}$ min) limits a slew rate on the pin.                                                                                                               |

| Output voltage<br>at GATE pin                                            | V <sub>GATE</sub>                                                                                            | -0.3   | -    | 15   | V    |                                                                                                                                                                                   |

| GATE to<br>SOURCE voltage                                                | V <sub>GATE-</sub><br>SOURCE_DC                                                                              | -0.3   | _    | 12   | V    |                                                                                                                                                                                   |

| GATE to<br>SOURCE voltage<br>transients                                  | V <sub>GATE-</sub><br>SOURCE_AC                                                                              | _      | -    | 15   | V    | For 500ms max                                                                                                                                                                     |

| Output voltage<br>at VREG pin                                            | V <sub>VREG</sub>                                                                                            | -0.3   | -    | 6    | V    |                                                                                                                                                                                   |

| Digital pins<br>output voltage<br>(PWRGD, FAULT,<br>WARN, GPOx,<br>SDAO) | V <sub>PWRGD</sub> ,<br>V <sub>FAULT</sub> ,<br>V <sub>WARN</sub> , V <sub>GPOX</sub> ,<br>V <sub>SDAO</sub> | -0.3   | -    | 6    | V    |                                                                                                                                                                                   |

| Input voltage at<br>VDD_RTNS pin                                         | VDD_RTNS <sub>DC</sub>                                                                                       | -0.3   | -    | 80   | V    |                                                                                                                                                                                   |

| Input voltage<br>transients at<br>VDD_RTNS pin<br>(table continues       | VDD_RTNS <sub>AC</sub>                                                                                       | -      | -    | 100  | V    | For 500 ms maximum.                                                                                                                                                               |

#### Table 2 (continued) Absolute maximum ratings

The following operating conditions must not be exceeded in order to ensure correct operation and reliability of the device. All voltage parameters are referenced to GND unless otherwise specified, positive currents are flowing into the pin.

| Parameter                                                                    | Symbol                                                                                                                           | Values |      |      | Unit | Note or condition   |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------|------|------|------|---------------------|

|                                                                              |                                                                                                                                  | Min.   | Тур. | Max. |      |                     |

| Input voltage at<br>VOUT pin                                                 | VOUT <sub>DC</sub>                                                                                                               | -1     | -    | 80   | V    |                     |

| Input voltage<br>transients at<br>VOUT pin                                   | VOUT <sub>AC</sub>                                                                                                               | -      | -    | 100  | V    | For 500 ms maximum. |

| Input voltage at<br>ISNS_REF pin                                             | V <sub>ISNS_REF</sub>                                                                                                            | -0.3   | -    | 0.3  | V    |                     |

| Input voltage at<br>ISNS pin                                                 | V <sub>ISNS</sub>                                                                                                                | -0.8   | -    | 0.8  | V    |                     |

| Current Sense<br>input voltage<br>(ISNS_REF -<br>ISNS)                       | V <sub>AISNS</sub>                                                                                                               | -0.8   | -    | 0.8  | V    |                     |

| Analog pins<br>input voltage<br>(UV/EN, OV,<br>ADDRx, MODEx,<br>IST, TSNS_N) | V <sub>UV_EN</sub> , V <sub>OV</sub> ,<br>V <sub>ADDRx</sub> ,<br>V <sub>MODEx</sub> , V <sub>IST</sub> ,<br>V <sub>TSNS_N</sub> | -0.3   | -    | 6    | V    |                     |

| Input voltage at TSNS_P pin                                                  | V <sub>TSNS_P</sub>                                                                                                              | -0.3   | -    | 2.5  | V    |                     |

| Digital pins<br>input voltage<br>(SCL, SDAI)                                 | V <sub>SCL</sub> , V <sub>SDAI</sub>                                                                                             | -0.3   | -    | 6    | V    |                     |

| Junction<br>temperature<br>range                                             | TJ                                                                                                                               | -40    | -    | 150  | °C   |                     |

| Storage<br>temperature<br>range                                              | Τ <sub>S</sub>                                                                                                                   | -55    | -    | 150  | °C   |                     |

## 3.2 Functional range

#### Table 3Functional and performance ranges description

| Absolute voltage range at VDD_RTN | Communication interface | FET gate                | VREG |

|-----------------------------------|-------------------------|-------------------------|------|

| 0 ≤ Vin < 6.5                     | Off                     | Off (passive pull-down) | Off  |

| (table continues )                | •                       |                         |      |

#### Table 3 (continued) Functional and performance ranges description

| Absolute voltage range at VDD_RTN | Communication interface | FET gate                                                                                                          | VREG              |

|-----------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------|

| 6.5 ≤ Vin < 9                     | On                      | Limited operation: - Off<br>(active pull-down); - limited<br>SOA regulation depending<br>on gate driver supply;   | 4.5V (minimum)    |

| 9 ≤ Vin < 14                      |                         | - On/enchancement is not<br>guaranteed (but ≥ 4.5 V)                                                              | 5.0 V (typically) |

| 14 ≤ Vin ≤ 80                     |                         | Full operation: - Off<br>(active pull-down); - full<br>SOA regulation; - On/<br>enhancement (typically<br>10.5 V) |                   |

#### Table 4Functional range

The following operating conditions must not be exceeded in order to ensure correct operation and reliability of the device. All voltage parameters are referenced to GND unless otherwise specified, positive currents are flowing into the pin,  $T_A = 25^{\circ}C$ .

| Parameter                                                                                 | Symbol                                                                                                  | Values |               |      | Unit | Note or condition                                                                                                                           |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------|---------------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                           |                                                                                                         | Min.   | Тур.          | Max. |      |                                                                                                                                             |

| Supply voltage<br>at VDD_RTN pin                                                          | VDD_RTN                                                                                                 | 6.5    |               | 80   | V    |                                                                                                                                             |

| Supply voltage<br>at VDD_RTN pin<br>to enable all<br>features                             | VDD_RTN <sub>EN</sub>                                                                                   | 14     | -             | -    | V    | See Table 3.                                                                                                                                |

| VDD_RTNS<br>sense pin input<br>voltage                                                    | VDD_RTNS                                                                                                | 6.5    | 12, 24,<br>48 | 80   | V    |                                                                                                                                             |

| VOUT sense pin<br>input voltage                                                           | VOUTS                                                                                                   | 0      | -             | 80   | V    |                                                                                                                                             |

| Current sense<br>input voltage<br>(ISNS_REF -<br>ISNS)                                    | V <sub>ΔISNS</sub>                                                                                      | -0.4   | -             | 0.4  | V    |                                                                                                                                             |

| Minimum<br>overcurrent<br>setting                                                         | I <sub>OC_MIN</sub>                                                                                     | 5      | -             | _    | A    | Minimum I <sub>OC</sub> (I <sub>OC</sub> = V <sub>SNS_CS</sub> / R <sub>SNS</sub> , see Setting I <sub>OC</sub> )<br>for optimum stability. |

| Analog pins<br>input voltage<br>(UV/EN, OV,<br>ADDRx, MODEx,<br>IST)<br>(table continues) | V <sub>UV_EN</sub> , V <sub>OV</sub> ,<br>V <sub>ADDRx</sub> ,<br>V <sub>MODEx</sub> , V <sub>IST</sub> | 0      | -             | 5.5  | V    |                                                                                                                                             |

## Table 4(continued) Functional range

The following operating conditions must not be exceeded in order to ensure correct operation and reliability of the device. All voltage parameters are referenced to GND unless otherwise specified, positive currents are flowing into the pin,  $T_A = 25^{\circ}C$ .

| Parameter                                                                | Symbol                                                                                                       | Values |      |      | Unit | Note or condition           |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------|------|------|------|-----------------------------|

|                                                                          |                                                                                                              | Min.   | Тур. | Max. |      |                             |

| Digital pins<br>input voltage<br>(SCL, SDAI)                             | V <sub>SCL</sub> , V <sub>SDAI</sub>                                                                         | 0      | _    | 5.5  | V    |                             |

| Output voltage<br>at VREG pin                                            | V <sub>VREG</sub>                                                                                            | 4.5    | 5    | 5.5  | V    | At 10 mA max external load. |

| Digital pins<br>output voltage<br>(PWRGD, FAULT,<br>WARN, GPOx,<br>SDAO) | V <sub>PWRGD</sub> ,<br>V <sub>FAULT</sub> ,<br>V <sub>WARN</sub> , V <sub>GPOX</sub> ,<br>V <sub>SDAO</sub> | 0      | -    | 5.5  | V    |                             |

| Junction<br>temperature<br>range                                         | Т                                                                                                            | -40    | _    | 125  | °C   |                             |

## 3.3 Thermal characteristics

### Table 5Thermal characteristics

| Parameter                                              | Symbol               | Values |      |      | Unit | Note or condition                             |  |  |

|--------------------------------------------------------|----------------------|--------|------|------|------|-----------------------------------------------|--|--|

|                                                        |                      | Min.   | Тур. | Max. | •    |                                               |  |  |

| Thermal<br>resistance<br>Junction-to-<br>case (bottom) | $R_{\Theta JC_Bot}$  | -      | 5    | -    | K/W  | PCB simulation setup as described in Table 6. |  |  |

| Thermal<br>resistance<br>Junction-to-<br>case (top)    | R <sub>ØJC_Top</sub> | -      | 30   | -    | K/W  | PCB simulation setup as described in Table 6. |  |  |

| Thermal<br>resistance<br>Junction-to-<br>Ambient       | R <sub>ØJA</sub>     | -      | 33   | -    | K/W  | PCB simulation setup as described in Table 6. |  |  |

| Package power dissipation                              | P <sub>PAK</sub>     | -      | -    | 0.8  | W    |                                               |  |  |

#### Table 6 PCB charac

### PCB characteristics for thermal simulation

|                                 |                                   | λ <sub>therm</sub> [W/m-K] |

|---------------------------------|-----------------------------------|----------------------------|

| Metalization                    | JEDEC 2s2p (JESD 51-7, JESD 51-5) | 388                        |

| Cooling Area [mm <sup>2</sup> ] | none                              | 388                        |

**Note:** Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

**Note:** This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org

## 3.4 Current consumption

#### Table 7Current consumption

VDD\_RTN - GND = 48 V,  $V_{ISNS REF} = 0 V$ ,  $V_{\Delta ISNS} = [V_{ISNS REF} - V_{ISNS}] = 0 V$ ,  $T_J = -40^{\circ}$ C to + 125°C, unless otherwise noted.

| Parameter           | Symbol           |      | Values |      | Unit | Note or condition                 |

|---------------------|------------------|------|--------|------|------|-----------------------------------|

|                     |                  | Min. | Тур.   | Max. |      |                                   |

| Current consumption | I <sub>VDD</sub> | -    | 6      | 10   | mA   | VDD_RTN supply current:           |

|                     |                  |      |        |      |      | FET is fully ON, telemetry in ON. |

## 3.5 ESD robustness

#### Table 8 ESD robustness

| Parameter Symbol      | Symbol               | Values |      |       | Unit | Note or condition                                                 |

|-----------------------|----------------------|--------|------|-------|------|-------------------------------------------------------------------|

|                       |                      | Min.   | Тур. | Max.  |      |                                                                   |

| ESD Robustness<br>HBM | V <sub>ESD_HBM</sub> | _      | _    | ±2000 | V    | Human Body Model sensitivity as per ANSI/ESDA/<br>JEDEC JS-001    |

| ESD Robustness<br>CDM | V <sub>ESD_CDM</sub> | _      | _    | ±500  | V    | Charge Device Model sensitivity as per ANSI/ESDA/<br>JEDEC JS-002 |

## 3.6 Electrical characteristics

#### Table 9 Electrical characteristics

VDD\_RTN - GND = 48 V,  $V_{ISNS_{REF}} = 0 V$ ,  $V_{\Delta ISNS} = (V_{ISNS_{REF}} - V_{ISNS}) = 0 V$ ,  $T_J = -40^{\circ}C$  to +125°C, unless otherwise noted.

| Parameter                            | Symbol                                         | Values |      |      | Unit | Note or condition |

|--------------------------------------|------------------------------------------------|--------|------|------|------|-------------------|

|                                      |                                                | Min.   | Тур. | Max. |      |                   |

| UV/EN and OV                         |                                                |        |      |      |      |                   |

| Input upper<br>threshold             | V <sub>UVEN_UTH</sub> ,<br>V <sub>OV_UTH</sub> | 1.09   | 1.11 | 1.13 | V    |                   |

| Input lower<br>threshold             | V <sub>UVEN_LTH</sub> ,<br>V <sub>OV_LTH</sub> | 1.04   | 1.06 | 1.08 | V    |                   |

| TSNS_P, TSNS_                        | N                                              |        |      |      |      |                   |

| TSNS_P<br>operating<br>voltage range | V <sub>TSNS_P</sub>                            | 0.25   | -    | 1    | V    |                   |

#### Table 9 (continued) Electrical characteristics

$VDD_RTN - GND = 48 V, V_{ISNS_{REF}} = 0 V, V_{\Delta ISNS} = (V_{ISNS_{REF}} - V_{ISNS}) = 0 V, T_J = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted.}$

| Parameter                                              | Symbol               |                                   | Values | ;     | Unit | Note or condition                                                                                                                                                             |

|--------------------------------------------------------|----------------------|-----------------------------------|--------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                        |                      | Min.                              | Тур.   | Max.  |      |                                                                                                                                                                               |

| TSNS_N<br>operating<br>voltage                         | V <sub>TSNS_N</sub>  | -                                 | 0      | -     | V    |                                                                                                                                                                               |

| ISNS_REF, ISNS                                         |                      |                                   |        |       |      |                                                                                                                                                                               |

| Minimum<br>detectable<br>differential<br>voltage level | V <sub>SNS_MIN</sub> | 0.01<br>* V <sub>SNS</sub><br>_CS | -      | -     | mV   | Between ISNS_REF and ISNS pins.                                                                                                                                               |

| Current sense<br>differential<br>voltage range         | V <sub>SNS_CS</sub>  | -                                 | 12.5   | -     | mV   | Set by CS_RNG[1:0] bits: CS_RNG[1:0] = 00                                                                                                                                     |

| Current sense<br>differential<br>voltage range         | V <sub>SNS_CS</sub>  | -                                 | 25     | -     | mV   | Set by CS_RNG[1:0] bits: CS_RNG[1:0] = 01                                                                                                                                     |

| Current sense<br>differential<br>voltage range         | V <sub>SNS_CS</sub>  | -                                 | 50     | -     | mV   | Set by CS_RNG[1:0] bits: CS_RNG[1:0] = 10                                                                                                                                     |

| Current sense<br>differential<br>voltage range         | V <sub>SNS_CS</sub>  | -                                 | 100    | -     | mV   | Set by CS_RNG[1:0] bits: CS_RNG[1:0] = 11                                                                                                                                     |

| SOC Differential<br>voltage level                      | V <sub>SNS_SOC</sub> | 9.5                               | 12.5   | 15.5  | mV   | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0]<br>bits:<br>SOC_FAULT_LIMIT[2:0] = 000 and CS_RNG[1:0] = 00<br>or 01                                                              |

| SOC Differential<br>voltage level                      | V <sub>SNS_SOC</sub> | 15.75                             | 18.75  | 21.75 | mV   | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0]<br>bits:<br>SOC_FAULT_LIMIT[2:0] = 001 and CS_RNG[1:0] = 00<br>or 01                                                              |

| SOC Differential<br>voltage level                      | V <sub>SNS_SOC</sub> | 22                                | 25     | 28    | mV   | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0]<br>bits:<br>SOC_FAULT_LIMIT[2:0] = 010 and CS_RNG[1:0] = 00<br>or 01; or SOC_FAULT_LIMIT[2:0] = 000 and<br>CS_RNG[1:0] = 10 or 11 |

| SOC Differential<br>voltage level                      | V <sub>SNS_SOC</sub> | 34.5                              | 37.5   | 40.5  | mV   | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0]<br>bits:<br>SOC_FAULT_LIMIT[2:0] = 011 and CS_RNG[1:0] = 00<br>or 01; or SOC_FAULT_LIMIT[2:0] =<br>001 and CS_RNG[1:0] = 10 or 11 |

#### Table 9 (continued) Electrical characteristics

VDD\_RTN - GND = 48 V,  $V_{ISNS_{REF}} = 0 V$ ,  $V_{\Delta ISNS} = (V_{ISNS_{REF}} - V_{ISNS}) = 0 V$ ,  $T_J = -40^{\circ}$ C to +125°C, unless otherwise noted.

| Parameter                          | Symbol               | Values |      |      | Unit | Note or condition                                                                                                                                                                                         |

|------------------------------------|----------------------|--------|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    |                      | Min.   | Тур. | Max. | ]    |                                                                                                                                                                                                           |

| SOC Differential<br>voltage level  | V <sub>SNS_SOC</sub> | 47     | 50   | 53   | mV   | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0]<br>bits:<br>SOC_FAULT_LIMIT[2:0] = 100 and CS_RNG[1:0] = 0<br>or 01; or SOC_FAULT_LIMIT[2:0] = 010<br>and CS_RNG[1:0] = 10 or 11                              |

| SOC Differential<br>voltage level  | V <sub>SNS_SOC</sub> | 71     | 75   | 79   | mV   | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0]<br>bits:<br>SOC_FAULT_LIMIT[2:0] = 101 and CS_RNG[1:0] = 0<br>or 01; or SOC_FAULT_LIMIT[2:0] =<br>011 and CS_RNG[1:0] = 10 or 11                              |

| SOC Differential<br>voltage level  | V <sub>SNS_SOC</sub> | 96     | 100  | 104  | mV   | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0]           bits:           SOC_FAULT_LIMIT[2:0] = 110 and CS_RNG[1:0] = 00           or 01; or SOC_FAULT_LIMIT[2:0] = 100           and CS_RNG[1:0] = 10 or 11 |

| SOC Differential<br>voltage level  | V <sub>SNS_SOC</sub> | 145    | 150  | 155  | mV   | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0]<br>bits:<br>SOC_FAULT_LIMIT[2:0] = 111 and CS_RNG[1:0] = 00<br>or 01; or SOC_FAULT_LIMIT[2:0] =<br>101 and CS_RNG[1:0] = 10 or 11                             |

| SOC Differential<br>voltage level  | V <sub>SNS_SOC</sub> | 193    | 200  | 207  | mV   | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0]<br>bits:<br>SOC_FAULT_LIMIT[2:0] = 110 and CS_RNG[1:0] = 10<br>or 11                                                                                          |

| SOC Differential<br>voltage level  | V <sub>SNS_SOC</sub> | 290    | 300  | 310  | mV   | Set by SOC_FAULT_LIMIT[2:0] and CS_RNG[1:0]<br>bits:<br>SOC_FAULT_LIMIT[2:0] = 111 and CS_RNG[1:0] = 10<br>or 11                                                                                          |

| Current sense<br>ADC resolution    | ADC <sub>RES</sub>   | -      | 12   | -    | bits |                                                                                                                                                                                                           |

| Max allowed<br>negative<br>current | I <sub>NEG_MAX</sub> | -      | 240  | -    | mA   | To trigger INEG warning.<br>$V_{SNS_{CS}} = 12.5 \text{ mV}$ , Rsns = 1 m $\Omega$ .                                                                                                                      |

| Max allowed<br>negative<br>current | I <sub>NEG_MAX</sub> | -      | 520  | -    | mA   | To trigger INEG warning.<br>$V_{SNS_{CS}} = 25 \text{ mV}$ , Rsns = 1 m $\Omega$ .                                                                                                                        |

| Max allowed<br>negative<br>current | I <sub>NEG_MAX</sub> | -      | 1100 | -    | mA   | To trigger INEG warning.<br>$V_{SNS_{CS}} = 50 \text{ mV}$ , Rsns = 1 m $\Omega$ .                                                                                                                        |

## Table 9 (continued) Electrical characteristics

VDD\_RTN - GND = 48 V,  $V_{ISNS_{REF}} = 0 V$ ,  $V_{\Delta ISNS} = (V_{ISNS_{REF}} - V_{ISNS}) = 0 V$ ,  $T_J = -40^{\circ}$ C to +125°C, unless otherwise noted.

| Parameter                                                                               | Symbol                            | Values |      |       | Unit | Note or condition                                                                    |

|-----------------------------------------------------------------------------------------|-----------------------------------|--------|------|-------|------|--------------------------------------------------------------------------------------|

|                                                                                         |                                   | Min.   | Тур. | Max.  |      |                                                                                      |

| Max allowed                                                                             | I <sub>NEG_MAX</sub>              | -      | 2200 | -     | mA   | To trigger INEG warning.                                                             |

| negative<br>current                                                                     |                                   |        |      |       |      | $V_{SNS}CS} = 100 \text{ mV}$ , Rsns = 1 m $\Omega$ .                                |

| GATE                                                                                    |                                   |        |      |       |      |                                                                                      |

| Gate voltage                                                                            | V <sub>GATE</sub>                 | 8.5    | 10.5 | 12.0  | V    | 14 V $\leq$ VDD_RTN $\leq$ 80 V, I <sub>GATE</sub> $\leq$ 5 $\mu$ A, FET is fully ON |

| Gate voltage                                                                            | V <sub>GATE</sub>                 | 4.5    | -    | -     | V    | 6.5 V $\leq$ VDD_RTN < 14 V, I <sub>GATE</sub> $\leq$ 5 $\mu$ A.                     |

| Pull-up current                                                                         | I <sub>GATE_PU</sub>              | 200    | 250  | 300   | μA   | At V <sub>GATE</sub> = 5 V                                                           |

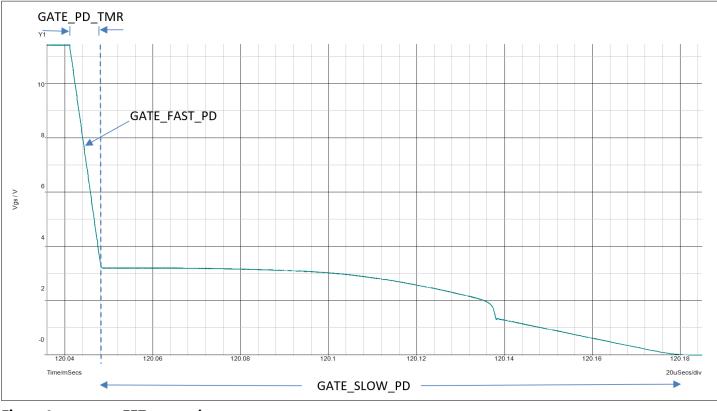

| Fast pull-down<br>current                                                               | I <sub>GATE_FPD</sub>             | 0.825  | 1.5  | 2.175 | A    | Set by GATE_FAST_PD[0]: GATE_FAST_PD[0] = 0                                          |

| GATE pin two<br>step turn-off<br>fast pull-down                                         | R <sub>GATE_2ST_FAS</sub><br>T_PD | 156    | 200  | 244   | Ω    | Set by GATE_FAST_PD[0]: GATE_FAST_PD[0] = 1                                          |

| Slow pull-down<br>current                                                               | I <sub>GATE_SPD</sub>             | 200    | 250  | 300   | μA   | Set by GATE_SLOW_PD[1:0]<br>bits: GATE_SLOW_PD[1:0] = 00                             |

|                                                                                         |                                   |        |      |       |      | Used for both regular/slow pull-down and second phase of the two-step turn-off.      |

| Slow pull-down<br>current                                                               | I <sub>GATE_SPD</sub>             | 400    | 500  | 600   | μA   | Set by GATE_SLOW_PD[1:0]<br>bits: GATE_SLOW_PD[1:0] = 01                             |

|                                                                                         |                                   |        |      |       |      | Used for both regular/slow pull-down and second phase of the two-step turn-off.      |

| Slow pull-down<br>current                                                               | I <sub>GATE_SPD</sub>             | 600    | 750  | 900   | μA   | Set by GATE_SLOW_PD[1:0]<br>bits: GATE_SLOW_PD[1:0] = 10                             |

|                                                                                         |                                   |        |      |       |      | Used for both regular/slow pull-down and second phase of the two-step turn-off.      |

| Slow pull-down<br>current                                                               | I <sub>GATE_SPD</sub>             | 1000   | 1250 | 1500  | μA   | Set by GATE_SLOW_PD[1:0]<br>bits: GATE_SLOW_PD[1:0] = 11                             |

|                                                                                         |                                   |        |      |       |      | Used for both regular/slow pull-down and second phase of the two-step turn-off.      |

| VDD_RTNS                                                                                |                                   |        |      |       |      |                                                                                      |

| Input current                                                                           | I <sub>VDD_RTNS</sub>             | -      | 15   | -     | μA   | At 48 V                                                                              |

| On-chip input<br>over voltage<br>upper threshold<br>for on-chip<br>input<br>overvoltage | OV <sub>IN_UTH</sub>              | -      | 70   | -     | V    | Set by OVIN_FAULT_LIMIT[1:0]<br>bits: OVIN_FAULT_LIMIT[1:0] = 00                     |

#### Table 9 (continued) Electrical characteristics

VDD\_RTN - GND = 48 V,  $V_{ISNS_{REF}} = 0 V$ ,  $V_{\Delta ISNS} = (V_{ISNS_{REF}} - V_{ISNS}) = 0 V$ ,  $T_J = -40^{\circ}$ C to +125°C, unless otherwise noted.

| Parameter                                                                                                  | Symbol                |      | Values                                      | ;    | Unit | Note or condition                                                    |

|------------------------------------------------------------------------------------------------------------|-----------------------|------|---------------------------------------------|------|------|----------------------------------------------------------------------|

|                                                                                                            |                       | Min. | Тур.                                        | Max. |      |                                                                      |

| On-chip input<br>over voltage<br>upper threshold<br>for on-chip<br>input<br>overvoltage<br>fault assertion | OV <sub>IN_UTH</sub>  | -    | 75                                          | -    | V    | Set by OVIN_FAULT_LIMIT[1:0]<br>bits: OVIN_FAULT_LIMIT[1:0] = 01     |

| On-chip input<br>over voltage<br>upper threshold<br>for on-chip<br>input<br>overvoltage<br>fault assertion | OV <sub>IN_UTH</sub>  | -    | 80                                          | _    | V    | Set by OVIN_FAULT_LIMIT[1:0]<br>bits: OVIN_FAULT_LIMIT[1:0] = 10     |

| On-chip input<br>over voltage<br>upper threshold<br>for on-chip<br>input<br>overvoltage<br>fault assertion | OV <sub>IN_UTH</sub>  | -    | 85                                          | _    | V    | Set by OVIN_FAULT_LIMIT[1:0]<br>bits: OVIN_FAULT_LIMIT[1:0] = 11     |

| On-chip input<br>over voltage<br>lower threshold<br>for on-chip<br>input<br>overvoltage<br>fault release   | OV <sub>IN_LTH</sub>  | -    | OV <sub>IN</sub><br>UTH <sup>–</sup><br>5 V | -    | V    | For on-chip input overvoltage fault release.                         |

| VOUT                                                                                                       |                       |      |                                             |      |      |                                                                      |

| Input current                                                                                              | I <sub>VOUT</sub>     | -    | 15                                          | _    | μA   | At 48 V                                                              |

| Output over<br>voltage upper                                                                               | OV <sub>OUT_UTH</sub> | -    | 70                                          | -    | V    | Set by OVOUT_FAULT_LIMIT [1:0]<br>bits: OVOUT_FAULT_LIMIT [1:0] = 00 |

overvoltage

fault assertion (table continues...)

#### Table 9 (continued) Electrical characteristics

VDD\_RTN - GND = 48 V,  $V_{ISNS_{REF}} = 0 V$ ,  $V_{\Delta ISNS} = (V_{ISNS_{REF}} - V_{ISNS}) = 0 V$ ,  $T_J = -40^{\circ}$ C to +125°C, unless otherwise noted.

| Parameter                                                                                 | Symbol                | Values |                                              |      | Unit | Note or condition                                                                                                                  |

|-------------------------------------------------------------------------------------------|-----------------------|--------|----------------------------------------------|------|------|------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                           |                       | Min.   | Тур.                                         | Max. |      |                                                                                                                                    |

| Output over<br>voltage upper<br>threshold for<br>output<br>overvoltage<br>fault assertion | OV <sub>OUT_UTH</sub> | -      | 75                                           | -    | V    | Set by OVOUT_FAULT_LIMIT [1:0]<br>bits: OVOUT_FAULT_LIMIT [1:0] = 01                                                               |

| Output over<br>voltage upper<br>threshold for<br>output<br>overvoltage<br>fault assertion | OV <sub>OUT_UTH</sub> | -      | 80                                           | -    | V    | Set by OVOUT_FAULT_LIMIT [1:0]<br>bits: OVOUT_FAULT_LIMIT [1:0] = 10                                                               |

| Output over<br>voltage upper<br>threshold for<br>output<br>overvoltage<br>fault assertion | OV <sub>OUT_UTH</sub> | -      | 85                                           | -    | V    | Set by OVOUT_FAULT_LIMIT [1:0]<br>bits: OVOUT_FAULT_LIMIT [1:0] = 11                                                               |

| Output over<br>voltage lower<br>threshold for<br>output<br>overvoltage<br>fault release   | OV <sub>OUT_LTH</sub> | _      | OV <sub>OUT</sub><br>_UTH <sup>-</sup><br>5V | -    | V    | For output overvoltage fault release.                                                                                              |

| Telemetry                                                                                 |                       |        |                                              |      |      |                                                                                                                                    |

| Monitored<br>voltage range<br>(input and<br>output<br>voltages)                           | V <sub>TLM</sub>      | 22     | -                                            | 88   | V    | <ul> <li>Set by VTLM_RNG[1:0] bits:</li> <li>2'b00: 88 V</li> <li>2'b01: 44 V</li> <li>2'b10: 22 V</li> <li>2'b11: n.a.</li> </ul> |

| Input voltage<br>measurements<br>accuracy                                                 | A <sub>VIN</sub>      | _      | ±0.2                                         | ±0.4 | %    | At VDD_RTNS vs GND: VDD_RTNS = 20 V to 40 V or<br>10 V to 20 V depending on corresponding<br>programmed range V <sub>TLM</sub> .   |

| Output voltage<br>measurements<br>accuracy                                                | A <sub>VOUT</sub>     | _      | ±0.2                                         | ±0.4 | %    | At VOUT vs GND: VOUT = 20 V to 40 V or 10 V to 20 V<br>depending on corresponding programmed range<br>V <sub>TLM</sub> .           |

| Input voltage<br>measurements<br>accuracy<br>(table continue)                             | A <sub>VIN</sub>      | _      | ±0.25                                        | ±0.5 | %    | At VDD_RTNS vs GND: VDD_RTNS = 40 V to 80 V,<br>$V_{TLM} = 88 V$ .                                                                 |

## Table 9 (continued) Electrical characteristics

VDD\_RTN - GND = 48 V,  $V_{ISNS_{REF}} = 0 V$ ,  $V_{\Delta ISNS} = (V_{ISNS_{REF}} - V_{ISNS}) = 0 V$ ,  $T_J = -40^{\circ}$ C to +125°C, unless otherwise noted.

| Parameter                                  | Symbol            |      | Values |      |   | Note or condition                                                                                                                                                                                |

|--------------------------------------------|-------------------|------|--------|------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                            |                   | Min. | Тур.   | Max. |   |                                                                                                                                                                                                  |

| Output voltage<br>measurements<br>accuracy | A <sub>VOUT</sub> | -    | ±0.25  | ±0.5 | % | At VOUT vs GND: VOUT = 40 V to 80 V, $V_{TLM}$ = 88 V.                                                                                                                                           |

| Current<br>measurement<br>accuracy         | A <sub>IIN</sub>  | -    | ±0.1   | ±0.2 | % | Between ISNS_REF & ISNS pins. $V_{\Delta ISNS} = V_{SNS_CS}$ , where $V_{SNS_CS} = 100$ mV or 50 mV.                                                                                             |

| Current<br>measurement<br>accuracy         | A <sub>IIN</sub>  | -    | ±0.2   | ±0.3 | % | Between ISNS_REF & ISNS pins. $V_{\Delta ISNS} = V_{SNS}CS / 2$ ,<br>where $V_{SNS}CS = 100$ mV or 50 mV.                                                                                        |

| Current<br>measurement<br>accuracy         | A <sub>IIN</sub>  | -    | ±0.35  | ±0.5 | % | Between ISNS_REF & ISNS pins. $V_{\Delta ISNS} = V_{SNS}CS / 4$ ,<br>where $V_{SNS}CS = 100$ mV or 50 mV.                                                                                        |

| Current<br>measurement<br>accuracy         | A <sub>IIN</sub>  | -    | ±0.16  | ±0.7 | % | Between ISNS_REF & ISNS pins. $V_{\Delta ISNS} = V_{SNS}CS$ , where $V_{SNS}CS = 25$ mV.                                                                                                         |

| Current<br>measurement<br>accuracy         | A <sub>IIN</sub>  | -    | ±0.4   | ±1.2 | % | Between ISNS_REF & ISNS pins. $V_{\Delta ISNS} = V_{SNS}CS / 2$ ,<br>where $V_{SNS}CS = 25$ mV.                                                                                                  |

| Current<br>measurement<br>accuracy         | A <sub>IIN</sub>  | -    | ±0.8   | ±2.3 | % | Between ISNS_REF & ISNS pins. $V_{\Delta ISNS} = V_{SNS}CS / 4$ ,<br>where $V_{SNS}CS = 25$ mV.                                                                                                  |

| Current<br>measurement<br>accuracy         | A <sub>IIN</sub>  | -    | ±0.4   | ±1.3 | % | Between ISNS_REF & ISNS pins. $V_{\Delta ISNS} = V_{SNS}_{CS}$ , where $V_{SNS}_{CS} = 12.5$ mV.                                                                                                 |

| Current<br>measurement<br>accuracy         | A <sub>IIN</sub>  | -    | ±0.8   | ±2.6 | % | Between ISNS_REF & ISNS pins. $V_{\Delta ISNS} = V_{SNS} / 2$ ,<br>where $V_{SNS} = 12.5$ mV.                                                                                                    |

| Current<br>measurement<br>accuracy         | A <sub>IIN</sub>  | -    | ±1.5   | ±5.4 | % | Between ISNS_REF & ISNS pins. $V_{\Delta ISNS} = V_{SNS} c_S / 4$ ,<br>where $V_{SNS} c_S = 12.5$ mV.                                                                                            |

| Calculated<br>input power<br>accuracy      | A <sub>PIN</sub>  | -    | ±0.35  | ±0.7 | % | At VDD_RTNS vs GND: VDD_RTNS = 40 V to 80 V,<br>$V_{TLM} = 88 V.$ And voltage between ISNS_REF &<br>ISNS pins: $V_{\Delta ISNS} = V_{SNS_CS}$ , where $V_{SNS_CS} = 100 \text{ mV}$<br>or 50 mV. |

| Calculated<br>input power<br>accuracy      | A <sub>PIN</sub>  | -    | ±0.41  | ±1.2 | % | At VDD_RTNS vs GND: VDD_RTNS = 40 V to 80 V,<br>$V_{TLM} = 88 V$ .<br>And voltage between ISNS_REF &<br>ISNS pins: $V_{\Delta ISNS} = V_{SNS_CS}$ , where $V_{SNS_CS} = 25 \text{ mV}$           |

tion IC

3 General product characteristics

#### Table 9 (continued) Electrical characteristics

VDD\_RTN - GND = 48 V,  $V_{ISNS_{REF}} = 0 V$ ,  $V_{\Delta ISNS} = (V_{ISNS_{REF}} - V_{ISNS}) = 0 V$ ,  $T_J = -40^{\circ}$ C to +125°C, unless otherwise noted.

| Parameter                                         | Symbol               |      | Values |       | Unit | Note or condition                                                                                                                                                                                                 |

|---------------------------------------------------|----------------------|------|--------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                   |                      | Min. | Тур.   | Max.  |      |                                                                                                                                                                                                                   |

| Calculated input power                            | A <sub>PIN</sub>     | -    | ±0.65  | ±1.8  | %    | At VDD_RTNS vs GND: VDD_RTNS = 40 V to 80 V,<br>$V_{TLM}$ = 88 V.                                                                                                                                                 |

| accuracy                                          |                      |      |        |       |      | And voltage between ISNS_REF & ISNS pins: $V_{\Delta ISNS} = V_{SNS_{CS}}$ , where $V_{SNS_{CS}} = 12.5$ mV.                                                                                                      |

| Calculated<br>energy accuracy                     | A <sub>EIN</sub>     | -    | 1.4    | 2.1   | %    | At VDD_RTNS vs GND: VDD_RTNS = 40 V to 80 V,<br>VTLM = 88 V. And voltage between ISNS_REF & ISNS<br>pins: VΔISNS = VSNS_CS, where VSNS_CS = 100 mV<br>or 50 mV.                                                   |

| Calculated<br>energy accuracy                     | A <sub>EIN</sub>     | -    | 1.4    | 2.7   | %    | At VDD_RTNS vs GND: VDD_RTNS = 40 V to 80 V,<br>VTLM = 88 V. And voltage between ISNS_REF & ISNS<br>pins: V $\Delta$ ISNS = VSNS_CS, where VSNS_CS = 25 mV                                                        |

| Calculated<br>energy accuracy                     | A <sub>EIN</sub>     | -    | 1.7    | 3.3   | %    | At VDD_RTNS vs GND: VDD_RTNS = 40 V to 80 V,<br>VTLM = 88 V. And voltage between ISNS_REF & ISNS<br>pins: V $\Delta$ ISNS = VSNS_CS, where VSNS_CS = 12.5<br>mV.                                                  |

| On-chip<br>temperature<br>monitored<br>range      | T <sub>ON-CHIP</sub> | -40  | -      | 150   | °C   |                                                                                                                                                                                                                   |

| On-chip<br>temperature<br>measurement<br>accuracy | A <sub>T2</sub>      | -5   | -      | 5     | °C   |                                                                                                                                                                                                                   |

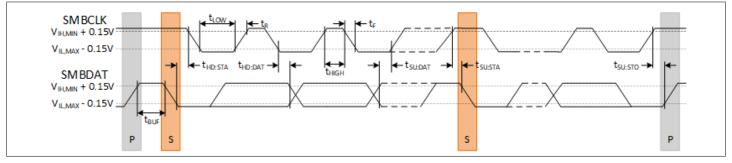

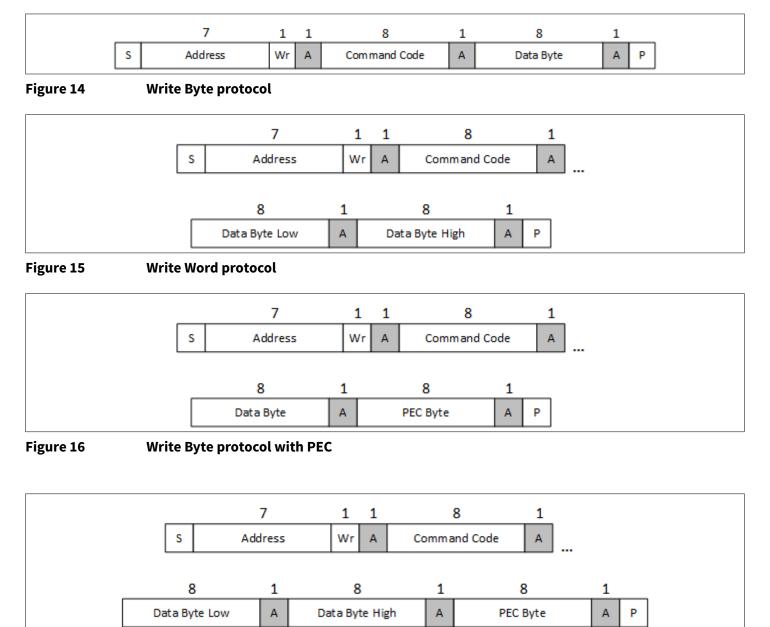

| Temperature<br>measurements<br>accuracy           | A <sub>T1</sub>      | -    | ±4.0   | ±12.5 | °C   | Sourcing currents in TSNS_P pin.<br>Sense the voltage between TSNS_P & TSNS_N pins.<br>External transistor is: MMBT3904.                                                                                          |