Microcontrollers

Edition 2006-08

Published by

Infineon Technologies AG

81726 München, Germany

© Infineon Technologies AG 2006.

All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# XC167CI-16F

16-Bit Single-Chip Microcontroller with C166SV2 Core

Microcontrollers

#### XC167

Revision History: V1.3, 2006-08

Previous Version(s):

V1.2, 2006-03

V1.1, 2003-06

V1.0, 2002-10

| Page      | Subjects (major changes since last revision)                                                                                                                                                                                                                        |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13        | Description of the TRST signal modified.                                                                                                                                                                                                                            |

| 19        | Footnote added about pins XTAL1/XTAL3 belonging to $V_{\mathrm{DDI}}$ power domain.                                                                                                                                                                                 |

| <b>53</b> | Instructions Set Summary improved.                                                                                                                                                                                                                                  |

| 60        | Footnote added about amplitude at XTAL1 pin.                                                                                                                                                                                                                        |

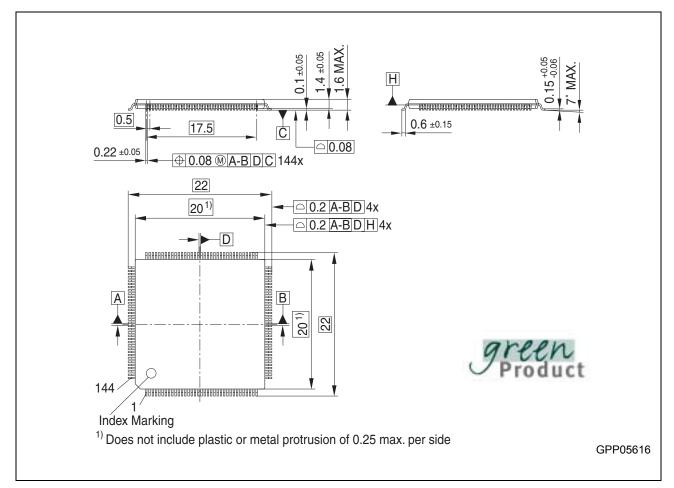

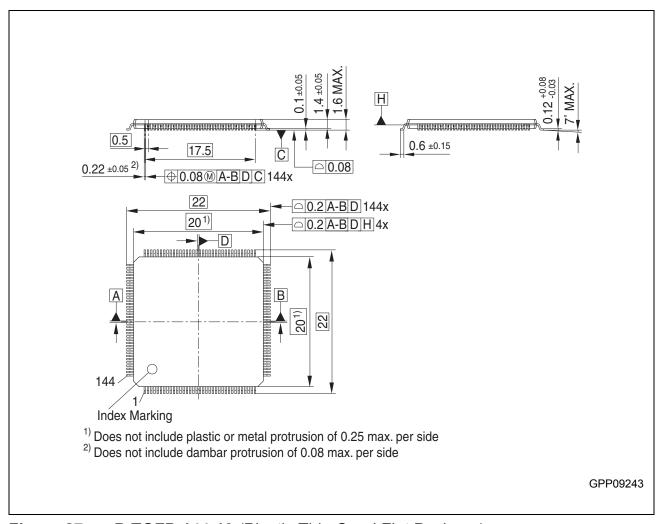

| 85        | Green package added.                                                                                                                                                                                                                                                |

| 85        | Thermal Resistance: $R_{\rm THA}$ replaced by $R_{\rm \ThetaJC}$ and $R_{\rm \ThetaJL}$ because $R_{\rm THA}$ strongly depends on the external system (PCB, environment). $P_{\rm DISS}$ removed, because no static parameter, but derived from thermal resistance. |

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document.

Please send your proposal (including a réference to this document) to:

mcdocu.comments@infineon.com

Data Sheet V1.3, 2006-08

## **Table of Contents**

# **Table of Contents**

| 1               | Summary of Features                                      | 4   |

|-----------------|----------------------------------------------------------|-----|

| <b>2</b><br>2.1 | General Device Information                               | 7   |

| 2.2             | Pin Configuration and Definition                         | 8   |

| 3               | Functional Description                                   | 1.1 |

| 3.1             | Memory Subsystem and Organization                        | 2   |

| 3.2             | External Bus Controller                                  |     |

| 3.3             | Central Processing Unit (CPU)                            | 6   |

| 3.4             | Interrupt System                                         | 8   |

| 3.5             | On-Chip Debug Support (OCDS)                             | 3   |

| 3.6             | Capture/Compare Units (CAPCOM1/2)                        |     |

| 3.7             | The Capture/Compare Unit CAPCOM6                         |     |

| 3.8             | General Purpose Timer (GPT12E) Unit                      |     |

| 3.9             | Real Time Clock                                          |     |

| 3.10            | A/D Converter 4                                          |     |

| 3.11            | Asynchronous/Synchronous Serial Interfaces (ASC0/ASC1) 4 | 5   |

| 3.12            | High Speed Synchronous Serial Channels (SSC0/SSC1) 4     |     |

| 3.13            | TwinCAN Module                                           |     |

| 3.14            | IIC Bus Module 4                                         |     |

| 3.15            | Watchdog Timer                                           | 9   |

| 3.16            | Clock Generation                                         |     |

| 3.17            | Parallel Ports                                           |     |

| 3.18            | Power Management                                         |     |

| 3.19            | Instruction Set Summary                                  |     |

| 4               | Electrical Parameters 5                                  | 6   |

| 4.1             | General Parameters                                       |     |

| 4.2             | DC Parameters 5                                          |     |

| 4.3             | Analog/Digital Converter Parameters 6                    | 5   |

| 4.4             | AC Parameters 6                                          |     |

| 4.4.1           | Definition of Internal Timing                            | 8   |

| 4.4.2           | On-chip Flash Operation 7                                |     |

| 4.4.3           | External Clock Drive XTAL1 7                             |     |

| 4.4.4           | Testing Waveforms                                        |     |

| 4.4.5           | External Bus Timing                                      |     |

| 5               | Package and Reliability                                  | 5   |

| 5.1             | Packaging                                                | 5   |

| 5.2             | Flash Memory Parameters 8                                |     |

# 16-Bit Single-Chip Microcontroller with C166SV2 Core XC166 Family

XC167

## 1 Summary of Features

- High Performance 16-bit CPU with 5-Stage Pipeline

- 25 ns Instruction Cycle Time at 40 MHz CPU Clock (Single-Cycle Execution)

- 1-Cycle Multiplication (16 ×16 bit), Background Division (32 / 16 bit) in 21 Cycles

- 1-Cycle Multiply-and-Accumulate (MAC) Instructions

- Enhanced Boolean Bit Manipulation Facilities

- Zero-Cycle Jump Execution

- Additional Instructions to Support HLL and Operating Systems

- Register-Based Design with Multiple Variable Register Banks

- Fast Context Switching Support with Two Additional Local Register Banks

- 16 Mbytes Total Linear Address Space for Code and Data

- 1024 Bytes On-Chip Special Function Register Area (C166 Family Compatible)

- 16-Priority-Level Interrupt System with 77 Sources, Sample-Rate down to 50 ns

- 8-Channel Interrupt-Driven Single-Cycle Data Transfer Facilities via Peripheral Event Controller (PEC), 24-Bit Pointers Cover Total Address Space

- Clock Generation via on-chip PLL (factors 1:0.15 ... 1:10), or via Prescaler (factors 1:1 ... 60:1)

- On-Chip Memory Modules

- 2 Kbytes On-Chip Dual-Port RAM (DPRAM)

- 4 Kbytes On-Chip Data SRAM (DSRAM)

- 2 Kbytes On-Chip Program/Data SRAM (PSRAM)

- 128 Kbytes On-Chip Program Memory (Flash Memory)

- On-Chip Peripheral Modules

- 16-Channel A/D Converter with Programmable Resolution (10-bit or 8-bit) and Conversion Time (down to 2.55 μs or 2.15 μs)

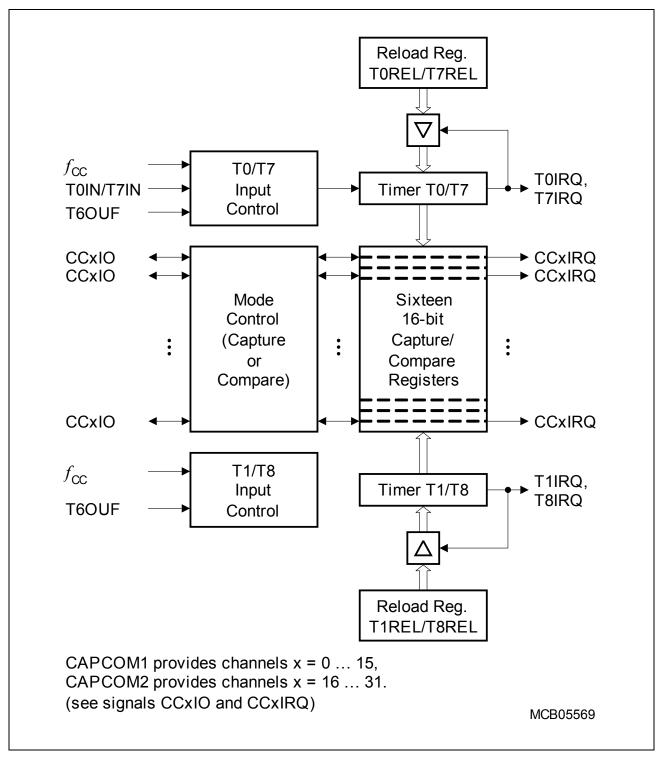

- Two 16-Channel General Purpose Capture/Compare Units (32 Input/Output Pins)

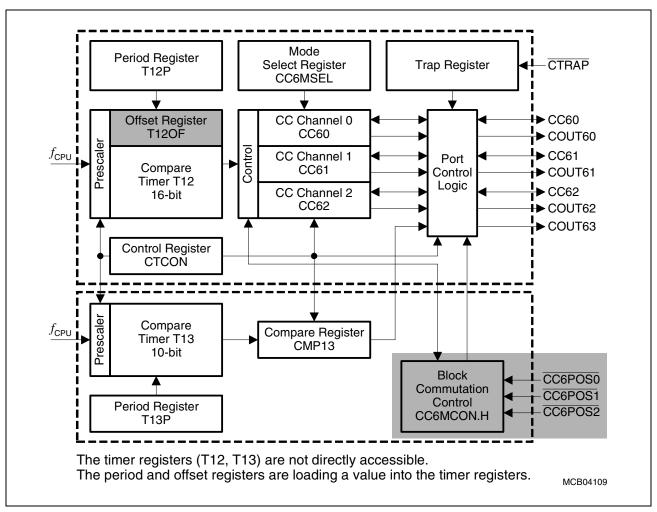

- Capture/Compare Unit for flexible PWM Signal Generation (CAPCOM6)

(3/6 Capture/Compare Channels and 1 Compare Channel)

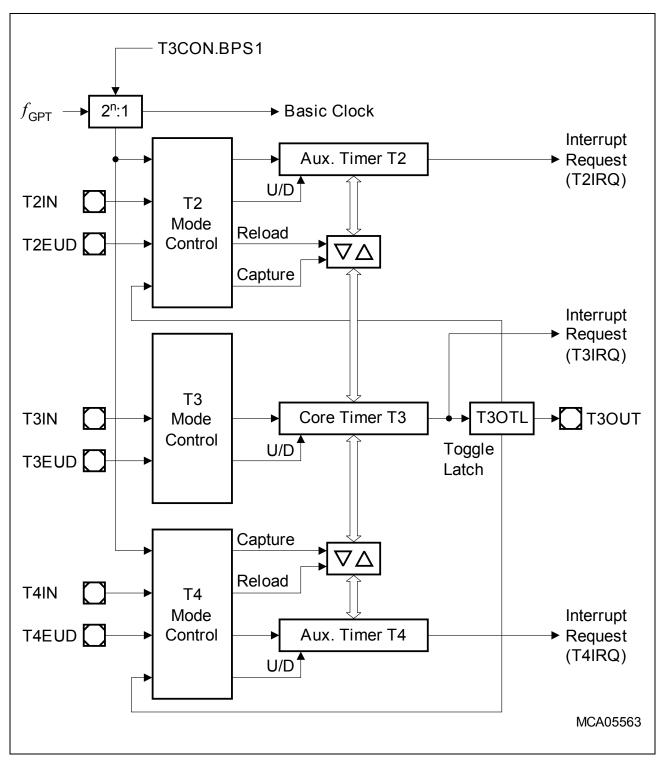

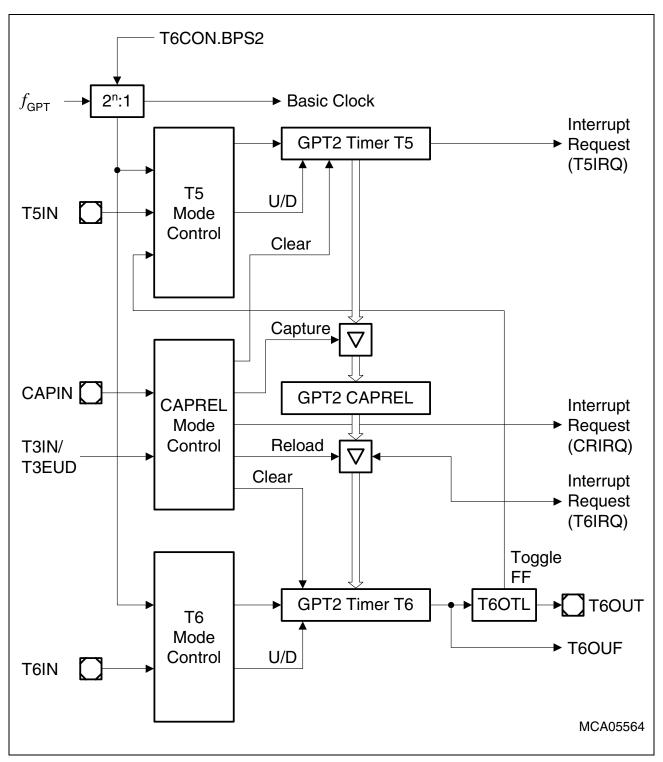

- Multi-Functional General Purpose Timer Unit with 5 Timers

- Two Synchronous/Asynchronous Serial Channels (USARTs)

- Two High-Speed-Synchronous Serial Channels

- On-Chip TwinCAN Interface (Rev. 2.0B active) with 32 Message Objects (Full CAN/Basic CAN) on Two CAN Nodes, and Gateway Functionality

- IIC Bus Interface (10-bit addressing, 400 kbit/s) with 3 Channels (multiplexed)

- On-Chip Real Time Clock, Driven by Dedicated Oscillator

- Idle, Sleep, and Power Down Modes with Flexible Power Management

- Programmable Watchdog Timer and Oscillator Watchdog

Data Sheet 4 V1.3, 2006-08

#### **Summary of Features**

- Up to 12 Mbytes External Address Space for Code and Data

- Programmable External Bus Characteristics for Different Address Ranges

- Multiplexed or Demultiplexed External Address/Data Buses

- Selectable Address Bus Width

- 16-Bit or 8-Bit Data Bus Width

- Five Programmable Chip-Select Signals

- Hold- and Hold-Acknowledge Bus Arbitration Support

- Up to 103 General Purpose I/O Lines, partly with Selectable Input Thresholds and Hysteresis

- On-Chip Bootstrap Loader

- Supported by a Large Range of Development Tools like C-Compilers,

Macro-Assembler Packages, Emulators, Evaluation Boards, HLL-Debuggers,

Simulators, Logic Analyzer Disassemblers, Programming Boards

- On-Chip Debug Support via JTAG Interface

- 144-Pin Green TQFP Package, 0.5 mm (19.7 mil) pitch (RoHS compliant)

#### **Ordering Information**

The ordering code for Infineon microcontrollers provides an exact reference to the required product. This ordering code identifies:

- the derivative itself, i.e. its function set, the temperature range, and the supply voltage

- the package and the type of delivery.

For the available ordering codes for the XC167 please refer to the "**Product Catalog Microcontrollers**", which summarizes all available microcontroller variants.

Note: The ordering codes for Mask-ROM versions are defined for each product after verification of the respective ROM code.

This document describes several derivatives of the XC167 group. **Table 1** enumerates these derivatives and summarizes the differences. As this document refers to all of these derivatives, some descriptions may not apply to a specific product.

For simplicity all versions are referred to by the term **XC167** throughout this document.

Data Sheet 5 V1.3, 2006-08

## **Summary of Features**

Table 1 XC167 Derivative Synopsis

| Derivative <sup>1)</sup>                  | Temp.<br>Range      | Program<br>Memory   | On-Chip RAM                                          | Interfaces                                       |

|-------------------------------------------|---------------------|---------------------|------------------------------------------------------|--------------------------------------------------|

| SAK-XC167CI-16F40F,<br>SAK-XC167CI-16F20F | -40 °C to<br>125 °C | 128 Kbytes<br>Flash | 2 Kbytes DPRAM,<br>4 Kbytes DSRAM,<br>2 Kbytes PSRAM | ASC0, ASC1,<br>SSC0, SSC1,<br>CAN0, CAN1,<br>IIC |

| SAF-XC167CI-16F40F,<br>SAF-XC167CI-16F20F | -40 °C to<br>85 °C  | 128 Kbytes<br>Flash | 2 Kbytes DPRAM,<br>4 Kbytes DSRAM,<br>2 Kbytes PSRAM | ASC0, ASC1,<br>SSC0, SSC1,<br>CAN0, CAN1,<br>IIC |

<sup>1)</sup> This Data Sheet is valid for devices starting with and including design step BB.

## 2 General Device Information

#### 2.1 Introduction

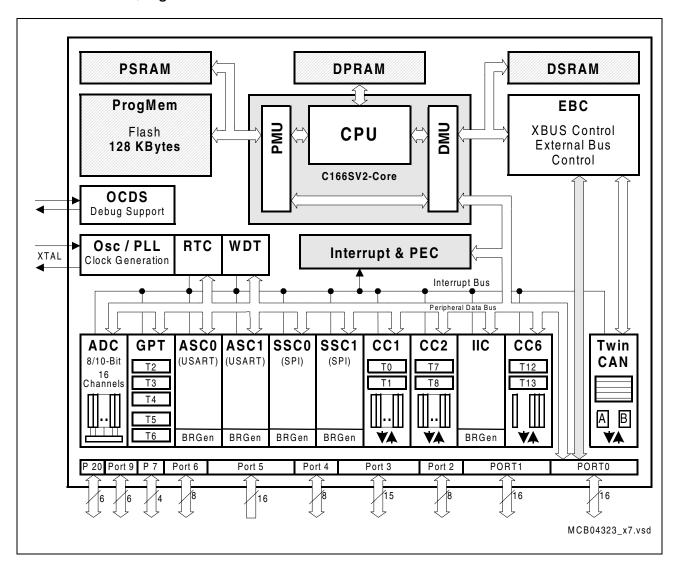

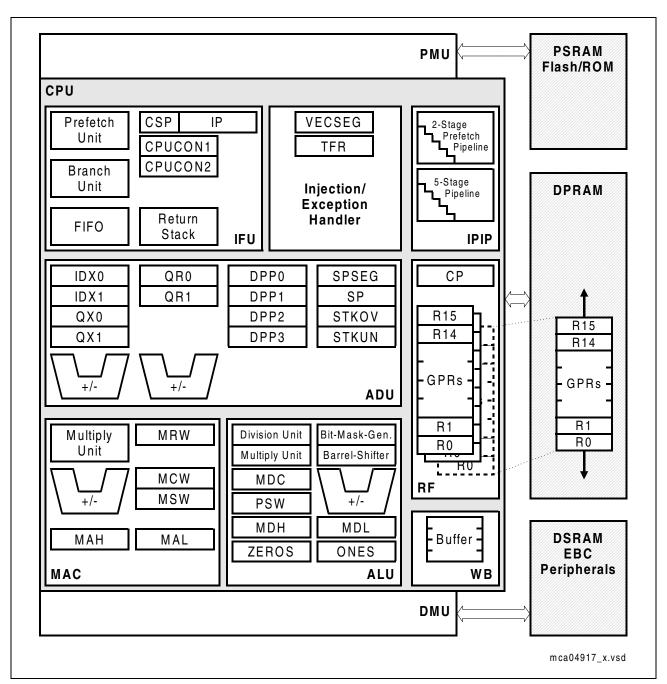

The XC167 derivatives are high-performance members of the Infineon XC166 Family of full featured single-chip CMOS microcontrollers. These devices extend the functionality and performance of the C166 Family in terms of instructions (MAC unit), peripherals, and speed. They combine high CPU performance (up to 40 million instructions per second) with high peripheral functionality and enhanced IO-capabilities. They also provide clock generation via PLL and various on-chip memory modules such as program Flash, program RAM, and data RAM.

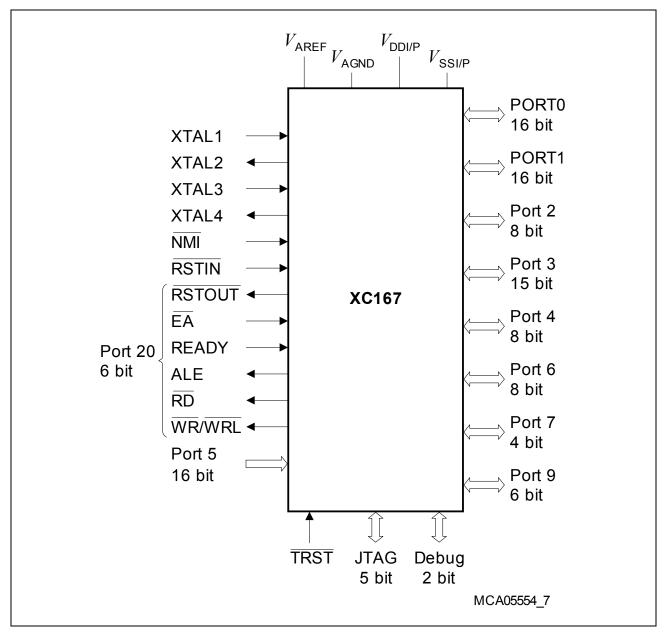

Figure 1 Logic Symbol

Data Sheet 7 V1.3, 2006-08

## 2.2 Pin Configuration and Definition

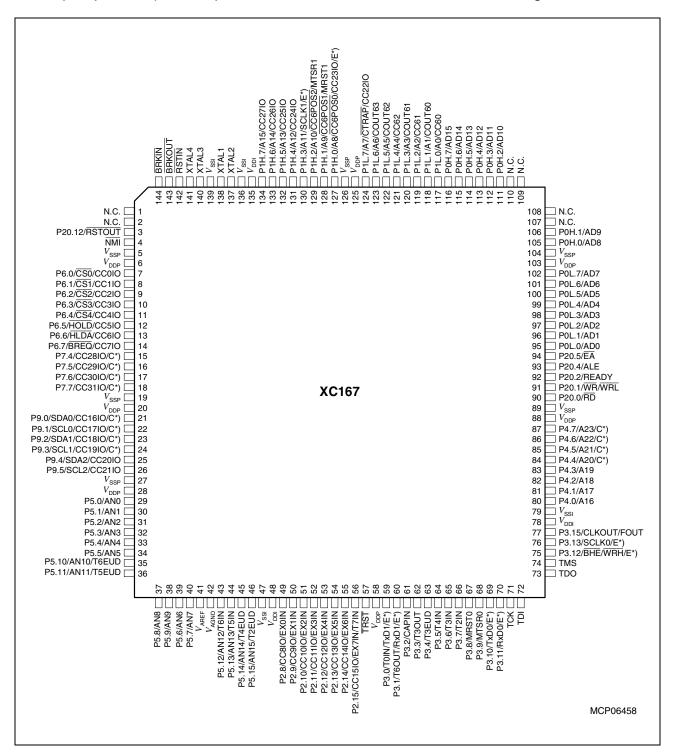

The pins of the XC167 are described in detail in **Table 2**, including all their alternate functions. **Figure 2** summarizes all pins in a condensed way, showing their location on the 4 sides of the package. E\*) and C\*) mark pins to be used as alternate external interrupt inputs, C\*) marks pins that can have CAN interface lines assigned to them.

Figure 2 Pin Configuration (top view)

**Table 2** Pin Definitions and Functions

| Sym-<br>bol | Pin<br>Num. | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                         |  |  |

|-------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| P20.12      | 3           | Ю              | For details                                                                                                                                                                                                                                                                                                                                                                                      | For details, please refer to the description of P20.                                                                                                                                                                                    |  |  |

| NMI         | 4           | I              | Non-Maskable Interrupt Input. A high to low transition at this pin causes the CPU to vector to the NMI trap routine. When the PWRDN (power down) instruction is executed, the NMI pin must be low in order to force the XC167 into power down mode. If NMI is high, when PWRDN is executed, the part will continue to run in normal mode. If not used, pin NMI should be pulled high externally. |                                                                                                                                                                                                                                         |  |  |

| P6          |             | IO             | programme<br>state) or ou<br>driver). The<br>or special).                                                                                                                                                                                                                                                                                                                                        | n 8-bit bidirectional I/O port. Each pin can be ed for input (output driver in high-impedance utput (configurable as push/pull or open drain input threshold of Port 6 is selectable (standard pins also serve for alternate functions: |  |  |

| P6.0        | 7           | O<br>IO        | CS0<br>CC0IO                                                                                                                                                                                                                                                                                                                                                                                     | Chip Select 0 Output, CAPCOM1: CC0 Capture Inp./Compare Output                                                                                                                                                                          |  |  |

| P6.1        | 8           | 0              | CS1<br>CC1IO                                                                                                                                                                                                                                                                                                                                                                                     | Chip Select 1 Output, CAPCOM1: CC1 Capture Inp./Compare Output                                                                                                                                                                          |  |  |

| P6.2        | 9           | 0              | CS2<br>CC2IO                                                                                                                                                                                                                                                                                                                                                                                     | Chip Select 2 Output, CAPCOM1: CC2 Capture Inp./Compare Output                                                                                                                                                                          |  |  |

| P6.3        | 10          | 0              | CS3                                                                                                                                                                                                                                                                                                                                                                                              | Chip Select 3 Output,                                                                                                                                                                                                                   |  |  |

| P6.4        | 11          | 0              | CC3IO<br>CS4                                                                                                                                                                                                                                                                                                                                                                                     | CAPCOM1: CC3 Capture Inp./Compare Output Chip Select 4 Output, CAPCOM1: CC4 Capture Inp./Compare Output                                                                                                                                 |  |  |

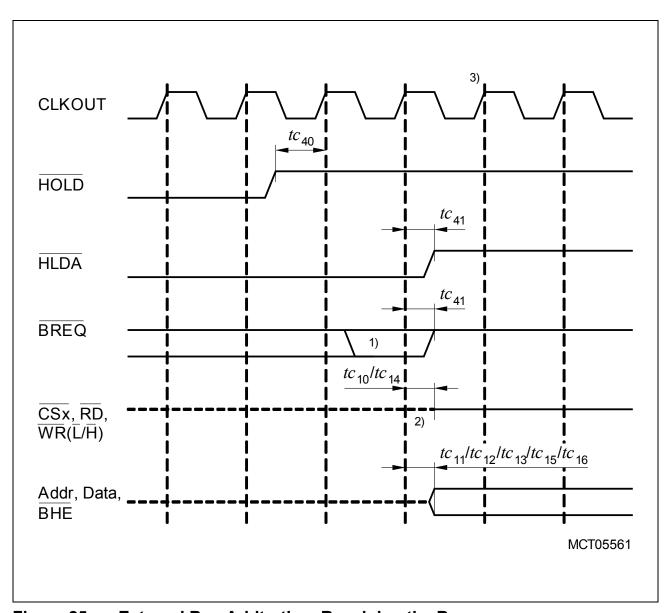

| P6.5        | 12          | IO<br>I        | CC4IO<br>HOLD                                                                                                                                                                                                                                                                                                                                                                                    | CAPCOM1: CC4 Capture Inp./Compare Output External Master Hold Request Input,                                                                                                                                                            |  |  |

| P6.6        | 13          | IO<br>I/O      | CC5IO<br>HLDA                                                                                                                                                                                                                                                                                                                                                                                    | CAPCOM1: CC5 Capture Inp./Compare Output Hold Acknowledge Output (master mode) or Input (slave mode),                                                                                                                                   |  |  |

| P6.7        | 14          | 10<br>0<br>10  | CC6IO<br>BREQ<br>CC7IO                                                                                                                                                                                                                                                                                                                                                                           | CAPCOM1: CC6 Capture Inp./Compare Output<br>Bus Request Output,<br>CAPCOM1: CC7 Capture Inp./Compare Output                                                                                                                             |  |  |

Table 2

Pin Definitions and Functions (cont'd)

| Sym- | Pin  | Input | Function                                                                      |

|------|------|-------|-------------------------------------------------------------------------------|

| bol  | Num. | Outp. |                                                                               |

| P7   |      | Ю     | Port 7 is a 4-bit bidirectional I/O port. Each pin can be                     |

|      |      |       | programmed for input (output driver in high-impedance                         |

|      |      |       | state) or output (configurable as push/pull or open drain                     |

|      |      |       | driver). The input threshold of Port 7 is selectable (standard or special).   |

|      |      |       | Port 7 pins provide inputs/outputs for CAPCOM2 and serial interface lines. 1) |

| P7.4 | 15   | I/O   | CC28IO CAPCOM2: CC28 Capture Inp./Compare Outp.,                              |

|      |      | 1     | CAN2_RxD CAN Node 2 Receive Data Input,                                       |

|      |      | 1     | EX7IN Fast External Interrupt 7 Input (alternate pin B)                       |

| P7.5 | 16   | I/O   | CC29IO CAPCOM2: CC29 Capture Inp./Compare Outp.,                              |

|      |      | 0     | CAN2_TxD CAN Node 2 Transmit Data Output,                                     |

|      |      | 1     | EX6IN Fast External Interrupt 6 Input (alternate pin B)                       |

| P7.6 | 17   | I/O   | CC30IO CAPCOM2: CC30 Capture Inp./Compare Outp.,                              |

|      |      | 1     | CAN1_RxD CAN Node 1 Receive Data Input,                                       |

|      |      | I     | EX7IN Fast External Interrupt 7 Input (alternate pin A)                       |

| P7.7 | 18   | I/O   | CC31IO CAPCOM2: CC31 Capture Inp./Compare Outp.,                              |

|      |      | 0     | CAN1_TxD CAN Node 1 Transmit Data Output,                                     |

|      |      | I     | EX6IN Fast External Interrupt 6 Input (alternate pin A)                       |

Table 2

Pin Definitions and Functions (cont'd)

| Sym-<br>bol | Pin<br>Num. | Input<br>Outp.    | Function                                                                                                                                                                                                                                              |

|-------------|-------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P9          |             | IO                | Port 9 is a 6-bit bidirectional I/O port. Each pin can be programmed for input (output driver in high-impedance state) or output (configurable as push/pull or open drain driver). The input threshold of Port 9 is selectable (standard or special). |

| P9.0        | 21          | I/O               | The following Port 9 pins also serve for alternate functions: <sup>1)</sup> CC16IO CAPCOM2: CC16 Capture Inp./Compare Outp., CAN2 RxD CAN Node 2 Receive Data Input,                                                                                  |

| P9.1        | 22          | I/O<br>I/O<br>O   | SDA0 IIC Bus Data Line 0 CC17IO CAPCOM2: CC17 Capture Inp./Compare Outp., CAN2 TxD CAN Node 2 Transmit Data Output,                                                                                                                                   |

| P9.2        | 23          | I/O<br>I/O<br>I   | SCL0 IIC Bus Clock Line 0 CC18IO CAPCOM2: CC18 Capture Inp./Compare Outp., CAN1_RxD CAN Node 1 Receive Data Input,                                                                                                                                    |

| P9.3        | 24          | I/O<br>I/O<br>O   | SDA1 IIC Bus Data Line 1 CC19IO CAPCOM2: CC19 Capture Inp./Compare Outp., CAN1_TxD CAN Node 1 Transmit Data Output,                                                                                                                                   |

| P9.4        | 25          | I/O<br>I/O<br>I/O | SCL1 IIC Bus Clock Line 1 CC20IO CAPCOM2: CC20 Capture Inp./Compare Outp., SDA2 IIC Bus Data Line 2                                                                                                                                                   |

| P9.5        | 26          | I/O<br>I/O        | CC21IO CAPCOM2: CC21 Capture Inp./Compare Outp., SCL2 IIC Bus Clock Line 2                                                                                                                                                                            |

Table 2

Pin Definitions and Functions (cont'd)

| Sym-<br>bol | Pin<br>Num. | Input<br>Outp. | Function    |            |                                           |

|-------------|-------------|----------------|-------------|------------|-------------------------------------------|

| P5          |             | 1              | Port 5 is a | 16-bit inp | ut-only port.                             |

| . •         |             |                |             | •          | so serve as analog input channels for the |

|             |             |                | •           |            | ey serve as timer inputs:                 |

| P5.0        | 29          | 11             | ANO         |            | y corre de unior inputer                  |

| P5.1        | 30          | 1              | AN1         |            |                                           |

| P5.2        | 31          | 1              | AN2         |            |                                           |

| P5.3        | 32          | 1              | AN3         |            |                                           |

| P5.4        | 33          | 1              | AN4         |            |                                           |

| P5.5        | 34          | 1              | AN5         |            |                                           |

| P5.10       | 35          | 1              | AN10,       | T6EUD      | GPT1 Timer T4 Ext. Up/Down Ctrl. Inp.     |

| P5.11       | 36          | 1              | AN11,       | T5EUD      | GPT1 Timer T2 Ext. Up/Down Ctrl. Inp      |

| P5.8        | 37          | 1              | AN8         |            | •                                         |

| P5.9        | 38          | 1              | AN9         |            |                                           |

| P5.6        | 39          | 1              | AN6         |            |                                           |

| P5.7        | 40          | 1              | AN7         |            |                                           |

| P5.12       | 43          | 1              | AN12,       | T6IN       | GPT2 Timer T6 Count/Gate Input            |

| P5.13       | 44          | 1              | AN13,       | T5IN       | GPT2 Timer T5 Count/Gate Input            |

| P5.14       | 45          | 1              | AN14,       | T4EUD      | GPT1 Timer T4 Ext. Up/Down Ctrl. Inp.     |

| P5.15       | 46          | 1              | AN15,       | T2EUD      | GPT1 Timer T2 Ext. Up/Down Ctrl. Inp.     |

Table 2

Pin Definitions and Functions (cont'd)

| Sym-<br>bol | Pin<br>Num. | Input<br>Outp. | Function                                              |                                                                                                                                                                                                            |

|-------------|-------------|----------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2          |             | IO             | programm<br>state) or o<br>driver). Th<br>or special) |                                                                                                                                                                                                            |

| P2.8        | 49          | I/O            | CC8IO<br>EX0IN                                        | ring Port 2 pins also serve for alternate functions:  CAPCOM1: CC8 Capture Inp./Compare Output,  Fast External Interrupt 0 Input (default pin)                                                             |

| P2.9        | 50          | I/O<br>I       | CC9IO<br>EX1IN                                        | CAPCOM1: CC9 Capture Inp./Compare Output, Fast External Interrupt 1 Input (default pin)                                                                                                                    |

| P2.10       | 51          | I/O            | CC10IO<br>EX2IN                                       | CAPCOM1: CC10 Capture Inp./Compare Outp., Fast External Interrupt 2 Input (default pin)                                                                                                                    |

| P2.11       | 52          | I/O            | CC11IO<br>EX3IN                                       | CAPCOM1: CC11 Capture Inp./Compare Outp., Fast External Interrupt 3 Input (default pin)                                                                                                                    |

| P2.12       | 53          | I/O            | CC12IO<br>EX4IN                                       | CAPCOM1: CC12 Capture Inp./Compare Outp., Fast External Interrupt 4 Input (default pin)                                                                                                                    |

| P2.13       | 54          | I/O<br>I       | CC13IO<br>EX5IN                                       | CAPCOM1: CC13 Capture Inp./Compare Outp., Fast External Interrupt 5 Input (default pin)                                                                                                                    |

| P2.14       | 55          | I/O<br>I       | CC14IO<br>EX6IN                                       | CAPCOM1: CC14 Capture Inp./Compare Outp., Fast External Interrupt 6 Input (default pin)                                                                                                                    |

| P2.15       | 56          | I/O<br>I<br>I  | CC15IO<br>EX7IN<br>T7IN                               | CAPCOM1: CC15 Capture Inp./Compare Outp., Fast External Interrupt 7 Input (default pin), CAPCOM2: Timer T7 Count Input                                                                                     |

| TRST        | 57          | I              | TRST sho                                              | em Reset Input. For normal system operation, pin uld be held low. A high level at this pin at the rising STIN activates the XC164CM's debug system. In pin TRST must be driven low once to reset the stem. |

Table 2

Pin Definitions and Functions (cont'd)

| Sym-<br>bol | Pin<br>Num. | Input<br>Outp. | Function                                                 |                                                                                                                                                                                                                                                     |  |

|-------------|-------------|----------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| P3          |             | Ю              | programme<br>state) or or<br>driver). The<br>or special) | 15-bit bidirectional I/O port. Each pin can be ed for input (output driver in high-impedance utput (configurable as push/pull or open drain e input threshold of Port 3 is selectable (standard ing Port 3 pins also serve for alternate functions: |  |

| P3.0        | 59          | <br>  O<br>    | TOIN<br>TxD1<br>EX1IN                                    | CAPCOM1 Timer T0 Count Input, ASC1 Clock/Data Output (Async./Sync), Fast External Interrupt 1 Input (alternate pin B)                                                                                                                               |  |

| P3.1        | 60          | 0<br>I/O<br>I  | T6OUT<br>RxD1<br>EX1IN                                   | GPT2 Timer T6 Toggle Latch Output, ASC1 Data Input (Async.) or Inp./Outp. (Sync.), Fast External Interrupt 1 Input (alternate pin A)                                                                                                                |  |

| P3.2        | 61          | 1              | CAPIN                                                    | GPT2 Register CAPREL Capture Input                                                                                                                                                                                                                  |  |

| P3.3        | 62          | 0              | T3OUT                                                    | GPT1 Timer T3 Toggle Latch Output                                                                                                                                                                                                                   |  |

| P3.4        | 63          | I              | T3EUD                                                    | GPT1 Timer T3 External Up/Down Control Input                                                                                                                                                                                                        |  |

| P3.5        | 64          | 1              | T4IN                                                     | GPT1 Timer T4 Count/Gate/Reload/Capture Inp                                                                                                                                                                                                         |  |

| P3.6        | 65          | I              | T3IN                                                     | GPT1 Timer T3 Count/Gate Input                                                                                                                                                                                                                      |  |

| P3.7        | 66          | I              | T2IN                                                     | GPT1 Timer T2 Count/Gate/Reload/Capture Inp                                                                                                                                                                                                         |  |

| P3.8        | 67          | I/O            | MRST0                                                    | SSC0 Master-Receive/Slave-Transmit In/Out.                                                                                                                                                                                                          |  |

| P3.9        | 68          | I/O            | MTSR0                                                    | SSC0 Master-Transmit/Slave-Receive Out/In.                                                                                                                                                                                                          |  |

| P3.10       | 69          | 0              | TxD0                                                     | ASC0 Clock/Data Output (Async./Sync.),                                                                                                                                                                                                              |  |

|             |             |                | EX2IN                                                    | Fast External Interrupt 2 Input (alternate pin B)                                                                                                                                                                                                   |  |

| P3.11       | 70          | I/O            | RxD0                                                     | ASC0 Data Input (Async.) or Inp./Outp. (Sync.),                                                                                                                                                                                                     |  |

| P3.12       | 75          | 0              | EX2IN<br>BHE                                             | Fast External Interrupt 2 Input (alternate pin A)                                                                                                                                                                                                   |  |

| F3.12       | 75          | 0              | WRH                                                      | External Memory High Byte Enable Signal, External Memory High Byte Write Strobe,                                                                                                                                                                    |  |

|             |             |                | EX3IN                                                    | Fast External Interrupt 3 Input (alternate pin B)                                                                                                                                                                                                   |  |

| P3.13       | 76          | 1/0            | SCLK0                                                    | SSC0 Master Clock Output/Slave Clock Input.,                                                                                                                                                                                                        |  |

| 1 3.13      | 70          | 1,0            | EX3IN                                                    | Fast External Interrupt 3 Input (alternate pin A)                                                                                                                                                                                                   |  |

| P3.15       | 77          | 0              | CLKOUT                                                   | Master Clock Output,                                                                                                                                                                                                                                |  |

| 1 0.10      | ' '         | Ö              | FOUT                                                     | Programmable Frequency Output                                                                                                                                                                                                                       |  |

| TCK         | 71          | I              | Debug Sys                                                | stem: JTAG Clock Input                                                                                                                                                                                                                              |  |

| TDI         | 72          | I              | Debug Sys                                                | stem: JTAG Data In                                                                                                                                                                                                                                  |  |

| TDO         | 73          | 0              | Debug Sys                                                | stem: JTAG Data Out                                                                                                                                                                                                                                 |  |

| TMS         | 74          | I              | Debug System: JTAG Test Mode Selection                   |                                                                                                                                                                                                                                                     |  |

Table 2

Pin Definitions and Functions (cont'd)

| Sym-<br>bol | Pin<br>Num. | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P4          |             | Ю              | Port 4 is an 8-bit bidirectional I/O port. Each pin can be programmed for input (output driver in high-impedance state) or output (configurable as push/pull or open drain driver). The input threshold of Port 4 is selectable (standard or special).  Port 4 can be used to output the segment address lines, the optional chip select lines, and for serial interface lines: <sup>1)</sup> |

| P4.0        | 80          | 0              | A16 Least Significant Segment Address Line                                                                                                                                                                                                                                                                                                                                                    |

| P4.1        | 81          | 0              | A17 Segment Address Line                                                                                                                                                                                                                                                                                                                                                                      |

| P4.2        | 82          | 0              | A18 Segment Address Line                                                                                                                                                                                                                                                                                                                                                                      |

| P4.3        | 83          | 0              | A19 Segment Address Line                                                                                                                                                                                                                                                                                                                                                                      |

| P4.4        | 84          | 0              | A20 Segment Address Line,                                                                                                                                                                                                                                                                                                                                                                     |

|             |             | 1              | CAN2_RxD CAN Node 2 Receive Data Input,                                                                                                                                                                                                                                                                                                                                                       |

|             |             | 1              | EX5IN Fast External Interrupt 5 Input (alternate pin B)                                                                                                                                                                                                                                                                                                                                       |

| P4.5        | 85          | 0              | A21 Segment Address Line,                                                                                                                                                                                                                                                                                                                                                                     |

|             |             | I              | CAN1_RxD CAN Node 1 Receive Data Input,                                                                                                                                                                                                                                                                                                                                                       |

|             |             | I              | EX4IN Fast External Interrupt 4 Input (alternate pin B)                                                                                                                                                                                                                                                                                                                                       |

| P4.6        | 86          | 0              | A22 Segment Address Line,                                                                                                                                                                                                                                                                                                                                                                     |

|             |             | 0              | CAN1_TxD CAN Node 1 Transmit Data Output,                                                                                                                                                                                                                                                                                                                                                     |

|             |             | I              | EX5IN Fast External Interrupt 5 Input (alternate pin A)                                                                                                                                                                                                                                                                                                                                       |

| P4.7        | 87          | 0              | A23 Most Significant Segment Address Line,                                                                                                                                                                                                                                                                                                                                                    |

|             |             | I              | CAN1_RxD CAN Node 1 Receive Data Input,                                                                                                                                                                                                                                                                                                                                                       |

|             |             | 0              | CAN2_TxD CAN Node 2 Transmit Data Output,                                                                                                                                                                                                                                                                                                                                                     |

|             |             | I              | EX4IN Fast External Interrupt 4 Input (alternate pin A)                                                                                                                                                                                                                                                                                                                                       |

Table 2 Pin Definitions and Functions (cont'd)

| Sym-<br>bol | Pin<br>Num. | Input<br>Outp. | Function                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|-------------|----------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P20         |             | Ю              | programme<br>state) or or<br>(standard | a 6-bit bidirectional I/O port. Each pin can be ed for input (output driver in high-impedance utput. The input threshold of Port 20 is selectable or special).  Ing Port 20 pins also serve for alternate functions:                                                                                                                                                                                                                            |

| P20.0       | 90          | 0              | RD                                     | External Memory Read Strobe, activated for every external instruction or data read access.                                                                                                                                                                                                                                                                                                                                                      |

| P20.1       | 91          | О              | WR/WRL                                 | External Memory Write Strobe. In WR-mode this pin is activated for every external data write access. In WRL-mode this pin is activated for low byte data write accesses on a 16-bit bus, and for every data write access on an 8-bit bus.                                                                                                                                                                                                       |

| P20.2       | 92          | I              | READY                                  | READY Input. When the READY function is enabled, memory cycle time waitstates can be forced via this pin during an external access.                                                                                                                                                                                                                                                                                                             |

| P20.4       | 93          | 0              | ALE                                    | Address Latch Enable Output. Can be used for latching the address into external memory or an address latch in the                                                                                                                                                                                                                                                                                                                               |

| P20.5       | 94          | 1              | ĒĀ                                     | multiplexed bus modes. External Access Enable pin.  A low-level at this pin during and after Reset forces the XC167 to latch the configuration from PORT0 and pin RD, and to begin instruction execution out of external memory.  A high-level forces the XC167 to latch the configuration from pins RD, ALE, and WR, and to begin instruction execution out of the internal program memory. "ROMless" versions must have this pin tied to '0'. |

| P20.12      | 3           | O              | RSTOUT  Note: Port                     | Internal Reset Indication Output.  Is activated asynchronously with an external hardware reset. It may also be activated (selectable) synchronously with an internal software or watchdog reset.  Is deactivated upon the execution of the EINIT instruction, optionally at the end of reset, or at any time (before EINIT) via user software.  20 pins may input configuration values (see EA).                                                |

Table 2

Pin Definitions and Functions (cont'd)

| Sym-<br>bol                                               | Pin<br>Num.                                  | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------|----------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PORT0                                                     |                                              | Ю              | PORT0 consists of the two 8-bit bidirectional I/O ports P0L                                                                                                                                                                                                                                                                                                                                                                     |

| P0L.0 -<br>P0L.7,<br>P0H.0,<br>P0H.1,<br>P0H.2 -<br>P0H.7 | 95 -<br>102,<br>105,<br>106,<br>111 -<br>116 |                | and P0H. Each pin can be programmed for input (output driver in high-impedance state) or output.  In case of an external bus configuration, PORT0 serves as the address (A) and address/data (AD) bus in multiplexed bus modes and as the data (D) bus in demultiplexed bus modes.  Demultiplexed bus modes:  8-bit data bus: P0H = I/O, P0L = D7 - D0  Multiplexed bus modes:  8-bit data bus: P0H = A15 - A8, P0L = AD7 - AD0 |

|                                                           |                                              |                | 16-bit data bus: P0H = AD15 - AD8, P0L = AD7 - AD0  Note: At the end of an external reset (EA = 0) PORT0 also may input configuration values.                                                                                                                                                                                                                                                                                   |

Table 2

Pin Definitions and Functions (cont'd)

| Sym-                                                                 | Pin                                                  | Input                                 | Function                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|----------------------------------------------------------------------|------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bol                                                                  | Num.                                                 | Outp.                                 |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| PORT1                                                                |                                                      | Ю                                     | PORT1 consists of the two 8-bit bidirectional I/O ports P1L and P1H. Each pin can be programmed for input (output driver in high-impedance state) or output.  PORT1 is used as the 16-bit address bus (A) in demultiplexed bus modes (also after switching from a demultiplexed to a multiplexed bus mode). |                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                                                                      |                                                      |                                       |                                                                                                                                                                                                                                                                                                             | ng PORT1 pins also serve for alt. functions:                                                                                                                                                                                                                                                                                                                                                                             |  |

| P1L.0<br>P1L.1<br>P1L.2<br>P1L.3<br>P1L.4<br>P1L.5<br>P1L.6<br>P1L.7 | 117<br>118<br>119<br>120<br>121<br>122<br>123<br>124 | I/O<br>O<br>I/O<br>O<br>I/O<br>O<br>I | CC60<br>COUT60<br>CC61<br>COUT61<br>CC62<br>COUT62<br>COUT63<br>CTRAP                                                                                                                                                                                                                                       | CAPCOM6: Input / Output of Channel 0 CAPCOM6: Output of Channel 0 CAPCOM6: Input / Output of Channel 1 CAPCOM6: Output of Channel 1 CAPCOM6: Input / Output of Channel 2 CAPCOM6: Output of Channel 2 Output of 10-bit Compare Channel CAPCOM2: CC22 Capture Inp./Compare Outp. CTRAP is an input pin with an internal pull-up resistor. A low level on this pin switches the CAPCOM6 compare outputs to the logic level |  |

| P1H.0                                                                | 127                                                  | I/O<br>I<br>I<br>I/O                  | CC22IO<br>CC6POS0<br>EX0IN<br>CC23IO                                                                                                                                                                                                                                                                        | defined by software (if enabled). CAPCOM2: CC22 Capture Inp./Compare Outp. CAPCOM6: Position 0 Input, Fast External Interrupt 0 Input (alternate pin B), CAPCOM2: CC23 Capture Inp./Compare Outp.                                                                                                                                                                                                                        |  |

| P1H.1                                                                | 128                                                  |                                       | CC6POS1<br>MRST1                                                                                                                                                                                                                                                                                            | CAPCOM2: CC23 Capture Inp./Compare Outp.  CAPCOM6: Position 1 Input,  SSC1 Master-Receive/Slave-Transmit In/Out.                                                                                                                                                                                                                                                                                                         |  |

| P1H.2                                                                | 129                                                  | I<br>I/O                              | CC6POS2<br>MTSR1                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| P1H.3                                                                | 130                                                  | I/O<br>I                              | SCLK1<br>EX0IN                                                                                                                                                                                                                                                                                              | SSC1 Master Clock Output / Slave Clock Input,<br>Fast External Interrupt 0 Input (alternate pin A)                                                                                                                                                                                                                                                                                                                       |  |

| P1H.4                                                                | 131                                                  | I/O                                   | CC24IO                                                                                                                                                                                                                                                                                                      | CAPCOM2: CC24 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                                                                                 |  |

| P1H.5<br>P1H.6<br>P1H.7                                              | 132<br>133<br>134                                    | I/O<br>I/O<br>I/O                     | CC25IO<br>CC26IO<br>CC27IO                                                                                                                                                                                                                                                                                  | CAPCOM2: CC25 Capture Inp./Compare Outp. CAPCOM2: CC26 Capture Inp./Compare Outp. CAPCOM2: CC27 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                               |  |

Table 2

Pin Definitions and Functions (cont'd)

| Sym-<br>bol    | Pin<br>Num.           | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|----------------|-----------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| XTAL2<br>XTAL1 | 137<br>138            | O              | XTAL2: Output of the main oscillator amplifier circuit XTAL1: Input to the main oscillator amplifier and input to the internal clock generator To clock the device from an external source, drive XTAL1, while leaving XTAL2 unconnected. Minimum and maximum high/low and rise/fall times specified in the AC Characteristics must be observed.  Note: Input pin XTAL1 belongs to the core voltage domain. Therefore, input voltages must be within the range                                                      |  |  |

|                |                       |                | defined for $V_{\mathrm{DDI}}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| XTAL3<br>XTAL4 | 140<br>141            | 0              | XTAL3: Input to the auxiliary (32-kHz) oscillator amplifier XTAL4: Output of the auxiliary (32-kHz) oscillator amplifier circuit  To clock the device from an external source, drive XTAL3, while leaving XTAL4 unconnected. Minimum and maximum high/low and rise/fall times specified in the AC Characteristics must be observed.                                                                                                                                                                                 |  |  |

|                |                       |                | Note: Input pin XTAL3 belongs to the core voltage domain. Therefore, input voltages must be within the range defined for $V_{\mathrm{DDI}}$ .                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| RSTIN          | 142                   | I              | Reset Input with Schmitt-Trigger characteristics. A low-level at this pin while the oscillator is running resets the XC167. A spike filter suppresses input pulses < 10 ns. Input pulses > 100 ns safely pass the filter. The minimum duration for a safe recognition should be 100 ns + 2 CPU clock cycles.  Note: The reset duration must be sufficient to let the hardware configuration signals settle.  External circuitry must guarantee low-level at the RSTIN pin at least until both power supply voltages |  |  |

|                |                       |                | have reached the operating range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| BRK<br>OUT     | 143                   | О              | Debug System: Break Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| BRKIN          | 144                   | I              | Debug System: Break In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| NC             | 1, 2,<br>107 -<br>110 | _              | No connection. It is recommended not to connect these pins to the PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

Table 2

Pin Definitions and Functions (cont'd)

| Sym-<br>bol          | Pin<br>Num.                             | Input<br>Outp. | Function                                                                                                                                       |  |

|----------------------|-----------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $V_{AREF}$           | 41                                      | _              | Reference voltage for the A/D converter.                                                                                                       |  |

| $V_{AGND}$           | 42                                      | _              | Reference ground for the A/D converter.                                                                                                        |  |

| $V_{DDI}$            | 48, 78,<br>135                          | -              | Digital Core Supply Voltage (On-Chip Modules): +2.5 V during normal operation and idle mode. Please refer to the Operating Conditions.         |  |

| $\overline{V_{DDP}}$ | 6, 20,<br>28, 58,<br>88,<br>103,<br>125 | -              | Digital Pad Supply Voltage (Pin Output Drivers): +5 V during normal operation and idle mode. Please refer to the <b>Operating Conditions</b> . |  |

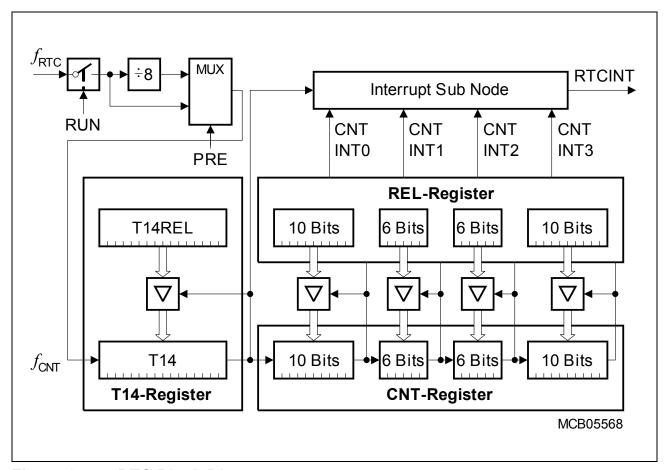

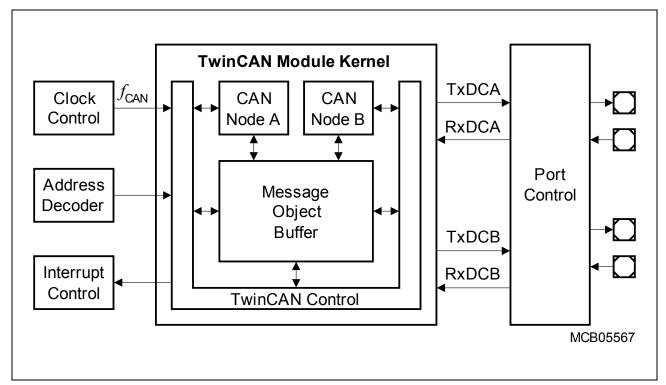

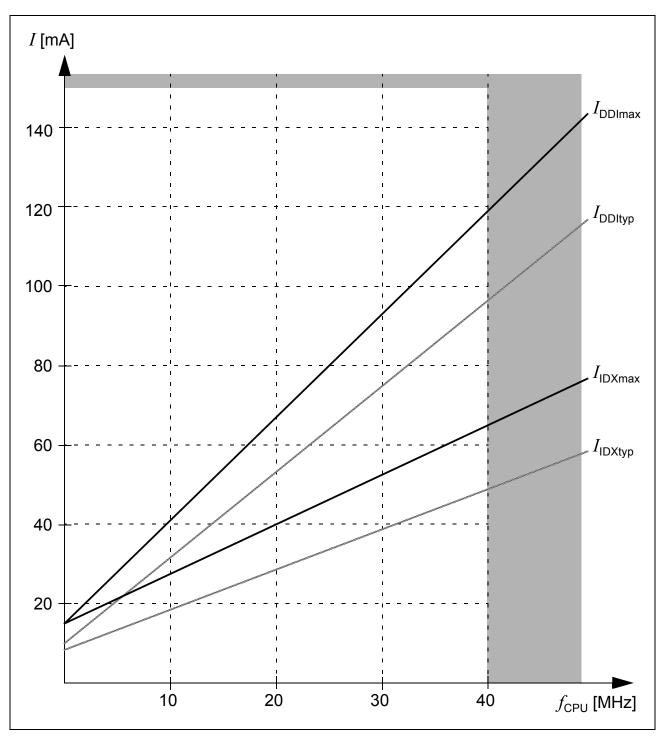

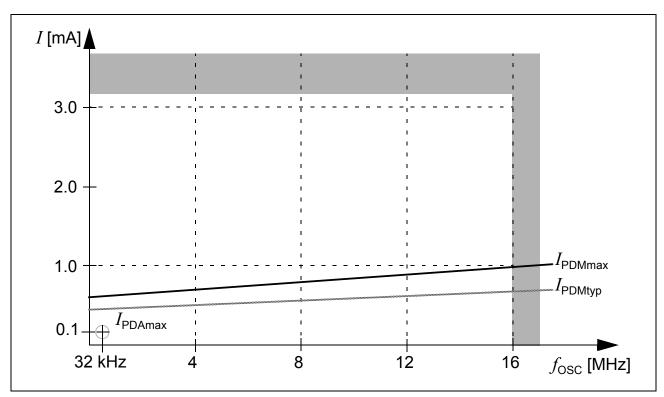

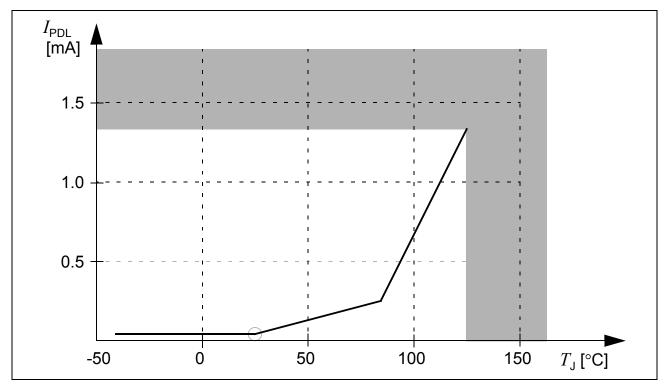

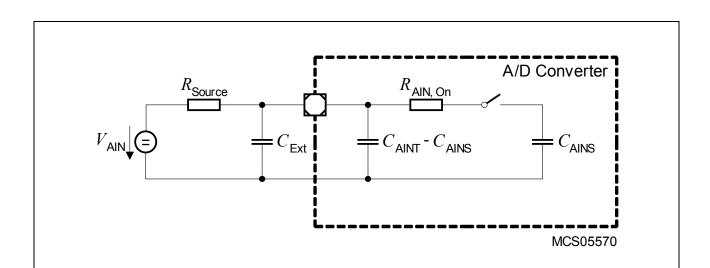

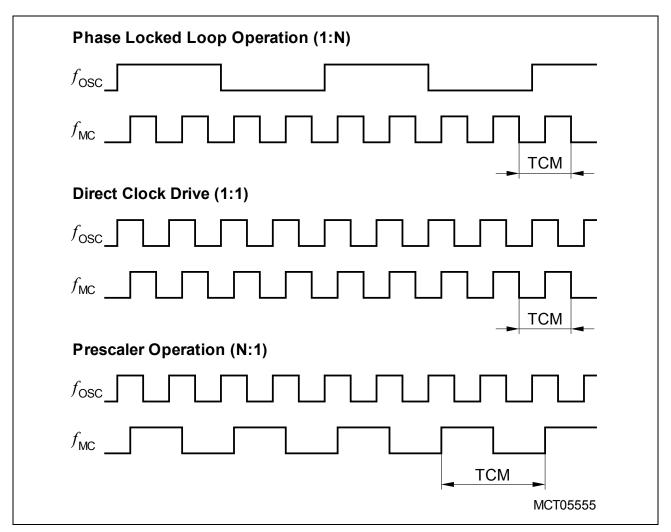

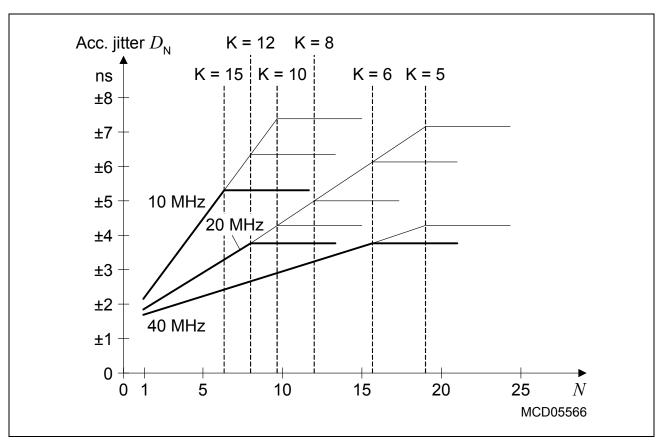

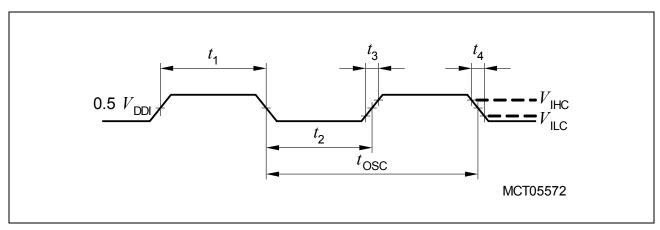

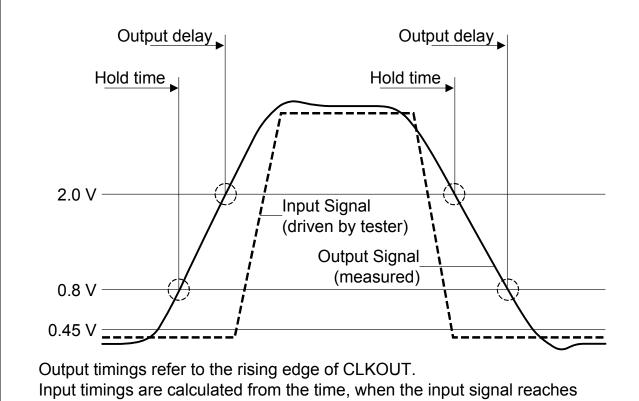

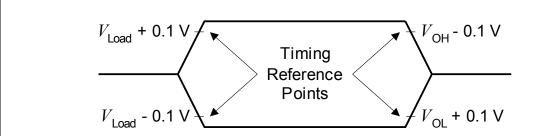

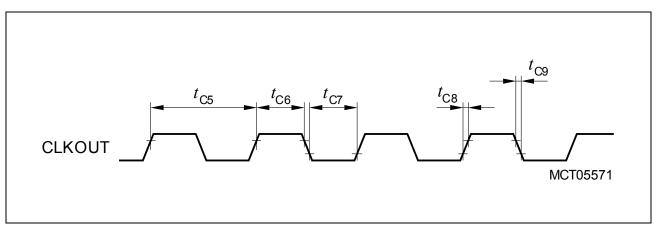

| $V_{\rm SSI}$        | 47, 79,<br>136,<br>139                  | _              |                                                                                                                                                |  |