# **OptimosTM Powerstage**

### TLF12505

### Features

- Integrated driver, control MOSFET Q1 and synchronous MOSFET Q2

- On-chip MOSFET Current sensing and reporting at 5uA/A.

- Input voltage (VIN) range of 4.25 V to 20 V

- VCC and VDRV supply of 4.9 V to 5.5 V

- Output voltage range from 0.225 V up to 5.5 V at VIN = 12 V

- Output current capability of 60 A

- Operation up to 2 MHz

- VDRV under voltage lockout (UVLO)

- Bootstrap under-voltage protection and flag

- 8mV / °C temperature analog output

- Over temperature protection flag and thermal shutdown

- Cycle-by-cycle over current protection (OCP) and flag

- Cycle-by-cycle negative over current protection (NOCP)

- Control MOSFET short (HSS) detection and flag

- Auto-replenishment on bootstrap capacitor

- Compatible with 3.3V and 5 V tri-state PWM Input

- DEEP SLEEP mode for power saving via EN= low (32 µA typ.)

- Small 5 mm x 6 mm x 0.9 mm PQFN package

- Lead free RoHS compliant package

- Compliant to automotive AEC-Q100 Rev H Grade 1 requirements

## **Potential applications**

- Automotive Computing (ADAS/AD, Cockpit etc.)

- DDR memory

## Description

- Qualified for automotive applications requiring AEC-Q100 Rev H Grade 1 Compliance

- High frequency, low profile DC-DC converters

The TLF12505 integrated power-stage contains a low quiescent current synchronous buck gate-driver IC which is co-packed with control and synchronous MOSFETs. The package is optimized for PCB layout, heat transfer, driver/MOSFET control timing, and minimal switch node ringing when layout guidelines are followed. The paired gate driver and MOSFET combination enables higher efficiency at lower output voltages required by cutting edge CPU, GPU, and DDR memory designs.

## Automotive 60A Optimos<sup>™</sup> Powerstage TLF12505

The internal MOSFET sensing achieves superior current sense accuracy vs. best-in-class controller-based Inductor DCR sense methods.

Protection includes IC temperature reporting and over temperature protection feature (OTP with thermal shutdown), cycle-by-cycle over current protection (OCP), negative over current protection, control MOSFET short detection (HSS - High side short detection), VDRV and bootstrap under-voltage protection. The TLF12505 also features "refreshing" of bootstrap capacitor to prevent the bootstrap capacitor from over-discharging.

Operation of up to 2 MHz switching frequency enables high performance transient response, allowing miniaturization of output inductors, as well as input and output capacitors while maintaining industry leading efficiency.

ineon

Table of Contents

## **Table of Contents**

| Feat | tures                                                     | 1  |

|------|-----------------------------------------------------------|----|

| Pote | ential applications                                       | 1  |

| Desc | cription                                                  | 1  |

| 1    | Pinout                                                    |    |

| 1.1  | Pinout, Numbering and Name of Pins (transparent top view) | 5  |

| 2    | Block Diagram                                             | 7  |

| 3    | Electrical Specification                                  |    |

| 3.1  | Absolute Maximum Ratings                                  | 8  |

| 3.2  | Thermal Characteristics                                   | 9  |

| 3.3  | Recommended Operating Conditions                          | 9  |

| 3.4  | Electrical Characteristics                                | 10 |

| 4    | Typical Operating Characteristics                         | 14 |

| 5    | Theory of Operation                                       | 16 |

| 5.1  | Description                                               | 16 |

| 5.2  | Sleep Modes                                               | 17 |

| 5.3  | Current Sensing and Reporting                             | 17 |

| 5.4  | VDRV Under-voltage Lock-out (UVLO)                        |    |

| 5.5  | Temperature Reporting and Over-temperature protection     |    |

| 5.6  | Over-current Protection and Flag                          |    |

| 5.7  | Bootstrap Capacitor Under-Voltage                         |    |

| 5.8  | Negative over current protection                          |    |

| 6    | Design Procedure                                          |    |

| 6.1  | Input Capacitors C <sub>VIN</sub>                         |    |

| 6.2  | Bootstrap Capacitor Cboot and Resistor Rboot              |    |

| 6.3  | Vcc and Vdrv Decoupling Capacitors                        |    |

| 6.4  | Mounting of Heat Sinks                                    |    |

| 7    | Application Diagram                                       |    |

| 7.1  | Typical Application                                       |    |

| 7.2  | Typical Single-phase Application Diagram                  |    |

| 8    | Mechanical Drawing                                        |    |

| 8.1  | Mechanical Dimensions (Top View and Side View)            |    |

| 8.2  | Mechanical Dimensions of Package in mm                    |    |

| Disc | laimer                                                    | 24 |

infineon

Pinout

## 1 Pinout

### Table 1Product Identification

| Part Number | Temp Range   | Package          | Marking  | Orderable Part Number |

|-------------|--------------|------------------|----------|-----------------------|

| TLF12505    | -40 to 125°C | PQFN 5 mm x 6 mm | TLF12505 | TLF12505AUMA1         |

### Figure 1 Picture of the Product

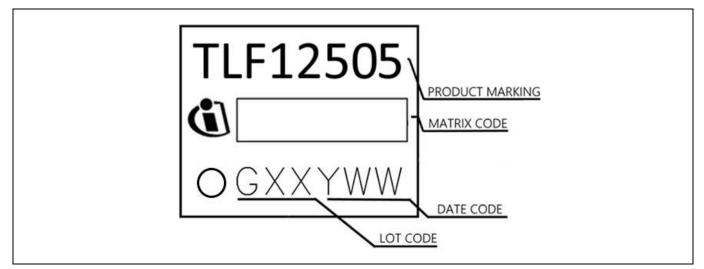

Figure 2 Pinout, Numbering and Name of Pins (transparent top view)

Pinout

## **1.1** Pinout, Numbering and Name of Pins (transparent top view)

| Table 2          | I/O Signats     |          |                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|------------------|-----------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin No.          | Name            | Pin Type | Buffer Type                                                                                                                                                               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 1                | IMONREF         | I/O      | Analog                                                                                                                                                                    | This pin provides a system reference for the IMON information. This pin can be tied to a fixed voltage between 1.1 V and 1.9 V such as bias rails of a PWM controller.                                                                                                                                                                                                                                                                                            |  |  |  |

| 11-18,<br>23, 38 | SW              | 0        | Analog                                                                                                                                                                    | Switching node of synchronous buck converter.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 30               | PHASE           | Ι        | Analog                                                                                                                                                                    | Switching node. For Bootstrap capacitor connection only.                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 31               | BOOT            | 1        | Analog                                                                                                                                                                    | Bootstrap capacitor connection. Connect an X7R ceramic capacitor with value between 0.22 $\mu$ F to 0.56 $\mu$ F from BOOT to PHASE pin. Recommended value is 0.47 $\mu$ F. The bootstrap capacitor provides the charge to turn on the control MOSFET. For VIN between 13.2V and 19V, a 2- $\Omega$ bootstrap resistor in series with the capacitor is required to help reduce SW ringing and EMI. For VIN > 19V, a 3.3- $\Omega$ bootstrap resistor is required. |  |  |  |

| 32               | PWM             | I/O      | +5 V logic                                                                                                                                                                | 5 V logic level PWM input. PWM input: "High" turns control<br>MOSFET on; "Tri-state" turns both MOSFETs off; "Low"<br>turns the synchronous MOSFET on.                                                                                                                                                                                                                                                                                                            |  |  |  |

| 33               | EN              | I        | +3.3 V logic                                                                                                                                                              | Pulling EN high enables the driver; pulling EN low disables<br>the driver and enters ultra-low quiescent current mode.<br>Floating this pin is not recommended, however a pull-<br>down is embedded to keep the driver off if the pin is<br>floating. Pin is VCC tolerant.                                                                                                                                                                                        |  |  |  |

| 34               | TMON /<br>FAULT | 0        | Analog                                                                                                                                                                    | The voltage at this pin is defined by the equation.<br>8mV * (Celsius Temperature) + 0.6 V. This pin will be<br>pulled up to 3.3 V under severe over-temperature, over-<br>current, HSS or bootstrap under-voltage condition.                                                                                                                                                                                                                                     |  |  |  |

|                  |                 | Analog   | Sensed current output signal referenced to the IMONRE<br>pin through external resistor. V (IMON – IMONREF) voltag<br>across that resistor represents current information. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

### Table 2 I/O Signals

| Table | 3 | Power | Supp | lv |

|-------|---|-------|------|----|

|       | • |       |      | `' |

| Pin No. | Name | Pin Type | Buffer Type | Function                                                                                                               |

|---------|------|----------|-------------|------------------------------------------------------------------------------------------------------------------------|

| 3       | VCC  | POWER    | -           | Bias voltage for control logic. Connect a 1 µF cap between VCC and AGND. VCC should be connected to +5 V power supply. |

| 4       | VDRV | POWER    | -           | The supply of gate driver. Connect a 1 μF cap between VDRV and PGND. VDRV should be connected to +5 V power supply.    |

| 24-29   | VIN  | POWER    | -           | 4.25 V to 20 V high current input voltage connection.                                                                  |

infineon

Pinout

| Table 4 | <b>Ground Pins</b> |

|---------|--------------------|

|         |                    |

| Pin No.  | Name | Pin Type | Buffer Type | Function                                                             |

|----------|------|----------|-------------|----------------------------------------------------------------------|

| 2        | AGND | GND      | -           | Signal ground. All interface signals are referenced to this pin.     |

| 5-10, 37 | PGND | GND      | -           | Power ground. It is also the power ground of the synchronous MOSFET. |

| 19-22    | PGND | GND      | -           | Power ground. It is also the power ground of the synchronous MOSFET. |

| 35       | PGND | GND      | -           | Power ground. It is also the power ground of the synchronous MOSFET. |

**Block Diagram**

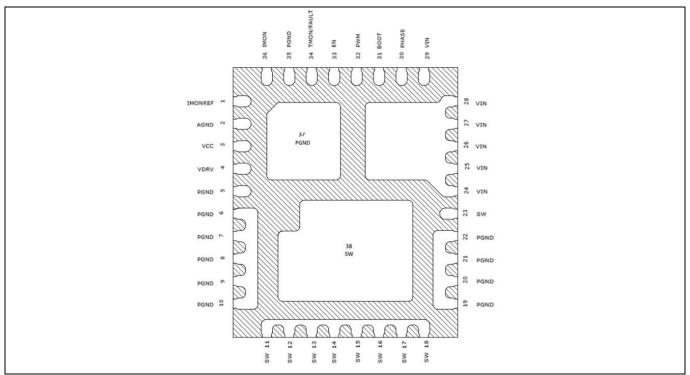

## 2 Block Diagram

Figure 3 Simplified Block Diagram

**Electrical Specification**

## 3 Electrical Specification

### 3.1 Absolute Maximum Ratings

*Note: TA* = 25 °*C*

Stresses above those listed in Table 5 "Absolute Maximum Ratings" may cause permanent damage to the device. These are absolute stress ratings only and operation of the device is not implied or recommended at these or any other conditions more than those given in the operational sections of this specification. Exposure over values of the recommended ratings for extended periods may adversely affect the operation and reliability of the device.

| Devenue de vi                    | Complete L                   | ١                      |                       | Note / Test  |      |                     |  |

|----------------------------------|------------------------------|------------------------|-----------------------|--------------|------|---------------------|--|

| Parameter                        | Symbol                       | Min. Typ.              |                       | Max.         | Unit | Condition           |  |

| Frequency of the PWM input       | f <sub>sw</sub>              | 0.1                    | -                     | 2            | MHz  |                     |  |

| Maximum average load current     | I <sub>OUT</sub>             | -                      | -                     | 60           | А    |                     |  |

| Input Voltage                    | V <sub>IN</sub>              | -0.30                  | -                     | 30           | ٧    | Pin VIN             |  |

| Logic supply voltage             | V <sub>cc</sub>              | -0.3                   | -                     | 6.5          | V    | Pin VCC             |  |

| High and low-side driver voltage | V <sub>DRV</sub>             | -0.3                   | -                     | 6.5          | V    | Pin VDRV            |  |

|                                  | V <sub>sw</sub> (DC)         | -1                     | -                     | 30           | V    | Die CW              |  |

| Switch node voltage              | V <sub>sw</sub> (AC)         | -8 for 10 ns           | -                     | 32 for 2 ns  | V    | Pin SW              |  |

|                                  | V <sub>PHASE</sub> (DC)      | -1                     | - 30<br>- 32 for 2 ns |              |      | Pin PHASE           |  |

| PHASE voltage                    | V <sub>PHASE</sub> (AC)      | -8 for 10 ns           |                       |              | V    |                     |  |

|                                  | V <sub>VIN-PHASE</sub> (DC)  | -1                     | -                     | 30           | V    |                     |  |

| VIN-PHASE voltage                | V <sub>VIN-PHASE</sub> (AC)  | -8 for 10 ns           | -                     | 32 for 2 ns  | V    |                     |  |

|                                  | V <sub>BOOT</sub> (DC)       | -0.3                   |                       | 29           |      | Pin BOOT            |  |

| BOOT voltage                     | V <sub>BOOT</sub> (AC)       | Below -0.3 for<br>5 ns | -                     | 34 for 1 ns  | V    |                     |  |

|                                  | V <sub>BOOT-PHASE</sub> (DC) | -0.3                   |                       | 6.5          | V    |                     |  |

| BOOT-PHASE voltage               | V <sub>BOOT-PHASE</sub> (AC) | Below -0.3 for<br>5 ns | ]-                    | 7.5 for 3 ns | v    |                     |  |

| EN voltage                       | V <sub>EN</sub>              | -0.3                   | -                     | 6.5          | V    | Pin EN              |  |

| PWM voltage                      | V <sub>PWM</sub>             | -0.3                   | -                     | 6.5          | V    | Pin PWM             |  |

| TMON voltage VTMON               |                              | -0.3                   | -                     | 3.6          | v    | Pin TMON /<br>FAULT |  |

| IMON voltage                     | VIMON                        | -0.3                   | _                     | 3.6          | ۷    | Pin IMON            |  |

| IMONREF voltage                  | Vimonref                     | -0.3                   | -                     | 3.6          | V    | Pin IMONRE          |  |

| Junction temperature             | T <sub>Jmax</sub>            | -40                    | -                     | 150          | °C   |                     |  |

| Storage temperature              | T <sub>STG</sub>             | -55                    | _                     | 150          | °C   |                     |  |

#### Table 5Absolute Maximum Ratings

neon

#### **Electrical Specification**

*Note:* All rated voltages are relative to voltages on the AGND and PGND pins unless otherwise specified.

#### Table 6ESD Resistivity

| Parameter                                      | Symbol |      | Value | s    | Unit | Note / Test Condition                                          |  |

|------------------------------------------------|--------|------|-------|------|------|----------------------------------------------------------------|--|

|                                                |        | Min. | Тур.  | Max. |      |                                                                |  |

| Electrostatic Discharge<br>Voltage at all pins | VESD   | -1.5 |       | 1.5  |      | Human Body Model<br>(100pF via 1.5kΩ) <sup><u>Note 2</u></sup> |  |

| Electrostatic Discharge<br>Voltage at all pins | VESD   |      | 500   |      | V    | CDM                                                            |  |

### 3.2 Thermal Characteristics

#### Table 7Thermal Characteristics

| Parameter                                     | eter Symbol Values   |      | s    | Unit | Note / Test Condition |  |

|-----------------------------------------------|----------------------|------|------|------|-----------------------|--|

|                                               |                      | Min. | Тур. | Max. |                       |  |

| Thermal resistance-Junction to PCB (pin 24)   | $\theta_{JC_{PCB}}$  | -    | 1.5  | -    | K/W                   |  |

| Thermal resistance-Junction to top of package | $\theta_{JC_{Top}}$  | -    | 17.8 | -    |                       |  |

| Thermal resistance to ambient                 | $\theta_{JA}^{Note}$ | -    | 28.4 | -    |                       |  |

Note: Thermal Resistance ( $\theta_{JA}$ ) is measured with the component mounted on a high effective thermal conductivity test board in free air.

### **3.3** Recommended Operating Conditions

#### Table 8 Recommended Operating Conditions

| Parameter                       | Symbol               |      | Value | S    | Unit | Note / Test Condition |  |

|---------------------------------|----------------------|------|-------|------|------|-----------------------|--|

|                                 |                      | Min. | Тур.  | Max. |      |                       |  |

| Input voltage                   | V <sub>IN</sub>      | 4.25 | -     | 20   | V    | Note 3                |  |

| MOSFET driver voltage           | V <sub>DRV</sub>     | 4.9  | -     | 5.5  |      | -                     |  |

| Logic supply voltage            | V <sub>cc</sub>      | 4.9  | -     | 5.5  |      | -                     |  |

| Frequency of the PWM            | f <sub>sw</sub>      | 300  | -     | 2000 | kHz  | -                     |  |

| EN voltage                      | VEN                  | -    | -     | 5.5  | V    | Pin EN                |  |

| PWM voltage                     | $V_{PWM}$            | -    | _     | 5.5  | V    | Pin PWM               |  |

| Current Sense reference voltage | V <sub>IMON_CM</sub> | 1.1  | -     | 1.9  | V    | Pins IMON, IMONREF    |  |

| Junction temperature            | T <sub>jOP</sub>     | -40  | -     | +125 | °C   |                       |  |

**Electrical Specification**

### 3.4 Electrical Characteristics

Note:  $V_{DRV} = V_{CC} = 5 V$ ,  $T_{J} = 25 °C$ ,  $V_{IMONREF} = 1.2V$

#### Table 9Voltage Supply, Biasing Current

| Parameter                                    | Symbol                | Values |      |      | Unit | Note / Test Condition        |

|----------------------------------------------|-----------------------|--------|------|------|------|------------------------------|

|                                              |                       | Min.   | Тур. | Max. |      |                              |

| UVLO VDRV rising                             | $V_{\text{UVLO}_{R}}$ | 3.9    | 4.05 | 4.2  | V    |                              |

| UVLO VDRV falling                            | $V_{\text{UVLO}_F}$   | 3.7    | 3.85 | 4.0  |      |                              |

| Bootstrap Under voltage<br>rising threshold  | V <sub>UVBOOT_R</sub> | 3.7    | 3.85 | 4.0  |      |                              |

| Bootstrap Under voltage<br>falling threshold | V <sub>UVBOOT_F</sub> | 3.65   | 3.82 | 4.0  |      |                              |

| Driver current                               | I <sub>VDRV</sub>     | -      | 20   | -    | mA   | EN = H, fSW = 600 kHz, D=15% |

|                                              |                       | -      | 220  | -    | μΑ   | EN = H, PWM floating         |

|                                              |                       | -      | 2.5  | -    | μΑ   | EN = L                       |

| Supply Current                               | I <sub>Vcc</sub>      | -      | 6    | -    | mA   | EN = H, fSW = 600 kHz, D=15% |

|                                              |                       | -      | 1.5  | -    | mA   | EN = H, PWM floating         |

|                                              |                       | -      | 30   | -    | μΑ   | EN = L                       |

| VIN Current                                  | I <sub>VIN</sub>      | -      | -    | 860  | μA   | No switching                 |

### Table 10Current Sense

| Param | Parameter                                                                                  |                      |      | Value | es   | Unit | Note / Test Condition                                                                                    |

|-------|--------------------------------------------------------------------------------------------|----------------------|------|-------|------|------|----------------------------------------------------------------------------------------------------------|

|       |                                                                                            |                      | Min. | Тур.  | Max. |      |                                                                                                          |

| IMON  | IMON Voltage range                                                                         | VIMON                | 0.8  | -     | 2.35 | V    | DC + AC components                                                                                       |

|       | IMON/IMONREF<br>reference voltage<br>range                                                 | V <sub>IMON_CM</sub> | 1.1  | -     | 1.9  | V    | Reference Voltage connected<br>externally for the current sense<br>signal                                |

|       | Current sense gain                                                                         | A <sub>cs</sub>      | -    | 5     | _    | μΑ/Α |                                                                                                          |

|       | IMON Gain resistor<br>range                                                                | R <sub>IMON</sub>    | _    | 1     | -    | kΩ   | Resistor to be connected<br>between IMON and IMONREF.<br>For 5mV/A, recommended 1kΩ<br>R <sub>IMON</sub> |

|       | Leakage Current                                                                            | $I_{Leak}$           | -2   | 0     | 2    | μΑ   | I <sub>OUT</sub> = 0A, V <sub>IMON</sub> =1.2V<br>PWM in tri-state                                       |

|       | Zero current offset                                                                        | l <sub>offset</sub>  | -3   | 0     | 3    | μΑ   | Corresponds to 3 mV at 5 mV/A.<br>( $R_{IMON} = 1 k\Omega$ ), device in<br>regulation                    |

|       | Accuracy at                                                                                |                      | -3.0 | -     | 3.0  | %    | for 25A < I <sub>OUT</sub> < I <sub>OCP_TH</sub> Note 1, Note 3                                          |

|       | $T_{J} = -5 \text{ to } 125^{\circ}\text{C}$<br>$V_{CC} = V_{DRV} = 5 \text{ V} \pm 10 \%$ |                      | -0.5 | -     | 0.5  | A    | for -25A < I <sub>OUT</sub> < 25A Note 1                                                                 |

**Electrical Specification**

### Table 11 Temperature Sense and Fault Communication

| Parameter       |                                            | Symbol                 | Values |      |      | Unit  | Note / Test Condition                                                                                                  |

|-----------------|--------------------------------------------|------------------------|--------|------|------|-------|------------------------------------------------------------------------------------------------------------------------|

|                 |                                            |                        | Min.   | Тур. | Max. |       |                                                                                                                        |

| TMON /<br>FAULT | Temperature<br>Sense Slope                 | Atmpgain               | 7.84   | 8.0  | 8.16 | mV/°C | 25°C ≤ T <sub>J</sub> ≤ 125°C, $\frac{Note 1}{2}$                                                                      |

|                 | Temperature<br>Sense Offset<br>Voltage     | V <sub>TMPOFFSET</sub> | 784    | 800  | 816  | mV    | T」= 25°C, 0.6 V + 8 mV/°C * T」                                                                                         |

|                 | TMON /<br>FAULT<br>Source<br>Current       | I <sub>tmonsrc</sub>   | 2.5    | 3    | 3.5  | mA    | TMON / FAULT pulled low                                                                                                |

|                 | TMON /<br>FAULT Sink<br>Current            | I <sub>tmonsnk</sub>   | 26     | 32   | 40   | μA    | TMON / FAULT pulled high                                                                                               |

|                 | Fault mode<br>Active High                  | Vtflthigh              | 2.6    | 3.3  | 3.6  | V     | I <sub>TMON/FAULT</sub> = 5 mA and under Over-<br>Temperature, Over-Current,<br>bootstrap undervoltage or HSS<br>Fault |

|                 | TMON /<br>FAULT<br>Low <sup>Note 1</sup>   | VTFLTLOW               | -      | _    | 0.35 | V     | No Fault, V <sub>DRV</sub> < V <sub>UVLO1_R</sub>                                                                      |

|                 | TMON /<br>FAULT pull<br>down<br>resistance | Rpulldn_tmon           | _      | 150  | _    | kΩ    | No Fault, V <sub>DRV</sub> < V <sub>UVLO1_R</sub>                                                                      |

### Table 12 Other Logic Functions, Inputs/Outputs and Thresholds

| Parameter |                                      | Symbol                     |      | Value | S    | Unit | Note / Test Condition                                               |

|-----------|--------------------------------------|----------------------------|------|-------|------|------|---------------------------------------------------------------------|

|           |                                      |                            | Min. | Тур.  | Max. |      |                                                                     |

| EN        | Enable<br>Power-on<br>Delay          | $t_{\text{EN\_ondelay}}$   | -    | 17    | 35   | μs   | PWM=0. Measured from EN rising edge to V <sub>sw</sub> > 1 V.       |

|           | Enable<br>Power-off<br>Delay         | $t_{\text{EN}_{offdelay}}$ | -    | -     | 1    | ns   | PWM=0. Measured from EN falling edge to V <sub>sw</sub> < 0.9* VIN. |

|           | Internal Pull-<br>down<br>Resistance | R <sub>pulldn_en</sub>     | -    | 280   | _    | kΩ   | When EN is floating                                                 |

|           | Input High<br>Voltage                | V <sub>EN_H</sub>          | 2.0  | -     | -    | V    |                                                                     |

|           | Input Low<br>Voltage                 | V <sub>EN_L</sub>          | -    | -     | 0.8  | V    |                                                                     |

**Electrical Specification**

| PWM                        | PWM Input<br>High<br>Threshold                     | V <sub>IH</sub>           | 2.4  | _     | _   | V  | PWM Low or Tri-state to High                           |

|----------------------------|----------------------------------------------------|---------------------------|------|-------|-----|----|--------------------------------------------------------|

|                            | PWM Input<br>Low<br>Threshold                      | VIL                       | -    | _     | 0.8 | V  | PWM High or Tri-state to Low                           |

|                            | PWM<br>Hysteresis                                  | I <sub>PWM_HYS</sub>      | -    | 40    | _   | mV | Active to Tri-state or Tri-state to<br>Active          |

|                            | PWM Input<br>Tri-State<br>Floating<br>Voltage      | V <sub>PWM_TRI</sub>      |      | 1.6   |     | V  | PWM Input Floating                                     |

|                            | Tri-state<br>Window                                | V <sub>PWM_S</sub>        | 1.2  | _     | 2.0 | V  |                                                        |

|                            | PWM Input<br>Equivalent<br>Pull-up<br>Resistance   | R <sub>PWM_PU</sub>       | _    | 20    | -   | kΩ | V <sub>PWM</sub> = 0 V                                 |

|                            | PWM Input<br>Equivalent<br>Pull-down<br>Resistance | R <sub>PWM_PD</sub>       | _    | 50    | _   | kΩ | V <sub>PWM</sub> = 3.3 V                               |

| Bootstrap<br>Diode         | Forward<br>Voltage                                 | V <sub>FWD</sub>          | -    | 620   | -   | mV | I(BOOT) = 5 mA                                         |

| SW<br>Bleeding<br>Resistor | SW Floating<br>Voltage                             | V <sub>SW_FLOAT</sub>     | -    | -     | 200 | mV | V <sub>PWM</sub> = 1.6 V or Tri-state, VCC = VDRV = 5V |

|                            | SW Pull<br>Down<br>Resistance                      | R <sub>SW_PULL_DOWN</sub> | 0.85 | 1.125 | 1.5 | kΩ |                                                        |

#### Table 13 Protection

| Paramete     | er                                        |                      | Value | es   |      | Unit | Note / Test Condition                                                |

|--------------|-------------------------------------------|----------------------|-------|------|------|------|----------------------------------------------------------------------|

|              |                                           | Symbol               | Min.  | Тур. | Max. |      |                                                                      |

| OTP          | Over Temp<br>Rising<br>Threshold          | T <sub>RISE</sub>    | -     | 155  | -    | °C   | TMON/FAULT pulled up high Note 1                                     |

|              | Over Temp<br>Falling<br>Threshold         | T <sub>FALL</sub>    | -     | 143  | -    | °C   | TMON/FAULT released Note 1                                           |

| HSS<br>FAULT | High-side<br>MOSFET<br>Short<br>Threshold | V <sub>HSS_TH</sub>  | _     | 560  | -    | mV   | V <sub>SW</sub> – V <sub>PGND</sub>                                  |

|              | TMON/FAULT<br>Delay                       | T <sub>HSS_DEL</sub> | -     | 150  | -    | ns   | After V <sub>HSS_TH</sub> is detected, and TMON/FAULT is pulled high |

### **Electrical Specification**

| OCP  | Over-Current<br>Threshold | I <sub>OCP_TH</sub>  | 80  | 90  | 100 | А     |                                                     |

|------|---------------------------|----------------------|-----|-----|-----|-------|-----------------------------------------------------|

|      | Over-Current<br>Delay     | T <sub>OCP_DEL</sub> | 10  | -   | -   | Cycle | PWM High-Low Cycles to<br>TMON/FAULT is pulled high |

| OCPn | Negative OCP<br>Threshold | T <sub>OCPN_TH</sub> | -55 | -50 | -45 | A     |                                                     |

### Table 14Timing Characteristics

| Parameter                                               | Symbol                    | Values |      |      | Unit | Note / Test Condition                                                                                                                                                                                                 |

|---------------------------------------------------------|---------------------------|--------|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                         |                           | Min.   | Тур. | Max. |      |                                                                                                                                                                                                                       |

| PWM High Propagation<br>Delay                           | t <sub>pwm_hi_delay</sub> | -      | 48   | -    | ns   | Measured from PWM rising edge to V <sub>sw</sub> starts to rise                                                                                                                                                       |

| PWM Low Propagation<br>Delay                            | t <sub>pwm_lo_delay</sub> | -      | 45   | -    | ns   | Measured from PWM falling edge to $V_{\mbox{\scriptsize SW}}$ starts to fall                                                                                                                                          |

| Tri-State to High<br>Propagation Delay                  | t <sub>tri_hi_delay</sub> | -      | 53   | -    | ns   | PWM Tri-state to High transition to $V_{SW} > 1 V$                                                                                                                                                                    |

| Tri-State Hold Off Time                                 |                           |        | 56   |      |      | PWM Low to Tri-state transition to SW starts to fall Note 1                                                                                                                                                           |

|                                                         | t <sub>TriHold</sub>      | _      | 75   | _    | ns   | PWM High to Tri-state transition to SW starts to fall Note 1                                                                                                                                                          |

| Minimum Recognized<br>PWM Pulse Width <sup>Note 1</sup> | t <sub>MinPWM</sub>       | -      | 17   | -    | ns   | PWM pulses shorter than t <sub>MinPWM</sub> will be ignored by driver. Note 1                                                                                                                                         |

| Minimum output pulse<br>width                           | t <sub>onswmin</sub>      | -      | 18   | _    | ns   | $\begin{array}{l} \mbox{Positive load current. PWM pulses} \\ \mbox{shorter than } t_{\mbox{OnSWmin}} \mbox{ will be extended} \\ \mbox{to } t_{\mbox{onSWmin}}. \begin{tabular}{l} \hline \end{tabular} \end{array}$ |

Note:

1. Guaranteed by design but not tested in production.

2. ESD Susceptibility HBM according to EIA / JESD 22-A 114

3. Device is functional down to VIN = 3V. IMON signal accuracy guaranteed down to minimum VIN = 6V.

**Electrical Specification**

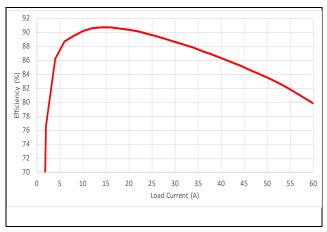

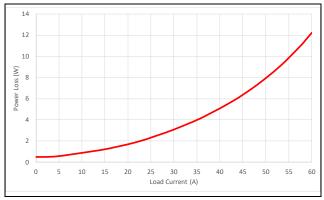

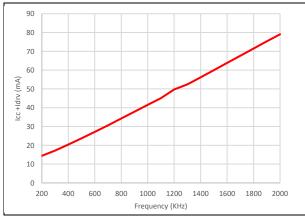

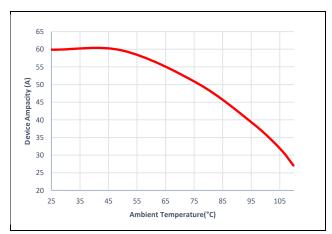

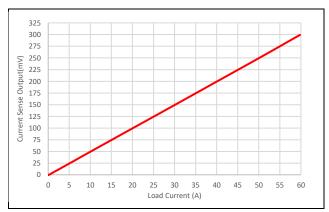

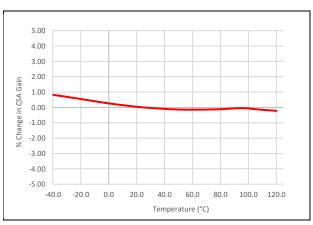

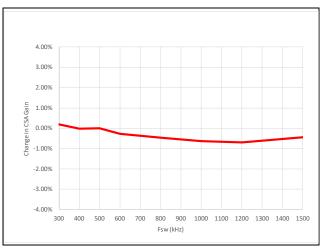

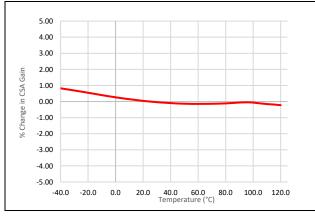

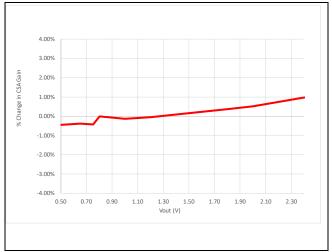

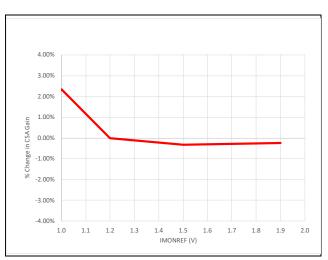

## 4 Typical Operating Characteristics

Single Phase Circuit of Figure 16,  $V_{IN} = 12 \text{ V}$ ,  $V_{OUT} = 0.8 \text{ V}$ ,  $f_{SW} = 500 \text{ kHz}$ , L = 150 nH, VCC = VDRV = 5 V,  $T_{AMBIENT} = 25 \text{ °C}$ , no heat sink, no air flow, 8-layer PCB board of 3.7" (L) x 2.6" (W), no PWM controller loss, no inductor loss, unless specified otherwise.

Figure 4 Power Stage Efficiency

Figure 5 Power Stage Loss

Figure 6 Vcc + Vdrv Current vs Frequency

Figure 7 Thermal Derating, Tcase<=125°C

Figure 8 Current Sense Output

Figure 9 Current Sense Gain vs Temperature

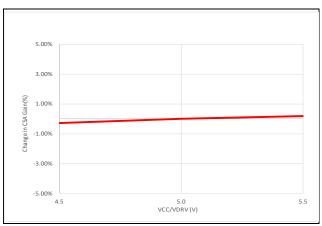

Single Phase Circuit of Figure 16,  $V_{IN} = 12 V$ ,  $V_{OUT} = 0.8 V$ ,  $f_{SW} = 500 \text{ kHz}$ , L = 150 nH, VCC = VDRV = 5 V,  $T_{AMBIENT} = 25 ^{\circ}$ C, no heat sink, no air flow, 8-layer PCB board of 3.7" (L) x 2.6" (W), no PWM controller loss, no inductor loss, unless specified otherwise.

Figure 11 Current sense gain variation vs Temperature

Figure 12 Current sense gain variation vs Vout

fineon

Figure 13 Current Sense gain variation vs IMONREF

Figure 14 Current sense gain variation vs VCC/VDRV

## 5 Theory of Operation

### 5.1 Description

The TLF12505 contains an improved high speed MOSFET driver optimized to drive a pair of co-packaged highside and low-side OptiMOS MOSFETs at frequency up to 2 MHz's. DC-DC controllers using traditional current sense methods like DCR sensing and Rdson sensing typically have limitations. DCR current sensing is sensitive to temperature changes of the inductor and needs temperature compensation either implemented externally using a thermo-couple or inside the power stage. Rdson current sensing, on the other hand, is not dependent on the inductor but there is a temperature co-efficient associated with the MOSFET Rdson. Besides, it is difficult to implement Rdson current sensing for high-side MOSFET which is therefore replaced by emulated current while the low-side current is sensed across the MOSFET. With the advanced current mirror sensing in TLF12505, all these limitations are eliminated while achieving superior accuracy. Current on both high-side as well as low-side MOSFET is mirrored on a sense MOSFET which is a part of the main MOSFET device, and hence comes with an inherent temperature compensation without the need for an additional circuitry. Real current-sensing on both MOSFET ensures that the system is always monitoring the real output current and can immediately react to any critical events like load step or over-current fault.

The TLF12505 reports accurate temperature with the gain of 8 mV / °C, which helps the system to actively monitor the temperature in real time. Temperature outputs from multiple power stages can be connected to report the highest temperature to Infineon's digital PWM controller.

The TLF12505 PWM input is compatible with industry standard 3.3V PWM input with tri-state and is tolerant for signals up to 5V inputs.

The TLF12505 can enable Body-Braking mode by responding to PWM tri-state signals sent from the controller, quickly disabling both MOSFETs in the power stage to enhance transient performance or provide a high impedance output.

The TLF12505 supports diode emulation mode through the PWM tri-state signal. Controlled by Infineon's digital PWM controller, the PWM tri-state signal will force the low-side FET to be off when the inductor current is about to go negative. The light-load efficiency then can be increased by preventing conduction loss caused by negative inductor current.

ineor

#### Theory of Operation

The TLF12505 also supports deep-sleep power saving mode. When in deep-sleep mode, the driver will disable most of the function circuitry to greatly reduce power consumption.

The TLF12505 features a full-range of protection, including VCC/VDRV Under-Voltage-Lockout (UVLO), thermal shutdown against an internal over-temperature condition, phase fault detection of a shorted high-side MOSFET, and cycle-by-cycle over-current protection due to an overload condition or saturated output inductor.

The TLF12505 also features internal protection circuitry to automatically replenish the voltage across the bootstrap capacitor. It avoids the gradual depletion of capacitor energy when the power stage sits in tri-state for a long period of time.

### 5.2 Sleep Modes

When EN is pulled low, the power stage enters deep-sleep mode. The gate driver circuitry will be turned off immediately and most of the logic circuitry will be shut down to reduce the bias current to less than 32  $\mu$ A. The IMON output will be shorted to IMONREF in deep sleep mode.

When EN toggles from low to high, the power stage will be active and able to accept PWM signals after a delay of 17 μs.

### 5.3 Current Sensing and Reporting

The TLF12505 features a very accurate current mirror architecture on both high-side as well as low-side MOSFET, thus reporting the real time current information. The current information is reported using the IMON pin. The reported current is in the form of current output with the gain of  $5\mu$ A /A from the IMON pin. To convert this into voltage, a  $1k\Omega$ , 0.1% resistor is recommended at the IMON pin and placed close to the PWM controller. A differential voltage signal from this resistor is connected to the controller as the reported current information. Note that for accurate current reporting, it is important that the other end of the resistor cannot be left floating. The converted voltage signal at the controller side has an effective gain of 5mV/A i.e., for every 1 A load, the controller will read 5mV from the power stage. The current-output differential signal from the power stage provides excellent noise immunity to the reported current information.

ineor

Theory of Operation

## 5.4 VDRV Under-voltage Lock-out (UVLO)

TLF12505 features a VDRV under-voltage lock-out fault circuitry that monitors the VDRV voltage actively. This is a non-catastrophic fault, and the TMON/FAULT pin is pulled low with a weak pull down if the VDRV voltage is below the UVLO threshold. If the power stage has not started up, the power stage PWM pin is also pulled down to 0V with a weak pull down. This can be monitored by the PWM controller as a signal from the power stage indicating that it is not ready yet for power up. As soon as VDRV voltage is above the UVLO threshold, the PWM pin is at tri-state instead of 0V, this indicating the controller that it is OK to send the PWM signals.

Once the power stage is in normal operation, if then it encounters a VDRV UVLO condition, the power stage stops switching, and both TMON pins and IMON-IMONREF signal are pulled down to 0V. If there are multiple phases connected in the same loop, the TMON pin voltage, being connected to other power stage TMON pins, will continue reporting the highest power stage temperature.

### 5.5 Temperature Reporting and Over-temperature protection

An internal temperature-sense circuit monitors the temperature of the TLF12505. The sensed temperature is reported at the TMON/FAULT pin with a linear voltage slope of 8mV/°C and a 0.6V offset at 0°C, as shown in equation (1).

$$V_{TMON/FAULT}(V) = 0.6V + 0.008V / °C x T_i (°C)$$

.....(1)

The TMON/FAULT pin also serves as a FAULT pin that is pulled to 3.3V in case of any catastrophic faults and is pulled down to 0V in case of any non-catastrophic faults. When there is no fault, it continues reporting temperature as long as the VCC supply is connected to a voltage in the recommended operating range. For a junction temperature below -25°C, the TMON voltage is clamped to 0.4V to avoid false triggering of VDRV undervoltage.

Once the temperature rises above the OTP rising threshold (155 °C), the TMON/FAULT output will be pulled high immediately, the driver will stop switching and stop responding to the PWM signal input from the controller. Both high-side and low-side MOSFET are turned off. The TMON/FAULT will remain high until temperature falls below the falling threshold (143 °C).

## 5.6 Over-current Protection and Flag

This feature protects the power stage from self-destruction from repetitive high current events such as saturated inductors due to poor component selection or by incorrectly optimized control loops. These high current events could eventually lead to a shorted high-side MOSFET failure.

Datasheet

## Automotive 60A Optimos<sup>™</sup> Powerstage TLF12505

With cycle-by-cycle self-preservation, the current is monitored every cycle. If the over-current threshold (default 90 A) has been exceeded, the PWM high pulse will be truncated so that the inductor current is allowed to relax. When TLF12505 detects 10 consecutive PWM cycle over-current events, the TMON/FAULT pin is flagged high to indicate the controller of the fault. Note the PWM pulse "on-time" should be at least 50ns for accurate functioning over-current protection.

### 5.7 Bootstrap Capacitor Under-Voltage

TLF12505 features a bootstrap capacitor under-voltage circuitry that detects a missing bootstrap capacitor before powering up or a damaged bootstrap capacitor during normal operation. Once bootstrap capacitor under-voltage is determined, the TMON/FAULT pin will be pulled high to report a catastrophic fault to the PWM controller.

### 5.8 Negative over current protection

TLF12505 features a negative over-current protection in the device to protect from very high negative current. As soon as the power stage detects the IMON reported (negative) current exceeding the negative over-current threshold (OCPn), the high-side FET is enabled for 200ns before the power stage continues following the PWM input signal. TMON continues reporting the power stage temperature during negative over-current fault event.

neon

Theory of Operation

## 6 Design Procedure

### 6.1 Input Capacitors C<sub>VIN</sub>

A 0402 or 0603, X7R, 1-μF ceramic capacitor and three 10-μF X7R ceramic capacitor are recommended at the VIN pins. Use of capacitors with lower ESR will improve efficiency, especially in single-phase operation. Layout guidelines and examples are available.

### 6.2 Bootstrap Capacitor Cboot and Resistor Rboot

A high temperature 0.22-μF or greater value 0402 X7R capacitor is recommended. It should be mounted on the same side of the PCB as the TLF12505 and as close as possible to the BOOT Pin. Low inductance routing of the PHASE pin connection to the negative terminal of the bootstrap capacitor is strongly recommended.

Bootstrap capacitor connection. Connect an X7R ceramic capacitor with value between 0.22  $\mu$ F to 0.56  $\mu$ F from BOOT to PHASE pin. Recommended value is 0.22 $\mu$ F. The bootstrap capacitor provides the charge to turn on the control MOSFET. For VIN > 13.2 V, a 2- $\Omega$  bootstrap resistor in series with the capacitor is required to help reduce SW ringing and EMI.

### 6.3 Vcc and Vdrv Decoupling Capacitors

A 1- $\mu$ F X7R decoupling capacitor is required between VCC and LGND pins, and a 1- $\Omega$  VCC resistor is recommended. A 1- $\mu$ F X7R decoupling capacitor is required between VDRV and PGND pins and can be directly connected to the 5-V supply. Both capacitors should be mounted on the same side of the PCB as the power stage and as close as possible to the VCC-LGND and VDRV-PGND pins. Low inductance routing between the capacitor and the PMC41520 is strongly recommended. Layout guidelines and examples are available.

### 6.4 Mounting of Heat Sinks

Care should be taken in the mounting of heat sinks so that even pressure is applied on the power stage surface. A thermal interface material should be used between the power stage and the heat sink to solve planarity issues and ensure even thermal conduction.

The VCC, VDRV, VIN and bootstrap capacitors are typically located on the same side of the PCB as the power stage. The height of these capacitors must be considered when using heat sinks.

Application

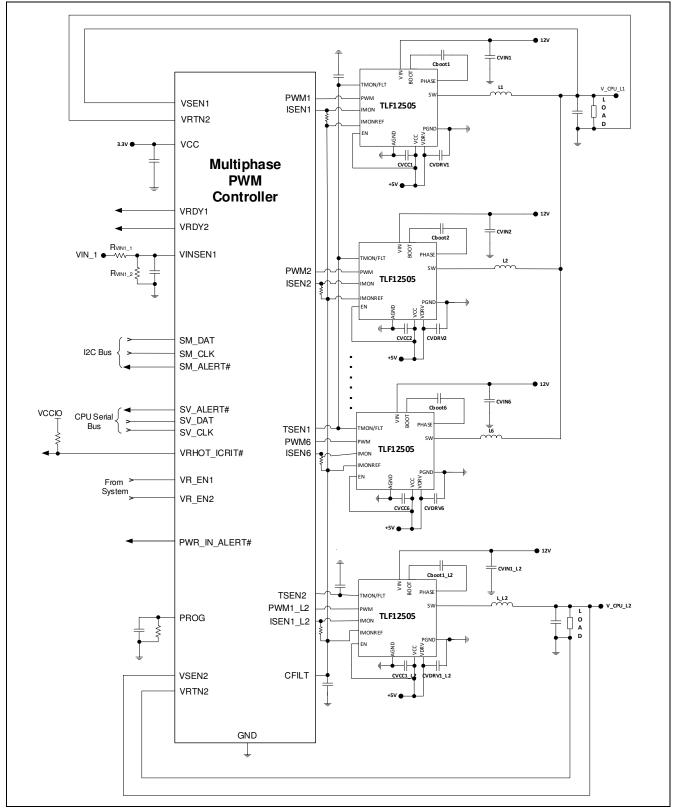

## 7 Application Diagram

## 7.1 Typical Application

Figure 15 6+1 - Phase Voltage Regulator - Typical Application (simplified schematic)

Application

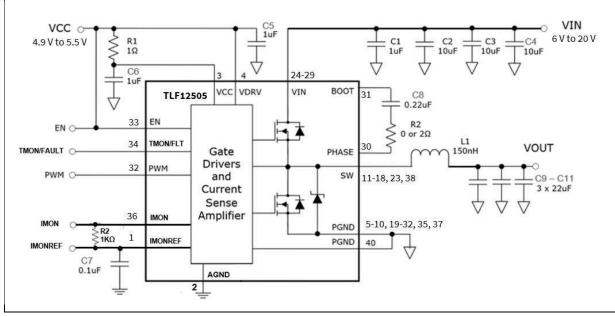

## 7.2 Typical Single-phase Application Diagram

Figure 16 Typical Application Diagram for Single-Phase Voltage Regulator

ineon

Mechanical Drawing

## 8 Mechanical Drawing

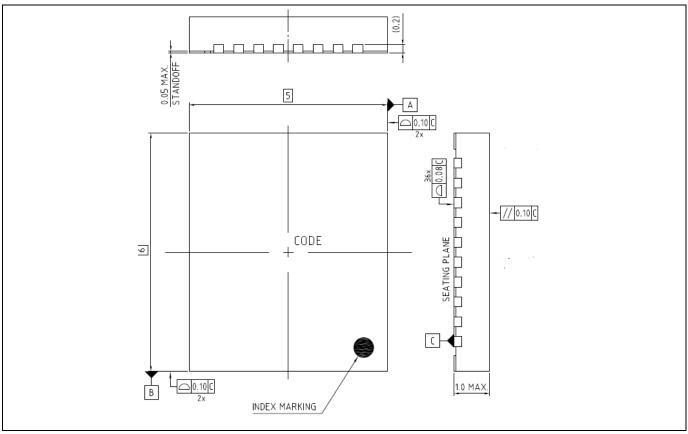

## 8.1 Mechanical Dimensions (Top View and Side View)

Figure 17 Mechanical Dimensions of Package (Top View and Side View) in mm

Mechanical Drawing

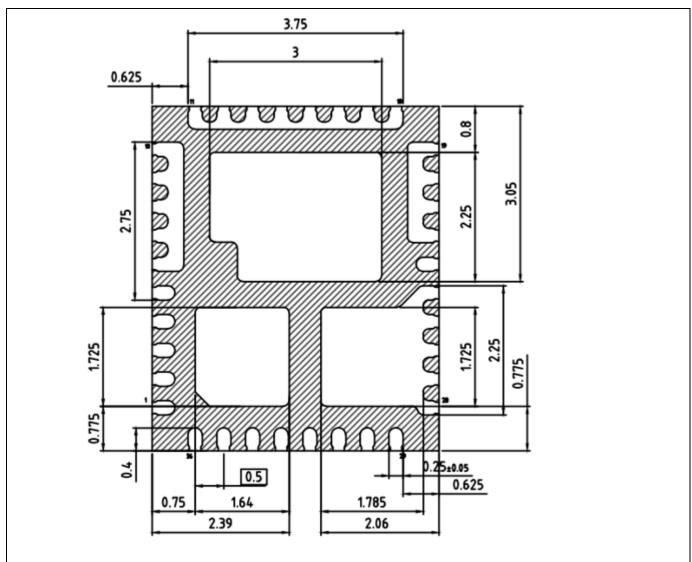

## 8.2 Mechanical Dimensions of Package in mm

Figure 18 Mechanical Dimensions of Package (Bottom View) in mm

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Published by Infineon Technologies AG 81726 München, Germany

Edition 2024-01-3030

© 2024 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document? Email: erratum@infineon.com

Document reference Z8F80149524

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application. For further information on the product, technology delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineor Technologies office.

Except as otherwise explicitly approved by Infineor Technologies in a written document signed by authorized representatives of Infineor Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof car reasonably be expected to result in personal injury.

### **Revision History**

TLF12505

#### Revision: 2024-02-05, Rev. 2.1

| Previous Revision |            |                                               |  |  |  |  |  |

|-------------------|------------|-----------------------------------------------|--|--|--|--|--|

| Revision          | Date       | Subjects (major changes since last revision)  |  |  |  |  |  |

| 2.0               | 2023-12-07 | Release of final version                      |  |  |  |  |  |

| 2.1               | 2024-02-05 | VIN-PHASE and BOOT-GND abs max spec. is added |  |  |  |  |  |

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: erratum@infineon.com

Published by Infineon Technologies AG 81726 München, Germany © 2023 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

The Infineon Technologies component described in this Data Sheet may be used in life-support devices or systems and/or automotive, aviation and aerospace applications or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support, automotive, aviation and aerospace device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Infineon:

TLF12505AUMA1