# TLE 7241E

Dual Channel Constant Current Control Solenoid Driver

## Automotive Power

Never stop thinking

#### **Table of Contents**

## **Table of Contents**

|                                                                                                                                       | Table of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| <b>1</b><br>1.1<br>1.2<br>1.3                                                                                                         | Overview .<br>Features .<br>Applications .<br>General Description .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3<br>4                                                                           |

| 2                                                                                                                                     | Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7                                                                                |

| 3                                                                                                                                     | Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9                                                                                |

| <b>4</b><br>4.1                                                                                                                       | Functional Range         Second S |                                                                                  |

| <b>5</b><br>5.1<br>5.2<br>5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>5.5<br>5.5.1<br>5.5.2<br>5.5.3<br>5.5.4<br>5.6<br>5.6.1<br>5.6.2 | Functional Description and Electrical Characteristics         Supply and Reference         Input/Output         Power Output         Protection and Control         Overvoltage Sensing and Protection         Overcurrent / Short to V <sub>BAT</sub> Sensing         Open Load / Short to Ground Detection         Thermal Shutdown         Current Control         Hysteretic Current Control         Dither Control and Operation         Input Command Out of Range / Dither Clipping         Error Correction Registers / Average Switch Threshold Trimming         SPI Command and Diagnosis Structure         SPI Signal Description         SPI Command Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13<br>14<br>15<br>16<br>17<br>21<br>28<br>30<br>30<br>37<br>43<br>44<br>46<br>46 |

| <b>6</b><br>6.1                                                                                                                       | Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| 7                                                                                                                                     | Package Outlines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 68                                                                               |

| 8                                                                                                                                     | Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 69                                                                               |

## Dual Channel Constant Current Control Solenoid Driver

**TLE 7241E**

### 1 Overview

#### 1.1 Features

- Two Fully Independent Channels

- Integrated N-channel DMOS transistors

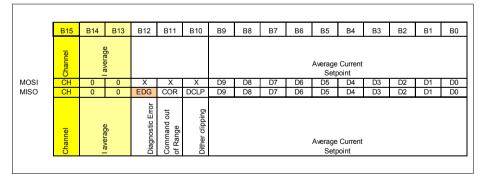

- Programmable Average Current with 10-bit resolution via SPI

- $I_{avq}$  range = 0 to 1000 mA (typical)

- Programmable Superimposed Dither

- Programmable Frequency (41 Hz to 1 kHz typ)

- Programmable Amplitude (12.5 to 390 mVpp typ)

- Programmable Hysteresis (40 to 110 mVpp typ)

- Interface and Control

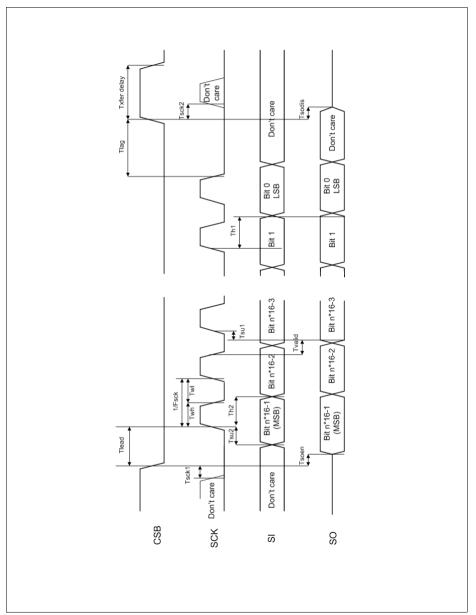

- 16-bit SPI (Serial Peripheral Interface) daisy chainable

- A single "Default" pin to disable both channels and reset the programmable registers of both channels

- 5.0 V and 3.3 V logic compatible I/O

- The contents of all registers can be verified via SPI

- Operation with or without external reference possible

- Protection

- Overcurrent

- Overvoltage

- Overtemperature

- Diagnostics

- Overcurrent / shorted solenoid

- Overtemperature

- Open load

- Short to GND

- Green Product (RoHS compliant)

- AEC Qualified

| Туре      | Ordering Code | Package      |

|-----------|---------------|--------------|

| TLE 7241E | on request    | PG-DSO-20-27 |

#### Overview

#### 1.2 Applications

- · Variable force solenoids (e.g. automatic transmission solenoids)

- Constant current controlled solenoids like

- Idle Speed Control

- Exhaust Gas Recirculation

- Valve control

- Suspension Control

#### 1.3 General Description

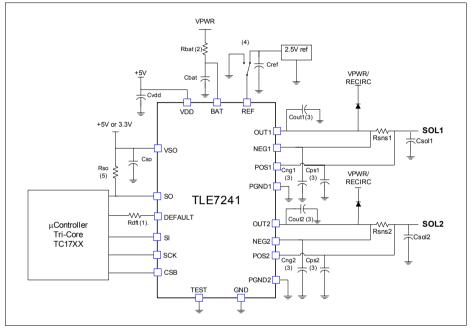

The TLE 7241E is a dual channel constant current control solenoid driver with integrated DMOS power transistors. The average load current can be programmed to a value in the range of 0 mA to 1000 mA (with a 1  $\Omega$  external sense resistor) with 10 bits of resolution. Load current is controlled using a hysteretic control scheme with a programmable hysteresis value. A triangular "dither" waveform can be superimposed on the switching current waveform in order to improve the transfer function of the solenoid. The amplitude and frequency of the dither waveform are programmable by the SPI interface. The device is protected from damage due to overcurrent, overvoltage and overtemperature conditions, and is able to diagnose and report open loads, shorted loads, and loads shorted to ground.

## Note: An external free-wheeling diode must be provided when using the TLE 7241E in constant current control mode, otherwise the IC will be damaged.

For best accuracy, an external 2.5 V reference voltage should be supplied at the REF pin. The TLE 7241E also includes an internal 2.5 V reference voltage, which can be selected by connecting the REF pin to ground. The reference voltage selection (internal or external) can be verified via the SPI interface.

#### TLE 7241E

#### Overview

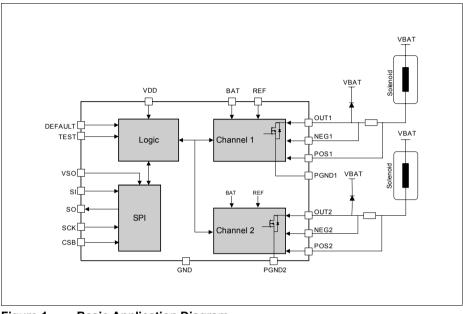

#### Application Block Diagram

Figure 1 Basic Application Diagram

#### Overview

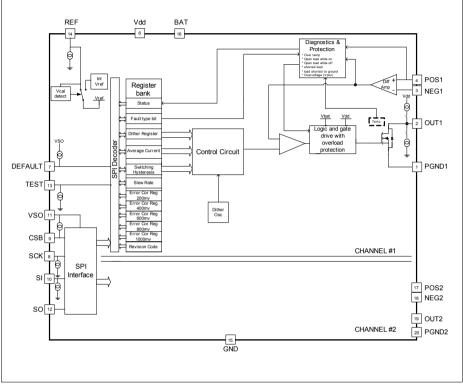

#### Detailed Block Diagram

Figure 2 Detailed Block Diagram

#### **Pin Configuration**

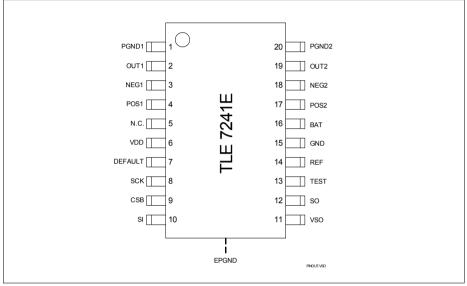

## 2 Pin Configuration

#### Pin Assignment

#### **Pin Definitions and Functions**

| Pin | Pin Name        | Pin Description                                                                                                         |

|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------|

| 1   | PGND1           | Power Ground Channel 1; internally connected to PGND2                                                                   |

| 2   | OUT1            | <b>Output Channel 1</b> ; Drain of Output DMOS; connect to negative terminal of external sense resistor                 |

| 3   | NEG1            | <b>Negative Sense Pin Channel 1</b> ; connect to negative terminal of external sense resistor with dedicated trace      |

| 4   | POS1            | <b>Positive Sense Pin Channel 1</b> ; connect to positive terminal of external sense resistor with dedicated trace      |

| 5   | NC              | Not Connected; not bonded internally                                                                                    |

| 6   | V <sub>DD</sub> | <b>Logic Supply Voltage;</b> connect a ceramic capacitor to GND near the device                                         |

| 7   | DEFAULT         | <b>Control Input;</b> Active high digital input. 3.3V and 5.0V logic compatible. In case of not used, connect to ground |

#### **Pin Configuration**

#### Pin Definitions and Functions (cont'd)

| Pin                       | Pin Name        | Pin Description                                                                                                                        |

|---------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 8                         | SCK             | <b>SPI Clock</b> ; Digital input pin. 3.3V and 5.0V logic compatible                                                                   |

| 9                         | CSB             | <b>Chip Select Bar</b> ; Active low digital input pin. 3.3V and 5.0V logic compatible                                                  |

| 10                        | SI              | Serial Data Input; 3.3V and 5.0V logic compatible                                                                                      |

| 11                        | V <sub>so</sub> | <b>SPI Supply Voltage;</b> connect a ceramic capacitor to GND near the device                                                          |

| 12                        | SO              | Serial Data Output; Supplied by Vso pin                                                                                                |

| 13                        | TEST            | Test Pin; connect to GND                                                                                                               |

| 14                        | REF             | <b>Voltage Reference;</b> connect to external 2.5 V reference, or connect to GND to enable internal reference.                         |

| 15                        | GND             | Ground; signal ground                                                                                                                  |

| 16                        | BAT             | <b>BAT Input;</b> connect to the solenoid supply voltage through a series resistor. Connect a ceramic capacitor to GND near the device |

| 17                        | POS2            | <b>Positive Sense Pin Channel 2</b> ; connect to positive terminal of external sense resistor with dedicated trace                     |

| 18                        | NEG2            | <b>Negative Sense Pin Channel 2</b> ; connect to negative terminal of external sense resistor with dedicated trace                     |

| 19                        | OUT2            | <b>Output Channel 2</b> ; Drain of Output DMOS; connect to negative terminal of external sense resistor                                |

| 20                        | PGND2           | <b>Power Ground Channel 2;</b> internally connected to PGND1                                                                           |

| Expose<br>d Lead<br>Frame | EPGND           | <b>GND;</b> Should be connected to GND, PGND1 and PGND2 and to the ground plane of the ECU                                             |

Note: If a channel is unused, the OUTx, NEGx, and POSx pins should be connected together.

#### **Maximum Ratings**

## 3 Maximum Ratings

#### Absolute Maximum Ratings<sup>1)</sup>

$T_{\rm j}$  = -40 to 150 °C

| Pos.  | Parameter                                               | Symbol                                                 |                                              | Unit                                                                                                                                                                                   | Notes                                         |   |

|-------|---------------------------------------------------------|--------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---|

|       |                                                         |                                                        | Min.                                         | Max.                                                                                                                                                                                   |                                               |   |

| Volta | ges                                                     |                                                        |                                              |                                                                                                                                                                                        |                                               |   |

| M.1   | Supply Voltage                                          | $\begin{array}{c} BAT \\ V_{DD} \\ V_{SO} \end{array}$ | -0.3<br>-0.3<br>-0.3                         | 50<br>6.0<br>6.0                                                                                                                                                                       | Vdc<br>Vdc<br>Vdc                             | - |

| M.2   | Analog Input Voltage                                    | POSx<br>NEGx<br>POSx-NEGx                              | -0.3<br>-0.3<br>-0.3                         | 50<br>50<br>20                                                                                                                                                                         | Vdc<br>Vdc<br>Vdc                             | - |

| M.3   | Output Voltage                                          | OUTx                                                   | -0.3                                         | 50                                                                                                                                                                                     | Vdc                                           | - |

| M.4   | Digital Input Voltage                                   | REF<br>TEST<br>SI<br>SCK<br>CSB<br>DEFAULT             | -0.3<br>-0.3<br>-0.3<br>-0.3<br>-0.3<br>-0.3 | $ \begin{array}{c} {\rm min.} \; (6.0, \; V_{\rm DD} + 0.3) \\ 6.0 \\ 6.0 \\ 6.0 \\ {\rm min.} \; (6.0, \; V_{\rm SO} + 0.3) \\ {\rm min.} \; (6.0, \; V_{\rm SO} + 0.3) \end{array} $ | Vdc<br>Vdc<br>Vdc<br>Vdc<br>Vdc<br>Vdc<br>Vdc | - |

| M.5   | Digital Output Pin<br>Voltage                           | SO                                                     | -0.3                                         | min. (6.0, V <sub>SO</sub> + 0.3)                                                                                                                                                      | Vdc                                           | - |

| M.6   | Dynamic Clamp<br>Voltage<br>T <sub>clamp</sub> < 2.0 ms | BAT<br>POSx<br>NEGx<br>OUTx                            | -1.5<br>-1.5<br>-1.5<br>-1.5                 | -<br>-<br>-                                                                                                                                                                            | V<br>V<br>V<br>V                              | - |

| M.7   | Ground Pin Voltage<br>(GND)                             | GND                                                    | -0.3                                         | 0.3                                                                                                                                                                                    | Vdc                                           | - |

| M.8   | Difference between<br>PGND1 and PGND2                   | PGNDx                                                  | -0.3                                         | 0.3                                                                                                                                                                                    | Vdc                                           | - |

| Othe  | rs                                                      |                                                        |                                              |                                                                                                                                                                                        |                                               |   |

| M.9   | Biased Junction<br>Temperature                          | T <sub>j</sub>                                         | -40                                          | 150                                                                                                                                                                                    | °C                                            | - |

| M.10  | Storage Temperature                                     | T <sub>st</sub>                                        | -55                                          | 150                                                                                                                                                                                    | °C                                            | - |

| M.11  | Single Clamp Energy<br>(OUTx) I=1.0A<br>Tj=150 °C       | E <sub>max</sub>                                       | -                                            | 30                                                                                                                                                                                     | mJ                                            | - |

#### **Maximum Ratings**

#### Absolute Maximum Ratings<sup>1</sup> (cont'd)

#### $T_{\rm i}$ = -40 to 150 °C

| Pos. | Parameter                                                  | Symbol |      | Limit Values | Unit | Notes |

|------|------------------------------------------------------------|--------|------|--------------|------|-------|

|      |                                                            |        | Min. | Max.         |      |       |

| M.12 | ESD HBM all pins<br>EIA/JESD22-A 114B<br>(1.5 K Ω, 100 pF) | -      | -2   | +2           | kV   | -     |

| M.13 | ESD MM all pins<br>EIA/JESD22-A115A<br>(0 Ω, 200 pF)       | -      | -200 | 200          | V    | -     |

1) Not subject to production test, specified by design

All voltages are with respect to PGND1 & 2. Positive current flows into the pin unless otherwise specified.

# Attention: Stresses above those listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Functional Range**

## 4 Functional Range

#### **Functional Range**

$T_{\rm i}$  = -40 to 150 °C; V<sub>REF</sub> = 2.5V

| Pos. | Parameter                                           | Symbol                            | Limi | t Values                         | Unit | Remarks                                           |

|------|-----------------------------------------------------|-----------------------------------|------|----------------------------------|------|---------------------------------------------------|

|      |                                                     |                                   | Min. | Max.                             |      |                                                   |

| F.1  | Voltage at BAT                                      | V <sub>BAT</sub>                  | 9    | 18                               | V    | -                                                 |

| F.2  | Voltage at $V_{\rm DD}$                             | $V_{DD}$                          | 4.75 | 5.25                             | V    | -                                                 |

| F.3  | Voltage at VSO                                      | V <sub>VSO</sub>                  | 3.1  | V <sub>DD</sub> +0.3<br>or 5.25V | V    | -                                                 |

| F.4  | Voltage at SI, SCK                                  | V <sub>INI</sub>                  | -0.3 | V <sub>DD</sub> + 0.3            | V    | -                                                 |

| F.5  | Voltage at CSB,<br>DEFAULT, SO                      | V <sub>IN2</sub>                  | -0.3 | V <sub>SO</sub> + 0.3            | V    | -                                                 |

| F.6  | Voltage at POS1,<br>POS2, NEG1,<br>NEG2, OUT1, OUT2 | $V_{OUT}, \\ V_{POS}, \\ V_{NEG}$ | -0.3 | 50                               | V    | -                                                 |

| F.7  | Voltage Difference<br>POS1-NEG1,<br>POS2-NEG2       | $V_{POS} - V_{NEG}$               | 0    | 1.23                             | V    | -                                                 |

| F.8  | Voltage at PGND1,<br>PGND2, GND                     | V <sub>GND</sub>                  | -0.3 | 0.3                              | V    | -                                                 |

| F.9  | SPI Clock Frequency                                 | $f_{clk}$                         |      | 3.2                              | MHz  | $C_{\rm SO}$ = 200 pF max;<br>$V_{\rm VSO}$ = 5 V |

| F.10 | Junction Temperature                                | Tj                                | -40  | 150                              | °C   | -                                                 |

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

#### 4.1 Thermal Resistance

| Pos. | Parameter                         | Symbol            | Limit Values |      |      | Unit | Conditions |

|------|-----------------------------------|-------------------|--------------|------|------|------|------------|

|      |                                   |                   | Min.         | Тур. | Max. |      |            |

| G.1  | Junction to Case <sup>1)</sup>    | R <sub>thjC</sub> |              |      | 5.2  | K/W  | 2)         |

| G.2  | Junction to Ambient <sup>1)</sup> | R <sub>thjA</sub> |              | 26   |      | K/W  | 2) 3)      |

#### **Functional Range**

- 1) Not subject to production test, specified by design.

- 2) Both channels on with 1W power dissipation per channel

- 3) Specified RthJA value is according to Jedec JESD51-2, -5, -7 at natural convection on FR4 2s2p board. The Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70mm Cu, 2 x 35 mm Cu). Where applicable a thermal via array under the exposed pad contacted the first inner layer.

### 5 Functional Description and Electrical Characteristics

#### 5.1 Supply and Reference

The device has incorporated a power-on reset circuit. This feature will reset the commanded average current to 0 mA (device off), and will reset the programmable registers to their default values. The fault register bits are reset during power on reset. The device will remain off until a valid command is received. The device will also be reset in the case of an undervoltage condition on the pin  $V_{\rm DD}$ . Note that if the voltage on the pin *REF* pin is greater than the voltage on the pin  $V_{\rm DD}$ , a current will flow from the *REF* pin to the  $V_{\rm DD}$  pin.

#### Electrical Characteristics 1)

| Pos.  | Parameter                                   | Symbol           | Li   | mit Val            | ues  | Unit | <b>Test Conditions and</b>                                                         |

|-------|---------------------------------------------|------------------|------|--------------------|------|------|------------------------------------------------------------------------------------|

|       |                                             |                  | Min. | Typ. <sup>2)</sup> | Max. |      | Instructions                                                                       |

| 5.1.1 | REF<br>Bias Current                         | I <sub>REF</sub> | -20  | -                  | 20   | μA   | $V_{\text{REF}}$ = 2.5 V<br>(includes leakage current<br>and a small current sink) |

| 5.1.2 | V <sub>DD</sub><br>5 V Supply<br>Current    | I <sub>DD</sub>  | _    | -                  | 15   | mA   | V <sub>DD</sub> = 5.25 V;<br>CSB = 5.0 V;<br>DAC = 3FF                             |

| 5.1.3 | V <sub>SO</sub><br>I/O Supply<br>Current    | I <sub>SO</sub>  | _    | -                  | 1    | mA   | V <sub>SO</sub> = 5.25 V;<br>CSB = 5.0 V                                           |

| 5.1.4 | BAT<br>Supply Current                       | I <sub>BAT</sub> | -    | -                  | 1    | mA   | V <sub>DD</sub> = 5.25 V;<br>CSB = 5.0 V                                           |

| 5.1.5 | $V_{\rm DD}$<br>Power-On Reset<br>Threshold | V <sub>POR</sub> | 2.5  | -                  | 3.5  | V    | Power-On Reset<br>Threshold                                                        |

| 5.1.6 | Internal<br>Reference<br>Voltage            | $V_{IREF}$       | 2.45 | 2.5                | 2.55 | V    | Tested at wafer test.                                                              |

$T_{i}$  = -40 to 150 °C; V<sub>BAT</sub> = 9 V to 18 V; V<sub>DD</sub> = 4.75 V to 5.25 V

1) Positive current flow is into the device.

Target @T<sub>J</sub> = 25 °C

Note: The listed characteristics are ensured over the operating range of the integrated circuit. Typical characteristics specify mean values expected over the production spread. If not otherwise specified, typical characteristics apply at  $T_A = 25$  °C and the given supply voltage.

#### 5.2 Input/Output

The DEFAULT pin is an active high input. A weak pull-up current (typical 15  $\mu$ A) on this pin ensures a defined level when this pin is not connected (e.g. open pin). An active high signal on the DEFAULT pin sets the commanded current for both channels to 0 mA, and resets all programmable registers to their default values. Any SPI commands that are received while the DEFAULT pin is high will be ignored, and the SO pin will remain in a high impedance state.

The fault register bits are not cleared when the Default pin is asserted.

Upon coming out of default mode, the commanded current will remain at 0 mA, device off, and the programmable registers will remain at their default values.

The DEFAULT pin must be asserted high whenever the voltage on the pin  $V_{\rm DD}$  is less than the minimum  $V_{\rm DD}$  operating voltage (4.75 V), otherwise the electrical characteristic specifications (see table below) may not be met. The diagnostic functions are not operational when the  $V_{\rm DD}$  voltage is less than 4.75V.

The TEST pin is an active high pin. This pin must be connected directly to ground in the application, as it is only used for IC test purposes. A passive pull-down resistor in the device ensures a logic low value when the pin is not connected.

#### Electrical Characteristics 1)

$T_i$  = -40 to 150 °C; V<sub>BAT</sub> = 9 V to 18 V; V<sub>DD</sub> = 4.75 V to 5.25 V

| Pos.  | Parameter                                   | Symbol            | Liı                    | mit Valu           | ies  | Unit | Test Conditions                                                              |

|-------|---------------------------------------------|-------------------|------------------------|--------------------|------|------|------------------------------------------------------------------------------|

|       |                                             |                   | Min.                   | Typ. <sup>2)</sup> | Max. |      | and Instructions                                                             |

| 5.2.1 | DEFAULT<br>Input Bias Current               | $I_{DEFAULT}$     | -25                    | -10                | -5   | μA   | $V_{\text{DEFAULT}} = 0 \text{ V};$<br>Pull-up source is pin $V_{\text{SO}}$ |

| 5.2.2 | TEST<br>Pull-down Resistor                  | R <sub>TEST</sub> | _                      | 20                 | -    | kΩ   | -                                                                            |

| 5.2.3 | SI, SCK, CSB,<br>DEFAULT Input<br>Threshold | V <sub>IH</sub>   | 2.0                    | _                  | -    | V    | SCK is specified by design, not subject to production test.                  |

| 5.2.4 | SI, SCK, CSB,<br>DEFAULT Input<br>Threshold | V <sub>IL</sub>   | _                      | -                  | 0.8  | V    | SCK is specified by design, not subject to production test.                  |

| 5.2.5 | SO Output High<br>Voltage                   | V <sub>OH</sub>   | 0.8<br>V <sub>SO</sub> | -                  | -    | V    | SO <i>I</i> <sub>o</sub> = -1 mA                                             |

| 5.2.6 | SO Output Low<br>Voltage                    | V <sub>OL</sub>   | -                      | -                  | 0.4  | V    | SO <i>I</i> <sub>o</sub> = 1 mA                                              |

1) Positive current flow is into the device.

Target @T<sub>J</sub> = 25 °C

#### 5.3 Power Output

The slew rate of the voltage on the pins OUT1 and OUT2 are programmable via the SPI interface. The fast settings are intended for fast switching solenoids (low inductance) to minimize power dissipation within the TLE 7241E, and to minimize DC current error due to overshooting the switch points. The slower slew rates can be used with slower switching solenoids (high inductance) to improve radiated emissions from the wiring harness.

#### Electrical Characteristics 1)

Limit Values Pos. Parameter Symbol Unit Test Conditions and Instructions Typ.<sup>2)</sup> Min. Max. 0.25 5.3.1 OUTx rise and OUTx 0.5 1 Threshold: 4 V to 10 V μS  $V_{\rm BAT} = 14 \, \rm V;$ fall times Slew  $t_{\rm R}$  and  $t_{\rm F}$ Rate reg = 0 $R_{\text{load}} = 5 \Omega$ 5.3.2 OUTx rise and OUTx 0.5 1 2 Threshold: 4 V to 10 V μS fall times Slew  $V_{BAT} = 14 \text{ V};$  $t_{\rm R}$  and  $t_{\rm F}$ Rate reg = 1  $R_{\text{load}} = 5 \Omega$ Threshold: 4 V to 10 V 5.3.3 OUTx rise and OUTx 1 2 4 uS  $V_{RAT} = 14 V;$ fall times Slew  $t_{\rm R}$  and  $t_{\rm F}$ Rate reg = 2 $R_{\text{load}} = 5 \Omega$ Threshold: 4 V to 10 V 5.3.4 OUTx rise and OUTx 25 5 10 μS  $V_{\rm BAT} = 14 \, \rm V;$ fall times Slew  $t_{\rm R}$  and  $t_{\rm F}$ Rate reg = 3 $R_{\text{load}} = 5 \Omega$  $V_{DS} = 24 \text{ V}$ 5.3.5 **OUTx Output** 10  $I_{DSS}$ \_ μA Off Leakage (00<sub>µ</sub>)  $V_{\rm DS} = V_{\rm CLAMP} - 1V$ 5.3.6 **OUTx Output** 3  $I_{DSS}$ mΑ \_ \_ Off Leakage  $V_{CLAMP}$  is the measured (00<sub>H</sub>) clamp voltage (Item 5.4.1.3) OUTx<sup>3)</sup> Driver 5.3.7  $R_{\rm DS(ON)}$ 240 450 Driver on Resistance \_ mΩ @T<sub>.1</sub> = 150 °C on Resistance

$T_{\rm i}$  = -40 to 150 °C; V<sub>BAT</sub> = 9 V to 18 V; V<sub>DD</sub> = 4.75 V to 5.25 V

1) Positive current flow is into the device.

2) *T*<sub>J</sub> = 25 °C

3) Electrical Distributions must be performed on this parameter as defined in the AEC-Q100 Specification Table 2 test 27.

#### 5.4 Protection and Control

#### Electrical Characteristics 1)

$T_i$  = -40 to 150 °C; V<sub>BAT</sub> = 9 V to 18 V; V<sub>DD</sub> = 4.75 V to 5.25 V

| Pos.  | Parameter          | Symbol             | Li   | ₋imit Values       |      | Unit | Test Conditions and                                        |

|-------|--------------------|--------------------|------|--------------------|------|------|------------------------------------------------------------|

|       |                    |                    | Min. | Typ. <sup>2)</sup> | Max. |      | Instructions                                               |

| 5.4.1 | POS/NEG<br>IBIAS   | POS/NEG<br>IBIAS   | -500 | -                  | 500  | μA   | DAC command =3FF<br>POS=NEG=0V &<br>POS=NEG=17V            |

| 5.4.2 | POS/NEG<br>LEAKAGE | POS/NEG<br>LEAKAGE | 20   | 40                 | 60   | μA   | Fault typing bit = 0, Zero<br>Current,<br>POS = NEG = 14 V |

|       |                    |                    | -20  | 0                  | 20   | μA   | Fault typing bit = 1, Zero<br>Current,<br>POS = NEG = 14 V |

1) Positive current flow is into the device.

2) T<sub>J</sub> = 25 °C

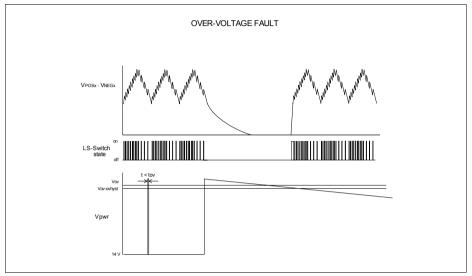

#### 5.4.1 Overvoltage Sensing and Protection

When the voltage on the BAT pin exceeds the Overvoltage Shutdown Threshold (see table below, **Item 5.4.1.1**), the output channel will shut off to protect the IC from excessive power dissipation. A short filter with a typical value of 6.5  $\mu$ s is included to prevent undesired shutdown due to short transient voltage spikes. Although SPI communication will remain functional, the output will remain off. The device will resume normal operation when the BAT voltage has dropped below the overvoltage hysteresis level. Note that the programmable registers are not reset, and the dither counter continues to operate during an overvoltage event.

Both channels are disabled when an overvoltage condition is detected.

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as outside normal operating range. Protections functions are not designed for continuous repetitive operation.

#### Figure 4 Overvoltage Shutdown

#### Electrical Characteristics <sup>1)</sup>

$T_{\rm i}$  = -40 to 150 °C; V<sub>BAT</sub> = 9 V to 18 V; V<sub>DD</sub> = 4.75 V to 5.25 V

| Pos.    | Parameter                     | Symbol             | Li   | mit Valı           | les  | Unit | Test Conditions                              |

|---------|-------------------------------|--------------------|------|--------------------|------|------|----------------------------------------------|

|         |                               |                    | Min. | Typ. <sup>2)</sup> | Max. | _    | and Instructions                             |

| 5.4.1.1 | BAT Overvoltage<br>Shutdown   | OV                 | 30   | 35                 | 40   | Vdc  | Ramp up BAT until<br>outputs Off             |

| 5.4.1.2 | BAT Overvoltage<br>hysteresis | OV <sub>HYST</sub> | -    | 1.0                | -    | Vdc  | Ramp BAT down until outputs On <sup>3)</sup> |

| 5.4.1.3 | OUTx Active<br>Clamp Voltage  | V <sub>clamp</sub> | 50   | 53                 | 60   | V    | $I_{\rm d}$ = 20 mA, output off              |

1) Positive current flow is into the device.

2) *T*<sub>J</sub> = 25 °C

3) Not subject to production test, specified by design.

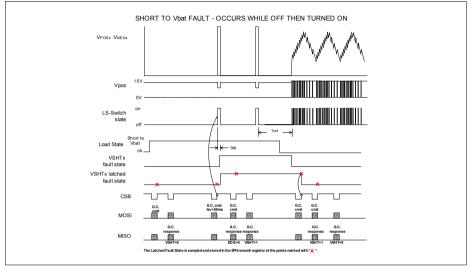

#### 5.4.2 Overcurrent / Short to V<sub>BAT</sub> Sensing

An overcurrent fault is detected by sensing the voltage at the POS input pin. A comparator is used to detect the voltage while the gate drive is on. When the voltage at the POS input pin exceeds the short circuit / overcurrent threshold (see table below, **Item 5.4.2.3**) for a time greater than the short sense time (see table below, **Item 5.4.2.1**)

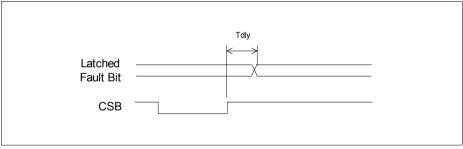

the driver will be turned off and the Overcurrent / Short to  $V_{\rm BAT}$  ( $V_{\rm SHT}$ ) fault bit will be latched until the fault register is read via SPI. The driver will remain in the off condition for the short circuit refresh time (see table below, **Item 5.4.2.2**). After the refresh time, the driver will automatically turn on again. If the short condition is no longer present, the channel will operate normally. If the short circuit condition persists, the driver will be cycled off after the short sense time once again. The refresh time has been chosen for minimal increase in power dissipation during a continuous fault condition.

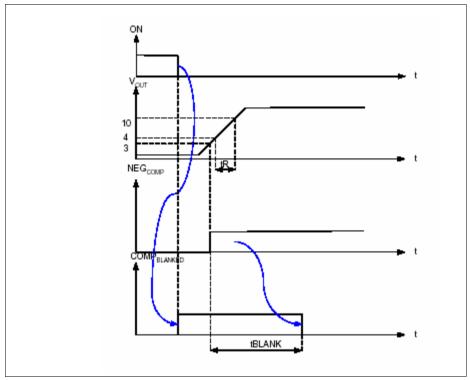

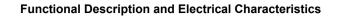

In order to prevent false detection of an overcurrent / short to  $V_{\text{BAT}}$  fault during an "off to on" transition of the low-side output transistor, the detection circuit is disabled for a blanking time (see "Electrical Characteristics" on Page 31, Item 5.5.1.1 and Item 5.5.1.2) after the transistor is enabled (see Figure 16 and Figure 17).

The output transistor control circuit includes a current limit feature that will limit the transistor current to a maximum value (see table below, **Item 5.4.2.4**) in order to protect the device from excessive current flow.

If a new average current command or configuration command is received for a shorted channel while that channel is within the short circuit refresh time, the new data will be stored but the channel will remain in the off state until the refresh time expires. The new data will become active when the short circuit condition is released.

The Overcurrent / Short to VBAT detection is channel specific.

- Note: An Overcurrent / Short to VBAT fault is not detected if the average current command is <50 mA (with 1 W sense resistor).

- Note: An overcurrent / short to  $V_{BAT}$  fault is latched until read via the MISO return word.

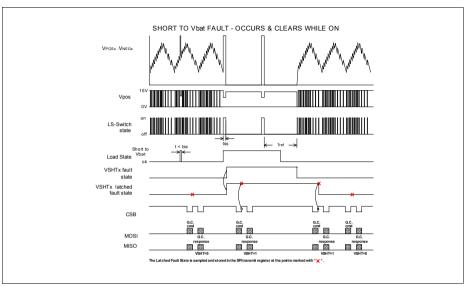

Figure 5 Short to V<sub>BAT</sub> - Channel On

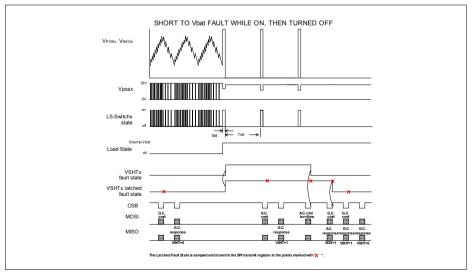

Figure 6 Short to V<sub>BAT</sub> - Channel On Then Turned Off

#### Electrical Characteristics <sup>1)</sup>

$T_{\rm i}$  = -40 to 150 °C; V<sub>BAT</sub> = 9 V to 18 V; V<sub>DD</sub> = 4.75 V to 5.25 V

| Pos.    | Parameter                                                   | Symbol               | Li   | imit Val           | ues  | Unit | <b>Test Conditions</b>                                   |

|---------|-------------------------------------------------------------|----------------------|------|--------------------|------|------|----------------------------------------------------------|

|         |                                                             |                      | Min. | Typ. <sup>2)</sup> | Max. | 1    | and Instructions                                         |

| 5.4.2.1 | OUTx Short<br>Sense Time                                    | t <sub>ss</sub>      | 30   | 60                 | 90   | μS   | 50 - 50 Threshold                                        |

| 5.4.2.2 | OUTx Short<br>Refresh Time                                  | t <sub>ref</sub>     | 3    | 14                 | 24   | ms   | 50 - 50 Threshold                                        |

| 5.4.2.3 | OUTx Short<br>circuit/<br>Overcurrent<br>Fault<br>Threshold | V <sub>VSHTOCT</sub> | 2.0  | 2.5                | 3.0  | Vdc  | V <sub>REF</sub> = 2.5 V                                 |

| 5.4.2.4 | OUTx Current<br>Limit                                       | I <sub>dlim</sub>    | 3.0  | 5.0                | 6.0  | A    | $V_{\rm BAT}$ = 14 V;<br>$V_{\rm DD}$ = 5V;<br>output on |

1) Positive current flow is into the device.

2) T<sub>J</sub> = 25 °C

#### 5.4.3 Open Load / Short to Ground Detection

The OLSG fault bit is set under the following conditions.

#### Operating Condition #1

The average current command is > 50 mA (with 1  $\Omega$  sense resistor) and the low-side driver is ON (solenoid current is increasing).

The OLSG (open load/short to ground) fault bit will be set if the low-side transistor remains on for a time greater than the on state open sense time ("Electrical Characteristics" on Page 23, Item 5.4.3.3).

#### Operating Condition #2

The average current command is > 50 mA (with 1  $\Omega$  sense resistor) and the low-side driver is OFF.

The OLSG fault bit is set if the voltage on the NEGx pin is less than the NEG pin OLSG threshold voltage ("Electrical Characteristics" on Page 23, Item 5.4.3.6) for a time greater than the NEG pin OLSG delay time ("Electrical Characteristics" on Page 23, Item 5.4.3.5).

#### **Operating Condition #3**

The average current command is < 50 mA (with a 1  $\Omega$  sense resistor) and the fault typing bit = 0.

The OLSG (open load/short to ground) fault bit will be set if the POS pin voltage is less than the off state open load threshold ("Electrical Characteristics" on Page 20, Item 5.4.2.3) for longer than the off state open load sense time ("Electrical Characteristics" on Page 23, Item 5.4.3.4) or the NEG pin is less than the NEG pin OLSG threshold voltage ("Electrical Characteristics" on Page 23, Item 5.4.3.6) for a time greater than the NEG pin OLSG delay time ("Electrical Characteristics" on Page 23, Item 5.4.3.5). A pull-down current ("Electrical Characteristics" on Page 23, Item 5.4.3.1) will be activated between the POS pin and ground when the Fault Typing bit = 0.

#### **Operating Condition #4**

The average current command is < 50 mA (with a 1  $\Omega$  sense resistor) and the fault typing bit = 1.

The OLSG fault bit will be set when the voltage on the pin POSx is below the off state open load threshold ("Electrical Characteristics" on Page 20, Item 5.4.2.3) for the a time greater than  $t_{os(off)}$  ("Electrical Characteristics" on Page 23, Item 5.4.3.4) or the NEG pin is less than the NEG pin OLSG threshold voltage ("Electrical Characteristics" on Page 23, Item 5.4.3.6) for a time greater than the NEG pin OLSG delay time

("Electrical Characteristics" on Page 23, Item 5.4.3.5). A pull-up current ("Electrical Characteristics" on Page 23, Item 5.4.3.2) will be activated between  $V_{DD}$  and the POS pin when the Fault Typing bit = 1.

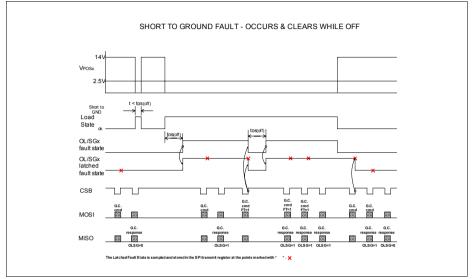

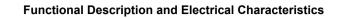

#### Distinguishing between Open Load and Short to Ground Faults

When an Open Load/Short to Ground is flagged, to distinguish between Open Load and Short-To-Ground, a general configuration command word must be sent three times to the appropriate channel with the fault typing bit set, and the average current must be programmed to zero. Check the OL/SG fault bit from the third write. A '0' signifies Open Load, '1' signifies Short-To-Ground. A short to ground will still be flagged for 0 mA command current. Note that setting the fault typing bit under both normal & fault conditions does not change the status of the output or the current flowing.

The fault typing bit enables a 40  $\mu$ A pull-up current on the POS pin when high, and enables a 40  $\mu$ A pull-down current on the POS pin when low.

#### Electrical Characteristics <sup>1)</sup>

$T_{\rm i}$  = -40 to 150 °C; V<sub>BAT</sub> = 9 V to 18 V; V<sub>DD</sub> = 4.75 V to 5.25 V

| Pos.    | Parameter                                                                  | Symbol                       | Li   | mit Valı           | les  | Unit | <b>Test Conditions</b>                                    |

|---------|----------------------------------------------------------------------------|------------------------------|------|--------------------|------|------|-----------------------------------------------------------|

|         |                                                                            |                              | Min. | Typ. <sup>2)</sup> | Max. |      | and Instructions                                          |

| 5.4.3.1 | POS Open detect<br>current                                                 | I <sub>OL</sub>              | 20   | 40                 | 60   | μA   | Fault typing bit = 0,<br>Zero Current                     |

| 5.4.3.2 | POS Load short to<br>ground detect                                         | I <sub>SG</sub>              | -60  | -40                | -20  | μA   | Fault typing bit = 1,<br>Zero Current,<br>POS = NEG = 2 V |

| 5.4.3.3 | OUTx On-State<br>open sense time –<br>POS pin                              | t <sub>os</sub> (on)         | 6    | 12                 | 24   | ms   | 50 - 50 Threshold <sup>3)</sup>                           |

| 5.4.3.4 | OUTx Off-State<br>open sense time –<br>POS pin                             | t <sub>os</sub> (off)        | 30   | 60                 | 90   | μS   | 50 - 50 Threshold <sup>3)</sup>                           |

| 5.4.3.5 | NEGx Open load /<br>short to ground<br>filter time – NEG<br>pin            | T <sub>OLSG_N</sub><br>(off) | 30   | 60                 | 90   | μs   | -                                                         |

| 5.4.3.6 | NEGx Open load /<br>short to ground<br>detection<br>threshold – NEG<br>pin | V <sub>OLSG_N</sub>          | 2.0  | 2.8                | 3.6  | V    | _                                                         |

1) Positive current flow is into the device.

2) T<sub>J</sub> = 25 °C

3) Not subject to production test, tested by scanpath.

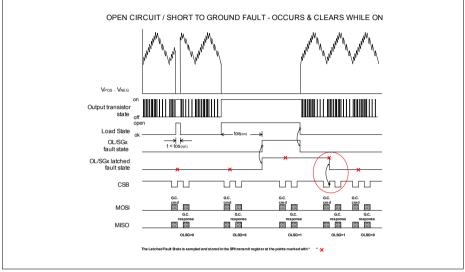

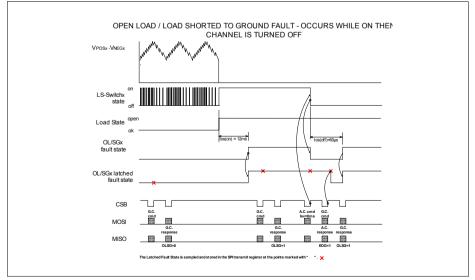

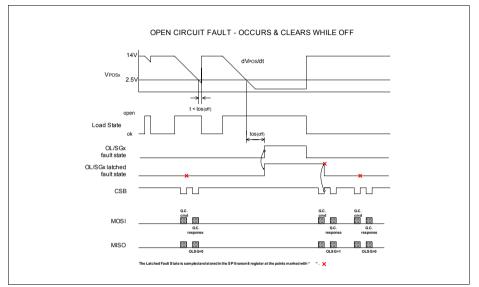

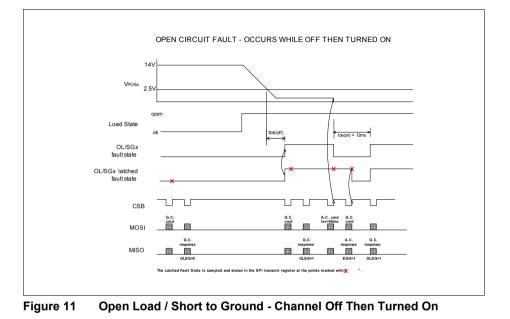

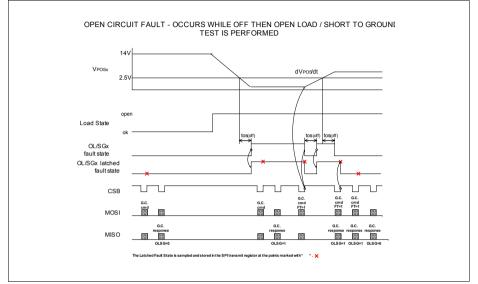

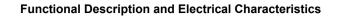

#### Diagnostics Timing Diagrams

Figure 8 Open Load / Short to Ground Fault - Channel On

#### Figure 10 Open Load Short to Ground - Channel Off

$$\frac{\mathrm{d}V_{\mathrm{POS}}}{\mathrm{d}t} = \frac{-(i_{\mathrm{OL}} - i_{\mathrm{Rrecirc}})}{(C_{\mathrm{POS}} + C_{\mathrm{NEG}} + C_{\mathrm{OUT}})} \tag{1}$$

$i_{OL}$  = open load detection pull down current (5.4.3.1)  $i_{Rrecirc}$  = reverse leakage current of recirculation diode  $C_{POS}$  = external capacitance on the POS pin  $C_{NEG}$  = external capacitance of the NEG pin  $C_{OUT}$  = external capacitance on the OUT pin

(2)

#### **Functional Description and Electrical Characteristics**

Figure 12 Open Load - Fault Type Bit = 1 Test

$$\frac{\mathrm{d}V_{\mathrm{POS}}}{\mathrm{d}t} = \frac{-(i_{\mathrm{SG}} - i_{\mathrm{Rrecirc}})}{(C_{\mathrm{POS}} + C_{\mathrm{NEG}} + C_{\mathrm{OUT}})}$$

$i_{SG}$  = short to ground detection pull up current (5.4.3.2)  $i_{Rrecirc}$  = reverse leakage current of recirculation diode  $C_{POS}$  = external capacitance on the POS pin  $C_{NEG}$  = external capacitance of the NEG pin  $C_{OUT}$  = external capacitance on the OUT pin

Figure 13 Short to Ground Fault Type Bit = 1 Test

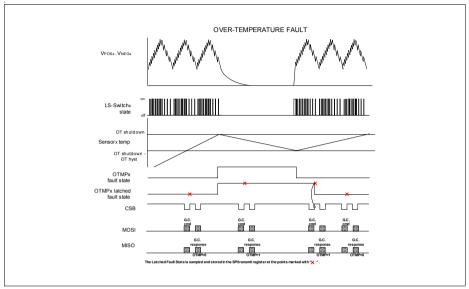

#### 5.4.4 Thermal Shutdown

Each output transistor includes an independent thermal shutdown circuit. When the temperature of the output transistor exceeds a threshold value (see table below, **Item 5.4.4.1**), the output transistor will be turned off and a fault bit will be set for the failed channel. The transistor will remain off until the local transistor temperature has decreased by the thermal hysteresis value (see table below, **Item 5.4.4.2**), the output transistor will then turn on again.

Thermal shutdown faults are channel specific.

Note: A thermal fault is latched until read via the MISO return word.

#### Figure 14 Overtemperature Shutdown with Restart

#### Electrical Characteristics <sup>1)</sup>

$T_{\rm i}$  = -40 to 150 °C; V<sub>BAT</sub> = 9 V to 18 V; V<sub>DD</sub> = 4.75 V to 5.25 V

| Pos.    | Parameter                                     | Symbol | Lii  | Limit Values       |      |    | <b>Test Conditions</b> |

|---------|-----------------------------------------------|--------|------|--------------------|------|----|------------------------|

|         |                                               |        | Min. | Typ. <sup>2)</sup> | Max. |    | and Instructions       |

| 5.4.4.1 | OUTx<br>Overtemperature<br>shutdown threshold | OTsd   | 160  | -                  | 190  | °C | 3)                     |

| 5.4.4.2 | OUTx<br>Overtemperature<br>hysteresis         | OThys  | -    | 10                 | -    | °C | 3)                     |

1) Positive current flow is into the device.

2) T<sub>J</sub> = 25 °C

3) Not subject to production test, specified by design.

#### 5.5 Current Control

#### 5.5.1 Hysteretic Current Control

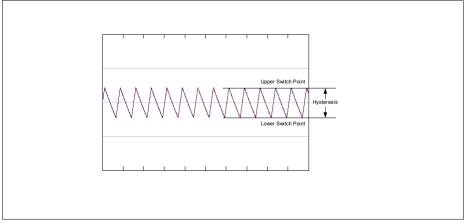

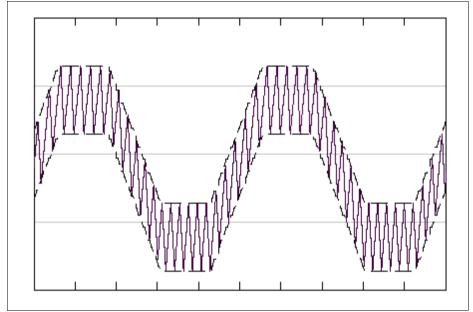

The TLE 7241E device uses a hysteretic control method to regulate the solenoid current. The output transistor is toggled on and off based on the measured value of the solenoid current. The solenoid current is measured at the pins POSx and NEGx which are connected to an external current sense resistor. The device calculates an upper and lower switch point based on the input commands from the microprocessor. The output transistor is turned on until the upper threshold is reached, and then turned off until the lower threshold is reached. See **Figure 15** for an example of the solenoid current waveform. In this example, the dither is disabled.

The average switch point

$$SP_{AVG} = \frac{\text{Upper switch pt + Lower switch pt}}{2}$$

(3)

is determined by the contents of the average current command register.

The relationship is:

$$SP_{AVG} = \frac{\text{register value}}{2^{10}} \times 1230 \text{ mV}$$

(4)

The hysteresis value can be programmed to a value from 40 mVpp to 110 mVpp in steps of 10 mVpp.

Figure 15 Output Current Waveform - No Dither

Note that the switching frequency and duty cycle of the output transistor are not directly controlled by the TLE 7241E device and are dependent on the characteristics of the solenoid (inductance, resistance, etc.) and the solenoid supply voltage.

#### Electrical Characteristics <sup>1)</sup>

| Pos.    | Parameter                                                                                                                                         | Symbol                        | Lin    | nit Valu           | es   | Unit | Test Conditions and<br>Instructions                                                                                   |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------|--------------------|------|------|-----------------------------------------------------------------------------------------------------------------------|

|         |                                                                                                                                                   |                               | Min.   | Typ. <sup>2)</sup> | Max. |      |                                                                                                                       |

| 5.5.1.1 | OUTx <sup>3)</sup><br>Blanking<br>time 1 (see<br><b>Figure 16</b> ,<br><b>Figure 17</b> )                                                         | T <sub>blank1</sub>           | -      | 5                  | -    | μs   | Slew Rate Register = 0 or 1.<br>From enable/disable of lowside output transistor to enabling of $V_{pos}$ comparator. |

| 5.5.1.2 | OUTx <sup>3)</sup><br>Blanking<br>time 2 (see<br><b>Figure 16</b> ,<br><b>Figure 17</b> )                                                         | T <sub>blank2</sub>           | -      | 15                 | -    | μs   | Slew Rate Register = 2 or 3.<br>From enable/disable of output transistor to enabling of $V_{pos}$ comparator.         |

| 5.5.1.3 | $\begin{array}{l} OUTx^{4)5)} \\ dV_{OUT} = \\ 200 \ mV \\ I_{avg} \text{ register} \\ = 0A6_{H} \end{array}$                                     | d <i>V</i> <sub>OUT 200</sub> | -5%    | 200                | +5%  | mV   | Output current<br>$I_{\rm OUT}$ = 200 mA with<br>$R_{\rm sense}$ = 1.0 $\Omega$<br><i>REF</i> = 2.5V                  |

| 5.5.1.4 | OUT $x^{4)5)}$<br>d $V_{OUT}$ =<br>400 mV<br>$I_{avg}$ register<br>= 14D <sub>H</sub>                                                             | d <i>V</i> <sub>OUT 400</sub> | -2.5 % | 400                | 2.5% | mV   | Output current<br>$I_{\rm OUT}$ = 400 mA with<br>$R_{\rm sense}$ = 1.0 $\Omega$<br><i>REF</i> = 2.5V                  |

| 5.5.1.5 | $\begin{array}{l} {\rm OUTx}^{4)5)} \\ {\rm d}V_{\rm OUT} = \\ 600 \ {\rm mV} \\ I_{\rm avg} \ {\rm register} \\ = 1{\rm F3}_{\rm H} \end{array}$ | dV <sub>OUT 600</sub>         | -2%    | 600                | 2%   | mV   | Output current<br>$I_{\rm OUT}$ = 600 mA with<br>$R_{\rm sense}$ = 1.0 $\Omega$<br><i>REF</i> = 2.5V                  |

| 5.5.1.6 | OUT $x^{4(5)}$<br>d $V_{OUT}$ =<br>800 mV<br>$I_{avg}$ register<br>= 29A <sub>H</sub>                                                             | dV <sub>OUT 800</sub>         | -2%    | 800                | 2%   | mV   | Output current<br>$I_{OUT}$ = 800 mA with<br>$R_{sense}$ = 1.0 $\Omega$<br><i>REF</i> = 2.5V                          |

#### Electrical Characteristics (cont'd)<sup>1)</sup>

| Pos.     | Parameter                                                                                                                                        | Symbol                | Lir  | nit Valu           | es   | Unit | Test Conditions and<br>Instructions                                                           |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|--------------------|------|------|-----------------------------------------------------------------------------------------------|

|          |                                                                                                                                                  |                       | Min. | Typ. <sup>2)</sup> | Max. |      |                                                                                               |

| 5.5.1.7  | $\begin{array}{l} {\rm OUTx}^{\rm 4)5)} \\ {\rm d}V_{\rm OUT} = \\ {\rm 1000 \ mV} \\ I_{\rm avg} \ {\rm register} \\ = 340_{\rm H} \end{array}$ | dV <sub>OUT1000</sub> | -3%  | 1000               | 3%   | mV   | Output current<br>$I_{OUT}$ = 1000 mA with<br>$R_{sense}$ = 1.0 $\Omega$<br><i>REF</i> = 2.5V |

| 5.5.1.8  | OUT $x^{3(5)}$<br>Switching<br>hysteresis<br>40<br>Sw Hyst.<br>register = 0<br>DAC counts<br>= $\pm 17$                                          | dV <sub>hyst40</sub>  | 29.6 | 39.6               | 49.6 | mVpp | 40 mV programmed<br>setting<br>Input Command ><br>200 mV<br><i>REF</i> = 2.5V                 |

| 5.5.1.9  | OUT $x^{3(5)}$<br>Switching<br>hysteresis<br>50<br>Sw Hyst.<br>register = 1<br>DAC counts<br>= $\pm 21$                                          | dV <sub>hyst50</sub>  | 40.4 | 50.4               | 60.4 | mVpp | 50 mV programmed<br>setting<br>Input Command ><br>200 mV<br><i>REF</i> = 2.5V                 |

| 5.5.1.10 | OUT $x^{3(5)}$<br>Switching<br>hysteresis<br>60<br>Sw Hyst.<br>register = 2<br>DAC counts<br>= $\pm 25$                                          | dV <sub>hyst60</sub>  | 50.1 | 60.1               | 70.1 | mVpp | 60 mV programmed<br>setting<br>Input Command ><br>200 mV<br><i>REF</i> = 2.5V                 |

#### Electrical Characteristics (cont'd)<sup>1)</sup>

| Pos.     | Parameter                                                                                               | Symbol               | Li   | mit Valu           | ies   | Unit | Test Conditions and<br>Instructions                                           |

|----------|---------------------------------------------------------------------------------------------------------|----------------------|------|--------------------|-------|------|-------------------------------------------------------------------------------|

|          |                                                                                                         |                      | Min. | Typ. <sup>2)</sup> | Max.  |      |                                                                               |

| 5.5.1.11 | OUT $x^{3(5)}$<br>Switching<br>hysteresis<br>70<br>Sw Hyst.<br>register = 3<br>DAC counts<br>= $\pm 29$ | dV <sub>hyst70</sub> | 59.7 | 69.7               | 79.7  | mVpp | 70 mV programmed<br>setting<br>Input Command ><br>200 mV<br><i>REF</i> = 2.5V |

| 5.5.1.12 | OUT $x^{3(5)}$<br>Switching<br>hysteresis<br>80<br>Sw Hyst.<br>register = 4<br>DAC counts<br>= $\pm 33$ | dV <sub>hyst80</sub> | 70.5 | 80.5               | 90.5  | mVpp | 80 mV programmed<br>setting<br>Input Command ><br>200 mV<br><i>REF</i> = 2.5V |

| 5.5.1.13 | OUT $x^{3(5)}$<br>Switching<br>hysteresis<br>90<br>Sw Hyst.<br>register = 5<br>DAC counts<br>= $\pm 37$ | dV <sub>hyst90</sub> | 80.1 | 90.1               | 101.1 | mVpp | 90 mV programmed<br>setting<br>Input Command ><br>200 mV<br><i>REF</i> = 2.5V |

#### Electrical Characteristics (cont'd)<sup>1)</sup>

| Pos.     | Parameter                                                                                                | Symbol                | Lin   | nit Valu           | es    | Unit | Test Conditions and<br>Instructions                                            |

|----------|----------------------------------------------------------------------------------------------------------|-----------------------|-------|--------------------|-------|------|--------------------------------------------------------------------------------|

|          |                                                                                                          |                       | Min.  | Typ. <sup>2)</sup> | Max.  |      |                                                                                |

| 5.5.1.14 | OUT $x^{3(5)}$<br>Switching<br>hysteresis<br>100<br>Sw Hyst.<br>register = 6<br>DAC counts<br>= $\pm 42$ | dV <sub>hyst100</sub> | 88.7  | 99.7               | 109.7 | mVpp | 100 mV programmed<br>setting<br>Input Command ><br>200 mV<br><i>REF</i> = 2.5V |

| 5.5.1.15 | OUT $x^{3(5)}$<br>Switching<br>hysteresis<br>110<br>Sw Hyst.<br>register = 7<br>DAC counts<br>= ±46      | dV <sub>hyst110</sub> | 100.5 | 110.5              | 120.5 | mVpp | 110 mV programmed<br>setting<br>Input Command ><br>200 mV<br><i>REF</i> = 2.5V |

- 1) Positive current flow is into the device.

- 2) T<sub>J</sub> = 25 °C

- 3) Not subject to production test, specified by design.

- 4) Electrical Distributions must be performed on this parameter as defined in the AEC-Q100 Specification Table 2 test 27.

- When the internal reference is used (REF pin grounded), the minimum and maximum limits must be increased by +/- 2%

Figure 16 Blanking Time (output transistor turning off)

Figure 17 Blanking Time (output transistor turning on)

#### 5.5.2 Dither Control and Operation

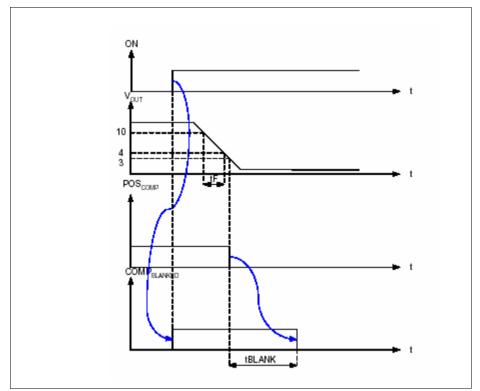

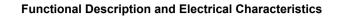

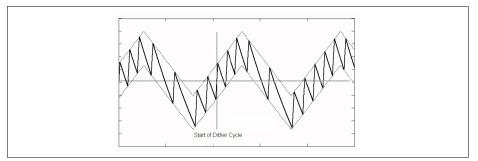

The dither waveform is generated digitally within the TLE 7241E by periodically adding or subtracting from the average current command register contents. **Figure 18** is an illustration of the Dither Waveform.

#### Figure 18 Dither Waveform

The Dither Frequency can be programmed over a range of 41 Hz to 1 kHz.

The Dither Amplitude can be programmed over a range from 12.5 mVpp to 390 mVpp.

The Dither waveform can be disabled by clearing both the dither amplitude and dither frequency fields in the Dither Configuration Register.

# Note: Programming the Dither Frequency field to zero when the Dither Amplitude is programmed to a non-zero value will result in incorrect current regulation.

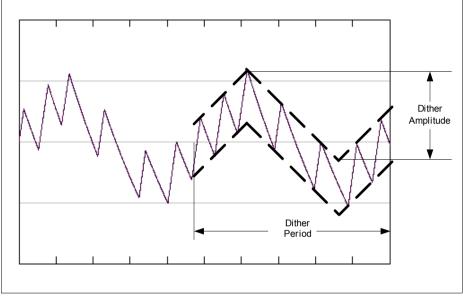

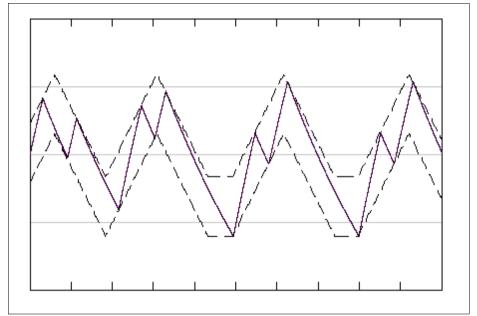

In some applications, an enhanced dither waveform is required. The enhanced dither waveform will hold the lower switch point at the minimum value (lowest lower switch point within the dither period) until the solenoid current crosses the lower switch point. This mode may be useful when the decay time of the solenoid current is slower than the slope of the dither waveform. See **Figure 19** for an illustration of the enhanced dither waveform. Enhanced Dither can be enabled by setting a bit in the SPI Dither Configuration word.

#### Figure 19 Enhanced Dither Waveform

When the enhanced dither bit is selected, the dither period will only be extended if the lower switch threshold is not crossed during the entire negative slope portion of the dither waveform.

Example see Figure 20.

The first dither period is not extended since the lower threshold was crossed during the negative slope portion of the dither waveform, the following two dither periods are extended since the low switch point was not crossed during the negative slope portion of the waveform.

#### Figure 20 Enhanced Dither Waveform

The extension of the dither period will be terminated when the lower switch threshold is crossed or when the extension time has exceeded the enhanced dither time out period (minimum 15 ms) - see Figure 21.

Figure 21 Enhanced Dither Time-out

# Electrical Characteristics <sup>1)</sup>

$T_{\rm i}$  = -40 to 150 °C; V<sub>BAT</sub> = 9 V to 18 V; V<sub>DD</sub> = 4.75 V to 5.25 V

| Pos.     | Parameter                                                  | Symbol               | Li    | mit Val            | ues   | Unit | <b>Test Conditions</b>                     |  |

|----------|------------------------------------------------------------|----------------------|-------|--------------------|-------|------|--------------------------------------------|--|

|          |                                                            |                      | Min.  | Typ. <sup>2)</sup> | Max.  |      | and Instructions                           |  |

| 5.5.2.1  | OUTx <sup>3)</sup><br>Enhanced<br>Dither time out          | T <sub>out(eD)</sub> | 15    | -                  | 25    | ms   | -                                          |  |

| 5.5.2.2  | OUTx Dither <sup>3)4)</sup><br>Amplitude Reg<br>= $04_{H}$ | I <sub>DAP-P</sub>   | 40.5  | 50                 | 60.5  | mVpp | 50 mV setting<br>programmed<br>REF = 2.5V  |  |

| 5.5.2.3  | OUTx Dither <sup>3)4)</sup><br>Amplitude Reg<br>= $08_{H}$ | I <sub>DAP-P</sub>   | 90.9  | 101                | 110.9 | mVpp | 100 mV setting<br>programmed<br>REF = 2.5V |  |

| 5.5.2.4  | OUTx Dither <sup>3)4)</sup><br>Amplitude Reg<br>= $0C_H$   | I <sub>DAP-P</sub>   | 141.4 | 151                | 161.4 | mVpp | 150 mV setting<br>programmed<br>REF = 2.5V |  |