## Programmable True power on sensor Data Sheet Version 1.1

## **TLE4983C-HTN E6747**

## Features

- TPO True Power On functionality

- Increased BTPO range

- Mono-cell chopped Hall system

- TIM Twisted Independent Mounting

- Dynamic self-calibrating algorithm

- End-of-line programmable switching points

- TC of back-bias magnet programmable

- High sensitivity and high stability of the magnetic switching points

- High resistance to mechanical stress

- Digital output signal (voltage interface)

- Short-circuit protection

- Module style package with two 4.7/47 nF integrated capacitors

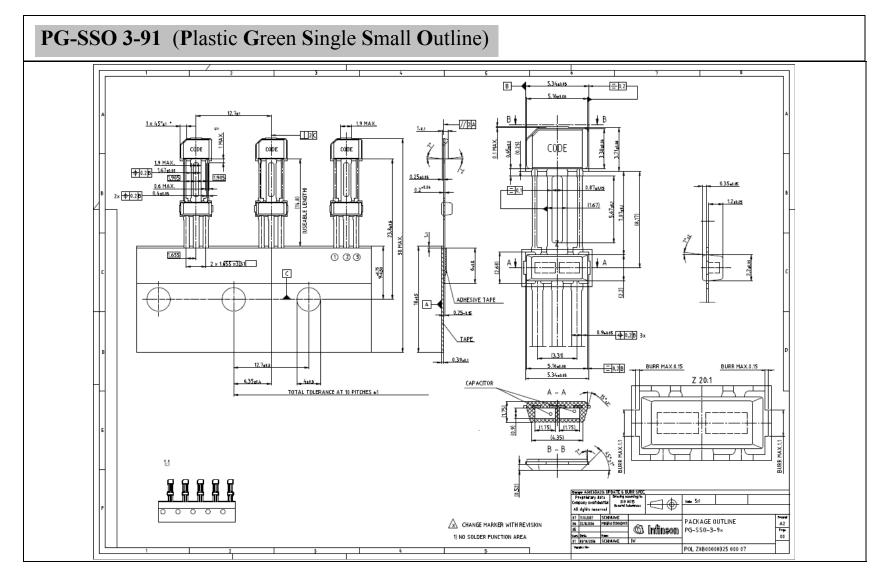

- Package: PG-SSO-3-91 with nickel plating

| Туре               | Marking | Ordering Code | Package     |

|--------------------|---------|---------------|-------------|

| TLE4983C-HTN E6747 | 83ACS3  | SP0003-74272  | PG-SSO-3-91 |

#### General information:

The TLE4983C is an active Hall sensor ideally suited for camshaft applications. Its basic function is to map either a tooth or a notch into a unique electrical output state. It has an electrical trimming option for post-fabrication trimming in order to achieve true power on capability even in the case of production spreads such as different magnetic configurations or misalignment. An additional self-calibration module has been implemented to achieve optimum accuracy during normal running operation. It comes in a three-pin package for the supply voltage and an open drain output.

#### Pin configuration PG-SSO-3-91

#### Pin definition and Function

| Pin No. | Symbol | Function          |

|---------|--------|-------------------|

| 1       | Vs     | Supply Voltage    |

| 2       | GND    | Ground            |

| 3       | Q      | Open Drain Output |

#### Functional description:

The basic operation of the TLE4983C is to map a "high positive" magnetic field (tooth) into a "low" electrical output signal and to map a "low positive" magnetic field (notch) into a "high" electrical output. Optionally the other output polarity can be chosen by programming the PROM. A magnetic field is considered as positive if the North Pole of a magnet shows towards the rear side of the IC housing. Since it seems that also backbias-reduced magnetic configurations still show significant flux densities in one distinct direction the circuit will be optimised for one flux direction in order to provide an optimal signal to noise behaviour.

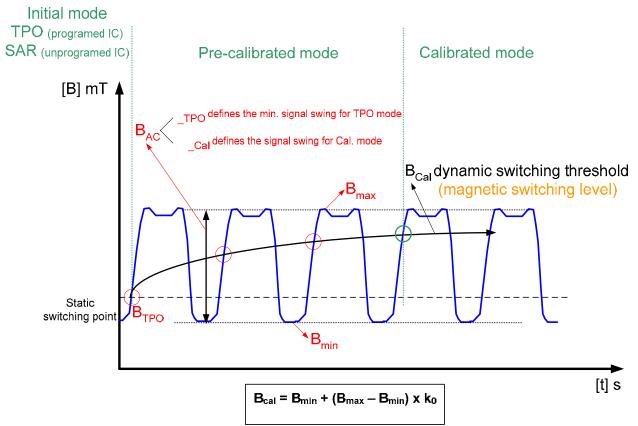

For understanding the operation of the TLE4983C three different modes have to be considered: Initial operation after power up: This mode will be referred to as "initial mode". Operation following the initialisation before having full information about the target wheel: This mode will be referred to as "precalibrated mode". Normal operation with running target wheel: This mode will be referred to as "calibrated mode".

#### Initial mode:

The magnetic information is derived from a chopped Hall amplifier. The threshold information comes from a PROM-register that may be programmed at any time, but only once (no EEPROM). The magnetic information is compared against the threshold and the output state is set correspondingly. Some hysteresis is introduced in order to avoid false switching due to noise.

In case that there is no PROM-value available (PROM has not been programmed before) the chip starts an auto-search for the actual magnetic value (SAR-mode). The initial threshold value is set to this magnetic value. This feature can be used to find a TPO-value for providing correct programming information to the chip simply by setting the chip in front of a well-defined static target. In this case a moving target wheel is not necessary.

In case there is a PROM value available, the open drain output will be turned on or off by comparing the magnetic field against the pre-programmed value.

During rotation of the target wheel a self-calibration procedure is started in the background. The IC memorises magnetic field values for adjusting the threshold to an optimum value. The exact way of threshold adjustment is described in more detail in the precalibrated mode.

#### Precalibrated mode:

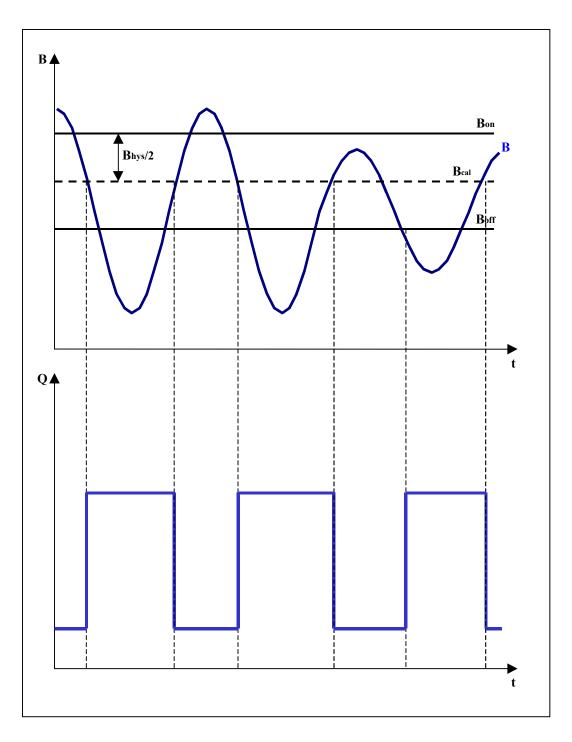

In the precalibrated mode the IC permanently monitors the magnetic signal. To say it in more detail, it searches for minimum (caused by a notch) and maximum (caused by a tooth) values in the signal. Once the IC has found a pair of min / max values it calculates the optimum threshold level and adjusts the system offset in such a way, that the switching occurs on this level. The internal offset update algorithm checks also the magnetical edge in that point in time when an offset update is to be released. Positive updates of the offset are released only at magnetic rising edges, negative offset updates only on magnetic falling edges. Otherwise an update on the wrong magnetic edge may cause additional switching. The threshold adjustment is limited to increments of approx. 15mT per calibration in order to avoid totally wrong information caused by large signal disturbances (EMC-events or similar). The optimum threshold level may differ depending on the target wheel. For example, for regular gearwheels the magnetic signal is close to a sinusoid and the optimum threshold value can be considered as 50% value, which is the mean value between minimum and maximum signal. For camshaft wheels an optimum threshold may be at a different percent-value in order to have minimum phase error over airgap variations. See fig.4 for definition of this dynamic switching level.

In case that the initial PROM-value does not lead to a switching of the IC because it is slightly out of the signal range the IC nevertheless does its switch value correction in the background. After having corrected for a sufficient amount the IC will start its output switching. The output switching includes some hysteresis in order to avoid false switching. During 16 switching events updates (number of updates depend on the magnetic signal) with 15mT are allowed.

Every valid<sup>1</sup> minimum or maximum will be considered. After the next 16 switching events a single update of max. 15mT (in both directions) is allowed.

For this single update the highest maximum and lowest minimum is taken into consideration.

If the IC has not been programmed yet, it uses the default 50% value between the minimum and the maximum as switching level.

<sup>&</sup>lt;sup>1</sup> Valid means signal detection with DNC

#### Calibrated mode:

After a certain number of switching events (32) the accuracy is considered to be quite high. At this time the chip is switched into an averaging mode (= calibrated mode) where only minor threshold corrections are allowed. In this mode a period of 32 switching events is taken to find the absolute minimum and maximum within this period. Threshold calculation is done with these minimum and maximum. A filter algorithm is implemented, which ensures that the threshold will only be updated, if the adjustment value calculated shows in the same direction over the last four consecutive periods. Every new calculated adjustment value that shows in the same direction causes an immediate update of the threshold value. If the direction of the calculated adjustment value changes, there must be again four consecutive adjustment values in the same direction for another update of the threshold value. Additionally there is an activation level implemented, allowing the threshold to be adjusted only if a certain amount (normally bigger than 1LSB) of adjustment is calculated. The threshold correction per cycle is limited to 1 LSB. The purpose of this strategy is to avoid larger offset deviations due to singular events. Also irregularities of the target wheel are cancelled out, since the minimum and maximum values are derived over at least one full revolution of the wheel. The output switching is done at the threshold level without visible hysteresis in order to achieve maximum accuracy. Nevertheless the chip has some internal protection mechanisms in order to avoid multiple switching due to noise.

#### Changing the mode:

Every time after power up the chip is reset into the initial mode. Subsequent modes (precalibrated, calibrated) are entered consequently as described before. In addition, two plausibility checks are implemented in order to enable some self-recovery strategy in case of unexpected events.

First, there is a watchdog, which checks for switching of the sensor at a certain lower speed limit. If for 12 seconds there is no switching at the output, the chip is reset into the initial mode.

Second, the IC checks if there is signal activity seen by the digital logic and if there is no outputswitching at the same time. If the digital circuitry expects that there should have been 4 switching events and actually no switching has occurred at the output, the IC is reset into the initial mode.

#### Reset:

There are several conditions, which can lead to a reset condition. For the IC behaviour we have to distinguish between a "output hold mode", a "long reset", a "short reset" and a "software reset".

#### Output hold mode:

This operating mode means that the output is held in the actual state and there is no reset on the digital part performed. This state will be released after the IC reaches his normal operation condition again and goes back into the operating mode he was before. The following conditions lead to the output hold mode:

• A drop in the supply voltage to a value less than 2.4V but higher than 2.0V for a time not longer than 1µs .. 2µs.

#### Long reset:

This reset means a total reset of the analogue as well as for the digital part of the IC. The output is forced to its default state ("high"). This condition remains for less than 1ms. After this time the IC is assumed to run in a stable condition and enters the initial mode where the output represents the state of the target wheel (PROM value). The following conditions lead to a long reset:

- Power-on condition.

- Low supply voltage: drop of the supply voltage to values less than 2.4V for a time longer than 1µs .. 2µs or drop of the supply voltage to values less than 2.0V.

#### Short reset:

This reset means a reset of the digital circuitry. The output memorizes the state he had before the reset. This condition remains for approx. 1µs. After that time the chip is brought into the initial mode (output stays "high" for approx. 200µs for an untrimmed IC). Then the output is released again and represents the state of the target wheel (PROM value). The following conditions lead to a short reset:

- Watchdog overflow: If there is no switching at the output for more than 12 seconds.

- If there are four min- or max-events found without a switching event at the output

#### Software reset:

This reset can be performed in the testmode through the serial-interface. The IC output is then used as data output for the serial interface.

The following condition lead to a software reset:

• There is a reset applied through the serial Interface

Table 1 shows an overview over the behaviour of the output under certain conditions.

|                    | Unprog                  | grammed  | Programmed       |                  |  |

|--------------------|-------------------------|----------|------------------|------------------|--|

|                    | Noninverted             | inverted | Noninverted      | Inverted         |  |

| output hold mode   | Q <sub>n-1</sub>        | -        | Q <sub>n-1</sub> | Q <sub>n-1</sub> |  |

| long reset         | High                    | -        | High             | High             |  |

| short reset        | High                    | -        | normal TPO       | inverted TPO     |  |

| initial mode       | high (self calibration) | -        | normal TPO       | inverted TPO     |  |

| precalibrated mode | Normal                  | -        | Normal           | Inverted         |  |

| calibrated mode    | Normal                  | -        | Normal           | Inverted         |  |

| Q <sub>n-1</sub> | state of output before a reset occurs                                      |

|------------------|----------------------------------------------------------------------------|

| normal TPO       | "Iow" if B>B <sub>TPO</sub> ; "high" if B <b<sub>TPO</b<sub>               |

| inverted TPO     | ·… "high" if B>B <sub>TPO</sub> ; "low" if B <b<sub>TPO</b<sub>            |

| normal           | … "Iow" if B>B <sub>Threshold</sub> ; "high" if B <b<sub>Threshold</b<sub> |

| inverted         | … "high" if B>B <sub>Threshold</sub> ; "low" if B <b<sub>Threshold</b<sub> |

|                  | Table1: Output behaviour under certain conditions                          |

#### Hysteresis concept:

There are two different hysteresis concepts implemented in the IC.

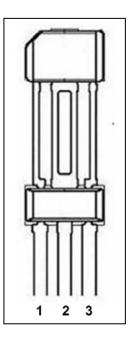

The first one is called *visible hysteresis*, meaning that the output switching levels are changed between two distinct values (depending on the direction of the magnetic field during a switching event), whenever a certain amount of the magnetic field has been passing through after the last switching event. The *visible hysteresis* is used in the precalibrated mode of unprogrammed sensors. See fig.1 for more details.

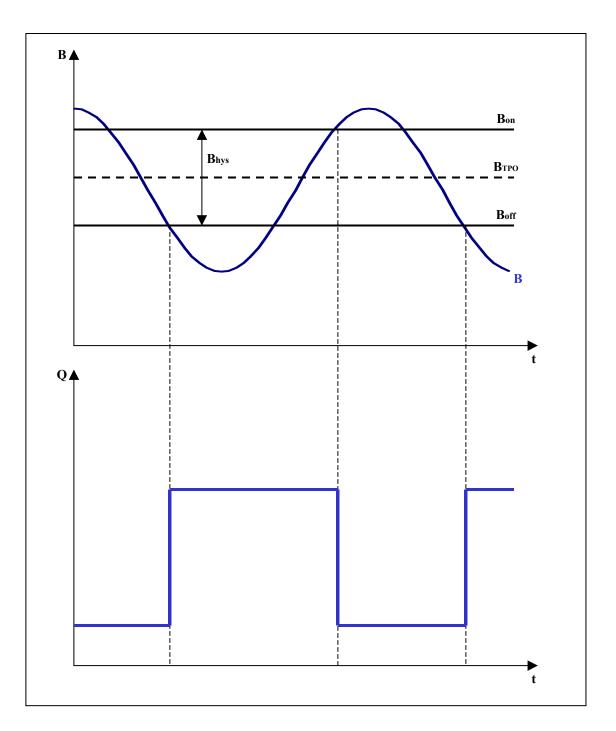

The second form of hysteresis is called *hidden hysteresis*. This means, that one cannot observe a hysteresis from outside. If the value of the switching level does not change, the output always switches at the same level. But inside the IC there are two distinct levels close above and below the switching level, which are used to arm the output. In other words if the value of the magnetic field crosses the lower of this hysteresis levels, then the output will be able to switch if the field crosses the switching level. After this switching event the output will be disabled until the value of the magnetic field crosses one of the two hysteresis levels. If it crosses the upper hysteresis level, then the output will be armed again and can switch if the magnetic field crosses the switching level. On the other hand, if the magnetic field does not reach the upper hysteresis level, but the lower hysteresis level will be crossed again after a switching event, then the output is allowed to switch, so that no tooth will be lost. But please notice that this causes an additional phase error. The *hidden hysteresis* is used for programmed sensors in precalibrated and calibrated mode. For more details see fig.2

## Fig. 1: Visible hysteresis valid for unprogrammed IC during precalibrated mode

## Fig. 2 Hidden hysteresis valid for programmed IC

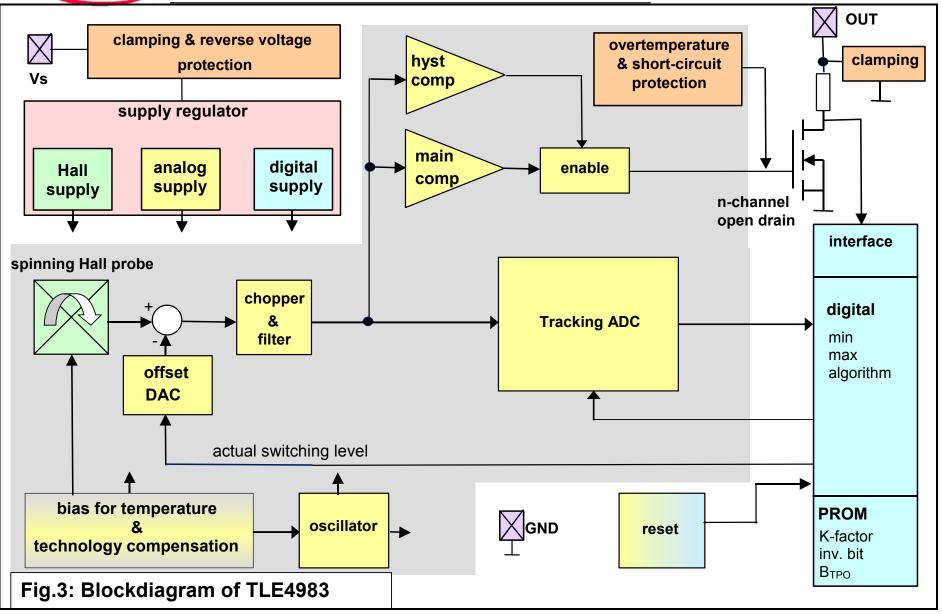

#### Block diagram:

The block diagram is shown in fig.3. The IC consists of a spinning Hall probe (monocell in the centre of the chip) with a chopped preamplifier. Next there is a summing node for threshold level adjustment. The threshold switching is actually done in the main comparator at a signal level of "0". This means, that the whole signal is shifted by this summing node in that way, that the desired switching level occurs at zero. This adjusted signal is fed into an A/D-converter. The converter feeds a digital calibration logic. This logic monitors the digitised signal by looking for minimum and maximum values and also calculates correction values for threshold adjustment. The static switching level is simply done by fetching a digital value out of a PROM. The dynamic switching level is done by calculating a weighted average of min and max value. For example, a factor of approximately 71% can be achieved by doubling the weight of the max value. Generally speaking, a threshold level of  $B_{cal} = B_{min} + (B_{max} - B_{min}) * k_0$  can be achieved by multiplying max with the switching level k<sub>0</sub> and min with (1-k<sub>0</sub>).

#### Serial interface:

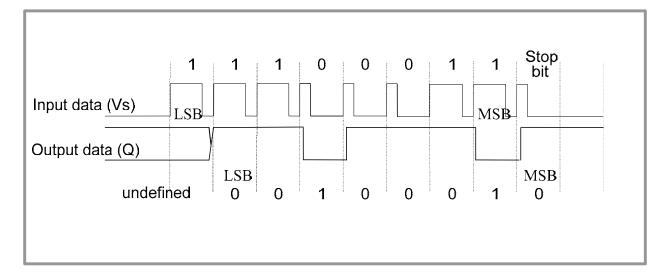

The serial interface is used to program the chip. At the same time it can be used to provide special settings and to read out several internal registers status bits. The interface description consists of a physical layer and a logical layer. The physical layer describes format, timing and voltage information, whereas the logical layer describes the available commands and the meaning of bits, words and addresses.

#### Physical interface layer:

The data transmission is done over the VS-pin, which generates input information and clock timing, and the out-pin Q, which delivers the output data. Generally the interface function is disabled; this means, that in normal operation including normal supply distortion the interface is not active and therefore the chip operates in its normal way. A special initialisation sequence must be performed to enter the interface mode that is also referred to as "testmode". There are two possible ways to achieve the testmode. They are called OpenPowerOn and OpenSyncVDD. For already programmed devices this initialisation procedures to testmode are not possible. The IC is still in test mode after programming the IC. It is possible to read out the programmed values as long as you do not leave the test mode.

OpenPowerOn: For a short time after power on or reset the chip monitors the output signal. The internal logic brings the output into a high impedance state, which will be a logical "high" caused by the external pull-up resistor. If now the chip sees a logical "low" (for at least 1ms), which is an output voltage lower than 0.3V, the chip enters the testmode.

Data transmission: Serial transmission is done in words (LSB first). A logical "1" is represented by a long (2/3 of one period) "high" voltage level (higher than 5V) on the supply followed by a short (1/3 of one period) "low" voltage level (lower than 5V), whereas a logical "0" is represented by a short "high" level on the supply followed by a long "low" level. At the same time this high/low voltage combination, which forms in fact a bit, acts as a serial interface clock which clocks out logical high / low values on the output. Due to the increased capacity a clocking period of 200µs is recommended (standard value for 4.7nF capacitor: 100µs).

See fig.5 for a more detailed timing diagram. End of word is indicated by a long (we recommend longer than 200µs, first 30µs should be higher than 5V and the rest lower than 5V) "low" supply. Please note, that for communicating 13 bits of data 14 VS-pulses are necessary. If more than 14 input bits are transmitted the output bits are irrelevant (transmission buffer empty) whereas the input bits remain valid and start overwriting the previously transmitted bits. In any case the last 14 transmitted bits are interpreted as transmitted data word (13 bits) + 1 stop bit. End of communication is signalled by a long "high" voltage level. A new communication has to be set up by a new initialisation sequence.

#### **Programming the PROM:**

One possibility for programming the static threshold value is to run the IC on a testbench (or in the car), to wait until the IC has reached the calibrated mode and then simply to issue the copy commands, which transfers the calibrated threshold value into the PROM.

Use the following procedure for this type of programming:

- 1) Apply an oscillating magnetic field with a suitable offset (Notice that for unfused devices this offset lies in the middle of the maximum and minimum value of the magnetic field).

- 2) Enter the testmode with the second procedure described in the chapter "Physical interface layer".

- 3) Wait until the IC has reached the calibration mode.

- 4) Choose a k-factor and supply a programming current to the output. For details see document: "How to program TLE498x".

- 5) Write the two following bit-combinations via the serial interface:

#### 101XXXXXk<sub>2</sub>k<sub>1</sub>k<sub>0</sub>l1 1011111111111

Here ki indicate the 3bits of the k-factor (k2 … MSB and k0 … LSB) in dual-code. This means: XXXX111 is equal to k0=0.7734 and XXXX011 is equal to k0=0.5234. The bit I is the so called Inverting bit, which determines either the output switches inverse to the applied magnetic field (I="0") or not (I="1").

6) Leave the testmode by writing a long "high" voltage level.

A second form of programming the static threshold value is to bring the IC in front of a target, which delivers a static magnetic field with a suitable strength and perform a power on by forcing the output to a low state for at least 1ms. This brings the chip in the testmode and he starts immediately a successive approximation and adjusts the value of the offset-DAC to the switching level that corresponds to the field strength.

Use the following procedure for this type of programming:

- 1) Apply a static magnetic field with a suitable strength.

- 2) Enter the testmode with the first procedure described in the chapter "Physical interface layer".

- 3) Wait until the IC has made the successive approximation and reached the right level for the offset-DAC (at least 10 periods of the internal clock frequency after releasing the output).

- 4) Choose a k-factor and supply a programming current to the output. For details see document: "How to program TLE498x".

- 5) Write the two following bit-combinations via the serial interface:

101XXXXXk<sub>2</sub>k<sub>1</sub>k<sub>0</sub>l1 1011111111111

Here ki indicate the 3bits of the k-factor (k2 ... MSB and k0 ... LSB) in dual-code. This means: XXXX111 is equal to k0=0.7734 and XXXX011 is equal to k0=0.5234. The bit I is the so called Inverting bit, which determines either the output switches inverse to the applied magnetic field (I="0") or not (I="1").

6) Leave the testmode by writing a long "high" voltage level.

It has to be noted that the chip has increased power dissipation during programming the PROM/fuses. The additional power is taken out of the output. Due to the PROM can not be tested during the sensor production please be aware that there is natural programming yield loss.

Furthermore there may be an influence from the programming equipment. Please contact your local technical support for more details or see document: "How to program TLE498x".

#### Overvoltage protection:

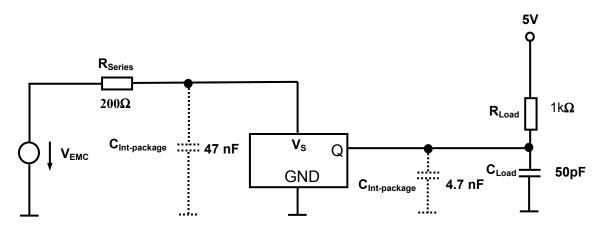

The process used for production has a breakthrough voltage of approximately 27.5V. The chip can be brought into breakthrough without damage if the breakthrough power (current) is limited to a certain value. Usually destruction is caused by overheating the device. Therefore for short pulses the breakthrough power can be higher than for long duration stress. For example for load dump conditions an external protection resistor of 200  $\Omega$  is recommended in 12V-systems and 50  $\Omega$  in 5V-systems.

Fig. 4: Dynamic threshold value

### Absolute maximum ratings:

| Symbol         | Name                            |      |     |     |      |                                                                                  |

|----------------|---------------------------------|------|-----|-----|------|----------------------------------------------------------------------------------|

|                |                                 | min  | typ | max | Unit | Note                                                                             |

| Vs             | supply voltage                  | -18  |     | 18  | V    |                                                                                  |

|                |                                 | -24  |     | 24  | V    | 1h with $R_{Series}$ >=200 $\Omega^2$                                            |

|                |                                 | -26  |     | 26  | V    | 5min with $R_{Series}$ >=200 $\Omega^{1}$                                        |

|                |                                 | -28  |     | 28  | V    | 1min with $R_{\text{Series}} \ge 200 \Omega^1$                                   |

| V <sub>Q</sub> | output OFF voltage              | -0.3 |     | 18  | V    |                                                                                  |

|                |                                 | -18  |     | 24  | V    | 1h with $R_{Load}$ >=500 $\Omega$                                                |

|                |                                 | -18  |     | 26  | V    | 5min with $R_{Load}$ >=500 $\Omega$                                              |

|                |                                 | -1.0 |     |     | V    | 1h without R <sub>Load</sub>                                                     |

| $V_{Q}$        | output ON voltage               |      |     | 16  | V    | current internal limited by short circuit protection (72h@T <sub>A</sub> <40°C)  |

|                |                                 |      |     | 18  | V    | current internal limited by short circuit protection (1h@T <sub>A</sub> <40°C)   |

|                |                                 |      |     | 24  | V    | current internal limited by short circuit protection (1min@T <sub>A</sub> <40°C) |

| Ι <sub>Q</sub> | continuous output current       | -50  |     | 50  | mA   |                                                                                  |

| Tj             | junction temperature            | -40  |     |     | °C   |                                                                                  |

|                |                                 |      |     | 155 | °C   | 5000h (not additive)                                                             |

|                |                                 |      |     | 165 | °C   | 2500h (not additive)                                                             |

|                |                                 |      |     | 175 | °C   | 500h (not additive)                                                              |

|                |                                 |      |     | 195 | °C   | 10x1h (additive to the other life times)                                         |

| $R_{thJA}$     | thermal resistance junction-air |      |     | 190 | K/W  |                                                                                  |

| Ts             | storage temperature             | -50  |     | 150 | °C   |                                                                                  |

| В              | magnetic field induction        |      |     |     | mT   | no limit                                                                         |

Note: Stresses above those listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD** Protection

| Parameter        | Symbol           | max | Unit | Remarks                                                              |

|------------------|------------------|-----|------|----------------------------------------------------------------------|

| ESD – protection | $V_{\text{ESD}}$ | ± 4 | kV   | According to standard EIA/JESD22-<br>A114-B, Human Body Model (HBM). |

<sup>&</sup>lt;sup>2</sup> Accumulated life time

## Operating range:

| Symbol              | Name                                         |       |       |                             |                                                                                                                                       |

|---------------------|----------------------------------------------|-------|-------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

|                     |                                              | min   | max   | Unit                        | Note                                                                                                                                  |

|                     |                                              | 3.3   | 18    | V                           | Continuous                                                                                                                            |

| Vs                  | operating supply<br>voltage                  |       | 24    | V                           | 1h with R <sub>Series</sub> >=200Ω;<br>extended limits for<br>parameters in characteristics                                           |

|                     | , onage                                      |       | 26    | V                           | 5min with R <sub>Series</sub> >=200Ω;<br>extended limits for<br>parameters in characteristics                                         |

|                     |                                              | -40   |       | С°                          |                                                                                                                                       |

|                     |                                              |       | 155   | °C                          | 5000h (not additive)                                                                                                                  |

| Тj                  | operating junction                           |       | 165   | °C                          | 2500h (not additive)                                                                                                                  |

| J                   | temperature                                  |       | 175   | °C                          | 500h (not additive) reduced<br>signal quality permittable<br>(e.g. jitter)                                                            |

| T <sub>cal</sub>    | trimming temperature                         | 15    | 35    | °C                          | V <sub>S</sub> =5/12V                                                                                                                 |

| Ι <sub>Q</sub>      | continuous output ON<br>current              | 0     | 20    | mA                          | V <sub>Qmax</sub> =0.5V                                                                                                               |

| V <sub>Q</sub>      | continuous output OFF                        | -0.3  | 18    | V                           | Continuous                                                                                                                            |

|                     | voltage                                      | -0.3  | 24    | V                           | 1h with $R_{Load}$ >=500 $\Omega$                                                                                                     |

| f <sub>B</sub>      | magnetic signal switching frequency          | 0     | 5     | kHz                         | Measured between two rising edges of the magnetic signal                                                                              |

| t <sub>edge</sub>   | rise time of magnetic<br>edge                | 85    |       | μs                          | Magnetic signal edge is not<br>allowed to rise faster<br>(otherwise tracking ADC is<br>not able to follow)                            |

| В                   | magnetic switching<br>level range            | -13   | 91    | mT                          |                                                                                                                                       |

| B <sub>TPO</sub>    | true power on range                          | -13   | 91    | mT                          | Allowed programmable TPO-<br>values; Hysteresis not<br>included (typ. B <sub>Hys</sub> =1mT)                                          |

| B <sub>AC_TPO</sub> | magnetic signal swing<br>for TPO-function    | 6     | 80    | mT <sub>pp</sub>            | B <sub>тРО</sub> =33mT<br>В <sub>НҮЅ</sub> = 0.75mT <sup>3</sup>                                                                      |

| $B_{AC\_cal}$       | magnetic signal swing<br>for calibrated mode | 3     | 80    | mT <sub>pp</sub>            |                                                                                                                                       |

| B <sub>over</sub>   | magnetic overshoot                           |       | 10    | % of $B_{ACcal}$            |                                                                                                                                       |

| k <sub>o</sub>      | adjustment range of switching level          | 33.59 | 77.34 | % of<br>B <sub>AC_cal</sub> | Switching point in calibrated<br>mode is determined by:<br>$B_{cal} = B_{min} + (B_{max} - B_{min}) * k_0$<br>$k_0$ step size = 6.25% |

$<sup>^3</sup>$  Encapsulated devices with  $B_{TPO}\!\!=\!\!44mT$  and  $B_{HYS}\!\!=\!\!0.5mT\,$  show minimum value of  $5mT_{pp}$

| Symbol             | Name                                                           |       |      |       |                                                                 |

|--------------------|----------------------------------------------------------------|-------|------|-------|-----------------------------------------------------------------|

|                    |                                                                | min   | max  | Unit  | Note                                                            |

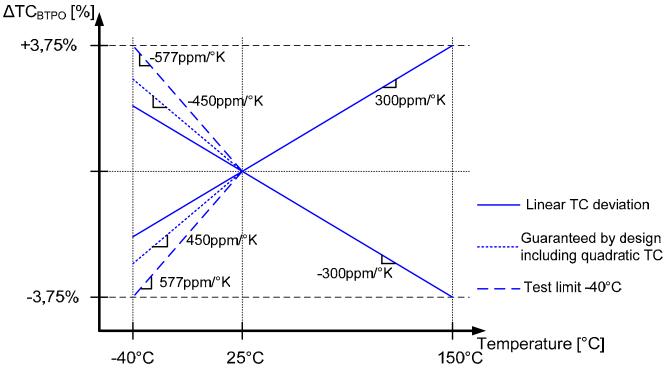

| TC <sub>BTPO</sub> | Programmable<br>temperature coefficient<br>of B <sub>TPO</sub> | -1200 | 0    | ppm/K | Range to compensate<br>TC <sub>magnet</sub> , typical -825ppm/K |

| ATC                | Deviation to<br>programmed                                     | -300  | 300  | ppm/K | Linear TC deviation<br>-40°C to 150°C <sup>1</sup>              |

| $\Delta TC_{BTPO}$ | temperature coefficient<br>of B <sub>TPO</sub>                 | -3.75 | 3.75 | %     | At -40°C and 150°C<br>See figure 6                              |

$^{1}\pm450$  ppm/K @ -40°C guaranteed by design refered to second order TC<sub>BTPO</sub> compensation. Furthermore this compensation comprises the adjustment to second order effect of magnet

Figure 6: Deviation to programmed temperature coefficient of BTPO

## AC/DC characteristics:

| Symbol               | Name                                                       |            |                   |            |          |                                                                                                                              |

|----------------------|------------------------------------------------------------|------------|-------------------|------------|----------|------------------------------------------------------------------------------------------------------------------------------|

|                      |                                                            | min        | typ               | max        | Unit     | Note                                                                                                                         |

| V <sub>Qsat</sub>    | output saturation voltage                                  |            | 0.25              | 0.5        | V        | I <sub>Q</sub> = 20mA                                                                                                        |

| I <sub>Qleak</sub>   | output leakage current                                     |            | 0.1               | 10         | μA       | V <sub>Q</sub> = 18V                                                                                                         |

| I <sub>Qshort</sub>  | currentlimit for shortcircuit protection                   | 30         | 50                | 80         | mA       |                                                                                                                              |

| T <sub>prot</sub>    | junction temperature limit for output protection           | 195        | 210               | 230        | °C       |                                                                                                                              |

| t <sub>rise</sub> 4  | output rise time                                           | 4          | 11                | 17         | μs       | $V_{Load}$ = 4,524V<br>$R_{Load}$ = 1k $\Omega$ , C <sub>Load</sub> = 4,7nF<br>included in package                           |

| t <sub>fall</sub> 5  | output fall time                                           | 1.4<br>2.4 | 2.4<br>4          | 3.4<br>5.6 | μs<br>µs | $V_{Load} = 5V;$<br>$V_{Load} = 12V;$<br>$R_{Load} = 1k\Omega, C_{Load} = 4,7nF$<br>included in package                      |

| I <sub>SVmin</sub>   | supply current @ 3.2V                                      |            | 6                 | 7          | mA       | $V_s$ = 3.2V; extended limits for parameters in characteristics                                                              |

| I <sub>SV</sub>      | supply current @ 3.3V                                      |            | 6                 | 7          | mA       | V <sub>S</sub> = 3.3V;                                                                                                       |

| I <sub>S</sub>       | supply current                                             |            | 5.6               | 7.5        | mA       |                                                                                                                              |

| I <sub>smax</sub>    | supply current @ 24V                                       |            |                   | 8.0        | mA       | R <sub>Series</sub> >=200Ω                                                                                                   |

| $V_{\text{Sclamp}}$  | Clamping voltage V <sub>S</sub> -Pin                       | 24         | 27.5              |            | V        | 1mA through clamping device                                                                                                  |

| $V_{\text{Qclamp}}$  | Clamping voltage Q-Pin                                     | 24         | 27.5              |            | V        | 1mA through clamping device                                                                                                  |

| $V_{\text{Sreset}}$  | Analog reset voltage                                       |            | 2.35              | 2.9        | V        |                                                                                                                              |

| t <sub>on</sub>      | power on time                                              |            | 0.56 <sup>6</sup> | 1          | ms       | Time to achieve specified                                                                                                    |

|                      |                                                            |            | 0.75 <sup>8</sup> |            | ms       | accuracy. During this time the output is locked <sup>7</sup>                                                                 |

| t <sub>d</sub> 9     | delay time of output to magnetic<br>edge                   | 8          | 15                | 22         | μs       | Higher magnetic slopes and overshoots reduce t <sub>d</sub> , because the signal is filtered internal. <sup>10</sup>         |

| $\Delta t_{d}$       | temperature drift of delay time of output to magnetic edge | -3.6       |                   | 3.6        | μs       | not additional to t <sub>d</sub>                                                                                             |

| n <sub>watch</sub>   | watchdog edges                                             |            | 4                 |            | -        | If n <sub>watch</sub> min or max-events have<br>been found and there was no<br>change at the output a reset is<br>performed. |

| $\mathbf{t}_{watch}$ | watchdog time                                              |            | 12                |            | s        | If there is no output change during t <sub>watch</sub> a reset is performed                                                  |

<sup>&</sup>lt;sup>4</sup> value of capacitor: 4.7nF±10%;(excluded drift due to temperature and over lifetime); ceramic: X8R; maximum voltage: 50V

$<sup>^{5}</sup>$  value of capacitor: 4.7nF±10%;(excluded drift due to temperature and over lifetime); ceramic: X8R; maximum voltage: 50V

<sup>&</sup>lt;sup>6</sup> trimmed IC.

<sup>&</sup>lt;sup>7</sup> output is in high-state.

<sup>&</sup>lt;sup>8</sup> untrimmed IC.

<sup>&</sup>lt;sup>9</sup> measured at  $T_j = 25^{\circ}$ C; represents the influence of the production spread (corresponds to the 3 $\sigma$ -value).

<sup>&</sup>lt;sup>10</sup> measured with a sinusoidal-field magnetic-field with 10mTpp and a frequency of 1kHz.

| Symbol                 | Name                                                      |       |       |       |      |                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------|-----------------------------------------------------------|-------|-------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |                                                           | min   | typ   | max   | Unit | Note                                                                                                                                                                                                                                                                                                                                                                                        |

| f <sub>clk</sub>       | clock frequency for digital part                          |       | 1.76  |       | MHz  |                                                                                                                                                                                                                                                                                                                                                                                             |

| f <sub>chopper</sub>   | clock frequency used by the chopper<br>preamplifier       |       | 220   |       | kHz  | output jitter is not affected by the chopper frequency                                                                                                                                                                                                                                                                                                                                      |

| $\Delta k_0$           | resolution of switching level<br>adjustment               |       | 6.25  |       | %    |                                                                                                                                                                                                                                                                                                                                                                                             |

| B <sub>Offset</sub>    | internal offset                                           | -2.2  | ±0.35 | 2.2   | mT   | Typ. value corresponds 1σ                                                                                                                                                                                                                                                                                                                                                                   |

| FSR <sub>ODAC</sub>    | full scale range of the offset-DAC                        | 104   | 130   | 162.5 | mT   | Typ. B <sub>ODAC_0</sub> = -16.3mT<br>Typ. B <sub>ODAC_1023</sub> = 113.8mT                                                                                                                                                                                                                                                                                                                 |

| FSR <sub>ODACtyp</sub> | full scale range of the offset-DAC                        | 112.7 | 130   | 152.8 | mT   | T <sub>j</sub> =25°C                                                                                                                                                                                                                                                                                                                                                                        |

| $B_{TPO\_res}$         | resolution of programmable<br>threshold in TPO mode       |       | 0.13  |       | mT   |                                                                                                                                                                                                                                                                                                                                                                                             |

| $\Delta B_{TPO}$       | drift of B <sub>TPO</sub> -point                          | -2    |       | +3.4  | mT   | B <sub>TPO</sub> =33mT <sup>11</sup>                                                                                                                                                                                                                                                                                                                                                        |

| $\Delta B_{AC\_cal}$   | accuracy of threshold in calibration<br>mode              | -2    |       | 2     | %    | percentage of $B_{AC}$ ; $B_{AC}$ =10mT <sub>pp</sub> sinusoidal signal <sup>12</sup> ; systematic deviation due to hysteresis in the filter algorithm of 1.5% at $B_{AC}$ =10mT <sub>pp</sub> not included;                                                                                                                                                                                |

| B <sub>neff</sub>      | effective noise value of the magnetic<br>switching points |       | 33    |       | μΤ   | $T_j = 25^{\circ}C$ ; The magnetic noise is<br>normal distributed, nearly<br>independent to frequency and<br>without sampling noise or digital<br>noise effects. The typical value<br>represents the rms-value here<br>and corresponds therefore to $1\sigma$<br>probability of normal distribution.<br>Consequently a $3\sigma$ value<br>corresponds to 0.3% probability<br>of appearance. |

|                        |                                                           |       | 55    | 120   | μT   | The typical value corresponds to<br>the rms-value at $T_j = 175$ °C.<br>The max value corresponds to<br>the rms-values in the full<br>temperature range and includes<br>technological spreads.                                                                                                                                                                                              |

Note: The listed AC/DC and magnetic characteristics are ensured over the operating range of the integrated circuit. Typical characteristics specify mean values expected over the production spread. If not other specified, typical characteristics apply at  $T_j$  = 25 °C and  $V_S$  = 12 V.

<sup>&</sup>lt;sup>11</sup> This value shows the deviation from the programmed  $B_{TPO}$  value and its temperature coefficient. Included are the package-effect, the deviation from the adjusted temperature coefficient of the  $B_{TPO}$  point (resolution of the temperature coefficient and spread of the technologie) and the drift of the offset (over temperature and lifetime). Not included is the hysteresis in the initial mode. Included are the package-effect, the deviation from the adjusted temperature coefficient of the  $B_{TPO}$  point (resolution of the temperature coefficient and spread of the technologie) and the drift offset (over temperature coefficient of the  $B_{TPO}$  point (resolution of the temperature coefficient and spread of the technologie) and the drift of the offset (over temperature and lifetime). Not included is the hysteresis in the initial mode.

<sup>&</sup>lt;sup>12</sup> bigger amplitudes of signal lead to smaller values of  $\Delta B_{AC_{cal}}$ .

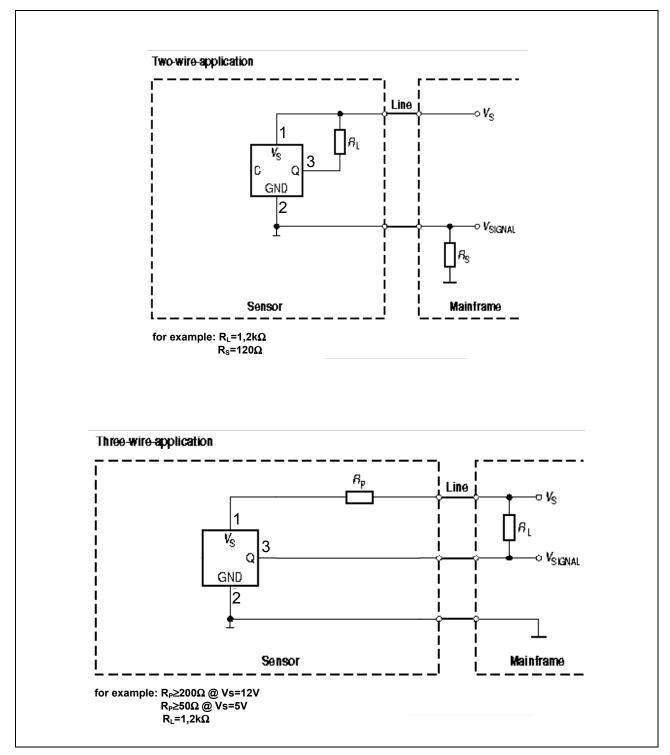

## **Application circuit**

## Figure 7 Application Circuits TLE4983C

## Electro Magnetic Compatibility - (values depend on R<sub>Series</sub>)

Additional Information:

Characterisation of Electro Magnetic Compatibility are carried out on sample base of one qualification lot. Not all specification parameters have been monitored during EMC exposure. Only key parameters e.g. switching current and duty cycle have been monitored.

Ref. ISO 7637-1; see test circuit of figure 8;

$\Delta B_{PP}$  = 10mT (ideal sinusoidal signal); V<sub>S</sub>=13.5V ± 0.5V, f<sub>B</sub>= 1000Hz; T= 25°C; R<sub>Series</sub> ≥ 200 $\Omega$ ;

| Parameter    | Symbol           | Level/typ  | Status          |

|--------------|------------------|------------|-----------------|

| Testpulse 1  | V <sub>EMC</sub> | IV / -100V | С               |

| Testpulse 2  |                  | IV / 100V  | A <sup>13</sup> |

| Testpulse 3a |                  | IV / -150V | А               |

| Testpulse 3b |                  | IV / 100V  | А               |

| Testpulse 4  |                  | IV / -7V   | А               |

Ref. ISO 7637-2; 2<sup>nd</sup> edition 06/2004 see test circuit of figure 8;

$\Delta B_{PP}$  = 2mT (amplitude sinus signal); V<sub>S</sub>=13.5V ± 0.5V, f<sub>B</sub>= 1000Hz; T= 25°C; R<sub>Series</sub> ≥ 200 $\Omega$ ;

| Parameter    | Symbol           | Level/typ  | Status          |

|--------------|------------------|------------|-----------------|

| Testpulse 2a | V <sub>EMC</sub> | IV / 40V   | А               |

| Testpulse 5a |                  | IV / 86.5V | С               |

| Testpulse 5b |                  | IV / 86.5V | A <sup>14</sup> |

Note: Test criteria for status A: No missing pulse no additional pulse on the IC output signal plus duty cycle and jitter are in the specification limits.

Test criteria for status B: No missing pulse no additional pulse on the IC output signal. (Output signal "OFF" means switching to the voltage of the pull-up resistor). Test criteria for status C: One or more parameter can be out of specification during the exposure but returns automatically to normal operation after exposure is removed.

Test criteria for status E: destroyed.

<sup>&</sup>lt;sup>13</sup> Valid during Vs is applied afterwards Status C, current consumption may be out of spec during testpulse

<sup>&</sup>lt;sup>14</sup> Suppressed Us\*=35V

#### Ref. ISO 7637-3; TP 1 and TP 2 ref. DIN 40839-3; see test circuit of figure 8;

| $\Delta B_{PP}$ = 10mT (ideal sinusoidal signal); V <sub>S</sub> =13.5V ± 0.5V, f <sub>B</sub> = 1000Hz; T= 25°C; F | $R_{Series} \ge 200\Omega;$ |

|---------------------------------------------------------------------------------------------------------------------|-----------------------------|

|---------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Parameter    | Symbol           | Level/typ | Status |

|--------------|------------------|-----------|--------|

| Testpulse 1  | V <sub>EMC</sub> | IV / -30V | А      |

| Testpulse 2  |                  | IV / 30V  | А      |

| Testpulse 3a |                  | IV / -60V | A      |

| Testpulse 3b |                  | IV / 40V  | А      |

Ref. ISO 11452-3; see test circuit of figure 8; measured in TEM-cell;

$\Delta B_{PP}$  = 4mT (ideal sinusoidal signal); V<sub>S</sub>=13.5V ± 0,5V, f<sub>B</sub>= 200Hz; T= 25°C; R<sub>Series</sub> ≥ 200 $\Omega$ ;

| Parameter          | Symbol                | Level/max   | Remarks         |

|--------------------|-----------------------|-------------|-----------------|

| EMC field strength | E <sub>TEM-Cell</sub> | IV / 200V/m | AM=80%, f=1kHz; |

Note: Stresses above those listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Test condition for the trigger window:  $f_{B-field}=200Hz$ ,  $B_{pp}=4mT$ , vertical limits are  $\pm 200mV$  and horizontal limits are  $\pm 200\mu s$ .

Figure 8: Testcircuit for EMC-tests

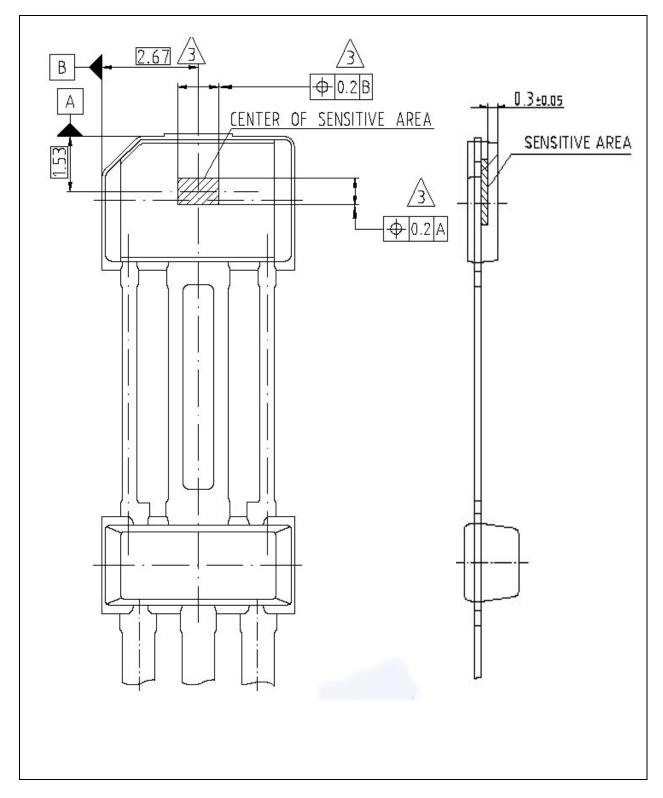

## Package Dimensions

## Position of the Hall Element

## Appendix:

#### Calculation of mechanical errors:

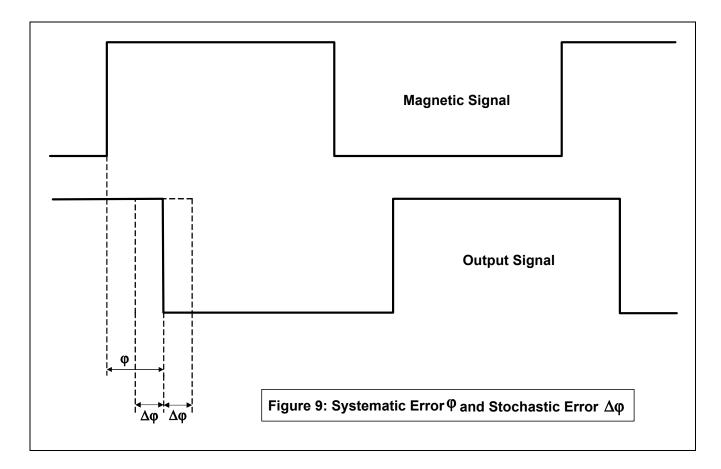

## Systematic Phase Error $\phi$

The systematic error comes in because of the delay-time between the threshold point and the time when the output is switching. It can be calculated as follows:

$$\varphi = \frac{360^\circ \bullet n}{60} \bullet t_d$$

- $\phi$  ... systematic phase error in °

- n ... speed of the camshaft-wheel in min<sup>-1</sup>

- $t_d$  ... delay time (see specification) in  $\mathit{sec}$

#### Stochastic Phase Error $\Delta \phi$

The stochastic phase error includes the error due to the variation of the delay time with temperature and the error caused by the resolution of the threshold. It can be calculated in the following way:

| $\Delta \varphi_d = \frac{360^\circ \bullet n}{60} \bullet \Delta t_d$                  |  |

|-----------------------------------------------------------------------------------------|--|

| $\Delta \varphi_{cal} = \frac{\partial \varphi}{\partial B} \bullet \Delta B_{AC\_cal}$ |  |

| 10                                    | •••         | stochastic phase error due to the variation of the delay time over temperature in ° stochastic phase error due to the resolution of the threshold value in ° |

|---------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>n</b>                              | ····<br>··· | speed of the camshaft wheel in <i>min<sup>-1</sup></i>                                                                                                       |

| $\frac{\partial \varphi}{\partial B}$ |             | inverse of the magnetic slope of the edge in $^{\circ}/T$                                                                                                    |

| $\Delta t_{d} \ \Delta B_{AC\_cal}$   |             | variation of delay time over temperature in <i>sec</i> accuracy of the threshold in <i>T</i>                                                                 |

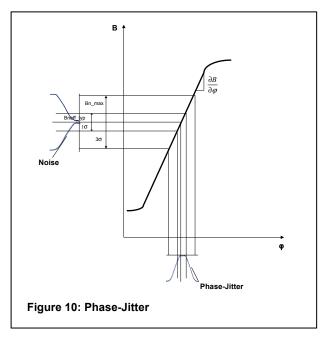

#### **Jitter (Repeatability)**

The phase jitter is normally caused by the analogue system noise. If there is an update of 1bit of the offset-DAC due to the algorithm, what could happen after a period of 16 teeth, then an additional step in the phase occurs (see description of the algorithm). This is not included in the following calculations. The noise is transformed through the slope of the magnetic edge into a phase error. The phase jitter is determined by the two formulas:

$$\varphi_{Jitter\_typ} = \frac{\partial \varphi}{\partial B} \bullet \left( B_{neff\_typ} \right)$$

$$\varphi_{Jitter\_max} = \frac{\partial \varphi}{\partial B} \bullet \left( B_{n\_max} \right)$$

| ΦJitter_typ<br>ΦJitter_max                  | <br>typical phase jitter at Tj=25°C in ° (1Sigma)<br>maximum phase jitter at Tj=175°C in ° (3Sigma) |                                                                   |  |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|

| $\frac{\partial \varphi}{\partial B}$       | <br>inverse of the magnetic slo                                                                     | pe of the edge in $^{\circ}/T$                                    |  |

| B <sub>neff_typ</sub><br>B <sub>n_max</sub> | <br>typical value of B <sub>neff</sub> in <i>T</i><br>maximum value of B <sub>n</sub> in <i>T</i>   | (1 $\sigma$ -value at Tj=25°C)<br>(3 $\sigma$ -value at Tj=175°C) |  |

## Example:

| Assumption:  | n = 3000 min <sup>-1</sup><br>$t_d = 14 \ \mu s$<br>$\Delta t_d = \pm 3 \ \mu s$<br>$\frac{\partial B}{\partial \varphi} = 1 \ mT/^{\circ}$<br>$\Delta B_{AC\_cal} = \pm 0.2 \ mT (=2)$<br>$B_{neff\_typ} = \pm 33 \ \mu T$ (1 $\sigma$ -B <sub>n\_max</sub> = $\pm 360 \ \mu T$ (3 $\sigma$ - | value at     | Г=25°С)                                                                                                                                                                                                                                                |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Calculation: |                                                                                                                                                                                                                                                                                                | <br><br><br> | systematic phase error<br>stochastic phase error due to delay time variation<br>stochastic phase error due to accuracy of the threshold<br>typical phase jitter (1 $\sigma$ -value at Tj=25°C)<br>maximum phase jitter (3 $\sigma$ -value at Tj=175°C) |

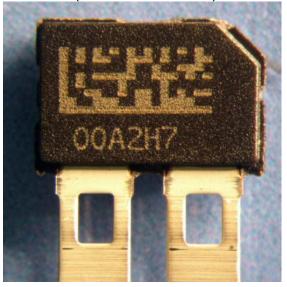

#### Appendix A: Marking & data matrix code information:

*Product is RoHS (restriction of hadzardous substances) compliant when marked with letter "G" in front or after the date code marking.*

As mentioned in information note N° **136/03** a data matrix code with 8x18 fields according to the ECC200 standard may be used for TLE4983C. Furthermore the marking technique on the front side of the device may be changed from a mask to a writing laser equipment. The information content (date code and device type) will hereby not be changed.

Please refer to you Key account team or regional sales responsible if you need further information

Example for data matrix code (rear side of sensor):

Comparison between mask writing vs. new laser writing (TLE 4941):

# Writing Lasering

| Revisior | n History:                         | Version 1.1 |  |  |  |

|----------|------------------------------------|-------------|--|--|--|

| Previous | Previous Version: 1.1              |             |  |  |  |

| 23       | Change: new package outline figure |             |  |  |  |

| 25       | Old package outline figure erased  |             |  |  |  |

|          |                                    |             |  |  |  |

|          |                                    |             |  |  |  |

|          |                                    |             |  |  |  |

|          |                                    |             |  |  |  |

|          |                                    |             |  |  |  |

|          |                                    |             |  |  |  |

|          |                                    |             |  |  |  |

|          |                                    |             |  |  |  |

Infineon Technologies AG © Infineon Technologies AI SC All Rights Reserved.

http://www.infineon.com/products/sensors

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: Sensors@infineon.com

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Infineon: TLE4983C-HT E6747 TLE4983C-HTN E6747