# PSoC<sup>™</sup> 4 HVPA-144K

Based on 32-bit Arm® Cortex®-M0+

## **General description**

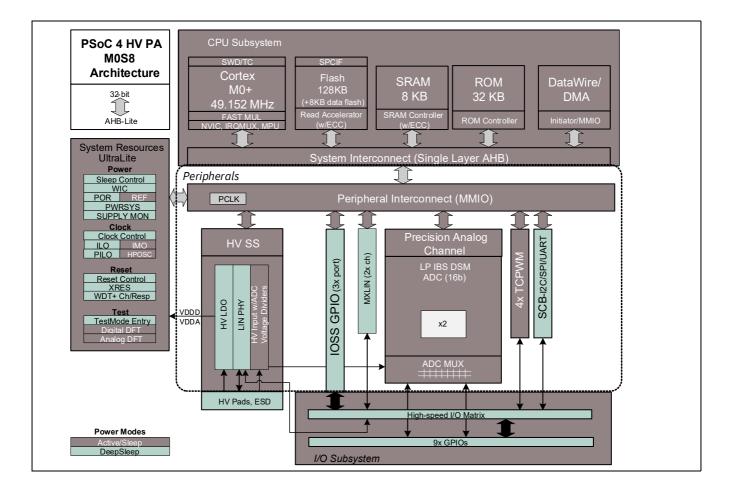

PSoC<sup>™</sup> 4 High Voltage Precision Analog (HVPA)-144K is a fully integrated programmable embedded system for lead acid battery monitoring and management. The system features an Arm<sup>®</sup> Cortex<sup>®</sup> M0+ processor and programmable and reconfigurable analog and digital blocks.

### Features

- Automotive Electronics Council (AEC) AEC-Q100 qualified

- 32-bit MCU subsystem

- 24- or 48-MHz Arm® Cortex® M0+ CPU with DMA controller

- Up to 128 KB of code flash with ECC

- Up to 8 KB of data flash with ECC

- Up to 8 KB of SRAM with ECC

- 1 KB of supervisory flash (SFlash) available for storing constants

- Precision analog

- Two precision  $\Delta\Sigma$  ADCs (16-20+ bits)

- Current channel with automatic gain

- Voltage channel with HV input divider

- Temperature and diagnostic channels

- Supports both internal and external temperature sensing

- Digital filtering, accumulators, and threshold comparisons on all channels

- High-voltage subsystem

- Operates directly off 12-V/24-V battery (tolerates up to 42 V)

- Integrated LIN transceiver

- ADC input voltage divider

- Functional safety for ASIL-B

- Developed according to the development process of ISO 26262 for ASIL B as a Safety Element out of Context (acc. ISO26262-10:2018E, clause 9)

- Memory protection unit (MPU)

- Window watchdog timer (WDT) with challenge-response functionality

- Supply monitoring; detection of overvoltage and brownout events for 3.3-V and 1.8-V supplies

- Hardware error correction (SECDED ECC) on all safety-critical memories (SRAM, flash)

- Analog diagnostics (backup reference voltage, redundancy in voltage, current, and temperature measurement paths)

- Timing and pulse-width modulation

- Four 16-bit timer/counter/pulse-width modulator (TCPWM) blocks

- Center-aligned, Edge, and pseudo-random modes

- Quadrature decoder

- Clock sources

- ±2% up to 49.152-MHz internal main oscillator (IMO)

- ±1% 2-MHz high-precision oscillator (HPOSC)

- $\pm 5\%$  or  $\pm 7\%$  32-kHz precision internal low-power oscillator (PILO) based on the part number

- $\pm 1\%$  or  $\pm 1.5\%$  accuracy on IMO and PILO when software calibrated to the HPOSC based on the part number

- 40-kHz internal low-speed oscillator (ILO)

#### Features

- Communication

- One independent run-time reconfigurable serial communication block (SCB) with re-configurable I<sup>2</sup>C, SPI, UART, or LIN Slave functionality

- One independent local interconnect network (LIN) block with two channels

- LIN protocol compliant with LIN 2.2A, 2.1, 2.0, 1.3, SAE J2602, and ISO 17987

- Package

- 32-QFN with wettable flanks (6 x 6 mm)

- Up to 9 GPIOs

Table of contents

## **Table of contents**

| General description                            |    |

|------------------------------------------------|----|

| Features                                       |    |

| Table of contents                              | 3  |

| Block diagram                                  |    |

| 1 Functional definition                        | 5  |

| 1.1 CPU and memory subsystem                   | 5  |

| 1.1.1 CPU                                      |    |

| 1.1.2 Memory with ECC                          | 5  |

| 1.1.3 Flash                                    |    |

| 1.1.4 SRAM                                     |    |

| 1.1.5 SROM                                     |    |

| 1.1.6 DMA                                      |    |

| 1.2 System resources                           |    |

| 1.2.1 Power system                             |    |

| 1.2.2 Power system supervision and monitoring  |    |

| 1.2.3 Clock system                             |    |

| 1.2.4 Reset                                    |    |

| 1.3 Fixed function digital                     |    |

| 1.3.1 Timer/counter/PWM (TCPWM) block          |    |

| 1.4 Local interconnect network (LIN) block     |    |

| 1.5 Serial communication block (SCB)           |    |

| 1.5.1 UART mode                                |    |

| 1.5.2 SPI mode                                 |    |

|                                                |    |

| 1.5.3 I2C mode                                 |    |

| 1.5.4 LIN Slave mode                           |    |

| 1.6 GPIO                                       |    |

| 1.7 Precision analog channel subsystem (PACSS) |    |

| 1.7.1 PACSS sequencer and timing               |    |

| 1.8 PACSS measurement/acquisition system       |    |

| 1.8.1 Analog DSM channel                       |    |

| 1.8.2 Analog DSM system                        |    |

| 1.8.3 Digital channel data path                |    |

| 1.8.4 Digital data system                      |    |

| 1.8.5 Current channel automatic gain control   | 25 |

| 1.8.6 Temperature sensor                       | 26 |

| 1.9 High-voltage subsystem                     |    |

| 1.9.1 AHB interface                            | 27 |

| 1.10 ESD protection                            | 29 |

| 1.11 Device programming & debugging            | 30 |

| 2 Sample application schematic                 | 31 |

| 3 Pinouts                                      | 32 |

| 3.1 Alternate pin functions                    | 33 |

| 4 Electrical specifications                    | 34 |

| 4.1 Absolute maximum ratings                   | 34 |

| 4.2 Device-level specifications                |    |

| 4.2.1 Operating current and wakeup times       |    |

| 4.2.2 Voltage regulators                       |    |

| 4.2.3 GPIO                                     |    |

| 4.2.4 XRES                                     |    |

| 4.2.5 Clocks                                   |    |

| 4.3 Analog                                     |    |

|                                                |    |

Table of contents

| 4.3.1 LIN transceiver            | 44 |

|----------------------------------|----|

| 4.3.2 Temperature channel        | 46 |

| 4.3.3 Diagnostic channel         | 47 |

| 4.3.4 Current channel            | 48 |

| 4.3.5 Voltage channel            | 50 |

| 4.4 Digital peripherals          |    |

| 4.4.1 TCPWM                      |    |

| 4.4.2 LIN                        |    |

| 4.4.3 Serial Communication Block | 53 |

| 4.4.4 SWD interface              | 55 |

| 4.5 Memory                       | 55 |

| 4.6 System resources             | 56 |

| 5 Ordering information           | 57 |

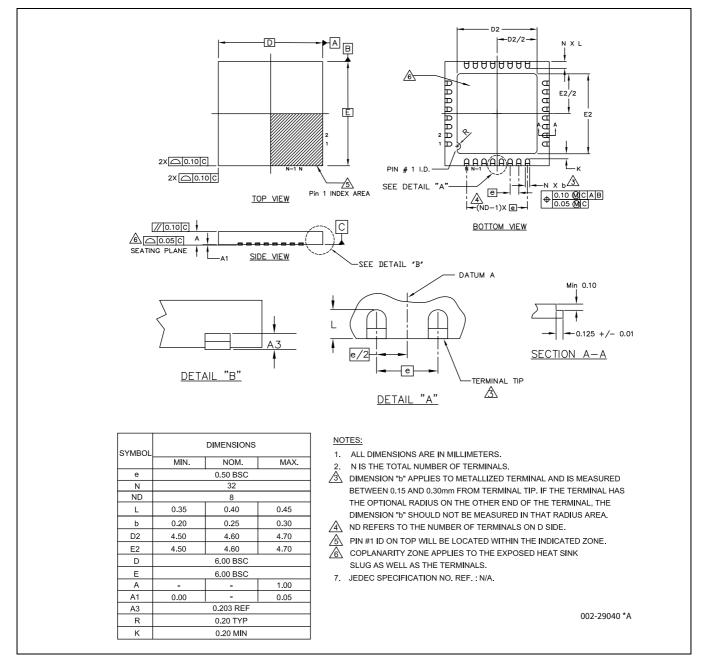

| 6 Packaging                      | 58 |

| 6.1 Package diagram              |    |

| 7 Acronyms                       | 60 |

| 8 Document conventions           | 64 |

| 8.1 Units of measure             |    |

| 9 Errata                         |    |

| Revision history                 | 68 |

Block diagram

## **Block diagram**

## 1 Functional definition

#### **1.1** CPU and memory subsystem

#### 1.1.1 CPU

The Cortex<sup>®</sup>-M0+ CPU in the PSoC<sup>™</sup> 4 HV PA is part of the 32-bit MCU subsystem, which is optimized for low-power operation with extensive clock gating. Most instructions are 16 bits in length and execute a subset of the Thumb-2 instruction set. The implementation includes a hardware multiplier that provides a 32-bit result in one cycle. It includes a nested vectored interrupt controller (NVIC) block with 32 interrupt inputs and includes a wakeup interrupt controller (WIC), which can wake the processor up from the Deep Sleep mode allowing power to be switched off to the main processor when the chip is in the Deep Sleep mode. The Cortex<sup>®</sup>-M0+ CPU provides a Non-Maskable Interrupt (NMI) input, which is made available to the user when it is not in use for system functions requested by the user.

Programs can execute from SROM, SRAM, or Flash memory.

The CPU also includes a debug interface, the SWD interface, which is a 2-wire form of JTAG; the debug configuration used for PSoC<sup>™</sup> 4 HV PA has four break-point (address) comparators and two watchpoint (data) comparators. The CPU also implements a design time configurable memory protection unit (MPU).

#### 1.1.2 Memory with ECC

Flash and SRAM include error correction code (ECC) circuitry capable of correcting single-bit errors and detecting 2-bit errors. If a single-bit error occurs, the data is corrected in-line, error information is stored (address and data), and an error flag is set which can generate an interrupt. If a multi-bit error is detected, the error information is stored and either an interrupt or reset is generated.

#### 1.1.3 Flash

The PSoC<sup>™</sup> 4 HV PA has a flash module with separate controllers for code flash and data flash. The flash controller includes an accelerator, tightly coupled to the CPU to improve average access times from the flash block. The flash accelerator delivers 85% single-cycle SRAM access performance on average. Part of a flash module can be used to emulate EEPROM.

#### 1.1.4 SRAM

Volatile static memory (SRAM) is used by the processor for storing variables and can program code, which can be written and executed in SRAM. SRAM memory is retained in all power modes (Active, Sleep, and Deep Sleep). At power-up, SRAM is uninitialized and should be written by application code before reading.

#### 1.1.5 SROM

A supervisory read-only memory (ROM) contains boot and configuration routines which can't be modified.

#### 1.1.6 DMA

A DMA engine with eight channels is provided that can do 32-bit transfers and has chainable ping-pong descriptors. This DMA engine allows data transfer between memory, registers, and peripherals without CPU intervention. DMA transfers can occur while the CPU is sleeping. Descriptors identify the data source and destination along with other information.

#### **1.2** System resources

#### **1.2.1** Power system

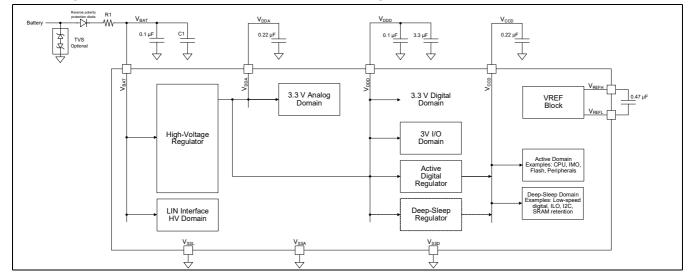

The power system includes regulators to generate appropriate voltages. The PSoC<sup>™</sup> 4 HV PA operates at full performance from a single supply on VBAT over a voltage range of 3.6 V to 28 V and remains functional up to 42V. In addition to an active mode, the PSoC<sup>™</sup> 4 HV PA has two low-power modes called Sleep and Deep Sleep. Transitions between the three power modes are managed by the power system in the system resources subsystem (SRSS).

The high-voltage regulator generates a 3.3-V supply from VBAT for V<sub>DDD</sub> and V<sub>DDA</sub>. V<sub>DDA</sub> powers analog circuits, while V<sub>DDD</sub> provides power for I/Os (GPIOs) and the 1.8-V core power regulators. There are different internal core regulators to support the various power modes. These include an Active Digital regulator and a Deep Sleep regulator.

Refer to **Figure 1** and **Table 1** for the power system block diagram and current specifications.

Figure 1 Power system block diagram

#### Table 1R1/C1 max current specifications

| Configuration | R1         | C1         | Max current |

|---------------|------------|------------|-------------|

| 1             | 10-15 ohm  | 2.2 μF     | 20 mA       |

| 2             | 6.6-10 ohm | 2 × 2.2 μF | 30 mA       |

Bypass capacitors must be used from  $V_{DDD}$ ,  $V_{DDA}$ , and  $V_{CCD}$  to ground. These capacitors should typically be X7R ceramic or better.

| Supply pair                           | Nominal cap      | Tolerance                  |

|---------------------------------------|------------------|----------------------------|

| V <sub>BAT</sub> – V <sub>SSD</sub>   | 0.1 μF<br>2.2 μF | +65% / -65%<br>+10% / -50% |

| V <sub>DDD</sub> – V <sub>SSD</sub>   | 0.1 μF<br>3.3 μF | +65% / -65%<br>+10% / -50% |

| V <sub>DDA</sub> – V <sub>SSA</sub>   | 0.22 μF          | +10% / -50%                |

| V <sub>CCD</sub> – V <sub>SSD</sub>   | 0.22 μF          | +10% / -50%                |

| V <sub>REFH</sub> – V <sub>REFL</sub> | 0.47 μF          | +38% / -48%                |

#### Table 2Bypass capacitors

The system has a high-voltage (HV) regulator which generates 3.3-V supplies and several regulators for various low-voltage core domains. The analog circuits run directly from the VDDA supply generated by the HV regulator. The core regulators include an Active Digital regulator for digital circuitry and a separate regulator for Deep Sleep.

The HV regulator is always enabled. The Active Digital regulator is enabled during the Active or Sleep power modes. It is turned off in the Deep Sleep power mode. The Deep Sleep regulator fulfills power requirements in the low-power modes.

| Table 3 | <b>Regulators and operating modes</b> |

|---------|---------------------------------------|

| Iable S | Regulators and operating modes        |

| Mode       | HV Regulator | Active Regulator | Deep Sleep Regulator |

|------------|--------------|------------------|----------------------|

| Active     | On           | On               | On                   |

| Sleep      | On           | On               | On                   |

| Deep Sleep | On           | Off              | On                   |

#### **1.2.2** Power system supervision and monitoring

The power supply includes supervision and monitoring to assure voltage levels as required exist for the respective modes. The voltage monitoring system includes power-on-reset (POR) and brownout detection (BOD). The supervisor either delays mode transitions (on POR, for example) until required voltage levels are achieved for proper function or generates resets (BOD, OVD) as appropriate.

**Power-on-reset (POR):** POR circuits provide a reset pulse during the initial power ramp. POR circuits monitor V<sub>CCD</sub> (core) voltage. The POR threshold is between 0.8 V and 1.5 V and guarantees all circuits have been properly initialized prior to release. POR circuits are used during initial chip power-up and then disabled.

**Brownout detect (BOD):** The BOD circuit protects the operating or retaining logic from possibly unsafe supply conditions by applying reset to the device. BOD circuit monitors the V<sub>CCD</sub> voltage. The BOD circuit generates a reset if core voltage dips below the minimum safe operating voltage (1.48 V–1.62 V in Active/Sleep and 1.11 V–1.5 V in Deep Sleep). The system will not come out of RESET until the supply is detected to be valid again.

To enable firmware to distinguish a normal power cycle from a brownout event, a special register is provided (RES\_CAUSE), which will not be cleared after a BOD generated RESET. However, this register will be cleared if the device goes through POR or XRES.

**Voltage references:** The SRSS includes a bandgap and current references for use by analog circuits and SRSS voltage regulators. The HV regulator has another reference and the precision analog subsystem has a high-precision voltage reference which provides accurate voltage references for the ADCs. The ADCs may measure the SRSS and HV regulator references and all supply voltages (V<sub>DDD</sub>, V<sub>DDA</sub>, V<sub>CCD</sub>, and V<sub>SS</sub> and V<sub>SSA</sub>) pins for diagnostic purposes. To allow better SNR and better absolute accuracy, an external reference or an external capacitor on the reference pin can improve accuracy by reducing noise.

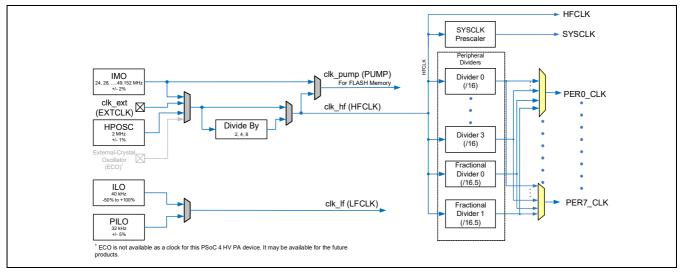

### 1.2.3 Clock system

The PSoC<sup>™</sup> 4 HV PA clock system is responsible for providing clocks to all subsystems that require clocks and for switching between different clock sources without glitching and for synchronizing clocks operating on different frequency domains to prevent meta-stable conditions. There are four oscillators implemented:

- One IMO for CPU and peripheral clock generation, which can be programmed for frequencies from 24 MHz to 48 MHz in 4-MHz steps. The 48-MHz setting can be boosted to 49.152 MHz.

- One high-precision fixed frequency 2-MHz oscillator for precision timing (HPOSC)

- One low-power 40-kHz low-speed oscillator (ILO)

- One 32-kHz precision low-power oscillator (PILO) for wakeup timers and watchdog timers.

There are also provisions for an external clock supplied by a GPIO pin. The ILO and PILO are permanently powered in all power modes.

#### Figure 2 PSoC<sup>™</sup> 4 HV PA clocking architecture

Software can lock the IMO and ILO to the HPOSC to increase precision of those oscillators. Software can also lock any of the oscillators to external time references such as the external clock input or LIN bit rate. Software lock is accomplished with dedicated calibration counters that are available in the system resources subsystem. The oscillators are designed in such a way that trim changes do not glitch or disturb clock outputs.

**IMO clock source:** The IMO is the primary source of internal clocking in the PSoC<sup>™</sup> 4 HV PA. It is trimmed during testing to achieve the specified accuracy. Trim values are stored in nonvolatile memory. Trimming can also be done on the fly to allow in-field calibration. The IMO default frequency is 24 MHz and it can be adjusted from 24 to 48 MHz in steps of 4 MHz. The 48-MHz setting can be boosted to 49.152 MHz using "Special" calibration data stored in SFLASH. IMO tolerance with Cypress-provided calibration settings is ±2%. This clock runs in Active and Sleep modes.

**HPOSC clock source:** The HPOSC is a 2 MHz 1% precision oscillator, which is on in Active power and Sleep mode and off in Deep Sleep modes. During Active mode, high-frequency precision is required for accurate timing of ADC measurements to accurately determine charge and discharge energy (amp-hour) balance. This is achieved with the IMO slaved to the HPOSC with software tracking.

**PILO clock source:** The Precision Internal Low Speed Oscillator (PILO) is a very low power oscillator with a nominal frequency of 32 kHz. It is primarily used to generate clocks for peripherals in low power modes. The PILO is implemented with the focus on low-power in the deep-sleep to keep supply current under 50uA. The accuracy over temperature and lifetime without periodic synchronization to the HPOSC is  $f_{PILO\_ACCY}$ . By means of regular synchronization with the HPOSC at least once per second, the same accuracy as in normal mode can be achieved ( $f_{PILO\_ACCY2}$ ). This accuracy can be maintained at least 60s after the last synchronization calibration while temperature and voltage are stable.

The PILO clocks low-power digital blocks including the watchdog timers and a lifetime counter. In active mode, it can also generate strobes enabling TCPWM counters to be used with software for calibrating of the ILO.

**ILO clock source**: The ILO operates with no external components and outputs a stable clock at 40-kHz nominal. The ILO is relatively low power and low accuracy. The ILO is available in all power modes. The ILO is a relatively inaccurate (–50% to +100% over voltage and temperature) oscillator, which is used to generate low-frequency clocks.

**Lifetime counter:** A 32-bit lifetime counter with a prescaler (/1 to /32) is available and triggered from the PILO clock. This counter runs in all modes and can be reset by POR. With the prescaler, the net resolution of the counter becomes 37-bit causing an overflow every 50 days. The counter will continue counting upon overflow.

#### 1.2.4 Reset

The PSoC<sup>™</sup> 4 HV PA can be reset from a variety of sources including a software reset. Reset events are asynchronous and guarantee reversion to a known state. The reset cause is recorded in a register, which is sticky through reset and allows software to determine the cause of the reset. An XRES pin is reserved for external reset to avoid complications with configuration and multiple pin functions during power-on or reconfiguration.

The following events cause resets:

- POR

- Brownout/overvoltage

- Watchdog reset

- Software reset

- External reset via XRES pin

- Fault system

- Protection violation

**Watchdog timers (WDT)**. The WDTs are used to automatically reset the device in the event of an unexpected firmware execution path. There are two WDTs, one that is available in the DeepSleep mode, and a challenge-response WDT (CRWDT).

The CRWDT includes a window watchdog function, generating timeout events if the CRWDT is serviced too soon, too late, or with the wrong software key. A register identifies the timeout cause. It generates a watchdog reset or interrupt if serviced too soon or too late. Service too soon potentially means an infinite loop including watchdog service is executing, while too late means the processor could be stuck and not processing properly. The challenge/response means the watchdog service routines must present specific data or "keys" in the order expected by the watchdog or a fault will occur. The fault will generate a watchdog reset or interrupt with the reset recorded in the Reset Cause register. The causes can be conditions such as watchdog too soon, watchdog late, or wrong key received.

Further details of the CRWDT can be found in the technical reference manual.

infineon

Functional definition

## **1.3** Fixed function digital

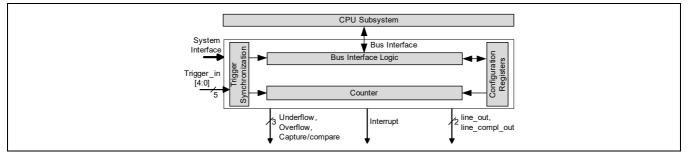

### 1.3.1 Timer/counter/PWM (TCPWM) block

The TCPWM in PSoC<sup>™</sup> 4 HV PA implements 16-bit timer, counter, pulse width modulator (PWM), and quadrature decoder functionality. Four TCPWM blocks exist on PSoC<sup>™</sup> 4 HV PA. The block can be used to measure the period and pulse width of an input signal (timer), count several events (counter), generate PWM signals, or decode quadrature signals.

The block provides true and complementary outputs with programmable offset between them to allow dead-band between outputs for driving complementary PWM loads. It also has a Kill input to force outputs to a predetermined state; this is used to inhibit outputs when faults are detected without requiring the need and delay of software intervention.

Features:

- The TCPWM block supports the following operational modes:

- Timer, Counter, Capture, Quadrature decoding

- Pulse width modulation (PWM) including Pseudo-random PWM and PWM with dead time

- PWM uses a period counter and capture counter complementary outputs are available

- Multiple counting modes up, down, and up/down

- Clock prescaling (division by 1, 2, 4, ... 64, 128)

- Double buffering of compare/capture and period values

- Generate triggers based on Compare, Overflow, or Underflow.

- Supports interrupt on:

- Terminal Count: The final value in the counter register is reached (zero or period count)

- Capture: When a capture event occurs (the counter value at the time of capture is saved)

- Compare: When the count equals the compare value

- Synchronized counters: The counters can reload, start, stop, and count at the same time

### **1.4** Local interconnect network (LIN) block

PSoC<sup>™</sup> 4 HV PA features a dedicated LIN communication block that supports autonomous transfer of the LIN frame to offloading the CPU. Some of the key features of this block include:

- Certified at C&S according to LIN 2.2A / ISO 17987 standards

- MXLIN has two channels: One is wired (through HSIOM) to the internal PHY and the other is available to GPIOs for an external PHY. They can both be used simultaneously, or they can be used in loop-back mode for testing.

- LIN protocol support in hardware according to LIN 2.2A / ISO 17987 standard

- Master and slave functionality

- Master node

- Autonomous header transmission and autonomous response transmission and reception

- Slave node

- Autonomous header reception and autonomous response transmission and reception

- Message buffer for PID, data, and checksum fields

- Classic and enhanced checksum

- Timeout detection

- Error detection

- Test modes including hardware error injection

- Baud rate detection

- 16x bit time oversampling

### **1.5** Serial communication block (SCB)

SCB supports three serial interface protocols: SPI, UART, and I<sup>2</sup>C. Only one of the protocols is supported by an SCB at any given time. The PSoC<sup>™</sup> 4 HV PA has one SCB.

This block supports the following features:

- UART with standard, SmartCard reader, Local Interconnect Network (LIN), and IrDA protocols

- UART with LIN slave functionality with LIN v1.3 and LIN v2.1/2.2/2.2A specification compliance

- SPI master and slave functionality with Motorola, TI, and NSC protocols

- I<sup>2</sup>C master and slave functionality

- EZ mode for SPI and I<sup>2</sup>C, which enables operation without CPU intervention

- Low-power (Deep Sleep) mode of operation for SPI and I<sup>2</sup>C protocols (using external clocking)

#### 1.5.1 UART mode

This is a full-feature UART operating at up to 1 Mbps supporting automotive single-wire interface (LIN), infra-red interface (IrDA), and SmartCard (ISO7816) protocols, all of which are minor variants of the PSoC<sup>™</sup> 4 HV PA UART protocol. In addition, it supports the 9-bit multiprocessor mode that allows addressing of peripherals connected over common RX and TX lines. Common UART functions such as parity error, break detect, and frame error are supported. An 8-deep FIFO allows much greater CPU service latencies to be tolerated.

The Universal Asynchronous Receiver/Transmitter (UART) protocol is an asynchronous serial interface protocol. UART communication is typically point-to-point.

The UART interface consists of two signals:

- TX: Transmitter output

- RX: Receiver input

The UART can also connect to the internal Local Interconnect Network (LIN) PHY.

The UART mode has the following features:

- Asynchronous transmitter and receiver functionality

- Supported UART protocols include Standard UART, LIN, SmartCard (ISO7816) reader, and IrDA

- LIN support includes

- Break detection

- Baud rate detection

- Collision detection (detect a dominant bus state when transmitting a recessive bit)

- Multi-processor mode

- Data frame size programmable from 4 to 9 bits

- Programmable number of STOP bits, which can be set in terms of half-bit periods between 1 and 4

- Parity (odd and even parity)

- Interrupt or polling CPU interface

- Programmable oversampling

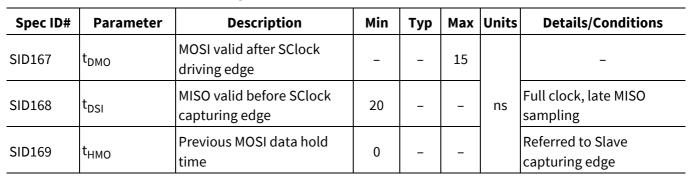

### 1.5.2 SPI mode

The Serial Peripheral Interconnect (SPI) mode supports full Motorola SPI, TI SSP (essentially adds a start pulse used to synchronize SPI Codecs), and National Microwire (half-duplex form of SPI). The SPI block can use the FIFO and supports an EzSPI mode in which data interchange is reduced to reading and writing an array in memory.

The SPI protocol is a synchronous serial interface protocol. Devices operate in either master or slave mode. The master initiates the data transfer. The SCB supports single-master-multiple-slaves topology for SPI. Multiple slaves are supported with individual slave select lines.

You can use the SPI master mode when the PSoC<sup>™</sup> must communicate with one or more SPI slave devices. The SPI slave mode can be used when the PSoC<sup>™</sup> must communicate with an SPI master device.

The SPI mode has the following features:

- Supports master and slave functionality

- Supports three types of SPI protocols:

- Motorola SPI modes 0, 1, 2, and 3

- Texas Instruments SPI, with coinciding and preceding data frame indicator for mode 1

- National Semiconductor (MicroWire) SPI for mode 0

- Supports up to four slave select lines

- Data frame size programmable from 4 bits to 16 bits

- Interrupts or polling CPU interface

- Programmable oversampling

- Supports EZ mode of operation EZSPI mode allows for operation without CPU intervention

- Supports externally clocked slave operation:

- In this mode, the slave operates in Active, Sleep, and Deep Sleep system power modes

- A standard SPI interface consists of four signals as follows. These signals connect to GPIO pins:

- SCLK: Serial clock (clock output from the master, input to the slave).

- MOSI: Master-out-slave-in (data output from the master, input to the slave).

- MISO: Master-in-slave-out (data input to the master, output from the slave).

- Slave Select (SS): Usually an active low signal (output from the master, input to the slave).

# 1.5.3 I<sup>2</sup>C mode

The hardware I<sup>2</sup>C block implements a full multi-master and slave interface (it is capable of multimaster arbitration). This block is capable of operating at speeds of up to 1 Mbps (Fast Mode Plus) and has flexible buffering options to reduce interrupt overhead and latency for the CPU. It also supports EZI2C that creates a mailbox address range in the memory of the PSoC<sup>™</sup> 4 HV PA and effectively reduces I<sup>2</sup>C communication to reading from and writing to an array in memory. The block supports an 8-deep FIFO for receive and transmit which, by increasing the time given for the CPU to read data, greatly reduces the need for clock stretching caused by the CPU not having read data on time. The FIFO mode is available in all channels and is very useful in the absence of DMA.

The I<sup>2</sup>C peripheral is compatible with the I<sup>2</sup>C Standard-mode, Fast-mode, and Fast-mode Plus devices as defined in the NXP I<sup>2</sup>C-bus specification and user manual (UM10204). The I<sup>2</sup>C bus I/O is implemented with GPIO in open-drain modes.

PSoC<sup>™</sup> 4 HV PA is not completely compliant with the I<sup>2</sup>C spec in the following respect:

GPIO cells are not overvoltage-tolerant and, therefore, cannot be hot-swapped or powered up independently

of the rest of the I<sup>2</sup>C system

The I<sup>2</sup>C mode has the following features:

- Master, slave, and master/slave mode

- Slow-mode (50 kbps), standard-mode (100 kbps), fast-mode (400 kbps), and fast-mode plus (1000 kbps) data-rates

- 7- or 10-bit slave addressing (10-bit addressing requires firmware support)

- Clock stretching and collision detection

- Programmable oversampling of I<sup>2</sup>C clock signal (SCL)

- Error reduction using a digital filter on the input path of the I<sup>2</sup>C data signal (SDA)

- Glitch-free signal transmission with an analog glitch filter

- Interrupt or polling CPU interface

#### 1.5.4 LIN Slave mode

The LIN Slave mode uses the SCB hardware block and implements a full LIN slave interface. This LIN Slave is compliant with LIN v1.3, v2.1/2.2, ISO 17987-6, and SAE J2602-2 specification standards. LIN slave can be operated at baud rates of up to ~20 Kbps with a maximum of 40-meter cable length.

### 1.6 GPIO

This section describes the PSoC<sup>™</sup> 4 HV PA I/O system. The GPIO pins are grouped into ports; a port can have a maximum of eight GPIOs. The PSoC<sup>™</sup> 4 HV PA has 9 GPIOs.

The GPIOs have these features:

- Output drive modes include push-pull (strong or weak), open drain/source, high-z, and pull-up/pull-down

- Selectable CMOS and low-voltage LVTTL input buffer mode

- Edge-triggered interrupts on rising edge, falling edge, or on both the edges, on pin basis

- Individual control of input and output disables

- Hold mode for latching previous state (for retaining I/O state in Deep Sleep)

- Selectable slew rates allowing dV/dt control to assist with noise control to improve EMI

All GPIOs can be used to receive analog input signals for the ADCs.

During power-on and reset, GPIO outputs are disabled to prevent conflict with externally applied signals and prevent crowbar and/or excessive turn-on current. Data output and pin state registers store, respectively, the values to be driven on the pins and the states of the pins themselves. An interconnect network known as a high-speed I/O matrix (HSIOM) is used to multiplex between various signals that may connect to an I/O pin.

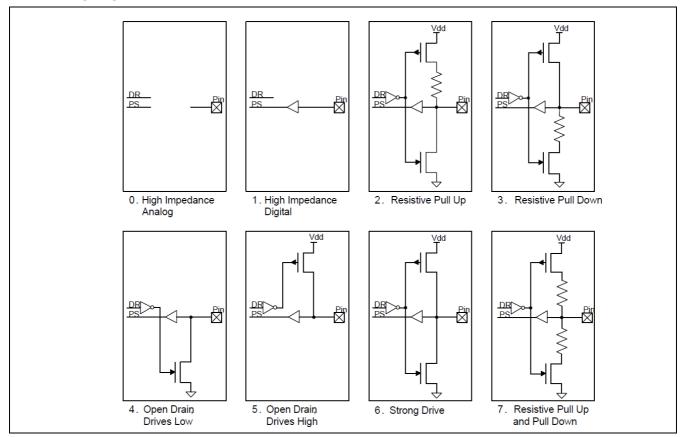

The following diagram illustrates the various available GPIO output drive modes.

Figure 4 GPIO output drive modes

Every I/O pin can generate an interrupt if so enabled and each I/O port has an interrupt request (IRQ) and interrupt service routine (ISR) vector associated with it.

The PSoC<sup>™</sup> 4 HV PA HV V<sub>DDD</sub> regulator has enough capacity to drive internal loads and external loads up to 10 mA. DC GPIO loads are considered external loads. The combined DC GPIO and external load current must not exceed the available 10 mA. Care must be taken when driving DC loads, such as LEDs, to make sure the total current being sourced from the GPIOs does not exceed this limit.

### **1.7** Precision analog channel subsystem (PACSS)

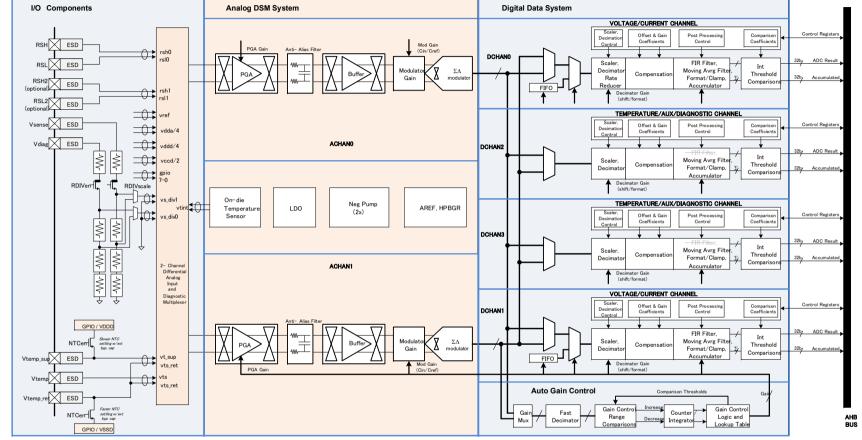

The PSoC<sup>™</sup> 4 HV PA Precision Analog Channel Subsystem (PACSS) is a high-performance data acquisition system consisting of two delta-sigma analog-to-digital converters (ADCs) and support circuitry. The two ADCs can quickly switch between input sources to create a third "virtual" ADC. The PACSS includes an analog input multiplexer, input buffer amplifiers, delta-sigma modulators, decimators, and digital signal processing channels. There is also a precision voltage reference, current references, and temperature sensors.

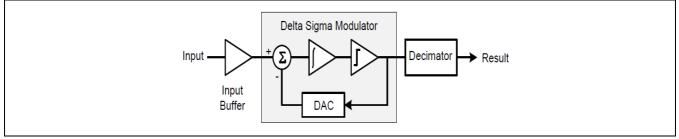

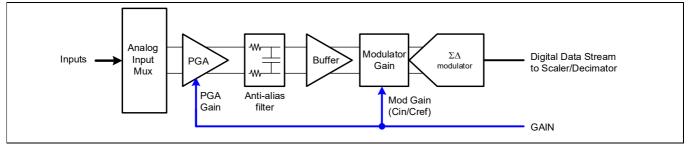

The following is a simplified picture of a delta sigma ADC.

Figure 5 PACSS overview

The delta-sigma ADC works by using a modulator, taking the difference between input and feedback signals (delta) and accumulating that difference (sigma) to produce a digital output. The digital stream goes to a decimator which converts the fast-oversampled bit stream into slower high-resolution results.

The PSoC<sup>™</sup> 4 HV PA PACSS has two delta-sigma analog-to-digital converters (ADCs) to perform 16-bit measurements at a sample rate of up to 48 ksps for continuous measurements. Higher resolution can be achieved at slower sample rates by accumulating more modulator results in the decimator.

The PSoC<sup>™</sup> 4 HV PA PACSS analog multiplexer selects between the differential input voltages including two HV voltage dividers, GPIO pads, internal temperature sensors, an external NTC temperature sensor, and diagnostic voltages. All analog signals can be supplied to either of the analog ADCs, which improves diagnostics since both ADCs can measure and compare the same signals.

The analog portion of the ADCs consists of a programmable gain amplifier, an anti-alias filter, a buffer, and a multi-level delta-sigma modulator (DSM). The output of the modulator goes to the digital portion of the channel and features a scaler, decimator, FIR filter, adder/multiplier to reduce gain and offset errors, averaging, and threshold comparisons.

There are four digital channels, which process outputs from either of the two analog DSMs. Two channels are with the FIR filter, and the other two are without the FIR Filter. The channels are typically used for current, voltage, temperature, and diagnostic measurements although they can be associated with any inputs (for example, V<sub>SENSE</sub> can be measured by one channel while V<sub>DIAG</sub> is measured by another).

The current channel has an automatic gain control, which allows a large dynamic range that enables measuring large starting currents or small battery-off currents. The gain of the current channel ranges from 1 to 512. Automatic gain can be disabled and set to a fixed value. A scaler between the modulator and decimator adjusts the weight of modulator data based on gain so the input to the LSB of the data going into the decimator is always 0.715 mA.

The gain of other channels is static instead of dynamic. Static gain is typically set to 1 but any value from 1 to 512 in powers of 2 can be used. The HV input channels have resistor voltage dividers, which attenuate the input voltage. The nominal divider ratio is 24x (28.8 V full-scale) with an optional value of 16x (19.2 V full scale).

Chopping is used to minimize offset voltage error. Channel chopping is implemented to further reduce offset error. Channel chopping is making a measurement followed by a second measurement with inputs swapped and result multiplied by -1. The two samples are averaged, which removes any residual channel offset.

ADC measurements can be triggered by software or hardware. Hardware triggers can be generated by timers or GPIO inputs. The ADCs can be triggered independently or simultaneously. A SYNC function can be implemented to allow multiple PSoC<sup>™</sup> 4 HV PA chips to perform simultaneous measurements. One device uses a GPIO output to simultaneously trigger the on-chip ADC measurements while signaling other PSoC<sup>™</sup> 4 HV PA chips to trigger measurements. The SYNC signal can be set using either a timer or software to write to the GPIO.

### 1.7.1 PACSS sequencer and timing

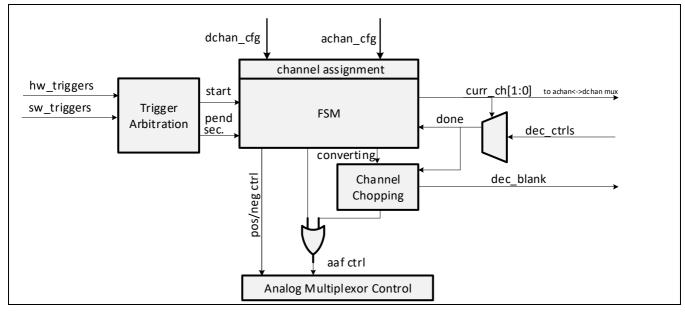

The PACSS sequencer generates control signals for performing analog-to-digital conversion. A block diagram of the sequencer is shown here.

#### Figure 6 PACSS sequencer

A peripheral clock from the system-wide resource clock system is used for sequencer timing. The same clock is used for all ADC channels. The clock goes to the delta-sigma modulator (DSM) controller, which generate timing strobes with a finite state machine which are used by other sections of the sequencer. The DSM controller also includes control and status registers which are accessed from the  $\mu$ C and DMA channels using the AHB bus. The controller also generates interrupt and DMA requests.

ADC conversions are initiated by triggers from generated by other sources. Those sources include timers (TCPWM), input signals from GPIOs, software requests, and end-of-conversion commands from an active ADC. Triggers can start one or two ADCs - when triggering two ADCs, both ADCs start together. An arbiter is used to prioritize ADC conversion requests and start conversions when the ADCs become available.

The arbiter also controls the analog multiplex or control block, which selects the analog input associated with the trigger. The analog multiplex or control sends the appropriate select signals to the analog multiplex or to connect analog inputs to the ADCs.

The two ADC channels have a channel controller which generates timing for that channel. There are separate controls for the analog and digital portion of the channels. The analog timing signals control the delta-sigma modulator and chopping switches, while the digital timing signals clock data path registers including the decimator, finite impulse response filter, and comparators and accumulators.

At the beginning of the conversion sequence, a four-cycle reset of the modulator clears state from previous conversions (the integrators in the modulator are initialized by this reset). The length of a conversion cycle requires the same number of clocks as the OSR setting. After the modulator is reset, the decimation filter needs to stabilize before output data is valid. For continuous measurements, the decimator needs to be one order higher than the modulator to maintain stability over time, and therefore a Sinc3 decimator (one order higher than the third order modulator) is used. This means that the decimator output is valid after the fourth conversion and then every conversion thereafter. For example, an OSR of 64 with a 3.072-MHz clock requires ~1.3 µs for reset, ~20.8 µs per conversion (or 48 ksps) in continuous mode, and 86.6 µs for the initial result.

For incremental (one-shot) conversions, the decimator can be the same order as the modulator, so a Sinc3 is used which reduces latency to three conversion cycles. Using the same conditions as the example above, the result requires 64 µs.

The incremental measurement mode can be used to measure several different voltage sources each conversion sequence while maintaining an aggregate sample rate. The sample rate can be adjusted by changing the OSR setting. With an OSR of 64 and a 3.072-MHz clock, the incremental sample rate is 16 ksps. If this mode is used to measure continuously, measure two different sources, the sample rate for each signal is half of the single source rate.

PSoC<sup>™</sup> 4 HV PA takes advantage of the incremental mode to create three channels with only two analog front-ends.

Since lead-acid battery sensing applications only need 8 ksps on the main voltage and current channels, the third channel can use either one of the analog front-ends, which is not being used between V/I measurements. This channel can be used for temperature measurement, to measure other signals, or for diagnostics. Diagnostics can include measuring power supplies, references, and even the same signal measured by the other channel. The main advantage of using shared analog front-ends is power reduction.

### **PACSS** measurement/acquisition system

Figure 7 **PACSS** measurement/acquisition

An analog multiplexer connects input signals to the two physical analog DSM channels. Several input sources are available including signals from I/O input. The analog channels have choppers, gain, filters, and DSM modulators. Several integrated multiplexers facilitate diagnostics and channel switching without disturbing filters. The digital section has four channels with one dedicated channel for each analog channel and two auxiliary channels, which can use either analog channel. The following sections provide more details about these blocks.

002-28660 Rev. \*J 2023-09-21

infineon

Functional definition

### 1.8.1 Analog DSM channel

A simplified diagram of an analog delta-sigma modulator (DSM) channel and part of the digital channel is shown below. For better clarity, the diagram omits analog multiplexers to bypass and swap blocks for diagnostics.

#### Figure 8 Analog DSM channel

The analog DSM channel receives a differential signal selected by an analog multiplexer. This differential signal is received by a programmable gain amplifier (PGA). The output of the PGA feeds a low-pass anti-alias filter (AAF) with a bandwidth of ~30 kHz. A buffer amplifier drives the DSM modulator - this amplifier has high bandwidth to settle the modulator capacitors to better than 16 bits each time they are settled. The modulator uses capacitor dividers to set gain - the modulator disturbs its input each time the input is sampled - the inputs need to settle before the next sample or errors result. The modulator is a third order with switched capacitor amplifier circuits. The modulator produces a multi-level digital bitstream sent to the digital channel.

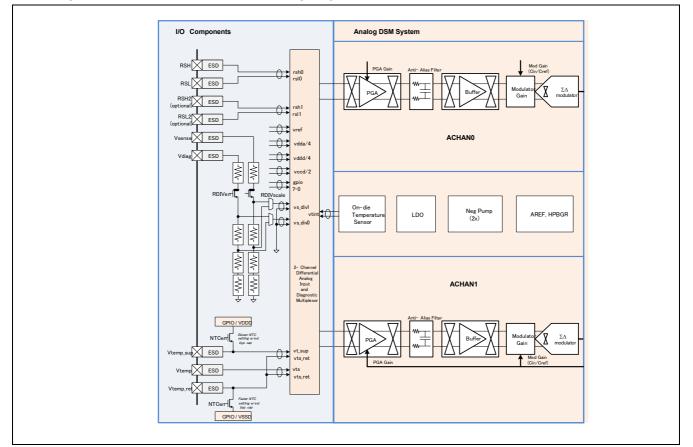

### 1.8.2 Analog DSM system

The analog DSM system is shown in the following diagram.

#### Figure 9 Analog DSM system

The DSM sequencer previously described controls conversions. The sequencer selects the analog input signal by controlling the analog mux, connecting the input to an analog DSM channel. Signals from GPIOs, on-chip power supplies and grounds, the high-voltage input voltage divider, and on-chip sensors and references can be selected.

GPIOs not directly connected to the analog multiplexer can use an analog input bus called the analog multiplex bus (AMUXBUS). The AMUXBUS has two signals (AMUXBUSA and AMUXBUSB), which can connect GPIOs to ADC using software controlled analog switches inside each I/O.

The analog DSM channel includes choppers and multiplexers in addition to the PGA, anti-alias filter, buffer amplifier, and DSM modulator. The choppers minimize offset error while the multiplexers assist input signal switching and diagnosis. To alternately measure two signals with one channel, the anti-alias filter can be bypassed since the AAF needs about 64 µs to settle to 16 bits before conversions can start - the measurement sample rate needs to slow to 4 ksps if the AAF is not bypassed. The other paths allow the input, PGA, and AAF signals to be swapped to the other channel for diagnostics.

This section also includes a precision reference system (voltage and current) and temperature sensor.

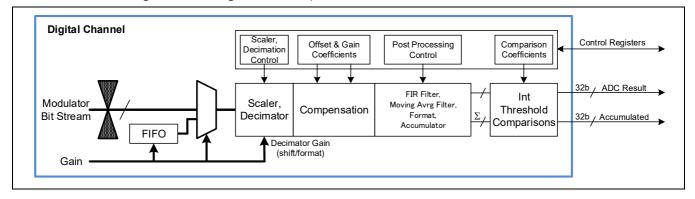

### 1.8.3 Digital channel data path

The digital data channel converts the modulator bit-stream output to parallel data and includes scaling, filtering and compensation. It also compares ADC values with thresholds to generate interrupts when thresholds are exceeded. A block diagram of the digital channel path is shown below.

Figure 10 Digital channel data path

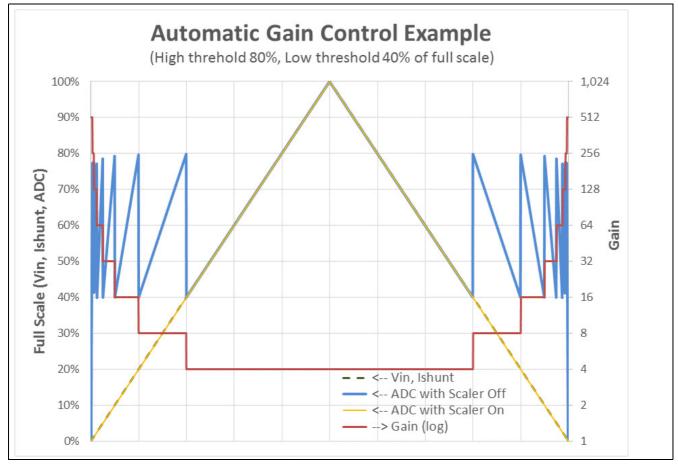

The modulator bit stream first goes to a channel chopper, which can multiply the bit stream by +1 or -1 (corresponding with a chopper that swaps inputs in the analog signal path). The voltage channel uses programmable fixed gain while the current channel can use either fixed or automatic gain.

A scaler is used so that the LSB of the ADC can have the same weight regardless of gain. The LSB is established by the ADC resolution at maximum gain – for the current channel, the LSB is 0.715 mA with a gain of 512. The scaler multiplies the output of the modulator by 512/Gain to normalize results and maintain 0.715 mA for the LSB regardless of gain setting. To multiply by 2, the scaler shifts results up one bit. To cover a gain range of 1 to 512 means results can be shifted up to 9 bits.

The output of the decimator goes to a compensation block, which multiplies results for gain adjustment and adds constants for offset correction. A 16-stage finite impulse filter (FIR) with programmable coefficients follows the compensation block. Results are then normalized to remove unused bits and averaging, accumulation, and threshold detection can be performed. Threshold comparison uses a window comparator, which can be programmed for high and low thresholds which trigger interrupts.

Channel control registers are programmed by the CPU using the AHB bus. Results can be transferred by DMA or CPU. A trigger can initiate a DMA transfer and an interrupt can notify the availability of the CPU data. These operations can be performed in parallel. The CPU can also poll for end-of-conversion to determine if data is available.

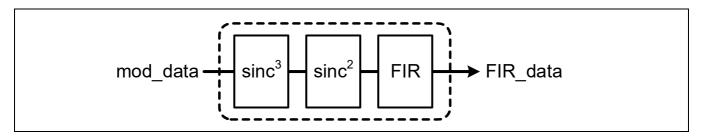

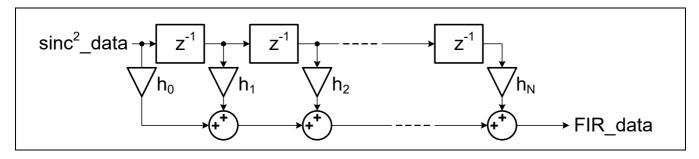

The ADC Channel digital back end has two decimators and a FIR filter. Over Sampling Rate (DR and DR2) of decimators is programmable. FIR filter coefficients and number of taps is also programmable. A high-level block diagram of the digital backend is shown in **Figure 11**.

Figure 11 High level block diagram of Digital Back End

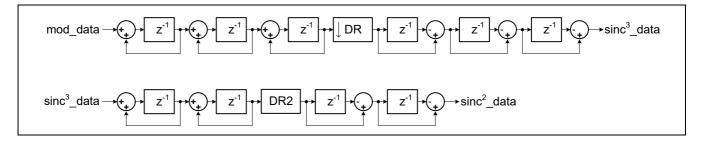

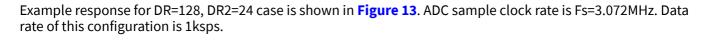

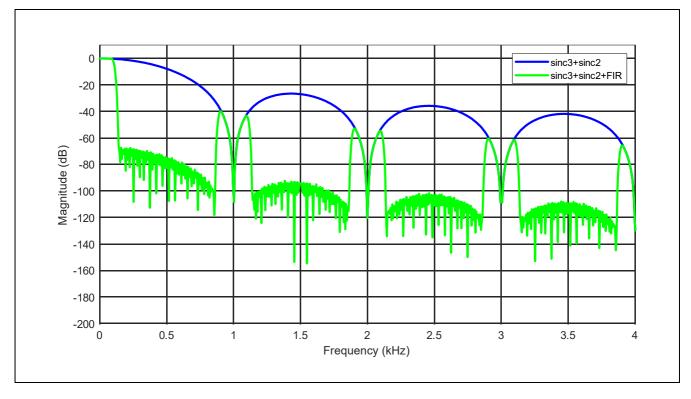

Decimator, also known as CIC filters are used to filter quantization noise of the Delta-Sigma ADC. **Figure 12** shows the block diagram of sinc3 and sinc2 decimators.

#### Figure 12 Block diagram of sinc3 and sinc2 decimators

The z-domain transfer function of an Lth-order CIC filter is typically presented as:

$$H(z) = \left[\frac{1 - z^{-DR}}{1 - z^{-1}}\right]^{L}$$

where,

- L is the filter order

- DR is the Over Sampling Rate

The sinc response is equal to zero at integer multiples of the data rate. This means that the magnitude response will show notches at these frequencies. Therefore:

- sinc3 has notches at N\*Fs/DR [notches at 24kHz, 48kHz, ...]

- sinc2 has notches at N\*Fs/(DR\*DR2) [notches at 1kHz, 2kHz, 3kHz, ...]

- where,

- N is integer number

- DR is the Over Sampling Rate of sinc3 decimator

- DR2 is the Over Sampling Rate of sinc2 decimator

- Fs is the ADC sample clock rate

#### Figure 13 sinc3 and sinc3+sinc2 output comparison

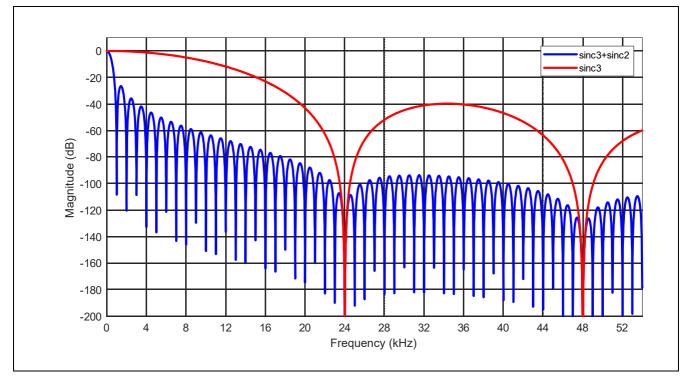

In addition, an FIR filter can be used to further reduce bandwidth. The FIR filter is fully programmable and has 64 taps (see **Figure 14**).

Figure 14 General structure of the FIR filter

**Figure 15** shows the combined output with 16-tap FIR filter. DR=128, DR2=24, ADC sample clock rate is Fs=3.072MHz. Coefficients used for the FIR filter are:

$[-0.00414\ -0.01741\ -0.02674\ -0.0151\ 0.02896\ 0.1049\ 0.18756\ 0.24197$

$0.24197\ 0.18756\ 0.1049\ 0.02896\ -0.0151\ -0.02674\ -0.01741\ -0.00414]$

Figure 15 Combined output of the Back End

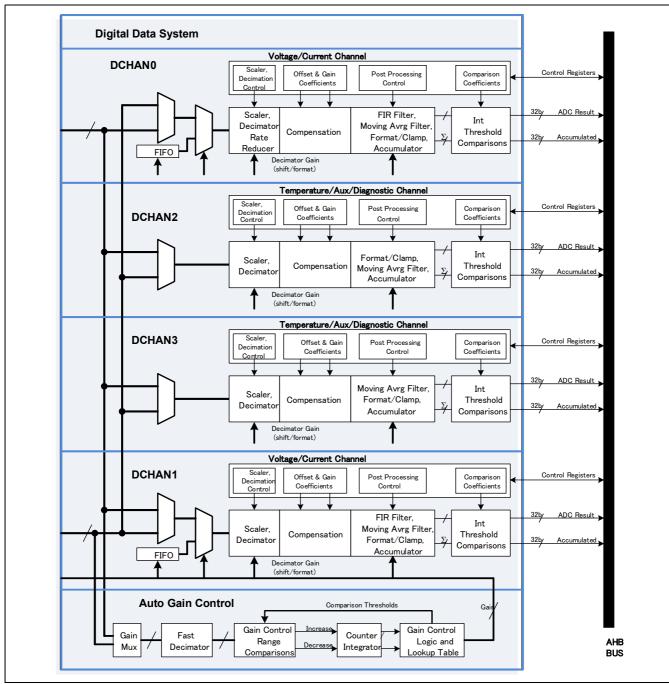

### 1.8.4 Digital data system

The following diagram shows the complete digital data system. There are four data channels, of which two are dedicated channels associated with their respective analog channels while the third and fourth can receive data from either analog channel. This allows the analog channel to feed alternate analog measurements from two different signal sources to the two data channels with appropriate configuration for those measurements. It also facilitates diagnosis by allowing either analog channel to be used to measure the same signals.

#### PSoC<sup>™</sup> 4 HVPA-144K Based on 32-bit Arm<sup>®</sup> Cortex<sup>®</sup>-M0+

Functional definition

Parameters for the alternate digital channel, especially compensation values, must be programmed to appropriate values corresponding to the analog channel being measured. The AGC function is described in the next section.

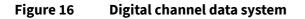

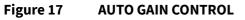

### **1.8.5** Current channel automatic gain control

The current channel includes an automatic gain control (AGC) mechanism shown in the block diagram below. This functions by measuring the analog channel input voltage with an ADC and increasing or decreasing gain when programmable thresholds are reached. The output of the gain control comparators is used by a look-up table to set scaler, PGA, and modulator gain settings. To minimize input referred noise, it is advisable to configure the gain table to increase PGA gain before increasing modulator gain.

Following is an example of the AGC with current going from 0% to 100% of full scale (3000A). The table shows full-scale amperes, resolution, and scaler values for gains from 4-512. As described in the previous sections, the scaler is used to normalize results so the LSB always has the same weight (0.715 mA) which is accomplished by multiplying the modulator by the scaler value; the scaler value is the same as 512/Gain.

The following diagram illustrates scaler operation. In this example, a 4-bit modulator input from  $\pm 7$  is scaled by 1 to 128. For example, when scaled by 128,  $\pm 7$  becomes  $\pm 7^*128$  (=  $\pm 1792$ ).

#### Figure 19 Scaler operation

The AGC can be configured to increase or decrease gain by factors of 2 or more. Large steps can track large current changes faster by reducing the number of gain changes needed for tracking.

#### **1.8.6** Temperature sensor

Temperature measurements are performed by measuring the difference in base-emitter voltage (VBE) of PNP bipolar transistors at two different current densities - temperature is directly proportional to the voltage difference. The principle of operation is:

$VBE = nkT/q^{1}ln(I/I_{S});$ dVBE = nkT/q^{1}ln(M^{1}/I\_{S}) - nkT/q^{1}ln(I/I\_{S}) = nkT^{1}ln(M); (1) VBE voltage at a given current and temperature

(2) Difference in VBE at two different current densities (current ratio "M")

$T(^{\circ}K) = dVBE^{*}q/(nk^{*}ln(M))$

(3) Temperature as a function of dVBE

Where VBE is the base-emitter diode voltage, dVBE is the difference in diode voltage at two different current densities (the ratio of current density is M), n is the base-emitter diode ideality factor, k is Boltzman's constant, q is the charge of an electron, I is the diode current, and I<sub>S</sub> is the diode saturation current.

Note that I<sub>S</sub> cancels as does the magnitude of I; n, k, and ln(M) are constants, which produce a nominal voltage of 179  $\mu$ V/°K with M=8.

Temperature is calculated from dVBE using a polynomial with factory-supplied calibration coefficients to compensate for errors and drift in n and M, which can vary slightly with temperature and temperature-related package stress. Boltzman constant k and electron charge q are physical constants which do not drift.

Two independent current reference sources are available to diagnose current reference malfunctions by comparing results using the two independent references. Similar redundancy is provided by changing transistor current density either by changing the magnitude of the current source or the size of the transistor.

Temperature measurement is usually performed with an interrupt routine, which can either be software or timer triggered.

### 1.9 High-voltage subsystem

The PSoC<sup>™</sup> 4 HV PA high-voltage subsystem includes the following functions:

- An AHB bus interface and control/status registers.

- The V<sub>BAT</sub> to V<sub>DDD</sub>/V<sub>DDA</sub> HV regulator (3.6 to 28-V input, 3.3-V nominal outputs)

- An input attenuator/voltage divider for  $V_{\mbox{SENSE}}$  and  $V_{\mbox{DIAG}}$  ADC inputs

- A LIN transceiver (physical interface or PHY)

### 1.9.1 AHB interface

The AHB includes the control and status registers needed for the HV subsystem.

#### 1.9.1.1 HV regulator

The high-voltage regulator is always on, supplied by VBAT, and provides V<sub>DDD</sub> and V<sub>DDA</sub>. It supplies a nominal output voltage of 3.3 V but may drop as low as 2.7 V when V<sub>BAT</sub> drops below 4 V.

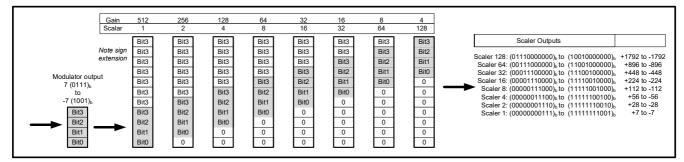

### 1.9.1.2 HV input attenuator

The HV input attenuator is a voltage divider used on the VSENSE and VDIAG to scale battery voltage to levels compatible with the ADCs, so battery voltages can be measured.

In typical lead-acid battery sensing applications, the  $V_{SENSE}$  input is normally connected directly to the battery with a series 2.2-k $\Omega$  resistors to measure battery voltage.  $V_{DIAG}$  can be used to measure voltage at other locations such as the ECU or other loads where monitoring is desired. It is sometimes used to measure ignition switch voltages such as the run bus (KL15), the start bus (KL50), or the always-on battery bus (KL-30).

The external 2.2-k $\Omega$  resistors in series with voltage sources limit current during ESD and transient voltage events. Since the nominal resistance of the on-chip voltage divider is about 2.4 M $\Omega$ , the accuracy of the external resistors is not critical since their contribution is only 0.1% of the total divider.

The voltage divider slightly loads the source being measured with the 2.4-M $\Omega$  resistor. A small current from source to ground flows through the divider (for example, 6  $\mu$ A when measuring a 12-V source). The voltage divider can be switched off using the RDIVen control bits.

The RDIVscale control bits select whether the voltage divider input-to-output ratio is 24 or 16. Since the ADC full scale input voltage is 1.2 V, the 24X ratio corresponds to 28.8-V full scale and 16X ratio corresponds to 19.2-V full scale. Voltage divider matching error results in a gain error, which can be corrected with gain correction in the ADC.

infineon

Functional definition

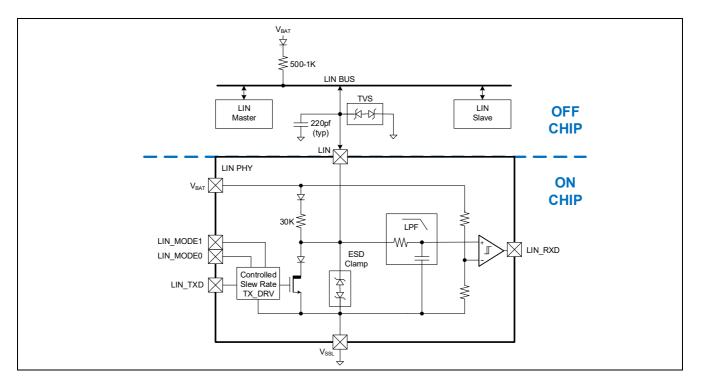

### 1.9.1.17 LIN transceiver

The LIN transceiver meets the requirements of LIN standard 2.2A and is downward compatible with the LIN 2.0. Data rates of 10 kBps and 20 kBps are supported. A non-LIN fast slew rates mode is available providing 100 kBps data rates for fast downloads for factory and field flash program updates using the LIN pin.

The LIN transceiver is guaranteed not to block the LIN bus with a dominant bit when the VBAT voltage is below the minimum LIN supply voltage (7V, VBAT\_LIN, LIN 2.2A Parameter 10) and may continue to operate below that voltage but communication is not guaranteed. The LIN transceiver is inhibited if VCCD is not valid to prevent erroneous control signals from interference with the LIN bus A timer is also present clocked by the low-speed clock system which disables the LIN if the bus is dominant for too long. The timer can generate an interrupt if the LIN bus wakeup signal (LIN bus in dominant state for 250 µs to 5 ms) is detected. LIN compliance testing is facilitated by making the transceiver data signals available on GPIO pins (LIN\_RX, LIN\_TX) as are the serial control block UART signals are also available (UART\_RX, UART\_TX).

The LIN transceiver has an open drain output and digital receiver connected to the LIN pin which connects to the LIN bus. The bus has pullups to VBAT with total pullup resistance between 500  $\Omega$  and 1 k $\Omega$ . A series diode between VBAT and the pull-ups prevents the bus from powering VBAT. The diode and pull-up resistor are usually located at or near the LIN master. The transceiver has a weak slave resistor (nominally 30 k $\Omega$ ) on-chip and the driver can be configured to provide a weak, normal, or fast pull-down. Both the pull-up and weak pull-down can be used for diagnostics without disturbing LIN bus communications.

The pull-up resistor and ESD networks prevent parasitic current paths if VBAT or ground become disconnected. The LIN driver will withstand differences of ±1 V if shorted to another ground and if continuously shorted to another ground or VBAT will not be permanently damaged. The LIN transceiver complies with Q100-2/IEC6100-4-2 ESD and ISO 7637 capacitively coupled transient pulses. Heating of LIN driver in normal operation does not affect measurement accuracy.

#### Table 4LIN Transceiver Truth Table

| LIN transceiver          | LIN MODE1                                                                                       | LIN_MODE0 | DRIVER       |           |            | Slave   |  |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------|-----------|--------------|-----------|------------|---------|--|--|--|

| function                 | LIN_MODEI                                                                                       |           | Slew Control | LIN_TXD=1 | LIN_TXD=0  | Pull-up |  |  |  |

| Fast Mode (non-LIN)      | 1                                                                                               | 1         | No           | Z (rec)   | Low (dom)  | On      |  |  |  |

| Normal/Enabled           | 1                                                                                               | 0         | Yes          | Z (rec)   | Low (dom)  | On      |  |  |  |

| Weak (diagnosis)         | 0                                                                                               | 1         | No           | Z (rec)   | Low (weak) | On*     |  |  |  |

| Disabled                 | 0                                                                                               | 0         | No           | Z (rec)   | Z          | Off     |  |  |  |

| rec - recessive; dom - c | ec - recessive; dom - dominant; Z - driver off; For LIN_TXD and LIN_RXD recessive=1, dominant=0 |           |              |           |            |         |  |  |  |

\* In weak (diagnosis) mode, slave pull-up is ON when LIN\_TXD=1, OFF when LIN\_TXD=0

#### **1.10 ESD** protection

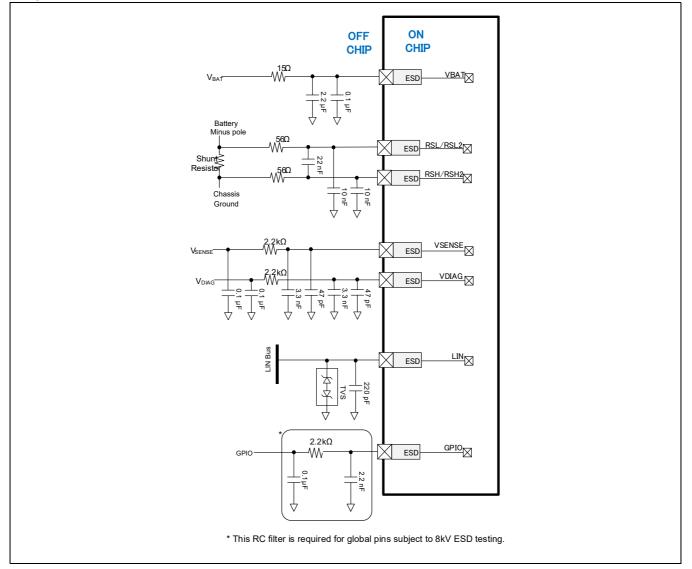

PSoC<sup>™</sup> 4 HV PA requires sufficient protection to withstand the high voltage ESD on specific pins. The ESD on LIN, VBAT, VSENSE, VDIAG, RSH, RSL, RSH2, and RSL2 is rated at ±8 kV (SIDA2), and is required to protected as shown in **Figure 22**.

#### Figure 22 ESD protection

### 1.11 Device programming & debugging

PSoC<sup>™</sup> 4 devices include extensive support for programming, testing, debugging, and tracing both hardware and firmware.

The Arm<sup>®</sup> serial-wire debug (SWD) interface supports all programming and debug features of the device.

Complete debug-on-chip functionality enables full-device debugging in the final system using the standard production device. It does not require special interfaces, debugging pods, simulators, or emulators. Only the standard programming connections are required to fully support debug.

The SWD interface is fully compatible with industry-standard third-party tools. PSoC<sup>™</sup> 4 provides a level of security not possible with multi-chip application solutions or with microcontrollers. It has the following advantages:

- Allows disabling of debug features

- Robust flash protection

- Allows customer-proprietary functionality to be implemented in on-chip programmable blocks

The debug circuits are enabled by default and can be disabled in firmware. If they are not enabled, the only way to re-enable them is to erase the entire device, clear flash protection, and reprogram the device with new firmware that enables debugging. Thus, firmware control of debugging cannot be over-ridden without erasing the firmware thus providing security.

Additionally, all device interfaces can be permanently disabled (device security) for applications concerned about phishing attacks due to a maliciously reprogrammed device or attempts to defeat security by starting and interrupting flash programming sequences. All programming, debug, and test interfaces are disabled when maximum device security is enabled. Therefore, PSoC<sup>™</sup> 4, with device security-enabled, may not be returned for failure analysis. This is a trade-off the PSoC<sup>™</sup> 4 allows the customer to make.

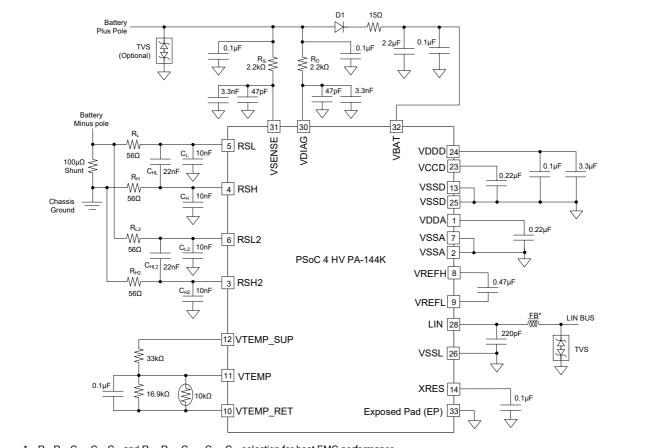

Sample application schematic

## Sample application schematic

- \*

- $\label{eq:RL} \begin{array}{l} \mathsf{R}_{\mathsf{L}}, \mathsf{R}_{\mathsf{H}}, \mathsf{C}_{\mathsf{H}}, \mathsf{C}_{\mathsf{L}}, \text{and } \mathsf{R}_{\mathsf{L2}}, \mathsf{R}_{\mathsf{H2}}, \mathsf{C}_{\mathsf{H2}}, \mathsf{C}_{\mathsf{H2}}, \mathsf{C}_{\mathsf{L2}} \text{ selection for best EMC performance.} \\ \text{Resistor values for voltage path } (\mathsf{R}_{\mathsf{S}}/\mathsf{R}_{\mathsf{D}}) : 2.2 \ \mathrm{k}\Omega \ \pm 1\% \ \text{or better is required to maintain voltage measurement accuracy specifications.} \end{array}$

- Max resistor value for current path  $(R_L/R_H/R_{L2}/R_{H2})$ : 500  $\Omega$ .

- RSH2, RSL2 and VDIAG pins are for redundant measurements based on configuration.

- Module GND connected to Battery Minus or Chassis Ground based on configuration.

- Unused IOs are recommended to be configured in High-Impedance analog mode with an external 10 k $\Omega$  100 k $\Omega$  pull-down resistor. Tested without diodes to 5000 cycles with ISO-Pulse1 (ISO 7637-2:2011);  $t_1 = 0.5$  s,  $t_2 = 0.2$  s,  $t_3 = 50$  µs,  $t_d = 2$  ms,  $U_s = \pm 150$  V,  $U_A = 13$  V,  $t_r = 1 \ \mu s$ , Pulse Generator Impedance = 2  $\Omega$ .

- Ferrite bead on the LIN bus is recommended only for 24 MHz operation.

Pinouts

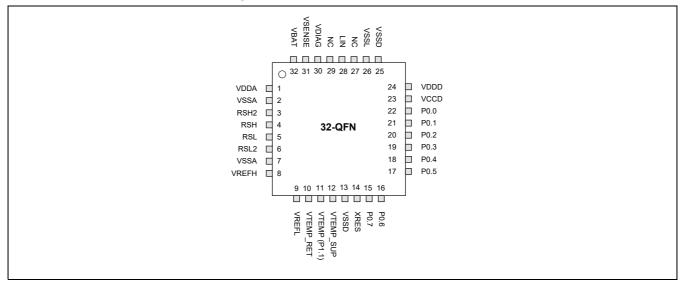

### 3 Pinouts

The following table provides the pin list for PSoC<sup>™</sup> HV PA for the 32-pin QFN package.

|     | 32-QFN    | 3   | 2-QFN  |

|-----|-----------|-----|--------|

| Pin | Name      | Pin | Name   |

| 1   | VDDA      | 17  | P0.5   |

| 2   | VSSA      | 18  | P0.4   |

| 3   | RSH2      | 19  | P0.3   |

| 4   | RSH       | 20  | P0.2   |

| 5   | RSL       | 21  | P0.1   |

| 6   | RSL2      | 22  | P0.0   |

| 7   | VSSA      | 23  | VCCD   |

| 8   | VREFH     | 24  | VDDD   |

| 9   | VREFL     | 25  | VSSD   |

| 10  | VTEMP_RET | 26  | VSSL   |

| 11  | VTEMP     | 27  | NC     |

| 12  | VTEMP_SUP | 28  | LIN    |

| 13  | VSSD      | 29  | NC     |

| 14  | XRES      | 30  | VDIAG  |

| 15  | P0.7      | 31  | VSENSE |

| 16  | P0.6      | 32  | VBAT   |

|     |           |     |        |

#### Table 532-QFN pin description

#### Descriptions of the power pins are as follows:

VDDD: Power supply for the digital section.

VDDA: Power supply for the analog section.

VSSD, VSSA: Ground pins for the digital and analog sections respectively.

VCCD: Power supply for the core (LV Logic)  $(1.8 V \pm 5\%)$

#### Figure 23 Pin assignment

### 3.1 Alternate pin functions

Each port pin can be assigned to one of multiple functions; it can, for example, be an analog I/O or a digital peripheral function. The pin assignments are shown in the following table.

| Name                      | Analog                                                                       |                | ACTIVE        |               |                     |                 | DEEP SLEEP |                    |

|---------------------------|------------------------------------------------------------------------------|----------------|---------------|---------------|---------------------|-----------------|------------|--------------------|

| Nume                      |                                                                              | ACT #0         | ACT #1        | ACT #2        | ACT #3              | DS #0           | DS #1      | DS #2              |

| P0.0                      | amuxbus_a/amuxbus_b tcpwm.tr_in[0] lin.lin_rx[0] scb.uart_rx:1 tcpwm.line[0] |                | tcpwm.line[0] | scb.spi_clk   |                     | scb.i2c_scl     |            |                    |

| P0.1                      | amuxbus_a/amuxbus_b                                                          | tcpwm.tr_in[1] | lin.lin_tx[0] | scb.uart_tx:1 | tcpwm.line_compl[0] | scb.spi_mosi    |            | scb.i2c_sda        |

| P0.2                      | amuxbus_a/amuxbus_b                                                          | tcpwm.tr_in[2] | lin.lin_en[0] |               | tcpwm.line[1]       | scb.spi_miso    |            |                    |

| P0.3                      | amuxbus_a/amuxbus_b                                                          | tcpwm.tr_in[3] |               |               | tcpwm.line_compl[1] | scb.spi_select0 |            |                    |

| P0.4                      | amuxbus_a/amuxbus_b                                                          | peri.virt_in_0 |               |               | tcpwm.line[2]       | scb.spi_select1 |            | cpuss.fault_out[1] |

| P0.5                      | amuxbus_a/amuxbus_b                                                          | srss.ext_clk   |               |               | tcpwm.line_compl[2] | scb.spi_select2 |            | cpuss.fault_out[0] |

| P0.6                      | amuxbus_a/amuxbus_b                                                          | peri.virt_in_1 |               |               |                     | scb.spi_select3 |            | cpuss.swd_data     |

| P0.7                      | amuxbus_a/amuxbus_b                                                          | peri.virt_in_2 |               |               |                     |                 |            | cpuss.swd_clk      |

| VTEMP_RET                 | pacss.vtemp_ret                                                              |                |               |               |                     |                 |            |                    |

| VTEMP (P1.1)              | pacss.vtemp                                                                  |                |               |               |                     |                 |            |                    |

| VTEMP_SUP                 | pacss.vtemp_sup                                                              |                |               |               |                     |                 |            |                    |

| VirtLinEn <sup>[1]</sup>  |                                                                              |                | lin.lin_en[1] |               |                     |                 |            |                    |

| VirtLinTxd <sup>[1]</sup> |                                                                              |                | lin.lin_tx[1] | scb.uart_tx   |                     |                 |            |                    |

| VirtLinRxd <sup>[1]</sup> |                                                                              |                | lin.lin_rx[1] | scb.uart_rx   |                     |                 |            |                    |

#### Table 6Alternate pin functions

34

**Electrical specifications**

#### **Electrical specifications** 4

#### Absolute maximum ratings 4.1

Within the maximum ratings, no damage shall occur. Parametric and functionality may deviate from specifications. All analog voltages are relative to V<sub>SSA</sub> and all digital voltages are relative to V<sub>SSD</sub>. A negative current if flowing out of a pin, and positive current into a pin.

| Table 7 Absolute maxin | mum ratings |

|------------------------|-------------|

|------------------------|-------------|

| Spec<br>ID# | Parameter                           | Description                                                                                           | Min   | Тур | Мах                      | Units | Details / Conditions                                                                                                        |

|-------------|-------------------------------------|-------------------------------------------------------------------------------------------------------|-------|-----|--------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------|

| SIDA1       | V <sub>ESDHBM</sub>                 | V <sub>HBM</sub> ESD on all pins                                                                      | ±2000 | _   | -                        | V     |                                                                                                                             |

| SIDA2       | V <sub>esdhv</sub>                  | ESD on LIN, V <sub>BAT</sub> , V <sub>SENSE</sub> , V <sub>DIAG</sub> , RSH,<br>RSL, RSH2, RSL2, GPIO | ±8000 | _   | _                        | V     | As per ISO10605<br>With required<br>external protection<br>as per the guidelines<br>in the <b>ESD protection</b><br>section |

| SIDA3       | V <sub>ESDCDMCOR</sub>              | CDM ESD on Corner Pins                                                                                | ±750  | Ι   | -                        | V     |                                                                                                                             |

| SIDA4       | V <sub>ESDCDM</sub>                 | CDM ESD on non-corner pins                                                                            | ±500  | Ι   | -                        | V     |                                                                                                                             |

| SIDA5       | V <sub>BAT</sub>                    | Supply voltage V <sub>BAT</sub> <sup>[2]</sup>                                                        | -0.3  | -   | 42                       | V     |                                                                                                                             |

| SIDA6       | V <sub>SHV</sub>                    | V <sub>SENSE</sub> /V <sub>DIAG</sub> ADC sense voltage <sup>[2]</sup>                                | -0.3  | -   | 42                       | V     |                                                                                                                             |

| SIDA7       | V <sub>SHV</sub>                    | V <sub>SENSE</sub> /V <sub>DIAG</sub> ADC sense voltage <sup>[2]</sup>                                | -40   | _   | 42                       | V     | With external 2.2-kΩ<br>resistor                                                                                            |

| SIDA8       | I <sub>SH</sub>                     | V <sub>SENSE</sub> /V <sub>DIAG</sub> current <sup>[2]</sup>                                          | -20   | Ι   | 1                        | mA    | Forced externally                                                                                                           |

| SIDA9       | I <sub>CS</sub>                     | R <sub>SH</sub> /R <sub>SL</sub> /R <sub>SH2</sub> /R <sub>SL2</sub> current <sup>[2]</sup>           | -1    | -   | 1                        | mA    | Forced externally                                                                                                           |

| SIDA10      | V <sub>LIN</sub>                    | LIN pin voltage <sup>[2]</sup>                                                                        | -27   | Ι   | 42                       | V     |                                                                                                                             |

| SIDA11      | I <sub>LIN</sub>                    | LIN pin current <sup>[2]</sup>                                                                        | -     | Ι   | 200                      | mA    |                                                                                                                             |

| SIDA12      | V <sub>GPIO</sub>                   | GPIO pin input voltage                                                                                | -0.5  | _   | V <sub>DDD</sub><br>+0.5 | V     |                                                                                                                             |

| SIDA13      | V <sub>DDA</sub> , V <sub>DDD</sub> | V <sub>DDA</sub> , V <sub>DDD</sub> supply voltage                                                    | -0.3  | Ι   | 4.7                      | V     |                                                                                                                             |

| SIDA13A     | I <sub>BAT</sub>                    | V <sub>BAT</sub> supply current <sup>[3]</sup>                                                        | -     | Ι   | 160                      | mA    |                                                                                                                             |

| SIDA13B     | I <sub>BATABSDC</sub>               | V <sub>BAT</sub> supply current, long-term<br>average                                                 | -     | _   | 40                       | mA    |                                                                                                                             |

| SIDA14      | V <sub>CCD</sub>                    | VCC core supply voltage                                                                               | -0.3  | Ι   | 1.95                     | V     |                                                                                                                             |

| SIDA16      | I <sub>GPIO</sub>                   | Current per GPIO pin                                                                                  | -20   | Ι   | 20                       | mA    |                                                                                                                             |

| SIDA17      | V <sub>SLV</sub>                    | RSHx, RSLx, VTEMP                                                                                     | -0.3  | _   | VDDA<br>+0.3             |       |                                                                                                                             |

| SIDA18      | Τ <sub>Α</sub>                      | Ambient temperature                                                                                   | -40   | Ι   | 125                      | °C    |                                                                                                                             |

| SIDA19      | Τ <sub>S</sub>                      | Storage temperature                                                                                   | -55   | Ι   | 125                      | °C    |                                                                                                                             |

| SIDA20      | Τ <sub>J</sub>                      | Junction temperature                                                                                  | -40   | -   | 150                      | °C    |                                                                                                                             |

| SIDA21      | T <sub>LIFE</sub>                   | Life time                                                                                             | 15    | _   | -                        | Years |                                                                                                                             |

| SIDA22      | T <sub>STORAGE1</sub>               | Storage time                                                                                          | 5     | _   | -                        | Years | T <sub>A</sub> = 55 °C, 85% r.H.                                                                                            |

| SIDA23      | T <sub>STORAGE2</sub>               | Storage time                                                                                          | 15    | -   | -                        | Years | T <sub>A</sub> =40 °C, 80% r.H.                                                                                             |

Notes

To prevent damage caused by high-voltage pulses, external protection (that is, series resistor, diode, TVS) may be required. To allow a minimum system level supply voltage of 4.5 V, external protection circuits including reverse protection diodes are designed in a way that guarantees the device minimum functional voltage V<sub>BAT</sub> of at least 3.6 V. 3. Absolute max current includes inrush / transient current during power-up.

#### PSoC<sup>™</sup> 4 HVPA-144K Based on 32-bit Arm<sup>®</sup> Cortex<sup>®</sup>-M0+

**Electrical specifications**

#### Table 7Absolute maximum ratings

| Spec<br>ID# | Parameter             | Description                                        | Min | Тур | Мах               | Units | Details / Conditions                  |

|-------------|-----------------------|----------------------------------------------------|-----|-----|-------------------|-------|---------------------------------------|

| SIDA24      | t                     | Short circuit tolerance time: HVREG <sup>[4]</sup> | -   | Ι   | 60                | min   | V <sub>BAT</sub> : 3.6 V to 28 V      |