# Primary side startup controller

## General description

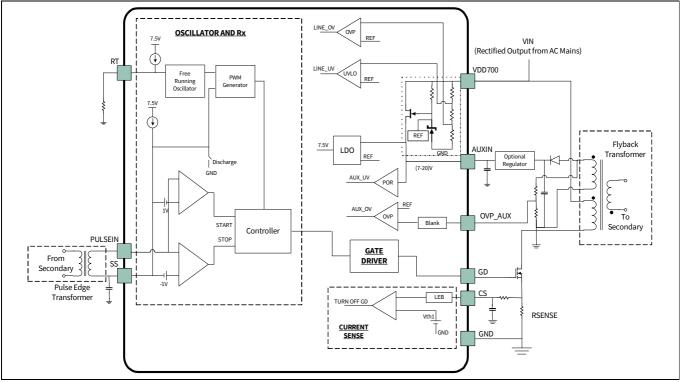

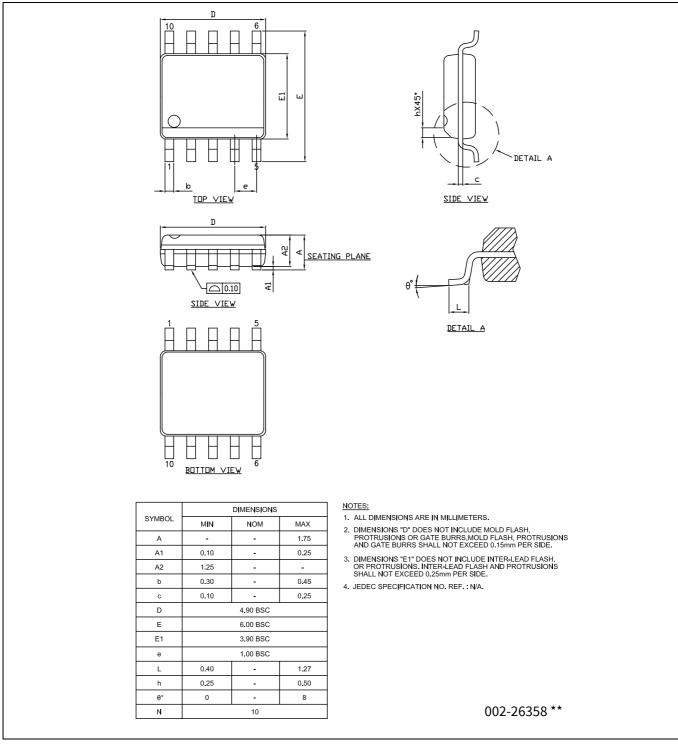

EZ-PD<sup>™</sup> PAG1P (<u>P</u>ower <u>A</u>dapter <u>G</u>eneration <u>1</u> <u>P</u>rimary) is Infineon's primary-side start-up controller for AC/DC applications targeting the mobile power adapter segment. EZ-PD<sup>™</sup> PAG1P interfaces directly with either the AC mains in an X-cap discharge mode or the DC output of a bridge rectifier. EZ-PD<sup>™</sup> PAG1P is available in a 10-pin SOIC package.

EZ-PD<sup>™</sup> PAG1P is designed for a secondary controlled AC/DC flyback converter topology. In this topology, voltage and current regulation is performed by the secondary controller. EZ-PD<sup>™</sup> PAG1P is responsible for providing the start-up function, driving the primary side FET as well as responding to fault conditions.

### Features

- Works across universal AC mains input 85 VAC to 265 VAC

- Low-side gate driver to drive primary side FET

- Line undervoltage protection (UVP) and line overvoltage protection

- Overcurrent protection (OCP)

- Overvoltage protection (OVP) during soft-start

- Programmable soft-start configurable with external capacitor

- Fixed auto-restart timer for fault recovery

- Supports X-cap discharge mode to obtain better efficiency

- Integrated high-voltage start-up and shunt regulator

- Synchronizes to PWM from secondary side using a pulse edge Transformer

### Functional block diagram

Table of contents

#### **Table of contents** .

| General description                              | 1  |

|--------------------------------------------------|----|

| Features                                         |    |

| Functional block diagram                         |    |

| Table of contents                                |    |

| 1 Pinout                                         |    |

| 2 Application overview                           |    |

| 3 Functional description                         | 7  |

| 3.1 Soft-start                                   |    |

| 3.2 X-cap mode                                   |    |

| 3.3 Secondary synchronization                    | 7  |

| 3.4 Power circuit                                |    |

| 3.5 Overcurrent and overvoltage fault protection |    |

| 3.6 Auto-restart timer                           | 8  |

| 3.7 Protection and fault condition               | 8  |

| 4 Electrical specifications                      | 11 |

| 5 Ordering information                           | 14 |

| 5.1 Ordering code definitions                    | 14 |

| 6 Packaging                                      |    |

| Revision history                                 | 16 |

Pinout

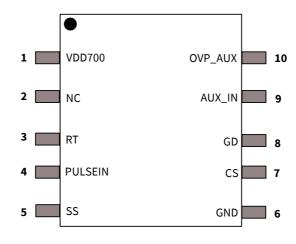

### 1 Pinout

#### Figure 1 Pin map

#### Table 1 EZ-PD<sup>™</sup> PAG1P pin description

| Pin number | Pin name | Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VDD700   | Start-up power supply input. VDD700 is the power supply source during the start-up phase. This pin can be connected to either the bridge rectifier output as shown in <b>Figure 2</b> , or directly to the AC mains through a diode as shown in <b>Figure 3</b> . This pin has a maximum voltage rating of 500 V.                                                                                                        |

| 2          | NC       | No connect                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3          | RT       | Timing resistor. The RT pin is used to connect to an external timing resistor of 499 k $\Omega$ which determines the free running oscillator frequency Fosc. Oscillator frequency is typically 30 kHz.                                                                                                                                                                                                                   |

| 4          | PULSEIN  | Pulse Edge Transformer (PET) input. Once the start-up phase is successfully complete, EZ-PD <sup>™</sup> PAG1P synchronizes to the secondary side pulses received at the PULSEIN input. The secondary controller provides PWM control information to the primary using a PET. The pulse amplitude shall not exceed V_PULSEINNEGAMP and V_PULSEINPOSAMP and the pulse width shall be in the T_PULSEINPW range.            |

| 5          | SS       | Soft-start pin. Connect a $0.1-\mu$ F capacitor to GND. The soft-start time is provided<br>in the specification section ( <b>Table 13</b> ). This pin also connects to the other end of<br>the pulse transformer. The external capacitor connected to the SS pin determines<br>the soft-start time. The duty cycle of the gate drive gradually increases to provide<br>a smooth transfer of power to the secondary side. |

| 6          | GND      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7          | CS       | Primary side current sense input. Current sense input is used to monitor the overcurrent fault scenario. Overcurrent fault is detected with the voltage between this input and ground exceeds V_CSTH1 threshold.                                                                                                                                                                                                         |

| 8          | GD       | Primary FET gate driver. EZ-PD <sup>™</sup> PAG1P integrates a low side gate driver to drive the gate of an external FET.                                                                                                                                                                                                                                                                                                |

Pinout

| Table 1 EZ-PD <sup>TM</sup> PAG1P pin description (continued) |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|---------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin number                                                    | Pin name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| 9                                                             | AUX_IN   | Auxiliary supply input. AUX_IN serves as the power supply source after the start-up phase. This pin should be connected to the output of auxiliary winding through a rectifier or a regulator depending on whether the maximum voltage on the output of the auxiliary winding exceeds 22 V. EZ-PD <sup>™</sup> PAG1P switches its power supply source to AUX_IN once the secondary side provides power.                                                      |  |  |  |  |  |  |

| 10                                                            | OVP_AUX  | Auxiliary winding overvoltage detection. EZ-PD <sup>™</sup> PAG1P monitors this pin for overvoltage condition on the secondary side, using an external resistor divider. Any voltage exceeding V_OVPAUXRISE on this pin is treated as an overvoltage fault condition. The overvoltage condition is monitored only during open loop operation. A Schottky diode to GND should be connected to ensure negative voltage is not seen when the gate driver is ON. |  |  |  |  |  |  |

#### Tabla 1 E7-DD™ DAG1D nin description (a ontin -1

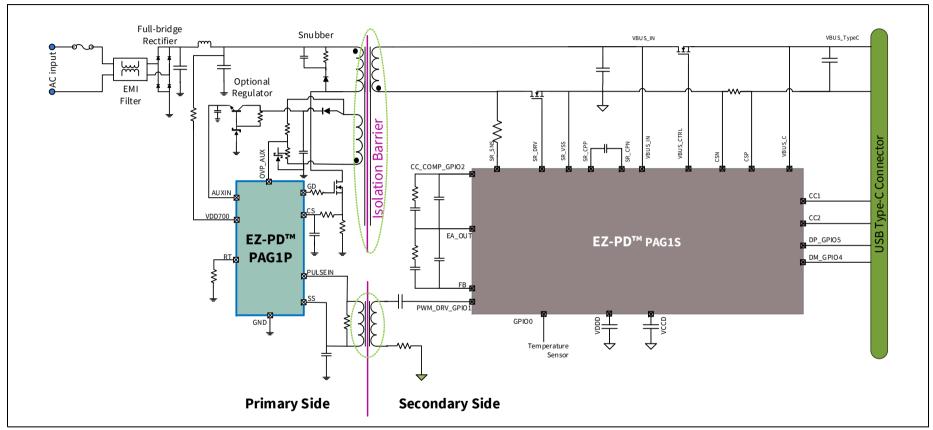

## Application overview

EZ-PD<sup>™</sup> PAG1P works with Infineon's secondary side controller EZ-PD<sup>™</sup> PAG1S. **Figure 2** shows the application diagram of a USB Power Delivery power adapter solution with 'EZ-PD<sup>™</sup> PAG1P + EZ-PD<sup>™</sup> PAG1S'. In this system, once the start-up phase is complete, the primary FET control is completely synchronized to the PWM pulses received from the secondary side. The PWM pulses are transmitted over an isolation barrier using a PET. EZ-PD<sup>™</sup> PAG1P takes over control of the primary FET only during power-up and system fault scenarios.

Figure 2 Type-C based mobile phone power adapter with EZ-PD<sup>™</sup> PAG1P (CYPAP111xx) and EZ-PD<sup>™</sup> PAG1S in a secondary controlled flyback topology configuration

Primary side startup controller

2

002-25572 Rev. \*F 2022-05-18

Application overview

Primary side startup controller

Full-bridge Snubber VBU S\_IN VBUS\_TypeC Rectifier AC input ٦n X çap Optional EMI Regulator Filter  $\leftrightarrow$ SR\_SEN SR\_GD RV Baı Isolation I Ş CC COMP GPIO2 AUXIN CC1 VDD700 CC2 EA\_OUT EZ-PD™ EZ-PD<sup>™</sup> PAG1S DP\_GPIO5 PAG1P RI DM\_GPIO4 Ş PULSEIN PWM\_DRV\_GPIO GPIO0 GND Temperature Sensor **Primary Side Secondary Side**

**Figure 3** shows the application diagram for a power adapter where EZ-PD<sup>™</sup> PAG1P is powered directly from the AC mains before the full bridge rectifier. This topology enables discharging the X cap using EZ-PD<sup>™</sup> PAG1P instead of using a passive resistor thereby improving efficiency.

Figure 3 Type-C based mobile phone power adapter with EZ-PD<sup>™</sup> PAG1P (CYPAP112xx) used in X-cap discharge configuration

Datasheet

002-25572 Rev. \*F 2022-05-18

### 3 Functional description

#### 3.1 Soft-start

The Soft-start feature allows EZ-PD<sup>™</sup> PAG1P to gradually increase the output voltage of the flyback converter till the secondary side takes control of the regulation. Soft-start is used during initial start-up sequence and fault condition. The duration of the soft-start is controlled by an external capacitor connected to the SS pin and the frequency of the soft-start is determined by an external resistor connected to the RT pin. An internal current source of 5 µA charges the external capacitor and the maximum amplitude for the soft-start ramp is 3.75 V. 3.75 V dictates the maximum duty cycle. Under Soft-start, the maximum ON time of the primary FET is limited to 19 µs which is equivalent to 70% duty cycle at 30 kHz. When the secondary side takes control, the maximum ON time is limited to 25 µs.

#### 3.2 X-cap mode

In EZ-PD<sup>™</sup> PAG1P X-cap part, X-cap mode is detected when 3 V\_VDD700UVRISE transitions occur within 64 ms. A flag is set indicating the part is operating in X-cap mode. When 3 V\_VDD700UVRISE transitions are not detected within 64 ms after the flag is set, a line disconnect is detected and an internal discharge path is turned ON to discharge the X-capacitor.

### 3.3 Secondary synchronization

During the start-up phase, if EZ-PD<sup>™</sup> PAG1P sees appropriate input pulses at the PULSEIN pin, then it synchronizes the primary FET control to the secondary pulses. The PWM control signal from the secondary side is coupled to the primary side using a Pulse Edge Transformer (PET). The PET is an important component to ensure proper frequency response and should have just an adequate Q-factor to avoid excessive overshoot. The positive pulse from the PET is treated as primary FET turn-on signal and the negative pulse from the PET is treated as primary FET turn-off signal. The pulse amplitude shall not exceed V\_PULSEINNEGAMP and V\_PULSEINPOSAMP and the pulse width shall be within T\_PULSEINPW range.

The synchronization path between the secondary and primary through the PET is also used for communication of shutdown condition. Three consecutive negative pulses from the secondary side is treated as a shutdown signal. On receiving such three consecutive negative pulses, EZ-PD<sup>™</sup> PAG1P will shutdown after 200 ms.

#### **3.4 Power circuit**

EZ-PD<sup>™</sup> PAG1P integrates a high voltage start-up regulator. During power-up, EZ-PD<sup>™</sup> PAG1P shall be powered from the line input via the VDD700 pin. Once voltage on the auxiliary winding is available from the secondary side, EZ-PD<sup>™</sup> PAG1P switches its power supply input to AUX\_IN pin and no power will be sourced from the VDD700 pin.

### 3.5 Overcurrent and overvoltage fault protection

EZ-PD<sup>™</sup> PAG1P implements overcurrent protection. When the CS pin voltage exceeds V\_CSTH1, EZ-PD<sup>™</sup> PAG1P limits the primary current by turning OFF the primary FET.

EZ-PD<sup>™</sup> PAG1P provides three types of voltage protection – protection against line undervoltage/overvoltage and secondary overvoltage. The line undervoltage/overvoltage monitoring is via VDD700 pin and the respective thresholds are V\_VDDUVRISE and V\_VDDOVRISE. Gate pulses are turned off until fault is removed. Once the voltage on VDD700 is within operating range, EZ-PD<sup>™</sup> PAG1P does an auto-restart.

In addition, EZ-PD<sup>™</sup> PAG1P monitors the voltage on OVP\_AUX pin for detecting overvoltage condition on the secondary side. The voltage on the OVP\_AUX pin is a scaled-down version of the secondary side voltage. When voltage on OVP\_AUX exceeds V\_OVPAUXRISE, the gate driver is turned off. Once the voltage on OVP\_AUX goes below the fault range, EZ-PD<sup>™</sup> PAG1P does an auto-restart. EZ-PD<sup>™</sup> PAG1P monitors secondary overvoltage only during start-up phase or during fault condition after auto-restart.

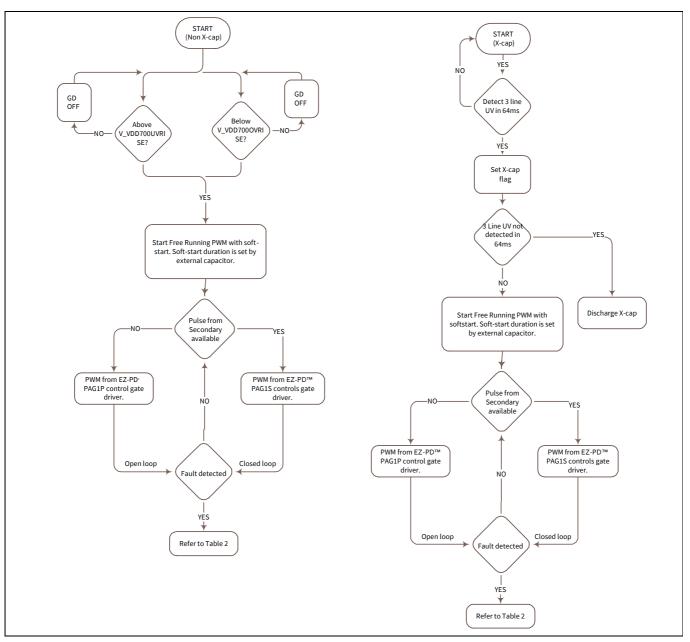

The flow chart in **Figure 4** and the **Functional block diagram** show the operation of the chip.

#### 3.6 Auto-restart timer

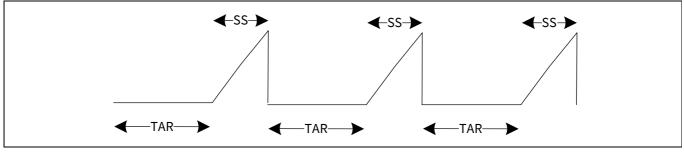

A fixed timer of TAR sec is available for various fault conditions. The timer is operated from a free running oscillator inside EZ-PD<sup>™</sup> PAG1P. Free running oscillator will be running at Fosc.

### 3.7 Protection and fault condition

Primarily there are four types of protection actions used in various fault conditions.

- 1. Autorestart: In this mode, EZ-PD<sup>™</sup> PAG1P will wait TAR sec before doing a soft start. This sequence is repeated continuously (see **Figure 5**).

- 2. Latch or shutdown: No auto-restart timer or soft start is implemented. Shuts the IC immediately and power to the IC needs to be removed to unlatch.

- 3. Gate OFF: This only turns OFF the gate drive pulse and waits for the fault condition to pass before the IC functions normally.

- 4. Max duty cycle: Gate driver will be ON for 19 μs (maximum) during soft-start. When secondary is in control, gate drive will be ON for 25 μs (maximum).

| Table 2 | Faults conditions and protection action |

|---------|-----------------------------------------|

|---------|-----------------------------------------|

| Sl# | Fault                                                                      | Action                                                                                                                                                                                     |

|-----|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VDD700 pin is under threshold voltage<br>V_VDD700UVRISE                    | Gate driver output is low. When VDD700 exceeds V_VDD700UVRISE, do a soft-start followed by Autore-start.                                                                                   |

| 2   | VDD700 pin exceeds threshold voltage<br>V_VDD7000VRISE                     | Gate driver output is low during fault condition followed by Autorestart.                                                                                                                  |

| 3   | OVP_AUX pin exceeds threshold voltage<br>V_OVPAUXRISE                      | Gate driver output is low during fault condition<br>followed by Autorestart. This is valid only when<br>EZ-PD™ PAG1P is operating in open loop.                                            |

| 4   | CS pin exceeds threshold voltage V_CSTH1                                   | Gate driver output is low during fault condition. In<br>open loop, do the Autorestart after fault condition is<br>removed. In closed loop, wait for the next pulse from<br>secondary side. |

| 6   | Stop command from Secondary side                                           | Shutdown after 200 ms.                                                                                                                                                                     |

| 7   | Receive no pulses from Secondary side for TAR sec<br>after last stop pulse | Autorestart                                                                                                                                                                                |

| 8   | Start pulse and no Stop pulse from Secondary side                          | Keep gate driver ON for 25 µs. EZ-PD™ PAG1P will wait<br>for TAR sec before doing Autorestart.                                                                                             |

Figure 4 EZ-PD<sup>™</sup> PAG1P operation flow chart

Figure 5 Auto-restart

Electrical specifications

## 4 Electrical specifications

#### Table 3Absolute maximum ratings

| Description                                  | Min  | Тур | Мах  | Unit | <b>Details/conditions</b>                                                                                            |

|----------------------------------------------|------|-----|------|------|----------------------------------------------------------------------------------------------------------------------|

| Voltage on VDD700                            | 0    | _   | 500  | V    | -                                                                                                                    |

| Output current on GD                         | -1   | _   | 1    | А    | -                                                                                                                    |

| Voltage on AUX_IN                            | 0    | _   | 22   |      | -                                                                                                                    |

| Voltage on CS, SS, OVP_AUX                   | -0.3 | _   | 8.25 | V    | _                                                                                                                    |

| Voltage on RT                                | 0    | _   | 8.25 | V    | _                                                                                                                    |

| Voltage on PULSEIN                           | -5   | _   | 8.25 |      | _                                                                                                                    |

| Operating junction temperature               | -40  | _   | 125  |      | -                                                                                                                    |

| Storage temperature                          | -55  | _   | 150  | °C   | _                                                                                                                    |

| Ambient temperature                          | -40  | _   | 105  |      | _                                                                                                                    |

| Electrostatic discharge human body model     | 2000 | _   | _    | V    | -                                                                                                                    |

| Electrostatic discharge charged device model | 500  | _   | _    | V    | -                                                                                                                    |

| Pin current for latch-up                     | -100 | _   | 100  | mA   | Except for SS and OVP_AUX<br>For SS and OVP_AUX, use<br>-0.5 V.<br>For RT, negative injection is<br>not recommended. |

#### Table 4Silicon power specifications

| Spec ID      | Parameter        | Description                                       | Min  | Тур | Мах | Unit | Details/conditions                                                             |

|--------------|------------------|---------------------------------------------------|------|-----|-----|------|--------------------------------------------------------------------------------|

| SID.VDD700.1 | VDD700           | High voltage supply                               | 120  | _   | 380 | v    | -                                                                              |

| SID.AUXIN.1  | V_AUXIN          | Auxiliary supply                                  | 13   | _   | 20  | v    | _                                                                              |

| SID.PWR.1    | I_VDD700_LATCH   | Current from<br>VDD700 (VDD700 =<br>325 V)        | _    | 50  | _   |      | EZ-PD™ PAG1P is in<br>shutdown.                                                |

| SID.PWR.2    | I_VDD700_NOGD    | Current from<br>VDD700 (VDD700 =<br>325 V)        | _    | 350 | _   |      | All circuits active except gate driver not toggling                            |

| SID.PWR.3    | I_VDD700_ACTIVE  | Current from<br>VDD700 (VDD700 =<br>325 V)        | _    | 800 | _   | μA   | All circuits active including<br>gate driver toggling at<br>30 kHz; CL = 1 nF. |

| SID.PWR.4    | I_AUXIN_NOGD     | Current from AUXIN<br>(AUXIN = 12 V)              | _    | 350 | _   |      | All circuits active except gate driver not toggling                            |

| SID.PWR.5    | I_AUXIN_ACTIVE   | Current from AUXIN<br>(AUXIN = 12 V)              | _    | 800 | _   |      | All circuits active including<br>gate driver toggling at<br>30 kHz; CL = 1 nF. |

| SID.PWR.6    | I_VDD700_STARTUP | Current from<br>VDD700 when<br>starting up        | _    | 10  | _   | mA   | VDD700 = 325 V; AUXIN = 0 V                                                    |

| SID.PWR.7    | I_XCAP_DISCHARGE | Current from<br>VDD700 while<br>discharging X-cap | 0.48 | 1.7 | 2   | IIIA | _                                                                              |

**Electrical specifications**

#### Table 5Undervoltage and overvoltage on VDD700

| Spec ID      | Parameter      | Description                           | Min | Тур | Мах | Unit | Details/conditions |

|--------------|----------------|---------------------------------------|-----|-----|-----|------|--------------------|

| SID.VDD700.2 | V_VDD700UVRISE | Undervoltage rising threshold         | 90  | 100 | 115 |      | -                  |

| SID.VDD700.3 | V_VDD700UVFALL | Undervoltage falling threshold        | 81  | 90  | 110 | V    | -                  |

| SID.VDD700.4 | V_VDD700OVRISE | Overvoltage rising threshold          | 400 | 430 | 490 | V    | -                  |

| SID.VDD700.5 | V_VDD700OVFALL | Overvoltage falling threshold         | 395 | 420 | 480 |      | -                  |

| SID.VDD700.6 | T_VDD700UVDB   | Debounce time<br>undervoltage falling | —   | 30  | _   | ms   | -                  |

#### Table 6Overvoltage on AUXIN

| Spec ID      | Parameter    | Description                                                       | Min | Тур | Мах  | Unit | Details/conditions |

|--------------|--------------|-------------------------------------------------------------------|-----|-----|------|------|--------------------|

| SID.OVPAUX.1 | V_OVPAUXRISE | Overvoltage<br>threshold on<br>OVP_AUX                            | 1.1 | 1.2 | 1.26 | V    | -                  |

| SID.OVPAUX.3 | T_OVPAUXBLK  | Blanking time on<br>OVP_AUX when GD<br>output goes high to<br>low | 0.9 | 1.1 | 1.3  | μs   | _                  |

Table 7 Gate driver

| Spec ID  | Parameter | Description                                       | Min | Тур | Мах | Unit | Details/conditions      |

|----------|-----------|---------------------------------------------------|-----|-----|-----|------|-------------------------|

| SID.GD.1 | V_GDVOL   | GD Low Level Output<br>voltage                    | _   | 1   | 2   | v    | AUXIN = 12 V and        |

| SID.GD.2 | V_GDVOH   | GD High Level<br>Output voltage                   | 8   | 10  | _   | V    | sinking 200 mA          |

| SID.GD.3 | T_GDTR    | Rise time                                         | -   | 25  | 60  |      | CL = 1 nF, AUXIN = 12 V |

| SID.GD.4 | T_GDTF    | Fall time                                         |     | 20  | 37  |      |                         |

| SID.GD.5 | T_GDPDR   | Delay time from<br>PULSEIN to GD,<br>rising edge  | _   | 90  | 125 | ns   |                         |

| SID.GD.6 | T_GDPDF   | Delay time from<br>PULSEIN to GD,<br>falling edge |     | 70  | 100 |      |                         |

#### Table 8Current sense fault protection

| Spec ID  | Parameter | Description                      | Min | Тур | Мах | Unit | Details/conditions |

|----------|-----------|----------------------------------|-----|-----|-----|------|--------------------|

| SID.CS.1 | V_CSTH1   | Threshold voltage pulse-by-pulse | 430 | 500 | 550 | mV   | _                  |

| SID.CS.3 | T_CSPD    | Delay time from CS<br>to GD      | _   | _   | 160 | ns   | CL = 1 nF          |

| SID.CS.4 | T_CSLEB   | Leading edge<br>blanking time    | 150 | 250 | 300 |      | _                  |

Electrical specifications

| Table 9 PULSEIN |                 |                                              |     |     |     |      |                    |

|-----------------|-----------------|----------------------------------------------|-----|-----|-----|------|--------------------|

| Spec ID         | Parameter       | Description                                  | Min | Тур | Мах | Unit | Details/conditions |

| SID.PULSEIN.1   | V_PULSEINNEGAMP | Minimum negative<br>going pulse<br>amplitude | -4  | -2  | _   | V    | _                  |

| SID. PULSEIN.2  | V_PULSEINPOSAMP | Maximum positive<br>going pulse<br>amplitude | _   | 2   | 4   | V    | _                  |

| SID. PULSEIN.3  | T_PULSEINPW     | Pulse Width                                  | 25  | _   | 200 | ns   | _                  |

#### Table 10Free running oscillator

| Spec ID   | Parameter | Description        | Min | Тур | Мах | Unit | Details/conditions                                                |

|-----------|-----------|--------------------|-----|-----|-----|------|-------------------------------------------------------------------|

| SID.OSC.1 | FOSC      | Frequency          | 27  | 30  | 38  | kHz  | F <sub>OSC</sub> = (I_RTCURR) *<br>(1/5 pF) * (1/4 V) =<br>30 kHz |

| SID.OSC.2 | DCMIN     | Minimum duty cycle | 3   | _   | _   | %    | _                                                                 |

| SID.OSC.3 | DCMAX     | Maximum duty cycle | _   | _   | 70  | 90   | _                                                                 |

#### Table 11 Timing resistor

| Spec ID  | Parameter | Description        | Min | Тур        | Мах | Unit | Details/conditions |

|----------|-----------|--------------------|-----|------------|-----|------|--------------------|

| SID.RT.1 | RT        | Timing resistor    | _   | 499±<br>1% | _   | kΩ   | _                  |

| SID.RT.2 | I_RTCURR  | Current through RT | _   | 2.4±<br>5% | _   | μA   | _                  |

#### Table 12Auto-restart time

| Spec ID  | Parameter | Description       | Min | Тур | Мах | Unit        | Details/conditions |

|----------|-----------|-------------------|-----|-----|-----|-------------|--------------------|

| SID.AR.1 | TAR       | Auto-restart time | _   | 2   | _   | Seco<br>nds | _                  |

#### Table 13Soft-start capacitor charging current

| Spec ID  | Parameter | Description                               | Min | Тур | Мах | Unit | Details/conditions                                                                                          |

|----------|-----------|-------------------------------------------|-----|-----|-----|------|-------------------------------------------------------------------------------------------------------------|

| SID.SS.1 | I_SSCURR  | Current for charging soft-start capacitor | _   | 4.8 | 6   | μΑ   | Soft-start time =<br>I/C V/s; Maximum<br>soft-start voltage is<br>3.75 V and start of<br>soft-start is 1 V. |

Ordering information

## 5 Ordering information

#### Table 14 Ordering part number

| Mode       | Package type               | Silicon revision      |  |

|------------|----------------------------|-----------------------|--|

| Non V con  |                            |                       |  |

| - попх-сар | 10 pin SOIC                | A3                    |  |

| V con      | - 10-pin SOIC              |                       |  |

| – л-сар    |                            |                       |  |

|            | Mode<br>Non X-cap<br>X-cap | Non X-cap 10-pin SOIC |  |

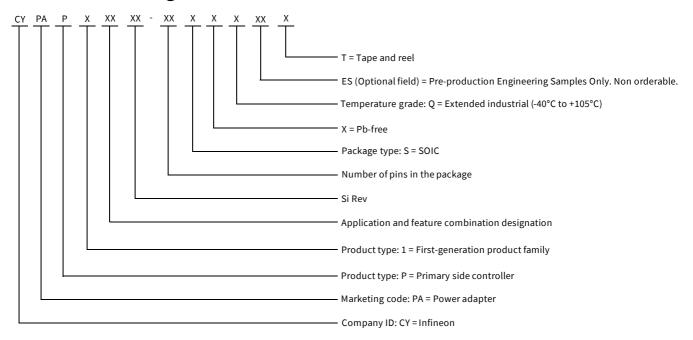

### 5.1 Ordering code definitions

Packaging

## 6 Packaging

**Revision history**

### **Revision history**

| Document<br>version | Date of release | Description of changes                                                                                                                                                                           |

|---------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *D                  | 2019-12-10      | Changed datasheet status to final                                                                                                                                                                |

| *E                  | 2020-06-18      | Updated SID.OSC.1 parameter min value from 24 to 27 and max value from 36 to 38 in <b>Table 10</b>                                                                                               |

| *F                  | 2022-05-18      | Updated to Infineon template<br>Changed part numbers from CYPAP111A3-10SXQES and CYPAP112A3-10SXQES<br>to CYPAP111A3-10SXQT and CYPAP112A3-10SXQT in <b>"Ordering information"</b><br>on page 14 |

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2022-05-18 Published by Infineon Technologies AG 81726 Munich, Germany

© 2022 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document? Go to www.infineon.com/support

Document reference 002-25572 Rev. \*F

#### **IMPORTANT NOTICE**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Infineon:

CYPAP111A3-10SXQ CYPAP111A3-10SXQT CYPAP112A3-10SXQ CYPAP112A3-10SXQT