## ISOFACE™

#### ISO2H823V2.5

#### Overview

The 2nd generation of Infineon Technologies ISOFACE™ 8-channel high-side driver IC ISO2H823V2.5 offers a 2.5 kV galvanic isolation meeting the IEC 61131-2 requirements for reinforced isolation. Concurrently, the ISO2H823V2.5 sets a new standard for system–level diagnostics: each of the 8 channels is equipped with a 5-fold diagnostic monitoring capability: open load in active mode (channel "ON"), open load in inactive mode (channel "OFF"), short-circuit to Vbb, short-circuit to GND and overtemperature.

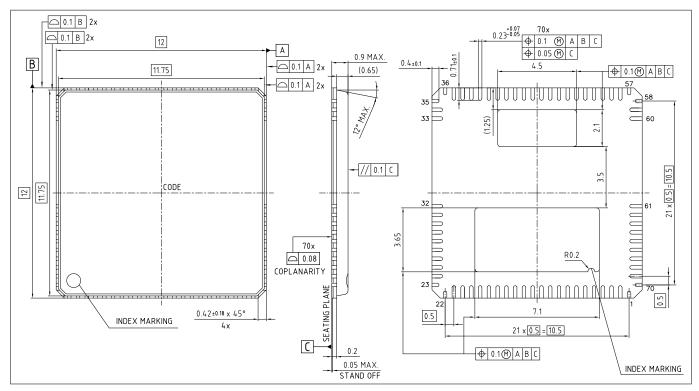

PG-VQFN-70

With the ever increasing level of complexity and integration in industrial control systems comprehensive diagnostic monitoring is highly valuable in a vast range of industrial applications, both for preventive maintenance as well as to shorten or avoid costly un-scheduled down-times.

#### **Product Highlights**

- 2.5 kV galvanic isolation integrated (UL508 & CSA22.2 certified) meeting IEC 61131-2 requirements for reinforced isolation

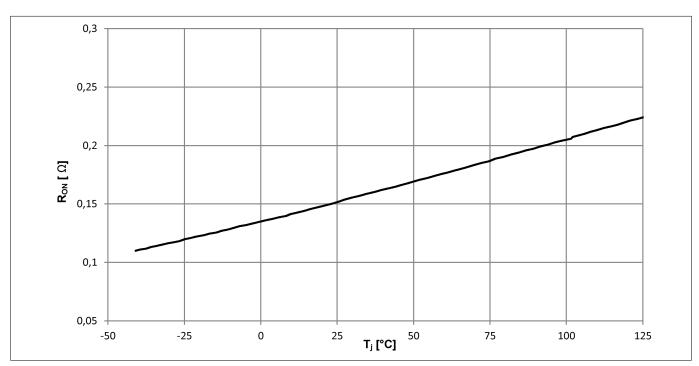

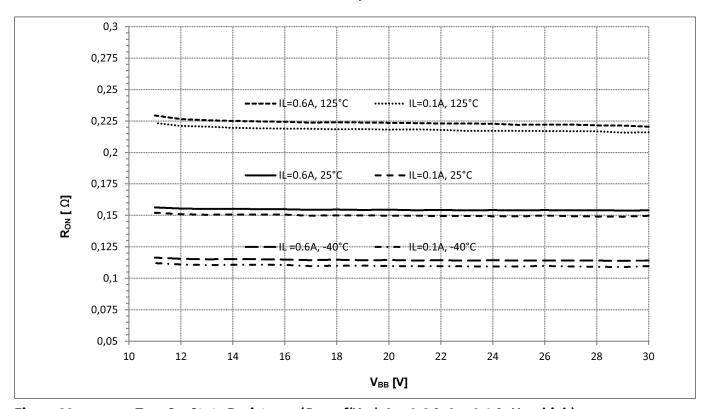

- 8 channel protected high-side switch with nominal current up to 600 mA per channel and 150 m $\Omega$  typ R<sub>ON</sub> (25°C)

- Comprehensive diagnostic feedback for each channel

- µController compatible 8-bit parallel/serial interface

- 12 mm x 12 mm PG-VQFN-70 package

#### **Key Features**

- Interface 3.3 V CMOS operation compatible

- Parallel/Serial µC interface

- High common mode transient immunity

- Integrated diagnostics:

- 5-fold diagnostic feedback per output channel: Open load in "ON"- and "OFF"-state, short circuit-to GND and short-circuit to supply, overtemperature

- 5-fold diagnostic feedback in addition reported on global level

- Common output disable pin

- Common error indication pin

- · Resynchronization to achieve low jitter when switching the high-side switch ON and OFF

- Active output current limitation for short circuit protection

- Reverse Output Voltage protection

- Undervoltage shutdown with auto-restart and hysteresis

- Integrated clamping to switch inductive loads up to 150 mJ energy per channel

- Thermal shutdown and diagnostics per channel with auto-restart

- V<sub>BB</sub> range from 11 V to 35 V designed for 24 V systems

| Туре         | Package    |

|--------------|------------|

| ISO2H823V2.5 | PG-VQFN-70 |

- ESD protection

- RoHS compliant

#### ISOFACE<sup>™</sup> ISO2H823V2.5

## infineon

#### Overview

#### **Typical Application**

- Isolated switch for industrial applications:

PLC, distributed control systems, industial PCs, robotics, etc.

- All types of resistive, inductive and capacitive loads

- μController compatible power switch for 24 V DC applications

- Driver for solenoid, relays and resistive loads

#### **Description**

The ISO2H823V2.5 is a galvanically isolated 8-bit data interface in PG-VQFN-70 package that provides 8 fully protected high-side power switches that are able to handle currents up to 730 mA per channel.

An 8-bit parallel  $\mu$ Controller compatible interface or a serial SPI-interface allows to connect the IC directly to a  $\mu$ Controller system. The input interface supports also a direct control mode for writing driver information and is designed to operate with 3.3 V CMOS compatible levels.

The data transfer from input to output side is realized by the integrated Coreless Transformer Technology.

This product is the second generation of isolated 8 channel digital output device (ISO2H823V2.5) and provides a robust integrated diagnosis for switches with low  $R_{ON}$  as well as an upgraded  $\mu$ Controller interface.

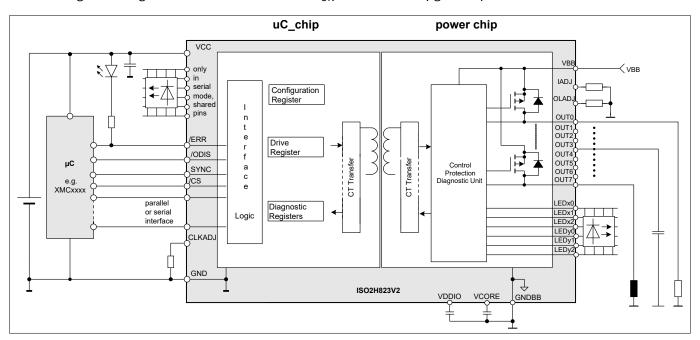

Figure 1 Typical Application

#### **Infineon Ordering Code:**

SP001225470

#### **Table of contents**

### **Table of contents**

|         | Overview                                                  | 1  |

|---------|-----------------------------------------------------------|----|

|         | Table of contents                                         | 3  |

| 1       | Pin configuration and functionality                       | 5  |

| 1.1     | Pin functionality                                         | 9  |

| 1.1.1   | Pins of power interface                                   | 9  |

| 1.1.2   | Pins of serial and parallel logic interface               | 9  |

| 2       | Block diagram                                             | 12 |

| 3       | Functional description                                    | 14 |

| 3.1     | Introduction                                              | 14 |

| 3.2     | Microcontroller interface                                 | 14 |

| 3.2.1   | Parallel interface mode                                   | 14 |

| 3.2.1.1 | Parallel direct mode                                      | 15 |

| 3.2.2   | Serial interface mode                                     | 16 |

| 3.2.2.1 | SPI modes                                                 | 17 |

| 3.2.2.2 | Daisy chain mode                                          | 19 |

| 3.2.2.3 | Cyclic Redundancy Check CRC                               | 20 |

| 3.2.3   | Common error indication output                            | 21 |

| 3.2.4   | Update of the diagnostic registers                        | 22 |

| 3.2.5   | SYNC operation                                            | 22 |

| 3.2.5.1 | SYNC-signal for drive-signals                             | 22 |

| 3.2.5.2 | SYNC-signal for diagnostics                               | 23 |

| 3.2.6   | ODIS output disable                                       | 25 |

| 3.2.7   | LEDGOFF                                                   | 25 |

| 3.2.8   | OLOFF                                                     | 26 |

| 3.2.9   | RESET (Hard and Soft)                                     | 26 |

| 3.2.9.1 | Hardware reset                                            | 26 |

| 3.2.9.2 | Soft reset                                                | 26 |

| 3.2.10  | Resynchronization of CT-Transmission                      | 26 |

| 3.3     | Output stage                                              | 28 |

| 3.3.1   | Output stage control                                      | 28 |

| 3.3.2   | Protection functionality                                  | 29 |

| 3.3.2.1 | Power transistor overvoltage protection                   | 29 |

| 3.3.2.2 | Power transistor overload protection                      | 29 |

| 3.3.2.3 | Current sense and limitation                              | 29 |

| 3.3.3   | Diagnostic functions                                      | 29 |

| 3.3.3.1 | Diagnostics in inactive mode                              | 31 |

| 3.3.3.2 | Diagnostics in active mode                                | 31 |

| 3.3.3.3 | Diagnostic scenarios in dependence of switching frequency | 32 |

#### **Table of contents**

| 3.3.3.4 | Global diagnostics                                                     | 33 |

|---------|------------------------------------------------------------------------|----|

| 3.3.3.5 | Power supply                                                           |    |

| 3.3.4   | LED matrix                                                             | 35 |

| 3.3.4.1 | LED matrix on the process side                                         |    |

| 3.3.4.2 | LED matrix on the uController side (only in serial communication mode) |    |

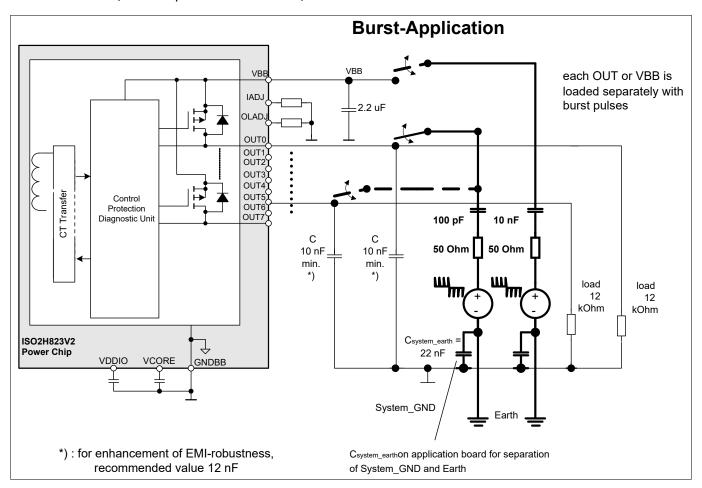

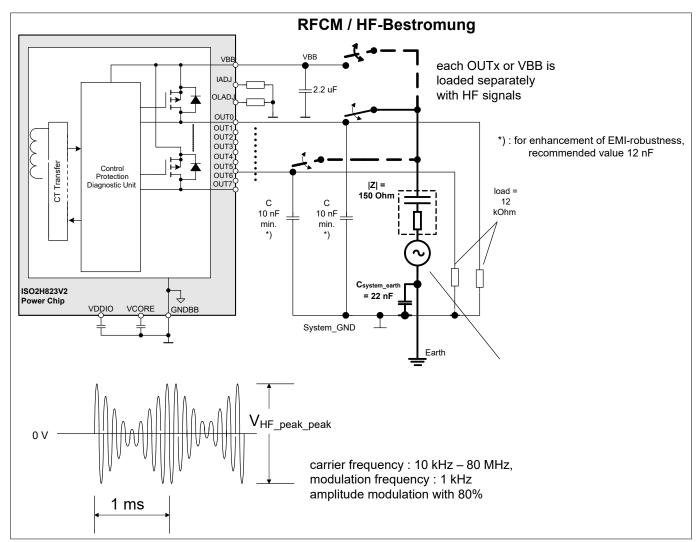

| 3.4     | EMI-Robustness                                                         |    |

| 3.4.1   | Burst robustness                                                       |    |

| 3.4.2   | RFCM-Robustness                                                        |    |

| 3.5     | Application hints                                                      |    |

| 3.5.1   | Layout recommendations                                                 | 39 |

| 4       | Electrical characteristics                                             | 41 |

| 4.1     | Absolute maximum ratings                                               | 41 |

| 4.2     | Operating conditions and power supply                                  | 42 |

| 4.3     | Load switching capabilities and characteristics                        | 45 |

| 4.4     | Output protection functions                                            |    |

| 4.5     | Electrical characteristics µController interface                       | 46 |

| 4.6     | Diagnostics                                                            | 50 |

| 4.7     | Isolation and safety-related specification                             | 51 |

| 4.8     | Reliability                                                            | 51 |

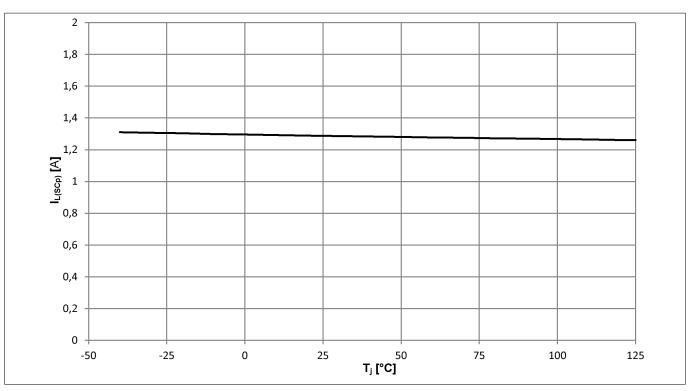

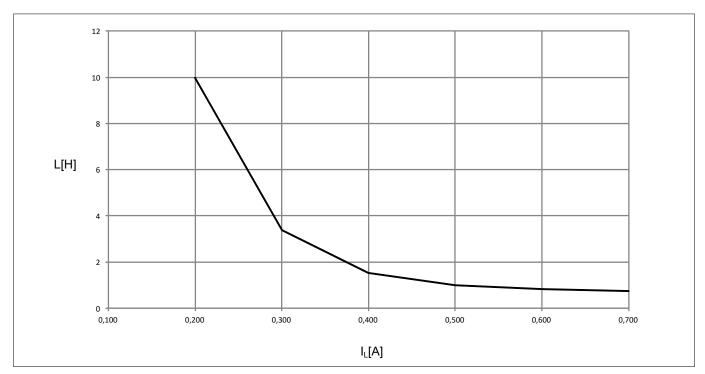

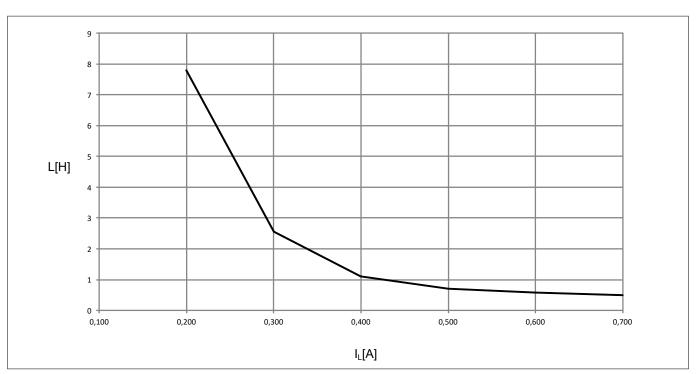

| 4.9     | Typical performance characteristics                                    | 52 |

| 5       | μController interface registers                                        | 57 |

| 5.1     | User registers                                                         | 58 |

| 5.1.1   | Output Driver register                                                 | 58 |

| 5.1.2   | Output Driver register for resynchronization                           | 59 |

| 5.1.3   | Collective Diagnostics register                                        | 60 |

| 5.1.4   | Global Error register                                                  | 62 |

| 5.1.5   | Channel Diagnostics Configuration register                             | 62 |

| 5.1.6   | Diagnostics registers for channel-x                                    | 64 |

| 5.1.7   | Other channel diagnostics registers                                    | 65 |

| 5.1.8   | Internal Error register                                                | 65 |

| 5.1.9   | Global Configuration register                                          | 67 |

| 6       | Package: Outlines and marking pattern                                  | 69 |

|         | Revision history                                                       | 70 |

|         | Disclaimer                                                             | 71 |

## infineon

#### 1 Pin configuration and functionality

## 1 Pin configuration and functionality

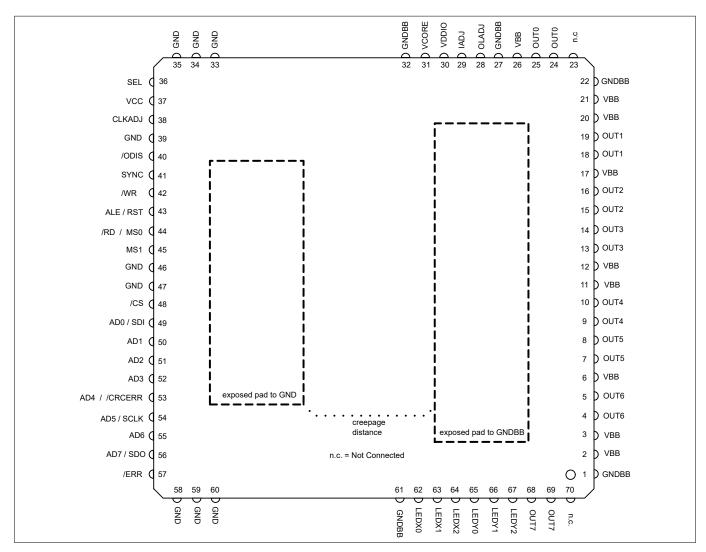

Figure 2 Power PG-VQFN-70 (430 mil)

Table 1 Pin configuration

| Pin   | Parallel Ir               | nterfac | e Mode   |                                 | Serial Interface Mode |      |          |  |  |

|-------|---------------------------|---------|----------|---------------------------------|-----------------------|------|----------|--|--|

|       | Symbol Ctrl Type Function |         | Function | Symbol                          | Ctrl                  | Туре | Function |  |  |

| top s | ide pins                  |         | 1        | 1                               |                       |      | 1        |  |  |

| 1     | GNDBB                     |         | А        | Output Stage Ground             | GNDBB                 |      |          |  |  |

| 2     | VBB                       |         | А        | Output Stage Positive<br>Supply | VBB                   |      |          |  |  |

| 3     | VBB                       |         | А        | Output Stage Positive<br>Supply | VBB                   |      |          |  |  |

| 4     | OUT6                      |         | А        | Switch Output 6                 | OUT6                  |      |          |  |  |

| 5     | OUT6                      |         | Α        | Switch Output 6                 | OUT6                  |      |          |  |  |

(table continues...)

## infineon

### 1 Pin configuration and functionality

Table 1 (continued) Pin configuration

| Pin | Parallel In | nterfac | e Mode         |                                                                  | Serial Inte | rface Mo | de      |          |

|-----|-------------|---------|----------------|------------------------------------------------------------------|-------------|----------|---------|----------|

|     | Symbol      | Ctrl 1) | <b>Type 2)</b> | Function                                                         | Symbol      | Ctrl     | Туре    | Function |

| 6   | VBB         |         | А              | Output Stage Positive<br>Supply                                  | VBB         |          |         |          |

| 7   | OUT5        |         | Α              | Switch Output 5                                                  | OUT5        |          |         |          |

| 8   | OUT5        |         | А              | Switch Output 5                                                  | OUT5        |          |         |          |

| 9   | OUT4        |         | А              | Switch Output 4                                                  | OUT4        |          |         |          |

| 10  | OUT4        |         | Α              | Switch Output 4                                                  | OUT4        |          |         |          |

| 11  | VBB         |         | А              | Output Stage Positive<br>Supply                                  | VBB         |          |         |          |

| 12  | VBB         |         | А              | Output Stage Positive<br>Supply                                  | VBB         |          |         |          |

| 13  | OUT3        |         | А              | Switch Output 3                                                  | OUT3        |          |         |          |

| 14  | OUT3        |         | Α              | Switch Output 3                                                  | ОИТ3        |          |         |          |

| 15  | OUT2        |         | Α              | Switch Output 2                                                  | OUT2        |          |         |          |

| 16  | OUT2        |         | Α              | Switch Output 2                                                  | OUT2        |          |         |          |

| 17  | VBB         |         | А              | Output Stage Positive<br>Supply                                  | VBB         |          |         |          |

| 18  | OUT1        |         | Α              | Switch Output 1                                                  | OUT1        |          |         |          |

| 19  | OUT1        |         | А              | Switch Output 1                                                  | OUT1        |          |         |          |

| 20  | VBB         |         | А              | Output Stage Positive<br>Supply                                  | VBB         |          |         |          |

| 21  | VBB         |         | А              | Output Stage Positive<br>Supply                                  | VBB         |          |         |          |

| 22  | GNDBB       |         | А              | Output Stage Ground                                              | GNDBB       |          |         |          |

| 23  | n.c.        | not c   | onnect         | ed                                                               | n.c.        | not c    | onnecte | d        |

| 24  | OUT0        |         | Α              | Switch Output 0                                                  | ОИТО        |          |         |          |

| 25  | OUT0        |         | Α              | Switch Output 0                                                  | ОИТО        |          |         |          |

| 26  | VBB         |         | A              | Output Stage Positive<br>Supply, Supply of<br>Reference Voltages | VBB         |          |         |          |

| 27  | GNDBB       |         | А              | Output Stage Ground                                              | GNDBB       |          |         |          |

| 28  | OLADJ       |         | Α              | Open Load Adjust                                                 | OLADJ       |          |         |          |

| 29  | IADJ        |         | А              | Current Reference Adjust                                         | IADJ        |          |         |          |

| 30  | VDDIO       |         | А              | CT Blocking Capacitor                                            | VDDIO       |          |         |          |

| 31  | VCORE       |         | Α              | Digital Core Supply                                              | VCORE       |          |         |          |

(table continues...)

# infineon

### 1 Pin configuration and functionality

Table 1 (continued) Pin configuration

| Pin   | Parallel In   | iterfac | e Mode         |                                    | Serial Interface Mode |      |             |                       |  |  |

|-------|---------------|---------|----------------|------------------------------------|-----------------------|------|-------------|-----------------------|--|--|

|       | Symbol        | Ctrl 1) | <b>Type</b> 2) |                                    |                       | Ctrl | Туре        | Function              |  |  |

| 32    | GNDBB         |         | А              | Output Stage Ground                | GNDBB                 |      |             |                       |  |  |

| gap u | sed for cree  | page di | stance         |                                    |                       |      |             |                       |  |  |

| 33    | GND           |         | Α              | Logic Ground                       | GND                   |      |             |                       |  |  |

| 34    | GND           |         | Α              | Logic Ground                       | GND                   |      |             |                       |  |  |

| 35    | GND           |         | Α              | Logic Ground                       | GND                   |      |             |                       |  |  |

| 36    | SEL           | 1       | PD             | Serial / Parallel Mode<br>Select   | SEL                   |      |             |                       |  |  |

| 37    | VCC           |         | A              | Positive 3.3 V logic supply        | VCC                   |      |             |                       |  |  |

| 38    | CLKADJ        |         | A              | Clock Frequency<br>Adjustment      | CLKADJ                |      |             |                       |  |  |

| 39    | GND           |         | А              | Logic Ground                       | GND                   |      |             |                       |  |  |

| 40    | <u>ODIS</u>   | ı       | PD             | Output Disable                     | <del>ODIS</del>       |      |             |                       |  |  |

| 41    | SYNC          | I       | PU             | Synchronize and Freeze Diagnostics | SYNC                  |      |             |                       |  |  |

| 42    | WR            | ı       | PU             | Data Write Input                   | n.c.                  | high | impedar     | nce "Z"               |  |  |

| 43    | ALE/RST       | I       | PD             | Address Latch Enable /<br>Reset    | RST                   | I    | PD          | Reset                 |  |  |

| 44    | RD            | I       | PU             | Data Read Input                    | MS0                   | I    | PD          | SPI Mode Select bit   |  |  |

| 45    | n.c.          |         |                | not connected                      | MS1                   | I    | PD          | SPI Mode Select bit   |  |  |

| 46    | GND           |         | А              | Logic Ground                       | GND                   |      |             | ,                     |  |  |

| 47    | GND           |         | А              | Logic Ground                       | GND                   |      |             |                       |  |  |

| 48    | <del>CS</del> | ı       | PU             | Chip Select                        | <del>CS</del>         |      |             |                       |  |  |

| 49    | AD0           | 10      | PPZ            | Addr-Data in/output bit0           | SDI                   | ı    | PD          | SPI Data input        |  |  |

| 50    | AD1           | Ю       | PPZ            | Addr-Data in/output bit1           | n.c.                  |      |             | high impedance "Z"    |  |  |

| 51    | AD2           | Ю       | PPZ            | Addr-Data in/output bit2           | n.c.                  |      |             | high impedance "Z"    |  |  |

| 52    | AD3           | Ю       | PPZ            | Addr-Data in/output bit3           | n.c.                  |      |             | high impedance "Z"    |  |  |

| 53    | AD4           | Ю       | PPZ            | Addr-Data in/output bit4           | CRCERR                | OD   | PU          | CRC Error output      |  |  |

| 54    | AD5           | Ю       | PPZ            | Addr-Data in/output bit5           | SCLK                  | I    | PD          | SPI Shift Clock input |  |  |

| 55    | AD6           | Ю       | PPZ            | Addr-Data in/output bit6           | n.c.                  |      | high impeda |                       |  |  |

| 56    | AD7           | 10      | PPZ            | Addr-Data in/output bit7           | SDO                   | 0    | PPZ         | SPI Data Output       |  |  |

| 57    | ERR           | OD      | PU             | Fault indication                   | ERR                   |      |             |                       |  |  |

(table continues...)

#### 1 Pin configuration and functionality

Table 1 (continued) Pin configuration

| Pin   | Parallel Ir    | nterfac | e Mode        |                     | Serial Inte | rface Mo | de      |          |

|-------|----------------|---------|---------------|---------------------|-------------|----------|---------|----------|

|       | Symbol Ctrl Ty |         | Type Function |                     | Symbol      | Ctrl     | Туре    | Function |

| 58    | GND            |         | А             | Logic Ground        | GND         |          |         | 1        |

| 59    | GND            |         | А             | Logic Ground        | GND         |          |         |          |

| 60    | GND            |         | Α             | Logic Ground        | GND         |          |         |          |

| gap ı | ised for cree  | page di | istance       |                     | ·           | ·        |         |          |

| 61    | GNDBB          |         | Α             | Output Stage Ground | GNDBB       |          |         |          |

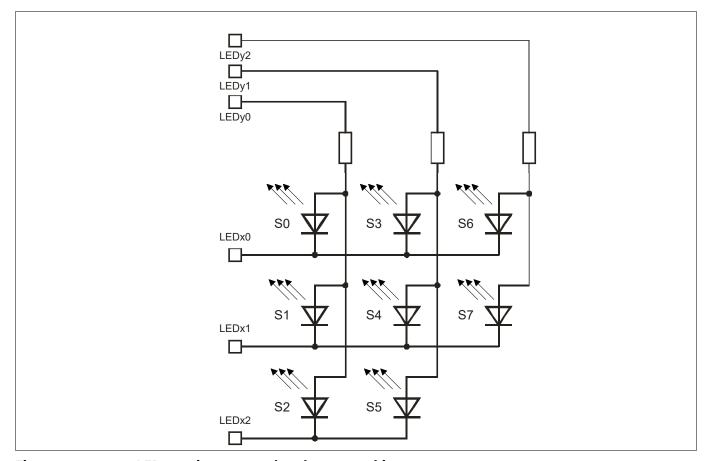

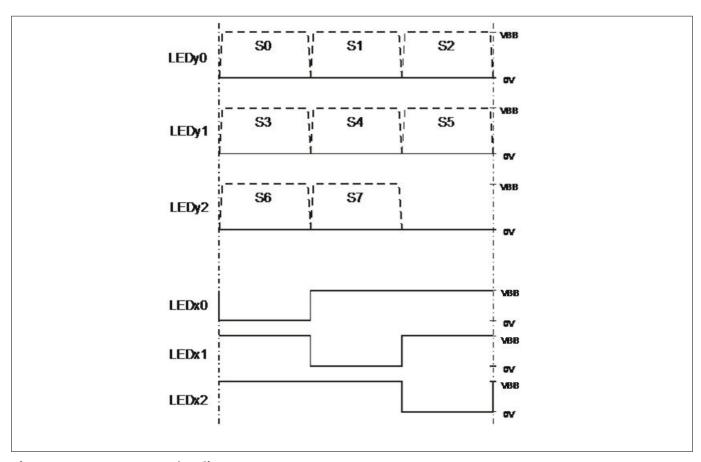

| 62    | LEDX0          |         | Α             | LED Output Row 0    | LEDX0       |          |         |          |

| 63    | LEDX1          |         | А             | LED Output Row 1    | LEDX1       |          |         |          |

| 64    | LEDX2          |         | Α             | LED Output Row 2    | LEDX2       |          |         |          |

| 65    | LEDY0          |         | А             | LED Output Column 0 | LEDY0       |          |         |          |

| 66    | LEDY1          |         | Α             | LED Output Column 1 | LEDY1       |          |         |          |

| 67    | LEDY2          |         | А             | LED Output Column 2 | LEDY2       |          |         |          |

| 68    | OUT7           |         | А             | Switch Output 7     | OUT7        |          |         |          |

| 69    | OUT7           |         | А             | Switch Output 7     | OUT7        |          |         |          |

| 70    | n.c.           | not c   | onnect        | ed                  | n.c.        | not c    | onnecte | d        |

<sup>1)</sup> Direction of the digital pins: I = input, O = output, IO = Input/Output

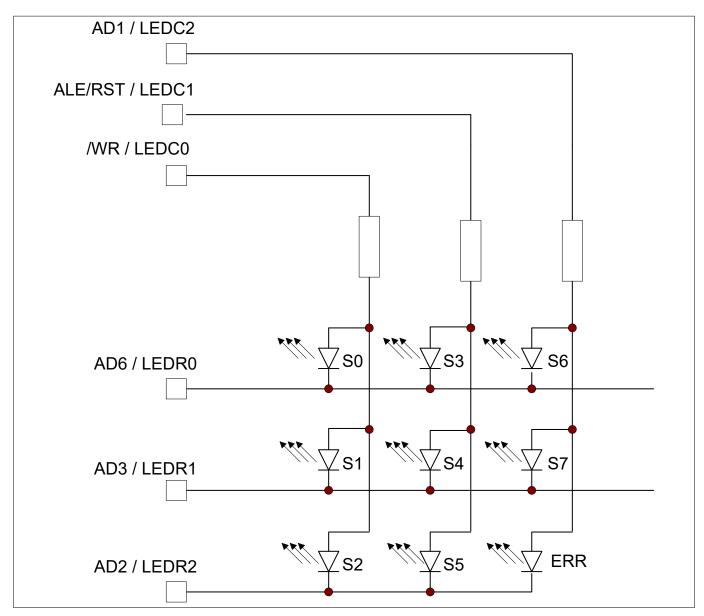

In case of serial mode six pins can be used to drive a LED-matrix on the uC-side (Table 2). For this purpose the bit LEDON in register GLCFG has to be set to "1".

Table 2 Pin Configuration for LED-Application on the uC-Side

| Pin   | Serial Interface Mode |      |      |          |  |  |  |  |  |

|-------|-----------------------|------|------|----------|--|--|--|--|--|

|       | Symbol                | Ctrl | Туре | Function |  |  |  |  |  |

| top s | ide pins              |      |      |          |  |  |  |  |  |

| 55    | AD6                   |      | OD   | LEDR0    |  |  |  |  |  |

| 52    | AD3                   |      | OD   | LEDR1    |  |  |  |  |  |

| 51    | AD2                   |      | OD   | LEDR2    |  |  |  |  |  |

| 42    | WR                    |      | OD   | LEDC0    |  |  |  |  |  |

| 43    | ALE/RST               |      | OD   | LEDC1    |  |  |  |  |  |

| 50    | AD1                   |      | OD   | LEDC2    |  |  |  |  |  |

<sup>2)</sup> Type of the pin: A = analog, OD = Open-Drain, PU = internal Pull-Up resistor, PD = internal Pull-Down resistor, PPZ = Push-Pull pin with High-Impedance functionality

## infineon

#### 1 Pin configuration and functionality

#### 1.1 Pin functionality

This section describes the pins of the  $\mu$ Controller Interface as well as the Process Interface.

#### 1.1.1 Pins of power interface

#### VBB (Positive supply 11-35 V output stage)

$V_{\rm BB}$  supplies the output stage. An external circuitry for reverse polarity protection is required (see Electrical Characteristics).

A ceramic capacitor of minimum 2.2 µF must be connected between VBB and GNDBB.

#### **GNDBB (Ground for VBB domain)**

This pin acts as the ground reference for the output stage that is supplied by  $V_{\rm BB}$ .

#### OUT0... OUT7 (Output channel 0 ... 7)

Due to EMI-requirements (Radio-Frequency-Common-Mode and burst-application) a capacitor of min.10 nF  $(\pm 10\%)$ , recommended value 12 nF  $\pm$  10%) for each output pin has to be connected to GNDBB.

#### LEDx0,1,2 (LED Row output channel 0,1,2)

Low side switches

#### LEDy0,1,2 (LED Column output channel 0,1,2)

High side drivers

#### **IADJ (Current Adjust)**

Reference current input, must be connected to GNDBB through a reference resistor of typ. 6.81 K $\Omega$  (E96 series). The DC-level  $V_{\text{IAD I}}$  is 1.215 V.

#### **OLADJ (Open Load Adjust)**

The current for the Open load detection can be adjusted by connecting a resistor between this pin and GNDBB (from the E96 series :  $25 \text{ k}\Omega$  -  $2.3 \text{ k}\Omega$ ). The DC-level  $V_{\text{OI ADJ}}$  is 1.215 V.

#### **VDDIO (3.3 V Supply Blocking Capacitor)**

A 1 µF ceramic capacitor must be connected between VDDIO and GNDBB.

#### **VCORE (Blocking Capacitor for 1.5 V Digital Core)**

A 470 nF ceramic capacitor must be connected between VCORE and GNDBB.

#### 1.1.2 Pins of serial and parallel logic interface

Some pins are common for both interface types, some others are specific for the parallel or serial access.

#### VCC (Positive 3.3 V logic supply)

$V_{\rm CC}$  supplies the output interface that is electrically isolated from the output power stage. The interface can be supplied with 3.3 V. A ceramic capacitor of minimum 2.2  $\mu$ F must be connected between VCC and GND.

#### ISOFACE<sup>™</sup> ISO2H823V2.5

#### 1 Pin configuration and functionality

#### **GND (Ground for VCC domain)**

This pin acts as the ground reference for the uC-interface that is supplied by  $V_{CC}$ .

#### **CLKADJ (Clock Adjust)**

A high precision resistor of 10 K $\Omega$  has to be connected between CLKADJ and GND. The DC-level  $V_{\text{CLKADJ}}$  is 0.5 V.

#### **ERR** (Fault Indication)

The low active ERR signal contains the OR-wired diagnostic information depending on choosen serial or parallel mode (VBB undervoltage or missing voltage detection, the internal data transmission failure detection unit and the fault(s) of the output switch). The output pin ERR provides an open drain functionality. This pin has an internal Pull-Up resistor. In normal operation the signal ERR is high.

#### **ODIS** (Output Disable)

The low active  $\overline{\text{ODIS}}$  signal immediately switches off the output channels OUT0-OUT7. This pin has an internal Pull-Down resistor. In normal operation the signal  $\overline{\text{ODIS}}$  is high. Setting  $\overline{\text{ODIS}}$  to Low clears the DRIVE register as well. The minimum width of the  $\overline{\text{ODIS}}$  signal is 5 µs.

#### **SEL (Serial or Parallel Mode Select)**

When this pin is in a logic Low state, the IC operates in Parallel Mode. For Serial Mode operation the pin has to be pulled into logic High state. During Start Up the IC is operating in Parallel Mode. This pin has an internal Pull-Down resistor and a 200 ns blanking time<sup>1)</sup>.

#### **SYNC**

In isochronous mode (clock-sync-mode) the transfer of the latched output data register into the output-stages is controlled by the SYNC signal. When the SYNC-signal is in low state, the output-stage won't be updated any longer, the last value is frozen. With the rising edge of SYNC the information of the latched output data registers will be transferred to the output stages. It can be choosen by a configuration bit whether all the channel diagnostic bits will be latched into the DIAG channel register every data cycle or only when the SYNC-signal is in high state. In the last case when the SYNC-signal is in low state, the DIAG channel register wouldn't be updated any longer, the last value would be frozen. SYNC is also used for resynchronization of the data transmission with the target to achieve a low jitter. This pin has an internal Pull-Up resistor and a 20 ns blanking time<sup>1</sup>.

#### **CS** (Chip Select)

When this pin is in a logic Low state, the IC interface is enabled and data can be transferred. This pin has an internal Pull-Up resistor and a 20 ns blanking time<sup>1)</sup>.

When the  $\overline{\text{CS}}$  pin is held Low whereas the ALE pin is High for at least 100 µs, the device is reset.

#### The following pins are provided in the parallel interface mode

#### AD7:AD0 (AddressData input / output bit7 ... bit0)

The pins AD0 .. AD7 are the bidirectional input / outputs for data write and read. Depending on the state of the ALE pin and the AD7 pin, register addresses or data can be transferred between the internal registers and e.g. the micro-controller. By connecting  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  and ALE/RST pins to GND and  $\overline{\text{RD}}$  to VCC, the parallel direct mode is activated.

the signal must be stable for the duration of the blanking time before it is accepted as valid

#### ISOFACE<sup>™</sup> ISO2H823V2.5

#### 1 Pin configuration and functionality

#### WR (Write)

By pulling this pin down, a write transaction is initiated on the AddressData bus and the data has to be valid on the rising edge of  $\overline{WR}$ . The AD7-bit of the register address has to be set to '1'. This pin has an internal Pull-Up resistor and a 20 ns blanking time<sup>1)</sup>.

#### RD (Read)

By pulling this pin down, a read transaction is initiated on the AddressData bus and the data becomes valid on the rising edge of  $\overline{RD}$ . The AD7-bit of the register address has to be set to '0'. This pin has an internal Pull-Up resistor and a 20 ns blanking time<sup>1</sup>).

#### ALE (Address Latch Enable)/RST

The pin ALE is used to select between address (ALE is in a logic High state) or data (ALE is in a logic Low state). Furthermore, a read or write transaction can be selected with the  $\overline{RD}$  and  $\overline{WR}$  pin. When ALE is pulled high, address is transferred and latched over the bit AD0 to AD7. During the time interval where ALE = High  $\overline{RD}$  or  $\overline{WR}$  has to be pulled to High. During the Low State of ALE all transactions hit the same address. This pin has an internal Pull-Down resistor and a 20 ns blanking time  $\overline{CS}$ .

#### The following pins are provided in the serial interface mode

#### MS0, MS1 (Serial Mode Select)

By driving these pins to Logic High or Low the Serial Interface Mode (number of bits - 8, 16, 24 - to be transferred, CRC) can be selected. These pins have both an internal Pull-Down resistor and a 200 ns blanking time<sup>1)</sup>.

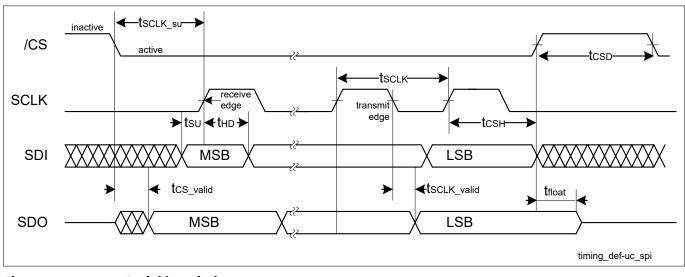

#### **SCLK (Serial Interface Shift Clock)**

Input data are sampled with rising edge and output data are updated with the falling edge of this input clock signal. This pin has an internal Pull-Down resistor and a 20 ns blanking time<sup>1</sup>.

#### **SDI (Serial Interface Input Data)**

SDI is put into a dedicated FIFO (clocked by SCLK) to program the DRIVE register and the internal address and the write data. This pin has an internal Pull-Down resistor and a 20 ns blanking time<sup>1)</sup>.

#### **SDO (Serial Interface Data Output)**

SDO provides the serial output data bits.

#### **CRCERR** (CRC Error Output)

This pin is in a logic Low state when CRC errors or Shift-Clock errors are detected internally. This pin has an open drain functionality and an internal Pull-Up resistor.

the signal must be stable for the duration of the blanking time before it is accepted as valid

#### 2 Block diagram

#### **Block diagram** 2

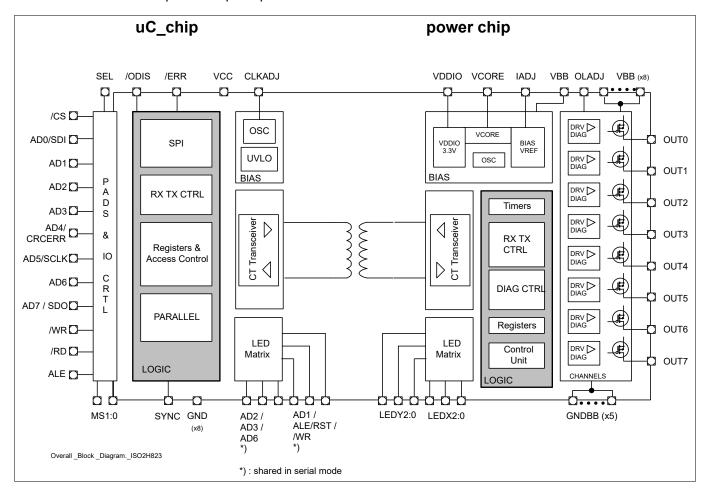

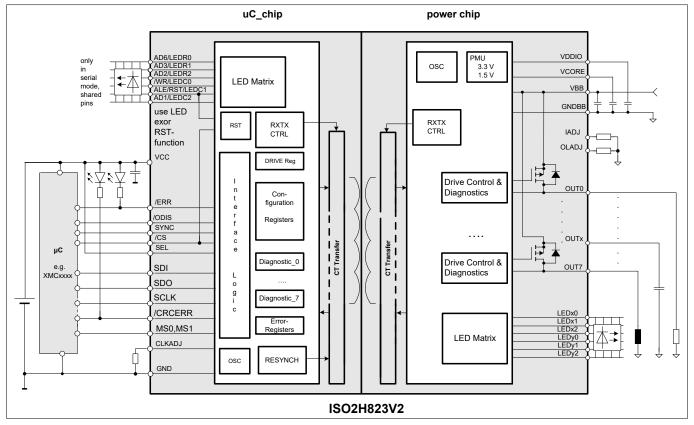

The IC is divided into an uC\_chip and into a power chip due to the galvanical isolation. The uC\_chip contains the uC-interface and the power chip the power switches.

Figure 3 **Block diagram**

#### 2 Block diagram

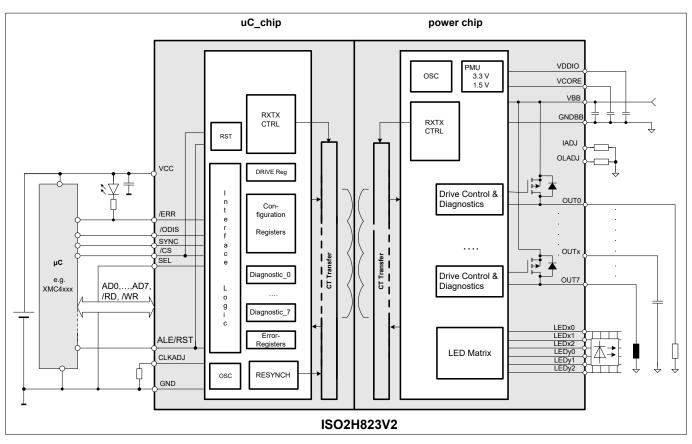

Figure 4 Application with parallel interface

Figure 5 Application with serial interface

## 3 Functional description

#### 3.1 Introduction

The IC contains 2 galvanic isolated voltage domains that are independent from each other. The input interface ( $\mu$ C-chip) is supplied at  $V_{CC}$  and the output stage (power chip) is supplied at  $V_{BB}$ . The different voltage domains can be switched on at different times. The output stage is only enabled once the input stage enters a stable state. The power chip generates out of  $V_{BB}$  two internal voltages  $V_{DDIO}$  = 3.3 V (±10%) and  $V_{CORE}$  = 1.5 V (±10%) which have to be buffered externally.

The ISOFACE™ ISO2H823V2.5 includes 8 high-side power switches that are controlled by means of the integrated parallel/serial interface. The interface is 8-bit µController compatible. Furthermore a direct control mode can be selected that allows the direct control of the outputs OUT0 ... OUT7 (power chip) by means of the inputs AD0 ... AD7 (µC-chip) without any additional logic signal. The IC can replace 8 optocouplers and the 8 high-side switches in conventional I/O-Applications as a galvanic isolation is implemented by means of the integrated coreless transformer technology. The µController compatible interface allows a direct connection to the ports of a microcontroller without the need for other components. Each of the 8 high-side power switches is protected against overload, overtemperature and against overvoltage by an active zener clamp.

#### 3.2 Microcontroller interface

The microcontroller interface can be configured as a parallel or serial interface via the SEL pin.

#### 3.2.1 Parallel interface mode

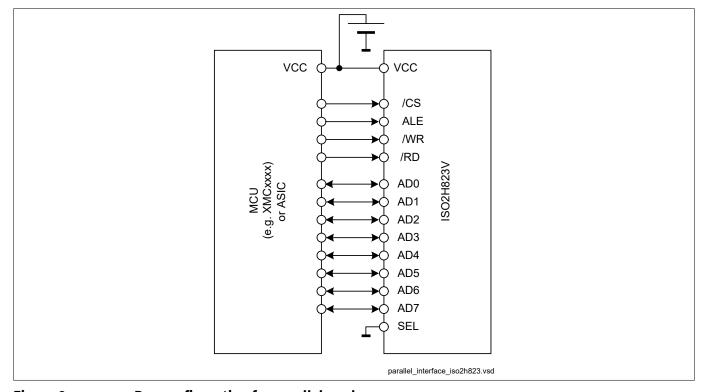

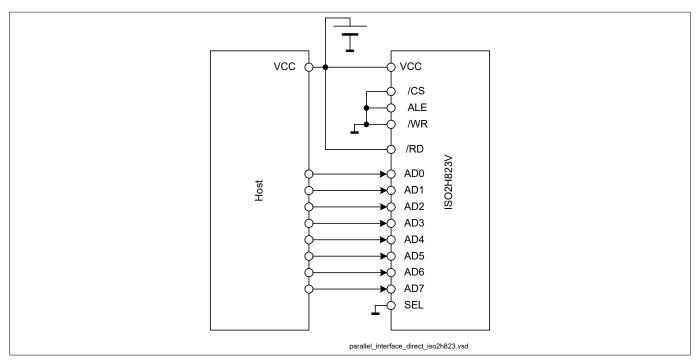

The ISO2H823V2.5 device contains a parallel interface that can be selected by pulling the SEL Pin to logic Low state. The interface can be directly controlled by the  $\mu$ Controller output ports (see Figure 6). The output pins AD7:AD0 are in state "Z" as long as  $\overline{\text{CS}} = 1$ ,  $\overline{\text{RD}} = 1$  and  $\overline{\text{WR}} = 1$ .

Figure 6 Bus configuration for parallel mode

# infineon

#### 3 Functional description

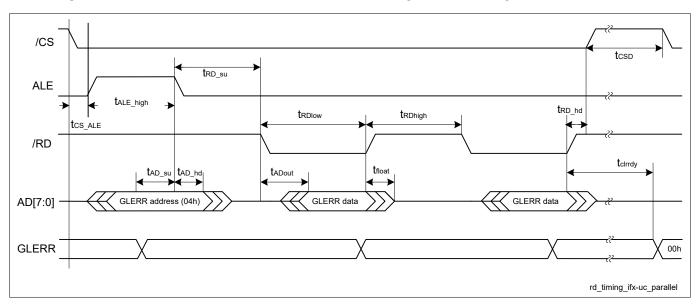

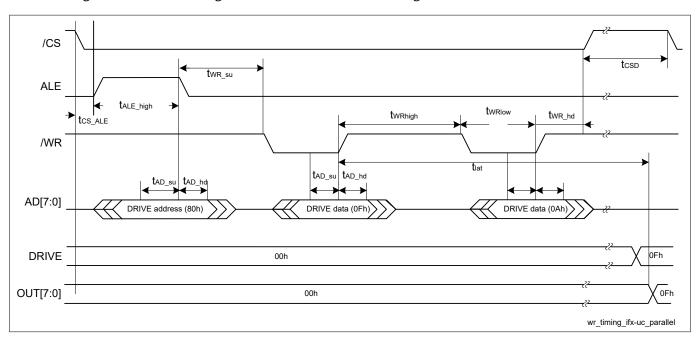

The timing requirements for the parallel interface are shown in Figure 7 (Read), Figure 8 (Write) and Table 23.

Figure 7 Timing by parallel read access (e.g. GLERR register)

For a reading access to internal registers the MSB of the address register has to be set to "0".

Figure 8 Timing by parallel write access (e.g. DRIVE register)

For a writing access to internal registers the MSB of the address register has to be set to "1".

#### 3.2.1.1 Parallel direct mode

The parallel interface can be also used in a direct mode that allows direct changes of the output OUT0...OUT7 by means of the corresponding inputs D0-D7 without additional logic signals. To activate the parallel direct mode  $\overline{CS}$ ,  $\overline{WR}$  and ALE pins have to be wired to ground and  $\overline{RD}$  has to be wired to VCC as shown in the Figure 9. Although the diagnostics cannot be read in this operation mode, the faults as specified in Table 3 are still reported at the  $\overline{ERR}$  pin (volatile).

Figure 9 Parallel direct mode

The direct mode is intended to be an additional parallel mode which is invoked directly after reset. In this case internal settings have already been realized (e.g. MSB of the address register is set to "1").

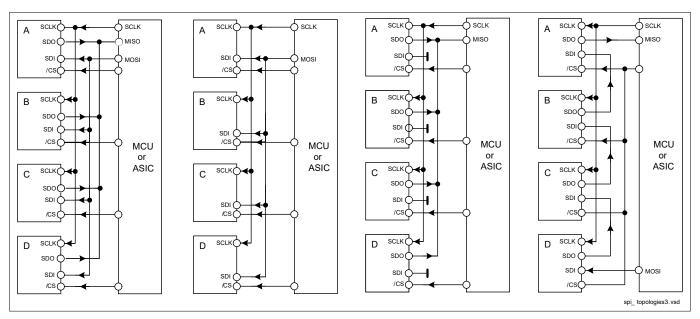

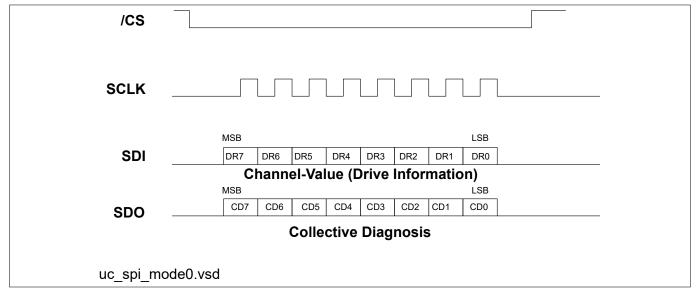

#### 3.2.2 Serial interface mode

The ISO2H823V2.5 device contains a serial interface that can be activated by pulling the SEL pin to logic High state. The interface can be directly controlled by the  $\mu$ Controller output ports. The output pin SDO is in state "Z" as long as  $\overline{\text{CS}}$  = 1. Otherwise, the bits at the SDI input are sampled with the rising edge of SCLK and registered into the input FIFO buffer of length dependent on the selected SPI-mode (8, 16, 24 bits, Figure 12, Figure 13, Figure 14, Figure 15). With every falling edge of SCLK the bits to be read are provided serially to the pin SDO.

The timing requirements for the serial interface are shown in Figure 10 and in Table 24.

Figure 10 Serial bus timing

Several SPI topologies are supported: pure bus topology, daisy chain and combinations (Figure 11). Of course independent individual control with a dedicated SPI controller interface for each slave IC is possible as well.

Figure 11 Example SPI topologies

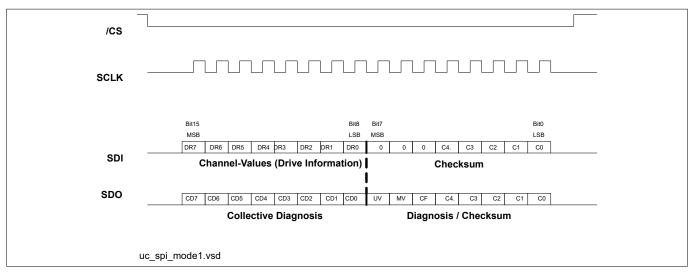

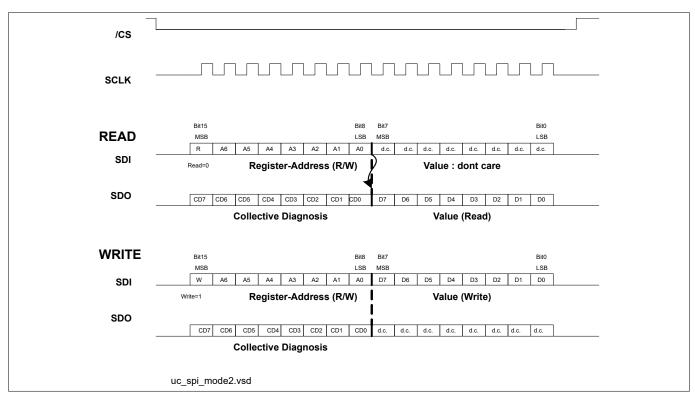

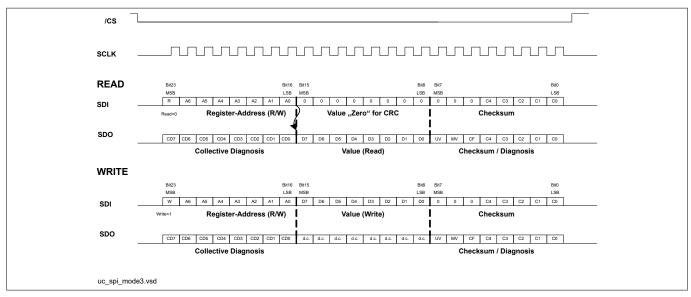

#### **3.2.2.1** SPI modes

Four different SPI-modes can be selected by means of MS0 and MS1 (Figure 12 - Figure 15).

Figure 12 SPI mode 0, MS0 = 0, MS1 = 0, daisy chain supported

Figure 13 SPI mode 1, MS0 = 1, MS1 = 0, daisy chain supported

Figure 14 **SPI Mode 2, MS0 = 0, MS1 = 1**

Figure 15 SPI mode 3, MS0 = 1, MS1 = 1

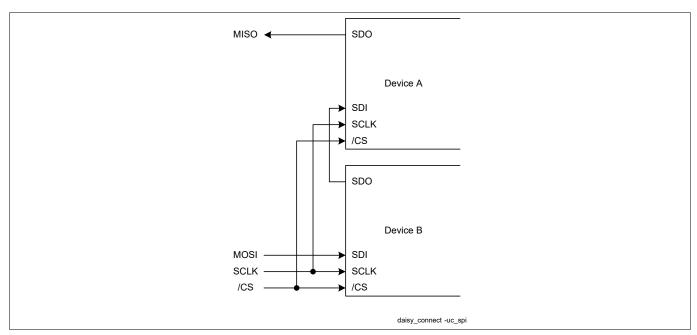

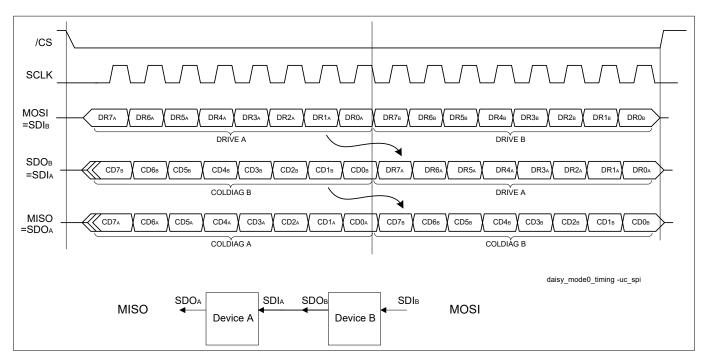

#### 3.2.2.2 Daisy chain mode

Up to 4 devices can be connected together as shown in the Figure 16 to operate in the daisy chain mode. Serial modes 0 and 1 can be operated in daisy chain mode. In this case, the SDO output of one device is directly connected to the SDI input of the next device. The SPI chain has to be connected to the  $\mu$ C or Bus ASIC (MOSI, MISO and common SCLK and  $\overline{\text{CS}}$  signals). If the received SCLK pulses are not fulfilling the modulo(8)-condition the  $\overline{\text{CRCERR}}$  pin will be activated.

In serial mode 1 the CRC-generation has to be reset after 16 SCLK-cycles. At the rising edge of  $\overline{\text{CS}}$  each connected daisy-chain-device checks its related 16 bit-stream concerning CRC-consistency.

Figure 16 Connecting two devices for daisy chain mode

The data shifted in the first device SDI input is shifted out at the SDO output after the first byte for the serial mode 0 (after the second byte for the mode 1) while  $\overline{\text{CS}}$  remains Low as shown in the Figure 17.

Figure 17 Typical timing diagram of daisy chain operation (Serial mode 0)

#### 3.2.2.3 Cyclic Redundancy Check CRC

To detect errors inside SPI data transmission two SPI-Modes are provided with integrated Cyclic Redundancy Check.

The 5-Bit-CRC checksum will be calculated with the polynom  $X^5 + X^4 + X^2 + 1$ . The bit length used for the calculation is 11 bits for SPI-mode 1 and 19 bits for SPI-mode 3. The internal CRC-working register is loaded with "11111" before start of the CRC-calculation.

The SPI-mode 1 supports only the write procedure for the DRIVE register (SPI-mode 1, MS1, MS0 = 01). Eight bits of drive-information plus 3 dummy bits and the related CRC-information (5 bits based on the fed-in 11 bits) are delivered to the CRC-engine. At the same time the COLDIAG-information in combination with the UV, MV, CF-bits and the related CRC-information (based on these 11bits: COLDIAG, UV, MV, CF) are fed out of SDO. The bit stream format is shown in Figure 13.

SPI-mode 3 provides register based access to the ISO2H823V2.5 with implemented CRC. The bit stream for a write access to a register consists of the register address (8 bits), register data (8 bits), 3 dummy bits and the CRC signature (5 bits) as shown in Figure 15. The total bitstream is fed into the CRC-input engines and processed according to the underlying CRC-algorithm serially. At the same time the COLDIAG-information in combination with the UV, MV, CF-bits and the related CRC-information (based on these 19 bits: COLDIAG, 8 dummy bits, UV, MV, CF) are fed out of SDO.

The bit stream for a read access to a register consists of the register address (8 bits), 11 dummy bits and the CRC signature (5 bits) as shown in Figure 15. The total bitstream is fed into the CRC-input engines and processed according to the underlying CRC-algorithm serially. At the same time the COLDIAG-information, register data in combination with the UV, MV, CF-bits and the related CRC-information (based on these 19 bits: COLDIAG,8 bits register data, UV, MV, CF) are fed out of SDO.

After processing the 24 in-bits (including the CRC-signature) the result of the CRC-algorithm processing has to be zero. In the case of another result different from zero the delivered signature is not consistent with the delivered bit stream. This will be indicated by driving the CRCERR Pin to Low.

In both cases (SPI-mode 1 and SPI-mode 3) the status of the CRCERR pin is evaluated not at the end of the bit sequence but with rising edge of  $\overline{\text{CS}}$ . The procedure is consistent with the daisy-chain application where each

#### 3 Functional description

partner of the daisy chain checks its own contribution with the rising edge of  $\overline{\text{CS}}$  when it is confirmed that the chain is completely filled.

$\overline{\text{CRCERR}}$  reflects both the fulfillment of the modulo-8-condition for the number of SCLK-signals and the correctness of the CRC-signature. Both kinds of information are evaluated only during  $\overline{\text{CS}}$  is Low and reported with the rising edge of  $\overline{\text{CS}}$ . Therefore it is assured that non-active ICs ( $\overline{\text{CS}}$  = High) does not report a  $\overline{\text{CRCERR}}$  = Low signal in case SCLK is toggling.

The signal  $\overline{\text{CRCERR}}$  has an internal pull-up-resistor of 50 k $\Omega$ . When releasing  $\overline{\text{CRCERR}}$  the internal pull-up resistor determines the rise time, which is about 3  $\mu$ s. It is possible to reduce the rise time to around 1  $\mu$ s by adding an external pull-up resistor of  $10\text{k}\Omega$  at the  $\overline{\text{CRCERR}}$  pin.

#### 3.2.3 Common error indication output

The dedicated ERR pin signalizes a common fault. This low-active pin has an open drain functionality with a pull-up resistor.

Depending on the  $\mu$ Controller-interface mode in use, several internal status signals are OR-wired to drive the ERR pin:

- In direct mode, the OTC flag (LEDGx-bit-field of CT-transmission, OR-wired, volatile) and the volatile W4P-information are routed to the ERR pin

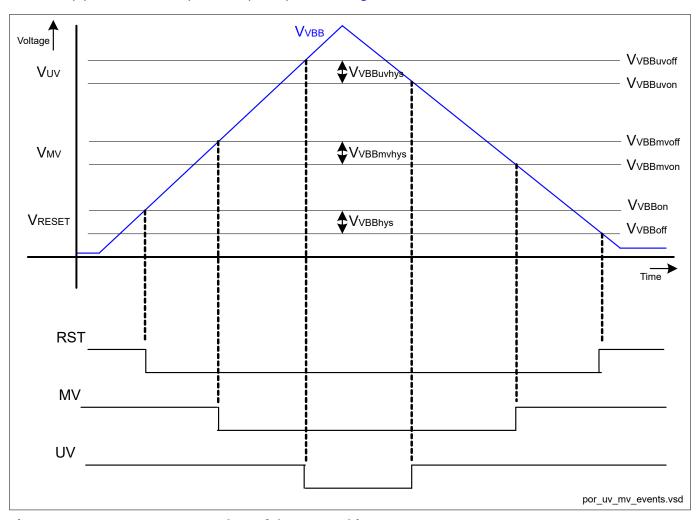

- The output stage undervoltage (UV) and missing voltage (MV) of the power-chip which are transmitted via the integrated coreless transformer are provided at the ERR pin

- The internal data transmission error (TE) over the galvanic isolation is available as well at the ERR pin

- The signal Wait-for-Power chip (W4P) is also provided. It detects that a continuous transmission error over a longer time has occurred e.g. when the process side is not supplied properly and that no diagnostic data are received on the µController-interface side

- The common fault error signal (CF) is routed out to the ERR pin in parallel mode. This signal is the OR-combination of the COLDIAG register bits (sticky)

- CF is not routed out to the ERR pin in any serial mode. In serial modes 1 and 3 the CF-bit is contained in the serial telegram

Table 3 provides the overview of the signals provided at the  $\overline{\text{ERR}}$  pin and the behaviour of the bits used. The prefix "S" specifies the bits as sticky.

During UVLO, all status signals and register bits are reset. The flags UV, MV, TE and W4P have a reset value of 1, so that by default these errors are active. As a consequence after power-up the  $\overline{ERR}$  pin is by default driven Low. The  $\overline{ERR}$  pin returns to High logic level once all the signals OR-wired at this pin are Low i.e. once all the fault conditions are not detected anymore and the bits have been cleared. This behaviour requires the external controller to read the GLERR and INTERR to "clear" the  $\overline{ERR}$  pin (except in parallel direct mode where the error bit is simply OTC of type: volatile bit generated by oring the volatile gated-LEDGx-information of each channel and W4P). In some operation modes the update and the clearing of the status bits are done automatically after every access (serial mode 0 and 1). For the other operation modes, the error bits need to be read with direct addressing to be updated and cleared (parallel mode and serial modes 2,3).

The ERR signal differs between serial modes and parallel modes since in serial modes 1 and 3 the CF bit is already shifted out when CRC is used. The serial or parallel mode is selected with the SEL signal whereas the serial submodes are controlled with the SPI MODE 2-bit signal.

Table 3 Bits composing the ERR signal

| Status bits | Serial com | munication |        |        | Parallel co   | Parallel communication |                 |  |  |  |  |

|-------------|------------|------------|--------|--------|---------------|------------------------|-----------------|--|--|--|--|

|             | Mode-0     | Mode-1     | Mode-2 | Mode-3 | Single access | Repeated read          | Direct<br>mode  |  |  |  |  |

| SUV         | Х          | Х          | Х      | Х      | Х             | Х                      |                 |  |  |  |  |

| SMV         | Х          | Х          | Х      | Х      | Х             | Х                      |                 |  |  |  |  |

| CF          |            |            |        |        | Х             | Х                      |                 |  |  |  |  |

| STE         | Х          | Х          | Х      | Х      | Х             | Х                      |                 |  |  |  |  |

| SW4P        | Х          | Х          | Х      | Х      | Х             | Х                      | X <sup>1)</sup> |  |  |  |  |

| ОТС         |            |            |        |        |               |                        | Х               |  |  |  |  |

<sup>1)</sup> Bit is volatile in direct mode

Upon reset most of the bits used in the  $\overline{ERR}$  generation are reset to High, the  $\overline{ERR}$  pin is pulled down on startup and will remain Low as long as the external controller does not clear the corresponding bits (and as long as the fault exists).

#### 3.2.4 Update of the diagnostic registers

The following list describes the handling of appearing and disappearing failures and therefore the diagnostics.

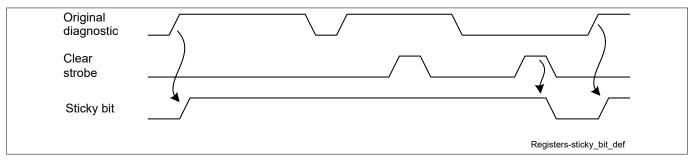

- Appearing diagnostic/failure: appearing diagnostics are stored internally within sticky registers and are

OR-ed into the register COLDIAG (except LEDGx). Therefore the appearing diagnostic/failure bit can be seen

immediately. After reading COLDIAG the diagnostic bits are transferred from the internal sticky registers to

DIAGO,..., DIAG7 from which these can be read now in detail

- Disappearing diagnostic/failure: the diagnostic bits are stored internally as sticky bits and therefore also

or-ed in COLDIAG. In the case the source for the diagnostic bits has disappeared the diagnostic bits are

still available internally and in COLDIAG until the user has read COLDIAG. Therefore the diagnostic bits

never disappear with vanishing of the source for setting the bits alone. Both conditions have to be fulfilled:

vanishing of the source of the occurrence and reading of COLDIAG

- In the case the isochronous mode for the channel diagnostic values is activated with the bit FRZSC in register GLCFG (see Chapter 3.2.5.2) the diagnostic bits are transferred from the internal sticky registers to DIAGO,..., DIAG7 with each edge of the SYNC-signal

#### 3.2.5 SYNC operation

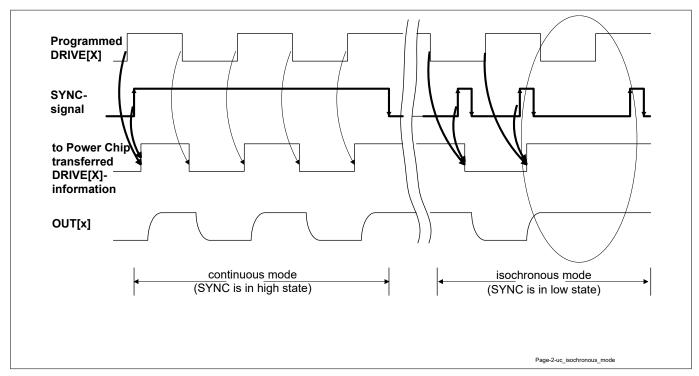

The Isochronous Mode enables the synchronization of several devices (e.g. to provide 32 channels when 4 devices are grouped in parallel). In this way the update of all the output channels as well as their diagnostics can be synchronized and held such that the Bus ASIC or microcontroller can program a new control word of the output channels and read the diagnostic status. In continuous mode, each device with its own built-in oscillator is updated independently.

The Isochronous Mode is controlled by the SYNC pin and independent of the selected serial or parallel interface (with the SEL pin). It concerns only the update of user registers in the system.

### 3.2.5.1 SYNC-signal for drive-signals

Figure 18 explains in detail the mechanism for SYNC = High, SYNC = Low and the rising and falling edges of SYNC for transferring the drive-information from the uC-Chip to the Power Chip.

Figure 18 **SYNC operation timing**

#### **SYNC = High, normal mode:**

The DRIVE-register can be written with new data and the contents of it is also transferred to the power chip.

#### **SYNC = Low, isochronous-mode:**

In isochronous mode the user can write the DRIVE-register but this value will not be transferred to the Power Chip. Therefore the driver configuration (activation of drivers in the Power Chip) is frozen. In Figure 18 it can be clearly seen that the toggling of the DRIVE[x]-information (SPI-data-cycle) at the right side had not been transferred to the process side (see oval area in Figure 18).

#### 3.2.5.2 **SYNC-signal for diagnostics**

Independent from the level of the SYNC-signal always the same reading-sequence of the diagnostics shall be obeyed: read COLDIAG register first and identify which channel x shows the setting of the diagnostic bit an then read the corresponding registers DIAGO,..., DIAG7 for which the diagnostic has been reported (in Table 4 and Table 5 this is illustrated exemplary for channel 0). Reading COLDIAG first assures that the DIAG0,..., DIAG7registers are loaded from the internal sticky registers.

#### **SYNC = High, continuous mode:**

When the signal SYNC is High (default), the continuous mode is selected and the diagnostic registers DIAGO,..., DIAG7 are always updated after read access to COLDIAG.

Table 4 shows the typical scenario where an external disturbance (open load or short-circuit-to VBB) causes the setting of the diagnostic registers DIAG0,..., DIAG7 (here exemplary DIAG0) and the collective diagnostic register COLDIAG. After vanishing of the disturbance and reading of COLDIAG the internal diagnostic registers are reset. The SYNC-waveform is sketched in the 1<sup>st</sup> row of Table 4 (please note that in case of continuous mode any waveform of SYNC is allowed).

#### Table 4 Continuous Mode (GLCFG: FRZSC = 0), Disturbance (to Channel 0) Scenario

| Waveform<br>of SYNC<br>(permanently high) | SYNC        | sync high  (or any waveform of SYNC is allowed when GLCGG:FRZSC = 0) |  |          |  |          |  |  |

|-------------------------------------------|-------------|----------------------------------------------------------------------|--|----------|--|----------|--|--|

| Scenario #                                |             |                                                                      |  |          |  |          |  |  |

| #1                                        | disturbance |                                                                      |  |          |  |          |  |  |

| Read results #1                           |             | READ=yes                                                             |  | READ=yes |  |          |  |  |

| COLDIAG                                   |             | 0x01                                                                 |  | 0x00     |  |          |  |  |

| DIAG0                                     |             | 0xvalue                                                              |  | 0x00     |  |          |  |  |

| #2                                        | dist        | urbance                                                              |  |          |  |          |  |  |

| Read results #2                           |             | READ=yes                                                             |  | READ=yes |  | READ=yes |  |  |

| COLDIAG                                   | :           | 0x01                                                                 |  | 0x01     |  | 0x00     |  |  |

| DIAG0                                     |             | 0xvalue                                                              |  | 0xvalue  |  | 0x00     |  |  |

#### **SYNC = Low, isochronous-mode:**

The isochronous mode for the channel diagnostic values is activated with the bit FRZSC in register GLCFG. If FRZSC = 1 (RESYN = 0) the isochronous mode for diagnostics is enabled.

When SYNC is Low, the DIAGO-7 and COLDIAG (including CF) are not updated anymore (frozen). At the falling edge of SYNC the information of the internal sticky registers is transferred to DIAGO,..., DIAG7. During SYNC = High the information of the internal sticky registers has been mirrored and OR-ed to COLDIAG. When isochronous mode is activated the DIAGO,..., DIAG7-registers and COLDIAG freeze the diagnostic data. But the internal sticky registers collect the diagnostic information independently from SYNC. With rising edge of SYNC the DIAG0,..., DIAG7 registers and COLDIAG are updated on base of the contents of the internal sticky registers.

Table 5 shows some scenarios where an external disturbance (open load or short-circuit-to VBB) cause the setting of the diagnostic registers DIAG0,..., DIAG7 (here DIAG0) and the collective diagnostic register COLDIAG. In all scenarios the same procedure is sketched where a disturbance occurs and the diagnostic registers are read in the following. The SYNC-waveform is sketched in the 1<sup>st</sup> row of Table 5 for isochronous mode with low and high periods), the disturbance is drawn in light shaded grey (please note that the disturbances in this examples are strictly time-limited with respect to the corresponding read-accesses at different time stamps. Examples of possible read-access events and the related read results are visualized as blocks in the corresponding rows of Table 5. The occurrence of the disturbances in relation to the edges of the SYNC-signal is altered for some of the displayed examples. The Read procedures may take place during the phase where SYNC is Low (=0) or High (=1). Depending on the occurrence of the disturbance in relation to the SYNC-edges and the read-process the diagnostic values have been already set in COLDIAG and DIAGO,.... DIAG7 or the old (i.e. previous) values have been frozen. In the second case the new values will be updated in COLDIAG and DIAGO,..., DIAG7 with the next rising edge of SYNC and can be read with the next read-cycle. Due to the sticky registers no diagnostic value is lost. After vanishing of the disturbance and reading the diagnostic values are reset.

Entries in COLDIAG can be reset during SYNC = Low after a reading procedure when the disturbance had been registered before the falling edge of SYNC and is therefore securely delivered. But DIAG0,..., DIAG7 remains unaffected from this reading procedure.

## **(infineon**

#### 3 Functional description

Table 5 Isochronous Mode (GLCFG: FRZSC = 1 (RESYN = 0)), Channel 0 Disturbed, Scenarios

| Waveform of SYNC (alternating high/low) | SYNC        | low                         |                       | hi                      | igh |                          | <u>_</u> | low                              | <u></u> |                                        |

|-----------------------------------------|-------------|-----------------------------|-----------------------|-------------------------|-----|--------------------------|----------|----------------------------------|---------|----------------------------------------|

| Scenario #                              |             |                             |                       |                         |     |                          |          |                                  |         |                                        |

| #1                                      | disturbance | Ì                           |                       | :                       |     |                          | İ        |                                  | Ť       |                                        |

| Read results #1 COLDIAG DIAG0           |             | READ=yes<br>0x01<br>0xvalue |                       | READ=<br>0x00<br>0x00   | yes |                          | -        |                                  |         |                                        |

| #2                                      | disturbance |                             |                       |                         |     |                          |          | i                                | i       |                                        |

| Read results #2 COLDIAG DIAG0           |             | READ=yes 0x01 0xvalue       | =yes<br>0x00<br>0xval | READ=<br>0x00<br>0x00   | yes |                          |          |                                  |         |                                        |

| #3                                      |             | disturbance                 |                       |                         |     |                          |          | i                                | İ       |                                        |

| Read results #3 COLDIAG DIAG0           |             | READ=yes<br>0x00<br>0x00    |                       | READ= 0x01 0xvalu       |     | READ=yes<br>0x00<br>0x00 |          |                                  |         |                                        |

| #4                                      |             | dist                        | urbance               |                         |     |                          |          |                                  | -       |                                        |

| Read results #4 COLDIAG DIAG0           |             | READ=y<br>0x00<br>0x00      | res                   | READ=<br>0x01<br>0xvalu |     | READ=yes<br>0x00<br>0x00 |          |                                  |         |                                        |

| #5                                      | disturbance |                             | : []                  |                         |     |                          |          | i                                | 1       |                                        |

| Read results #5 COLDIAG DIAG0           |             | READ=yes 0x01 0xvalue       |                       |                         |     |                          | 0:       | EAD=yes<br>x00<br>x00            |         |                                        |

| #6                                      |             | disturbance                 |                       |                         |     |                          |          |                                  |         |                                        |

| Read results #6 COLDIAG DIAG0           |             | READ=yes<br>0x00<br>0x00    |                       |                         |     |                          | 0:       | EAD=yes<br>x <b>01</b><br>xvalue | (       | READ=yes<br><b>0x00</b><br><b>0x00</b> |

| #7                                      |             | dist                        | urbance               |                         |     |                          |          | 1                                | -       |                                        |

| Read results #7 COLDIAG DIAG0           |             | READ=yes<br>0x00<br>0x00    |                       |                         |     |                          | 0        | EAD=yes<br>x <b>01</b><br>xvalue | 0       | READ=yes<br>0x00<br>0x00               |

#### 3.2.6 ODIS output disable

The low active  $\overline{\text{ODIS}}$  signal immediately switches off the output channels OUT0-OUT7. This pin has an internal Pull-Down resistor. In normal operation the signal  $\overline{\text{ODIS}}$  is High. Setting  $\overline{\text{ODIS}}$  to Low clears the registers as well. The minimum width of the  $\overline{\text{ODIS}}$  signal is 5  $\mu$ s.

#### 3.2.7 LEDGOFF

The gated-LED-signal LEDGx, x = 0,...,7 is per default reported in the diagnostic registers DIAG0,..., DIAG7 (not ored in the COLDIAG-register). LEDGx is updated with a long time constant every 100 ms. Therefore the bit LEDGOFF in GLCFG offers the possibility to suppress the reporting in the diagnostic registers DIAG0,..., DIAG7.

#### 3 Functional description

#### 3.2.8 **OLOFF**

The bit OLOFF in GLCFG offers the possibility to suppress the reporting of OLIX, OLAX in the diagnostic registers DIAGO,..., DIAG7.

#### 3.2.9 **RESET (Hard and Soft)**

#### 3.2.9.1 **Hardware reset**

The external hardware reset command (triggered via pins CS and ALE) can be enabled or disabled by the bit RSTOFF in the register GLCFG, by default the external hardware reset function is enabled. The external hardware reset forces the logic asynchronous reset for the uC\_chip (acts like a power-on-reset), all registers are loaded with the default values. It is triggered when the signal ALE is set High whereas the  $\overline{CS}$  signal is set Low for at least 100 us. Once an internal timer reaches the end value of 100 us then the hardware reset condition is fulfilled and "latched". At the point where one of the signals ALE and  $\overline{CS}$  returns to its default value, the reset is processed. With resetting the DRIVE-register and restarting the CT-transmission the output switches are turned off.

#### 3.2.9.2 **Soft reset**

The soft reset for the uC chip is triggered by the bit SWRST (self clearing after performing the soft reset) in the register GLCFG. If the soft reset is triggered the DRIVE, INTERR, GLERR, DIAGO,..., DIAG7, COLDIAG, DIAGCFG register are set to their reset values synchronously. In addition the internal flags are cleared. The CTtransmission is restarted. The actual transmission cycle is not disturbed. With resetting the DRIVE-register and restarting the CT-transmission the output switches are turned off.

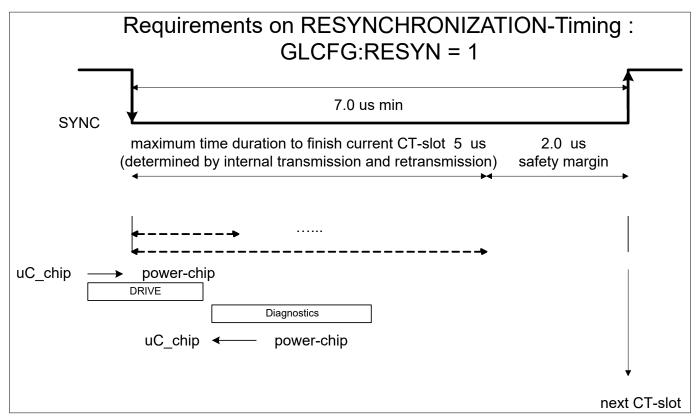

#### 3.2.10 **Resynchronization of CT-Transmission**

During the CT-transmission the drive-information DRIVE for the 8 power switches is sent from the uc-Chip to the Power-Chip. Subsequently one of the diagnostic informations (status-information, OTx, OLIx, OLAx, OCLx, SCVx or LEDGx-information for the 8 power switches) is sent back. The duration of a CT-time slot with transmission of drive - information and back-transmission of one of the diagnostic information lasts about 5 us ± 20 %. (internal operating frequency: 10 MHz, resistor at pin CLKADJ: 10 k $\Omega$ ). When the user programs the drive register a timing uncertainty arises when the specific programmed switch is activated or deactivated in the power chip. The data of the drive register can be transferred to the power chip only in the next free CT-time slot.

The goal of resynchronization is to limit the timing uncertainty due to transmission and retransmission to a value below ± 1.5 us but with a fixed latency of minimum 7.0 us . For triggering the transmission the signal SYNC is used when GLCFG:RESYN = 1. A timing difference between switching on and off of the power transistors exists which is already included in the timing uncertainty value above. Switching off a power transistor is delayed by up of 0.5 us max relative to the SYNC-rising edge compared to switching on a power transistor

Figure 19 Timing of resynchronization

#### **Transmission without resynchronization:**

- GLCFG:RESYN = 0 or 1

- signal SYNC = 1

- write the drive information into DRIVE

- the contents of DRIVE is transferred via the CT to the power-chip

#### Transmission with resynchronization:

- signal SYNC = 1

- GLCFG:RESYN = 1

- write the drive information into DRIVE\_RESYNCH

- signal SYNC = 0

- the duration of the signal SYNC = 0 (minimum 7.0 us) determines the time for resynchronization and the time until the next CT-transfer

- In the meantime the pending transmission and retransmission has been finished and the contents of DRIVE\_RESYNCH has been transferred to DRIVE

- set signal SYNC = 1, the CT-transfer is started from DRIVE with the rising edge of SYNC

Without any negative pulses on SYNC the CT-transfer is operated permanentely from DRIVE; the negative pulses on SYNC are solely used for resynchronization, the isochronous mode for drive-information and for diagnostics is inactive when GLCFG:RESYN is set to "1".

Information for the DRIVE\_RESYNCH-register can be written long before the resynchronzation trigger with falling and rising edge of SYNC.

The user has to obey the timing requirements of the SYNC-signal. For a duration longer than 300 us  $\pm$  20% the watchdog in the power chip disables the output drivers. For a duration of the SYNC-signal shorter than recommended the resynchronization is not guaranteed and the normal transmission fed by the register DRIVE can be performed.

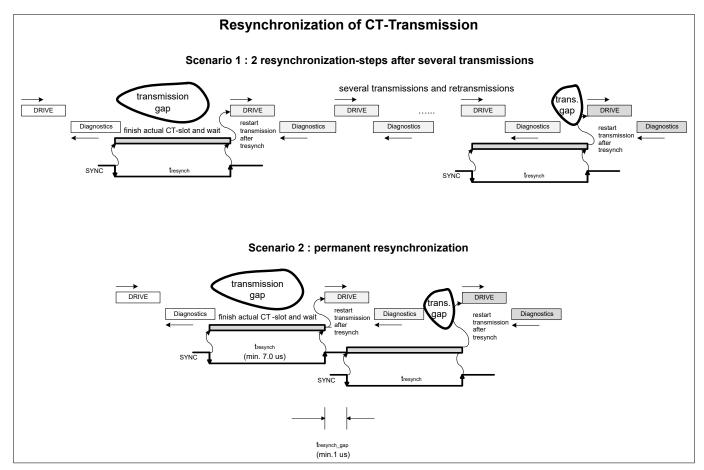

Figure 20 shows 2 different applications of resynchronization. The timing gap between two synchronizations can be as low as 1 us. In this way the customer can decide between single synchronization steps and permanent synchronized transmission with the drawback of reduced CT throughput (waiting time for new transmission).

Figure 20 **Examples of application of resynchronization**

Application hint: It is not possible to select GLCFG:RESYN = 1 and isochronous mode of drive information or/and isochronous mode of diagnostics at the same time. That means resynchronization and isochronous mode of driver information and diagnostics at the same time is not possible. With GLCFG:RESYN = 1 edges on SYNC are used solely for resynchronization.

#### 3.3 **Output stage**

Each channel contains a high-side power FET that is protected by embedded protection functions. The continuous current for each channel is 600 mA nominal, which depends on the cooling conditions and the total power dissipation.

#### **Output stage control** 3.3.1

Each output is independently controlled by an output latch and a common reset line via the pin ODIS that disables all eight outputs and resets the latches.

## infineon

#### 3 Functional description

### 3.3.2 Protection functionality

#### 3.3.2.1 Power transistor overvoltage protection

Each of the eight output stages has it's own zener clamp that limits the voltage over the power stage at the power transistor when solenoid loads are switched off.  $V_{\rm ONCL}$  is then clamped to 52 V (typ.).

#### 3.3.2.2 Power transistor overload protection

The outputs are provided with a linear current limitation, which regulates the output current to the current limit value in case of overload. The electrical operation point does not lead to a shutdown.

The excess power dissipation in the power transistor during current limitation will lead to a rapid increase of the junction temperature. When the junction temperature exceeds 150 °C (typ.) the output will switch off and will switch on again when the junction temperature has cooled down by a temperature hysteresis of 15 K (typ.). Therefore during persisting overload a thermal on-off toggling may occur.

The thermal hysteresis is reset during inactive mode. Therefore when switching to the active mode the power transistor is first switched on if the junction temperature is below 150 °C.

#### 3.3.2.3 Current sense and limitation

To achieve an excellent accuracy for the current limitation and current referred diagnostic (OCLx) an external reference resistor is used. The resistor must be connected between the pins IADJ (as close as possible) and GNDBB. The nominal resistor value is  $6.81~k\Omega$  (E96; current drawn out of IADJ typ. 178  $\mu$ A) , the tolerance should be within 2% to meet an overall current limit tolerance from 0.73 A to 1.3 A.

Operation with other resistor values than 6.8 k $\Omega$  ±5% is not allowed and may lead to insufficient short circuit protection.

To offer open load diagnostics in active mode, a part of the power transistor is driven down when the drain-source-voltage drops below a certain limit (low load condition). The voltage drop across the remaining part is used to evaluate an open load diagnostic.

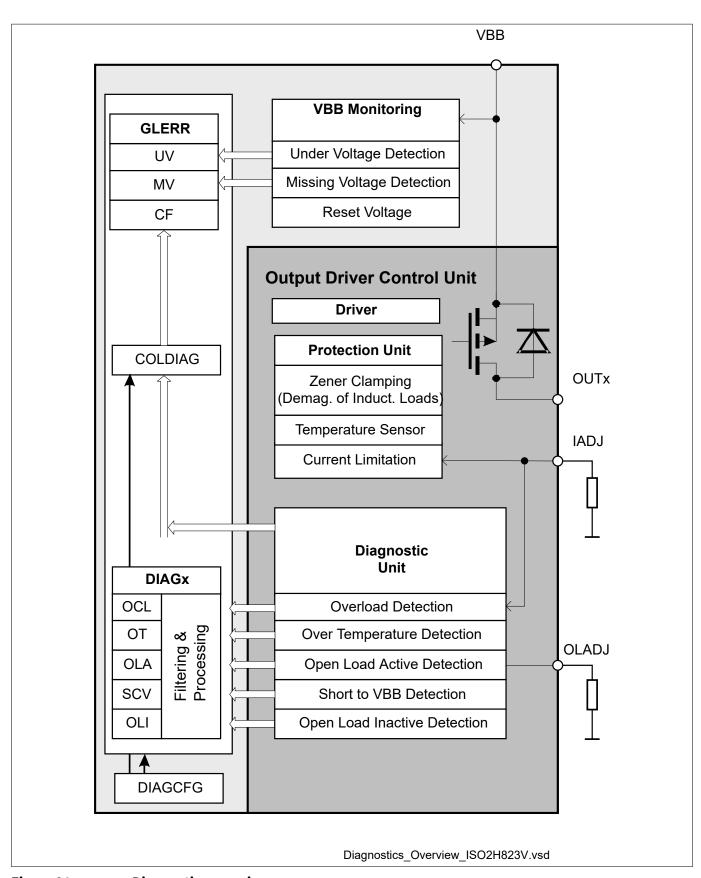

## 3.3.3 Diagnostic functions

For each of the output stages 5 different types of diagnostics are available. Table 6 specifies the diagnostics. Some of the diagnostics are available only in active mode, others only in inactive mode. The diagnostics OLIX, OLAX, SCVx can be prolonged within the complementary mode. Overtemperature in inactive mode is not reported (set to zero).

Table 6 Diagnostic

| Item | Diagnostic type                   | Inactive mode | Active mode                   |

|------|-----------------------------------|---------------|-------------------------------|

| ОТх  | Overtemperature                   | no            | yes (OTx Active)              |

| OLIx | Open Load/Wire Break, "inactive"  | yes           | no                            |

| OLAx | Open Load/Wire Break, "active"    | no            | yes                           |

| OCLx | Current Sense, Overload Detection | no            | yes                           |

| SCVx | Short Circuit to V <sub>BB</sub>  | yes           | not distinguishable from OLAx |

# infineon

#### 3 Functional description

Figure 21 Diagnostics overview

The diagnostics OLIx, SCVx are reported in inactive mode and OLAx is reported in active mode. When the duration of the disturbance was not sufficient to guarantee a 6 ms blanking/filtering time these diagnostics are

## ISOFACE<sup>™</sup> ISO2H823V2.5

#### 3 Functional description

at least reported when switching from one mode into the other mode. The diagnostics OLIx, OLAx and SCVx, OLAx appear in pairs one component for the inactive mode and one component for the active mode with a delay for the filtering. In order not to allow reporting gaps the diagnostics are prolonged until the complementay part is occurring or until a time-out counter has expired (i.e. the diagnostic OLIx (SCVx) is prolonged also during the active time period until the filter delivers a reliable OLAx- (OLAx-) diagnostics and vice versa).

#### 3.3.3.1 Diagnostics in inactive mode

When the output is in inactive mode a diagnostic current is fed to the output. If the load is connected and the load resistance is less than  $12 \text{ k}\Omega$ , the output voltage will be 300 mV or less.

If no load is connected a voltage drop of 7 V is present at the output. A voltage in the range of 5.5 V up to 9.2 V at the output OUTx is detected and reported as open load inactive (OLIx) after filtering.

If the output is shorted to  $V_{BB}$  the output voltage will be close to  $V_{BB}$  level even in inactive mode, this depends upon the type of the short circuit. A voltage level above 9.2 V at the output is detected and reported as short circuit to  $V_{BB}$  (SCVx) after filtering.

The window comparator for OLIx (5.5 V - 9.2 V) is realized with the analog level comparators for 5.5 V and 9.2 V and the digital filters for OLIx and SCVx. After filtering SCVx has the priority against OLIx. By means of the digital filters EMI-contributions shall be filtered before deciding about OLIx or SCVx.

If a capacitive load with a long RC time constant is connected to the ISO2H823V2.5 (like a 12 k $\Omega$  resistor through a long cable with 100 nF capacitance) when switching off, the output voltage sequently passes through the windows of short to VBB detection and broken wire detection. During a blanking time of 6 ms (typ.) the diagnostic signals are ignored to avoid false triggering of diagnostic registers.

If the corresponding channel is switched on again before the end of the blanking time (6 ms), the state of the diagnostic signals present before switching on is transferred to the diagnostic registers, bypassing the blanking window of 6 ms and filtered instead with a filtering time of 100 us, 0.5 ms, 1 ms depending on the switching frequency.

Table 7 Filter time in inactive mode for OLIx and SCVx

| Duration of inactive time $t_{OFF}$ before switching | Filter time              |

|------------------------------------------------------|--------------------------|

| 0 ms < t <sub>OFF</sub> < 1.5 ms                     | 100 us                   |

| 1.5 ms < t <sub>OFF</sub> < 3 ms                     | 0.5 ms                   |

| 3 ms < t <sub>OFF</sub> < 6 ms                       | 1 ms                     |

| t <sub>OFF</sub> > 6 ms                              | 6 ms (OLIx), 2 ms (SCVx) |

For the largest SCVx-filter a filter-length of 2.0 ms is choosen but a setting of SCVx is only possible after the blanking window of 6 ms. No single channel over temperature diagnostics is given during inactive mode to avoid false triggering when switching inductive loads.

### 3.3.3.2 Diagnostics in active mode

During active mode operation the remaining voltage drop of a low load condition is compared to the voltage drop across a reference transistor biased with a reference current. The reference current can be set by the value of a resistor connected between OLADJ and GNDBB defining the threshold for open load diagnostics. The resulting open load threshold is inversely proportional to the connected resistor (25 k $\Omega$  - 2.3 k $\Omega$ , E96 series; current out of the OLADJ-pin 48.6  $\mu$ A - 528  $\mu$ A) and can be set within 0.5 mA to 5 mA.

Like the diagnostics in inactive mode the open load diagnostics in active mode (OLAx) is ignored during a 6 ms blanking window after switching on. If the channel is switched off before the end of the blanking window the current state of the open load diagnostics is transferred to the diagnostic registers, bypassing the blanking

#### 3 Functional description

window of 6 ms and filtered instead with a filtering time of 100  $\mu$ s, 0.5 ms or 1.0 ms (depending on the switching frequency).

The over load diagnostic (OCLx) occurs generally if the output stage limits the load current. Therefore the diagnostic threshold is equal to the current limiting value. An overload may and a short to GNDBB will very likely lead to a thermal shutdown. The shutdown is indicated separately by the diagnostics OTx. The standard filter time for overload (OCLx) and overtemperature (OTx) is 50 us (for a thermal shutdown).

Table 8 Filter time in active mode for OLAX

| Duration of active time $t_{\rm ON}$ before switching | Filter time |

|-------------------------------------------------------|-------------|

| 0 ms < t <sub>ON</sub> < 1.5 ms                       | 100 us      |

| 1.5 ms < t <sub>ON</sub> < 3 ms                       | 0.5 ms      |

| 3 ms < t <sub>ON</sub> < 6 ms                         | 1 ms        |

| t <sub>ON</sub> > 6 ms                                | 6 ms        |

Some loads like incandescent lamps or DC motors show an inrush current, which is normal and should not trigger an overload diagnostic. In some cases even a transient thermal shutdown can not be avoided but an OTx-message is avoided, e.g. for the time duration of lighting up a cold lamp (max. 200 ms). In this case and only for this short time duration the current limiting threshold can be set to 1.5 A and the temperature threshold to 200°C by the internal finite state machine.

The ISO2H823V2.5 adapts filtering of over load and thermal shutdown diagnostics as well as shutdown temperature and current limit level by evaluating the previous turn off time and the load resistance.

### 3.3.3.3 Diagnostic scenarios in dependence of switching frequency

The Table 9 explains the occurence of diagnostics dependent on the switching frequencies for the disturbance "Short-Circuit-to-VBB".

Table 9 Occurence of diagnostics during the disturbance: Short-Circuit-to-VBB

|                                                                     | Reported diagnostic | Unwanted diagnostics at onset of SCV-diagnostics              | Unwanted diagnostics when resolving SCV-diagnostics |

|---------------------------------------------------------------------|---------------------|---------------------------------------------------------------|-----------------------------------------------------|

| Stable switching frequency: f                                       |                     |                                                               |                                                     |

| permanently "low" : f ≤ 62,5 Hz                                     | SCVx, OLAx          |                                                               | OLIx <sup>1)</sup>                                  |