# ILD8150/ILD8150E

## LED driver IC for high power LEDs with hybrid dimming down to 0.5%

## Features

- DC/DC buck with hysteretic current regulation

- Output current up to 1.5 A DC

- Integrated 80 V high-side MOSFET switch with low R<sub>ON</sub>

- Hybrid dimming to 0.5% of the target current

- Wide operating voltage range 8 V to 80 V

- Cycle-by-cycle current limitation

- Under-voltage lockout

- Thermal protection

- Flicker free operation

- Digital soft-start

- Pull-down transistor to avoid LED glowing

## **Potential applications**

• Electronic Control Gear (ECG) for LED luminaries

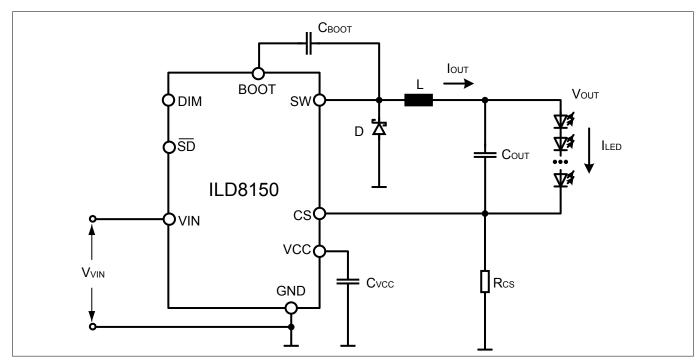

#### Figure 1 DC/DC buck constant current

### **Product validation**

Qualified for industrial applications according to the relevant tests of JEDEC47/20/22.

| Product type | Package                   |

|--------------|---------------------------|

| ILD8150      | PG-DSO-8                  |

| ILD8150E     | PG-DSO-8 with exposed pad |

### Description

## Description

The ILD8150 is a 80 V DC/DC converter IC for LED applications to drive high-power LEDs. For applications operating close to SELV limits it provides a high safety voltage margin. The buck LED driver IC is tailored for LEDs in general lighting applications with average currents up to 1.5 A using a high-side integrated switch. A complete set of features and protections provide a well fit for professional LED lighting solutions.

#### Performance and innovation

The hysteretic current control provides an extremely fast regulation and stable LED current combined with good EMI performance. The efficiency of the LED driver is remarkable high due to the low *R*<sub>ON</sub> of the internal switch.

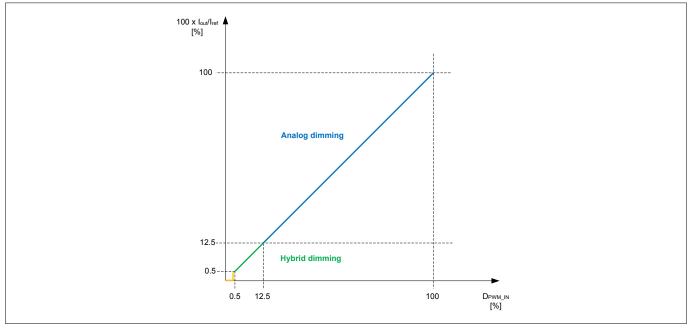

Hybrid dimming is an Infineon unique one-pin dimming method that combines analog dimming and PWM dimming of the LEDs current in one hybrid dimming curve.

A PWM input signal between 250 Hz and 20 kHz controls dimming of the LEDs current in analog mode from 100 percent to 12.5 percent and 12.5 percent to 0.5 percent in hybrid mode with flicker-free modulation frequency of 3.4 kHz. The digital PWM dimming detection with high resolution makes it the perfect match for microcontroller and high quality dimming applications.

The IC supply is directly driven from the primary stage and the low-power shut down contributes to a very high stand-by system efficiency.

High output current accuracy from device to device under all loads and input voltages conditions makes it perfect for tunable white and flat panel designs where current must be identical string to string.

#### Protection

A wide range of operating supply voltage from 8 V to 80 V DC enables a wide use in many applications and provides a good margin when bus voltage exceeds shortly the SELV limits.

The soft-start function protects the primary stage from abrupt current request.

The over temperature protection is triggered when the junction temperature exceeds the temperature threshold turning off the output stage. The output stage turns on again when the junction temperature falls below the temperature threshold.

Under voltage lock-out protects the bootstrap voltage and the hysteretic design ensures cycle-by-cycle current limitation.

### Table of contents

### **Table of contents**

|       | <b>Features</b>                                           |

|-------|-----------------------------------------------------------|

|       | Potential applications 1                                  |

|       | Description                                               |

|       | Table of contents    3                                    |

| 1     | Functional block diagram                                  |

| 2     | Pin configuration                                         |

| 3     | Functional description                                    |

| 3.1   | Buck controller features                                  |

| 3.1.1 | Output current regulation                                 |

| 3.1.2 | Dimming6                                                  |

| 3.1.3 | Digital soft-start                                        |

| 3.1.4 | Low power mode                                            |

| 3.2   | Protection features                                       |

| 3.2.1 | Over-temperature protection 10                            |

| 3.2.2 | Under-voltage protection                                  |

| 4     | Thermal and electrical characteristics $\ldots \ldots 11$ |

| 4.1   | Package characteristics                                   |

| 4.2   | Absolute maximum ratings                                  |

| 4.3   | Operating conditions                                      |

| 4.4   | Electrical characteristics                                |

| 5     | Package dimensions                                        |

|       | Revision history                                          |

|       | <b>Disclaimer</b>                                         |

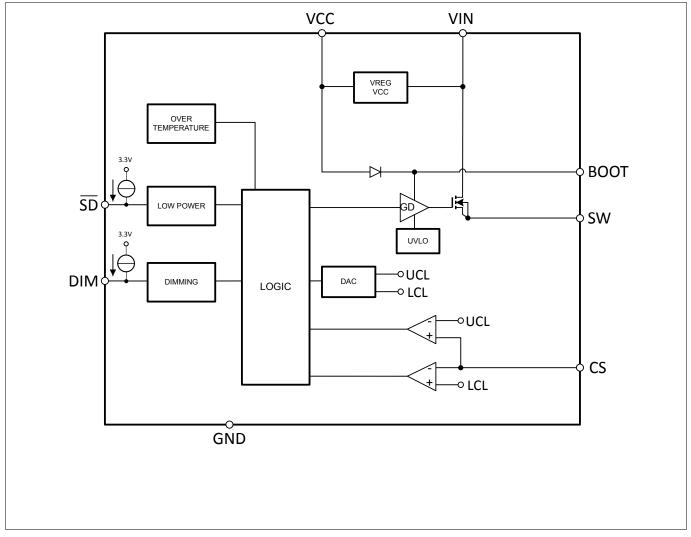

Functional block diagram

1 Functional block diagram

**Block diagram**

Pin configuration

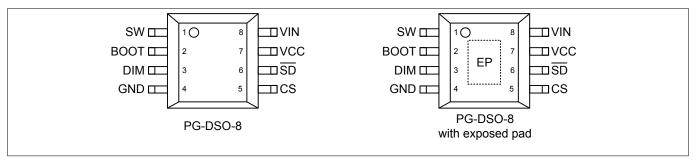

### Figure 3 Pin-out

Both PG-DSO-8 and PG-DSO-8 with exposed pad have the same pin-out. The exposed pad is internally not connected.

| Table 1          | F   | Pin functions                                                     |

|------------------|-----|-------------------------------------------------------------------|

| Name             | No. | Function                                                          |

| SW               | 1   | Internal switch output.                                           |

| BOOT             | 2   | Internal switch driver bootstrap, connect to bootstrap capacitor. |

| DIM              | 3   | Input for PWM dimming (internally pulled-up).                     |

| GND              | 4   | Ground.                                                           |

| CS               | 5   | Current sense feedback.                                           |

| SD (neg.)        | 6   | Shutdown (internally pulled-up). <sup>1)</sup>                    |

| VCC              | 7   | Output of the internal regulator, connect to bypass capacitor.    |

| VIN              | 8   | Input voltage.                                                    |

| EP <sup>2)</sup> | 9   | Exposed pad, connect to GND (internally not connected).           |

<sup>2</sup> PG-DSO-8 with exposed pad only.

<sup>&</sup>lt;sup>1</sup> To use the shutdown functionality 3.3 V must be provided externally at DIM pin.

**Functional description**

## 3 Functional description

This chapter provides a summary of the integrated functions and features, and describes the relationships between them. The parameters and equations are based on typical values at  $T_A = 25$  °C.

### **3.1** Buck controller features

### 3.1.1 Output current regulation

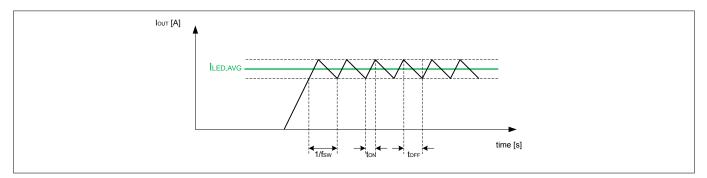

The hysteretic control allows fast and always stable output current and guarantees an intrinsic cycle-by-cycle over-current protection.

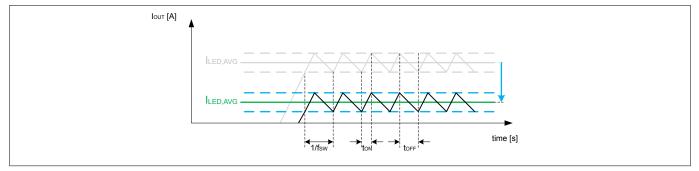

The pin CS feeds back the voltage level on the current sense resistor  $R_{CS}$  to the hysteretic controller. The hysteretic controller implements two voltage thresholds  $V_{CSH}$  and  $V_{CSL}$ . When the CS voltage crosses above the  $V_{CSH}$  threshold the internal switch turns-off. When the CS voltage crosses below the  $V_{CSL}$  the internal switch turns-on. The thresholds  $V_{CSH}$  and  $V_{CSL}$  determine the output current peak-to-peak ripple  $I_{OUT, RIPPLE} = (V_{CSH} - V_{CSL})/R_{CS}$ . The target LEDs current is the undimmed average current determined by the formula  $I_{LED, AVG} = V_{CS, AVG}/R_{CS}$  with  $V_{CS, AVG} = (V_{CSH} + V_{CSL})/2$ . The continuous-conduction-mode (CCM) timings are  $t_{ON} = (I_{OUT, RIPPLE} \bullet L)/(V_{VIN} - V_{OUT})$  and  $t_{OFF} = (I_{OUT, RIPPLE} \bullet L)/V_{OUT}$ .

Figure 4 show the CCM output current waveform.

#### Figure 4 Output current waveform

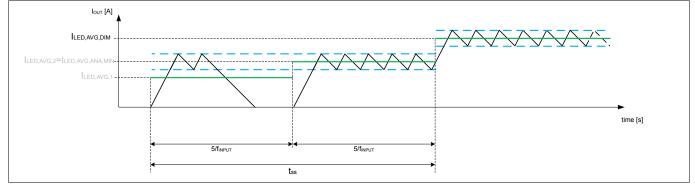

### 3.1.2 Dimming

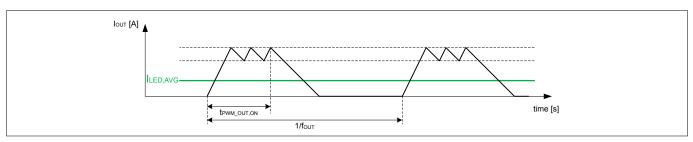

In analog dimming the output current is proportional to the internal CS reference voltage and the output current varies analogically between 100% and 12.5% of the target output current. Hybrid dimming applies below 12.5% of the target output current so that the output current is stable at 12.5% and amplitude modulated. The modulation signal has a frequency of typically 3.4 kHz to satisfy the IEEE1789-2015 recommendation for no observable flicker in light.

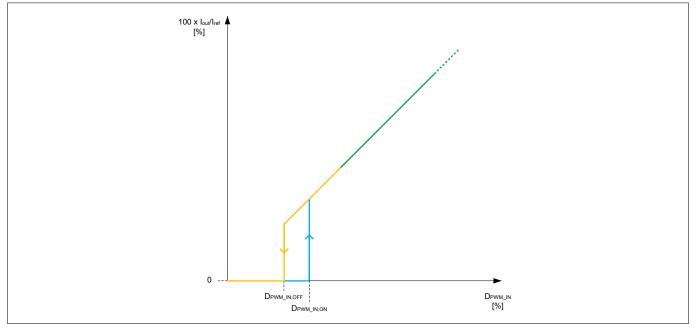

*Figure 5* shows the mapping between the input PWM duty cycle and the output current as a ratio of the target output current. *Figure 8* shows the detail of dim-to-off.

#### **Functional description**

#### Figure 5 Hybrid dimming curve

Figure 6 shows the output current in analog dimming.

### Figure 6 Output current waveform in analog dimming at two dimming levels

*Figure 7* shows the output current in hybrid dimming.

#### Figure 7 Output current waveform in hybrid dimming

The ILD8150 turns the output stage respectively off when the PWM dimming input signal duty cycle is less than  $D_{PWM\_IN,OFF}$  and on when the PWM dimming input signal duty cycle is higher than  $D_{PWM\_IN,ON}$ . The two dim-to-off levels create a hysteresis that avoids unstable states at the on/off boundary.

#### **Functional description**

#### Figure 8 Dimming curve dim-to-off detail

The ILD8150 evaluates the PWM dimming input signal duty cycle  $D_{PWM_IN}$  at the DIM pin. In analog dimming the duty cycle maps to a proportional CS reference voltage. In hybrid dimming the duty cycle maps to a hybrid dimming duty cycle using the hybrid dimming curve. The hybrid dimming frequency is fixed and does not relate to the input PWM frequency.

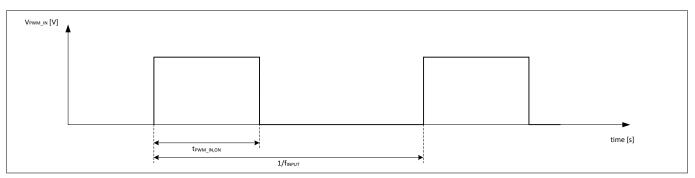

*Figure 9* shows the details of the input PWM signal where  $D_{PWM_{IN}} = t_{PWM_{IN},ON} \bullet f_{INPUT}$ .

#### Figure 9 Input PWM signal

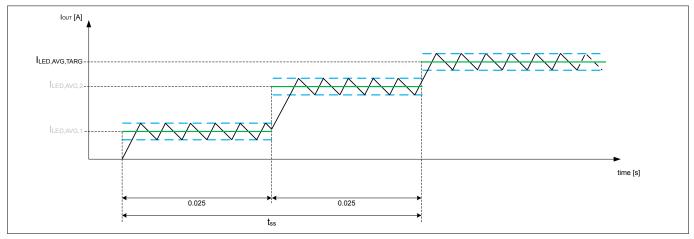

### **3.1.3** Digital soft-start

Soft-start is a feature that smooths output current transients during start-up.

Output current smoothing is digitally managed by the IC and applies in case of abrupt dimming changes. When the IC goes to dim-to-off the output current smoothing applies resulting in a soft-stop behavior. Benefits are the avoidance of under shoots or over shoots at primary side reflecting in a stable power regulation and reduction of components stress.

Digital soft-start uses of the PWM dimming signal. The PWM duty cycle sets the target dimming level and the PWM frequency sets the speed to reach that level. To lower PWM frequencies correspond a slower soft-start, to higher PWM frequencies correspond a faster soft-start. The output current ramps up to the target value in a determined soft start time  $t_{SS}$ .  $t_{SS}$  is defined as the time to reach the desired dimming level from a change in the PWM dimming signal. The number of steps of the soft-start ramp may vary depending on the actual and the target dimming level.

### **Functional description**

#### Figure 10 Digital soft-start

### Figure 11 Digital soft-start in dim-mode

*Figure 11* shows the output current soft-start in case of PWM dimming signal applied at the DIM pin.

*Note:* Output current smoothing does not affect the output current for small variations of the dimming signal e.g. to create light fading effects.

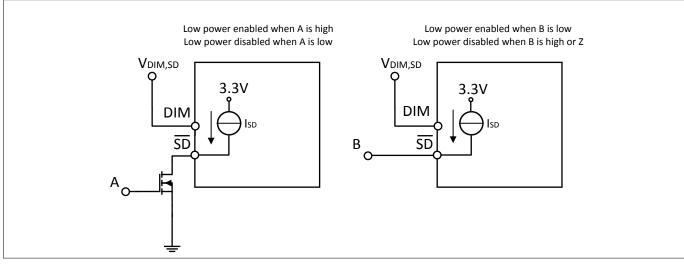

### 3.1.4 Low power mode

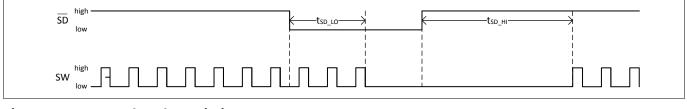

If the shut-down signal (SD neg.) is driven low for more than  $t_{SD\_LO}$  the low power mode is active. If the shut-down signal is held high for more than  $t_{SD\_HI}$  the IC resumes from low power mode.  $-I_{SD,HPU}$  dynamic current is needed to turn the IC into low power mode, then the current changes into static  $-I_{SD,LPU}$ . DIM pin needs to be driven externally with at least  $V_{DIM,SD}$  voltage during low power mode.

#### **Functional description**

Shut-down signal interfacing

Figure 13 Shut-down timings

### **3.2 Protection features**

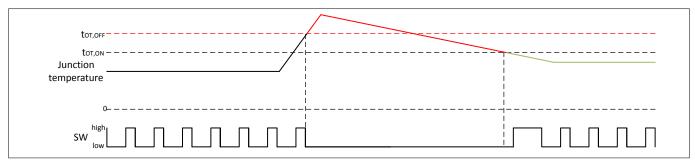

### 3.2.1 Over-temperature protection

The over-temperature protection turns off the output stage when the junction temperature exceeds the temperature threshold  $T_{OT,OFF}$ . When the junction temperature falls below the temperature threshold  $T_{OT,ON}$  the output stage turns on again.

In case of over-temperature the IC stops switching and waits for the over-temperature condition to disappear. The low power mode is not entered in case of over-temperature.

Figure 14

Over-temperature protection reaction

### 3.2.2 Under-voltage protection

The gate driver implements an under-voltage lock-out (UVLO) protection at high-side that switches-off the gate driver in case of BOOT under voltage (e.g. due to wrong bootstrap capacitor selection or incorrect system dimensioning).

In case of gate driver UVLO, the switch activity is interrupted in order to reload the bootstrap capacitor charge.

## 4 Thermal and electrical characteristics

This chapter describes the thermal and electrical characteristics of the ILD8150.

### 4.1 Package characteristics

#### Table 2 Package characteristics

| Parameter                                                                    | Symbol               | Limit val | ues | Unit | Remarks                                                                                                           |

|------------------------------------------------------------------------------|----------------------|-----------|-----|------|-------------------------------------------------------------------------------------------------------------------|

|                                                                              |                      | min       | max |      |                                                                                                                   |

| Thermal resistance for PG-<br>DSO-8 junction-to-ambient                      | R <sub>thJA</sub>    | _         | 170 | K/W  | JEDEC 1s0p no cooling<br>area, for 345 mW power<br>dissipation, <i>T</i> <sub>A</sub> = 90 °C                     |

|                                                                              | R <sub>thJA</sub>    | _         | 135 | K/W  | JEDEC 1s0p 100 mm <sup>2</sup><br>cooling area, for 440<br>mW power dissipation,<br>$T_A = 90 ^{\circ}C$          |

| Thermal resistance for PG-<br>DSO-8 junction-to-case top                     | R <sub>thJCtop</sub> | —         | 42  | K/W  | for 440 mW power<br>dissipation, <i>T</i> <sub>A</sub> = 90 °C                                                    |

| Thermal resistance for PG-<br>DSO-8 with exposed pad<br>junction-to-ambient  | R <sub>thJA</sub>    | _         | 160 | K/W  | JEDEC 1s0p no cooling<br>area, for 372 mW power<br>dissipation, <i>T</i> <sub>A</sub> = 90 °C                     |

|                                                                              | R <sub>thJA</sub>    | _         | 90  | K/W  | JEDEC 1s0p 100 mm <sup>2</sup><br>cooling area, for 635<br>mW power dissipation,<br><i>T</i> <sub>A</sub> = 90 °C |

| Thermal resistance for PG-<br>DSO-8 with exposed pad<br>junction-to-case top | R <sub>thJCtop</sub> | _         | 60  | K/W  | for 635 mW power<br>dissipation, <i>T</i> <sub>A</sub> = 90 °C                                                    |

### 4.2 Absolute maximum ratings

Attention: Stresses above the values listed below may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit. These values are not tested during production test.

| Parameter             | Symbol            | Symbol Limit values |     | Unit | Remarks |

|-----------------------|-------------------|---------------------|-----|------|---------|

|                       |                   | min                 | max |      |         |

| Junction temperature  | TJ                | _                   | 165 | °C   |         |

| Storage temperature   | T <sub>S</sub>    | -65                 | 150 | °C   |         |

| Soldering temperature | T <sub>SOLD</sub> | —                   | 260 | °C   |         |

Table 3Absolute maximum ratings

| Parameter             | Symbol            | Limit val       | ues              | Unit | Remarks                                                 |

|-----------------------|-------------------|-----------------|------------------|------|---------------------------------------------------------|

|                       |                   | min             | max              |      |                                                         |

| Latch-up              | I <sub>LU</sub>   | _               | 100              | mA   | <sup>3)</sup> Pin voltages acc. to abs.<br>max. ratings |

| ESD HBM <sup>4)</sup> | V <sub>HBM</sub>  | _               | 2000             | V    | 5)                                                      |

| ESD CDM               | V <sub>CDM</sub>  | _               | 500              | V    | 6)                                                      |

| Voltage at pin SW     | V <sub>SW</sub>   | -0.7            | 90               | V    |                                                         |

| Voltage at pin BOOT   | V <sub>BOOT</sub> | V <sub>SW</sub> | 90 <sup>7)</sup> | V    | Voltage internally supplied to BOOT pin                 |

| Voltage at pin DIM    | V <sub>DIM</sub>  | -0.3            | 3.6              | V    |                                                         |

| Voltage at pin CS     | V <sub>CS</sub>   | -0.3            | 1.5              | V    |                                                         |

| Voltage at pin SD     | V <sub>SD</sub>   | -0.3            | 3.6              | V    |                                                         |

| Voltage at pin VCC    | V <sub>VCC</sub>  | -0.3            | 9                | V    | Voltage internally supplied to VCC pin                  |

| Voltage at pin VIN    | V <sub>VIN</sub>  | -0.3            | 90               | V    |                                                         |

#### Table 3 Absolute maximum ratings (continued)

### 4.3 Operating conditions

The recommended operating conditions are shown for which the DC electrical characteristics are valid.

### Table 4Operating conditions

| Parameter            | Symbol           | Limit values |     | Unit | Remarks |

|----------------------|------------------|--------------|-----|------|---------|

|                      |                  | min          | max |      |         |

| Junction temperature | TJ               | -40          | 150 | °C   |         |

| VIN pin voltage      | V <sub>VIN</sub> | 8            | 80  | V    |         |

- <sup>5</sup> ESD-HBM according to JEDEC JS-001.

- <sup>6</sup> ESD-CDM according to JEDEC JS-002.

<sup>&</sup>lt;sup>3</sup> Latch-up according to JEDEC JESD78D,  $T_A$ = 85°C.

<sup>&</sup>lt;sup>4</sup> Two different classes of ESD protection elements are implemented within ILD8150/ILD8150E: 1. ESD protection at pin VS will be triggered if the voltage at pin VS rises by more than 5 V with a slew rate of more than 5 V/µs. This condition is met during an ESD event, but might also occur if the LED driver gets hotplugged into a power supply and the VS blocking capacitor has a too small capacitance. ESD protection will remain triggered as long as the slewrate condition is met. If the ESD protection gets triggered while VS is supplied the IC might be damaged. 2. ESD protection at all other pins is triggered once the connected voltage signal exceeds a threshold higher than the maximum voltage rating specified for each pin. No preventions regarding slew rate control need to be taken for these pins..

<sup>&</sup>lt;sup>7</sup> The voltage difference between BOOT and SW pins must never exceed 9 V.

### 4.4 Electrical characteristics

The DC electrical characteristics provide the spread of values applicable within operating conditions (see chapter 4.3).

Typical values represent the median values related to  $T_A = 25$  °C.

#### Table 5DC electrical characteristics

| Parameter                                          | Symbol                    |      | Values |      | Unit | Note or test condition                                                                |

|----------------------------------------------------|---------------------------|------|--------|------|------|---------------------------------------------------------------------------------------|

|                                                    |                           | Min. | Тур.   | Max. |      |                                                                                       |

| Integrated switch and driver                       |                           |      | _      |      |      |                                                                                       |

| VIN pin to SW pin ON                               | R <sub>ON</sub>           | _    | 290    | _    | mΩ   | / <sub>SW</sub> =200 mA <sup>8)</sup>                                                 |

| resistance                                         | R <sub>ON</sub>           | _    | _      | 545  | mΩ   | / <sub>SW</sub> =200 mA and <i>T</i> J=150 °C <sup>8)</sup>                           |

|                                                    | R <sub>ON</sub>           | _    | 330    | _    | mΩ   | / <sub>SW</sub> =200 mA <sup>9)</sup>                                                 |

|                                                    | R <sub>ON</sub>           | _    | _      | 585  | mΩ   | / <sub>SW</sub> =200 mA and <i>T</i> <sub>J</sub> =150 °C <sup>9)</sup>               |

| Gate-driver under-voltage<br>lock-out (turn-off)   | V <sub>GD_UVLO,OFF</sub>  | -    | 3.6    | _    | V    | V <sub>GD</sub> =V <sub>BOOT</sub> -V <sub>SW</sub>                                   |

| Gate-driver under-voltage<br>lock-out (turn-on)    | V <sub>GD_UVLO,ON</sub>   | -    | 3.7    | -    | V    | V <sub>GD</sub> =V <sub>BOOT</sub> -V <sub>SW</sub>                                   |

| Supply                                             |                           |      | _      |      | _    |                                                                                       |

| Voltage internally supplied to<br>VCC pin          | V <sub>VCC</sub>          | _    | _      | 7.3  | V    |                                                                                       |

| VIN pin operating current in dim-to-off            | I <sub>VIN_DO</sub>       | -    | -      | 2.3  | mA   | V <sub>DIM</sub> =0 V                                                                 |

| VIN pin operating current in shutdown              | I <sub>VIN_SD</sub>       | -    | -      | 100  | μA   | V <sub>SD</sub> =0 V and V <sub>DIM</sub> =3.3V<br>provided externally <sup>10)</sup> |

|                                                    | I <sub>VIN_SD</sub>       | -    | -      | 140  | μA   | V <sub>SD</sub> =0 V and V <sub>DIM</sub> =3.3V<br>provided externally <sup>11)</sup> |

| VIN under-voltage lock-out<br>(turn-off)           | V <sub>VIN_UVLO,OFF</sub> | -    | 7.1    | _    | V    |                                                                                       |

| VIN under-voltage lock-out<br>(turn-on)            | V <sub>VIN_UVLO,ON</sub>  | -    | 7.5    | _    | V    |                                                                                       |

| Shutdown                                           |                           | - 1  | _      |      | _    |                                                                                       |

| SD pin input high voltage                          | V <sub>SD,IH</sub>        | 2.1  | _      | _    | V    |                                                                                       |

| SD pin input low voltage                           | V <sub>SD,IL</sub>        | _    | _      | 1.0  | V    |                                                                                       |

| SD pin, reduced pull-up<br>current during shutdown | -I <sub>SD,LPU</sub>      | -    | -      | 3.0  | μA   | V <sub>SD</sub> =0 V V <sub>DIM</sub> >V <sub>DIM,SD</sub> provided<br>externally     |

| SD pin, initial pull-up current to start shutdown  | -I <sub>SD,HPU</sub>      | -    | 48     | 71   | μA   | $V_{SD} > V_{SD,IH} V_{DIM} > V_{DIM,SD}$<br>provided externally                      |

<sup>8</sup> PG-DSO-8

<sup>9</sup> PG-DSO-8 with exposed pad

<sup>10</sup> Tested at  $V_{VIN}$ =8 V.

<sup>11</sup> Tested at  $V_{VIN}$ =80 V.

#### Table 5DC electrical characteristics (continued)

| Parameter                            | Symbol                | Symbol Values |      |          | Unit | Note or test condition                                                              |

|--------------------------------------|-----------------------|---------------|------|----------|------|-------------------------------------------------------------------------------------|

|                                      |                       | Min.          | Тур. | Max.     |      |                                                                                     |

| DIM pin low power mode<br>current    | I <sub>DIM,SD</sub>   | _             | 52   | 105      | μΑ   | V <sub>SD</sub> =0 V                                                                |

| DIM pin low power mode<br>voltage    | V <sub>DIM,SD</sub>   | 3.1           | -    | —        | V    | V <sub>SD</sub> =0 V                                                                |

| Regulation                           | ·                     |               |      |          |      |                                                                                     |

| CS reference voltage high            | V <sub>CSH</sub>      | 379           | 390  | 401      | mV   | undimmed                                                                            |

| CS reference voltage low             | V <sub>CSL</sub>      | 320           | 330  | 340      | mV   | undimmed                                                                            |

| CS reference voltage<br>hysteresis   | HYST <sub>CS</sub>    | 7             | _    | _        | %    | peak-to-average<br>$HYST_{CS}$ $= 100x \frac{V_{CSH} - V_{CSL}}{V_{CSH} + V_{CSL}}$ |

| Dimming                              | ·                     |               |      |          |      |                                                                                     |

| DIM pin input high voltage           | V <sub>DIM,IH</sub>   | 2.1           | _    | <b>—</b> | V    |                                                                                     |

| DIM pin input low voltage            | V <sub>DIM,IL</sub>   | _             | _    | 1.0      | V    |                                                                                     |

| Input low current (internal pull-up) | -I <sub>DIM,LPU</sub> | —             | -    | 65       | μΑ   | V <sub>DIM</sub> =0 V                                                               |

The values in switching characteristics are verified by design and not tested in production test.

#### Table 6Switching characteristics

| Parameter                       | Symbol              |      | Values |                    |     | Note or test condition                                 |

|---------------------------------|---------------------|------|--------|--------------------|-----|--------------------------------------------------------|

|                                 |                     | Min. | Тур.   | Max.               | _   |                                                        |

| Integrated switch and drive     | r                   |      | _      |                    |     |                                                        |

| Undimmed average switch current | I <sub>SW,AVG</sub> | -    | _      | 1.5 <sup>12)</sup> | A   | selectable using CS shunt resistor                     |

| Switching frequency             | f <sub>SW</sub>     | _    | _      | 2                  | MHz |                                                        |

| Shutdown                        | ·                   |      |        | - <b>I</b>         | 1   |                                                        |

| SD pin stable high              | t <sub>SD_HI</sub>  | 20   | -      | -                  | ms  | time to begin of SW turn-on<br>(low power mode exit)   |

| SD pin stable low               | t <sub>SD_LO</sub>  | 5    | -      | -                  | μs  | time to begin of SW turn-off<br>(low power mode entry) |

| Regulation                      | I                   | 1    | -      |                    |     |                                                        |

|                                 |                     |      |        |                    |     |                                                        |

| Delay from V <sub>CS</sub> crossing to | t <sub>CSSW</sub> | — | <br>120 | ns |  |

|----------------------------------------|-------------------|---|---------|----|--|

| begin of SW turn-off or turn-          |                   |   |         |    |  |

| on                                     |                   |   |         |    |  |

<sup>&</sup>lt;sup>12</sup> The system must be capable of dissipating the power.

### Thermal and electrical characteristics

### Table 6 Switching characteristics (continued)

| Parameter                                      | Symbol                  |      | Values            |                           | Unit  | Note or test condition    |

|------------------------------------------------|-------------------------|------|-------------------|---------------------------|-------|---------------------------|

|                                                |                         | Min. | Тур.              | Max.                      | 1     |                           |

| Dimming                                        |                         |      | _                 |                           | _     |                           |

| Output current hybrid<br>dimming frequency     | f <sub>OUT</sub>        | 3060 | 3400              | 3740                      | Hz    |                           |

| Input PWM frequency                            | f <sub>INPUT</sub>      | 250  | _                 | 20000                     | Hz    |                           |

| Input PWM recognizable duty cycle              | D <sub>PWM_IN</sub>     | 0    | _                 | 100                       | %     |                           |

| Input PWM duty cycle dim-to-<br>off (turn-off) | D <sub>PWM_IN,OFF</sub> | -    | 0.45              | -                         | %     |                           |

| Input PWM duty cycle dim-to-<br>off (turn-on)  | D <sub>PWM_IN,ON</sub>  | _    | 0.5               | -                         | %     |                           |

| Input PWM recognizable duty cycle accuracy     | A <sub>PWM_IN</sub>     | -    | ±2 <sup>-14</sup> | -                         | LSB-1 | f <sub>INPUT</sub> =1 kHz |

| Over-temperature protectior                    | 1                       |      | _                 |                           | _     |                           |

| Thermal shutdown threshold<br>(turn-off)       | T <sub>OT,OFF</sub>     | 153  | _                 | 161                       | °C    |                           |

| Thermal shutdown threshold<br>(turn-on)        | T <sub>OT,ON</sub>      | 138  | -                 | 146                       | °C    |                           |

| Thermal shutdown hysteresis                    | T <sub>OT,HYST</sub>    | 15   | _                 | _                         | °C    |                           |

| Soft-start                                     |                         |      |                   |                           |       |                           |

| Soft-start time in dimming                     | t <sub>SS</sub>         | —    | _                 | 10/<br>f <sub>INPUT</sub> | S     |                           |

| Soft-start time undimmed                       | t <sub>SS,100%</sub>    | _    | _                 | 50                        | ms    |                           |

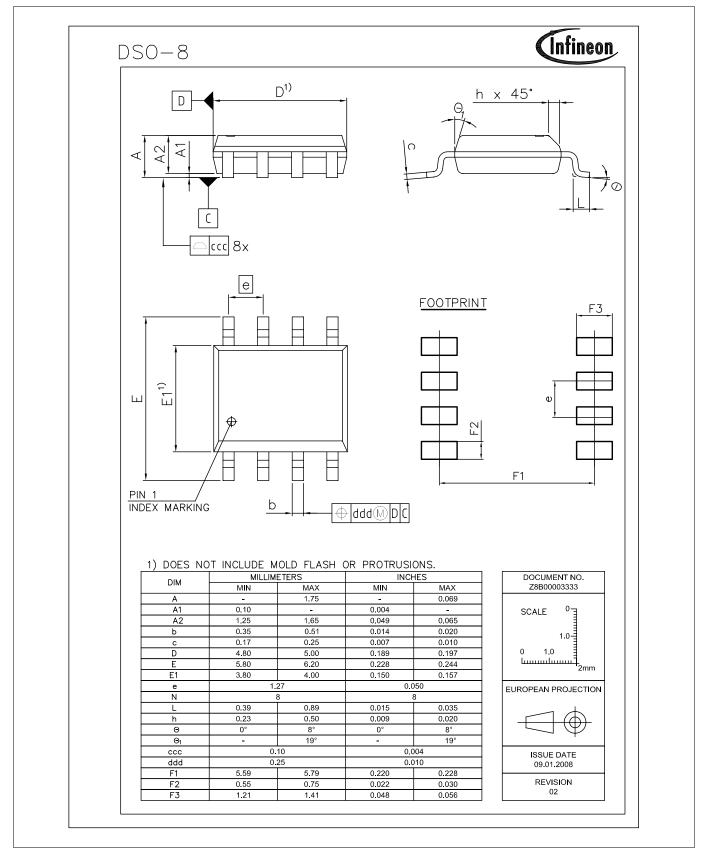

### Package dimensions

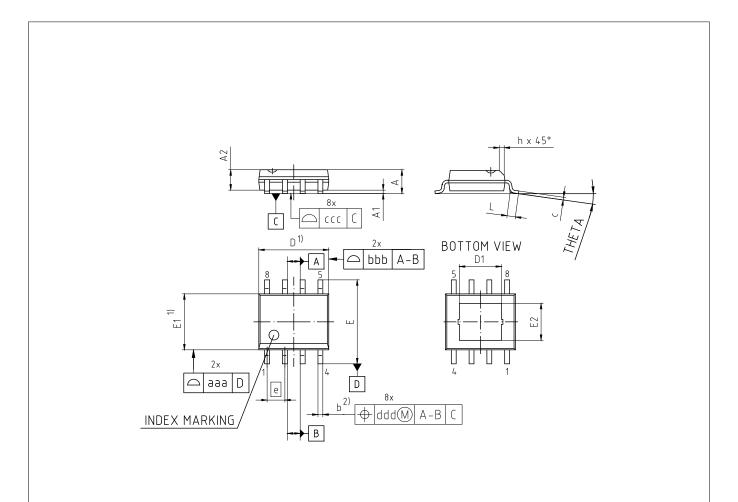

## 5 Package dimensions

The package dimensions of PG-DSO-8 and PG-DSO-8 with exposed pad are provided.

Figure 15 Package dimensions for PG-DSO-8

### Package dimensions

1) DOES NOT INCLUDE PLASTIC OR METAL PROTRUSION OF 0.15 MAX. PER SIDE 2) DAMBAR PROTRUSION SHALL BE MAXIMUM 0.1 mm TOTAL IN EXCESS OF LEAD WIDTH.

| DIMENSIONS | MILLIMETERS |      |

|------------|-------------|------|

|            | MIN.        | MAX. |

| A          | -           | 1.70 |

| A1         | 0.00        | 0.10 |

| A2         | 1.45        |      |

| b          | 0.32        | 0.50 |

| c          | 0.19        | 0.25 |

| D          | 4.80        | 5.10 |

| D1         | 2.80        | 3.20 |

| E          | 5.80        | 6.20 |

| E1         | 3.80        | 4.00 |

| E2         | 2.45        | 2.85 |

| е          | 1.27        |      |

| h          | 0.35        |      |

| L          | 0.39        | 0.99 |

| THETA      | 0°          | 8°   |

| aaa        | 0.10        |      |

| bbb        | 0.10        |      |

| ccc        | 0.08        |      |

| ddd        | 0.20        |      |

Figure 16

#### Package dimensions for PG-DSO-8 with exposed pad

### **Revision history**

# **Revision history**

Major changes since previous revision

### **Revision history**

| Revision instory |                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------|

| Reference        | Description                                                                                          |

| V1.0             | First release                                                                                        |

| V1.1             | Absolute maximum ratings changed (V <sub>SW</sub> min)                                               |

| V1.2             | $R_{\rm ON}$ split for $T_{\rm A}$ = 25 °C and $T_{\rm J}$ = 150 °C                                  |

| V1.3             | –I <sub>SD,HPU</sub> , I <sub>DIM,LPI</sub> and V <sub>DIM,SD</sub> added, SD pin behavior described |

| V1.4             | ESD protection described                                                                             |

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2021-01-19 Published by Infineon Technologies AG 81726 Munich, Germany

© 2021 Infineon Technologies AG All Rights Reserved.

Do you have a question about any aspect of this document? Email: erratum@infineon.com

Document reference IFX-vxc1510921414939

#### **IMPORTANT NOTICE**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Infineon: REFILD8150DC15ASMDTOBO1