# ICC80QSG

## **Datasheet for ICC80QSG**

## Features

The ICC80QSG flyback controller is tailored for battery charger application to meet the required performance. **Features**

- Secondary side regulation (SSR), for battery charging current control

- High efficiency and low electromagnetic interference (EMI) with quasi-resonant valley switching

- Quasi-resonant mode (QRM) operation with continuous conduction mode (CCM)-prevention and valley switching discontinuous conduction mode (DCM) in mid to light load

- Burst mode for very light loads and low system standby power consumption

- Reduced gate driver output voltage during burst mode for lower standby power

- Adjustable on-time mapping at valley changing position, for the desired maximum operating switching frequency

- Adjustable maximum on-time limits input power and current allowing safe-operation under low line condition

- Comprehensive set of protections:

- internal overtemperature protection (OTP)

- flyback output overvoltage protection (OVP)

- primary side over-current protection (OCP)

- brownin protection

- brownout protection

- VCC overvoltage protection

- open loop protection

- input overvoltage protection

- Externally configurable hysteresis of brownin and brownout

- Adaptive brownout level triggering based on bus voltage ripple protect primary components from overheating and saturation with higher brownout level at higher input/output power

- Supports on/off control with external pull-down signal

- Soft start to reduce component stress during turn-on

- External start-up circuit control signal

## **Potential applications**

- Tailored for battery charger application up to 130 W

- Also suited for adapter, printer, PC, TV, monitor, set-top box, audio amplifier applications up to 130 W

## **Product validation**

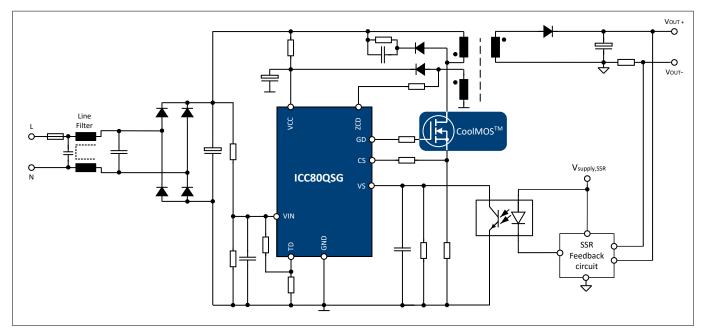

#### Figure 1 Flyback with SSR control

| Product type | Package  | Ordering code |

|--------------|----------|---------------|

| ICC80QSG     | PG-DSO-8 | SP005731066   |

## **Product validation**

Qualified for applications listed above based on the test conditions in the relevant tests of JEDEC20/22.

## Description

The ICC80QSG is a voltage mode controller for flyback topologies operating in quasi-resonant mode and valley switching DCM, to achieve high efficiency of power transfer across wide operating range.

For battery charging application, the IC offers a wide power range as well as a comprehensive set of protections. The IC is easy to design in and requires a minimum number of external components.

The gate driver current enables reasonable designs up to 130 W with state-of-the-art MOSFETs. The system performance and efficiency can be optimized using Infineon CoolMOS<sup>™</sup> P7 power MOSFETs.

The integrated burst mode function allows designs with a very low standby power consumption during standby mode and very light loads.

Table of contents

## **Table of contents**

|        | Table of contents                                             |

|--------|---------------------------------------------------------------|

| 1      | Pin configuration                                             |

| 2      | Block diagram                                                 |

| 3      | Functional description                                        |

| 3.1    | Start-up                                                      |

| 3.2    | TD pin internal pull-up and external start-up circuit control |

| 3.3    | Input voltage detection and protection8                       |

| 3.4    | ZCD pin signal sensing                                        |

| 3.5    | TD configuration                                              |

| 3.6    | VS pin signal sensing                                         |

| 3.7    | Operating modes                                               |

| 3.8    | Pulse generation                                              |

| 3.9    | Primary side overcurrent protection 18                        |

| 3.10   | VCC voltage protections                                       |

| 3.11   | Flyback output overvoltage protection19                       |

| 3.12   | Overtemperature protection                                    |

| 3.13   | Open loop protection                                          |

| 3.14   | State flow chart and fault reaction21                         |

| 3.15   | Adjustable functions                                          |

| 4      | <b>Electrical characteristics and parameters</b> 23           |

| 4.1    | Absolute maximum ratings                                      |

| 4.2    | Operating conditions                                          |

| 4.3    | DC electrical characteristics                                 |

| 4.3.1  | Power supply                                                  |

| 4.3.2  | Zero crossing detection                                       |

| 4.3.3  | Voltage sense                                                 |

| 4.3.4  | Input voltage detection                                       |

| 4.3.5  | TD configuration                                              |

| 4.3.6  | Current sense                                                 |

| 4.3.7  | PWM generation                                                |

| 4.3.8  | Gate driver                                                   |

| 4.3.9  | Clock oscillators                                             |

| 4.3.10 | Temperature sensor                                            |

| 5      | Package dimensions                                            |

| 6      | Glossary                                                      |

| 7      | Revision history                                              |

Table of contents

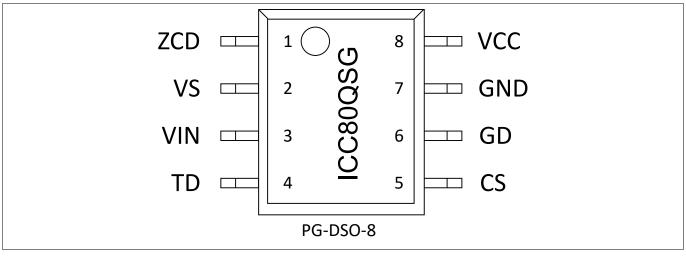

## 1 Pin configuration

1

## **Pin configuration**

## Figure 2 Pin configuration

## Table 1Pin definition and function

| Symbol | Pin | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ZCD    | 1   | <b>Zero crossing detection</b><br>This pin is connected to an auxiliary winding via a series resistor to detect the zero crossing, for QRM valley switching. This series resistor value can be adjusted to configure the on-time mapping and maximum on-time.                                                                                                                                                                                                   |

| VS     | 2   | <b>Feedback sensing</b><br>This pin measures the feedback signal in the form of load current, for output regulation<br>with voltage mode control.                                                                                                                                                                                                                                                                                                               |

| VIN    | 3   | <b>Input voltage detection</b><br>This pin is used to measure the primary bus voltage via a resistor divider for the power<br>limitation function, brownin, brownout and input overvoltage protection.                                                                                                                                                                                                                                                          |

| TD     | 4   | <b>Turn-on delay</b><br>The resistance to ground <i>R</i> <sub>TD</sub> of this pin can adjust the turn-on delay upon zero crossing detection for QRM valley switching. The internal pull-up of this pin can also be used to control an external start-up circuit for active <i>V</i> <sub>VCC</sub> charging. In addition, connecting a resistor between this pin and <i>VIN</i> pin can configure the hysteresis between brownin and brownout voltage levels. |

| CS     | 5   | <b>MOSFET current sense and flyback output overvoltage protection</b><br>This pin is used for primary side overcurrent protection. The series resistance (connected between this pin and the primary MOSFET current shunt resistor) can be used to adjust the flyback output over-voltage protection level.                                                                                                                                                     |

| GD     | 6   | <b>Gate driver</b><br>This pin controls the gate of the MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                 |

| GND    | 7   | <b>Ground</b><br>This pin is connected to ground and represents the ground level of the IC for the supply voltage, gate driver and sense signals.                                                                                                                                                                                                                                                                                                               |

| VCC    | 8   | <b>Operating voltage supply</b><br>This pin supplies the IC.                                                                                                                                                                                                                                                                                                                                                                                                    |

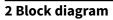

2 Block diagram

Figure 3

**Block diagram**

## 3 Functional description

These sections describe the listed functions in detail.

## 3.1 Start-up

In the pre-start-up phase, ICC80QSG measures the *TD* pin resistance to ground  $R_{TD}$ , the average *VIN* pin voltage  $V_{VIN,avg}$ , and its internal junction temperature  $T_j$ . If the conditions for start-up are met, ICC80QSG initiates a soft start, to reduce the component stress during start-up.

After the soft start is completed without any protection triggering, ICC80QSG enters the RUN state for output regulation based on *VS* pin signal sensing.

*Note:* The reduced gate driver voltage V<sub>GDred</sub> (7 V typ.) is applied during start-up.

## 3.2 TD pin internal pull-up and external start-up circuit control

Apart from charging the  $V_{VCC}$  from the HV bus voltage via the current limiting resistor in Figure 1, ICC80QSG *TD* pin also supports the control of an exemplary external start-up circuit in Figure 4 for active  $V_{VCC}$  charging, with the following typical start-up sequence:

- When ICC80QSG is in the undervoltage lockout (UVLO) state and V<sub>VCC</sub> < V<sub>VCCon</sub> (12.5 V typ.), the *TD* pin internal pull-up is disabled.

- **2.**  $V_{VCC}$  is charged to  $V_{VCCon}$  by the external start-up circuit, to activate ICC80QSG.

- **3.** In the pre-start-up phase, ICC80QSG enables the *TD* pin internal pull-up resistor of  $R_{TD,RUN}$  (10 k $\Omega$  typ.) and  $R_{TD,flyback}$  (40 k $\Omega$  typ.) sequentially, to measure the *TD* pin resistance to ground of  $R_{TD}$ .

- **4.** If the start-up conditions are met and the start-up is successful, *R*<sub>TD,RUN</sub> is enabled in the soft start phase and in RUN state, to disable the external start-up circuit from charging the V<sub>VCC</sub>. If any protection is triggered, ICC80QSG enters UVLO state (returns sequence number 1) after a restart timer is expired.

- Note: The internal voltage reference for the TD pin internal pull-up, V<sub>REF</sub> is typically 3.3 V.

- Note:  $R_{\text{TD,RUN}}$  is disabled in burst mode when VCC drops to  $V_{\text{VCCwake}}$  (7.6 V typ.), to allow the external start-up circuit to charge  $V_{\text{VCC}}$  to  $V_{\text{VCCburst}}$  (8.1 V typ).

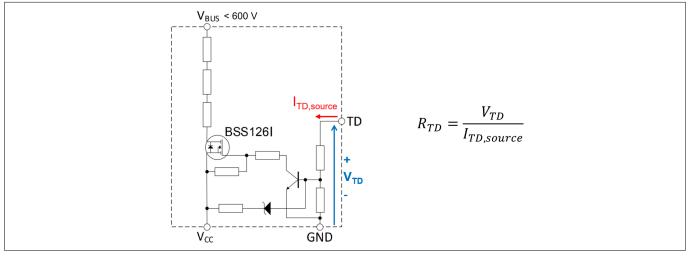

Figure 4 shows the equation for  $R_{TD}$  calculation when the exemplary start-up circuit is connected to the *TD* pin. The  $R_{TD}$  detected in the pre-start-up phase must be designed to be at least 27 k $\Omega$  when *TD* pin is internally pulled up by  $R_{TD,RUN}$ , and not more than 68 k $\Omega$  when *TD* pin is internally pulled up by  $R_{TD,flyback}$ . The is to activate the *VS* pin load current sensing for output regulation and stay within the TD configuration limit.

Exemplary external start-up circuit for active  $V_{VCC}$  charging, and  $R_{TD}$  generic equation

## 3.3 Input voltage detection and protection

ICC80QSG detects the AC or DC amplitude based on the ADC sampling of the VIN pin voltage. For the power limiting function, brownin and brownout protections, the controller measures the average VIN pin voltage  $V_{\text{VIN},\text{avg}}$  based on the middle value of the highest VIN pin voltage sample and the lowest VIN pin voltage sample within an observation time. The observation time in RUN state is around 10.6 ms and 12.7 ms, based on the last synced AC line frequency of 50 Hz and 60 Hz, respectively.

*Note:* In case of non-line-syncing, the observation time is around 10.6 ms. For example, non-line-syncing can happen when the system is started up with a DC input.

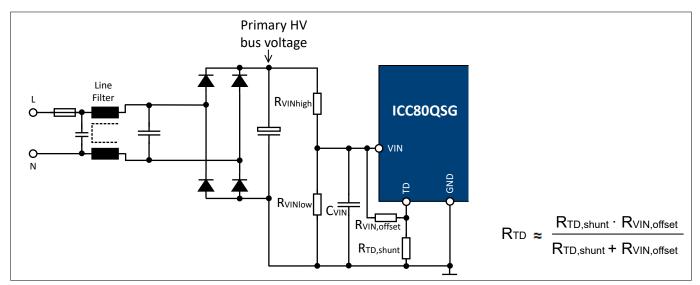

At higher power transfer, the primary bus voltage ripple is higher, and  $V_{VIN,avg}$  becomes lower. As a result, a relatively higher AC input brownout protection level can be triggered at higher power transfer, to better protect the primary components from overheating and saturation in case of input under-voltage condition occurs. Apart from that, the hysteresis between AC input brownin and brownout level can be added externally with  $R_{VIN,offset}$ , as shown in Figure 5. It works by creating an offset voltage on the *VIN* pin when the *TD* pin internal pull-up is enabled in RUN state.

When the  $R_{\text{VIN,offset}}$  is connected between TD pin and VIN pin,  $R_{\text{TD}}$  can be approximated based on the equation shown in Figure 5. The  $R_{\text{TD}}$  detected in the pre-start-up phase must be designed to be at least 27 k $\Omega$  when TDpin is internally pulled up by  $R_{\text{TD,RUN}}$ , and not more than 68 k $\Omega$  when TD pin is internally pulled up by  $R_{\text{TD,flyback}}$ , to activate the VS pin load current sensing for output regulation and stay within the TD configuration limit.

#### Figure 5 V<sub>IN</sub> pin circuit

In addition, the ICC80QSG VIN pin has an input overvoltage threshold of  $V_{VINOV}$  (2.0 V typ.) and a short protection with a threshold of  $V_{VINshort}$  (200 mV typ.).

During operation, if a sampled VIN pin voltage  $V_{VIN} < V_{VINshort}$  is detected for more than a blanking time, the VIN pin short protection is triggered. If the  $V_{VIN} < V_{VINshort}$  condition remains after the VIN pin short protection restart time of  $t_{restart}$  (200 ms typ.), the brownin protection is triggered based on  $V_{VIN,avg} < V_{BI}$  detection instead. This leads to a fast restart cycle of  $t_{restart,fast}$  (25 ms typ.) afterwards.

By pulling down the *VIN* pin signal to a level that triggers the *VIN* pin short protection or brownout protection, ICC80QSG gate pulse generation can be disabled and the controller current consumption can be lowered.

## 3.4 ZCD pin signal sensing

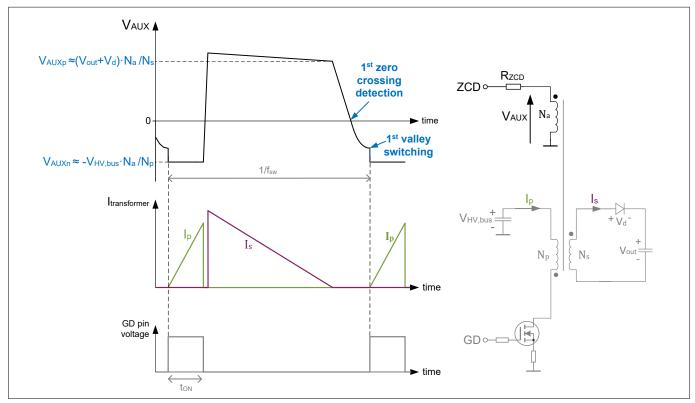

ICC80QSG ZCD pin detects the auxiliary winding voltage zero-crossing via a ZCD series resistor of  $R_{ZCD}$  connected to the winding. A zero-crossing is detected with the hysteresis of  $V_{ZCDUp}$  (55 mV typ.) and  $V_{ZCDDown}$  (45 mV typ.) thresholds.

In QRM, ICC80QSG counts the number of zero crossings until the target number is reached, and switches on at the valley to minimize the switching loss. If the target number is not reached and further zero crossing signals

#### **3 Functional description**

are not detectable via *ZCD* pin, zero crossing events can be generated internally by extrapolation. Figure 6 shows an example of the 1<sup>st</sup> zero crossing detection and the 1<sup>st</sup> valley switching in QRM operation.

# Figure 6 Exemplary waveform of QRM operation with 1<sup>st</sup> zero crossing detection and 1<sup>st</sup> valley switching

$R_{ZCD}$  limits the ZCD pin sink and source currents when the auxiliary winding voltage exceeds the ZCD pin internal clamping levels  $V_{ZCDpclp}$  (0.55 V typ.) and  $V_{ZCDnclp}$  (-0.5 V typ.), respectively. When the sensed voltage level of the auxiliary winding is not sufficient (for example, during start-up), an internal start-up timer initiates a new cycle every  $t_{Rep}$  (52 µs typ.) after turn-off of the gate driver. From the ZCD pin sink and source currents, ICC80QSG detects the ZCD pin positive peak settled clamping current  $I_{ZCDpclp}$  (for flyback output overvoltage protection) and negative peak settled clamping current  $I_{ZCDnclp}$ .

$$I_{ZCDpclp} = \frac{V_{AUXp} - V_{ZCDpclp}}{R_{ZCD}}$$

#### **Equation 1**

$$I_{ZCDnclp} = \frac{\left|V_{AUXn}\right| - \left|V_{ZCDnclp}\right|}{R_{ZCD}}$$

#### **Equation 2**

Where  $V_{AUXp}$  and  $V_{AUXn}$  are the positive peak and negative peak values, respectively, of the settled auxiliary winding voltages, as shown in Figure 6.

In addition, ICC80QSG derives the ZCD pin peak to peak settled clamping current  $I_{\text{ZCDclp}}$  based on the sum of  $I_{\text{ZCDpclp}}$  and  $I_{\text{ZCDnclp}}$ , for its internal operations, such as pulse generation and power limitation.

$I_{ZCDclp} = I_{ZCDpclp} + I_{ZCDnclp}$

#### **Equation 3**

## 3.5 TD configuration

The *TD* pin resistance to ground  $R_{TD}$  measurement in the pre-start-up phase has to be fine-tuned manually for a given system, to adjust the turn-on delay (TD) upon zero-crossing detection, for quasi-resonant valley switching.

If there is any circuit more than just a resistor connected between *TD* pin and ground, the following generic equation for *R*<sub>TD</sub> calculation is applied:

$$R_{TD} = \frac{V_{TD}}{I_{source, TD}}$$

#### **Equation 4**

Where  $V_{TD}$  is the *TD* pin voltage with reference to ground and  $I_{source,TD}$  is the current flowing out of *TD* pin, when the internal pull-up resistor of  $R_{TD,RUN}$  or  $R_{TD,flyback}$  is enabled in the pre-start-up phase.

Based on Equation 4, the equation for  $R_{TD}$  approximation in Figure 5 can be derived, when a resistor  $R_{VIN,offset}$  is added between *VIN* pin and *TD* pin to configure the brownin and brownout hysteresis.

The minimum  $R_{TD}$  value for TD configuration and to activate the VS pin load current sensing for output regulation in RUN state is 27 k $\Omega$ , when TD pin is internally pulled up by  $R_{TD,RUN}$  in the pre-start-up phase.

The maximum  $R_{TD}$  value for TD configuration is 68 k $\Omega$ , when *TD* pin is internally pulled up by  $R_{TD,flyback}$  in the pre-start-up phase.

If a calculation based on the equation for  $R_{TD}$  approximation results to an approximate  $R_{TD}$  which is close to 27 k $\Omega$  or 68 k $\Omega$ , Equation 4 should be used to verify whether the actual  $R_{TD}$  is still within limits.

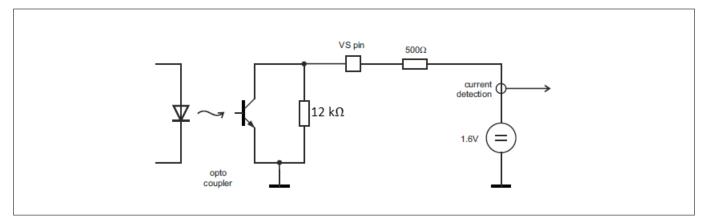

## 3.6 VS pin signal sensing

In RUN state, ICC80QSG measures the feedback signal for output regulation based on the ADC sampling of the *VS* pin load current. When operating in QRM with AC input, ICC80QSG also synchronizes some of its operation to the line frequency or AC half cycle, when the *VS* pin load current ripple is large enough.

To activate the VS pin load current sensing for output regulation in RUN state, a 12 k $\Omega$  resistor must be connected from the VS pin to ground, and  $R_{TD}$  must be at least 27 k $\Omega$  when TD pin is internally pulled up by  $R_{TD,RUN}$  in the pre-start-up phase.

For secondary side regulation, the VS pin load current consists of the current flowing through the opto coupler and the 12 k $\Omega$  resistor. When the VS pin load current is - $I_{VSADCmin}$  (210  $\mu$ A typ.) or less, the power transfer is maximum. When the VS pin load current is - $I_{VSADCmax}$  (610  $\mu$ A typ.) or more, the power transfer is minimum.

#### VS pin load current sensing based on secondary side regulation

## 3.7 Operating modes

In RUN state, ICC80QSG operates in either QRM or burst mode.

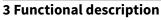

## Quasi-resonant mode (QRM)

QRM maximizes the efficiency and minimizes the EMI by turning on the power switch at the drain voltage valley. ICC80QSG controls the on-time and valley number in QRM. When the valley number changes, the controller compensates the QRM on-time to achieve a relatively constant power transfer for a smooth transition.

Figure 8 areas highlighted in blue show the on-time compensation effect (in zig-zag pattern) when, for example, the QRM valley number is increased from 1 to 2, from 2 to 3, and from 3 to 4. When the relative power is further decreased, the on-time compensation continues at higher valley changing position (in smaller zig-zag), until it reaches the maximum valley number of 32. To ensure the QRM switching frequency reduction stays above the audible range, the QRM off-time is limited to a maximum value of  $t_{\rm Off}$  (47 µs typ.).

Increasing the ICC80QSG valley number ensures that the system-dependent QRM remains below a certain limit, to achieve a high efficiency and low EMI spectrum over a wide operating range.

Figure 8

Exemplary switching characteristics versus relative power, with on-time compensation for valley changing

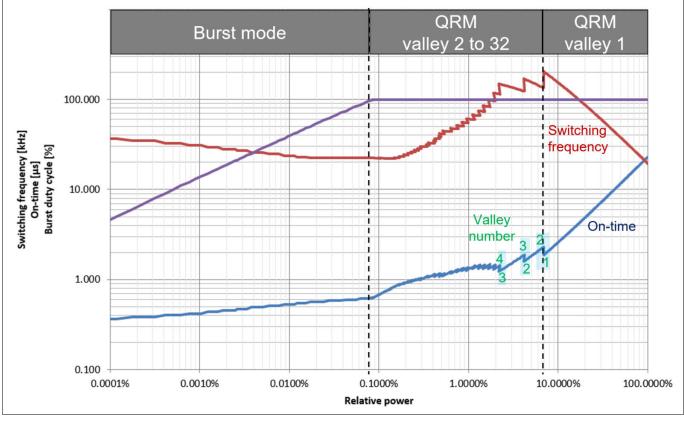

#### Burst mode

Burst mode transfers lesser power than QRM, to support light loads and no load/standby operation.

To achieve a low standby power, the controller sleeps during burst pause, to reduce its current consumption. In addition, the controller operates in burst mode with a reduced gate driver voltage level of  $V_{GDred}$  (7 V typ.), to minimize the gate charge loss.

The controller wakes up at a regular repetition frequency  $f_{\text{wake,reg}}$ , to do the burst pulsing based on the measured VS pin load current signal, and goes to sleep during burst pause, as shown in Figure 9.

$f_{\text{wake,reg}}$  is approximately four times the last synced input line frequency. For example,  $f_{\text{wake,reg}}$  is around 240 Hz, if the last synced input line frequency is 60 Hz.

#### **3 Functional description**

Note:

In case of non-line-syncing happened before entering the burst mode, f<sub>wake,reg</sub> = 200 Hz typ. is applied. For example, non-line-syncing can happen when the system is supplied with a DC input or when the VS pin load current ripple is very small at low load.

To maintain sufficient  $V_{VCC}$  in burst mode, the controller operates with the following two mechanisms:

- Instead of waking up based on the regular  $f_{wake,reg}$ , a higher priority VCC wake-up threshold can trigger a burst start if  $V_{VCC}$  drops to  $V_{VCCwake}$  (7.6 V typ.). The controller continues the burst pulsing until  $V_{VCC} = V_{VCCburst}$  (8.1 V typ.).

- The *TD* pin internal pull-up resistor is disabled when *V*<sub>VCC</sub> drops to *V*<sub>VCCwake</sub>, to allow an external start-up circuit to charge *V*<sub>VCC</sub> to *V*<sub>VCCburst</sub>.

As a result, the burst cycle  $1/f_{burst}$  does not necessarily follow  $1/f_{wake,reg}$ , as shown in Figure 9. The burst cycle can be extended by an integer times of  $1/f_{wake,,reg}$  in case of a burst pulse skipping, or can be reduced by a portion of  $1/f_{wake,reg}$  in case of a VCC wake-up burst triggering, or from a combination of both effects.

Attention: The VCC wake-up burst control mechanism is intended to work with the VCC voltage supply via the ZCD winding. In case of the VCC voltage is supplied via a winding voltage, which follows a certain ratio of the primary bus voltage, it is a must to ensure that the VCC voltage during burst mode is always higher than V<sub>VCCburst</sub> maximum value (9.1 V maximum) by a sufficient margin, especially when the input voltage is low and close to brownout level, so that the VCC wake-up burst mechanism can be avoided, to achieve a good output regulation.

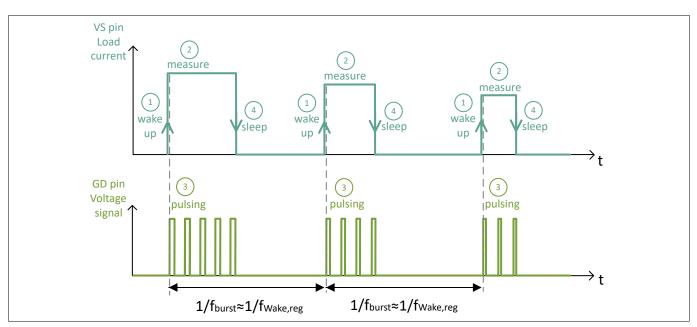

## 3.8 Pulse generation

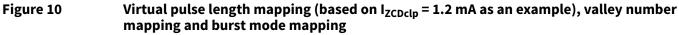

In RUN state, the ICC80QSG maps the measured VS pin load current to the virtual pulse length, valley number and burst duty cycle, as shown in Figure 10.

These internal parameters are processed together with the power limitation parameter, and fed to the pulse generation and TD correction function block, as shown in the Block diagram.

#### Virtual pulse length mapping and its use case

The virtual pulse length mapping is an illustrative on-time mapping which excludes:

- the system-dependent on-time compensation effect for valley number change (see Figure 8)

- the turn-on delay effect (configured by the *TD* pin resistance to ground) for QRM valley switching

- the power limiting effect on the maximum on-time (to be explained in this chapter)

- the minimum gate pulse length limit by the pulse generation block

- The virtual pulse length mapping shown in Figure 10 is not static.

It shifts vertically based on the ZCD pin peak to peak settled clamping current  $I_{ZCDclp}$ , which is dependent on the  $R_{ZCD}$ , transformer winding turns ratio, operating input and output voltages.

As shown in Figure 11, a different  $I_{ZCDclp}$  level leads to a change on the virtual pulse length at every valleychanging position, including the burst mode entry position. It means when the input voltage is lower or when  $R_{ZCD}$  value is increased for example, a decrease of  $I_{ZCDclp}$  leads to the relative on-time decrease at every valley-changing position, including the burst mode entry position. And vice-versa.

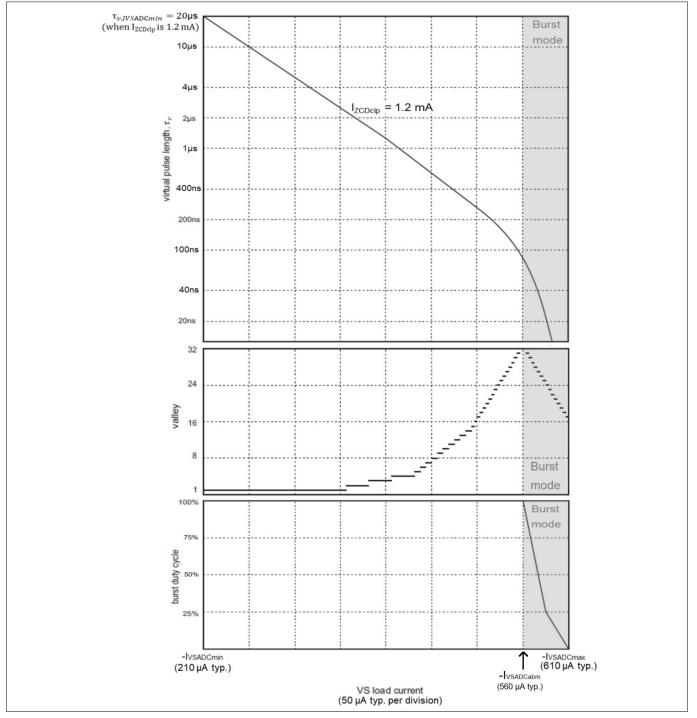

#### Figure 11 Effect of I<sub>ZCDclp</sub> change on the virtual pulse length mapping

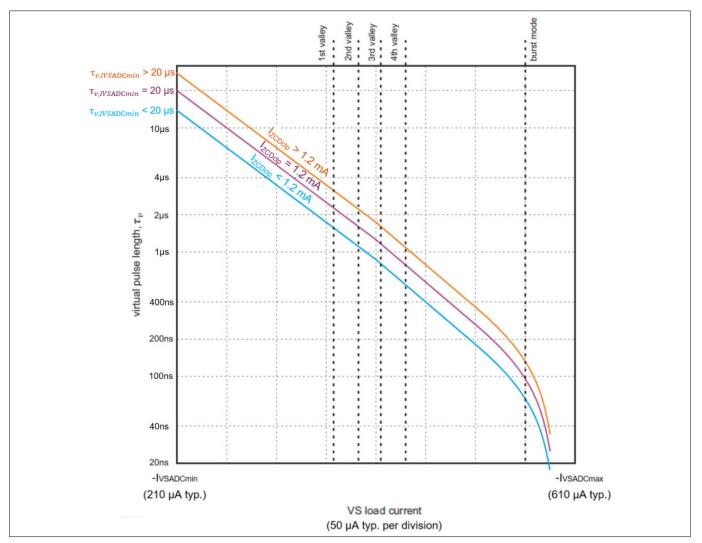

As an example, the virtual pulse length mapping based on  $I_{ZCDclp} = 1.2$  mA in Figure 11 is derived based on the following steps:

- **1.** Based on  $I_{\text{ZCDclp}}$  = 1.2 mA, obtain  $\tau_{v,\text{IVSADCmin}}$  = 20 µs from Figure 12.

- 2. Mark  $\tau_{v,IVSADCmin} = 20 \ \mu s$  on the y-axis, and take it as the starting point for the virtual pulse length mapping curve plot, which is relatively well exponential in the range from 20  $\mu s$  to 1  $\mu s$ , with a halving of the pulse length per 50  $\mu A VS$  pin load current increase.

For example, another practical use case of the virtual pulse length mapping is to estimate the minimum on-time of the QRM 1<sup>st</sup> valley switching (approximately 10% of  $\tau_{v,IVSADCmin}$ ), to estimate the system maximum switching frequency.

# Note: When the valley number is higher than 1 in QRM, or when in burst mode, the virtual pulse length mapping value should not be taken directly as the estimated on-time, since it excludes the on-time compensation effect for valley number change.

# Figure 12 Virtual pulse length at I<sub>VSADCmin</sub>, τ<sub>v,IVSADCmin</sub> versus ZCD peak to peak settled clamping current, I<sub>ZCDclp</sub>

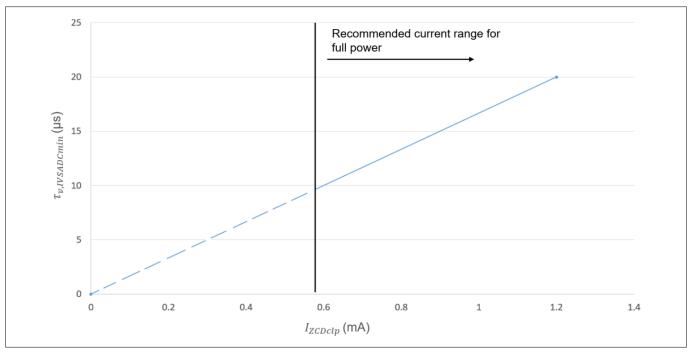

#### Power-limitation and maximum on-time

The ICC80QSG power limitation features limit the maximum on-time  $t_{ON,max}$  based on:

$$t_{ON,\max} \approx \tau_{v,IVSADC\min} \cdot \min\left[1, \frac{1}{2^{3.058 \cdot \ln\left(\frac{V_{VIN,avg}}{0.4}\right) - 1.25}}\right]$$

#### **Equation 5**

For  $t_{ON,max}$  estimation, it is important to note that  $\tau_{v,IVSADCmin}$  changes with different  $V_{VIN,avg}$  level, when the input voltage detection circuit in Figure 5 is applied. This is because  $\tau_{v,IVSADCmin}$  is scaled depending on  $I_{ZCDclp}$  in Figure 12, while  $I_{ZCDclp}$  is dependent on the input voltage, as explained in ZCD pin signal sensing.

t<sub>ON,max</sub> is applied when the VS pin load current is I<sub>VSton,sat</sub> or lower, where I<sub>VSton,sat</sub> can be estimated based on:

$$-I_{VSton, sat} \approx -I_{VSADCmin} + \max\left[0, \ 152.9 \cdot \ln\left(\frac{V_{VIN, avg}}{0.4}\right) - 62.5\right] \cdot 10^{-6}$$

#### **Equation 6**

Figure 13 shows the virtual pulse length with the power limiting maximum on-time effect, when V<sub>VIN,avg</sub> is 0.65 V, 1.0 V, 1.5 V and 1.9 V, respectively.

## **3 Functional description**

When  $V_{\text{VIN,avg}}$  is at the brownin level ( $V_{\text{BI}} = 0.647 \text{ V typ.}$ ), the power limitation is enabled with  $t_{\text{ON,max}} = \text{approx}$ . 85% of  $\tau_{\text{V,IVSADCmin}}$ , as shown in Figure 13. For example, if the desired  $t_{\text{ON,max}}$  at brownin level is 17 µs typ., it is necessary to have  $\tau_{\text{V,IVSADCmin}} = 17 \text{ µs} / 85\% = 20 \text{ µs}$ . And, according to Figure 12,  $\tau_{\text{V,IVSADCmin}} = 20 \text{ µs}$  is obtained when  $I_{\text{ZCDclp}} = 1.2 \text{ mA}$  is applied. As a result, to achieve  $t_{\text{ON,max}} = 17 \text{ us typ.}$  at brownin level,  $R_{\text{ZCD}}$  should be dimensioned to produce  $I_{\text{ZCDclp}} = 1.2 \text{ mA}$  typ. at brownin level.

## Valley number and burst duty cycle

The valley number and burst duty cycle mappings based on VS pin load current are shown in Figure 10. The burst duty cycle refers to the ratio of the burst pulsing duration to burst cycle time.  $-I_{VSADCabm}$  (560  $\mu$ A typ.) marks the boundary between QRM and burst mode.

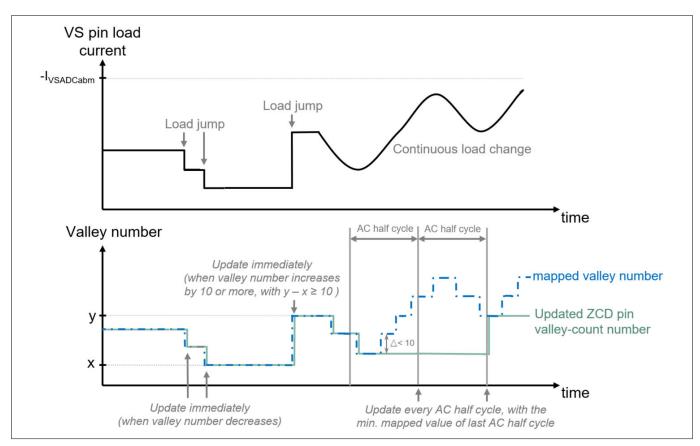

In QRM, the mapped valley number is not necessarily taken directly or immediately as the *ZCD* pin valley-count number, for the pulse generation. The update of the *ZCD* pin valley-count number is done based on the following valley selection hysteresis mechanism:

- 1. To minimize the multiple valley changes within one AC half cycle, ICC80QSG updates the *ZCD* valleycount number once every AC half cycle, based on the lowest mapped valley number from the last AC half cycle, as shown in Figure 14. During each AC half cycle, the controller adjusts the on-time to stay in the selected valley number. In this way, the number of valley jumps is limited to a minimum.

- 2. When a load jump happens, if the valley number has to be decreased, it happens immediately. For the case of valley number increase, if the load jump results to a valley number increase by 10 or more, it happens immediately. Otherwise, the change happens only at the start of the next AC half cycle, as shown in Figure 14.

#### **3 Functional description**

Note: If the selected ZCD valley-count number cannot happen before the maximum off-time t<sub>off</sub> (47 µs typ.) is reached, the pulse generation will be based on t<sub>off</sub>, instead of the selected ZCD valley counting number.

#### Figure 14 Illustrative example of the QRM valley selection hysteresis mechanism

Note: If the AC half cycle period cannot be synced, for example when the input voltage is DC, or when the VS pin load current ripple is very small, the regular valley update cycle will be based on either approximately 10 ms, or the last synced AC half cycle period.

In burst mode, the controller measures the VS load current at a regular wake-up interval, and applies the mapped valley number immediately as the ZCD pin valley-count number for the burst switching pulse generation. Also, the mapped burst duty cycle is taken immediately to determine the burst pulsing duration, as shown in Figure 9. If the measured VS load current is -/<sub>VSADCmin</sub> (610 µs typ.) or more, the burst pulsing is skipped.

Instead of waking up based on the regular interval, a higher priority VCC wake-up threshold can trigger a burst start if  $V_{VCC}$  drops to  $V_{VCCwake}$  (7.6 V typ.). In case of VCC wake-up burst being triggered, the burst pulsing duration depends on the time needed to charge the  $V_{VCC}$  from  $V_{VCCwake}$  to  $V_{VCCburst}$  (8.1 V typ.).

Attention: The VCC wake-up burst control mechanism is intended to work with the VCC voltage supply via the ZCD winding. In case of the VCC voltage is supplied via a winding voltage, which follows a certain ratio of the primary bus voltage, it is a must to ensure that the VCC voltage during burst mode is always higher than V<sub>VCCburst</sub> maximum value (9.1 V maximum) by a sufficient margin, especially when the input voltage is low and close to brownout level, so that the VCC wake-up burst mechanism can be avoided, to achieve a good output regulation.

#### Burst mode regular wake-up interval and burst cycle time

Refer to the burst mode section in the Operating modes chapter.

## **3.9 Primary side overcurrent protection**

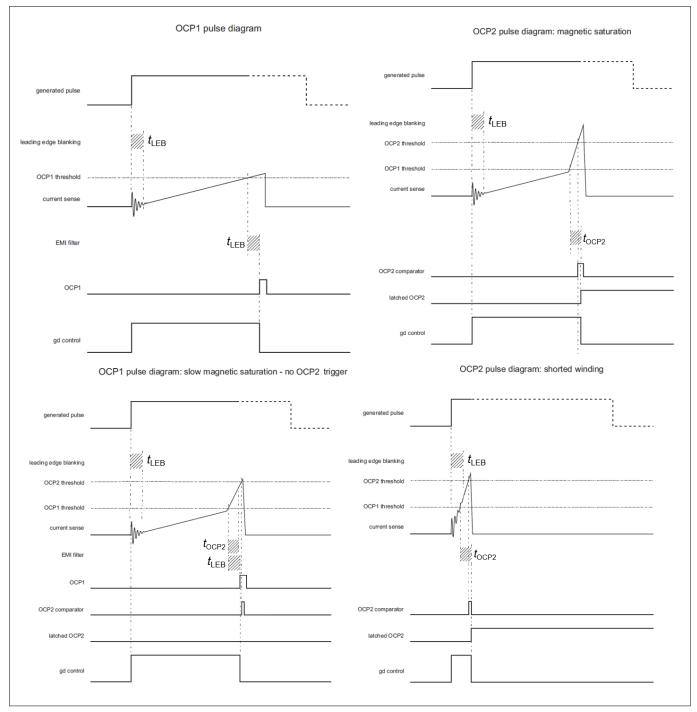

The primary side overcurrent protection level 1 (OCP1) is performed by means of the cycle-by-cycle peak current limitation. An internal leading edge blanking  $t_{LEB}$  (160 ns typ.) prevents false triggering of this protection due to a leading edge spike. If the measured *CS* pin voltage exceeds  $V_{OCP1}$  (0.61 V typ.) for more than  $t_{LEB}$  (160 ns typ.), the protection is triggered and the *GD* pin output is pulled low for that switching cycle. The primary side overcurrent protection level 2 (OCP2) is meant for covering fault conditions like a short in the transformer primary winding or transformer core saturation. In this case, the OCP1 does not limit properly the peak current due to the very steep slope of the peak current. If the measured *CS* pin voltage with an initial level of at least  $V_{OCP1}$  reaches  $V_{OCP2}$  (1.21 V typ.) or more within the time window of  $t_{OCP2}$  (150 ns typ.), the OCP2 protection is triggered.

Figure 15

#### Timing overview of the OCP1 and OCP2

## 3.10 VCC voltage protections

An UVLO is implemented to activate and deactivate the controller depending on the supply voltage on the VCC pin. The UVLO contains a hysteresis with the voltage thresholds  $V_{VCCon}$  (12.5 V typ.) for activating the controller and  $V_{VCCmin}$  (6.6 V typ.) for deactivating the controller.

When the controller is not active, the current consumption is  $I_{VCCstart}$  (30  $\mu$ A typ.).

If the voltage on VCC pin reaches  $V_{VCCclamp}$  (24.2 V typ.) during start-up, restart and in the burst pause, the controller is able to sink up to  $I_{VCCclamp}$  (2.5 mA typ.). The VCC overvoltage protection is implemented based on a threshold of  $V_{VCCmax}$  (25 V typ.).

#### VCC wake-up burst

To maintain sufficient V<sub>VCC</sub> in burst mode, the controller operates with the following two mechanisms:

- The VCC wake-up threshold can trigger a burst start if  $V_{VCC}$  drops to  $V_{VCCwake}$  (7.6 V typ.). The controller continues the burst pulsing until  $V_{VCC} = V_{VCCburst}$  (8.1 V typ.).

- The *TD* pin internal pull-up resistor is disabled when *V*<sub>VCC</sub> drops to *V*<sub>VCCwake</sub>, to allow an external start-up circuit to charge *V*<sub>VCC</sub> to *V*<sub>VCCburst</sub>.

- Attention: The VCC wake-up burst control mechanism is intended to work with the VCC voltage supply via the ZCD winding. In case of the VCC voltage is supplied via a winding voltage, which follows a certain ratio of the primary bus voltage, it is a must to ensure that the VCC voltage during burst mode is always higher than V<sub>VCCburst</sub> maximum value (9.1 V maximum) by a sufficient margin, especially when the input voltage is low and close to brownout level, so that the VCC wake-up burst mechanism can be avoided, to achieve a good output regulation.

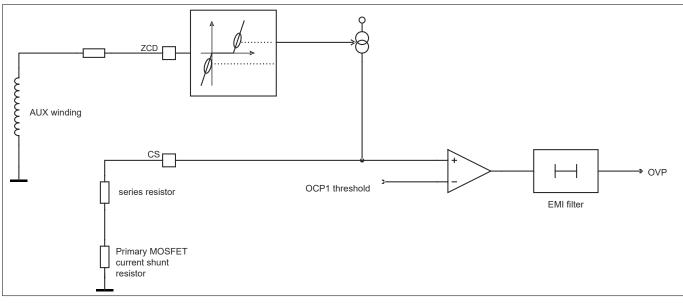

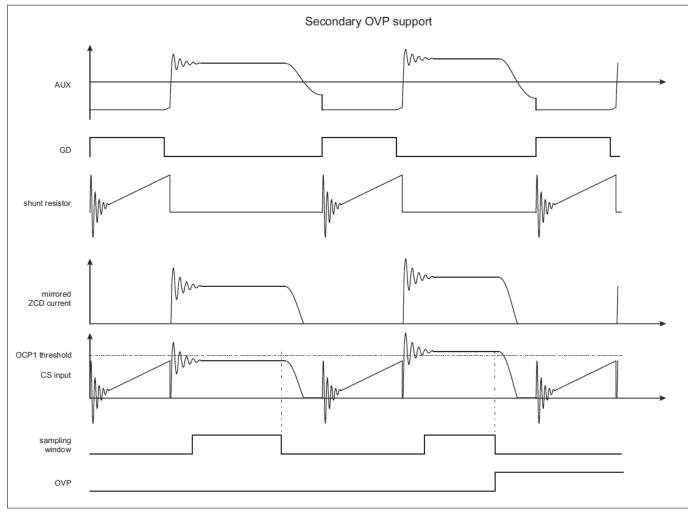

## 3.11 Flyback output overvoltage protection

During the transformer demagnetization time, the ZCD pin positive peak settled current  $I_{ZCDpclp}$  is internally converted to a current flowing out of the CS pin with the conversion ratio  $n_{ZCDOVP}$ . The CS pin voltage level at this time is therefore approximately the multiplication of this out-flowing current and the CS pin resistance to ground. If this voltage level exceeds the  $V_{OCP1}$  threshold (0.61 V typ.) for more than a blanking time, the flyback OVP is triggered.

Since the CS pin series resistor value is very much greater than the primary MOSFET current shunt resistor value, the flyback output OVP level can be adjusted based on the CS pin series resistance.

Figure 16

Flyback secondary output OVP

Due to this protection, the voltage on CS pin is not zero during the transformer demagnetization, but mirrors the reflected output voltage.

#### Figure 17 Flyback CS waveform

## **3.12 Overtemperature protection**

ICC80QSG offers an overtemperature protection using an internal temperature sensor. The overtemperature protection is triggered when internal junction temperature  $T_i$  reaches T (130°C typ.).

## 3.13 Open loop protection

An open feedback loop results in maximum power transfer after the soft start. The flyback output overvoltage protection can be triggered once the overvoltage threshold is exceeded for longer than the related blanking time. This causes an auto-restart.

In the case of an open VS pin, due to the VS pin sourcing a current of  $-I_{VSBias}$  (1 µA typ.) out of the controller during normal operation, the VS pin voltage rises. The VS pin voltage is compared to the overvoltage comparator threshold  $V_{VSOVOFFFB}$  (2.7 V typ.). If the voltage exceeds the threshold for longer than the related blanking time, the VS pin overvoltage protection blocks any switching. A reset may occur if the VCC voltage drops below  $V_{VCCmin}$ .

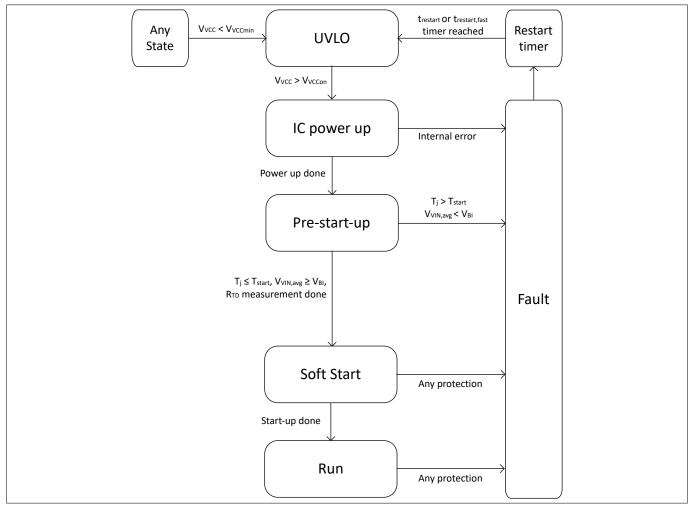

## 3.14 State flow chart and fault reaction

#### Flow chart

The Figure 18 shows the different states of the IC and the conditions to change the state.

#### Figure 18 State flow chart

#### **Fault reaction**

The controller handles protections as listed in Table 2.

*Note:* Some blanking times vary slightly with the line frequency.

## **3 Functional description**

| Table 2 | Fault matrix |

|---------|--------------|

|         | I GOLCHIGCHA |

| Fault                                    | Detection                                                  | Typical           | State                |               |     | Reaction                                                                    |

|------------------------------------------|------------------------------------------------------------|-------------------|----------------------|---------------|-----|-----------------------------------------------------------------------------|

|                                          |                                                            | blanking<br>time  | Pre-<br>start-<br>up | Soft<br>start | Run |                                                                             |

| Insufficient supply                      | V <sub>VCC</sub> < V <sub>VCCon</sub>                      | 1 µs              | Х                    | -             | -   | Wait in reset                                                               |

| Insufficient supply                      | V <sub>VCC</sub> < V <sub>VCCmin</sub>                     | 1 µs              | Х                    | Х             | Х   | Reset                                                                       |

| VCC overvoltage                          | $V_{\rm VCC} > V_{\rm VCCOVP}$                             | 1 µs              | -                    | Х             | Х   | Auto-restart after t <sub>restart</sub>                                     |

| VIN short protection                     | V <sub>VIN</sub> < V <sub>VINshort</sub>                   | 1 µs              | -                    | Х             | Х   | Auto-restart after t <sub>restart</sub>                                     |

| Brownin protection                       | V <sub>VIN,avg</sub> < V <sub>BI</sub>                     | 2 ms              | Х                    | -             | -   | Fast auto-restart after<br>t <sub>restart,fast</sub>                        |

| Brownout protection                      | $V_{\rm VIN,avg} < (V_{\rm BI} - \Delta V_{\rm BI-BO})$    | 2 ms              | -                    | X             | x   | Auto-restart after t <sub>restart</sub>                                     |

| VIN overvoltage protection               | V <sub>VIN,avg</sub> > V <sub>VINOV</sub>                  | 2 ms              | -                    | X             | x   | Auto-restart after t <sub>restart</sub>                                     |

| Overcurrent protection<br>(OCP1)         | V <sub>CS</sub> > V <sub>OCP1</sub>                        | t <sub>LEB</sub>  | -                    | Х             | X   | Turn off gate driver for<br>the on-going switching<br>cycle                 |

| Overcurrent protection (OCP2)            | V <sub>CS</sub> > V <sub>OCP2</sub>                        | t <sub>OCP2</sub> | -                    | X             | X   | Auto-restart after t <sub>restart</sub>                                     |

| Flyback output<br>overvoltage protection | $I_{\text{ZCDpclp}} * n_{\text{ZCDOVP}} > V_{\text{OCP1}}$ | 100 µs            | -                    | X             | X   | Auto-restart after t <sub>restart</sub>                                     |

| Overtemperature                          | T <sub>j</sub> > T or T <sub>j</sub> > T <sub>start</sub>  | 18 µs             | Х                    | Х             | Х   | Auto-restart after t <sub>restart</sub>                                     |

| <i>VS</i> overvoltage                    | V <sub>VS</sub> > V <sub>VSOVOFFFB</sub>                   | 20 µs             | -                    | X             | X   | Turn off gate driver and restart if V <sub>VS</sub> < V <sub>VSOVONFB</sub> |

## 3.15 Adjustable functions

Some features of the controller can be adjusted using external circuitry:

- The maximum power/on-time/operating point can be configured using the ZCD pin series resistance to the ZCD/auxiliary winding

- The flyback output overvoltage protection can be configured using the CS pin series resistance to the primary MOSFET current shunt resistor.

- Brownin and brownout protection and the related input overvoltage protection

- Primary side overcurrent protection

All signals are measured with respect to the ground pin, *GND*. The voltage levels are valid provided that other ratings are not violated.

## 4.1 Absolute maximum ratings

Note: Absolute maximum ratings are defined as ratings, which if exceeded may lead to destruction of the integrated circuit. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit. These values are not tested during production test.

| Parameter                              | Symbol            |      | Values |                        | Unit | Note or test condition                                  |

|----------------------------------------|-------------------|------|--------|------------------------|------|---------------------------------------------------------|

|                                        |                   | Min. | Тур.   | Max.                   |      |                                                         |

| VCC voltage                            | V <sub>VCC</sub>  | -0.5 | -      | 26                     | V    |                                                         |

| Junction temperature                   | Tj                | -40  | _      | 150                    | °C   |                                                         |

| Storage temperature                    | T <sub>S</sub>    | -55  | _      | 150                    | °C   |                                                         |

| Soldering temperature                  | T <sub>S</sub>    | -    | -      | 260                    | °C   | Wave soldering<br>according to<br>JESD22-A111 Rev<br>A. |

| Thermal resistance junction to ambient | R <sub>ThJA</sub> | -    | -      | 185                    | K/W  |                                                         |

| Power dissipation at 50°C              | PD                | _    | _      | 0.5                    | W    |                                                         |

| ESD capability HBM                     | V <sub>ESD</sub>  | -    | -      | 2                      | kV   | ESD-HBM<br>according to ANSI/<br>ESDA/JEDEC<br>JS-001.  |

| ESD capability CDM                     | V <sub>ESD</sub>  | -    | -      | 500                    | V    | ESD-CDM<br>according to ANSI/<br>ESDA/JEDEC<br>JS-002.  |

| GD voltage                             | V <sub>GD</sub>   | -0.5 | -      | V <sub>VCC</sub> + 0.3 | V    |                                                         |

| CS voltage                             | V <sub>CS</sub>   | -0.5 | -      | 3.6                    | V    |                                                         |

| <i>CS</i> current                      | I <sub>CS</sub>   | -2   | _      | 2                      | mA   |                                                         |

| ZCD voltage                            | V <sub>ZCD</sub>  | -1.2 | _      | 3.6                    | V    |                                                         |

| ZCD current                            | I <sub>ZCD</sub>  | -4   | _      | 4                      | mA   |                                                         |

| <i>VS</i> voltage                      | V <sub>VS</sub>   | -0.3 | -      | 3.6                    | V    |                                                         |

| VIN voltage                            | V <sub>VIN</sub>  | -0.3 | -      | 3.6                    | V    |                                                         |

| TD voltage                             | V <sub>TD</sub>   | -0.3 | -      | 3.6                    | V    |                                                         |

## Table 3 Absolute maximum ratings

## 4.2 **Operating conditions**

The recommended operating conditions are shown for which the DC electrical characteristics are valid.

| Parameter                                     | Symbol              |                       | Values |      | Unit | Note or test                                                       |

|-----------------------------------------------|---------------------|-----------------------|--------|------|------|--------------------------------------------------------------------|

|                                               |                     | Min.                  | Тур.   | Max. |      | condition                                                          |

| Junction temperature                          | TJ                  | -40                   | -      | Т    | °C   |                                                                    |

| Supply voltage                                | V <sub>VCC</sub>    | V <sub>VCCburst</sub> | -      | 23   | V    |                                                                    |

| External capacitance at the <i>TD</i> pin     | C <sub>TD</sub>     | -                     | _      | 1    | nF   |                                                                    |

| ZCD pin peak to peak settled clamping current | / <sub>ZCDclp</sub> | -                     | -      | 1.4  | mA   | For V <sub>VIN</sub> = V <sub>BI</sub> after<br>internal averaging |

## Table 4Operating characteristics

## 4.3 DC electrical characteristics

The electrical characteristics provide the spread of values applicable within the specified supply voltage and junction temperature range. Devices are tested in production at  $T_A = 25^{\circ}$ C. Values have been verified either with simulation models or by device characterization up to 125°C. Typical values represent the median values related to  $T_A = 25^{\circ}$ C.

All voltages refer to GND, and the assumed supply voltage is  $V_{VCC}$  = 15 V, if not otherwise specified.

## 4.3.1 Power supply

#### Table 5 Power supply characteristics

| Parameter                                                         | Symbol                 |      | Values |      | Unit | Note or test condition                        |

|-------------------------------------------------------------------|------------------------|------|--------|------|------|-----------------------------------------------|

|                                                                   |                        | Min. | Тур.   | Max. |      |                                               |

| VCC turn-on threshold                                             | V <sub>VCCon</sub>     | 12.0 | 12.5   | 13.1 | V    |                                               |

| Start-up current                                                  | I <sub>VCCstart</sub>  | -    | 30     | -    | μA   |                                               |

| Supply current                                                    | I <sub>CC</sub>        | -    | 2.0    | -    | mA   | IC self-supply<br>excluding gate<br>currents. |

| Supply current during burst pause                                 | I <sub>CCburst</sub>   | -    | 220    | -    | μA   |                                               |

| Supply current in protection mode                                 | I <sub>CCrestart</sub> | -    | 40     | -    | μA   |                                               |

| VCC undervoltage threshold                                        | V <sub>VCCmin</sub>    | 6.0  | 6.6    | 7.6  | V    |                                               |

| VCC wake-up threshold                                             | V <sub>VCCwake</sub>   | 6.6  | 7.6    | 8.8  | V    |                                               |

| VCC burst threshold                                               | V <sub>VCCburst</sub>  | 7.1  | 8.1    | 9.1  | V    |                                               |

| Difference between V <sub>VCCwake</sub> and V <sub>Vccburst</sub> | V <sub>delta</sub>     | 500  | _      | -    | mV   |                                               |

| VCC overvoltage threshold                                         | V <sub>VCCmax</sub>    | 23.8 | 25     | 26.4 | V    |                                               |

| VCC clamp voltage                                                 | V <sub>VCCclamp</sub>  | -    | 24.2   | -    | V    |                                               |

| VCC clamp current                                                 | I <sub>VCCclamp</sub>  | -    | 2.5    | -    | mA   |                                               |

## 4.3.2 Zero crossing detection

#### Table 6Electrical characteristics

| Parameter                                              | Symbol               |       | Values |       | Unit | Note or test                                              |

|--------------------------------------------------------|----------------------|-------|--------|-------|------|-----------------------------------------------------------|

|                                                        |                      | Min.  | Тур.   | Max.  |      | condition                                                 |

| Zero crossing threshold (falling edge)                 | V <sub>ZCDDown</sub> | 10    | 45     | _     | mV   |                                                           |

| Zero crossing threshold (rising edge)                  | V <sub>ZCDUp</sub>   | -     | 55     | 90    | mV   |                                                           |

| Clamping of positive voltages                          | V <sub>ZCDpclp</sub> | 400   | 550    | 700   | mV   | I <sub>ZCDSink</sub> = 1 mA                               |

| Clamping of negative voltages                          | V <sub>ZCDnclp</sub> | -600  | -500   | -400  | mV   | I <sub>ZCDSource</sub> = - 1 mA                           |

| ZCD ringing suppression time                           | t <sub>Ringsup</sub> | 350   | 700    | 1100  | ns   |                                                           |

| ZCD to CS current ratio for flyback secondary side OVP | n <sub>ZCDOVP</sub>  | 0.455 | 0.484  | 0.513 |      | I <sub>CSsource</sub> / I <sub>ZCDpclp</sub><br>at 1.2 mA |

| ZCD to CS current ratio for flyback secondary side OVP | n <sub>ZCDOVP</sub>  | 0.450 | 0.484  | 0.518 |      | I <sub>CSsource</sub> / I <sub>ZCDpclp</sub><br>at 0.8 mA |

## 4.3.3 Voltage sense

*Note:* R<sub>TD</sub> *limits from* Table 9 *apply for* Table 7.

## Table 7 Electrical characteristics

| Parameter                                          | Symbol                  |      | Values |      |    | Note or test condition                |

|----------------------------------------------------|-------------------------|------|--------|------|----|---------------------------------------|

|                                                    |                         | Min. | Тур.   | Max. |    |                                       |

| VS bias current                                    | - I <sub>VSBias</sub>   | 0.5  | 1.0    | 1.5  | μA | $V_{\rm VS} = V_{\rm ref}.$           |

| Voltage source for optocoupler/<br>feedback supply | V <sub>VS</sub>         | 1.56 | 1.6    | 1.63 | V  | Internal series resistance of 500 Ω.  |

| VS current threshold for start up                  | - I <sub>VSsink</sub>   | 102  | 130    | 154  | μA | $12 \text{ k}\Omega$ from VS to GND.  |

| Open pin turn-off                                  | V <sub>VSOVOFFFB</sub>  | 2.64 | 2.7    | 2.76 | V  |                                       |

| Voltage for restart after overvoltage turn-off     | V <sub>VSOVONFB</sub>   | 2.54 | 2.6    | 2.66 | V  |                                       |

| ADC lower current limit                            | - I <sub>VSADCmin</sub> | 166  | 210    | 260  | μA | For maximum on-time during operation. |

| ADC upper current limit                            | - I <sub>VSADCmax</sub> | 500  | 610    | 720  | μA | For minimum on-time in burst mode.    |

## 4.3.4 Input voltage detection

#### Table 8Electrical characteristics

| Parameter                          | neter Symbol Values |      |      |      | Unit | Note or test condition                                                           |

|------------------------------------|---------------------|------|------|------|------|----------------------------------------------------------------------------------|

|                                    |                     | Min. | Тур. | Max. |      |                                                                                  |

| Hysteresis of brownin and brownout | ∆V <sub>BI-BO</sub> | -    | 16   | -    | mV   | RUN state and not<br>in burst mode. DC<br>threshold after internal<br>averaging. |

## 4 Electrical characteristics and parameters

## Table 8 (continued) Electrical characteristics

| Parameter                      | Symbol                |       | Values |       | Unit | Note or test condition                 |

|--------------------------------|-----------------------|-------|--------|-------|------|----------------------------------------|

|                                |                       | Min.  | Тур.   | Max.  |      |                                        |

| Brownin voltage level          | V <sub>BI</sub>       | 0.617 | 0.647  | 0.677 | V    | DC threshold after internal averaging. |

| VIN pin short to GND threshold | V <sub>VINshort</sub> | 150   | 200    | 250   | mV   |                                        |

| VIN overvoltage threshold      | V <sub>VINOV</sub>    | 1.9   | 2.0    | 2.1   | V    |                                        |

## 4.3.5 TD configuration

#### Table 9Electrical characteristics

| Parameter                                                                                                                               | Symbol                  |      | Values |      |    | Note or test condition                                                                                                                                                                                                                                 |  |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|--------|------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                         |                         | Min. | Тур.   | Max. | _  |                                                                                                                                                                                                                                                        |  |

| Internal pull-up resistor for pre-start-up <i>R</i> <sub>TD</sub> measurement                                                           | R <sub>TD,flyback</sub> | 32   | 40     | 48   | kΩ | Internal voltage 3.3 V.                                                                                                                                                                                                                                |  |

| Internal pull-up resistor for RUN state and pre-start-up <i>R</i> <sub>TD</sub> measurement                                             | R <sub>TD,RUN</sub>     | 8    | 10     | 12   | kΩ | Internal voltage 3.3<br>V. Pull-up is disabled<br>in burst mode if VCC<br>wake-up is triggered<br>from V <sub>VCC</sub> ≤ V <sub>VCCwake</sub> ,<br>until V <sub>VCC</sub> reaches<br>V <sub>VCCburst</sub> .                                          |  |

| <i>TD</i> pin resistance to ground, for TD<br>configuration and to activate <i>VS</i> pin load<br>current sensing for output regulation | R <sub>TD</sub>         | 27   | -      | 68   | kΩ | Internal voltage 3.3 V.<br>Minimum value based<br>on Internal pull-up<br>resistor of <i>R</i> <sub>TD,RUN</sub> .<br>Maximum value based<br>on internal pull-up<br>resistor of <i>R</i> <sub>TD,flyback</sub> .<br>Measured in pre-start-<br>up phase. |  |

## 4.3.6 Current sense

#### Table 10Electrical characteristics

| Parameter                       | Symbol             | Values |      |      | Unit | Note or test                                            |

|---------------------------------|--------------------|--------|------|------|------|---------------------------------------------------------|

|                                 |                    | Min.   | Тур. | Max. |      | condition                                               |

| OCP1 turn-off threshold         | V <sub>OCP1</sub>  | 570    | 610  | 650  | mV   |                                                         |

| OCP1 leading-edge blanking time | t <sub>LEB</sub>   | _      | 160  | _    | ns   |                                                         |

| OCP2 turn-off threshold         | V <sub>OCP2</sub>  | 1140   | 1210 | 1260 | mV   |                                                         |

| OCP2 trigger time               | t <sub>OCP2</sub>  | -      | 150  | -    | ns   | Pulse width when<br>V <sub>CS</sub> > V <sub>OCP2</sub> |

| CS pull-up current              | -I <sub>CSPU</sub> | 0.5    | 1    | 1.5  | μA   |                                                         |

## 4.3.7 PWM generation

#### Table 11Electrical characteristics

| Parameter       | Symbol              | Values |      |      | Unit | Note or test                                                                                                |

|-----------------|---------------------|--------|------|------|------|-------------------------------------------------------------------------------------------------------------|

|                 |                     | Min.   | Тур. | Max. |      | condition                                                                                                   |

| Maximal on-time | t <sub>ON_max</sub> | -      | 20   | -    | μs   | For I <sub>ZCDclp</sub> = 1.4<br>mA, and V <sub>VIN</sub> = V <sub>BI</sub><br>after internal<br>averaging. |

| Repetition time | t <sub>Rep</sub>    | 47     | 52   | 60   | μs   | $V_{\rm ZCD} = 0 V$                                                                                         |

| Off-time        | t <sub>Off</sub>    | 42     | 47   | 52.5 | μs   |                                                                                                             |

## 4.3.8 Gate driver

#### Table 12Electrical characteristics

| Parameter               | Symbol               | Symbol Values |      |      |    | Note or test                                                                          |

|-------------------------|----------------------|---------------|------|------|----|---------------------------------------------------------------------------------------|

|                         |                      | Min.          | Тур. | Max. |    | condition                                                                             |

| GD source current       | -I <sub>source</sub> | 125           | _    | -    | mA |                                                                                       |

| GD sink current         | I <sub>sink</sub>    | 250           | _    | -    | mA |                                                                                       |

| <i>GD</i> peak voltage  | V <sub>GDfull</sub>  | 10.4          | 11.0 | 11.6 | V  | $V_{VCC} > (V_{GDfull} + 0.5 V)$<br>and in QRM.                                       |

| Reduced GD peak voltage | V <sub>GDred</sub>   | 6.5           | 7.0  | 7.5  | V  | V <sub>VCC</sub> > (V <sub>GDred</sub> + 0.7<br>V), during start-up or<br>burst mode. |

## 4.3.9 Clock oscillators

#### Table 13Electrical characteristics

| Parameter         | Symbol                    | Values |      |      | Unit | Note or test                                                       |

|-------------------|---------------------------|--------|------|------|------|--------------------------------------------------------------------|

|                   |                           | Min.   | Тур. | Max. |      | condition                                                          |

| Restart time      | t <sub>restart</sub>      | -      | 200  | -    | ms   |                                                                    |

| Fast restart time | t <sub>restart,fast</sub> | -      | 25   | -    | ms   | Only for <i>VIN</i> under<br>voltage (brownin<br>protection) event |

## 4.3.10 Temperature sensor

#### Table 14Electrical characteristics

| Parameter                                   | Symbol |      | Values |      |    | Note or test |

|---------------------------------------------|--------|------|--------|------|----|--------------|

|                                             |        | Min. | Тур.   | Max. |    | condition    |

| Relative accuracy of the temperature sensor | ΔΤ     | -6   | -      | +6   | °C |              |

| Shutdown temperature                        | Т      | _    | 130    | -    | °C |              |

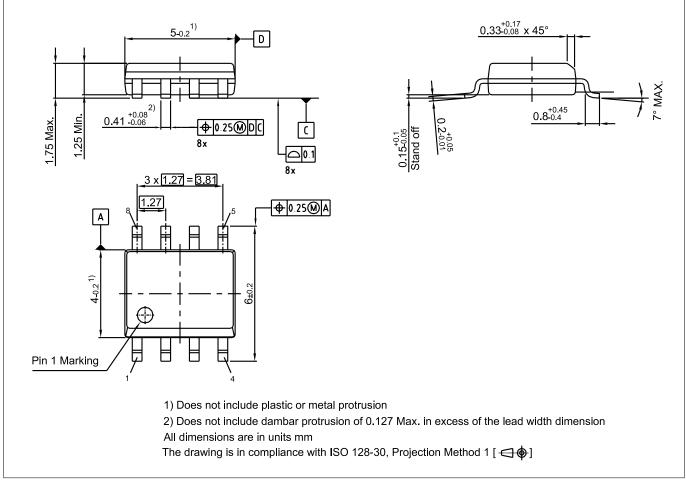

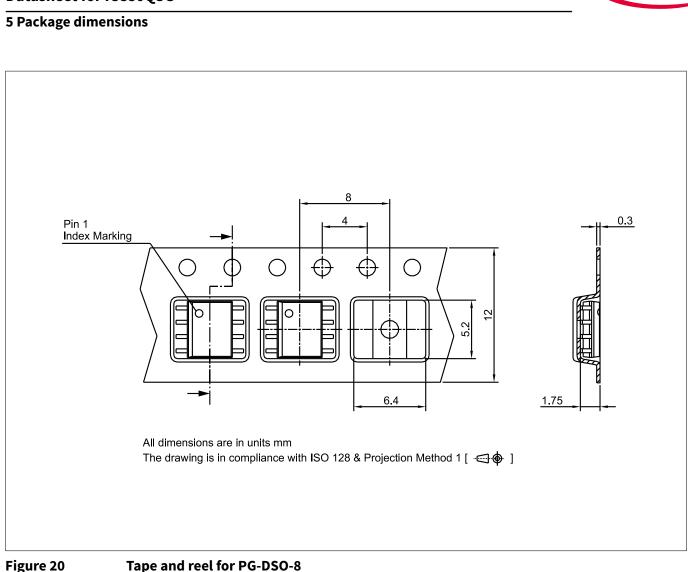

#### **5 Package dimensions**

## 5 Package dimensions

The package dimensions of PG-DSO-8 are provided.

Figure 19

#### Package dimensions for PG-DSO-8

*Note:* You can find all of our packages, packing types and other package information on our Infineon Internet page "Products": http://www.infineon.com/products.

#### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pbfree finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020). Further information on packages: https://www.infineon.com/packages

ineon

6 Glossary

6 Glossary

| AC   | Alternating current           |

|------|-------------------------------|

| ADC  | Analog-to-digital converter   |

| BM   | Burst mode                    |

| CV   | Constant voltage              |

| ССМ  | Continuous conduction mode    |

| DC   | Direct current                |

| DCM  | Discontinuous conduction mode |

| EMI  | Electromagnetic interference  |

| ESD  | Electrostatic discharge       |

| ОСР  | Overcurrent protection        |

| ОТР  | Overtemperature protection    |

| OVP  | Overvoltage protection        |

| QR   | Quasi-resonant                |

| QRM  | Quasi-resonant mode           |

| SSR  | Secondary side regulation     |

| UVLO | Under voltage lockout unit    |

|      |                               |

7 Revision history

## 7 Revision history

| Revision | Date       | Changes         |

|----------|------------|-----------------|

| 1.0      | 2022-05-04 | Initial release |

|          |            |                 |

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2022-05-04 Published by Infineon Technologies AG 81726 Munich, Germany

© 2022 Infineon Technologies AG All Rights Reserved.

Do you have a question about any aspect of this document? Email: erratum@infineon.com

Document reference IFX-fwe1638193296808

#### Important notice

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

#### Warnings

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Infineon: ICC80QSGXUMA1