# Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

# Continuity of document content

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

# Continuity of ordering part numbers

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

# EZ-PD<sup>™</sup> CMG1 Datasheet

# USB Type-C EMCA Controller

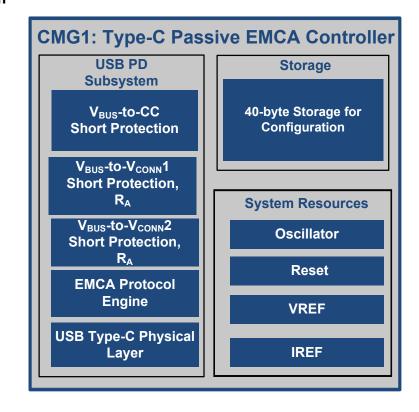

# **General Description**

EZ-PD<sup>™</sup> CMG1 is a dedicated USB Type-C EMCA controller that complies with the USB Type-C and Power Delivery (PD) standards for Electronically Marked Type-C Thunderbolt and non-Thunderbolt passive cable applications. EZ-PD CMG1 integrates a complete Type-C transceiver including the R<sub>A</sub> termination resistors on the VCONN pins and VBUS short circuit protection on both VCONN and CC pins. CMG1 also includes 40 bytes of storage for configuration of vendor-, device-, and cable-specific configuration data. EZ-PD CMG1 is targeted for passive EMCA implementations with either one or two e-marker chips on the cable.

### Features

#### **Type-C Support and USB-PD Support**

- Supports USB PD3.0 spec and USB Type-C spec version 1.3 (Including support for the revised minimum VCONN operating voltage of 3 V)

- Integrated high-voltage protection on CC, VCONN1, and VCONN2 pins to protect against accidental shorts to the VBUS pin on the Type-C connector

- 40-byte storage programmable over Type-C interface for storing vendor-, device-, and cable-specific configuration data

- Termination resistor R<sub>A</sub> on VCONN1 and VCONN2

- Supports R<sub>A</sub> weakening to reduce power consumption

- Supports electronically marked passive cable implementations with one or two controllers

#### **Clocks and Oscillators**

Integrated oscillator eliminating the need for external clock

#### Power

- 2.7 V to 5.5 V operation

- Sleep: 1.7 mA

#### System-Level ESD Protection

- On CC, VCONN1, and VCONN2 pins

- ±8 kV Contact Discharge and ±15 kV Air Gap Discharge based on IEC61000-4-2 level 4C

#### Package

- 9-ball WLCSP

- Supports industrial temperature range (-40 °C to +85 °C)

# Logic Block Diagram

Cypress Semiconductor Corporation Document Number: 002-20412 Rev. \*I

# Contents

| Pinouts                                    | . 3 |

|--------------------------------------------|-----|

| Power                                      | . 4 |

| CMG1 Application Configuration Update Over |     |

| CC Interface                               | . 5 |

| Application Diagrams                       | . 6 |

| Electrical Specifications                  |     |

| Absolute Maximum Ratings                   | . 8 |

| Device-Level Specifications                | . 8 |

| Ordering Information                       | 10  |

| Ordering Code Definition                   | 10  |

| Packaging                                  |     |

| Acronyms<br>Document Conventions        |    |

|-----------------------------------------|----|

| Units of Measure                        | 13 |

| Document History Page                   | 14 |

| Sales, Solutions, and Legal Information | 15 |

| Worldwide Sales and Design Support      | 15 |

| Products                                | 15 |

| PSoC® Solutions                         | 15 |

| Cypress Developer Community             | 15 |

| Technical Support                       | 15 |

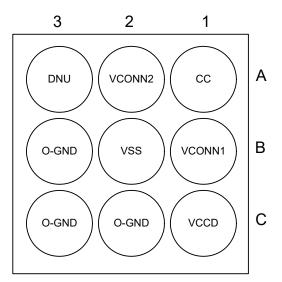

# Pinout

#### Table 1. 9-Ball CSP Pin Description

| 9-Ball CSP | Pin Name             | Description                                                                                        |

|------------|----------------------|----------------------------------------------------------------------------------------------------|

| A1         | СС                   | Communication Channel (VBUS short protected)/IEC                                                   |

| A2         | VCONN2               | VCONN2 supply with $R_A$ termination (2.7 V to 5.5 V) (VBUS Short protected)/IEC                   |

| A3         | DNU <sup>[1]</sup>   | Do not use <sup>[1]</sup>                                                                          |

| B1         | VCONN1               | VCONN1 supply with R <sub>A</sub> termination (2.7 V to 5.5 V) (VBUS Short protected)/IEC          |

| B2         | VSS                  | Ground pin. Mandatory to connect to system GND                                                     |

| В3         | O-GND <sup>[2]</sup> | Optional GND pin. This pin can be connected to the system GND for better board layout routability. |

| C1         | VCCD                 | 1.8-V Core Voltage Out. Connect to 1-µF capacitor                                                  |

| C2         | O-GND <sup>[2]</sup> | Optional GND pin. This pin can be connected to system GND for better board layout routability.     |

| C3         | O-GND <sup>[2]</sup> | Optional GND pin. This pin can be connected to system GND for better board layout routability.     |

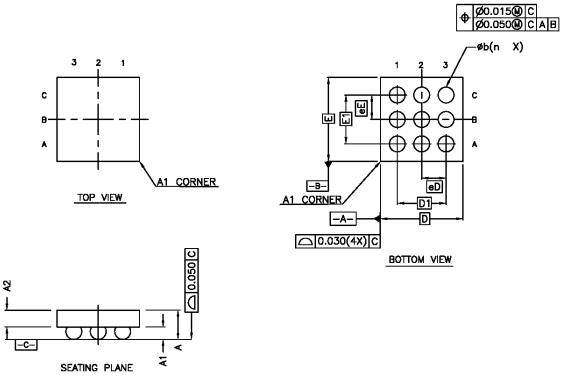

#### Figure 1. Pinout of 9-WLCSP Bottom (Balls Up) View

#### Notes

- Keep pin A3 floating for all passive EMCA applications. See Figure 4 and Figure 5 for more details.

Any of the optional GND pins B3, C2, and C3 can be connected to system GND for better board layout routability. If connected to GND, ensure that the selected pin/s are shorted with the VSS pin (B2) of the CMG1 device in their board layout. If users are not planning to connect these optional GND pins to system GND, then it is mandatory to leave them unconnected in their board designs.

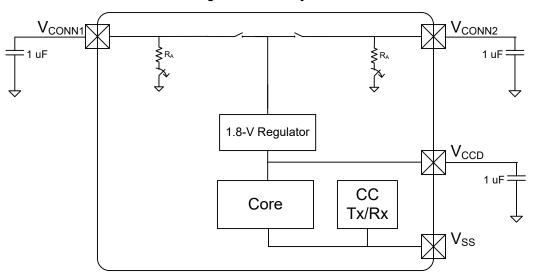

### Power

Figure 2 shows an overview of the CMG1 power system requirement. CMG1 operates from two possible external supply sources, VCONN1 and VCONN2. The VCONN supplies support operation over 2.7 V–5.5 V. CMG1 has two different power modes: Active and Sleep, transitions between which are managed by the Power System. The VCCD pin, the output of the core regulator (1.8 V), is brought out for connecting a 1- $\mu$ F capacitor for regulator stability only. This pin is not supported as a power supply.

Figure 2. Power System

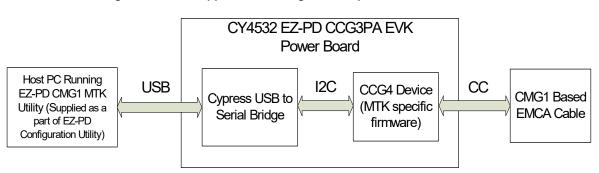

# CMG1 Application Configuration Update Over CC Interface

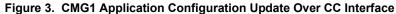

The CMG1 Manufacturing Test Kit (MTK) Utility is used for updating the configuration parameters of the CMG1 devices over the CC interface. The CMG1 MTK Utility is integrated as a part of the EZ-PD Configuration Utility and is supported by its version 1.1 Beta (or later). Vendor-specific and cable-specific parameters can be set using the EZ-PD Configuration Utility. Once the parameters are set, the CMG1 MTK Utility is used for configuration and testing of CMG1-based passive EMCA cables.

To use the CMG1 MTK Utility, you must use the CY4532 EZ-PD CCG3PA EVK as shown in a high-level block diagram in Figure 3. The CMG1 MTK Utility is accompanied with a CMG1 MTK-specific firmware solution, which is intended for the CCG4 device present on the CY4532 EZ-PD CCG3PA EVK's Power Board. If customers are using the CY4532 EZ-PD CCG3PA EVK for the first time to update the configuration parameters of CMG1 devices, then the CCG4 device's firmware needs to be updated to this MTK-specific firmware (detailed instructions are provided in Getting Started with EZ-PD CMG1 Application Note).

The EZ-PD Configuration Utility 1.1 Beta (or later), which integrates and supports the CMG1 MTK Utility, can be downloaded here. For further details, follow the instructions provided in Getting Started with EZ-PD CMG1 Application Note for hardware setup and step-by-step instructions. Also, see Chapter 4 of the EZ-PD Configuration Utility User Manual for more details on how to configure and test CMG1-based passive EMCA cables.

# **Application Diagrams**

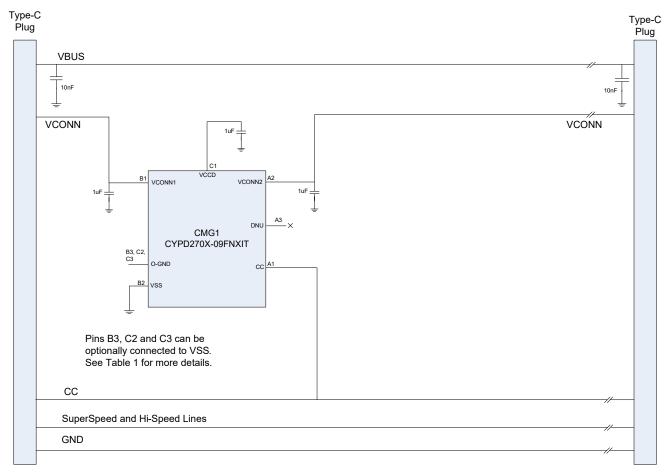

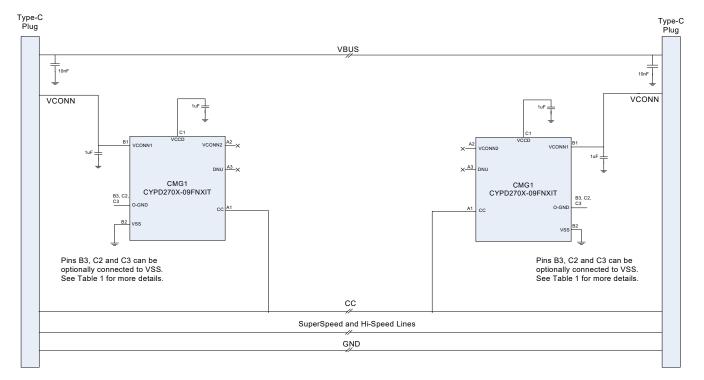

Figure 4 and Figure 5 show the application diagrams of a Passive EMCA application using CMG1 devices. Figure 4 shows the application using a single CMG1 device per cable present at one of the two plugs, whereas Figure 5 shows the same with two CMG1 devices per cable present at each plug. The VBUS signal, the SuperSpeed lines, Hi-Speed lines, and CC lines are connected directly from one end to another. The application diagram shown in Figure 4 requires a single VCONN wire to run through the cable so that the CMG1 device can be powered irrespective of which plug is connected to the host (DFP). However, in the application diagram shown in Figure 5, the VCONN signal does not run through the entire cable, but only runs to the respective VCONN pin of the CMG1 device at each end of the plug. Also, only one CMG1 device is powered at any given instance, depending on which one is nearer to the DFP that supplies VCONN.

#### Figure 4. Passive EMCA Application - Single CMG1 Chip Per Cable

#### Figure 5. Passive EMCA Application - Single CMG1 Chip Per Plug

# **Electrical Specifications**

#### **Absolute Maximum Ratings**

#### Table 2. Absolute Maximum Ratings

| Parameter               | Description                                  | Min   | Тур | Max | Units | Details/Conditions                              |

|-------------------------|----------------------------------------------|-------|-----|-----|-------|-------------------------------------------------|

| V <sub>CONN_MAX</sub>   | Max supply voltage relative to $V_{SS}$      | -     | _   | 25  | V     | Absolute max                                    |

| V <sub>CC_PIN_ABS</sub> | Max voltage on the CC pin                    | _     | _   | 25  | V     |                                                 |

| ESD_HBM                 | Electrostatic discharge human body model     | 2200  | _   | -   | V     | _                                               |

| ESD_CDM                 | Electrostatic discharge charged device model | 500   | _   | _   | V     | _                                               |

| LU                      | Pin current for latch-up                     | -140  | _   | 140 | mA    | -                                               |

| ESD_IEC_CON             | Electrostatic discharge<br>IEC61000-4-2      | 8000  | _   | _   | V     | Contact discharge on CC and $V_{CONN}$ pins     |

| ESD_IEC_AIR             | Electrostatic discharge<br>IEC61000-4-2      | 15000 | _   | _   | V     | Air discharge for CC and V <sub>CONN</sub> pins |

#### **Device-Level Specifications**

See basic specifications in the following tables. More specifications will be added in a future version of this document.

#### Table 3. DC Specifications

| Spec ID                     | Parameter                                   | Description                                                      | Min     | Тур                  | Max      | Units              | Details/Conditions                                                                            |

|-----------------------------|---------------------------------------------|------------------------------------------------------------------|---------|----------------------|----------|--------------------|-----------------------------------------------------------------------------------------------|

| SID.PWR#1                   | V <sub>CONN1</sub> or<br>V <sub>CONN2</sub> | Power supply input voltage                                       | 2.7     | -                    | 5.5      | V                  | -                                                                                             |

| SID.PWR#5                   | V <sub>CCD</sub>                            | Output voltage (for core logic)                                  | I       | 1.8                  | -        | V                  | _                                                                                             |

| SID.PWR#12                  | C <sub>EFC</sub>                            | External regulator voltage bypass on $V_{CCD}$                   | 0.8     | 1                    | 1.2      | μF                 | X5R ceramic or better                                                                         |

| SID.PWR#13                  | C <sub>VCONN</sub>                          | Power supply decoupling capacitor on $V_{CONN1}$ and $V_{CONN2}$ | 0.8     | 1                    | _        | μF                 | X5R ceramic or better                                                                         |

| Active Mode, V <sub>C</sub> | ONN1 Or V <sub>CO</sub>                     | <sub>NN2</sub> = 2.7 V to 5.5 V. Typical values                  | measur  | ed at V <sub>o</sub> | CONN1 OF | V <sub>CONN2</sub> | = 5 V                                                                                         |

| SID.PWR#8                   | I <sub>DD_A</sub>                           | Active current                                                   | _       | 5                    | 7.5      | mA                 | CC I/O in Transmit or<br>Receive                                                              |

| Sleep Mode, Typ             | ical values                                 | measured at $V_{CONN1}$ or $V_{CONN2}$ = 5                       | V and T | <sub>A</sub> = 25 °  | С        |                    |                                                                                               |

| SID25A                      | I <sub>DD_S</sub>                           | Sleep mode current                                               | _       | 1.7                  | 3.0      | mA                 | CC as wakeup source. One<br>VCONN supply is powered,<br>the other is floating or<br>grounded. |

#### Table 4. PD DC Specifications

| Spec ID   | Parameter            | Description                                                                        | Min  | Тур  | Max | Units | Details/Conditions                                                                      |

|-----------|----------------------|------------------------------------------------------------------------------------|------|------|-----|-------|-----------------------------------------------------------------------------------------|

| SID.PD.6  | R <sub>A</sub>       | Power cable termination                                                            | 0.8  | 1    | 1.2 | kΩ    | All supplies force to 0 V and 0.2 V applied at V <sub>CONN1</sub> or V <sub>CONN2</sub> |

| SID.PD.7  | R <sub>A_OFF</sub>   | Power cable termination - disabled                                                 | 0.4  | 0.75 | Ι   | MΩ    | 2.7 V applied at $V_{CONN1}$ or $V_{CONN2}$ with $R_A$ disabled                         |

| SID.PD.14 | I <sub>LEAK</sub>    | Leaker on V <sub>CONN1</sub> or V <sub>CONN2</sub> for discharge upon cable detach | 150  | -    | -   | μA    | -                                                                                       |

| SID.PD.15 | V <sub>GNDOFST</sub> | Ground offset tolerated by BMC receiver                                            | -500 | -    | 500 | mV    | Relative to remote BMC trans-<br>mitter                                                 |

| SID.PD.16 | Z <sub>OPEN_PD</sub> | Impedance of CC pin with VCONN1<br>and VCONN2 un-powered                           | 200  | -    | _   | kΩ    | 0 V ≤ CC Voltage ≤ 5.5 V                                                                |

#### Table 5. Storage Specifications

| Spec ID    | Parameter | Description         | Min | Тур | Мах | Units  | Details/Conditions                          |

|------------|-----------|---------------------|-----|-----|-----|--------|---------------------------------------------|

| SID.MEM#3  | NVL_ERASE | NVL bulk erase time | 25  | -   | 100 | ms     | –40 °C ≤ T <sub>A</sub> ≤ 85 °C             |

| SID.MEM#4  | NVL_WRITE | NVL program         | 2   | -   | 10  | ms     | $-40$ C $\leq$ 1 <sub>A</sub> $\leq$ 05 C   |

| SID.MEM#5  | NVL_DR    | NVL data retention  | 20  | -   | -   | years  | $25 \ ^\circ C \le T_A \le 55 \ ^\circ C$   |

| SID.MEM#5A | NVL_DR    | NVL data retention  | 10  | -   | -   | years  | $55 \ ^\circ C \le T_A \le 85 \ ^\circ C$   |

| SID.MEM#6  | NVL_ENPB  | NVL write endurance | 100 | -   | -   | cycles | $25 \text{ °C} \leq T_A \leq 55 \text{ °C}$ |

# **Ordering Information**

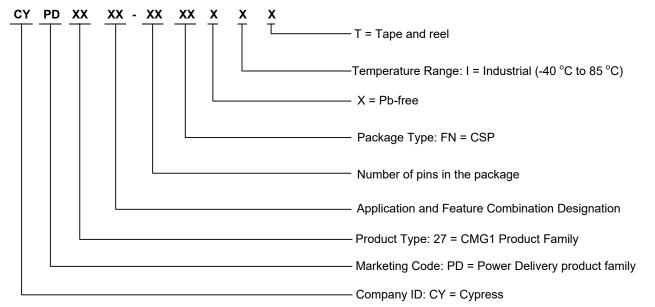

Table 6 lists the EZ-PD CMG1 part numbers and features.

#### Table 6. CMG1 Ordering Information

| MPN              | Application                  | Type-C Ports | Role | Package Type | Si ID |

|------------------|------------------------------|--------------|------|--------------|-------|

| CYPD2703-09FNXIT | Passive Cable                | 1            | EMCA | 9-ball CSP   | 2600  |

| CYPD2704-09FNXIT | Thunderbolt Passive<br>Cable | 1            | EMCA | 9-ball CSP   | 2601  |

#### **Ordering Code Definition**

# Packaging

#### Table 7. Package Characteristics

| Parameter       | Description                         | Conditions | Min    | Тур   | Max   | Units |

|-----------------|-------------------------------------|------------|--------|-------|-------|-------|

| T <sub>A</sub>  | Operating ambient temperature       | Industrial | -40    | 25    | 85    | °C    |

| TJ              | Operating junction temperature      | Industrial | -38.68 | 26.32 | 86.32 | °C    |

| T <sub>JA</sub> | Package θ <sub>JA</sub> (9-pin CSP) |            | _      | _     | 31.9  | °C/W  |

| T <sub>JC</sub> | Package θ <sub>JC</sub> (9-pin CSP) |            | _      | _     | 20.02 | °C/W  |

#### Table 8. Solder Reflow Peak Temperature

| Package   | Maximum Peak Temperature | Maximum Time within 5 °C of Peak<br>Temperature |

|-----------|--------------------------|-------------------------------------------------|

| 9-pin CSP | 260 °C                   | 30 seconds                                      |

#### Table 9. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package   | MSL   |

|-----------|-------|

| 9-pin CSP | MSL 1 |

Figure 6. 9-ball CSP Package Outline

SIDE VIEW

| SYMBOL | DI                | MENSIC  | ONS   |  |  |

|--------|-------------------|---------|-------|--|--|

| STMBUL | MIN.              | MAX.    |       |  |  |

| A      | -                 | -       | 0.520 |  |  |

| A1     | 0.122             | 0.152   | 0.182 |  |  |

| A2     | 0.250             | 0.300   |       |  |  |

| D      | 1                 | .351 BS | C     |  |  |

| E      | 1                 | .376 BS | С     |  |  |

| D1     | 0                 | .800 BS | С     |  |  |

| E1     | 0                 | .800 BS | С     |  |  |

| n      |                   | 9       |       |  |  |

| Øb     | 0.188 0.218 0.248 |         |       |  |  |

| eD     | 0.400 BSC         |         |       |  |  |

| əE     | 0                 | .400 BS | C     |  |  |

#### NOTES

1. ALL DIMENSIONS ARE IN MILLIMETERS.

002-21607 \*B

# Acronyms

#### Table 10. Acronyms Used in this Document

| Acronym | Description                                                                                                                                                  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CC      | configuration channel                                                                                                                                        |  |  |

| CPU     | central processing unit                                                                                                                                      |  |  |

| DFP     | downstream facing port                                                                                                                                       |  |  |

| DRP     | dual role port                                                                                                                                               |  |  |

| EMCA    | electronically marked cable assembly, a USB<br>cable that includes an IC that reports cable<br>characteristics (e.g., current rating) to the Type-C<br>ports |  |  |

| ESD     | electrostatic discharge                                                                                                                                      |  |  |

| IC      | integrated circuit                                                                                                                                           |  |  |

| MCU     | microcontroller unit                                                                                                                                         |  |  |

| NC      | no connect                                                                                                                                                   |  |  |

| NVL     | non-volatile latch                                                                                                                                           |  |  |

| PD      | power delivery                                                                                                                                               |  |  |

| PHY     | physical layer                                                                                                                                               |  |  |

| POR     | power-on reset                                                                                                                                               |  |  |

| PSoC®   | Programmable System-on-Chip™                                                                                                                                 |  |  |

| RX      | receive                                                                                                                                                      |  |  |

| ТХ      | transmit                                                                                                                                                     |  |  |

| Туре-С  | a new standard with a slimmer USB connector and<br>a reversible cable, capable of sourcing up to 100 W<br>of power                                           |  |  |

| USB     | Universal Serial Bus                                                                                                                                         |  |  |

## **Document Conventions**

#### **Units of Measure**

#### Table 11. Units of Measure

| Symbol | Unit of Measure        |  |  |

|--------|------------------------|--|--|

| °C     | degrees Celsius        |  |  |

| Hz     | hertz                  |  |  |

| KB     | 1024 bytes             |  |  |

| kHz    | kilohertz              |  |  |

| kΩ     | kilo ohm               |  |  |

| Mbps   | megabits per second    |  |  |

| MHz    | megahertz              |  |  |

| MΩ     | mega-ohm               |  |  |

| Msps   | megasamples per second |  |  |

| μA     | microampere            |  |  |

| μF     | microfarad             |  |  |

| μs     | microsecond            |  |  |

| μV     | microvolt              |  |  |

| μW     | microwatt              |  |  |

| mA     | milliampere            |  |  |

| ms     | millisecond            |  |  |

| mV     | millivolt              |  |  |

| nA     | nanoampere             |  |  |

| ns     | nanosecond             |  |  |

| Ω      | ohm                    |  |  |

| pF     | picofarad              |  |  |

| ppm    | parts per million      |  |  |

| ps     | picosecond             |  |  |

| S      | second                 |  |  |

| sps    | samples per second     |  |  |

| V      | volt                   |  |  |

# **Document History Page**

| Document Title: EZ-PD™ CMG1 Datasheet, USB Type-C EMCA Controller<br>Document Number: 002-20412 |         |                    |                    |                                     |  |  |  |

|-------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|-------------------------------------|--|--|--|

| Revision                                                                                        | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change               |  |  |  |

| *H                                                                                              | 6242326 | VGT                | 07/13/2018         | Changed datasheet status to Final.  |  |  |  |

| *                                                                                               | 6554744 | VGT                | 04/24/2019         | Updated 9-ball CSP package diagram. |  |  |  |

### Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products

| Arm <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Internet of Things                                    | cypress.com/iot        |

| Memory                                                | cypress.com/memory     |

| Microcontrollers                                      | cypress.com/mcu        |

| PSoC                                                  | cypress.com/psoc       |

| Power Management ICs                                  | cypress.com/pmic       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless Connectivity                                 | cypress.com/wireless   |

### **PSoC<sup>®</sup> Solutions**

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6 MCU

#### **Cypress Developer Community**

Community | Projects | Video | Blogs | Training | Components

Technical Support cypress.com/support

Notice regarding compliance with Universal Serial Bus specification. Cypress offers firmware and hardware solutions that are certified to comply with the Universal Serial Bus specification, USB Type-C<sup>™</sup> Cable and Connector Specification, and other specifications of USB Implementers Forum, Inc (USB-IF). You may use Cypress or third party software tools, including sample code, to modify the firmware for Cypress USB products. Modification of such firmware could cause the firmware/hardware combination to no longer comply with the relevant USB-IF specification. You are solely responsible ensuring the compliance of any modifications you make, and you must follow the compliance requirements of USB-IF before using any USB-IF trademarks or logos in connection with any modifications you make. In addition, if Cypress modifies firmware based on your specifications, then you are responsible for ensuring compliance with any desired standard or specifications as if you had made the modification. CYPRESS IS NOT RESPONSIBLE IN THE EVENT THAT YOU MODIFY OR HAVE MODIFIED A CERTIFIED CYPRESS PRODUCT AND SUCH MODIFIED PRODUCT NO LONGER COMPLIES WITH THE RELEVANT USB-IF SPECIFICATIONS.

© Cypress Semiconductor Corporation, 2017-2019. This document is the property of Cypress Semiconductor Corporation and its subsidiaries ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress shall have no liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. CYPRESS DOES NOT REPRESENT, WARRANT, OR GUARANTEE THAT CYPRESS PRODUCTS, OR SYSTEMS CREATED USING CYPRESS PRODUCTS, WILL BE FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION (collectively, "Security Breach"). Cypress disclaims any liability relating to any Security Breach, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from any Security Breach. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. "High-Risk Device" means any device or system whose failure could cause personal injury, death, or property damage. Examples of High-Risk Devices are weapons, nuclear installations, surgical implants, and other medical devices. "Critical Component" means any component of a High-Risk Device whose failure to perform can be reasonably expected to cause, directly or indirectly, the failure of the High-Risk Device, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from any use of a Cypress product as a Critical Component in a High-Risk Device. You shall indemnify and hold Cypress, its directors, officers, employees, agents, affiliates, distributors, and assigns harmless from and against all claims, costs, damages, and expenses, arising out of any claim, including claims for product liability, personal injury or death, or property damage arising from any use of a Cypress product as a Critical Component in a High-Risk Device. Cypress products are not intended or authorized for use as a Critical Component in any High-Risk Device except to the limited extent that (i) Cypress's published data sheet for the product explicitly states Cypress has qualified the product for use in a specific High-Risk Device, or (ii) Cypress has given you advance written authorization to use the product as a Critical Component in the specific High-Risk Device and you have signed a separate indemnification agreement.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Infineon: CYPD2703-09FNXIT CYPD2704-09FNXIT