40 W reference design with CDM10V isolated 0-10 V dimming interface

## XDP™ digital power

### **About this document**

### Scope and purpose

This document contains the specifications, schematics, Bill of Materials (BOM) and measurement results of the 40 W LED driver with 0 to 10 V dimming interface, using Infineon's XDPL8105 and CDM10V. It also includes a fine-tuning guide, debugging guide and frequently asked questions to ease the process of designing a customized LED driver with the XDPL8105 based on the user's own project requirements.

### **Intended audience**

This document is intended for anyone wishing to design high-performance single-stage digital Flyback dimmable LED drivers using the XDPL8105 and the isolated 0 to 10 V dimming interface using CDM10V.

### **Table of contents**

| About th | iis document                        |    |

|----------|-------------------------------------|----|

| Table of | contents                            |    |

| 1        | Introduction                        | 3  |

| 2        | Design features                     | 4  |

| 3        | Design specifications               | 5  |

| 4        | Schematic and PCB layout            | 7  |

| 5        | CDM10V circuit design and operation | 9  |

| 6        | Performance                         | 11 |

| 6.1      | Non-dimming                         | 11 |

| 6.1.1    | Output regulation and tolerance     | 11 |

| 6.1.2    | System efficiency                   | 12 |

| 6.1.3    | PF and iTHD                         | 13 |

| 6.1.4    | Thermal test                        | 14 |

| 6.1.5    | Conducted emissions (EN 55015B)     |    |

| 6.2      | Dimming                             | 17 |

| 7        | Bill of materials                   |    |

| 7.1      | BOM                                 |    |

| 7.2      | Transformer specifications          | 20 |

| 8        | Configuration set-up and procedures | 21 |

| 8.1      | XDPL8105 configuration              | 21 |

| 8.2      | CDM10V configuration                | 25 |

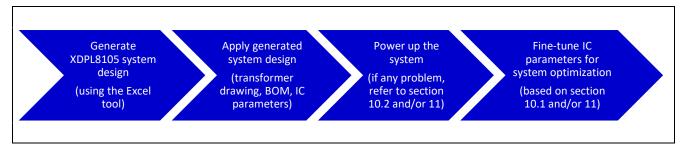

| 9        | Customizing your own system design  | 27 |

### Introduction

| 10       | XDPL8105 fine-tuning and debugging guide                                                                                                            | .29        |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 10.1     | XDPL8105 fine-tuning guide                                                                                                                          |            |

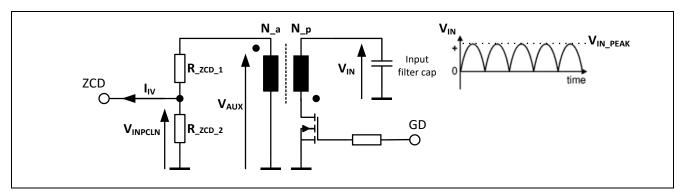

| 10.1.1   | Input voltage-sensing parameter fine-tuning                                                                                                         | .29        |

| 10.1.2   | QR valley switching parameter fine-tuning                                                                                                           | .31        |

| 10.1.3   | Output current regulation parameter fine-tuning                                                                                                     | .32        |

| 10.1.4   | Control loop and light quality-related parameter fine-tuning                                                                                        | .33        |

| 10.1.5   | Input power quality-related parameter fine-tuning                                                                                                   | .33        |

| 10.2     | XDPL8105 debugging guide                                                                                                                            | .34        |

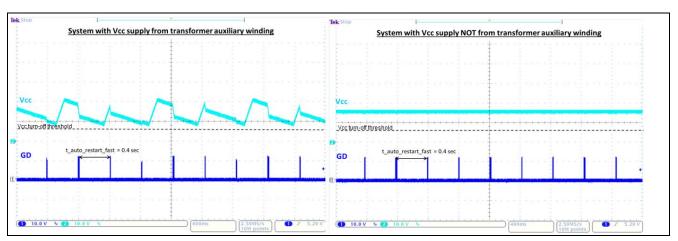

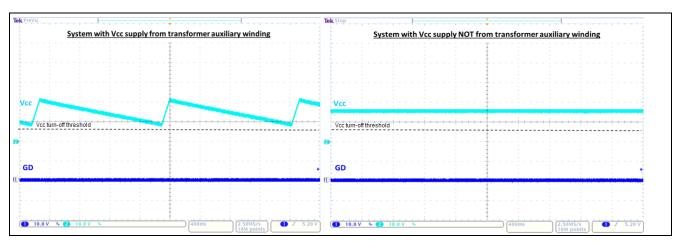

| 10.2.1   | Pin GD and V <sub>cc</sub> signal debugging                                                                                                         | .34        |

| 10.2.2   | Debug mode                                                                                                                                          | .37        |

| 11       | Frequently asked questions                                                                                                                          | .39        |

| 11.1     | Does the XDPL8105 support dim-to-off?                                                                                                               | .39        |

| 11.2     | What is the lowest possible output current with minimum dimming input?                                                                              | .40        |

| 11.3     | Why is the actual output current with minimum dimming input much higher than the parameter                                                          |            |

|          | I_out_dim_min setting (at maximum AC input voltage and minimum LED load voltage)?                                                                   | .40        |

| 11.4     | What causes the longer time-to-light with minimum dimming input?                                                                                    | .40        |

| 11.5     | How can time-to-light with minimum dimming input be improved?                                                                                       |            |

| 11.6     | How can the output current regulation be optimized?                                                                                                 | .41        |

| 11.7     | Why does the output LED current have high ripple?                                                                                                   | .41        |

| 11.8     | How can LED current ripple be reduced?                                                                                                              |            |

| 11.9     | Why is there a light flicker when the input voltage is stepped up or down?                                                                          | .42        |

| 11.10    | What are the configurable options for the dimming curve?                                                                                            | .42        |

| 11.11    | Can the HV series resistor be connected directly to the input filter capacitor after the bridge rectifier?                                          | 43         |

| 11.12    | What is the parameter <i>t_min_demag</i> used for?                                                                                                  |            |

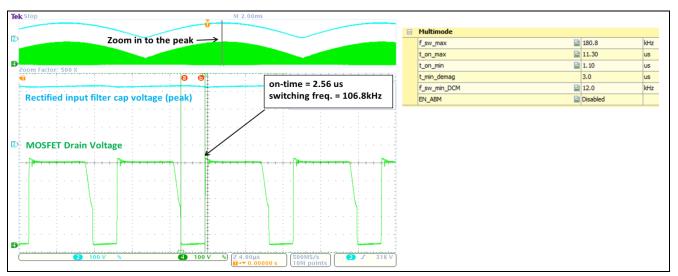

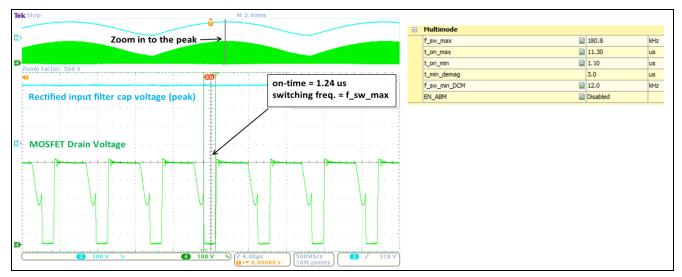

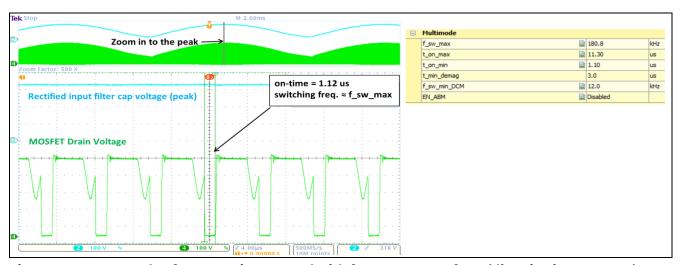

| 11.13    | How does multi-mode operation work when dimmed up or down?                                                                                          |            |

| 11.14    | How can the controller operating mode be identified during actual testing?                                                                          |            |

| 11.15    | Why is the QRM on-time or DCM switching period changing at different AC input phase angles                                                          |            |

| 11 10    | despite having stable light output in steady-state?                                                                                                 |            |

| 11.16    | Why does the output current stay at <i>I_out_set</i> despite being dimmed down?                                                                     | .41        |

| 11.17    | What could cause the start-up UVP for V <sub>out</sub> to be triggered despite having the correct number of LEDs connected to the secondary output? | 47         |

| 11.18    | What could cause inaccuracy of the input under-voltage (brown-out) protection threshold?                                                            |            |

| 11.18    | What is the main benefit of configuring the GD pin peak-source current parameter <i>I_GD_pk</i> ?                                                   |            |

| 11.19    | Why is the output bleeder mandatory in the design?                                                                                                  |            |

| 11.21    | Can XDPL8105 be used with input voltage higher than 425 V AC or 600 V DC?                                                                           |            |

|          |                                                                                                                                                     | .49        |

| 11.22    | Can XDPL8105 be used as a controller of the Flyback converter that has a front-stage PFC boost converter?                                           | <b>4</b> C |

| 11.23    | Can the Flyback transformer auxiliary winding be used to supply the microcontroller's operating                                                     |            |

| 11.23    | voltage?                                                                                                                                            |            |

| 10       | ·                                                                                                                                                   |            |

| 12       | References                                                                                                                                          |            |

| Revision | history                                                                                                                                             | 52         |

Introduction

### 1 Introduction

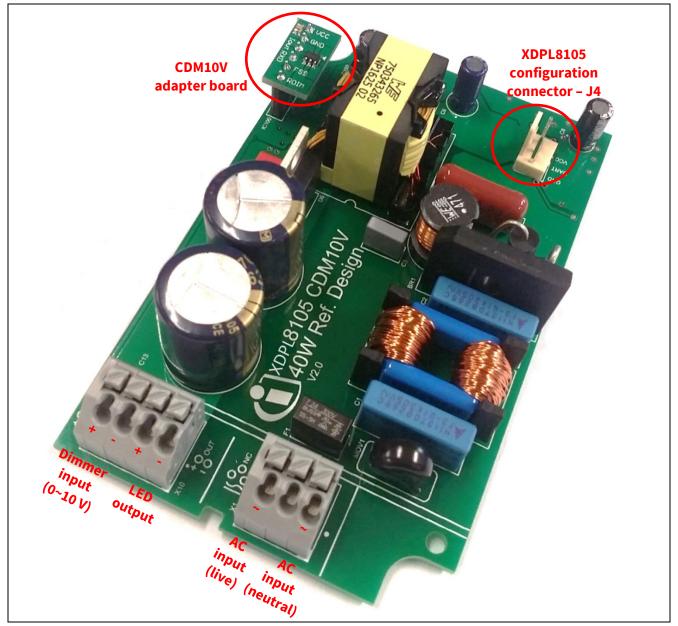

The XDPL8105 40 W reference design is a digitally configurable LED driver with a universal input of 90 to 305 V AC, a wide output load range of 16 to 45 V DC and isolated 0 to 10 V dimming (with CDM10V). Please refer to the next page for the main design features of this board based on Infineon's XDPL8105 and CDM10V.

Note:

The 40 W reference design sample is ready to be tested on being received and without the need for any pre-programming by the user, as the XDPL8105 chip on the PCB has already been burned with the first full configuration set of working parameters. Please connect the AC input, LED output and dimming input as shown in **Figure 1** for the test set-up.

ATTENTION: LETHAL VOLTAGES ARE PRESENT ON THIS REFERENCE DESIGN. DO NOT OPERATE THE BOARD UNLESS YOU ARE TRAINED TO HANDLE HIGH VOLTAGE CIRCUITS. DO NOT LEAVE THIS BOARD UNATTENDED WHEN IT IS POWERED UP.

Figure 1 XDPL8105 40 W reference design with CDM10V adapter board and configuration connector

**Design features**

## 2 Design features

- Single-stage Flyback with Power Factor Correction (PFC) and high-precision primary-side-controlled constant current output

- Excellent current accuracy (±3 percent) across universal-input voltage range (90 to 305 V AC) and wideoutput voltage range (18 V to 45 V)

- Integrated 600 V HV cell for fast start-up

- · High efficiency with QR operation

- Low dimming output with Discontinuous Conduction Mode (DCM) and Active Burst Mode (ABM) operation

- High Power Factor (PF) and low input current Total Harmonic Distortion (iTHD) with advanced switchingcycle modulation scheme

- Low BOM

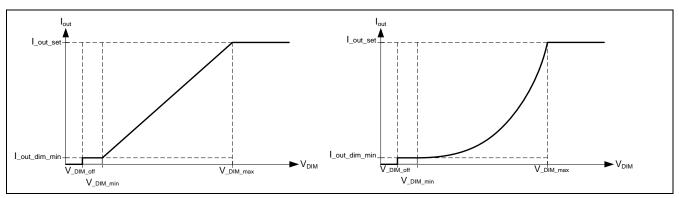

- Configurable dimming curve to either linear or quadratic (eye-adaptive)

- Configurable output current at minimum dimming input (from 10 percent to 1 percent)

- Quick design and variant handling supported by digital parameter configurability with .dp Vision GUI e.g. output current setting, dimming curve shape selection, protection handling and operation fine-tuning

- Supports transformer-less IEC60929-compliant isolated 0 to 10 V dimming using CDM10V

Note:

CDM10V is a device which transmits analog voltage-based signals from a 0 to 10 V dimmer or potentiometer to the dimming or PWM input of a lighting controller IC in the form of a 5 mA current-based PWM signal to drive an external isolated optocoupler. It replaces many components in a traditional solution and reduces BOM and PCB space significantly. For more details about CDM10V, please visit the Infineon website: <a href="http://www.infineon.com/cdm10v">http://www.infineon.com/cdm10v</a>

**Design specifications**

# 3 Design specifications

**Table 1** and **Table 2** respectively list the electrical specifications and system protections of this reference design.

Table 1 Electrical specifications

| Specification                                                                                                     | Symbol              | Value          | Unit |

|-------------------------------------------------------------------------------------------------------------------|---------------------|----------------|------|

| AC input voltage range                                                                                            | V <sub>AC</sub>     | 90~305         | Vrms |

| Output LED load range (includes dimming)                                                                          | $V_{LED}$           | 16~45          | V    |

| Non-dimmed output current setting <sup>1</sup>                                                                    | l_out_set           | 880            | mA   |

| Total line, load regulation                                                                                       | -                   | ±3             | %    |

| Dimming input voltage range                                                                                       | V <sub>DIMMER</sub> | 0~10           | V    |

| Dimming input resistance range <sup>2</sup>                                                                       | R <sub>DIMMER</sub> | 5~50           | kΩ   |

| Minimum output current setting <sup>1</sup>                                                                       | I_out_dim_min       | 88             | mA   |

| Output current dimming curve <sup>1</sup>                                                                         | C_dim               | Quadratic      | _    |

| Efficiency (V <sub>in</sub> : 120~277 V AC, V <sub>out</sub> : 30~45 V, non-dimming)                              | η                   | More than 89   | %    |

| Power factor (V <sub>in</sub> : 120~277 V AC, V <sub>out</sub> : 30~45 V, non-dimming)                            | PF                  | More than 0.95 | _    |

| Input current total harmonic distortion (V <sub>in</sub> : 120~277 V AC, V <sub>out</sub> : 30~45 V, non-dimming) | iTHD                | Less than 10   | %    |

$<sup>^{\</sup>rm 1}\,\mbox{Configurable}$  in XDPL8105 .

$<sup>^2</sup>$  Based on CDM10V pin  $R_{\text{dim+}}$  default bias current of 200  $\mu A.$  See  ${\color{red}Table~3}$  for configurable options.

## **Design specifications**

### Table 2System protections

| Protection                                                          | Symbol                       | Value        | Unit |

|---------------------------------------------------------------------|------------------------------|--------------|------|

| Nominal input Over-Voltage Protection (OVP) level <sup>1</sup>      | $V_{inOV}$                   | 329          | Vrms |

| Nominal input Under-Voltage Protection (UVP) level <sup>1</sup>     | V_inUV                       | 62           | Vrms |

| Nominal output OVP level <sup>2</sup>                               | $V_{ m outOV}$               | 48.4         | V    |

| Nominal output over-current (average) protection level <sup>3</sup> | I_out_max_avg                | 1320         | mA   |

| Nominal output over-current (peak) protection level <sup>1</sup>    | I_out_max_peak               | 1980         | mA   |

| IC over-temperature detection threshold <sup>2</sup>                | T_critical                   | 119          | °C   |

| Input OVP reaction                                                  | Reaction_ <sub>OVP_Vin</sub> | Latch mode   | _    |

| Input UVP reaction                                                  | Reaction_uvp_vin             | Auto-restart | _    |

| Output OV (output open) protection reaction <sup>4</sup>            | Reaction_OVP_Vout            | Auto-restart | _    |

| Output UV (output short) protection reaction                        | Reaction_uvp_vout            | Auto-restart | _    |

| Output over-current (average) protection reaction                   | Reaction_lout_max_avg        | Auto-restart | _    |

| Output over-current (peak) protection reaction                      | Reaction_lout_max_pk         | Auto-restart | _    |

| IC over-temperature protection reaction                             | Reaction_ <sub>TP</sub>      | Latch mode   | _    |

| Auto-restart time <sup>5</sup>                                      | t_auto_restart               | 1.0          | S    |

$<sup>^{\</sup>rm 1}\,{\rm Protection}$  can be disabled and its level can be configured.

$<sup>^{\</sup>rm 2}$  Protection cannot be disabled but its level can be configured.

$<sup>^3</sup>$  Protection can be disabled but its level cannot be configured and fixed as 150 percent of I\_out\_set.

<sup>&</sup>lt;sup>4</sup> Protection reaction can be configured to either auto-restart or latch mode.

$<sup>^{\</sup>rm 5}$  Auto-restart time of the protections can be configured.

**Schematic and PCB layout**

## 4 Schematic and PCB layout

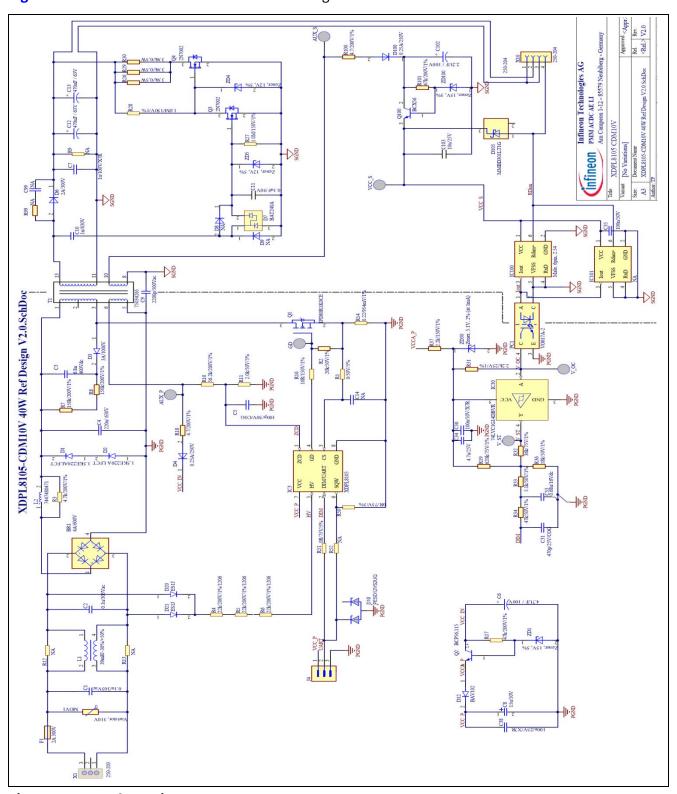

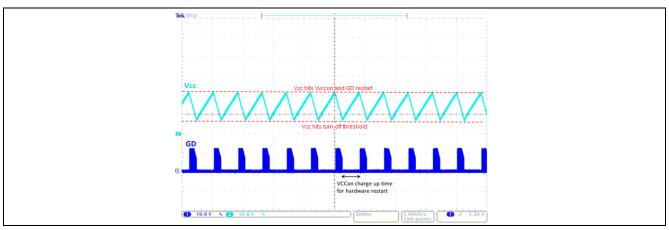

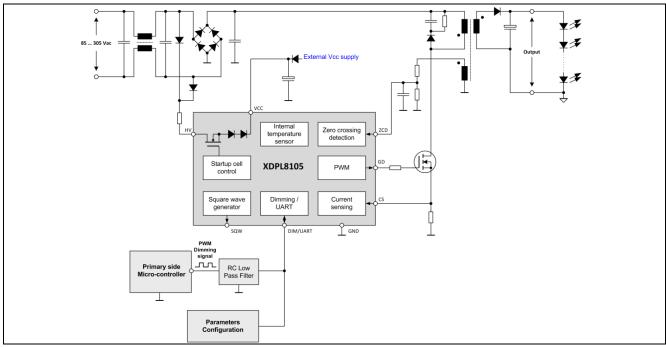

Figure 2 shows the schematic of this reference design.

Figure 2 Schematic

Note: By default, the reference design main board is connected with the CDM10V adapter board via IC100. If necessary, the user can unplug the adapter board and mount CDM10V on the main board via IC101.

### **Schematic and PCB layout**

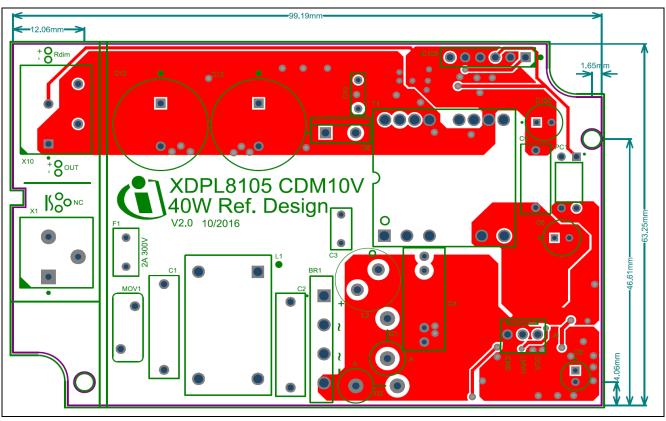

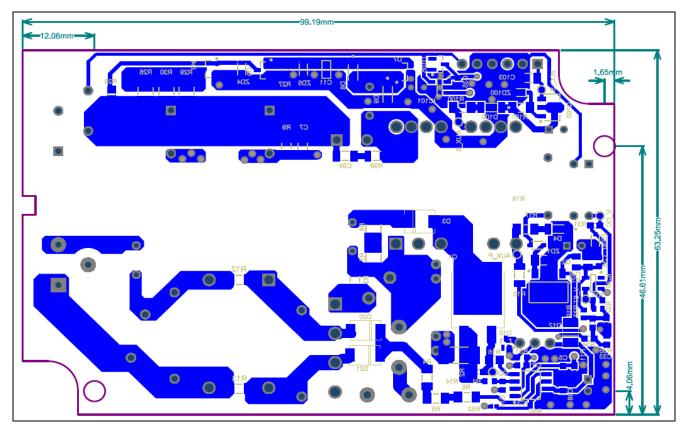

Figure 3 and Figure 4 respectively show the PCB top and bottom layouts of this reference design.

Figure 3 PCB top layout and dimensions

Figure 4 PCB bottom layout and dimensions

CDM10V circuit design and operation

#### **CDM10V** circuit design and operation 5

R100, D100 and C102 form a rectifier circuit which supplies a voltage from the transformer winding based on a ratio of the output load voltage. In this design, it is necessary to add the voltage regulator circuitry (consisting of R101, ZD100, Q100 and C103) after the rectifier circuitry to ensure that the CDM10V pin V<sub>cc</sub> voltage supply is kept stable and within the limits while supporting the wide output load voltage range of 16~45 V. By selecting a Zener diode, ZD100, which has a low voltage rating and yet is sufficient to supply the CDM10V operating voltage, the CDM10V chip losses can be kept low. A 15 V Zener is used in this design.

D105 is connected between pin R<sub>dim+</sub> and pin V<sub>CC</sub> to ensure the voltage level at pin R<sub>dim+</sub> does not exceed its maximum voltage rating of V<sub>cc</sub> + 0.7 V, in case of an active voltage source (e.g. DC power supply) being applied to the 0 to 10V dimmer input of this reference design for testing purposes. For productive use only a passive voltage source (e.g. potentiometer, current sink dimmer) can be connected to pin R<sub>dim+</sub>, and D105 can be omitted. For productive use either the active or passive voltage source can be connected to pin R<sub>dim+</sub>, and it is highly recommended to use a low-leakage Schottky diode for D105 such as MMBD301LT1G, to maintain high accuracy of the dimmer voltage measurement on pin R<sub>dim+</sub>.

CDM10V pins GND, RxD and V<sub>FSS</sub> are directly connected to a secondary-side ground plane, which is also used as the cooling area.

The optocoupler, PC1, is directly driven by a 5 mA current-based PWM signal from pin I<sub>out</sub> of CDM10V. The PWM duty cycle changes based on the voltage level at CDM10V pin R<sub>dim+</sub>, which should be connected to either the 0 to 10 V dimmer or the potentiometer.

There are many ways of designing the primary-side circuitry connecting to the optocoupler, depending on the dimming input type of the primary controller. This reference design presents an exemplary circuit based on the primary controller XDPL8105, which has an analog non-inverting dimming input.

IC30, a single-channel Schmitt trigger inverter IC, is used here for many reasons. One is to invert the receiving signal of PC1 so that it matches the XDPL8105 non-inverting dimming input. A second reason is to reconstruct the receiving signal of PC1, which is heavily distorted by the slow-rising slope, into a more accurate digital PWM signal (the slow-rising slope is caused by the low pull-up current to the coupler and the selection of a slowswitching optocoupler). The final reason is that the required analog voltage levels can be adjusted with the two resistor dividers after and over it (R19 and R36 for the minimum voltage/maximum dimming and R32 and R36 for the maximum voltage/no dimming).

The supply voltage of 5.1 V for IC30 and the coupler of PC1 (via pull-up resistor R31) is stepped down from the regulated auxiliary self-supply voltage of the D12 anode by using a resistor (R37), a Zener diode (ZD30) and two capacitors (C34 and C36). For fast and smooth XDPL8105 start-up, D12 is necessary to ensure the XDPL8105 pin HV charging current only flows to its V<sub>CC</sub> capacitors (C8 and C38), but not to other parts of the primary circuit.

Since the XDPL8105 has an analog dimming input, the digital PWM signal generated by IC30 must be filtered. As the XDPL8105 already has an internal six-stage digital filter for its dimming input sensing, an external singlestage low-pass filter (R33 and C33) with a cut-off frequency at 100 Hz is deployed in this reference design. Otherwise, it is strongly recommended to have two stages of a 100 Hz low-pass filter.

In order to retain both the signal integrity of the communication and the dimming functionality of XDPL8105, the pin DIM/UART impedance cannot be too low, and thus an additional RC filter (C31 and R34) is deployed after the 100 Hz low-pass filter (R33 and C33). It is important to note that C31 should not exceed 1 nF.

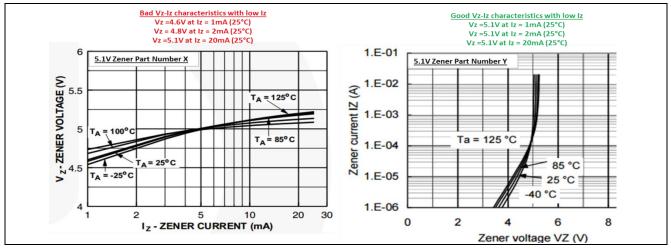

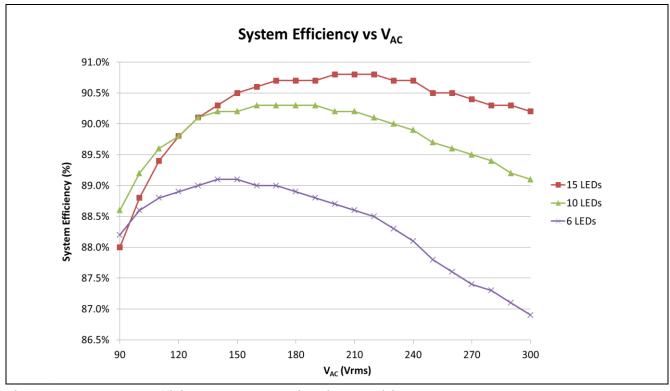

Since ZD30, the Zener voltage (Vz), serves as the reference voltage of the digital PWM-to-analog signal conversion, it is very important to select a 5.1 V Zener part number of ZD30 which has good Vz-Iz characteristics (stable Vz with low Zener current, Iz) and a low tolerance (e.g. 2.5 percent or below) for highly accurate

## CDM10V circuit design and operation

dimming input signals. Figure 5 shows how to determine the good and poor Zener Vz-Iz characteristics from two different part numbers (X and Y) with 5.1 V Zener voltage.

Figure 5 Example of how to determine good and poor Zener Vz-Iz characteristics

Table 3 shows the default and configurable settings of the four parameters in the CDM10V device. The CDM10V adapter board in this reference design uses the default settings. If necessary, please refer to Section 8.2 for more information on CDM10V configuration.

Default and configurable settings of the four parameters in the CDM10V device Table 3

| Parameter             | Fuse | e bits setting and description | Remark                 |

|-----------------------|------|--------------------------------|------------------------|

|                       | 00   | 200 μΑ                         | Default CDM10V setting |

| Pin R <sub>dim+</sub> | 01   | 100 μΑ                         | -                      |

| bias current          | 10   | 50 μΑ                          | -                      |

|                       | 11   | 500 μΑ                         | -                      |

| Dim-to-off            | 0    | Disabled                       | Default CDM10V setting |

| option                | 1    | Enabled                        | -                      |

|                       | 00   | 1000 Hz                        | Default CDM10V setting |

| Pin I <sub>out</sub>  | 01   | 500 Hz                         | -                      |

| PWM output frequency  | 10   | 200 Hz                         | -                      |

| rrequericy            | 11   | 2000 Hz                        | -                      |

|                       | 00   | 5 percent                      | Default CDM10V setting |

| Pin I <sub>out</sub>  | 01   | 2 percent                      | -                      |

| PWM output            | 10   | 1 percent                      | _                      |

| linimum duty cycle    | 11   | 10 percent                     | _                      |

**Performance**

#### **Performance** 6

#### **Non-dimming** 6.1

The measurement results under non-dimming conditions are presented in this section.

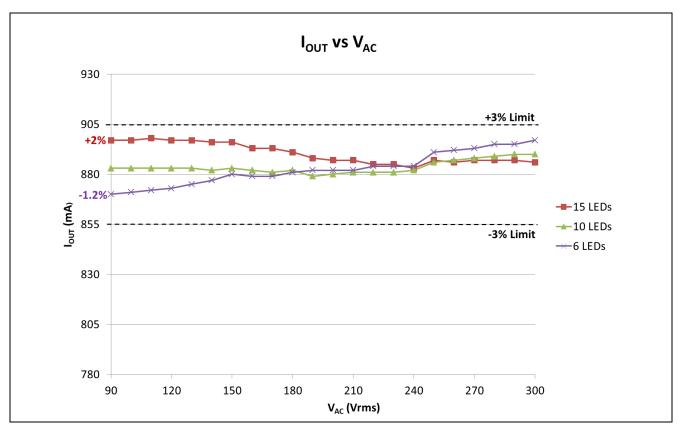

#### 6.1.1 **Output regulation and tolerance**

The total line (V AC = 90~300 V<sub>rms</sub>) and load regulation (V<sub>LED</sub> = 18~45 V) of the output current under non-dimming conditions are ±2 percent or less, based on the output current set-point of 880 mA.

Figure 6 Line and load regulation of output current under non-dimming conditions

In total 50 reference design samples have been tested, and the non-dimmed output current of each board was recorded using the same test condition (V AC input: 90 Vrms, output: 15 LEDs and ambient temperature of 25°C) to check the output tolerance, which is contributed to by both the IC and external components' tolerance. The tolerance study was done based on this test condition because it has the highest output current regulation of +2 percent (see Figure 6), so that the total output regulation and sample output tolerance can be estimated.

Figure 7 shows the distribution data of the non-dimmed output current.

### **Performance**

Figure 7 Output current histogram based on 50 reference design samples

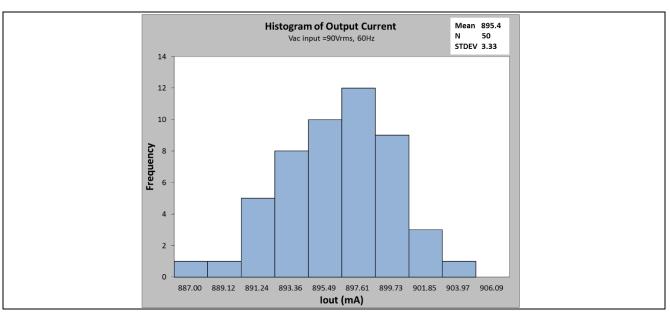

The result shows that the output current tolerance is approximately  $\pm 1$  percent and standard deviation is 3.33 mA. Therefore, the total output regulation and sample output tolerance is approximately  $\pm 3$  percent.

## **6.1.2** System efficiency

The system efficiency measurements under non-dimming conditions are shown in Figure 8.

Figure 8 System efficiency under non-dimming conditions

### controller

**Performance**

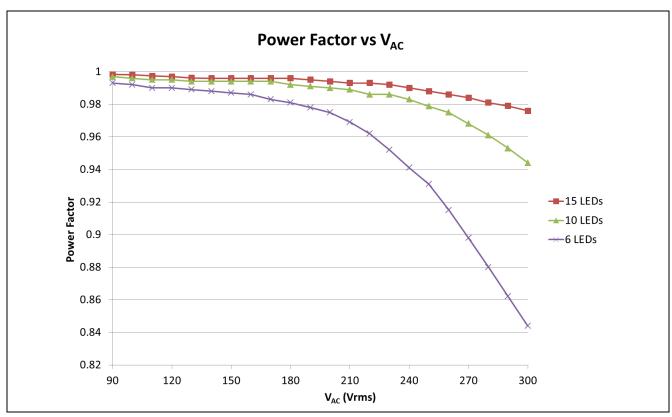

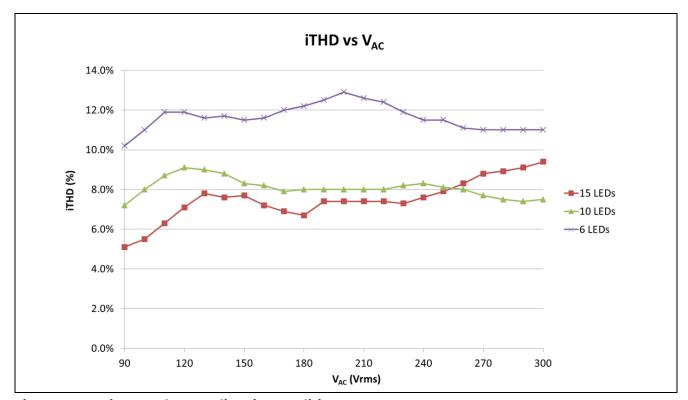

#### PF and iTHD 6.1.3

The PF and iTHD measurements under non-dimming conditions are shown in Figure 9 and Figure 10.

Figure 9 PF under non-dimming conditions

Figure 10 iTHD under non-dimming conditions

## controller

#### **Performance**

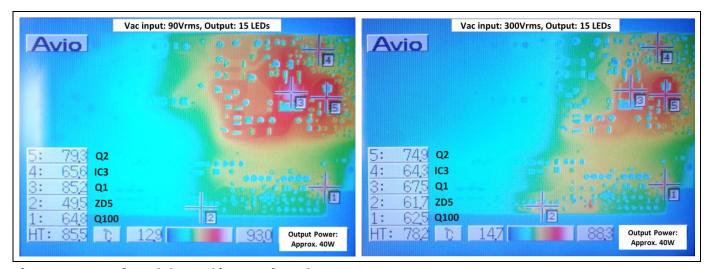

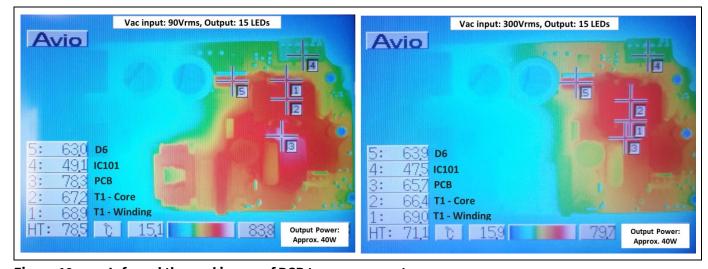

#### Thermal test 6.1.4

The open-frame thermal test was done on the reference design using an infrared thermography camera (TVS-500EX) at an ambient temperature of 20°C.

The temperature measurements of the following main components (see **Table 4**) were taken after two hours running at maximum LED voltage and maximum output current.

Table 4 Main components for temperature measurements

| PCB bottom |                                                    | PCB top      |                             |

|------------|----------------------------------------------------|--------------|-----------------------------|

| Component  | Description                                        | Component    | Description                 |

| Q2         | Primary V <sub>cc</sub> regulator NPN transistor   | D6           | Output diode                |

| IC3        | Flyback-controlled XDPL8105                        | IC101        | CDM10V                      |

| Q1         | Flyback MOSFET IPD80R1K0CE                         | PCB          | Hottest PCB area            |

| ZD5        | Output bleeder Zener diode                         | T1 – core    | Flyback transformer core    |

| Q100       | Secondary V <sub>cc</sub> regulator NPN transistor | T1 – winding | Flyback transformer winding |

Figure 11 Infrared thermal image of PCB bottom components

Figure 12 Infrared thermal image of PCB top components

**Performance**

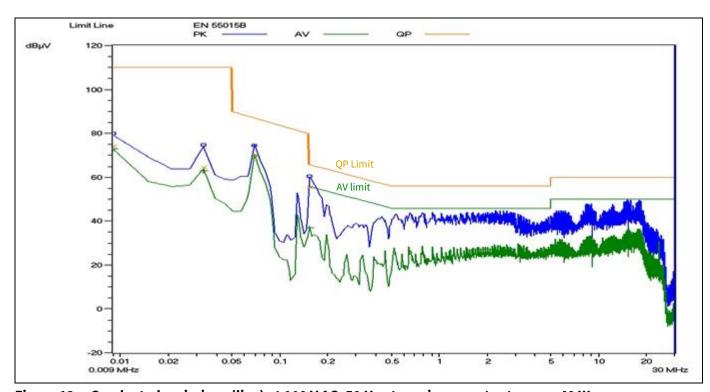

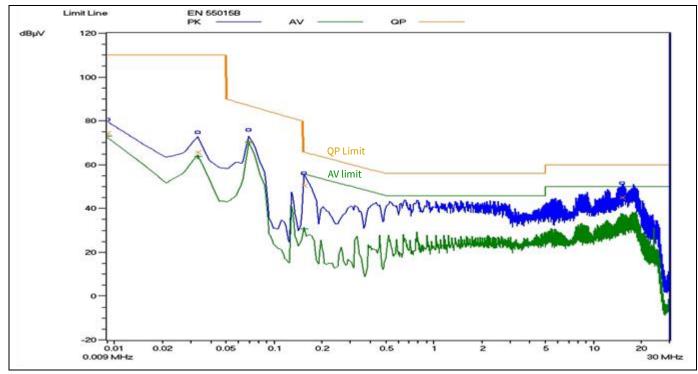

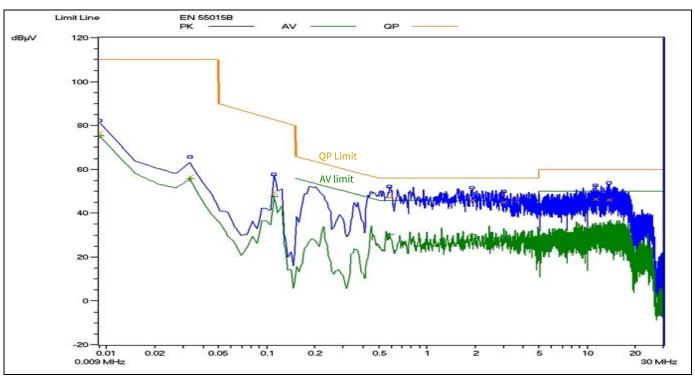

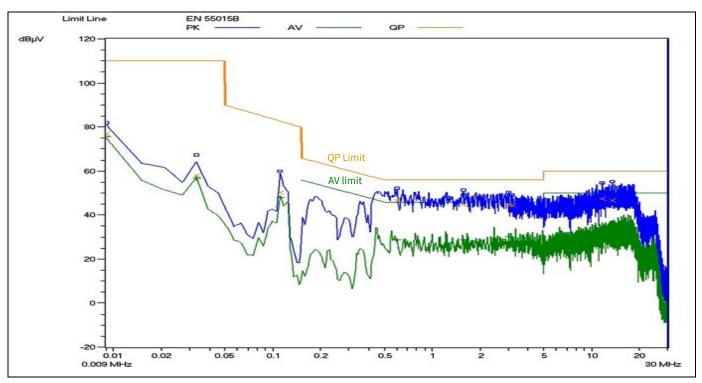

## 6.1.5 Conducted emissions (EN 55015B)

The conducted emissions test was performed at maximum output power (40 W) of this reference design (maximum output LED load voltage under non-dimming conditions) and there is more than 3 dB margin observed for both live and neutral measurements based on EN 55015 standard Class B limits.

Figure 13 Conducted emissions (live) at 110 V AC, 50 Hz at maximum output power 40 W

Figure 14 Conducted emissions (neutral) at 110 V AC, 50 Hz at maximum output power 40 W

### **Performance**

Figure 15 Conducted emissions (live) at 230 V AC, 50 Hz at maximum output power 40 W

Figure 16 Conducted emissions (neutral) at 230 V AC, 50 Hz at maximum output power 40 W

Note: The items of measuring equipment used for this conducted emissions test were Schaffner NNB41 and SMR4503.

## controller

**Performance**

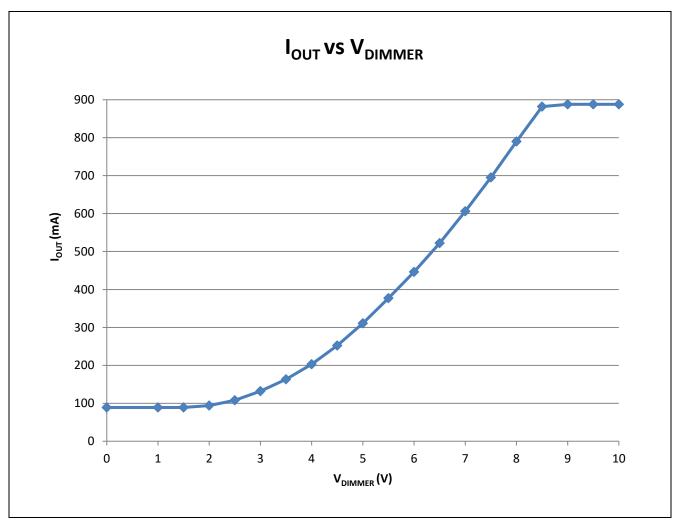

#### **Dimming** 6.2

This section provides the output current,  $I_{OUT}$ , measurement results when  $V_{DIMMER} = 0~10~V$  is applied (see **Table** 5), with an AC input voltage of 277 Vrms, 60 Hz and an output load of 10 LEDs.

Based on the measurement results, the plotted dimming curve has a quadratic shape (see Figure 17) because the reference design XDPL8105 chip has already been burned with the parameter C\_DIM setting "Quadratic".

The user can configure the dimming curve shape parameter, C\_DIM, to either "Linear" or "Quadratic". Note:

| Table 5                 | Outp | ut curren | ıt dimmin | ıg measur | ement |     |     |     |     |      |

|-------------------------|------|-----------|-----------|-----------|-------|-----|-----|-----|-----|------|

| V <sub>DIMMER</sub> (V) | 0    | 1.0       | 1.5       | 2.0       | 2.5   | 3.0 | 3.5 | 4.0 | 4.5 | 5.0  |

| I <sub>OUT</sub> (mA)   | 89   | 89        | 89        | 94        | 108   | 132 | 163 | 203 | 252 | 311  |

|                         |      |           |           |           |       |     |     |     |     |      |

| V <sub>DIMMER</sub> (V) | 5.5  | 6.0       | 6.5       | 7.0       | 7.5   | 8.0 | 8.5 | 9.0 | 9.5 | 10.0 |

| I <sub>OUT</sub> (mA)   | 377  | 446       | 522       | 606       | 695   | 790 | 882 | 888 | 888 | 888  |

Figure 17 Quadratic dimming curve (adapted to eye sensitivity)

**Bill of Materials**

#### **Bill of materials** 7

This section provides the BOM and also the transformer specifications.

#### **BOM** 7.1

#### **BOM of main board** Table 6

| Designator       | Value                                                 | Part number             | Manufacturer       | Quantity |

|------------------|-------------------------------------------------------|-------------------------|--------------------|----------|

| BR1              | 4 A/600 V                                             | GBU4J-E3/45             | Vishay             | 1        |

| C1, C2           | 0.1 μ/305 V AC                                        | B32922C3104K            | Epcos              | 2        |

| C3               | 6.8 n/400 V                                           | BFC237065682            | Vishay             | 1        |

| C4               | 220 n/630 V                                           | ECW-FA2J224J            | Panasonic          | 1        |

| C5               | 100 p/50 V/C0G                                        | C0603C101F5GAC          | Kemet              | 1        |

| C6               | 4.7 μF/100 V 20 percent radial                        | ECA2AM4R7               | Panasonic          | 1        |

| C7               | 1 μ/100 V                                             | 12061C105K4Z2A          | AVX                | 1        |

| C8               | 15 μ/50 V                                             | EEU-FC1H150H            | Panasonic          | 1        |

| C9               | 2200 p/500 V AC                                       | VY1222M47Y5UQ63V0       | Vishay             | 1        |

| C10              | 1 n/630 V                                             | FKP2J011001D00JSSD      | Wima               | 1        |

| C11              | 0.1 μF/50 V                                           | GRM188R71H104KA93D      | Murata             | 1        |

| C12, C13         | 470 μF/63 V/20 percent radial                         | EEU-FC1J471             | Panasonic          | 2        |

| C31              | 470 p/25 V/COG                                        | 06033A471K4T2A          | AVX                | 1        |

| C33              | 0.68 μ/16 V                                           | GRM188R61C684KA75#      | Murata             | 1        |

| C34              | 4.7 μ/25 V                                            | C2012X7R1E475K125AB     | TDK                | 1        |

| C35, C36,<br>C38 | 100 n/50 V                                            | MC0603B104K500CT        | Multicomp          | 3        |

| C102             | 2.2 μF/100 V/20 percent radial                        | UPW2A2R2MDD             | Nichicon           | 1        |

| C103             | 10 μ/25 V                                             | GRM31CR71E106KA12L      | Murata             | 1        |

| D1, D2           | 220 V/1.5 kW                                          | 1.5KE220A               | STMicroelectronics | 2        |

| D3               | Diode, fast, 3 A, 1000 V                              | RS3MB-13-F              | Diodes             | 1        |

| D4, D100         | Diode, fast, 0.25 A, 250 V                            | BAV103,115              | NXP Semiconductors | 2        |

| D6               | Schottky, 40 A, 250 V                                 | MBR40250G               | On Semiconductor   | 1        |

| D7               | Schottky, 0.4 A, 240 V                                | BAT 240A E6327          | Infineon           | 1        |

| D10              | ESD diode, 12 V                                       | PESD12VS2UQ             | NXP                | 1        |

| D12              | Diode, fast, 0.25 A, 200 V                            | BAV102                  | NXP                | 1        |

| D20, D21         | Diode, fast, 1 A, 600 V                               | ES1J                    | FAIRCHILD          | 2        |

| D105             | Schottky, 0.2 A, 30 V                                 | MMBD301LT1G             | ONSEMI             | 1        |

| F1               | Fuse 300 V/2 A                                        | SS-5H-2A-APH            | Bussmann by Eaton  | 1        |

| IC3              | Digital Flyback controller IC                         | XDPL8105                | Infineon           | 1        |

| IC30             | Single Schmitt trigger inverter                       | SN74LVC1G14DBVR         | Texas Instruments  | 1        |

| IC100            | Male, six-pin, 2.54 connector to CDM10V adapter board | SL1.025.36Z cut six-pin | Fischer Elektronik | 1        |

| J4               | 2.54 mm header, three-pin, vert.                      | MC34631                 | Multicomp          | 1        |

| L1               | 39 mH/0.8 A                                           | B82732F2801B001         | Epcos              | 1        |

| L2               | 470 μH/1.15 A                                         | 7447480471              | Würth Elektronik   | 1        |

| MOV1             | Varistor, 510 V                                       | ERZE08A511              | Panasonic          | 1        |

| PC1              | VO617A-2                                              | VO617A-2                | Vishay             | 1        |

| Q1               | MOSFET, 0.95 Ω, 800 V, DPAK                           | IPD80R1K0CEBTMA1        | Infineon           | 1        |

| Q2               | NPN, 1 A, 80 V, SOT-223                               | BCP56,115               | NXP                | 1        |

| Q3, Q4           | MOSFET, 0.3 A, 60 V, SOT-23                           | 2N7002                  | Infineon           | 2        |

## Bill of Materials

| Designator       | Value                                                                     | Part number      | Manufacturer     | Quantity |

|------------------|---------------------------------------------------------------------------|------------------|------------------|----------|

| Q100             | NPN, 1 A, 80 V, SOT-89                                                    | BCX56-16,115     | NXP              | 1        |

| R1, R50,<br>R51  | 0 R                                                                       | RC0603JR-070RL   | Yageo/Phycomp    | 3        |

| R2               | 20 k                                                                      | AC0603FR-0720KL  | Yageo/Phycomp    | 1        |

| R3               | 4.7 k                                                                     | RC1206FR-074K7   | Yageo/Phycomp    | 1        |

| R4, R5, R6       | 22 k                                                                      | RC1206FR-0722K   | Yageo/Phycomp    | 3        |

| R7, R8           | 150 k/0.5 W                                                               | CRCW1210150KFKEA | Vishay           | 2        |

| R10              | 56.2 k                                                                    | CRCW120656K2FKEA | Vishay           | 1        |

| R11              | 2.0 k                                                                     | AC0603JR-072KL   | Yageo/Phycomp    | 1        |

| R14              | 0.22                                                                      | RCWE1206R220FKEA | Vishay           | 1        |

| R16              | 10 R                                                                      | RC0805FR-0710R   | Yageo/Phycomp    | 1        |

| R17, R101        | 47 k                                                                      | RC1206FR-0747K   | Yageo/Phycomp    | 2        |

| R18              | 4.7                                                                       | AC1206FR-074R7L  | Yageo/Phycomp    | 1        |

| R19              | 620 k                                                                     | CRCW0603620KFKEA | Vishay           | 1        |

| R26, R29,<br>R30 | 3.9 k/0.5 W                                                               | ERJU14F3901U     | Panasonic        | 3        |

| R27, R28         | 1.0 meg                                                                   | AC0805FR-071ML   | Yageo/Phycomp    | 2        |

| R31              | 2.2 k                                                                     | MCHP03W8F2201T5E | Multicomp        | 1        |

| R32              | 36 k                                                                      | CRCW060336K0FKED | Vishay           | 1        |

| R33              | 5.1 k                                                                     | AC0603FR-075K1L  | Yageo/Phycomp    | 1        |

| R34              | 47 k                                                                      | AC0603FR-0747KL  | Yageo/Phycomp    | 1        |

| R36              | 18 k                                                                      | AC0603FR-0718KL  | Yageo/Phycomp    | 1        |

| R37              | 2.2 k                                                                     | RC0805FR-072K2L  | Yageo/Phycomp    | 1        |

| R100             | 4.7                                                                       | AC1206FR-074R7L  | Yageo/Phycomp    | 1        |

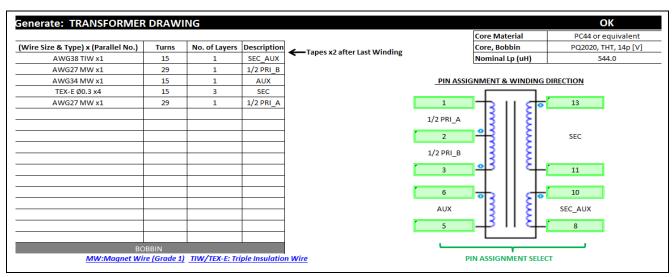

| T1               | PQ2020; Lp = 544 μH; Np = 58; Ns = 15; Na = 15; N <sub>sec_aux</sub> = 15 | 750343265 Rev03  | Würth Elektronik | 1        |

| X1               | 250-203                                                                   | 250-203          | WAGO             | 1        |

| X10              | 250-204                                                                   | 250-204          | WAGO             | 1        |

| ZD1, ZD100       | Zener, 15V, 5 percent                                                     | BZX384-C15       | NXP              | 2        |

| ZD4, ZD5         | Zener, 12V, 5 percent                                                     | BZX384-C12       | NXP              | 2        |

| ZD30             | Zener, 5.1V, 2.5 percent                                                  | DZ2J051M0L       | Panasonic        | 1        |

#### **BOM of adapter board** Table 7

| Designator | Value                              | Part number         | Manufacturer       | Quantity |

|------------|------------------------------------|---------------------|--------------------|----------|

| C1         | 100 n/50 V                         | C0805C104K5RACTU    | Kemet              | 1        |

| IC101      | CDM10V                             | CDM10V              | Infineon           | 1        |

| JP1        | Female, six-pin, 2.54 mm connector | BL5.36Z cut six-pin | Fischer Elektronik | 1        |

# controller

**Bill of Materials**

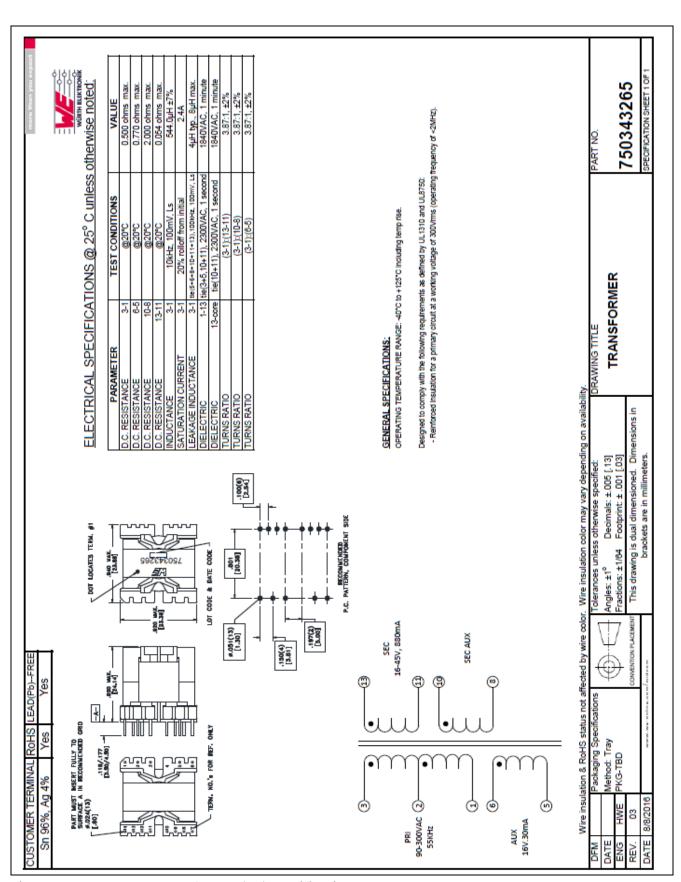

#### **Transformer specifications** 7.2

Figure 18 Flyback transformer (T1) specifications

**Configuration set-up and procedures**

## 8 Configuration set-up and procedures

## 8.1 XDPL8105 configuration

The tools needed for XDPL8105 parameter configurations are listed in Table 8.

Table 8 Tools needed for XDPL8105 parameter configurations

| Tool type | Tool name                          | Description                                         | Ordering/<br>download link                                                                                                                 | Ordering/download content                                                                                                                                                                                                                                                                            |

|-----------|------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hardware  | .dp Interface<br>Gen2              | .dp Interface<br>board                              | IF-BOARD.DP-GEN2                                                                                                                           | .dp Interface Gen2 x 1<br>USB cable x 1                                                                                                                                                                                                                                                              |

|           | .dp Vision                         | GUI for parameter configuration of all .dp products | .dp Vision                                                                                                                                 | Latest version of the .dp Vision installer (*.exe)                                                                                                                                                                                                                                                   |

| Software  | XDPL8105<br>parameters<br>csv file | XDPL8105<br>parameters<br>configuration file        | XDPL8105 40 W reference board homepage  Note: Please download the zipped package which contains the .dp Vision folder set- up file (*.msi) | Latest version of .dp Vision folder set-up file (*.msi), which installs the following:  XDPL8105 application note and the 40 W reference design parameter configuration file (*.csv), including images for the configuration file.  XDPL8105 design tool (*.xlsm) and design tool user guide (*.pdf) |

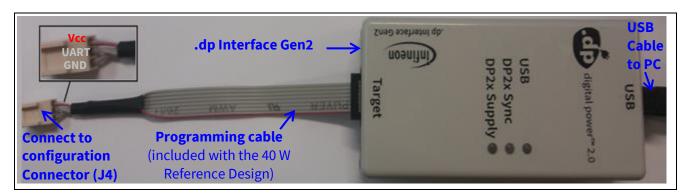

**Figure 19** shows the hardware set-up needed between the PC and the configuration connector (J4 of the 40 W reference design) for XDPL8105 parameter configuration.

Note: Please ensure the reference design board is not supplied with any voltage before connecting the programmable cable to the board configuration connector J4.

Figure 19 Hardware set-up for XDPL8105 configuration

### **Configuration set-up and procedures**

Please download the latest .dp Vision user manual from this <a href="https://homepage.link">homepage link</a> for detailed instructions on the installation and how to use this GUI for parameter configuration. Alternatively, the following simple guide is also available for quick and easy reference.

For the software tools installation, .dp Vision needs to be installed first before running the XDPL8105 .dp Vision folder set-up file (see **Table 8** for the download links). After setting up the hardware connection for XDPL8105 configuration (see **Figure 19**), please start the program by clicking the shortcut ".dp Vision" on the desktop.

Note:

During the program start-up, if the system shows there is a newer version of .dp Vision, please follow the procedure and update accordingly. Since the following screenshots were taken based on .dp Vision version 2.0.8.0, newer versions of .dp Vision might appear different.

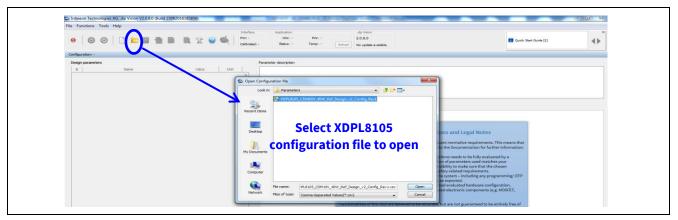

Then open the XDPL8105 parameter configuration file (\*.csv) from the installation folder of the XDPL8105 project add-on, as shown in **Figure 20**. The default installation folder is located at C:\Users\<Username>\Infineon Technologies AG\.dp vision\Parameters

Figure 20 Opening the XDPL8105 parameter configuration file (\*.csv) in .dp Vision

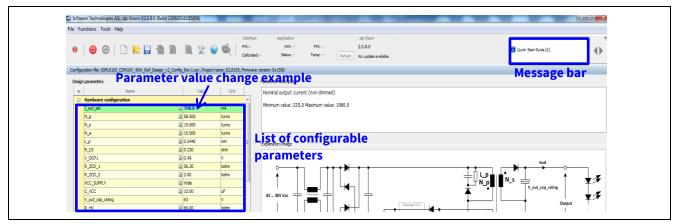

After opening the parameter csv file, a list of XDPL8105 configurable parameters will be shown (see the box on the left in **Figure 21**). If a parameter value is changed and no limit violation is found, the changed value itself will turn blue, like the example of changing *I\_out\_set* parameter from 880 mA to 700 mA in **Figure 21**. Otherwise, if an error is detected (e.g. exceeded min./max. value), the parameter value that caused the error will turn red and the message bar of .dp Vision (see the top right of **Figure 21**) will show an error message.

Note: The user is not allowed to test or burn the configuration if an error is detected.

Figure 21 Changing parameter values of XDPL8105 configuration file in .dp Vision

### **Configuration set-up and procedures**

There are two options available to configure the IC based on the list of parameter values shown in .dp Vision.

### - Burn configuration

As the XDPL8105 chip on the 40 W reference design PCB has already been permanently burned with a first full set of parameters in its OTP memory space, any parameter value change using this option is considered as parameter patching. The OTP memory space dedicated for patching or burning the parameter value change has a memory size of 77 words.

Each time the burn configuration function is executed, .dp Vision will detect if there is parameter value difference between the saved configuration file and the target XDPL8105. If a difference is detected, each burn configuration will consume a minimum of three words. However, the process will be aborted if it requires more memory space than is available on the target IC. In that case, the user will have to replace the XDPL8105 chip with a new one in order to burn the configuration. It is important to note that the new XDPL8105 chip from Infineon does not contain any parameters, so the user should burn a first full set of parameters using this function before any application testing.

Table 9 below shows the recommended procedures for using the burn configuration function in .dp Vision to burn a first full set of parameters or patch the parameters into the OTP memory.

Table 9 **Burn configuration procedures**

| able 3 | built configuration procedures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Step   | Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| I      | Open the configuration file using .dp Vision (see example in Figure 20).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| II     | If necessary, change any parameter value (see example in <b>Figure 21</b> ), then press [File] >> [Save] or [File] >> [Save as] to save the configuration file. Otherwise, proceed to step III.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Ш      | Ensure that the primary supply voltages (e.g. AC input) to the board are switched off or disconnected and the hardware connection for configuration is OK based on <b>Figure 19</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| IV     | Press $\begin{picture}(20,0) \put(0,0){\line(1,0){15}} $ |  |  |  |  |  |

| V      | Press to burn the configuration to the target XDPL8105.  After this step, you should see a pop-up window, which is similar to one of those below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|        | Patching parameter(s)  1 parameter(s) have been changed. This operation will consume 5 patch(es) out of 37 free patches. Do you want to proceed with burning procedure?  NOTE: Please be aware that this process is irreversible.  Cancel Proceed Show differences  OR  Burning new parameters set (Step 1 of 2)  Found 65 difference(s) between values from dp device (tp Value) and .dp Vison configuration set (leve Value). Difference(s):  ## Address Dp Value New Value 1. 0x8106 0x0000 0x456C 2. 0x8107 0x0000 0x6553 3. 0x8109 0x0000 0x6553 4. 0x8109 0x0000 0x3833 5. 0x810B 0x0000 0x0048 6. 0x810C 0x00000 0x0048 7. 0x810B 0x0000 0x0048 8. 0x810C 0x00000 0x0044 9. 0x810T 0x0000 0x0004  Do you want to proceed with burning procedure?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| VI     | Press "Proceed" or "Yes" to burn/patch the configuration.  After this step, a pop-up window should show that the burning/patching is successfully completed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| VII    | Press "OK" on the pop-up window, then disconnect the programming cable from the XDPL8105 configuration connector and test the application, if needed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

### **Configuration set-up and procedures**

## - Test configuration

This function will download the parameter values from the list in .dp Vision into the XDPL8105 RAM memory space. This will then be followed by an automatic IC start-up for application testing with the new configuration.

Unlike using the burn configuration, parameter configuration with this option is not permanent because the loaded RAM contents will be lost once the IC supply voltage is turned off, but the advantage of using this option is that it does not consume OTP memory space, thus there is no limit on the amount of parameter value changes. Please note that this option can only be used to test the application under non-dimming operation because the DIM/UART pin of the XDPL8105 cannot sense the dimming voltage while it is used for UART communication for the test configuration.

**Table 10** shows the recommended procedures for using test configuration functions in .dp Vision to load the new parameter values to the RAM and test the application with the new configuration.

Table 10 Test configuration procedures

| Step | Instruction                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Open the configuration file using .dp Vision (see example in Figure 20).                                                                                                                                                                                                                                                                                                                                                         |

| II   | Ensure that the primary supply voltage (e.g. AC input) to the board is switched off and the hardware connection for configuration is OK based on <b>Figure 19</b> .                                                                                                                                                                                                                                                              |

| III  | Press to supply power and establish a connection to the target XDPL8105. After this step, the XDPL8105 will be in configuration mode and the device status should change to .                                                                                                                                                                                                                                                    |

| IV   | Ensure the LED output is connected to the board and turn on the AC input (e.g. 230 V AC) to the board. After this step, the board does not start up because the XDPL8105 is still in configuration mode.                                                                                                                                                                                                                         |

| V    | Change the necessary parameter value (see example in <b>Figure 21</b> ) and press to test the new configuration with the target XDPL8105.                                                                                                                                                                                                                                                                                        |

| VI   | If the IC automatically starts up with the new configuration, you should see a pop-up window like the one shown below. Press "OK" to proceed.  Test Configuration Set  New configuration is successfully downloaded to RAM.                                                                                                                                                                                                      |

| VII  | To test another configuration change, repeat steps II to VI. If the following message box appears in between the steps, press "Yes" to proceed.  External supply error  External power supply connected. Please be aware that the external power supply can affect voltage set commands in the test procedure.  Otherwise, turn off the AC input and disconnect the programming cable from the XDPL8105 configuration connector. |

Note:

If any error is encountered between steps I and VII of either the burn configuration or test configuration procedures, please kindly refer to the message bar of .dp Vision for the error message. For more details, please see the .dp Vision user manual.

**Configuration set-up and procedures**

## 8.2 CDM10V configuration

CDM10V configuration requires only a hardware tool, as shown in **Table 11**.

Table 11 Tool needed for CDM10V configuration

| Tool type | Tool name           | Description        | Ordering link         | Ordering content             |

|-----------|---------------------|--------------------|-----------------------|------------------------------|

| Hardware  | COOLDIM_PRG_BOARD   | CDM10V programming | COOLDIM PRG BOARD     | CDM10V programming board x 1 |

| Haraware  | COOLDINI_I NO_DO/NO | board              | S COOLDING THE DOTALD | USB cable x 1                |

|           |                     | 1                  |                       | User manual x 1              |

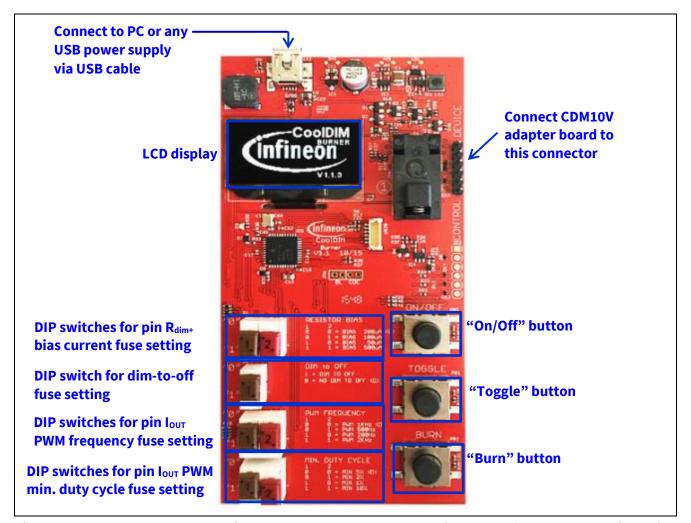

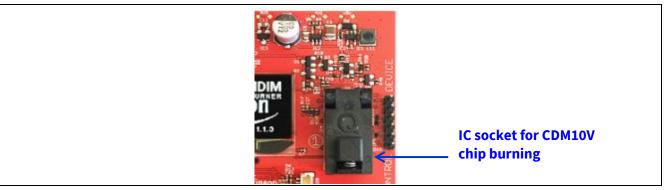

**Figure 22** shows the CDM10V programming board and the hardware connection set-up needed to configure the CDM10V adapter board in this reference design.

Note:

The CDM10V adapter board is normally attached to the 40 W reference design mainboard for the application testing, as shown in **Figure 1**. For CDM10V configuration, the CDM10V adapter board has to be unplugged from the reference design mainboard and connected to the CDM10V programming board connector, as shown in **Figure 22**.

Figure 22 CDM10V programming board and hardware connection set-up for CDM10V configuration

### **Configuration set-up and procedures**

Upon completing the hardware set-up and connection, please refer to **Table 12** below for the recommended procedures on CDM10V configuration or fuse burning.

Table 12 CDM10V configuration or fuse burning procedures

| Step | Instruction                                                                                                                                                                                                                                   |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

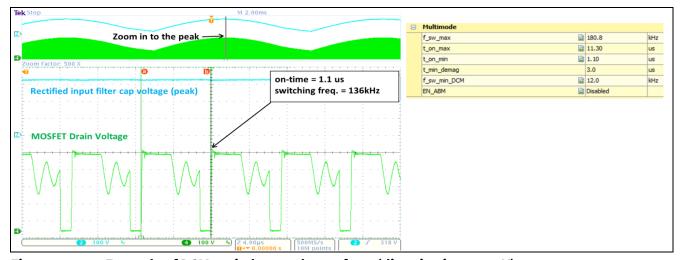

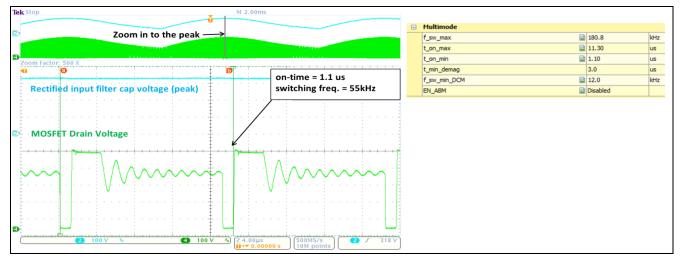

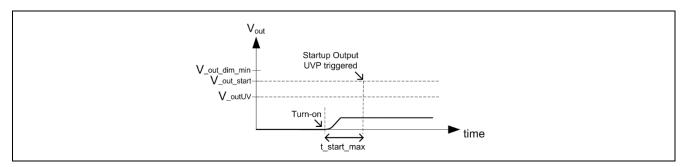

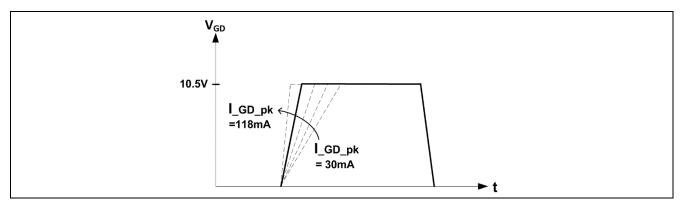

| I    | Press the "On/Off" button to supply voltage and establish connection to the chip.                                                                                                                                                             |