## **Next Generation Microcontroller Supply**

#### 1 Overview

#### **Features**

- High efficient next generation microcontroller power supply system

- Wide battery input voltage range < 4.5 V up to 45 V</li>

- Operating temperature range T<sub>i</sub> = -40°C to +150°C

- Pre-regulator for low all over power loss:

Integrated current mode Buck converter 5.5 V/2.5 A

- Post-regulators, e.g. for system and controller I/O supply:

- LDO1: 5 V ±2%, 800 mA current limit

- LDO2: 3.3 V ±2% or 2.6V ±2% (selectable output), 700 mA current limit

- Integrated linear regulator control circuit to supply controller cores:

- LDO3 control for an external NPN power stage:

- 1.5 V ±2% at TLE7368E

- 1.2 V ±2% at TLE7368-2E

- 1.3 V ±2% at TLE7368-3E

- Post-regulators for off board supply:

- 2 Tracking regulators following the main 5 V, 105 mA and 50 mA

- Stand-by regulator with lowest current consumption:

- Linear voltage regulator as stand-by supply for e.g.memory circuits

- Hardware selectable output voltages as 1.0 V or 2.6 V, 30 mA

- Independent battery input, separated from Buck regulator input

- Hardware controlled on/off logic

- Undervoltage detection:

- Undervoltage reset circuits with adjustable reset delay time at power up

1

- Undervoltage monitoring circuit on stand-by supply

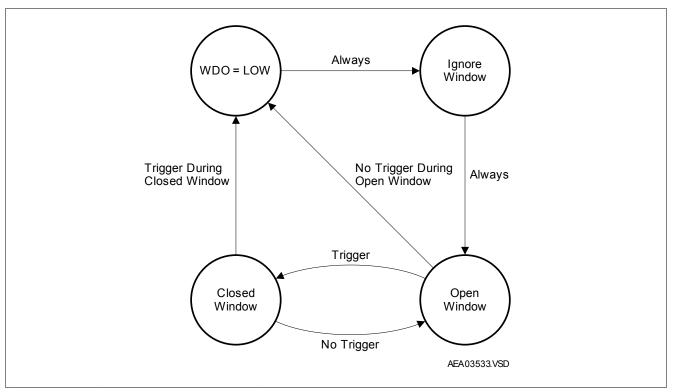

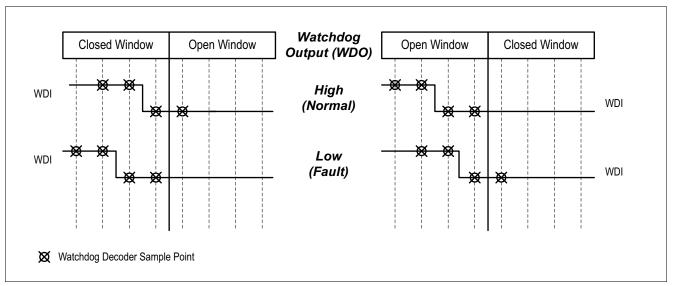

- Window watchdog circuit

- Overcurrent protection on all regulators

- Power sequencing on controller supplies

- Overtemperature shutdown

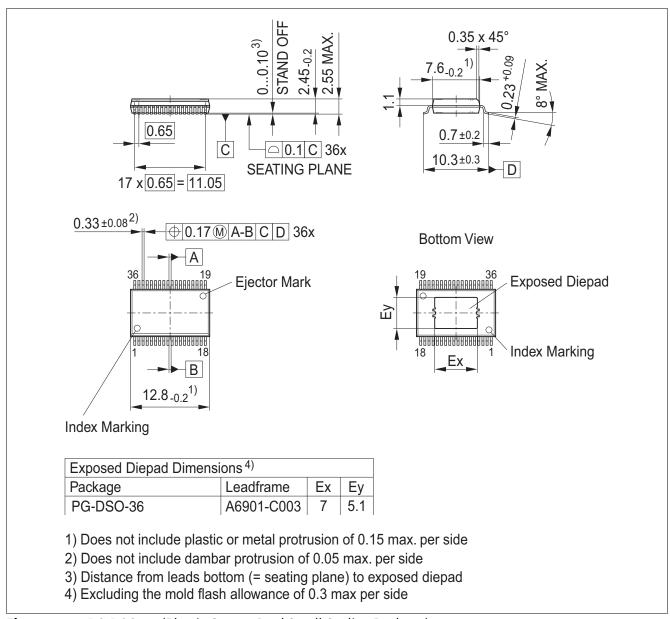

- · Package: Small exposed pad PG-DSO-36

- Green Product (RoHS compliant)

#### **Next Generation Microcontroller Supply**

#### Overview

#### **Potential application**

Microcontroller supply

#### **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100.

#### **Description**

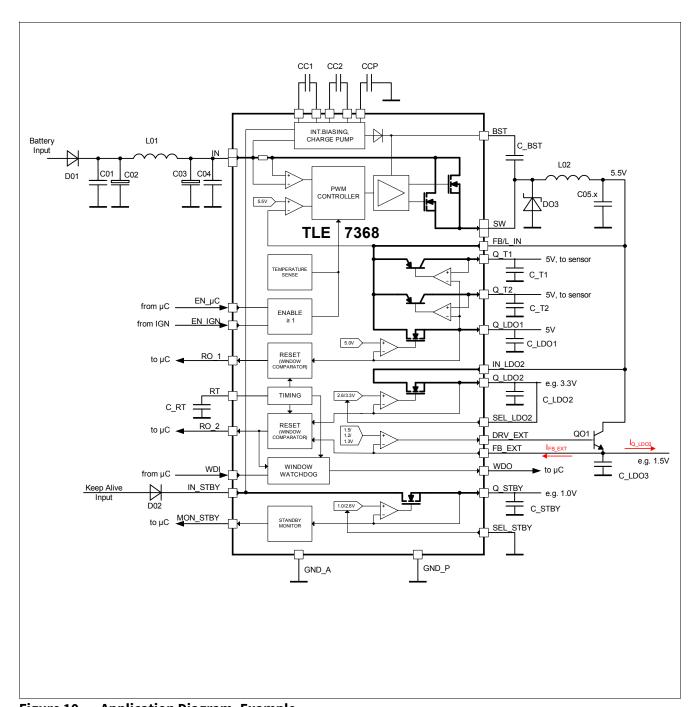

The **TLE7368** device is a multifunctional power supply circuit especially designed for Automotive powertrain systems using a standard 12 V battery. The device is intended to supply and monitor next generation 32-bit microcontroller families (13  $\mu$ m lithography) where voltage levels such as 5 V, 3.3 V or 1.5/1.2/1.3 V are required.

The regulator follows the concept of its predecessor TLE6368/SONIC, where the output of a pre-regulator feeds the inputs of the micro's linear supplies. In detail, the **TLE7368** cascades a Buck converter with linear regulators and voltage followers to achieve lowest power dissipation. This configuration allows to power the application even at high ambient temperatures.

The step-down converter delivers a pre-regulated voltage of 5.5 V with a minimum peak current capability of 2.5 A.

Supplied by this step down converter two low drop linear post-regulators offer 5 V and 3.3 V (2.6 V) with high accuracy. The current capability of the regulators is 800 mA and 700 mA. The 3.3 V (2.6 V) linear regulator does have its own input allowing to insert a dropper from the Buck output to reduce the on chip power dissipation if necessary. For the same reason, reduction of on chip power dissipation, the core supply (1.5 V, 1.2 V or 1.3 V) follows the concept of integrated control circuit with external power stage.

Implementing the on board and microcontroller supplies in this way described, allows operation even at high ambient temperatures.

The regulator system contains the so called power sequencing function which provides a controlled power up sequence of the three output voltages.

In addition to the main regulators the inputs of two voltage trackers are connected to the 5.5 V Buck converter output voltage. Their protected outputs follow the main 5 V linear regulator with high accuracy and are able to drive loads of 50 mA and 105 mA.

To monitor the output voltage levels of each of the linear regulators two independent undervoltage detection circuits are available. They can be used to implement the reset or an interrupt function.

For energy saving reasons, e.g. while the motor is turned off, the **TLE7368** offers a stand-by mode. The standby mode can be enabled and disabled either by battery or the microcontroller. In this stand-by mode just the stand-by regulator remains active and the current drawn from battery is reduced to a minimum for extended battery lifetime. A selection pin allows to configure the output voltages of the stand-by regulator to the application's needs. The input of the stand-by regulator is separated from the high power input of the pre-/post-regulator system.

The **TLE7368** is based on Infineon's Power technology SPT<sup>™</sup> which allows bipolar, CMOS and power DMOS circuitry to be integrated on the same monolithic chip/circuitry.

| Туре       | Package   | Marking     |

|------------|-----------|-------------|

| TLE7368E   | PG-DSO-36 | TLE7368 E   |

| TLE7368-2E | PG-DSO-36 | TLE7368-2 E |

| TLE7368-3E | PG-DSO-36 | TLE7368-3 E |

## **Next Generation Microcontroller Supply**

# **Table of Contents**

| 1     | Overview                                              | . 1  |

|-------|-------------------------------------------------------|------|

|       | Table of Contents                                     | 3    |

| 2     | Block Diagram                                         | . 4  |

| 3     | Pin Configuration                                     |      |

| 3.1   | Pin Assignment                                        |      |

| 3.2   | Pin Definitions and Functions TLE7368E                |      |

| 4     | General Product Characteristics                       | 8    |

| 4.1   | Absolute Maximum Ratings                              | 8    |

| 4.2   | Functional Range                                      | 11   |

| 4.3   | Thermal Resistance                                    | 12   |

| 4.4   | Electrical Characteristics                            | . 12 |

| 5     | Detailed Internal Circuits Description                | 23   |

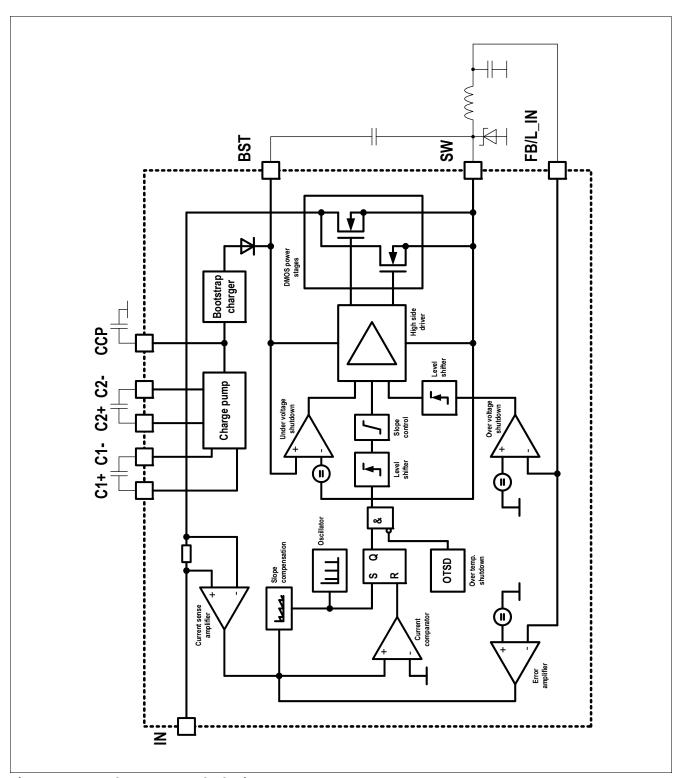

| 5.1   | Buck Regulator                                        |      |

| 5.1.1 | Buck Regulator Control Scheme                         | 23   |

| 5.1.2 | High Side Driver Supply and 100% Duty Cycle Operation | 23   |

| 5.1.3 | Electromagnetic Emission Reduction                    | 25   |

| 5.1.4 | Charge Pump                                           | 25   |

| 5.1.5 | Buck Converter Protection Circuits                    | 25   |

| 5.2   | Linear Regulators                                     | 25   |

| 5.3   | Voltage Tracking Regulators                           | . 26 |

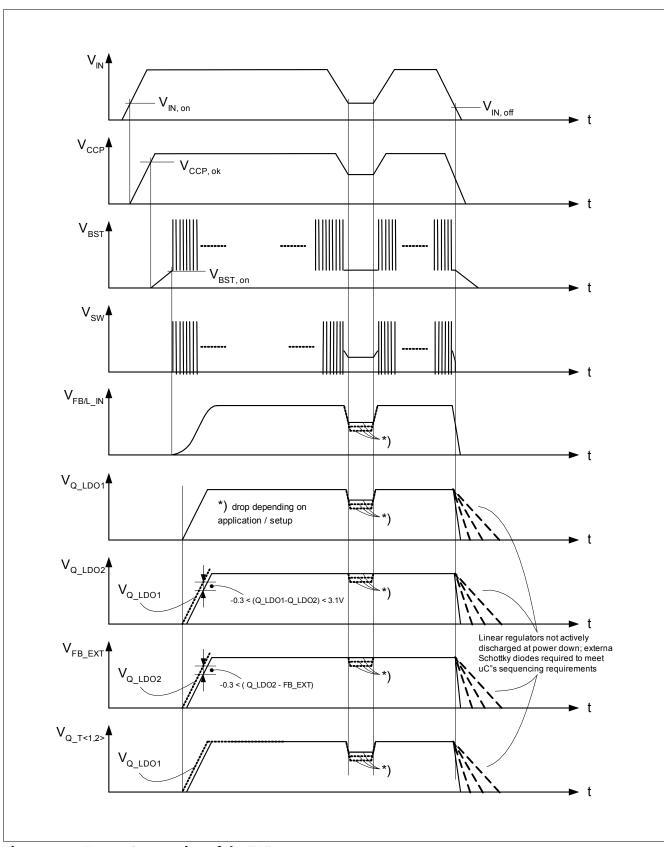

| 5.4   | Power Up and Power Down Sequencing                    | 26   |

| 5.5   | Stand-by Regulator                                    | . 28 |

| 5.6   | Overtemperature Protection                            |      |

| 5.7   | Device Enable Function                                |      |

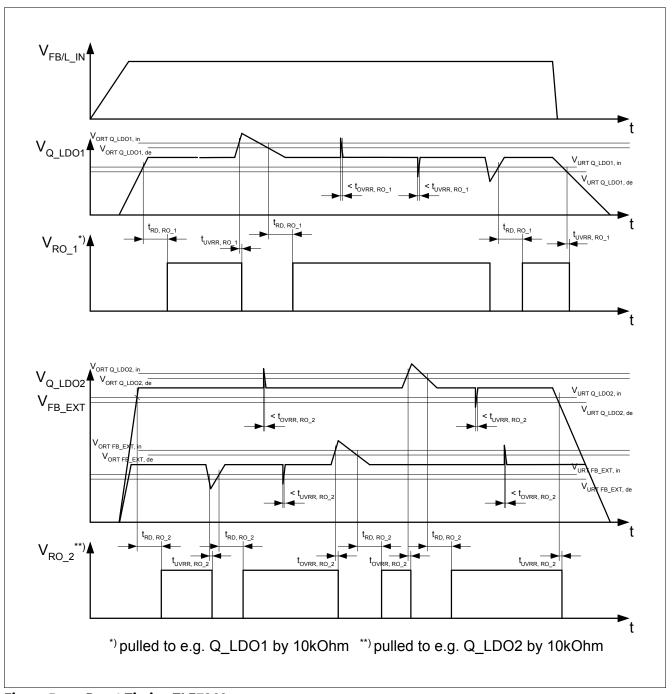

| 5.8   | Reset Function                                        |      |

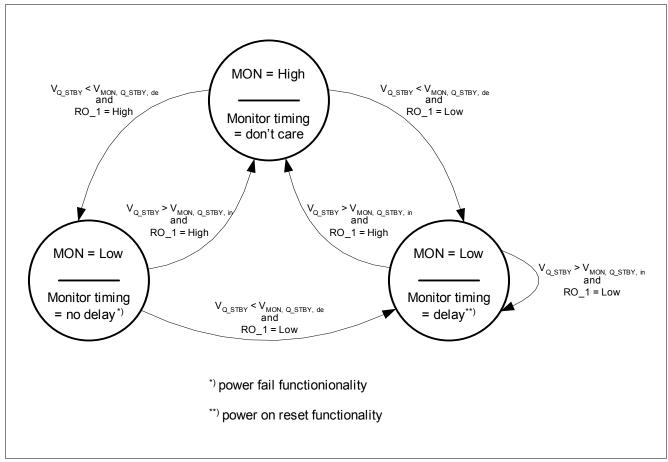

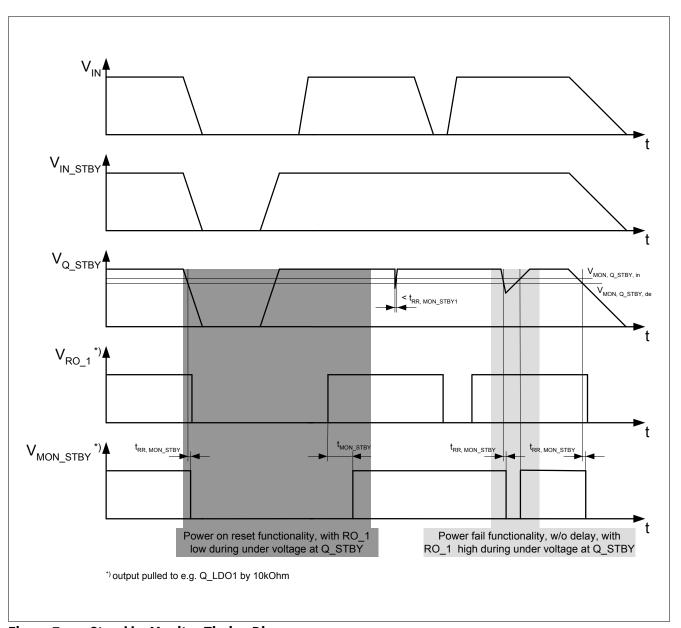

| 5.9   | Monitoring Circuit                                    |      |

| 5.10  | Watchdog Circuit                                      | 32   |

| 6     | Application Information                               | 35   |

| 6.1   | Choosing Components for the Buck Regulator            | . 36 |

| 6.2   | Setting up LDO1, LDO2                                 | 36   |

| 6.3   | Setting up of LDO3                                    | 37   |

| 6.4   | Setting up the Stand-by Regulator                     |      |

| 6.4.1 | Stand-by Regulator's Output Voltage Configuration     | 37   |

| 7     | Package Outlines                                      | 38   |

| 8     | Revision History                                      | 39   |

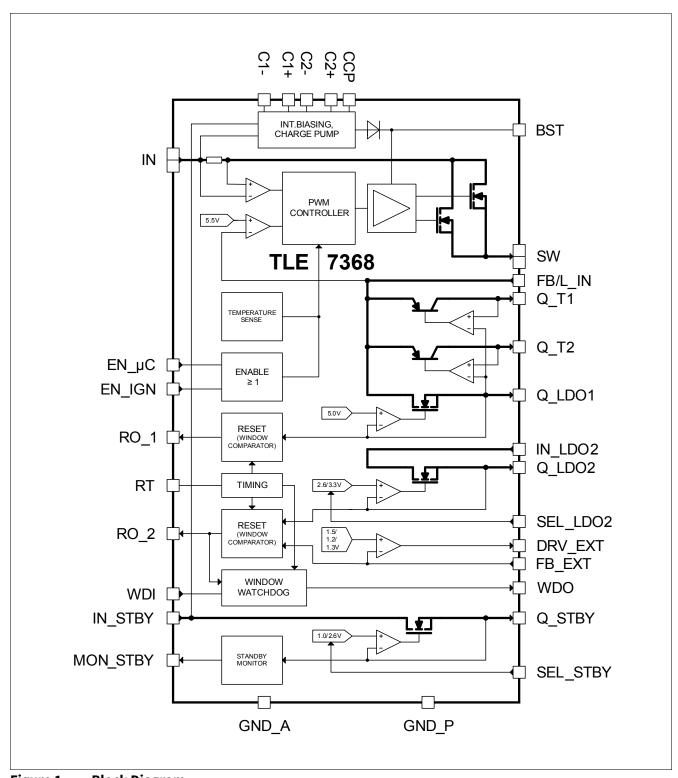

**Block Diagram**

## 2 Block Diagram

Figure 1 Block Diagram

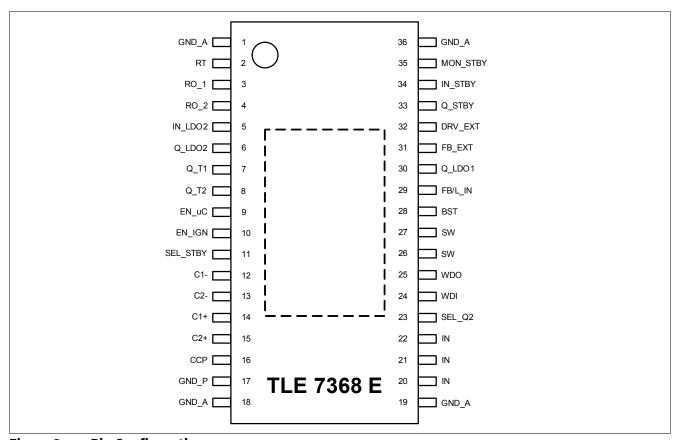

**Pin Configuration**

# 3 Pin Configuration

## 3.1 Pin Assignment

Figure 2 Pin Configuration

### 3.2 Pin Definitions and Functions TLE7368E

| Pin | Symbol  | Function                                                                           |

|-----|---------|------------------------------------------------------------------------------------|

| 1   | GND_A   | Analog ground connection;                                                          |

|     |         | Connect to heatslug resp. exposed pad.                                             |

| 2   | RT      | Reset and watchdog timing pin;                                                     |

|     |         | Connect a ceramic capacitor to GND to determine the time base for the reset        |

|     |         | delay circuits and the watchdog cycle time                                         |

| 3   | RO_1    | Reset output Q_LDO1;                                                               |

|     |         | Open drain output, active low.                                                     |

|     |         | Connect an external 10 k $\Omega$ pull-up resistor to microcontroller I/O voltage. |

| 4   | RO_2    | Reset output Q_LDO2 and FB_EXT;                                                    |

|     |         | Open drain output, active low.                                                     |

|     |         | Connect an external 10 $k\Omega$ pull-up resistor to microcontroller I/O voltage   |

| 5   | IN_LDO2 | LDO2 input;                                                                        |

|     |         | Connect this pin straight to the Buck converter output or add a dropper in         |

|     |         | between to reduce power dissipation on the chip.                                   |

## **Next Generation Microcontroller Supply**

## **Pin Configuration**

| Pin        | Symbol   | Function                                                                                                                                                                                                                                                                |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6          | Q_LDO2   | <b>Voltage regulator 2 output;</b> 3.3 V or 2.6 V, depending on the state of SEL_LDO2. Block to GND with capacitor close to the IC pins for stable regulator operation; selection of capacitor $C_{\rm Q\_LDO2}$ according to <b>Chapter 4.4</b> and <b>Chapter 6</b> . |

| 7          | Q_T1     | <b>Tracking regulator 1 output;</b> Block to GND with capacitor close to the IC pins for stable regulator operation; selection of capacitor $C_{Q_{-T1}}$ according to <b>Chapter 4.4</b> and <b>Chapter 6</b> .                                                        |

| 8          | Q_T2     | <b>Tracking regulator 2 output;</b> Block to GND with capacitor close to the IC pins for stable regulator operation; selection of capacitor $C_{Q_T2}$ according to <b>Chapter 4.4</b> and <b>Chapter 6</b> .                                                           |

| 9          | EN_uC    | Enable input microcontroller;  High level enables / low level disables the IC except the stand-by regulators; Integrated pull-down resistor                                                                                                                             |

| 10         | EN_IGN   | Enable input ignition line; High level enables / low level disables the IC except the stand-by regulators; Integrated pull-down resistor                                                                                                                                |

| 11         | SEL_STBY | Selection input for stand-by regulator; Connect to GND to select 2.6 V output voltage for Q_STBY; Connect straight to Q_STBY to select 1.0 V output voltage for Q_STBY                                                                                                  |

| 12         | C1-      | Charge pump negative #1;<br>Connect a ceramic capacitor 100 nF, to C1+                                                                                                                                                                                                  |

| 13         | C2-      | Charge pump negative #2;<br>Connect a ceramic capacitor 100 nF, toC2+                                                                                                                                                                                                   |

| 14         | C1+      | Charge pump positive #1; Connect a ceramic capacitor 100 nF, to C1-                                                                                                                                                                                                     |

| 15         | C2+      | Charge pump positive #2; Connect a ceramic capacitor 100 nF, to C2-                                                                                                                                                                                                     |

| 16         | ССР      | Charge pump output; Connect a ceramic capacitor, 220 nF, to GND; Used for internal IC supply, do not use for other circuitry.                                                                                                                                           |

| 17         | GND_P    | Power ground; Exclusive GND connection of charge pump; Connect this pin to the power ground star point on the PCB.                                                                                                                                                      |

| 18, 19     | GND_A    | Analog ground connection; Connect to exposed pad.                                                                                                                                                                                                                       |

| 20, 21, 22 | IN       | Buck regulator input; Connect to a pi-filter (or if not used to battery) with short lines; connect filter capacitors in any case with short lines; connect a small ceramic directly at the pin; For details refer to Chapter 6. Interconnect the pins.                  |

| 23         | SEL_LDO2 | Selection input LDO2; Connect to GND to select 2.6 V output voltage for LDO2; Connect straight to Q_LDO2 to select 3.3 V output voltage for LDO2.                                                                                                                       |

## **Next Generation Microcontroller Supply**

## **Pin Configuration**

| Pin    | Symbol   | Function                                                                                                                                                                             |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24     | WDI      | Window Watchdog input;                                                                                                                                                               |

|        |          | Apply a watchdog trigger signal to this pin                                                                                                                                          |

| 25     | WDO      | Window Watchdog output;                                                                                                                                                              |

|        |          | Open drain output, active low,                                                                                                                                                       |

|        |          | connect external 10 kΩ pull-up resistor to microcontroller I/O voltage                                                                                                               |

| 26, 27 | SW       | Buck power stage's output;                                                                                                                                                           |

|        |          | Connect both pins directly, on short lines, to the Buck converter circuit, i.e. the                                                                                                  |

|        |          | catch diode and the Buck inductance                                                                                                                                                  |

| 28     | BST      | Bootstrap driver supply input;                                                                                                                                                       |

|        |          | Connect the buck power stage's driver supply capacitor to the SW pins; For capacitor selection please refer to <b>Chapter 6</b> .                                                    |

| 29     | FB/L_IN  | <b>Buck converter feedback input plus input for LDO1 and trackers;</b> Connect the                                                                                                   |

|        |          | output of the buck converter circuit with short lines to these pins; For Buck output                                                                                                 |

|        |          | capacitor selection please refer to <b>Chapter 6</b> .                                                                                                                               |

| 30     | Q_LDO1   | Voltage regulator 1 output;                                                                                                                                                          |

|        |          | 5 V output; Block to GND with capacitor close to the IC pins for stable regulator                                                                                                    |

|        |          | operation; Selection of capacitor $C_{Q\_LDO1}$ according to <b>Chapter 4.4</b> and                                                                                                  |

|        |          | Chapter 6.                                                                                                                                                                           |

| 31     | FB_EXT   | External regulator feedback input;                                                                                                                                                   |

|        |          | Feedback input of control loop for the external power stage regulator. Connect to                                                                                                    |

|        |          | the emitter of the regulating transistor; Block to GND with capacitor close to the IC pins for stable regulator operation; Selection of capacitor $C_{\text{O }FB EXT}$ according to |

|        |          | <b>Chapter 4.4</b> and <b>Chapter 6</b> .                                                                                                                                            |

| 32     | DRV_EXT  | Bipolar power stage driver output;                                                                                                                                                   |

| 32     | DIV_EXT  | Connect the base of an external NPN transistor directly to this pin; Regarding                                                                                                       |

|        |          | choice of the external power stage refer to <b>Chapter 6</b> .                                                                                                                       |

| 33     | Q_STBY   | Stand-by regulator output;                                                                                                                                                           |

|        |          | Output voltage depending on the state of SEL_STBY; Block to GND with capacitor                                                                                                       |

|        |          | close to the IC pins for stable regulator operation; Selection of capacitor $C_{\text{O\_STBY}}$                                                                                     |

|        |          | according to <b>Chapter 4.4</b> and <b>Chapter 6</b> .                                                                                                                               |

| 34     | IN_STBY  | Input to stand-by regulator;                                                                                                                                                         |

|        |          | Always connect the reverse polarity protected battery line to this pin; Input to all                                                                                                 |

|        |          | IC internal biasing circuits;                                                                                                                                                        |

|        |          | Block to GND directly at the IC with ceramic capacitor; For proper choice of input                                                                                                   |

|        |          | capacitors please refer to <b>Chapter 6</b> .                                                                                                                                        |

| 35     | MON_STBY | Monitoring output for stand-by regulator; power fail active low output with                                                                                                          |

|        |          | special timing, open drain, connect external pull-up resistor.                                                                                                                       |

| 36     | GND_A    | Analog ground connection;                                                                                                                                                            |

|        |          | Connect to exposed pad.                                                                                                                                                              |

## **Next Generation Microcontroller Supply**

#### **General Product Characteristics**

## 4 General Product Characteristics

## 4.1 Absolute Maximum Ratings

Table 1 Absolute Maximum Ratings<sup>1)</sup>,  $T_i = -40$ °C to +150°C; all voltages with respect to ground.

| Parameter            | Symbol                       |                       | Values |      |    | Note or                 | Number   |

|----------------------|------------------------------|-----------------------|--------|------|----|-------------------------|----------|

|                      |                              | Min.                  | Тур.   | Max. |    | <b>Test Condition</b>   |          |

| Stand-by Regulator I | Input IN_STBY                |                       | ı      |      | 1  |                         | - 11     |

| Voltage              | $V_{IN\_STBY}$               | -0.3                  | _      | 45   | V  | _                       | P_4.1.1  |

| Current              | I <sub>IN_STBY</sub>         | _                     | -      | _    | Α  | Limited internally      | P_4.1.2  |

| Selection Input SEL_ |                              |                       | ı      |      |    |                         | - 1      |

| Voltage              | $V_{\rm SEL\_STBY}$          | -0.3                  | _      | 5.5  | V  | _                       | P_4.1.3  |

| Voltage              | $V_{\rm SEL\_STBY}$          | -0.3                  | -      | 6.2  | ٧  | t < 10 s <sup>2)</sup>  | P_4.1.4  |

| Current              | I <sub>SEL_STBY</sub>        | _                     | -      | _    | Α  | Limited internally      | P_4.1.5  |

| Buck Regulator Inpu  |                              | <u>'</u>              | •      | ,    | -  |                         | <u>"</u> |

| Voltage              | V <sub>IN</sub>              | V <sub>SW</sub> - 0.3 | _      | 45   | V  | _                       | P_4.1.6  |

| Voltage              | V <sub>IN</sub>              | -0.3                  | -      | 45   | V  | _                       | P_4.1.7  |

| Current              | I <sub>IN</sub>              | _                     | _      | _    | Α  | Limited internally      | P_4.1.8  |

| Watchdog Input WDI   | <u> </u>                     |                       | ı      |      |    |                         | - 1      |

| Voltage              | $V_{\mathrm{WDI}}$           | -0.3                  | -      | 5.5  | V  | -                       | P_4.1.9  |

| Voltage              | $V_{WDI}$                    | -0.3                  | _      | 6.2  | V  | $t < 10 \text{ s}^{2)}$ | P_4.1.10 |

| Current              | I <sub>WDI</sub>             | _                     | _      | _    | Α  | Limited internally      | P_4.1.11 |

| Watchdog Output WI   |                              |                       |        |      |    |                         | - 1      |

| Voltage              | $V_{ m WDO}$                 | -0.3                  | _      | 5.5  | V  | _                       | P_4.1.12 |

| Voltage              | $V_{ m WDO}$                 | -0.3                  | _      | 6.2  | ٧  | $t < 10 \text{ s}^{2)}$ | P_4.1.13 |

| Current              | $I_{\mathrm{WDO}}$           | _                     | _      | _    | А  | Limited internally      | P_4.1.14 |

| Charge Pump Positiv  |                              | <u>'</u>              | •      | ,    | -  |                         | <u>"</u> |

| Voltage              | V <sub>C&lt;1+, 2+&gt;</sub> | -0.3                  | _      | 18   | V  | _                       | P_4.1.15 |

| Current              | I <sub>C&lt;1+, 2+&gt;</sub> | _                     | _      | _    | mA | -                       | P_4.1.16 |

| Charge Pump Negati   |                              |                       | •      |      |    |                         |          |

| Voltage              | V <sub>C&lt;1-, 2-&gt;</sub> | -0.3                  | _      | 5.5  | V  | _                       | P_4.1.17 |

| Current              | I <sub>C&lt;1-, 2-&gt;</sub> | _                     | _      | _    | mA | -                       | P_4.1.18 |

| Charge Pump Output   |                              | <u>'</u>              | •      | ,    | -  |                         | <u>"</u> |

| Voltage              | $V_{\rm CCP}$                | -0.3                  | _      | 18   | V  | _                       | P_4.1.19 |

| Current              | I <sub>CCP</sub>             | _                     | -      | -    | mA | -                       | P_4.1.20 |

| Reset Output RO_1    | 1                            |                       | 1      | 1    | l  | 1                       | 1        |

| Voltage              | $V_{\mathrm{RO}\_1}$         | -0.3                  | -      | 5.5  | V  | _                       | P_4.1.21 |

| Voltage              | $V_{RO\_1}$                  | -0.3                  | _      | 6.2  | V  | t < 10 s <sup>2)</sup>  | P_4.1.22 |

## **Next Generation Microcontroller Supply**

#### **General Product Characteristics**

Absolute Maximum Ratings<sup>1)</sup>,  $T_j$  = -40°C to +150°C; all voltages with respect to ground. Table 1

| Parameter            | Symbol                       |      | Value | Values                      |     | Note or                             | Number   |

|----------------------|------------------------------|------|-------|-----------------------------|-----|-------------------------------------|----------|

|                      |                              | Min. | Тур.  | Max.                        |     | <b>Test Condition</b>               |          |

| Current              | I <sub>RO_1</sub>            | _    | _     | -                           | Α   | Limited internally                  | P_4.1.23 |

| Reset Output RO_2    |                              | *    |       |                             | *   |                                     | -        |

| Voltage              | $V_{\mathrm{RO}_2}$          | -0.3 | _     | 5.5                         | V   | _                                   | P_4.1.24 |

| Voltage              | $V_{RO_2}$                   | -0.3 | _     | 6.2                         | ٧   | t < 10 s <sup>2)</sup>              | P_4.1.25 |

| Current              | I <sub>RO_2</sub>            | _    | _     | _                           | Α   | Limited internally                  | P_4.1.26 |

| Reset Timing RT      |                              |      |       |                             |     |                                     |          |

| Voltage              | $V_{RT}$                     | -0.3 | _     | 5.5                         | V   | _                                   | P_4.1.27 |

| Voltage              | $V_{RT}$                     | -0.3 | _     | 6.2                         | ٧   | t < 10 s <sup>2)</sup>              | P_4.1.28 |

| Current              | I <sub>RT</sub>              | -    | _     | -                           | Α   | Limited internally                  | P_4.1.29 |

| Tracking Regulator   | Outputs Q_T<12>              |      | ı     | 1                           |     |                                     |          |

| Voltage              | V <sub>Q_T&lt;12&gt;</sub>   | -5   | _     | 40                          | ٧   | $V_{\text{FB/L_IN}} = 5.5 \text{V}$ | P_4.1.30 |

| Voltage              | V <sub>Q_T&lt;12&gt;</sub>   | -5   | _     | 35                          | ٧   | off mode;                           | P_4.1.31 |

|                      | -                            |      |       |                             |     | $V_{\text{FB/L\_IN}} = 0V$          |          |

| Current              | I <sub>Q_T&lt;12&gt;</sub>   | _    | _     | _                           | Α   | Limited internally                  | P_4.1.32 |

| Enable Ignition EN_I |                              | ı    |       |                             | T   |                                     |          |

| Voltage              | $V_{EN\_IGN}$                | -0.3 | _     | 45                          | V   | -                                   | P_4.1.33 |

| Current              | I <sub>EN_IGN</sub>          | _    | _     | _                           | mA  | _                                   | P_4.1.34 |

| Enable Micro EN_uC   |                              |      |       |                             |     |                                     |          |

| Voltage              | $V_{EN\_uC}$                 | -0.3 | _     | 5.5                         | ٧   | _                                   | P_4.1.35 |

| Voltage              | V <sub>EN_uC</sub>           | -0.3 | _     | 6.2                         | V   | $t < 10 \text{ s}^{2)}$             | P_4.1.36 |

| Current              | I <sub>EN_uC</sub>           | -5   | _     | 5                           | mA  | _                                   | P_4.1.37 |

| Voltage Regulator O  | utputs Q_LDO<1               | 2>   |       |                             |     |                                     |          |

| Voltage              | $V_{\mathrm{Q\_LDO1}}$       | -0.3 | _     | $V_{\text{FB/L\_IN}}$ + 0.3 | V   | -                                   | P_4.1.38 |

| Voltage              | $V_{\mathrm{Q\_LDO2}}$       | -0.3 | _     | V <sub>IN_LDO2</sub> + 0.3  | V   | -                                   | P_4.1.39 |

| Voltage              | V <sub>Q_LDO&lt;12&gt;</sub> | -0.3 | _     | 5.5                         | ٧   | _                                   | P_4.1.40 |

| Voltage              | V <sub>Q_LDO&lt;12&gt;</sub> | -0.3 | _     | 6.2                         | ٧   | $t < 10 \text{ s}^{2)}$             | P_4.1.41 |

| Current              | I <sub>Q_LDO&lt;12&gt;</sub> | _    | _     | _                           | Α   | Limited internally                  | P_4.1.42 |

| Selection Input SEL  | •                            |      |       | 1                           | II. | 1                                   |          |

| Voltage              | V <sub>SEL_LDO2</sub>        | -0.3 | _     | 5.5                         | ٧   | _                                   | P_4.1.43 |

| Voltage              | V <sub>SEL_LDO2</sub>        | -0.3 | _     | 6.2                         | ٧   | $t < 10 \text{ s}^{2)}$             | P_4.1.44 |

| Current              | I <sub>SEL_LDO2</sub>        | _    | _     | _                           | Α   | Limited internally                  | P_4.1.45 |

| External Driver Out  | <u> </u>                     | 1    |       |                             | 1   | ·                                   | <u>I</u> |

| Voltage              | $V_{DRV\_EXT}$               | -0.3 | _     | 5.5                         | ٧   | _                                   | P_4.1.46 |

| Voltage              | V <sub>DRV_EXT</sub>         | -0.3 | _     | 6.2                         | ٧   | t < 10 s <sup>2)</sup>              | P_4.1.47 |

| Current              | I <sub>DRV_EXT</sub>         | _    | _     | _                           | Α   | Limited internally                  | P_4.1.48 |

|                      | DKV_EXI                      | 1    |       |                             | 1   | 1                                   |          |

## **Next Generation Microcontroller Supply**

Table 1 Absolute Maximum Ratings<sup>1)</sup>,  $T_j = -40$ °C to +150°C; all voltages with respect to ground.

| Parameter                       | Symbol                 | <b>5</b> , , ,               | Value | ·s                    | Unit | Note or                                 | Number   |

|---------------------------------|------------------------|------------------------------|-------|-----------------------|------|-----------------------------------------|----------|

|                                 |                        | Min.                         | Тур.  | Max.                  |      | <b>Test Condition</b>                   |          |

| External Regulator Feedb        | ack Input FB           | _EXT                         |       |                       |      | -                                       | 1        |

| Voltage                         | $V_{\rm FB\_EXT}$      | -0.3                         | -     | 5.5                   | ٧    | _                                       | P_4.1.49 |

| Voltage                         | $V_{FB\_EXT}$          | -0.3                         | -     | 6.2                   | ٧    | $t < 10 \text{ s}^{2)}$                 | P_4.1.50 |

| Current                         | I <sub>FB_EXT</sub>    | _                            | -     | -                     | Α    | Limited internally                      | P_4.1.51 |

| Feedback and Post-Regul         |                        | B/L_IN                       | 1     |                       |      |                                         |          |

| Voltage                         | V <sub>FB/L_IN</sub>   | V <sub>Q_LDO1</sub> -<br>0.3 | _     | 18                    | V    | _                                       | P_4.1.52 |

| Voltage                         | $V_{\rm FB/L\_IN}$     | -0.3                         | _     | 18                    | ٧    | -                                       | P_4.1.53 |

| Current                         | I <sub>FB/L_IN</sub>   | _                            | _     | _                     | Α    | Limited internally                      | P_4.1.54 |

| Linear Regulator 2 Input        |                        |                              |       |                       | -    |                                         | 1        |

| Voltage                         | $V_{\rm IN\_LDO2}$     | V <sub>Q_LDO2</sub> -<br>0.3 | -     | 18                    | V    | -                                       | P_4.1.55 |

| Voltage                         | $V_{\rm IN\_LDO2}$     | -0.3                         | _     | 18                    | ٧    | -                                       | P_4.1.56 |

| Current                         | I <sub>IN_LDO2</sub>   | _                            | _     | _                     | Α    | Limited internally                      | P_4.1.57 |

| Bootstrap Supply BST            |                        | -                            | +     |                       | -    | -                                       | -        |

| Voltage                         | $V_{BST}$              | V <sub>SW</sub> - 0.3        | _     | V <sub>SW</sub> + 5.5 | ٧    | _                                       | P_4.1.58 |

| Voltage                         | $V_{BST}$              | -0.3                         | _     | 51                    | ٧    | -                                       | P_4.1.59 |

| Current                         | I <sub>BST</sub>       | _                            | -     | -                     | Α    | Limited internally                      | P_4.1.60 |

| Buck Power Stage SW             |                        |                              | J     | 1                     | T.   |                                         |          |

| Voltage                         | $V_{\sf SW}$           | -2                           | -     | $V_{IN} + 0.3$        | V    | _                                       | P_4.1.61 |

| Voltage                         | $V_{\sf SW}$           | -2                           | _     | 45                    | ٧    | -                                       | P_4.1.62 |

| Current                         | I <sub>SW</sub>        | _                            | -     | -                     | Α    | Limited internally                      | P_4.1.63 |

| Stand-by Regulator Outp         | ·                      |                              | J.    | 1                     |      |                                         |          |

| Voltage                         | $V_{\rm Q\_STBY}$      | -0.3                         | -     | 5.5                   | V    | _                                       | P_4.1.64 |

| Voltage                         | $V_{\rm Q\_STBY}$      | -0.3                         | _     | 6.2                   | ٧    | $t < 10 \text{ s}^{2)}$                 | P_4.1.65 |

| Current                         | $I_{Q\_STBY}$          | _                            | -     | -                     | Α    | Limited internally                      | P_4.1.66 |

| Monitoring Output MON_          |                        |                              | 1     |                       |      |                                         |          |

| Voltage                         | $V_{\text{MON\_STBY}}$ | -0.3                         | -     | 5.5                   | ٧    | _                                       | P_4.1.67 |

| Voltage                         | V <sub>MON_STBY</sub>  | -0.3                         | -     | 6.2                   | ٧    | t < 10 s <sup>2)</sup>                  | P_4.1.68 |

| Current                         | I <sub>MON_STBY</sub>  | _                            | -     | -                     | Α    | Limited internally                      | P_4.1.69 |

| Temperatures                    | <u> </u>               |                              | 1     |                       |      |                                         |          |

| Junction Temperature            | T <sub>j</sub>         | -40                          | _     | 150                   | °C   | _                                       | P_4.1.70 |

| Storage Temperature             | $T_{\rm stg}$          | -50                          | _     | 150                   | °C   | _                                       | P_4.1.71 |

| ESD-Protection (Human E         | Body Model)            |                              | 1     |                       | 1    | •                                       |          |

| Electrostatic discharge voltage | V <sub>ESD</sub>       | -2                           | _     | 2                     | kV   | Human Body Model<br>(HBM) <sup>3)</sup> | P_4.1.72 |

#### **Next Generation Microcontroller Supply**

#### **General Product Characteristics**

Table 1 Absolute Maximum Ratings<sup>1)</sup>,  $T_i = -40$ °C to +150°C; all voltages with respect to ground.

| Parameter                                           | Symbol Va        |      |      | /alues |   | Note or                                     | Number   |

|-----------------------------------------------------|------------------|------|------|--------|---|---------------------------------------------|----------|

|                                                     |                  | Min. | Тур. | Max.   |   | <b>Test Condition</b>                       |          |

| ESD-Protection (Charged D                           | evice Mode       | l)   | ,    |        | * |                                             | ·        |

| Electrostatic discharge voltage to GND              | V <sub>ESD</sub> | -500 | _    | 500    | V | Charged Device<br>Model (CDM) <sup>4)</sup> | P_4.1.73 |

| Electrostatic discharge voltage, corner pins to GND | V <sub>ESD</sub> | -750 | -    | 750    | V | Charged Device<br>Model (CDM) <sup>4)</sup> | P_4.1.74 |

- 1) Not subject to production test, specified by design.

- 2) Exposure to those absolute maximum ratings for extended periods of time (t > 10 s) may affect device reliability.

- 3) According to JEDEC standard EIA/JESD22-A114-B (1.5 k $\Omega$ , 100 pF)

- 4) According to EIA/JESD22-C101 or ESDA STM5.3.1

#### **Notes**

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

#### 4.2 Functional Range

Table 2 Functional Range

| Parameter                              | Symbol             |      | Value | S    | Unit | Note or               | Number  |

|----------------------------------------|--------------------|------|-------|------|------|-----------------------|---------|

|                                        |                    | Min. | Тур.  | Max. |      | <b>Test Condition</b> |         |

| Stand-by input voltage                 | $V_{IN\_STBY}$     | 3.0  | _     | 45   | ٧    | 1)                    | P_4.2.1 |

| Buck input voltage                     | $V_{IN}$           | 4.5  | _     | 45   | ٧    | 1)                    | P_4.2.2 |

| Peak to peak ripple voltage at FB/L_IN | $V_{\rm FB/L\_IN}$ | 0    | _     | 150  | mVpp | -                     | P_4.2.3 |

| Junction temperature                   | T <sub>i</sub>     | -40  | _     | 150  | °C   | _                     | P_4.2.4 |

<sup>1)</sup> At minimum battery voltage regulators with higher nominal output voltage will not be able to provide the full output voltage. Their outputs follow the battery with certain drop.

Note:

Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

## **Next Generation Microcontroller Supply**

#### **General Product Characteristics**

#### 4.3 Thermal Resistance

Table 3 Thermal Resistance

| Parameter           | Symbol     | Values |      | s Unit |     | Jnit Note or                            | Number  |

|---------------------|------------|--------|------|--------|-----|-----------------------------------------|---------|

|                     |            | Min.   | Тур. | Max.   |     | <b>Test Condition</b>                   |         |

| PG-DSO-36           | <u>'</u>   |        |      |        |     |                                         | ,       |

| Junction to ambient | $R_{thJA}$ | _      | 54   | _      | K/W | Footprint only <sup>1)</sup>            | P_4.3.5 |

| Junction to ambient | $R_{thJA}$ | _      | 42   | _      | K/W | Heat sink area 300mm <sup>2 1)</sup>    | P_4.3.6 |

| Junction to ambient | $R_{thJA}$ | -      | 35   | -      | K/W | Heat sink area<br>600mm <sup>2 1)</sup> | P_4.3.7 |

| Junction to case    | $R_{thJC}$ | _      | 5.6  | _      | K/W | _                                       | P_4.3.8 |

<sup>1)</sup> Worst case regarding peak temperature; zero airflow; mounted on FR4;  $80 \times 80 \times 1.5 \text{ mm}^3$ ;  $35 \,\mu\text{m}$  Cu;  $5 \,\mu\text{m}$  Sn

#### 4.4 Electrical Characteristics

Table 4 Electrical Characteristics,  $V_{IN} = V_{IN\_STBY} = 13.5 \text{ V}$ ,  $T_j = -40 ^{\circ}\text{C}$  to +150  $^{\circ}\text{C}$ ,  $V_{CCP} = 9.0 \text{ V}$ ; SEL\_STBY = Q\_STBY; all voltages with respect to ground.

| Parameter                           | Symbol                | Values |      | Unit | Note or Test Condition | Number                                                                                                  |         |  |

|-------------------------------------|-----------------------|--------|------|------|------------------------|---------------------------------------------------------------------------------------------------------|---------|--|

|                                     |                       | Min.   | Тур. | Max. |                        |                                                                                                         |         |  |

| Buck Regulator                      | ı                     |        |      |      |                        |                                                                                                         |         |  |

| Switching frequency                 | f                     | 280    | 370  | 425  | kHz                    | -                                                                                                       | P_4.4.1 |  |

| Current transition rise/fall time   | t <sub>r,1</sub>      | -      | 50   | _    | ns                     | <sup>1)</sup> ; slope magnitude 1 A; fixed internally                                                   | P_4.4.2 |  |

| Power stage on resistance           | R <sub>ON, Buck</sub> | -      | _    | 280  | mΩ                     | _                                                                                                       | P_4.4.3 |  |

| Power stage peak current limit      | I <sub>peak, SW</sub> | 2.5    | -    | 4.6  | A                      | $V_{\rm IN}$ = 5.0 V;<br>$V_{\rm SW}$ ramped down from 5.0 V<br>to 3.7 V;<br>$V_{\rm FB/L\_IN}$ = 5.0 V | P_4.4.4 |  |

| Buck converter output voltage       | V <sub>FB/L_IN</sub>  | 5.4    | -    | 6.0  | V                      | $I_{\text{Buck}} = 2.0 \text{ A}^{2}$                                                                   | P_4.4.5 |  |

| Buck converter output voltage       | V <sub>FB/L_IN</sub>  | 5.4    | -    | 6.4  | V                      | $I_{\text{Buck}} = 100 \text{ mA}^{2}$                                                                  | P_4.4.6 |  |

| Buck converter, turn on threshold   | V <sub>IN, on</sub>   | -      | -    | 4.5  | V                      | $V_{\text{IN}}$ increasing                                                                              | P_4.4.7 |  |

| Buck converter, turn off threshold  | V <sub>IN, off</sub>  | 3.5    | _    | _    | V                      | $V_{\text{IN}}$ decreasing                                                                              | P_4.4.8 |  |

| Buck converter On/off<br>hysteresis | V <sub>IN, hyst</sub> | 450    | 500  | 550  | mV                     | $V_{\rm IN,  hyst} = V_{\rm IN,  on} - V_{\rm IN,  off}$                                                | P_4.4.9 |  |

## **Next Generation Microcontroller Supply**

Table 4 Electrical Characteristics,  $V_{\text{IN}} = V_{\text{IN\_STBY}} = 13.5 \text{ V}$ ,  $T_{\text{j}} = -40^{\circ}\text{C to } +150^{\circ}\text{C}$ ,  $V_{\text{CCP}} = 9.0 \text{ V}$ ; SEL\_STBY = Q\_STBY; all voltages with respect to ground. (cont'd)

| Parameter                                                | Symbol                   | Values                |      |                       | Unit | <b>Note or Test Condition</b>                                                                                                                                                                                                                           | Number   |

|----------------------------------------------------------|--------------------------|-----------------------|------|-----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                          |                          | Min.                  | Тур. | Max.                  |      |                                                                                                                                                                                                                                                         |          |

| Bootstrap<br>undervoltage lockout,<br>turn on threshold  | V <sub>BST_UV, on</sub>  | -                     | -    | V <sub>SW</sub> + 5.0 | V    | Bootstrap voltage increasing                                                                                                                                                                                                                            | P_4.4.10 |

| Bootstrap<br>undervoltage lockout,<br>turn off threshold | V <sub>BST_UV, off</sub> | V <sub>SW</sub> + 3.2 | -    | _                     | V    | Bootstrap voltage decreasing                                                                                                                                                                                                                            | P_4.4.11 |

| Bootstrap<br>undervoltage lockout,<br>hysteresis         | $V_{ m BST\_UV,hyst}$    | 0.2                   | _    | 1                     | V    | $V_{\text{BST\_UV, hyst}} = V_{\text{BST\_UV, on}} - V_{\text{BST\_UV, off}}$                                                                                                                                                                           | P_4.4.12 |

| Charge Pump                                              |                          |                       |      |                       |      |                                                                                                                                                                                                                                                         |          |

| Charge pump voltage                                      | $V_{\rm CCP}$            | 9                     | _    | 15                    | V    | $C_{C1} = 100 \text{ nF};$<br>$C_{C2} = 100 \text{ nF};$<br>$C_{CCP} = 220 \text{ nF}$                                                                                                                                                                  | P_4.4.13 |

| Charge pump voltage                                      | V <sub>CCP</sub>         | 9                     | _    | 13.5                  | V    | $V_{IN} = 4.5 \text{ V};$ $C_{C1} = 100 \text{ nF};$ $C_{C2} = 100 \text{ nF};$ $C_{CCP} = 220 \text{ nF}$                                                                                                                                              | P_4.4.14 |

| Charge pump switching frequency                          | $f_{CCP}$                | 1.0                   | -    | 2.5                   | MHz  | -                                                                                                                                                                                                                                                       | P_4.4.15 |

| Voltage Regulator Q_L                                    | DO1                      |                       |      |                       |      |                                                                                                                                                                                                                                                         |          |

| Output voltage                                           | $V_{\rm Q\_LDO1}$        | 4.9                   | _    | 5.1                   | V    | $1 \text{ mA} < I_{Q\_LDO1} < 700 \text{ mA}^{3)}$                                                                                                                                                                                                      | P_4.4.16 |

| Output current limitation                                | $I_{\rm Q\_LDO1,lim}$    | 800                   | _    | 1600                  | mA   | $V_{\rm Q\_LDO1} = 4.0 \text{ V}$                                                                                                                                                                                                                       | P_4.4.17 |

| Drop voltage                                             | $V_{\rm dr,Q\_LDO1}$     | -                     | -    | 400                   | mV   | $I_{Q\_LDO1} = 500 \text{ mA;}$<br>$V_{FB/L\_IN} = 5.0 \text{ V;}^{3) 4)}$                                                                                                                                                                              | P_4.4.18 |

| Drop voltage                                             | $V_{\rm dr,Q\_LDO1}$     | _                     | _    | 400                   | mV   | $I_{Q\_LDO1} = 250 \text{ mA;}$<br>$V_{IN} = 4.5 \text{ V;}^{3) \text{ 4}}$                                                                                                                                                                             | P_4.4.19 |

| Load regulation                                          | $\Delta V_{\rm Q\_LDO1}$ | -                     | 60   | 120                   | mV/A |                                                                                                                                                                                                                                                         | P_4.4.20 |

| Power supply ripple rejection                            | PSRR <sub>Q_LD 01</sub>  | 26                    | -    | -                     | dB   | $V_{\text{FB/L\_IN}} = 5.6 \text{ V};$<br>$V_{\text{FB/L\_IN, ripple pp}} = 150 \text{ mV};$<br>$f_{\text{FB/L\_IN, ripple}} = 370 \text{ kHz};$<br>$I_{\text{Q\_LDO1}} = 250 \text{ mA};$<br>$C_{\text{Q\_LDO1}} = 4.7  \mu\text{F, } \text{X7R}^{1)}$ | P_4.4.21 |

| Output capacitor                                         | $C_{\mathrm{Q\_LDO1}}$   | 1                     | -    | 470                   | μF   | 1) 5)                                                                                                                                                                                                                                                   | P_4.4.22 |

| Output capacitor                                         | ESR C <sub>Q_LDO1</sub>  | _                     | -    | 2                     | Ω    | at 10 kHz <sup>1)</sup>                                                                                                                                                                                                                                 | P_4.4.23 |

| Voltage Regulator Q_L                                    |                          |                       |      |                       |      |                                                                                                                                                                                                                                                         |          |

| Output voltage                                           | $V_{\rm Q\_LDO2}$        | 3.23                  | -    | 3.37                  | V    | SEL_LDO2 = Q_LDO2;<br>IN_LDO2 = FB/L_IN;<br>1 mA < I <sub>Q_LDO2</sub> < 500 mA                                                                                                                                                                         | P_4.4.24 |

## **Next Generation Microcontroller Supply**

Electrical Characteristics,  $V_{\rm IN} = V_{\rm IN\_STBY} = 13.5$  V,  $T_{\rm j} = -40^{\circ}$ C to +150°C,  $V_{\rm CCP} = 9.0$  V; SEL\_STBY = Q\_STBY; all voltages with respect to ground. (cont'd) Table 4

| Parameter                     | Symbol                       |      | Value | 5    | Unit | Note or Test Condition                                                                                                                                                                                | Number   |

|-------------------------------|------------------------------|------|-------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                               |                              | Min. | Тур.  | Max. |      |                                                                                                                                                                                                       |          |

| Output current limitation     | I <sub>Q_LDO2, lim</sub>     | 700  | -     | 1400 | mA   | SEL_LDO2 = Q_LDO2;<br>IN_LDO2 = FB/L_IN;<br>V <sub>Q_LDO2</sub> = 2.8 V                                                                                                                               | P_4.4.25 |

| Drop voltage                  | V <sub>dr, Q_LDO2</sub>      | -    | _     | 400  | mV   | SEL_LDO2 = Q_LDO2;<br>$V_{CCP} = 9 \text{ V};$<br>$I_{Q_LDO2} = 500 \text{ mA;}^{4) 6}$                                                                                                               | P_4.4.26 |

| Drop voltage                  | V <sub>dr, Q_LDO2</sub>      | -    | -     | 400  | mV   | SEL_LDO2 = Q_LDO2;<br>$V_{CCP} = 9 \text{ V};$<br>$I_{Q_LDO2} = 250 \text{ mA};$<br>$V_{IN} = 4.5 \text{ V};^{4)6)}$                                                                                  | P_4.4.27 |

| Load regulation               | $\Delta V_{\mathrm{Q_LDO2}}$ | _    | -     | 80   | mV/A | 3.3 V mode<br>1 mA < I <sub>Q_LDO2</sub> < 650 mA                                                                                                                                                     | P_4.4.28 |

| Output voltage                | $V_{\mathrm{Q\_LDO2}}$       | 2.56 | _     | 2.67 | V    | SEL_LDO2 = GND;<br>IN_LDO2 = FB/L_IN;<br>1 mA < I <sub>Q_LDO2</sub> < 500 mA                                                                                                                          | P_4.4.29 |

| Output current limitation     | I <sub>Q_LDO2, lim</sub>     | 700  | _     | 1400 | mA   | SEL_LDO2 = GND;<br>IN_LDO2 = FB/L_IN;<br>V <sub>Q_LDO2</sub> = 2.0 V                                                                                                                                  | P_4.4.30 |

| Drop voltage                  | $V_{ m dr,Q\_LDO2}$          | -    | _     | 400  | mV   | SEL_LDO2 = GND;<br>$V_{CCP} = 9 \text{ V};$<br>$I_{Q_LDO2} = 500 \text{ mA};^{4)6)}$                                                                                                                  | P_4.4.31 |

| Drop voltage                  | V <sub>dr, Q_LDO2</sub>      | _    | _     | 400  | mV   | SEL_LDO2 = GND;<br>$V_{CCP} = 9 \text{ V};$<br>$I_{Q_LDO2} = 250 \text{ mA};$<br>$V_{IN} = 4.5 \text{ V};^{4)6)}$                                                                                     | P_4.4.32 |

| Load regulation               | $\Delta V_{ m Q\_LDO2}$      | -    | -     | 65   | mV/A | 2.6 V mode<br>1 mA < I <sub>Q_LDO2</sub> < 650 mA                                                                                                                                                     | P_4.4.33 |

| Power supply ripple rejection | PSRR <sub>Q_LDO2</sub>       | 26   | -     | -    | dB   | $V_{\rm IN\_LDO2}$ = 5.6 V;<br>$V_{\rm IN\_LDO2, ripple pp}$ = 150 mV;<br>$f_{\rm IN\_LDO2, ripple}$ = 370 kHz;<br>$I_{\rm Q\_LDO2}$ = 250mA;<br>$C_{\rm Q\_LDO2}$ = 4.7 µF ceramic X7R <sup>1)</sup> | P_4.4.34 |

| Selector Pull-down resistor   | R <sub>SEL_LDO2</sub>        | 0.7  | 1.2   | 1.9  | МΩ   | _                                                                                                                                                                                                     | P_4.4.35 |

| Output capacitor              | $C_{\mathrm{Q\_LDO2}}$       | 1    | _     | 470  | μF   | 1)5)                                                                                                                                                                                                  | P_4.4.36 |

| Output capacitor              | ESR C <sub>Q_LDO2</sub>      | -    | _     | 2    | Ω    | at 10 kHz; <sup>1)</sup>                                                                                                                                                                              | P_4.4.37 |

| External Voltage Reg          |                              |      |       | 1    | 1    | 1                                                                                                                                                                                                     | -        |

| Driver current limit          | I <sub>DRV_EXT, lim</sub>    | 75   | -     | 150  | mA   | TLE7368E $V_{\text{FB\_EXT}} = 1.2 \text{ V}$                                                                                                                                                         | P_4.4.38 |

| Driver current limit          | I <sub>DRV_EXT, lim</sub>    | 75   | -     | 150  | mA   | TLE7368-2E $V_{\text{FB\_EXT}} = 0.9V$                                                                                                                                                                | P_4.4.39 |

## **Next Generation Microcontroller Supply**

Table 4 Electrical Characteristics,  $V_{\text{IN}} = V_{\text{IN\_STBY}} = 13.5 \text{ V}$ ,  $T_{\text{j}} = -40^{\circ}\text{C to } +150^{\circ}\text{C}$ ,  $V_{\text{CCP}} = 9.0 \text{ V}$ ; SEL\_STBY = Q\_STBY; all voltages with respect to ground. (cont'd)

| Parameter                                  | Symbol                      | Values |      |      | Unit | Note or Test Condition                                                                                                                                                                                                                                                                      | Number   |

|--------------------------------------------|-----------------------------|--------|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                            |                             | Min.   | Тур. | Max. |      |                                                                                                                                                                                                                                                                                             |          |

| Driver current limit                       | I <sub>DRV_EXT</sub> , lim  | 75     | -    | 150  | mA   | TLE7368-3E<br>V <sub>FB EXT</sub> = 1.0V                                                                                                                                                                                                                                                    | P_4.4.40 |

| Feedback voltage                           | V <sub>FB_EXT</sub>         | 1.505  | _    | 1.55 | V    | TLE7368E                                                                                                                                                                                                                                                                                    | P_4.4.41 |

| Feedback voltage                           | V <sub>FB_EXT</sub>         | 1.19   | _    | 1.23 | V    | TLE7368-2E                                                                                                                                                                                                                                                                                  | P_4.4.42 |

| Feedback voltage                           | $V_{FB\_EXT}$               | 1.30   | _    | 1.34 | V    | TLE7368-3E                                                                                                                                                                                                                                                                                  | P_4.4.43 |

| Feedback input current                     |                             | -250   | _    | _    | μΑ   | -                                                                                                                                                                                                                                                                                           | P_4.4.44 |

| Load regulation                            | $\Delta V_{\text{FB\_EXT}}$ | -      | -    | 20   | mV/A | $V_{\text{FB/L_IN}} = 5.4 \text{ V};$<br>$V_{\text{CCP}} = 9.0 \text{ V};$<br>$I_{\text{Q_LDO3}} = 100  \mu\text{A to } 1 \text{ A};^{7)}$                                                                                                                                                  | P_4.4.45 |

| Output capacitor                           | $C_{FB\_EXT}$               | 4.7    | -    | -    | μF   | 2)5)7) $I_{Q_{LDO3}} = 1 \text{ A}$                                                                                                                                                                                                                                                         | P_4.4.46 |

| Output capacitor                           | $ESRC_{FB\_EXT}$            | 0.006  | -    | 0.1  | Ω    | at 1 MHz; <sup>2)</sup>                                                                                                                                                                                                                                                                     | P_4.4.47 |

| Voltage Tracker Q_T1                       |                             |        |      |      |      | <u> </u>                                                                                                                                                                                                                                                                                    |          |

| Output voltage tracking accuracy to Q_LDO1 | $\Delta V_{\mathrm{Q_T1}}$  | -10    | -    | 10   | mV   | 0 mA < I <sub>Q_T1</sub> < 105 mA                                                                                                                                                                                                                                                           | P_4.4.48 |

| Output current limitation                  | $I_{Q_T1}$                  | 120    | _    | 240  | mA   | V <sub>Q_T1</sub> = 4.0 V                                                                                                                                                                                                                                                                   | P_4.4.49 |

| Drop voltage                               | $V_{\mathrm{dr,Q\_T1}}$     | -      | -    | 400  | mV   | $I_{Q_{-}T1} = 105 \text{ mA};$<br>$V_{FB/L_{-}IN} = 5.3 \text{ V};$<br>$V_{Q_{-}LDO1} = 5.0 \text{ V}^{4)}$                                                                                                                                                                                | P_4.4.50 |

| Power supply ripple rejection              | PSRR <sub>Q_T1</sub>        | 26     | -    | -    | dB   | $V_{\text{FB/L\_IN}} = 5.6 \text{ V};$<br>$V_{\text{FB/L\_IN, ripple pp}} = 150 \text{ mV};$<br>$f_{\text{FB/L\_IN, ripple}} = 370 \text{ kHz};$<br>$V_{\text{Q\_LDO1}} = 5.0 \text{ V};$<br>$I_{\text{Q\_T1}} = 100 \text{ mA};$<br>$C_{\text{Q\_T1}} = 4.7 \mu\text{F ceramic X7R;}^{1)}$ | P_4.4.51 |

| Output capacitor                           | $C_{Q_T1}$                  | 4.7    | _    | _    | μF   | 1)5)                                                                                                                                                                                                                                                                                        | P_4.4.52 |

| Output capacitor                           | $ESR C_{Q\_T1}$             | _      | _    | 3    | Ω    | at 10 kHz; <sup>1)</sup>                                                                                                                                                                                                                                                                    | P_4.4.53 |

| Voltage Tracker Q_T2                       |                             |        |      |      |      |                                                                                                                                                                                                                                                                                             |          |

| Output voltage tracking accuracy to Q_LDO1 | $\Delta V_{\mathrm{Q_T2}}$  | -10    | _    | 10   | mV   | 0 mA < I <sub>Q_T2</sub> < 50 mA;                                                                                                                                                                                                                                                           | P_4.4.54 |

| Output current limitation                  | $I_{Q_T2}$                  | 60     | -    | 110  | mA   | V <sub>Q_T2</sub> = 4.0 V                                                                                                                                                                                                                                                                   | P_4.4.55 |

| Drop voltage                               | $V_{\rm dr,Q\_T2}$          | -      | _    | 400  | mV   | $I_{Q_{-T2}} = 50 \text{ mA};$<br>$V_{FB/L_{-IN}} = 5.3 \text{ V};$<br>$V_{Q_{-LDO1}} = 5.0 \text{ V}^{4)}$                                                                                                                                                                                 | P_4.4.56 |

## **Next Generation Microcontroller Supply**

Electrical Characteristics,  $V_{\rm IN} = V_{\rm IN\_STBY} = 13.5$  V,  $T_{\rm j} = -40^{\circ}$ C to +150°C,  $V_{\rm CCP} = 9.0$  V; SEL\_STBY = Q\_STBY; all voltages with respect to ground. (cont'd) Table 4

| Parameter                     | Symbol                   | Values  |      |      | Unit | <b>Note or Test Condition</b>                                                                                                                                                                                                                                                | Number   |

|-------------------------------|--------------------------|---------|------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                               |                          | Min.    | Тур. | Max. |      |                                                                                                                                                                                                                                                                              |          |

| Power supply ripple rejection | PSRR <sub>Q_T2</sub>     | 26      | -    | -    | dB   | $V_{\rm FB/L\_IN} = 5.6 \text{ V};$<br>$V_{\rm FB/L\_IN,  ripple  pp} = 150  \text{mV};$<br>$f_{\rm FB/L\_IN,  ripple} = 370  \text{kHz};$<br>$V_{\rm Q\_LDO1} = 5.0  \text{V};$<br>$I_{\rm Q\_T2} = 40  \text{mA};$<br>$C_{\rm Q\_T2} = 4.7  \mu\text{F ceramic X7R;}^{1)}$ | P_4.4.57 |

| Output capacitor              | $C_{Q_T2}$               | 4.7     | _    | _    | μF   | 1)5)                                                                                                                                                                                                                                                                         | P_4.4.58 |

| Output capacitor              | $ESR C_{Q\_T2}$          | -       | -    | 3    | Ω    | at 10 kHz; <sup>1)</sup>                                                                                                                                                                                                                                                     | P_4.4.59 |

| Stand-by Regulator            |                          |         |      |      |      |                                                                                                                                                                                                                                                                              |          |

| Output voltage                | $V_{\mathrm{Q\_STBY}}$   | 0.93    | 1.02 | 1.08 | V    | $V_{\text{IN\_STBY}} > 3 \text{ V};$<br>$100  \mu\text{A} < I_{\text{Q\_STBY}} < 10  \text{mA};$<br>$\text{SEL\_STBY} = \text{Q\_STBY}$                                                                                                                                      | P_4.4.60 |

| Output voltage                | $V_{\mathrm{Q\_STBY}}$   | 0.93    | 1.02 | 1.08 | V    | $V_{\text{IN\_STBY}} > 4.5 \text{ V};$<br>$I_{\text{Q\_STBY}} = 30 \text{ mA};$<br>SEL_STBY = Q_STBY                                                                                                                                                                         | P_4.4.61 |

| Output voltage                | $V_{\mathrm{Q\_STBY}}$   | 2.51    | 2.62 | 2.73 | V    | $V_{\text{IN\_STBY}} > 3.0 \text{ V};$<br>$100  \mu\text{A} < I_{\text{Q\_STBY}} < 10 \text{ mA};$<br>$\text{SEL\_STBY} = \text{GND}$                                                                                                                                        | P_4.4.62 |

| Selector pull-up<br>current   | I <sub>SEL_STBY</sub>    | -2      | -5   | -10  | μΑ   | SEL_STBY = GND                                                                                                                                                                                                                                                               | P_4.4.63 |

| Output current<br>limitation  | I <sub>Q_STBY, lim</sub> | 31      | -    | 90   | mA   | $V_{\rm Q\_STBY} = 0.5 \text{ V}$                                                                                                                                                                                                                                            | P_4.4.64 |