# Synchronous Rectified Buck MOSFET driver IC

PX3519

# Datasheet

Revision 2.3, 2015-10-21

Power Management and Multimarket

Edition 2015-10-21 Published by Infineon Technologies AG 81726 Munich, Germany © 2015 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| <b>Revision Histo</b> | ry                                                                       |

|-----------------------|--------------------------------------------------------------------------|

| Page or Item          | Subjects (major changes since previous revision)                         |

|                       |                                                                          |

| Revision 2.0          | 2013-07-17 first issue                                                   |

| Revision 2.1          | 2014-08-21 changes:                                                      |

|                       | Table 5 page 8: PHASE voltage, pulsed Minimum to -12V                    |

| Revision 2.2          | 2014-09-19 changes:                                                      |

|                       | R <sub>PHASE</sub> added in the Simplified Block Diagram                 |

|                       | SOA diagram for R <sub>PHASE</sub> introduced                            |

| Revision 2.3          | 2015-10-21 changes:                                                      |

|                       | Power up and power down sequence introduced                              |

|                       | ➔ Junction operating temperature from -25°C to -40°C table 1 and table 7 |

#### Trademarks of Infineon Technologies AG

AURIX<sup>™</sup>, BlueMoon<sup>™</sup>, COMNEON<sup>™</sup>, C166<sup>™</sup>, CROSSAVE<sup>™</sup>, CanPAK<sup>™</sup>, CIPOS<sup>™</sup>, CoolMOS<sup>™</sup>, CoolSET<sup>™</sup>, CORECONTROL<sup>™</sup>, DAVE<sup>™</sup>, EasyPIM<sup>™</sup>, EconoBRIDGE<sup>™</sup>, EconoDUAL<sup>™</sup>, EconoPACK<sup>™</sup>, EconoPIM<sup>™</sup>, EiceDRIVER<sup>™</sup>, EUPEC<sup>™</sup>, FCOS<sup>™</sup>, HITFET<sup>™</sup>, HybridPACK<sup>™</sup>, ISOFACE<sup>™</sup>, I<sup>2</sup>RF<sup>™</sup>, IsoPACK<sup>™</sup>, MIPAQ<sup>™</sup>, ModSTACK<sup>™</sup>, my-d<sup>™</sup>, NovalithIC<sup>™</sup>, OmniTune<sup>™</sup>, OptiMOS<sup>™</sup>, ORIGA<sup>™</sup>, PROFET<sup>™</sup>, PRO-SIL<sup>™</sup>, PRIMARION<sup>™</sup>, PrimePACK<sup>™</sup>, RASIC<sup>™</sup>, ReverSave<sup>™</sup>, SatRIC<sup>™</sup>, SIEGET<sup>™</sup>, SINDRION<sup>™</sup>, SMARTi<sup>™</sup>, SmartLEWIS<sup>™</sup>, TEMPFET<sup>™</sup>, thinQ!<sup>™</sup>, TriCore<sup>™</sup>, TRENCHSTOP<sup>™</sup>, X-GOLD<sup>™</sup>, XMM<sup>™</sup>, X-PMU<sup>™</sup>, XPOSYS<sup>™</sup>.

#### Other Trademarks

Advance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, PRIMECELL™, REALVIEW™, THUMB™ of ARM Limited, UK. AUTOSAR™ is licensed by AUTOSAR development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. FlexRay<sup>™</sup> is licensed by FlexRay Consortium. HYPERTERMINAL<sup>™</sup> of Hilgraeve Incorporated. IEC<sup>™</sup> of Commission Electrotechnique Internationale. IrDA<sup>™</sup> of Infrared Data Association Corporation. ISO<sup>™</sup> of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC<sup>™</sup>, NUCLEUS<sup>™</sup> of Mentor Graphics Corporation. Mifare<sup>™</sup> of NXP. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF Micro Devices, Inc. SIRIUS™ of Sirius Sattelite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.

Last Trademarks Update 2010-06-09

Applications

# 1 Applications

- Desktop and Server VR12.X Vcore and non-Vcore buck-converters

- Network and Telecom uncontrolled processor VR

- Single Phase and Multiphase POL

- CPU/GPU Regulation in Notebook, Graphics Cards and Gaming

- Voltage Modules requiring high power density

- Memory (DDR2/3)

# 2 Features

- High frequency operation: up to 1.2MHz

- Capability to drive MOSFET for 50A per phase

- Wide VCC input voltage range: 4.5V to 9V

- Wide input voltage range: up to 13.2V

- Low power dissipation

- Includes bootstrap diode

- Gate disable pin for fast low side switch off

- Adaptive shoot through protection

- Compatible to standard +3.3V controller.

- Tri-state PWM input functionality

- Small package: 3mmx3mm VDSON-8

- RoHS compliant

#### Table 1Product Identification

| Part Number | Temp Range   | Package             | Marking |

|-------------|--------------|---------------------|---------|

| PX3519      | -40 to 125°C | 3x3 8-leads VDSON-8 | 3519    |

Figure 1 Picture of the product

Description

# 3 Description

# 3.1 Pinout

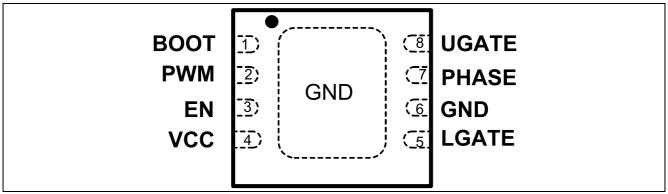

| Figure 2 | Pinout, numbering and name of pins (transparent top view) |

|----------|-----------------------------------------------------------|

|          | · ····································                    |

| Pin No. | Name  | Pin Type | Buffer Type | Function                                                                                                                                                                                                                                                                                                                                   |

|---------|-------|----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | BOOT  | 0        | Analog      | <b>Floating bootstrap supply pin for the upper gate drive</b> .<br>Connect the bootstrap capacitor <sup>1)</sup> between this pin and the<br>PHASE pin. The bootstrap capacitor provides the charge to<br>turn on the upper MOSFET. See the Internal Bootstrap<br>Device section herein for guidance in choosing the<br>capacitance value. |

| 2       | PWM   | 1        | Logic       | PWM drive logic input                                                                                                                                                                                                                                                                                                                      |

|         |       |          |             | Connect this pin to the PWM output from the controller.                                                                                                                                                                                                                                                                                    |

| 3       | EN    | 1        | Logic       | Enable signal                                                                                                                                                                                                                                                                                                                              |

|         |       |          |             | Used to activate the device. When connected to high level<br>the status of the driver outputs (UGATE, LGATE), is<br>determined by the PWM. When connected to low level the<br>driver outputs are disabled regardless of signal levels on<br>PWM input. EN input must be driven high or low and must<br>not be left floating.               |

| 5       | LGATE | 0        | Analog      | Low side gate signal                                                                                                                                                                                                                                                                                                                       |

|         |       |          |             | Connect to the gate of the low-side power N-channel MOSFET                                                                                                                                                                                                                                                                                 |

| 7       | PHASE | 1        | Analog      | <b>Return path for the upper gate driver.</b><br>Connect this pin to the source of the upper MOSFET and<br>the drain of the lower MOSFET. This pin provides a return<br>path for the upper gate drive.                                                                                                                                     |

| 8       | UGATE | 0        | Analog      | Upper gate drive output.<br>Connect to the gate of high-side power N-channel MOSFET                                                                                                                                                                                                                                                        |

Table 2 I/O Signals

<sup>1)</sup> See section 5.2 for guidance in choosing capaciatance value

#### Description

#### Table 3 Power Supply

|         |      | 1        |             |                                                                                             |  |  |  |  |

|---------|------|----------|-------------|---------------------------------------------------------------------------------------------|--|--|--|--|

| Pin No. | Name | Pin Type | Buffer Type | Function                                                                                    |  |  |  |  |

| 4       | VCC  | POWER    | -           | Supply for housekeeping/logic and driver sections power to the IC.                          |  |  |  |  |

|         |      |          |             | Connect to +4.5V – 8V. Place a high quality low ESR ceramic capacitor from this pin to GND. |  |  |  |  |

#### Table 4 Ground Pins

| Pin No. | Name    | Pin Type | Buffer Type | Function                                                                                                                                                                                                                   |

|---------|---------|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6       | GND     | GND      | -           | <b>GND connection.</b><br>Can be left open since main GND connection to circuit board is via die pad. Must not be used as single ground connection.                                                                        |

| -       | Die Pad | GND      | -           | <b>Bias and reference ground.</b><br>All signals are referenced to this node. It is also the power ground return of the driver. It is mandatory to connect the die paddle electrically and thermally to the circuit board. |

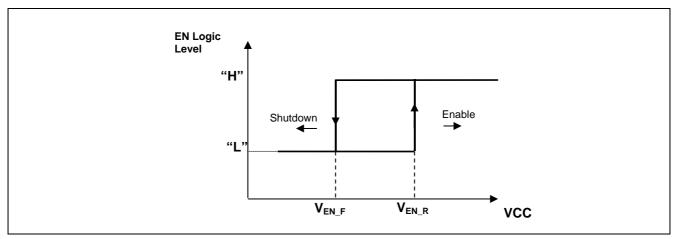

# 3.2 General description

The PX3519 is a dual high speed driver designed to drive a wide range of high-side and low-side power Nchannel MOSFETs in synchronous rectified buck converters. When combined with the Infineon PX38xx/PX88xx family of Digital Multi-phase Controllers or PX75xx Digital Point of Load (DiPOL<sup>™</sup>) Controllers and N-channel MOSFETs, the PX3519 forms a complete core-voltage regulator solution for advanced micro and graphics processors as well as point-of-load applications. The PX3519 provides the capability of driving the high-side gate and low-side gate with a variable gate driving voltage, ranging from 4.5V up to 8V, to tailor the efficiency of the system based on the customer conditions and needs. The input voltage for the power stage can range from 5V up to 13.2V. Adaptive shoot-through protection is integrated into the IC which prevents both upper and lower MOSFETs from conducting simultaneously while minimizing dead time. An enable pin is provided to switch off the outputs of the driving stage.

#### Description

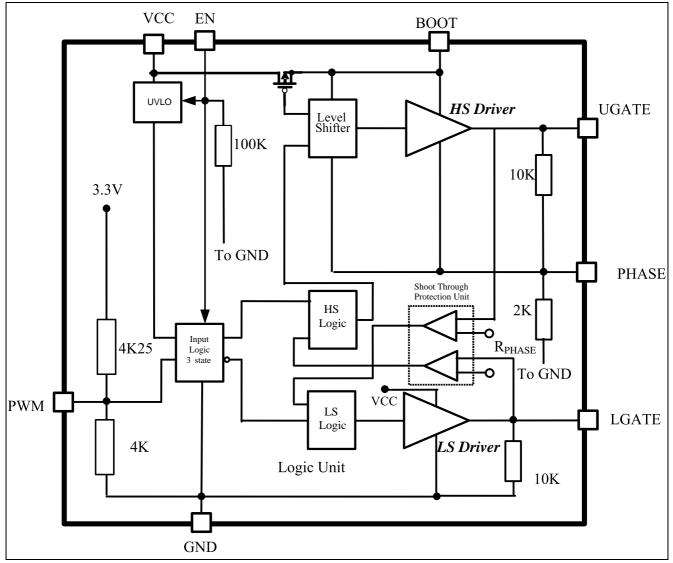

Figure 3 Simplified block diagram

# 4 Electrical specification

# 4.1 Absolute Maximum Ratings

Stresses above those listed in Table 5 "Absolute Maximum Ratings" may cause permanent damage to the device. These are absolute stress ratings only and operation of the device is not implied or recommended at these or any other conditions in excess of those given in the operational sections of this specification. Exposure to the absolute maximum ratings for extended periods may adversely affect the operation and reliability of the device.

| Parameter                  | Symbol                                 | Values |      |      | Unit | Note / Test |

|----------------------------|----------------------------------------|--------|------|------|------|-------------|

|                            |                                        | Min.   | Тур. | Max. |      | Conditions  |

| VCC supply voltage (DC)    | V <sub>vcc</sub>                       | -0.3   |      | 9    | V    |             |

| BOOT voltage, DC           | V <sub>BOOT</sub>                      | -0.3   |      | 25   | V    |             |

| BOOT voltage, pulsed       | V <sub>BOOT</sub>                      | -0.3   |      | 30   | V    |             |

| BOOT to PHASE voltage      | V <sub>BOOT -</sub> V <sub>PHASE</sub> | -0.3   |      | 9    | V    |             |

| PHASE voltage, DC          | V <sub>PHASE</sub>                     | -1     |      | 16   | V    |             |

| PHASE voltage, pulsed      | V <sub>PHASE</sub>                     | -12    |      | 25   | V    | 2)          |

| LGATE voltage, DC          | LGATE                                  | -0.3   |      | 9.3  | V    |             |

| HGATE voltage to PHASE, DC | H <sub>GATE -</sub> V <sub>PHASE</sub> | -0.3   |      | 9.3  | V    |             |

| V <sub>PWM</sub>           |                                        |        |      | 3.6  | V    |             |

| EN                         | V <sub>EN</sub>                        |        |      | 3.6  | V    |             |

| Junction temperature       | T-Jmax-                                | -40    | -    | 150  | °C   | -           |

| Storage temperature        | T-STG-                                 | -55    | -    | 150  | °C   | _           |

#### Table 5 Absolute Maximum Ratings (Tambient = 25°C)

<sup>2)</sup> The pulse duration is 2ns for the minimum and 10ns for the maximum.

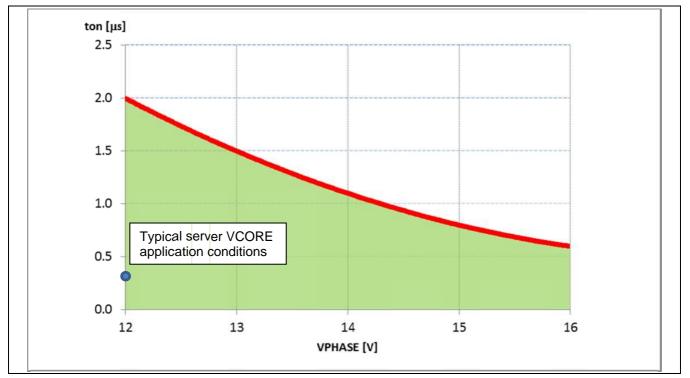

Figure 4 Safe Operating Area of R<sub>PHASE</sub>

#### **Electrical specification**

Note: ton refers to the on-time of the HS-MOSFET. For input voltages below 12 V no limits on the duration of ton need to be applied. The relative position of a typical Server VCORE application conditions V<sub>IN</sub>=12V V<sub>OUT</sub>=1.8V f<sub>SW</sub>=450kHz is represented as reference. This Safe Operating Area is verified by design, not 100% tested in production.

Note: All rated voltages are relative to voltages on the GND pins unless otherwise specified.

#### **Electrical specification**

# 4.2 Thermal characteristics

#### Table 6 Thermal Characteristics

| Parameter                                                 | Symbol |      | Values | ;    | Unit | Note / Test Condition |

|-----------------------------------------------------------|--------|------|--------|------|------|-----------------------|

|                                                           |        | Min. | Тур.   | Max. |      |                       |

| Thermal resistance, junction-soldering point <sup>3</sup> | θjs    | -    | 7      | -    | K/W  | -                     |

| Thermal resistance, junction-top of package               | θJtop  | -    | 20     | -    |      | -                     |

# 4.3 Recommended Operating Conditions and Electrical characteristics

Note: VCC = 5V, Tambient =  $25^{\circ}$ C

| Parameter                                                                 | Symbol          |      | Valu | es   | Unit | Test conditions   |

|---------------------------------------------------------------------------|-----------------|------|------|------|------|-------------------|

|                                                                           |                 | Min. | Тур. | Max. |      |                   |

| Supply voltage<br>rising edge between 3.1V and 4.5V :<br>dvcc/dt>5V/100ms | V-VCC-          | 4.5  | -    | 8    | V    | -                 |

| Frequency of the PWM                                                      | f <sub>SW</sub> | -    | -    | 1.2  | MHz  | Note <sup>4</sup> |

| Enable pin voltage                                                        | V-EN            | 0    | -    | 3.3  | V    |                   |

| Junction temperature                                                      | T-jop-          | -40  | -    | +125 | °C   | -                 |

| Minimum on time                                                           |                 |      | 20   |      | ns   | Note <sup>4</sup> |

| Minimum off time                                                          |                 |      | 30   |      | ns   | Note <sup>4</sup> |

| Table 8 | Voltage Supply And Biasing Current |

|---------|------------------------------------|

|---------|------------------------------------|

| Parameter                                                              | Symbol                    |      | Values |      | Unit | Test conditions   |

|------------------------------------------------------------------------|---------------------------|------|--------|------|------|-------------------|

|                                                                        |                           | Min. | Тур.   | Max. |      |                   |

| UVLO rising<br>rising edge between 3.1V and 4.5V :<br>dvcc/dt>5V/100ms | V <sub>UVLO_R</sub>       | -    | 3.6    | 4.3  | V    | VCC rising        |

| UVLO falling                                                           | V <sub>UVLO_F</sub>       | -    | 3.2    | -    |      | VCC falling       |

| IC current                                                             | I <sub>VCC_300kHz</sub>   | -    | 2      | -    | mA   | fsw = 300kHz      |

|                                                                        | I <sub>VCC_PWML</sub>     | -    | 1.67   | -    |      | PWM = 0V          |

|                                                                        | I <sub>VCC_ENL_PWML</sub> | -    | 1100   | -    | μA   | EN = 0V<br>PWM=0V |

|                                                                        | I <sub>VCC_O</sub>        | -    | 780    | -    |      | PWM = Open        |

<sup>&</sup>lt;sup>3</sup> The junction-soldering point is referred to the GND bottom exposed pad.

# **Electrical specification**

| Table 9 | Logic Inputs And Threshold |

|---------|----------------------------|

|---------|----------------------------|

| Parameter |                           | Symbol                |      | Values | ;    | Unit | Test conditions                |

|-----------|---------------------------|-----------------------|------|--------|------|------|--------------------------------|

|           |                           |                       | Min. | Тур.   | Max. |      |                                |

| EN        | Input low                 | V-EN_L-               |      |        | 0.8  | V    |                                |

|           | Input high                | V-EN_H-               | 2.0  |        |      |      |                                |

| PWM       | Input low                 | V-PWM_L-              | -    | -      | 0.8  | V    | V- <sub>PWM-</sub> falling     |

|           | Input high                | V-PWM_H-              | 2.5  | _      | _    |      | V-PWM- rising                  |

|           | Input resistance          | R-IN-PWM-             | -    | 2.06   | -    | kΩ   | $V_{\text{PWM}} = 1 \text{ V}$ |

|           | Open voltage              | V- <sub>PWM_O</sub> . | -    | 1.6    | -    | V    | V-PWM_O-                       |

|           | Tristate shutdown window_ | V <sub>-PWM_S</sub> . | 1.2  | -      | 2.0  |      | -                              |

#### Table 10Timing Characteristics

| Parameter                               | Symbol              | Values |      |      | Unit | Test conditions              |

|-----------------------------------------|---------------------|--------|------|------|------|------------------------------|

|                                         |                     | Min.   | Тур. | Max. |      |                              |

| Upper Gate (UGATE) Output               |                     |        |      |      |      |                              |

| Shutdown hold off time                  | t <sub>SSHD_U</sub> |        | 50   |      | ns   | Note, no load                |

| UGATE rise time                         | t <sub>r_U</sub>    |        | 10   |      |      | Note <sup>4</sup> , 3nF load |

| UGATE fall time                         | t <sub>f_U</sub>    |        | 10   |      | -    | Note <sup>4</sup> , 3nF load |

| tri-state to high propagation delay     | t <sub>PDTS_U</sub> |        | 15   |      |      | Note, no load                |

| UGATE turn-on propagation delay         | t <sub>PDH_U</sub>  |        | 15   |      | ]    | Note, no load                |

| UGATE turn-off propagation delay        | t <sub>PDL_U</sub>  |        | 20   |      | -    | Note, no load                |

| ower Gate (LGATE) Output                |                     |        |      |      |      |                              |

| Shutdown hold-off time                  | t <sub>SSHD_L</sub> |        | 50   |      | ns   | Note, no load                |

| LGATE rise time                         | t <sub>r_L</sub>    |        | 10   |      |      | Note <sup>4</sup> , 3nF load |

| LGATE fall time                         | t <sub>f_L</sub>    |        | 5    |      | ]    | Note <sup>4</sup> , 3nF load |

| tri-state to low propagation delay time | t <sub>PDTS_L</sub> |        | 15   |      |      | Note, no load                |

| LGATE turn-on propagation delay time    | t <sub>PDH_L</sub>  |        | 15   |      | ]    | Note, no load                |

| LGATE turn-off propagation delay time   | t <sub>PDL_L</sub>  |        | 7    |      | ]    | Note, no load                |

| Enable (EN)                             |                     |        |      |      |      |                              |

| Propagation delay Time rising falling   | <i>t</i> PDEN       |        | 15   |      | ns   |                              |

<sup>4)</sup> Parameter verified by design, not 100% tested in production

# **Electrical specification**

#### Table 11Output Characteristics

| Parameter                    | Symbol              | Values |      |      | Unit | Test conditions                          |  |

|------------------------------|---------------------|--------|------|------|------|------------------------------------------|--|

|                              |                     | Min.   | Тур. | Max. | -    |                                          |  |

| Output Characteristics       |                     |        |      |      |      |                                          |  |

| Upper drive source current   | I <sub>SRC_UG</sub> |        | 2    |      | А    | Note <sup>2</sup> current pulse < 20ns   |  |

| Upper drive source impedance | R <sub>SRC_UG</sub> |        | 0.8  |      | Ω    | I <sub>SRC_UG</sub> = 200mA              |  |

| Upper drive sink current     | I <sub>SNK_UG</sub> |        | 2    |      | А    | Note <sup>2</sup> , current pulse < 20ns |  |

| Upper drive sink impedance   | R <sub>SNK_UG</sub> |        | 0.6  |      | Ω    | I <sub>SINK_UG</sub> = 200mA             |  |

| Lower drive source current   | I <sub>SRC_LG</sub> |        | 2    |      | А    | Note <sup>2</sup> , current pulse < 40ns |  |

| Lower drive source impedance | R <sub>SRC_LG</sub> |        | 0.8  |      | Ω    | I <sub>SRC_UG</sub> = 200mA              |  |

| Lower drive sink current     | I <sub>SNK_LG</sub> |        | 4    |      | А    | Note <sup>2</sup> , current pulse < 40ns |  |

| Lower drive sink impedance   | R <sub>SNK_LG</sub> |        | 0.35 |      | Ω    | I <sub>SINK_UG</sub> = 200mA             |  |

# 5 Theory of operation

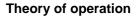

The PX3519 functionality is enabled by the EN pin. When the EN pin voltage overcomes the rising voltage threshold of the UVLO the driver begins to operate depending on the PWM status and the VCC pin status (VCC has to be higher then the rising threshold voltage). For VCC is recommended to have a slope for the rising edge higher than 5V/100ms around the rising UVLO threshold.

The VCC can range between 4.5V and 8V and it is the supply pin for both driver and logic sections.

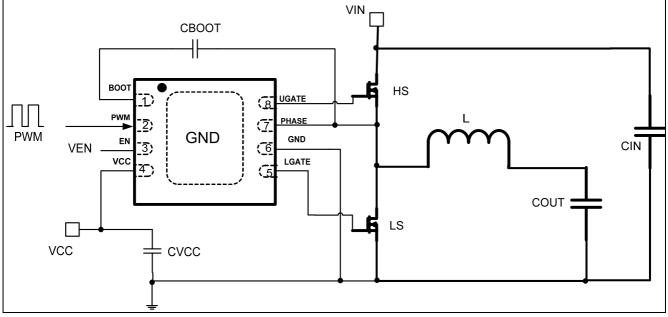

The PX3519 functionality is driven by the PWM signal transitions. When the PWM signal performs a transition between low state to high state (PWM voltage higher than 2.5V) the Low Side MOSFET is turned off, after the turn off delay propagation time. Then the High Side MOSFET is turned on, after the turn on propagation delay time. Once the on time is expired the PWM signal provides a transition between the high state to the low state (PWM voltage lower than 0.8V). This will drive the High Side MOSFET from the ON state to the OFF state, after the turn off propagation delay time. The PX3519 is also capable to drive the two external MOSFETs both in off state. When the PWM signal enters in the shut down window or tri-state (typically between 1.2V and 2.0V) after the shut down hold off time both MOSFETs are switched off. This feature is useful when the IC controller wants to reduce the number of active phases in order to reduce the power consumption. In principle the tri-state status can be used also to improve the transition between high loads to low load.

The PX3519 implements an embedded resistor network, which forces the PWM pin of the device in the middle of the shut down window if the PWM input from the controller is floating.

In order to avoid cross conduction between the High Side MOSFET and the Low Side MOSFET an anti-shootthrough control is implemented with the adaptive scheme. The adaptive scheme is implemented in order to use a variety of different power MOSFETs for different kind of conversion. Nevertheless the dead time is kept as short as possible in order to increase the efficiency of the overall solution.

The driver includes gate drive functionality to protect against shoot through. In order to protect the power stage from overlap, both High Side and Low Side MOSFETs being on at the same time, the adaptive control circuitry monitors the voltage at the "PHASE" pin. When the PWM signal goes low, the High Side MOSFET will begin to turn off. Once the "PHASE" pin falls below 1V, the Low Side MOSFET is gated on. Additionally, the gate to source voltage of the High Side MOSFET is also monitored. When VGS (High Side) is discharged below 1V, a threshold known to turn the High Side MOSFET off, a secondary delay is initiated, which results in the Low Side being gated "ON" regardless of the state of the "PHASE" pin. This way it will be ensured that the converter can sink current efficiently and the bootstrap capacitor will be refreshed appropriately during each switching cycle.

During the start up depending on several factors it can be that the power input for the conversion (input rail) rises before the VCC input. In this case it could happen that the high side has an induced turn on. In order to avoid this undesirable effect the PX3519 embeds a resistance of 10 kOhm between UGATE pin and PHASE pin.

In order to reduce the sensitivity to issues generated during the power on sequence (like the induced turn on of the high side MOSFET) and to reduce further the power consumption an EN pin is implemented; in this case the designer has the possibility to create a short delay time between the VCC and the EN pin voltage to ensure the proper functionality. Moreover the EN pin can be used to disable the driver stage in case a very low consumption is required.

# 5.1 Driver characteristics

The gate driver of the PX3519 has one supply voltage to simplify the layout of the system. The VCC pin is used to power the section related to the logic for detecting the status of PWM pin and EN pin. The VCC pin is used also to supply the power section related to the driver of the power mosfet.

The MOSFETs selected for this application are optimized for 5V gate drive, thus giving the end user optimized high load as well as light load efficiency. Nevertheless the driving voltage can be increased up to 8V in order to have a customized efficiency curve depending on the application conditions. The reference for the power circuitry including the driver output stage and the reference for the gate driver control circuit is GND.

Proper response of the driver to the PWM signal is only guaranteed when UVLO have been cleared by the respective supply voltages (ref to table 8). Therefore, it is strongly recommended to only issue pulses to PWM when no UVLO conditions are present. The power down sequence should set PWM to HiZ with respect the internal threshold, before ramping down VIN (see figure 6 for VIN connection), PVCC and VCC respectively.

#### Theory of operation

# 5.2 Current capability and internal Bootstrap

The PX3519 implements high current capability and low ohmic pull down resistances for the driving stages. The high current capability ensures fast switching transition for the MOSFETs in order to reduce the switching losses (2A of driving source/sink current for the upper MOSFET) even with high gate charge high side. The low ohmic pull down resistance (Low driver sink impedance 0.35 Ohm) is mainly important to avoid the induced turn on phenomenon on the low side during the fast turn on of the high side MOSFET.

The high side is powered through the bootstrap circuitry. The PX3519 provides an embedded bootstrap diode. To complete the power network only a capacitance between PHASE and BOOT is needed. In many cases the PX3519 is optimized for the best switching behavior. An external resistance is not needed. The bootstrap capacitance is chosen depending on the high side gate charge. The following formula is giving a good estimation of the voltage drop across the bootstrap capacitance due to the charging of the high side:

$$C_{BOOT} > \frac{Q_{GS}HS}{\Delta V_{BOOT}}$$

Where the  $\triangle VBOOT$  is the desired variation of the bootstrap voltage.

The low side driver is powered through the VCC pin. The same considerations and formula done for the bootstrap capacitance can be done for the capacitance used to filter the VCC pin.

The flexibility to adjust the driving voltage from 4.5V to 8V gives designers the possibility to shape the efficiency curve in anyway that is desired.

### 5.3 Power dissipation

The power dissipation of the driver is given by the gate charge of the external power MOSFETs. The following formulas held:

$$P_{DISS} = VCC * f_{SW} * (Q_{GS_HS} + Q_{GS_LS})$$

Where FSW is the switching frequency and QGHS and QGLS are respectively the gate charge of the high side and the gate charge of the low side at the VCC driving voltage. The very low thermal resistance package used for the PX3519 allows the device to avoid any usage of external resistances to decrease the power dissipation inside the driver even with high driving voltage. Since the thermal resistance is strongly influenced by the numbers of layers used in the board, it is recommended to check roughly the expected junction temperature via the power calculation.

# 5.4 Inputs to the internal control circuits

The **PWM** is the control input to the IC from an external PWM controller and is compatible with 3.3V.

The PWM input has tri-state functionality. When the voltage remains in the specified PWM-shutdown-window for at least the PWM-shutdown-holdoff time T\_tsshd, the operation will be suspended by keeping both MOSFET gate outputs low. Once left open, the pin is internally fixed to  $V_{PWM_O}$  = 1.6 V level.

| PWM logic level                         | Driver output             |  |  |

|-----------------------------------------|---------------------------|--|--|

| Low                                     | LGATE= High, UGATE = Low  |  |  |

| High                                    | LGATE = Low, UGATE = High |  |  |

| Open (left floating, or High impedance) | LGATE = Low, UGATE = Low  |  |  |

#### Table 12 PWM Pin Functionality

During power-up sequence, the initial state of the PWM signal is ignored, until the first rising edge. Since all the thresholds are derived from an internal linear regulator they will not depend on the VCC input.

### 5.5 Enable pin

The EN pin has the main function to control the driver stage itself and enables operation. Once the voltage across the EN pin is higher than the rising edge threshold of the EN pin and the voltage across the VCC pin is above the rising edge threshold of the UVLO, the driver stage turns on and off the MOSFET based on the PWM status. The EN pin can not be left floating.

The enable can be used for three different purposes:

- 1. Power sequence: It can be delayed in order to turn on the power stage once VCC is at the expected level. This will reduce the probability of improper turn on sequences or oscillation created by unstable conditions.

- 2. Power saving: there are two ways of disabling the driver stage: the first one is through the PWM signal; once the PWM signal is in the tri-state window the gate activity is stopped. The second one is the EN pin; once the enable pin is pulled below the falling edge threshold the driver stage is completely switched off. The difference between the two methods is basically that the PWM still leaves alive all the comparators and the auxiliary voltages, so that the consumption of the power stage is not at the minimum level.

- 3. Zero Cross: if the controller is capable to detect the crossing of the inductor current, the EN pin could be used to switch off the low side MOSFET faster than the PWM (due to the hold off time)'in order to avoid the current reverse.

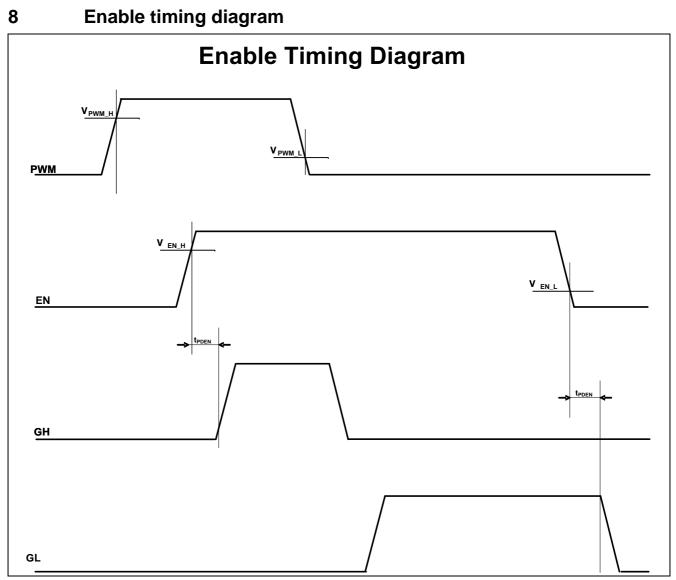

Figure 5 Enable pin

# 5.6 Layout consideration

The PX3519 has a good protection system against unwanted overshoot and undershoot; the PHASE pin can range between dynamically -12V to 25V.

The parasitic inductances of the PCB and of the power devices' packaging (both upper and lower MOSFETs) can cause serious ringing, exceeding absolute maximum rating of the devices. Careful layout can help minimize such unwanted stress. The following advice is meant to lead to an optimized layout:

Keep decoupling loops (VCC-GND and BOOT-PHASE) as short as possible and use high quality ceramic capacitance with low ESR (10mOhm) and low ESL (lower than 1nH).

Minimize trace inductance, especially on low-impedance lines. All power traces (UGATE, PHASE, LGATE, GND, VCC) should be short and wide, as much as possible.

Minimize the area of the PHASE node. Ideally, the source of the upper and the drain of the lower MOSFET should be as close as close as possible. Minimize the current loop of the output and input power trains. Short the source connection of the lower MOSFET to ground as close to the transistor pin as feasible. Input capacitors (especially ceramic decoupling) should be placed as close to the drain of upper and source of lower MOSFETs as possible.

To optimize heat spreading, copper should be placed directly underneath the IC whether it has an exposed pad or not. The copper area can be extended beyond the bottom area of the IC and/or connected to buried copper plane(s) with thermal vias. This combination of vias for vertical heat escape, extended copper plane, and buried planes for heat spreading allows the IC to achieve its full thermal potential.

Application

# 6 Application

Figure 6 Pin interconnection outline (transparent top view)

Gate driver timing diagram

# 7 Gate driver timing diagram

Figure 7 Adaptive gate driver timing diagram

Enable timing diagram

Figure 8 Enable Vs PWM timing diagram

**Mechanical drawing**

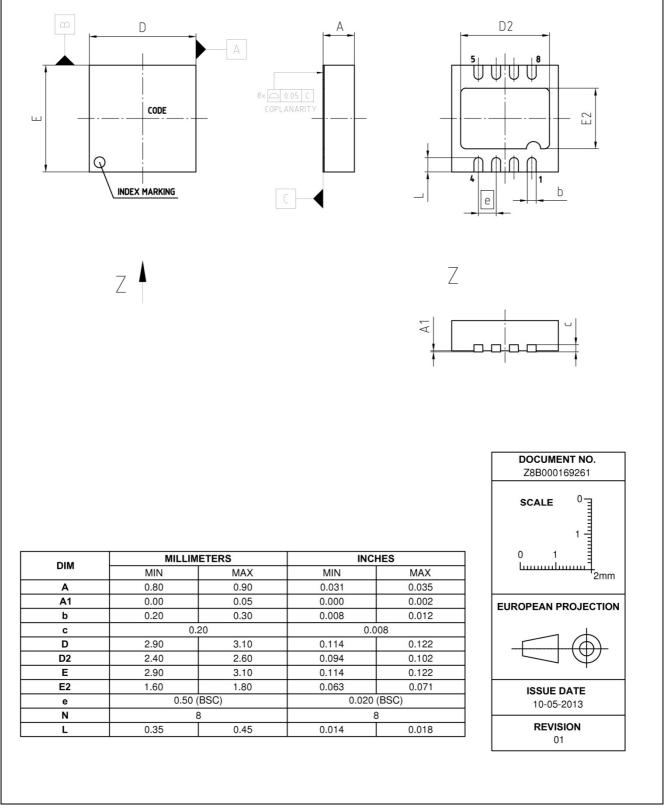

# 9 Mechanical drawing

Mechanical drawing

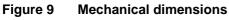

Figure 10 Footprint and solder stencil recommendations

www.infineon.com

Published by Infineon Technologies AG

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Infineon: PX3519