**ILD2111**

Digital DC/DC Buck Controller IC

Datasheet

Revision 1.0, 2015-04-08

# Digital DC/DC Controller with I-Set Product highlights

- Assumes control of functionality where a microcontroller is required in conventional systems

- Device configurable by a comprehensive parameter set

- High efficiency over wide input and output ranges

- High accuracy of +/-5% over output current range and useful temperature

#### **Features**

- Hysteretic current regulation

- Output current adjustable in up to 16 steps with a dynamic range of 1:4 between min. and max. configurable by an external resistor

- Flicker-free and phase-aligned PWM dimming based on input PWM signal

- Fully configurable internal and external smart overtemperature protection

- · Open/short load protection

- Overpower protection

## **Applications**

LED drivers, e.g. 2-stage professional lighting systems

Integrated electronic control gear for LED luminaires

#### **Description**

The ILD2111 high-performance is а microcontroller-based digital DC/DC buck LED controller, designed as a constant current source. The driving current is adjustable with a simple external resistor. Flicker-free dimming supported by means of phase-aligned PWM LED current. An ASSP digital microcontroller-based engine is highly configurable using a comprehensive parameter set to provide fine tuning of operation and protection features. High-precision hysteretic output current regulation is achieved thanks to the digital control loops.

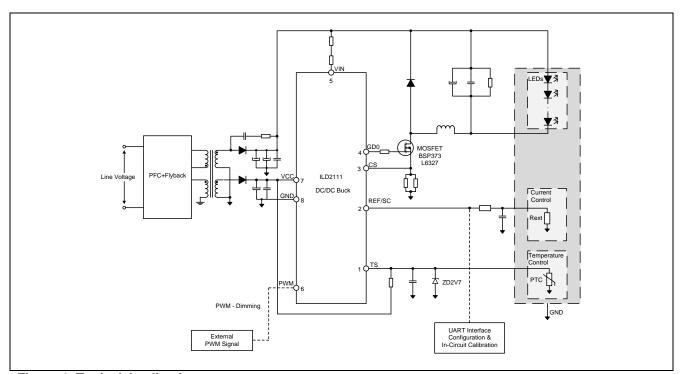

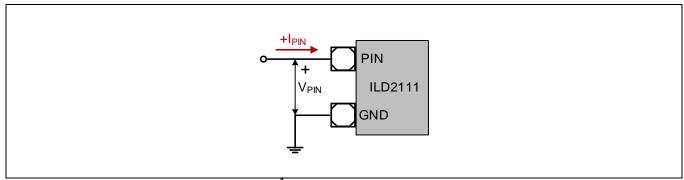

Figure 1. Typical Application

| Product type | Package     |  |  |  |  |

|--------------|-------------|--|--|--|--|

| ILD2111      | PG-DSO-8-58 |  |  |  |  |

## Table of Contents

# **Table of Contents**

| 1     | Pin Configuration and Description                                        | 4  |

|-------|--------------------------------------------------------------------------|----|

| 2     | Block Diagram                                                            | 5  |

| 3     | Functional Description                                                   | 6  |

| 3.1   | Introduction                                                             | 6  |

| 3.2   | Main Supply (VCC)                                                        | 11 |

| 3.3   | Controller Features                                                      | 11 |

| 3.3.1 | Configurable Leading Edge Blanking (LEB) and Sampling Time at Pin CS     | 12 |

| 3.3.2 | Configurable Gate Driver Output                                          | 12 |

| 3.3.3 | Reference Current Setup                                                  | 13 |

| 3.3.4 | Output Current Control and Measuring                                     | 17 |

| 3.3.5 | Current Startup, Soft-Start and Shutdown Control                         |    |

| 3.4   | Current Ripple vs. Switching Frequency Control Scheme                    | 20 |

| 3.4.1 | Fixed Current Ripple                                                     |    |

| 3.4.2 | Frequency and Ripple Control                                             |    |

| 3.5   | Input Voltage Measurement and Calibration                                |    |

| 3.6   | Protection Features                                                      |    |

| 3.6.1 | Undervoltage Protection for DC Input Line – V <sub>IN</sub> Undervoltage |    |

| 3.6.2 | Overvoltage Protection for DC Input Line – V <sub>IN</sub> Overvoltage   |    |

| 3.6.3 | Output Undervoltage Protection – V <sub>OUT</sub> Undervoltage           |    |

| 3.6.4 | Open Output Protection                                                   |    |

| 3.6.5 | Output Overvoltage Protection – V <sub>OUT</sub> Overvoltage             |    |

| 3.6.6 | Output Overpower Protection – P <sub>OUT</sub> Overpower                 |    |

| 3.6.7 | Overtemperature Protection                                               |    |

| 3.6.8 | Overcurrent Protection – Level 2 (OCP2)                                  |    |

| 3.6.9 | Functional Protections                                                   |    |

| 3.7   | External PWM Dimming                                                     |    |

| 3.8   | Output Current PWM Modulation                                            |    |

| 3.9   | Configuration                                                            |    |

| 3.9.1 | Overview of Configurable Parameters                                      |    |

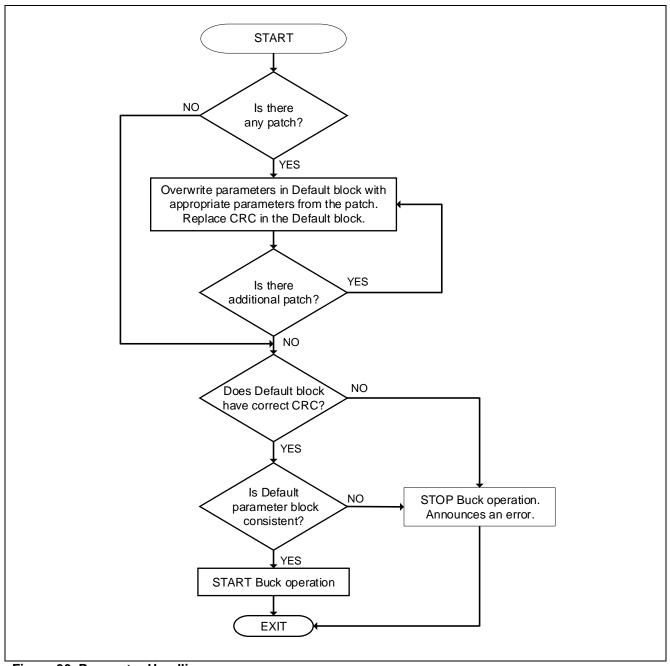

| 3.9.2 | Configuration Procedure – Parameter Handling                             | 52 |

| 4     | Electrical Characteristics                                               | 54 |

| 4.1   | Definitions                                                              |    |

| 4.2   | Absolute Maximum Ratings                                                 |    |

| 4.3   | Package Characteristics                                                  |    |

| 4.4   | Operating Conditions                                                     |    |

| 4.5   | DC Electrical Characteristics                                            | 57 |

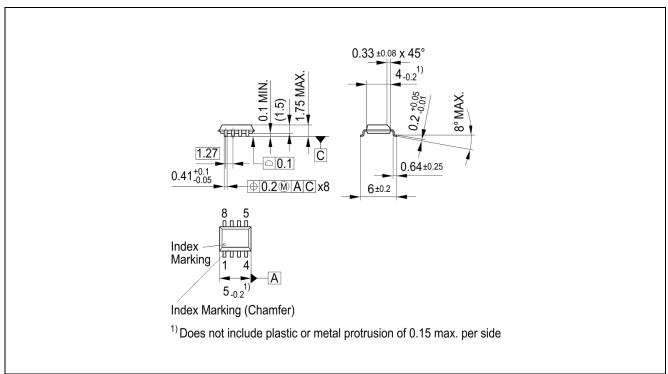

| 5     | Outline Dimensions                                                       | 63 |

# 1 Pin Configuration and Description

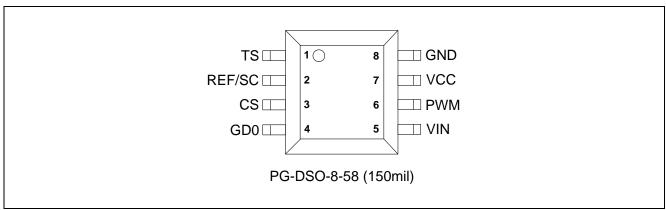

The pin configuration is shown in Figure 2 and Table 1-1. The pin functions are described later.

Figure 2. Pin Configuration

Table 1-1. Pin Definitions and Functions

| Symbol | Pin | Туре | Function                                                                                                                                                                                   |

|--------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TS     | 1   | I    | Temperature Sensor The pin TS is used for external temperature measurement using PTC or an appropriate passive temperature sensor.                                                         |

| REF/SC | 2   | Ю    | Reference/Serial Communication                                                                                                                                                             |

|        |     |      | The pin REF/SC is multiplexed. During startup it is used for reference current sensing by means of an external RC circuit. Afterwards, it serves as a UART serial communication interface. |

| CS     | 3   | I    | Current Sense                                                                                                                                                                              |

|        |     |      | Current measurement on an external shunt resistor.                                                                                                                                         |

| GD0    | 4   | 0    | Gate Driver Output 0                                                                                                                                                                       |

|        |     |      | Output for directly driving a power MOS.                                                                                                                                                   |

| VIN    | 5   | I    | Voltage Input Voltage input measurement. Requires an external series resistor for voltage sensing and current limitation.                                                                  |

| PWM    | 6   | ı    | PWM Dimming Signal                                                                                                                                                                         |

|        |     |      | Input for PWM-based dimming signal.                                                                                                                                                        |

| VCC    | 7   | I    | Positive Voltage Supply                                                                                                                                                                    |

|        |     |      | IC power supply.                                                                                                                                                                           |

| GND    | 8   | 0    | Power and Signal Ground                                                                                                                                                                    |

**Block Diagram**

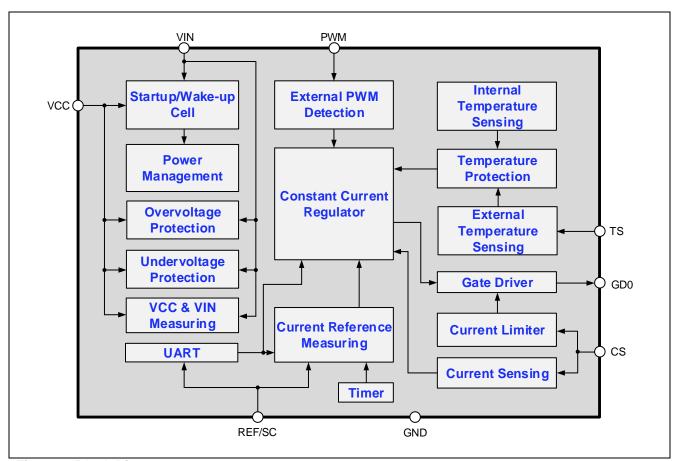

# 2 Block Diagram

The block diagram of ILD2111 is shown in Figure 3.

Figure 3. Block Diagram

# 3 Functional Description

The functional description provides an overview of the integrated functions and features, and their relationship. The parameters and equations provided are based on typical values at  $T_A = 25$ °C. The corresponding minimum and maximum values are shown in Section 4, Electrical Characteristics.

#### 3.1 Introduction

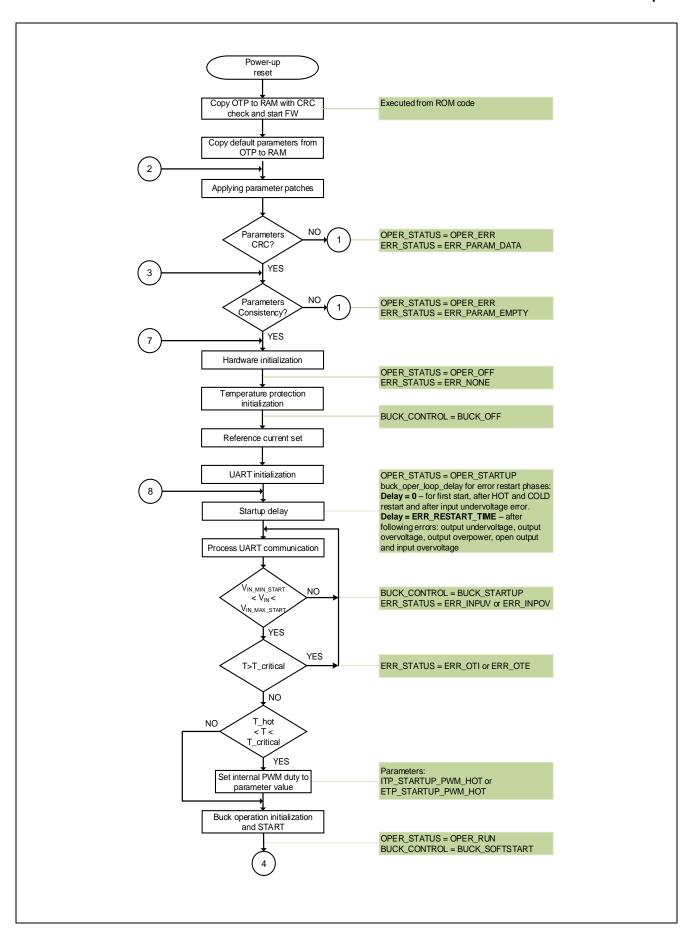

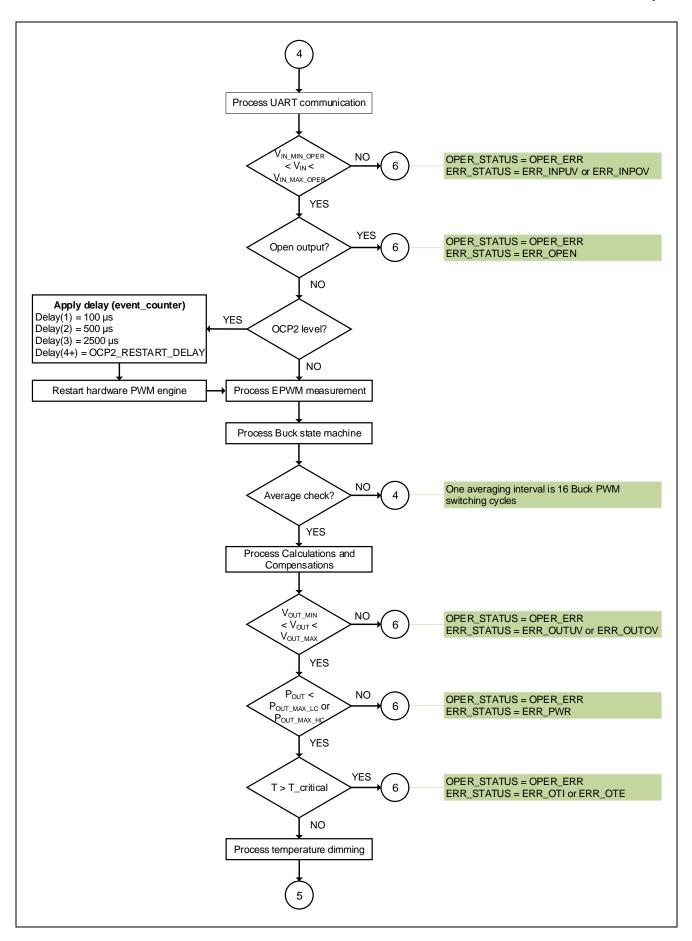

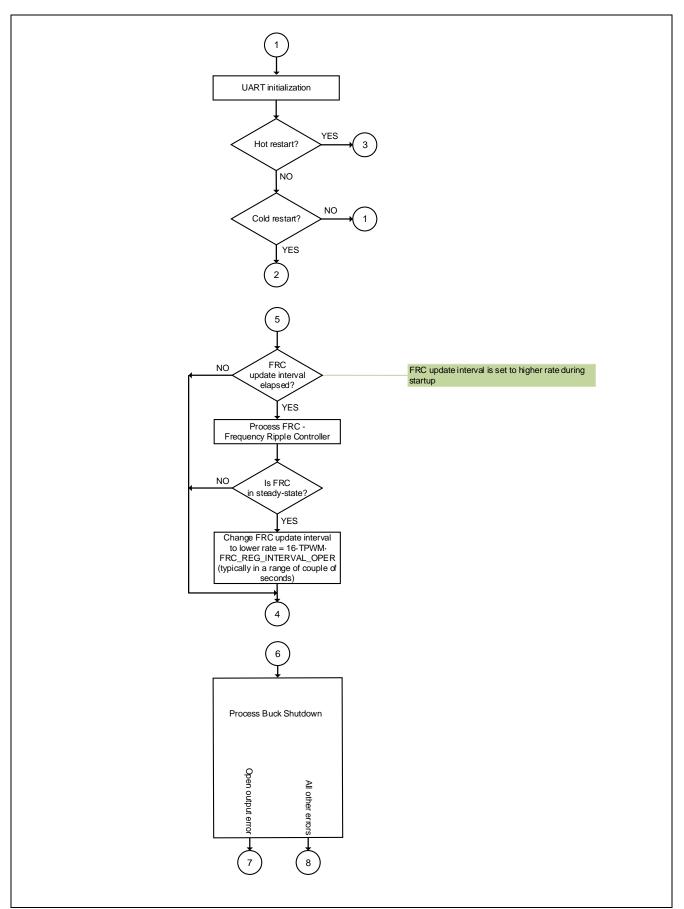

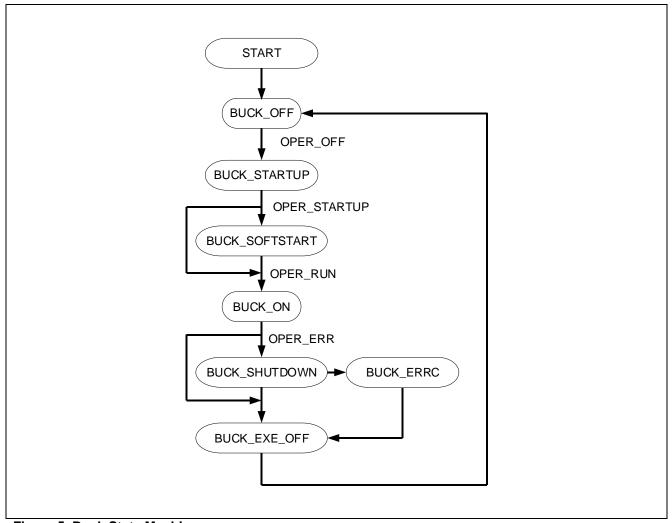

The ILD2111 is a high-performance digital microcontroller-based DC/DC buck LED controller designed as a constant current source with hysteretic output current regulation. The controller typically uses a floating buck topology operating in a Continuous Conduction Mode (CCM). In order to reduce switching losses and increase efficiency, as well as to control the switching frequency over a wide variety of external component values, input voltage and load variations, a frequency ripple control is introduced. Both internal and external temperature measurements are implemented and accompanied with an intelligent temperature protection algorithm with two threshold values. The controller utilizes a variety of protection features, including overpower, open and short load conditions. The ILD2111 is a dimmable device controlled by an external PWM signal. The device can be parameterized by means of a single pin UART interface at the REF/SC pin (see Section 3.9). A complete top-level device operation process, including protection and error handling, is shown in Figure 4. Table 3-1 shows device operating statuses, buck statuses associated with the buck state machine, as well as error and associated error codes. The buck state machine diagram is shown in Figure 5.

Figure 4. Device Operating Flowchart

Operating statuses are presented in Table 3-1 below.

| Status         | Operating Statuses | Value             | Description                                                        |  |  |

|----------------|--------------------|-------------------|--------------------------------------------------------------------|--|--|

| OPER_STATUS    | OPER_OFF           | 0000 <sub>H</sub> | Off - initial buck state                                           |  |  |

|                | OPER_STARTUP       | 0001 <sub>H</sub> | Startup - Vin & temperature checking                               |  |  |

|                | OPER_RUN           | 0002 <sub>H</sub> | Run                                                                |  |  |

|                | OPER_ERR           | 0004 <sub>H</sub> | Stopped by error                                                   |  |  |

|                | OPER_STOP          | 0008 <sub>H</sub> | Stopped by UART command                                            |  |  |

| ERR_STATUS     | ERR_NONE           | 0000 <sub>H</sub> | No errors                                                          |  |  |

|                | ERR_INPUV          | 0001 <sub>H</sub> | Input undervoltage                                                 |  |  |

|                | ERR_INPOV          | 0002 <sub>H</sub> | Input overvoltage                                                  |  |  |

|                | ERR_OUTUV          | 0004 <sub>H</sub> | Output undervoltage                                                |  |  |

|                | ERR_OUTOV          | 0008 <sub>H</sub> | Output overvoltage                                                 |  |  |

|                | ERR_PWR            | 0010 <sub>H</sub> | Output overpower                                                   |  |  |

|                | ERR_OPEN           | 0020 <sub>H</sub> | Output open                                                        |  |  |

|                | ERR_OCP            | 0040 <sub>H</sub> | OCP2 level detection                                               |  |  |

|                | ERR_OTI            | 0080 <sub>H</sub> | Overtemperature internal sensor                                    |  |  |

|                | ERR_OTE            | 0100 <sub>H</sub> | Overtemperature external sensor                                    |  |  |

|                | ERR_PARAM_EMPTY    | 0400 <sub>H</sub> | Default parameter block empty                                      |  |  |

|                | ERR_PARAM_DATA     | 0800 <sub>H</sub> | Default parameter block checksum error                             |  |  |

| ERR_MODE       | ERR_MODE_LATCH     |                   | Error handling latch                                               |  |  |

|                | ERR_MODE_RESTART   |                   | Error handling auto restart                                        |  |  |

|                | ERR_MODE_OFF       |                   | Error handling is off                                              |  |  |

|                | ERR_MODE_NOP       |                   | Error handling does not affect auto restart counter                |  |  |

| BUCK_STATUS 1) | BUCK_OFF           |                   | Buck is off                                                        |  |  |

|                | BUCK_STARTUP       |                   | Buck is in start-up phase (initialized, waiting for                |  |  |

|                |                    |                   | start-up condition, i.e. voltage and temperature)                  |  |  |

|                | BUCK_SOFTSTART     |                   | Buck is in soft-start phase (implements increasing                 |  |  |

|                |                    |                   | current slope until reaching reference current)                    |  |  |

|                | BUCK_SHUTDOWN      |                   | Buck is in shutdown phase (implements current                      |  |  |

|                |                    |                   | decreasing slope)                                                  |  |  |

|                | BUCK_EXE_OFF       |                   | Buck is executing off, buck operation stopped                      |  |  |

|                | BUCK_ERRC          |                   | Buck in error state (generate small error current)                 |  |  |

|                | BUCK_ON 2)         |                   | Buck is on (normal operation, default state of                     |  |  |

|                |                    |                   | operation)                                                         |  |  |

|                |                    |                   | During normal operation, in addition to the                        |  |  |

|                |                    |                   | aforementioned operations, the following actions will be executed: |  |  |

|                |                    |                   | - Open-output processing                                           |  |  |

|                |                    |                   | Output current PWM dimming processing                              |  |  |

|                |                    |                   | - V <sub>CC</sub> / internal temperature measurement and           |  |  |

|                |                    |                   | processing                                                         |  |  |

|                |                    |                   | - External temperature measurement and                             |  |  |

|                |                    |                   | processing                                                         |  |  |

|                |                    |                   | <ul> <li>OCP1 - peak current processing</li> </ul>                 |  |  |

|                |                    |                   | OCP2 - peak current processing                                     |  |  |

|                |                    |                   | EPWM measurement and processing                                    |  |  |

|                |                    |                   | - PI regulator processing                                          |  |  |

|                |                    |                   | - Input over- and undervoltage processing                          |  |  |

|                |                    |                   | Output over- and undervoltage processing                           |  |  |

|                |                    |                   | <ul> <li>Output overpower processing</li> </ul>                    |  |  |

<sup>1)</sup> See buck state machine in Figure 5.

The number of averaged buck cycles for steady-state operation, where calculations and protections are handled, is defined by the constant Buck\_steady\_delay (see **Table 3-14**).

Figure 5. Buck State Machine

## 3.2 Main Supply (VCC)

The device is powered via the VCC pin. All device supply voltages are internally generated from the  $V_{\text{CC}}$  voltage.

## 3.3 Controller Features

Table 3-2 gives an overview of the controller features that are described in the referenced sections.

**Table 3-2. Controller Features**

| Configurable Leading Edge Blanking (LEB) and Sample Time at Pin CS | Section 3.3.1        |

|--------------------------------------------------------------------|----------------------|

| Configurable Gate Driver Output                                    | Section <b>3.3.2</b> |

| Reference Current Setup                                            | Section 3.3.3        |

| Output Current Control and Measuring                               | Section 3.3.4        |

| Current Startup, Soft-Start and Shutdown Control                   | Section <b>3.3.5</b> |

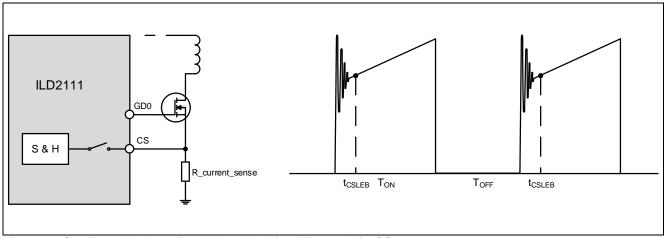

## 3.3.1 Configurable Leading Edge Blanking (LEB) and Sampling Time at Pin CS

A configurable leading edge blanking time  $t_{CSLEB}$  is integrated into the current sensing path to provide more accurate output current sensing and regulation. Leading-edge spikes during the PowerMOS switch-on phase, as shown in **Figure 6**, can affect sampled output current values, resulting in imprecise current sensing. The LEB time is used to prevent false overcurrent detection, while the sample time defines the moment of the current sampling for A/D conversion. The time  $t_{CSLEB}$  and the sampling time are configured by the constants CS\_blanking\_time and CS\_sample\_time respectively (see **Table 3-19**) in order to provide output current sampling at the moment when no spikes are present.

Figure 6. Configurable Leading Edge Blanking Time at Pin CS

## 3.3.2 Configurable Gate Driver Output

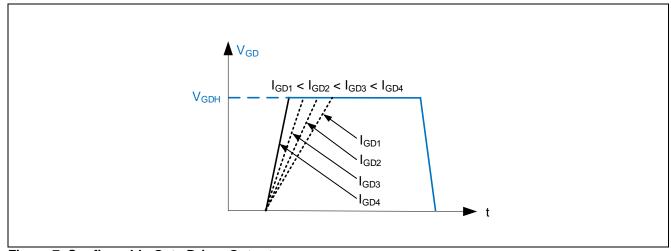

The gate driver output (GD0) can be configured with respect to the final voltage level and gate drive current, which influence the rising voltage slope for switching on the external PowerMOS (see Figure 7) and therefore a switch-on time. A compromise should and could be made between switching power losses and electromagnetic radiation by using these parameters (especially gate drive current values). The output gate voltage  $V_{GDH}$  and gate current  $I_{GD}$  can be programmed by the parameters, providing an adjustable PowerMOS turn-on time. The programmable output gate voltage range is from 4.5 V to 15 V (see Table 3-8).  $V_{GDH}$  cannot be higher than the power supply voltage  $V_{CC}$ , regardless of the programmed value. The programmable gate current range is from 30 mA to 118 mA (see Table 3-8). Figure 7 shows the gate driver output voltage signal. Different rising slopes correspond to different gate driving currents. The slope is proportional to the current.

Figure 7. Configurable Gate Driver Output

## 3.3.3 Reference Current Setup

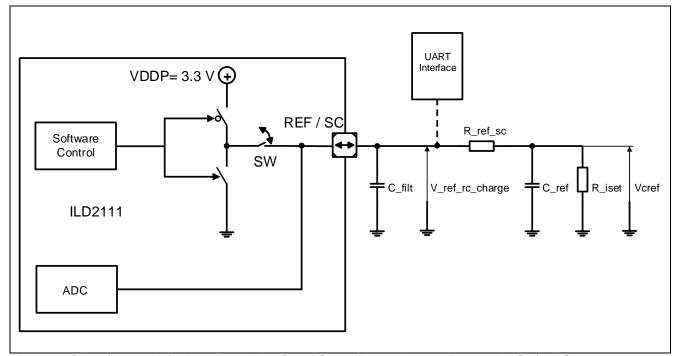

The reference current value is obtained by measurement using the value of the external resistor R\_iset connected to the pin 'REF/SC' together with the reference capacitor C\_ref via the discharge time of the capacitor (see Figure 8 and Figure 9). Depending on the resistance of R\_iset, the appropriate reference current, stored in a table of 16 currents (see Table 3-12), is used as a reference for the output current. The reference current setup procedure (I-set) will always be executed during the startup sequence or during Open output protection recovery – see Section 3.6.4.

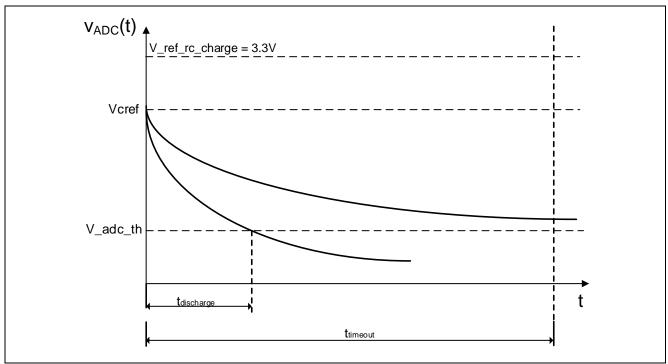

When the internal switch SW is turned on for a short period of time defined by the constant RC\_cap\_charge\_time (see Table 3-19) while the digital output is high, the C\_ref is fully charged to Vcref, where this voltage depends on the internal VDDP voltage and voltage divider R\_ref\_sc - R\_iset. R\_ref\_sc is used for decoupling the reference current measurement circuitry and serial UART communication. Care must be taken that the ratio of R\_iset to R\_ref\_sc is sufficient to have only a low impact on Vcref. Otherwise, it has to be included in the time thresholds calculation. When the switch is turned off, the C\_ref discharges through the external resistor R\_iset. The discharging time of the capacitor C\_ref depends on the value of the external resistor. During the discharging interval, the pin voltage is measured by ADC while an internal timer measures the discharging time. When the capacitor voltage drops below the constant threshold level V\_adc\_th (constant V\_ADC\_th, see Table 3-13), the internal timer value is latched and used to determine the reference current from the predefined I-set table.

Figure 8. Charging and Discharging of the C\_ref Capacitance Depending on the Switch State

C\_filt is a ceramic capacitor used to filter noise, caused by the converter switching operation. Mainly it is used to suppress noise for ADC measurement as well as UART communication.

Figure 9. C\_ref Discharging Interval Determined by the Reference Resistor Value

The charging voltage Vcref is calculated as:

$$Vcref = \frac{R\_iset}{R\ iset + R\ ref\ sc} \cdot V\_ref\_rc\_charge. \tag{1}$$

The equation for V\_adc\_th is:

$$V_{adc\_th} = Vcref \cdot e^{-\frac{t_{discharge}}{R_{iset} \cdot C_{ref}}}.$$

(2)

Therefore:

$$t_{discharge} = R_{iset} \cdot C_{ref} \cdot ln \frac{v_{cref}}{v_{-adc\_th}}.$$

(3)

If a lower voltage threshold is not reached after the predefined time-out period  $t_{\text{timeout}}$  (constant RC\_measurement\_timeout, see **Table 3-19**), the reference current determination process ends and the last value from the current table is taken as the reference (Ref\_current\_16, see **Table 3-12**). Component values and their tolerances must provide unique thresholds in order to be detected appropriately (see **Figure 10**).

More accurate equations will be obtained if typical component tolerance values are included.

The following are assumed:

- Maximum reference resistance: R\_iset\_max(n) = R\_iset(n) + R\_iset\_tolerance<sup>1</sup>

- Minimum reference resistance: R iset min(n) = R iset(n) R iset tolerance

- Maximum reference capacitance: C\_ref\_max = C\_ref + C\_ref\_tolerance<sup>2</sup>

- Minimum reference capacitance: C\_ref\_min = C\_ref C\_ref\_tolerance

Datasheet 14 Revision 1.0, 2015-04-08

<sup>&</sup>lt;sup>1</sup> The reference resistance R\_ref\_sc is used to decouple the UART interface and current set resistance R\_iset due to multiplexed functionality of the REF/SC pin. In this case, the tolerance of the R\_ref\_sc resistance is not taken into account (its tolerance is ignored).

<sup>&</sup>lt;sup>2</sup> Examples of C\_ref\_tolerance are the tolerance of the used capacitor as well as the cable capacitance that connects R\_iset to the detection circuit.

Therefore, minimum and maximum discharging times are given by:

$$T_RC_n)_min = R_iset_min(n) \cdot C_ref_min \cdot ln \frac{Vcref_min(n)}{V \ adc \ th}$$

(4)

and

$$T_RC_n)_max = R_iset_max(n) \cdot C_ref_max \cdot ln \frac{Vcref_max(n)}{V_adc_th}.$$

(5)

Where n is the ordinal number of the resistor, while Vcref\_min and Vcref\_max are the minimum and maximum voltage values of charged capacitance respectively:

$$Vcref\_min = \frac{R\_iset\_min}{R\_iset\_min + R\_ref\_sc} \cdot V\_ref\_rc\_charge$$

(6)

and

$$Vcref\_max = \frac{R\_iset\_max}{R\_iset\_max + R\_ref\_sc} \cdot V\_ref\_rc\_charge.$$

(7)

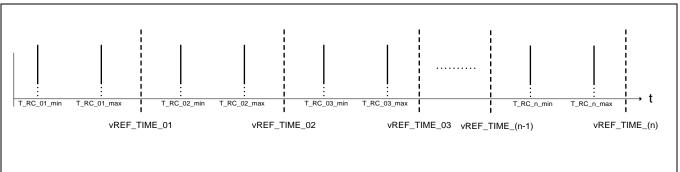

Figure 10. Time Constant vREF\_TIME\_n Threshold Calculations

As shown above, the discharging time threshold is obtained as follows:

$$vREF\_TIME\_n = T\_RC\_n\_max + \frac{T\_RC\_(n+1)\_min-T\_RC\_n\_max}{2}.$$

(8)

The last discharge time threshold is given by:

$$vREF\_TIME\_n = T\_RC\_n\_max + \frac{T\_RC\_n\_max - T\_RC\_n\_min}{2}.$$

(9)

The measured discharge time - t<sub>discharge</sub> is compared with the calculated thresholds, beginning with the smallest, and based on that, it will be determined which reference resistor is detected, hence reference output current. For example, if the measured discharge time is greater than vREF\_TIME\_01, vREF\_TIME\_02, vREF\_TIME\_03 and smaller than vREF\_TIME\_04, the 4<sup>th</sup> reference resistor and reference current from the list will be chosen (see Table 3-3).

The ratio between the maximum and minimum current has to be equal to or less than 4 ( $I_ref_max / I_ref_min \le 4$ ) for best current accuracy. For example, if the minimum reference current is 250 mA, the maximum reference current from the range should not exceed 1000 mA.

The components (R\_iset, C\_ref) must be carefully selected to avoid overlapping time intervals, because in that case an appropriate threshold could not be calculated to provide unique detection. For example, if the resistance values are too close (including tolerances), discharge time intervals will overlap, and calculated thresholds will be set inside the overlapped area. Therefore it cannot be guaranteed that the same current will be selected across different IC production series and external component tolerances.

Reference current determination only takes place during the initial chip startup and after the load has been disconnected - open output is detected. During normal buck operation, the REF/SC pin can be used as a communication port.

## **Example**

For typical applications, which cover – for example – the outputs ranging from 250 mA to 800 mA (in 50 mA steps), reference resistor values for the specific current values (assuming C\_ref = 10 nF and threshold voltage value of V\_adc\_th = 0.6075 V) are given in Table 3-3. Resistors from the series E96 with a variation (tolerance) of 1% are used. The reference pin serial resistor is R\_ref\_sc = 3.3 k $\Omega$ . The recommended capacitor C\_ref tolerance should be  $\leq 5\%^1$ . The recommended C\_ref capacitor type is a zero-drift CoG (NPO).

**Table 3-3. Reference Resistor Values Example**

| Ordinal number | I_ref_n [mA] | R_iset_n [kΩ] | vREF_TIME_n [µs] |  |  |

|----------------|--------------|---------------|------------------|--|--|

| 1              | 800          | 2.15          | 70               |  |  |

| 2              | 750          | 10.00         | 180              |  |  |

| 3              | 700          | 15.00         | 280              |  |  |

| 4              | 650          | 21.50         | 430              |  |  |

| 5              | 600          | 610           |                  |  |  |

| 6              | 550          | 43.20         | 780              |  |  |

| 7              | 500          | 53.60         | 950              |  |  |

| 8              | 450          | 63.40         | 1110             |  |  |

| 9              | 400          | 71.50         | 1270             |  |  |

| 10             | 350          | 82.50         | 1430             |  |  |

| 11             | 300          | 90.90         | 1580             |  |  |

| 12             | 250          | 100.00        | 1860             |  |  |

Although, typically, the application uses less than 16 reference currents, all parameters (Ref\_current\_01- Ref\_current\_16, see Table 3-12) must be filled (arranged) in 4 groups, using copies with the same reference current. It is assumed that approximately the same currents have approximately the same parameters. Thereafter, all appropriate reference time thresholds (Reference\_time\_01 - Reference\_time\_16) will be automatically allocated to the groups (see Table 3-19). Each group consists of four consecutive currents and each group is associated with the unique set of FRC parameters. The currents from the same group will have the same minimum and maximum switching frequency limits and minimum and maximum current ripple limits as well (see Table 3-20).

One possible arrangement is given below in **Table 3-4**.

<sup>&</sup>lt;sup>1</sup> For different component tolerances, different discharge times will be obtained by equations. The resistor values in **Table 3-3** are given as examples. The number of different reference resistor values must match the number of different reference currents. For different applications (different output currents and output power), different values of the external resistors can be taken.

**Table 3-4. Reference Current Arrangement**

| Group number | Reference Currents     |

|--------------|------------------------|

| 1.           | 800 mA, 750 mA, 700 mA |

| 2.           | 650 mA, 600 mA, 550 mA |

| 3.           | 500 mA, 450 mA, 400 mA |

| 4.           | 350 mA, 300 mA, 250 mA |

## 3.3.4 Output Current Control and Measuring

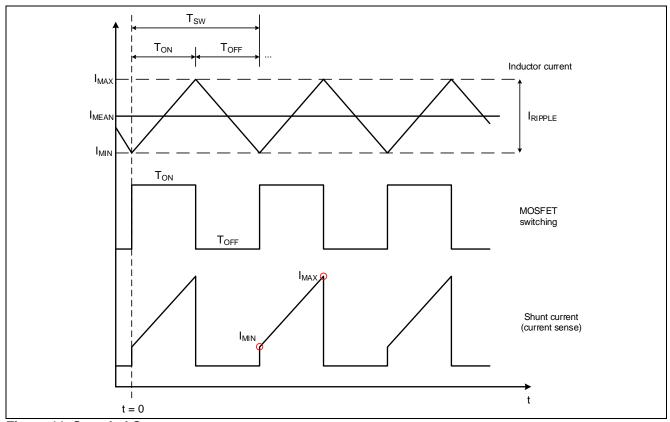

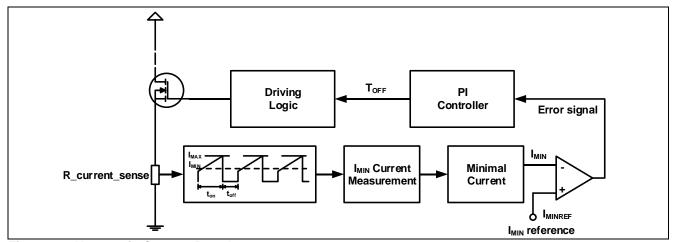

The output current is measured at the CS pin by means of an external shunt resistor. The controller, using floating buck topology, operates in a Continuous Conduction Mode (CCM) and is realized as a hysteretic current controller. The average output current is regulated using minimum and maximum currents ( $I_{MAX}$  and  $I_{MIN}$ , see Figure 11). Maximum and minimum current values are defined with respect to allowed output current ripple. The maximum current is set as a true analog comparator threshold value using an internal DAC. The minimum current value is regulated by the internal PI regulator controlling  $T_{OFF}$  time.

When the MOSFET is turned on,  $T_{ON}$  is approximately given as follows (all resistances and voltage drops of used components are neglected):

$$T_{ON} = (I_{MAX} - I_{MIN}) \cdot \frac{L_{EXT}}{V_{IN} - V_{OUT}} = I_{RIPPLE} \cdot \frac{L_{EXT}}{V_{IN} - V_{OUT}}.$$

(10)

When the MOSFET is turned off,  $T_{OFF}$  is approximately given as follows (all resistances and voltage drops of used components are neglected):

$$T_{OFF} = (I_{MAX} - I_{MIN}) \cdot \frac{L_{EXT}}{V_{OUT}} = I_{RIPPLE} \cdot \frac{L_{EXT}}{V_{OUT}}.$$

(11)

where  $V_{\text{IN}}$  and  $V_{\text{OUT}}$  are the input and output voltages respectively and  $L_{\text{EXT}}$  is the buck inductance.

Therefore, the switching frequency of the buck cycle can be rendered as:

$$f_{SW} = \frac{1}{T_{ON} + T_{OFF}} = \frac{1}{I_{RIPPLE} \cdot L_{EXT} \cdot (\frac{1}{V_{IN} - V_{OUT}} + \frac{1}{V_{OUT}})}.$$

(12)

Figure 11. Sampled Current

When the current reaches its maximum value ( $I_{MAX}$ ), the MOSFET is turned off for a duration of  $T_{OFF}$ , which is defined by the output of the PI regulator. After this interval elapses, the MOSFET is turned on again, the minimum current ( $I_{MIN}$ ) is sampled and the mean current for the entire PWM interval is calculated as:

$$I_{MEAN} = \frac{I_{MAX} + I_{MIN}}{2}. (13)$$

The minimum current samples are averaged and averaging happens every 16 switching cycles. This average value is then compared to a reference providing an error signal for the PI regulator, as shown in Figure 12. Based on that error, the PI regulator calculates the new  $T_{OFF}$  time resulting in output current regulation, hence closing the regulation loop.

Figure 12. Hysteretic Current Regulator

Revision 1.0, 2015-04-08

PI regulator parameters can be adjusted for faster transient response (dynamic behavior) during startup and more stable output current during normal steady-state operation. These constants (Pl\_shift\_softstart\_lc, Pl\_gain\_shift\_softstart\_hc, Pl\_gain\_shift\_lc and Pl\_gain\_shift\_hc, see Table 3-17) are divided into two groups depending on the current range (constant Ref\_current\_HCTH, see Table 3-14) and operating conditions (startup or normal). Constants for low currents (low range - LC) typically have larger values than high current parameter values (high range - HC) because, for lower currents, the error signal has to be multiplied by a larger number (Gain) to obtain appropriate behavior regarding response and stability of the output current.

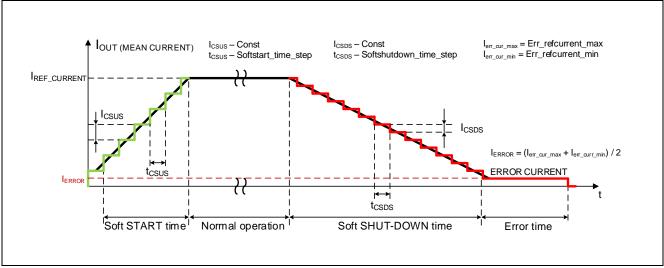

## 3.3.5 Current Startup, Soft-Start and Shutdown Control

Current soft-start and shutdown control is implemented in order to keep the input voltage  $V_{IN}$  and supply voltage  $V_{CC}$ , which come from the primary stage (usually a flyback converter with a transformer auxiliary winding for VCC voltage), within the operating range and stable.

During the soft-start time, the output (mean) current increases slowly with programmable parameters. The startup current is defined by the constant Softstart\_start\_curr (see **Table 3-16**). Current and time steps are defined by the constant Softstart\_curr\_step (see **Table 3-16**) and parameter Softstart\_time\_step respectively (see **Table 3-11**, green line in **Figure 13**). The time step can be set as a number of system ticks (the default value is 100  $\mu$ s). If any of the step ( $I_{CSUS}$  = Softstart\_curr\_step or  $I_{CSUS}$  = Softstart\_time\_step) values is zero, the buck converter will start with a 100% current, and without soft-start.

During soft shutdown time, the output current decreases slowly with programmable current and time steps (constant Softshutdown\_curr\_step - Table 3-16 and parameter Softshutdown\_time\_step - Table 3-11, see red line in Figure 13). Hence, the input voltage  $V_{IN}$  and supply voltage  $V_{CC}$  remain in the operating range and the device will work correctly.

If the soft shutdown is not enough to provide an appropriate operating range (for  $V_{IN}$  and  $V_{CC}$ ), some minimum current (ERROR CURRENT –  $I_{ERROR}$ ) defined by the parameters Err\_refcurrent\_max and Err\_refcurrent\_min (see **Table 3-9** and **Figure 13**) will be generated for a defined time period (error time). When this time interval has elapsed (Error time timeout – constant Err\_current\_time, see **Table 3-14**), the output current is zero. If the current soft shutdown is not needed, it is necessary to set either the parameter to zero ( $I_{CSDS}$  = Softshutdown\_curr\_step or  $I_{CSDS}$  = Softshutdown\_time\_step).

Figure 13. Soft-Start and Soft Shutdown Definitions

## 3.4 Current Ripple vs. Switching Frequency Control Scheme

The switching frequency and output current ripple must be handled in such a way as to ensure that the efficiency is as high as possible and that the ripple is in a proper range with sufficient margin to the specified maximum. Two options for implementing a suitable system are described below.

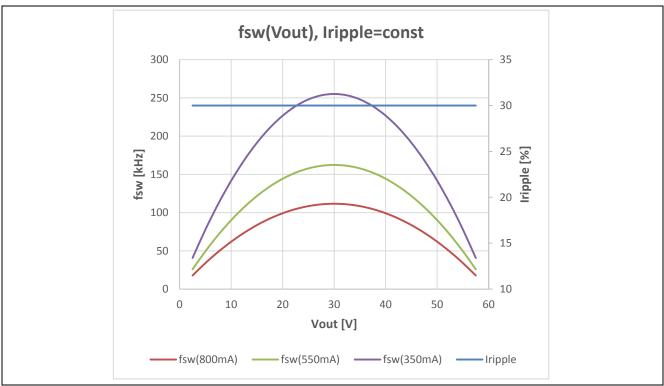

## 3.4.1 Fixed Current Ripple

For a fixed current ripple, it is necessary to choose an appropriate value for the current ripple (parameter Curr\_ripple\_perc, see **Table 3-12**) so the switching frequency does not exceed the maximum allowed frequency around the output voltage  $V_{OUT} = V_{IN}/2$ . The maximum switching frequency should not exceed 250 kHz. Examples for three different current values are shown in **Figure 14**.

Figure 14. Switching Frequency vs. Output Voltage for Constant Output Current Ripple Iripple = 30%

## 3.4.2 Frequency and Ripple Control

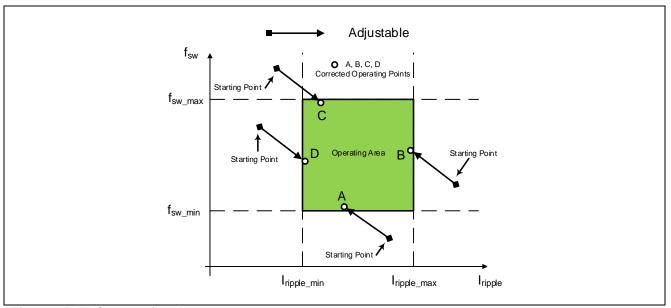

The ILD2111 supports a powerful Frequency Ripple Controller (FRC) because the switching frequency of the Buck converter is not constant due to different loads (different number of LEDs leading to different output voltages). The main idea is to stabilize the operating point within configurable limits (operating area – green field, see **Figure 15**). During startup and normal operation, the frequency-ripple control update interval is defined by the constants FRC\_reg\_interval\_start and FRC\_reg\_interval\_oper (see **Table 3-20**). The number of FRC passes, before being considered steady, is defined by the constant FRC\_pass\_oper\_th (see **Table 3-20**).

Figure 15. FRC Operating Area

All reference current values will be arranged in four groups (see **Table 3-12**) where currents from the same group have the same switching frequency and current ripple limits, as explained in Section **3.3.3**.

For each group, there are predefined (available) parameters and constants (see Table 3-12 and Table 3-20):

- 1) Curr ripple perc Initial (starting) current ripple (in percentage form).

- 2) Curr\_ripple\_min\_(group) Minimum allowed ripple value (minimum absolute output current ripple value, Iripple\_min in mA, not in percentage form).

- 3) Curr\_ripple\_max\_(group) Maximum allowed ripple value (maximum absolute output current ripple value, Iripple\_max in mA, not in percentage form).

- 4) FRC\_freq\_min\_limit\_(group) Maximum allowed Tpwm (defining the minimum switching frequency allowed, fsw min).

- 5) FRC\_freq\_max\_limit\_(group) Minimum allowed T<sub>PWM</sub> (defining the maximum switching frequency allowed, f<sub>sw\_max</sub>).

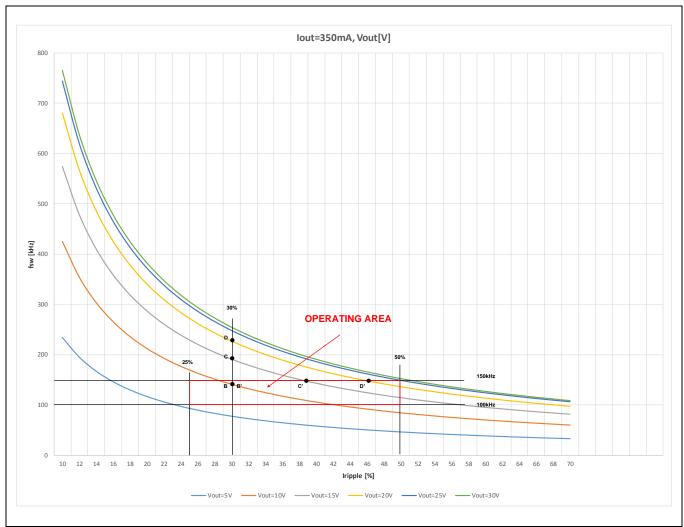

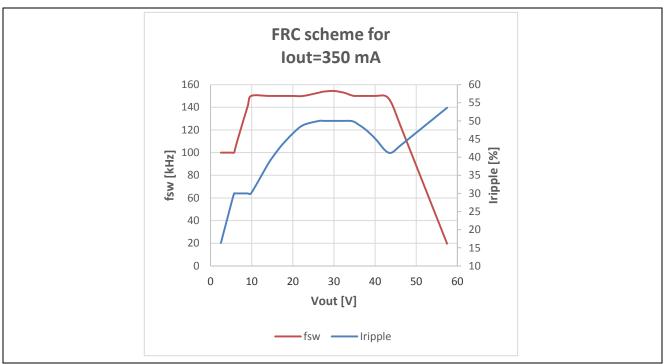

An example is provided below for better understanding. The following parameters apply in this example for  $I_{OUT}$  = 350 mA:

- 1.  $I_{ripple init} = 30\%$  (or 105 mA) Initial starting current ripple.

- 2.  $I_{ripple min} = 25\%$  (or 87.5 mA) Minimum allowed current ripple.

- 3.  $I_{ripple max} = 50\%$  (or 175 mA) Maximum allowed current ripple.

- 4.  $f_{sw\_min} = 100 \text{ kHz}$  (or  $T_{PWM\_max} = 1/f_{sw\_min} = 10 \text{ }\mu s$ ) Minimum allowed switching frequency.

- 5.  $f_{sw max} = 150 \text{ kHz}$  (or  $T_{PWM min} = 1/f_{sw max} = 6.67 \mu s$ ) Maximum allowed switching frequency.

#### The Frequency Ripple Control algorithm works as following:

The system begins to operate with the defined ripple, which is given as a percentage of the average current (e.g.  $I_{ripple\_init} = 30\% I_{OUT}$ ). This value is used to calculate the maximum (adding the half-ripple value to the reference current value) and minimum (subtracting the half-ripple value to the reference current value) hysteretic currents. There are several possible cases depending on the output voltage:

- 1) If the achieved operating frequency is within allowed borders (defined by  $f_{sw\_min}$  and  $f_{sw\_max}$ ), and the starting value of the ripple is within allowed absolute ripple borders (defined by  $I_{ripple\_min}$  and  $I_{ripple\_max}$ ), no correction will be performed (e.g. Vout = 10 V orange curve, operating point B is in the operating area, B=B', see Figure 16).

- 2) If the achieved operating frequency is above the maximum allowed switching frequency  $f_{sw\_max}$  (e.g. Vout = 15 V grey curve, point C; Vout = 20 V yellow curve, point D), the firmware will start to slowly increase the ripple in order to lower the operating frequency (the slope of this increasing ripple depends on the buck inductance  $L_{EXT}$ , see equation (12) on page 17). It will continue increasing the ripple until the frequency falls below the high threshold  $f_{sw\_max}$  (corrected points C' and D', see Figure 16).

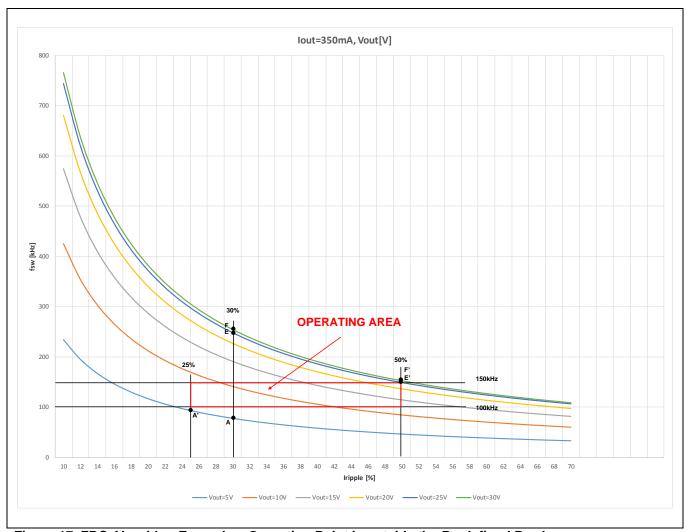

- 3) If the achieved operating frequency is above the maximum allowed switching frequency  $f_{sw\_max}$  (e.g. Vout = 25 V dark blue curve, point E; Vout = 30 V green curve, point F), the firmware will start to slowly increase the ripple in order to lower the operating frequency (the slope of this increasing ripple depends on the buck inductance  $L_{EXT}$ , see equation (12) on page 17). It will continue increasing the ripple until it hits its maximum allowed value  $I_{ripple\_max}$ . The switching frequency will be determined by  $I_{ripple\_max}$  and could be outside the predefined borders (corrected points E' and F', see Figure 17).

- 4) If the achieved operating frequency is below the minimum allowed switching frequency  $f_{sw\_min}$  (e.g. Vout = 5 V blue curve, point A), the firmware will start to slowly decrease the ripple in order to raise the operating frequency (the slope of this decreasing ripple depends on the buck inductance  $L_{EXT}$ , see equation (12) on page 17). It will continue decreasing the ripple until the frequency reaches the low threshold value defined by the parameter  $f_{sw\_min}$ , or if the ripple hits the minimum allowed value defined by the parameter  $I_{ripple\_min}$ . In this case, the switching frequency could be outside the predefined borders (corrected point A', see Figure 17).

Figure 16. FRC Algorithm Example – Operating Point successfully put into Operating Area

Figure 17. FRC Algorithm Example – Operating Point is outside the Predefined Borders

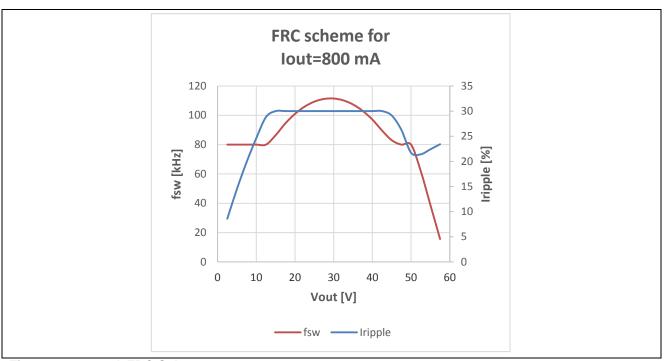

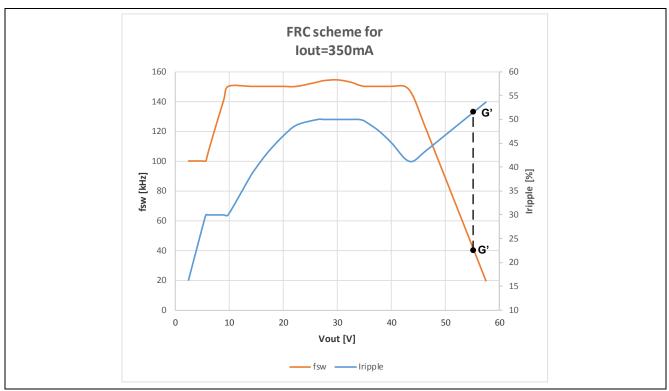

An example of a frequency ripple control scheme is shown below in **Figure 18**, **Figure 19** and **Figure 20**. Resistances and voltage drops of used components ( $V_D$  – forward voltage of the freewheeling diode,  $R_L$  – inductor resistance,  $R_{ON} = R_{DS}$  – channel resistance when the MOSFET is ON,  $R_{CS}$  – shunt resistance connected to the CS pin,  $V_{OUT} = N \cdot V_{LED} + N \cdot R_{LED} \cdot I_{OUT}$  – output voltage (LED lighting load), N – number of LEDs,  $V_{LED}$  – LED forward voltage,  $R_{LED}$  – LED forward resistance) are included in calculations.

Figure 18. 800 mA FRC Scheme

Figure 19. 550 mA FRC Scheme

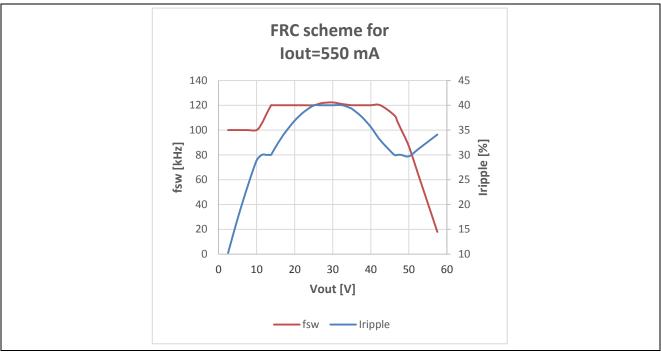

Figure 20. 350 mA FRC Scheme

Frequency Ripple Controller behavior depends on the output voltage load as mentioned before. As can be seen in previous figures, the FRC regulates the switching frequency and current ripple for this dedicated example as follows:

- 1<sup>st</sup> area Vout <10 V: The system will be started with the minimum constant switching frequency and the ripple will increase accordingly.

- 2<sup>nd</sup> area 10 V < Vout < 15 V approximately: The system will be started with a selectable initial current ripple (30% of lout). The switching frequency will be changed accordingly (not valid for 800 mA).

- 3<sup>rd</sup> area 15 < Vout < 25 V approximately: The system will be started with the maximum frequency value; it will be kept constant at a predefined value and the current ripple will increase accordingly (not valid for 800 mA).

- 4<sup>th</sup> area Vout ≈ V<sub>IN</sub>/2: The system is started with the maximum predefined current ripple, but the frequency cannot be kept within predefined borders, which means that the frequency will be determined by the T<sub>OFF</sub> and I<sub>ripple</sub> values and external hardware components.

- 5<sup>th</sup> area Vout > 45 V (near V<sub>IN</sub>) approximately: T<sub>OFF\_min</sub> criteria have the highest priority<sup>1</sup>, so the frequency and ripple will have the values determined by the external hardware components (not by FRC) and can be outside the defined limits.

Datasheet

Revision 1.0, 2015-04-08

If the high voltage load is applied at the output (large number of LEDs, the output voltage is near the input voltage), the operating frequency will be low and if it falls below  $f_{sw\_min}$ , the frequency-ripple controller will start to correct it by decreasing the ripple value, as described above. On the other hand, due to the high output voltage,  $T_{OFF}$  is quite short (see equation (11) on page 17). It is very important that the turn-off time must be longer than the predefined  $T_{OFF\_min}$  time (constant Toff\_min, see Table 3-19), because during that time all calculations must be performed before starting a new cycle. At that point, the frequency-ripple controller starts to increase the ripple again in order to meet  $T_{OFF\_min}$  criteria. The final outcome is that the current ripple and switching frequency could stay outside the predefined limits (above  $I_{ripple\_max}$  and below  $f_{sw\_min}$  respectively) — point G in Figure 21. If  $T_{OFF}$  falls below the minimum allowed value (low ripple means short  $T_{OFF}$  time for constant output voltage), the regulator cannot maintain the average current any longer, therefore influencing accuracy. If parameters are configured properly, any of above mentioned actions lead to stable operating conditions for the given current/load situation. However, there is drift in the operating frequency produced by the input voltage ripple that has to be taken into account when deciding on parameter values. The frequency ripple controller will always try to put the operating point into the operating area, but its final position will depend on the other criteria that affect its position.

Figure 21. Operating Point determined by Toff\_min criteria

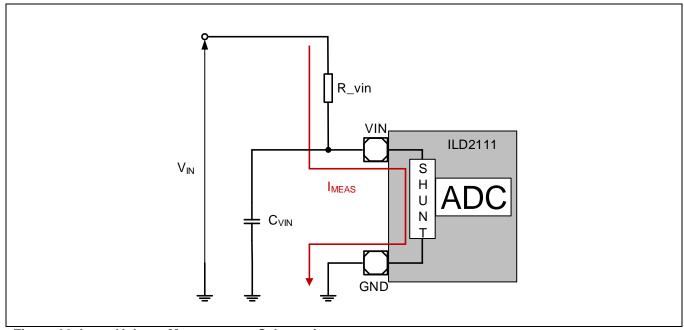

## 3.5 Input Voltage Measurement and Calibration

There are some indirect measurements, like the output voltage  $V_{OUT}$  and output power  $P_{OUT}$ , that take input voltage measurement as an input. Therefore the accuracy of those measurements depends on the input voltage  $V_{IN}$  accuracy, and typically is lower due to the accuracies of other variables. Therefore it is important that the input voltage is accurately measured. The input voltage is sensed at the VIN pin. A filter capacitor  $C_{VIN}$  (typically 100 nF) is used for voltage (at the pin VIN) filtering of conductive and electromagnetic interference caused by the converter switching operation. The measurement circuit is shown in Figure 22 below.

Figure 22. Input Voltage Measurement Schematic

Two measurement ranges related to the VIN pin are implemented. They are called current ranges because calibration is based on the current flowing into the VIN pin. The two ranges use a different value of the internal shunt resistor, where ADC measures the voltage drop. The reason for calibration is to make results independent of  $R_{SHUNT}$  production tolerance by including the measured value of  $R_{SHUNT}$  as part of internal chip calibration data during chip production.

Nominal shunt values for an appropriate current range are as follows:

- 1) Current range  $00_b \Rightarrow I_{MEAS} = 209 \mu A$ ,  $R_{SHUNT} = 6690 \Omega$ .

- 2) Current range  $01_b \Rightarrow I_{MEAS} = 1.6 \text{ mA}$ ,  $R_{SHUNT} = 1490 \Omega$ .

The current range is defined by the parameter Vin current range (see Table 3-8).

Depending on the input voltage range to be measured, for lower power dissipation, the value of the external resistor R\_vin and the maximum current measurement range must be chosen carefully. Especially for high  $V_{IN}$  voltage (bus voltage), power dissipation needs to be considered as part of system losses.

For more details, see the examples below.

## Examples:

1) If the maximum bus voltage is high, e.g.  $V_{\text{INMAX}} = 500 \text{ V}$ , the current measurement range (209  $\mu$ A) should be chosen to minimize power dissipation over R\_vin. The value of the external resistor R\_vin is obtained from the equation below (209  $\mu$ A would ideally be full scale at the ADC; to achieve accurate measurement over the production spread of ILD2111, use a margin factor of 75%).

Therefore,

$$R_{vin} = \frac{V_{INMAX}}{0.75 \cdot I_{209\mu A}} - R_{SHUNT} = 3.18 \text{ M}\Omega.$$

(14)

2) If the maximum bus voltage is lower, e.g.  $V_{INMAX} = 80 \text{ V}$ , the current measurement range (1.6 mA) should be chosen.

Therefore,

$$R_{\nu}in = \frac{V_{INMAX}}{0.75 \cdot I_{1.6mA}} - R_{SHUNT} = 65.2 \text{ k}\Omega.$$

(15)

## 3.6 Protection Features

**Table 3-5** gives an overview of the supported protection features. Two protection modes are implemented (auto restart mode and latch mode), which can be entered. Protection features can be configured by the parameters that are shown in **Table 3-9** and **Table 3-10**. An error counter counts errors up to 4 restarts, defined by the constant value Err\_restart\_tries (see **Table 3-14**). The error counter is reset when the device operates without additional errors for the time defined by the constant Err\_cnt\_clear\_time (see **Table 3-14**), or at the startup sequence, e.g. if V<sub>CC</sub> falls below the voltage threshold (see **Table 4-4**).

## **Table 3-5. Protection Features**

| Undervoltage Protection for DC Input Line – V <sub>IN</sub> Undervoltage | Section <b>3.6.1</b> |

|--------------------------------------------------------------------------|----------------------|

| Overvoltage Protection for DC Input Line – V <sub>IN</sub> Overvoltage   | Section <b>3.6.2</b> |

| Output Undervoltage Protection – V <sub>OUT</sub> Undervoltage           | Section <b>3.6.3</b> |

| Open Output Protection                                                   | Section <b>3.6.4</b> |

| Output Overvoltage Protection – V <sub>OUT</sub> Overvoltage             | Section <b>3.6.5</b> |

| Output Overpower Protection – P <sub>OUT</sub> Overpower                 | Section <b>3.6.6</b> |

| Overtemperature Protection                                               | Section <b>3.6.7</b> |

| Overcurrent Protection – Level 2 (OCP2)                                  | Section 3.6.8        |

| Functional Protections                                                   | Section 3.6.9        |

Protection functions are shown in a matrix in Table 3-6 below.

| Description of Fault                               | Characte      | Operating Mode<br>Detection Active |         |        |          |               | Consequence |                                                                                                                                                        |

|----------------------------------------------------|---------------|------------------------------------|---------|--------|----------|---------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                    | Fault         |                                    |         |        |          | 1             |             |                                                                                                                                                        |

|                                                    | Name of Fault | Minimum Duration of effect         | Startup | Normal | Shutdown | Error Current | Buck OFF    |                                                                                                                                                        |

| V <sub>IN</sub> Undervoltage                       | INPUV         | 1.6 ms                             | Х       | Х      | -        | -             | -           | Startup - Waits until condition is removed Normal – Auto-restart                                                                                       |

| V <sub>IN</sub> Overvoltage                        | INPOV         | 1.6 ms                             | Х       | Х      | -        | -             | -           | Startup - Waits until condition is removed Normal – Auto-restart                                                                                       |

| V <sub>OUT</sub> Undervoltage                      | OUTUV         | 0.8 ms<br>@40 kHz                  | -       | X      | -        | -             | -           | Auto-restart mode with 4 tries (restarts). After 4 failed attempts, the device enters latch mode                                                       |

| Open Output                                        | OPEN          | 1)                                 | X       | X      | -        | -             | -           | Auto-restart mode with 4 tries (restarts). In each restart try, I-se procedure will be executed. After 4 failed attempts, the device enters latch mode |

| V <sub>OUT</sub> Overvoltage                       | OUTOV         | 0.4 ms<br>@40 kHz                  | -       | Х      | -        | -             | -           | Auto-restart mode with 4 tries (restarts). After 4 failed attempts, the device enters latch mode                                                       |

| P <sub>OUT</sub> Overpower                         | PWR           | 6.4 ms<br>@40 kHz                  | -       | X      | -        | -             | -           | Auto-restart mode with 4 tries (restarts). After 4 failed attempts, the device enters latch mode                                                       |

| Overtemperature (Internal or External)             | OTI or<br>OTE | 0.4 ms<br>@40 kHz                  | X       | X      | -        | -             | -           | Startup - Waits until condition is removed Normal – Auto-restart                                                                                       |

| OCP2                                               | ОСР           | Instantly                          | X       | Х      | -        | -             | -           | The device is in predefined time loop until the device is switched off or when the cause of the OCP2 event is removed – see Section 3.6.8              |

| X = Checked during Op<br>- = Not checked during    | Operation M   | ode                                |         |        |          |               |             |                                                                                                                                                        |

| In each restart attempt,<br>determined by the cons |               |                                    | •       |        |          | ation         | is          |                                                                                                                                                        |

All protections are described in the following sections.

Defined by constant Open\_out\_timeout, see Section 3.6.4 .

## 3.6.1 Undervoltage Protection for DC Input Line – V<sub>IN</sub> Undervoltage

Undervoltage protection for the DC input line prevents the device from operating with an excessively low  $V_{IN}$  voltage. If the input voltage is below the specified value, the output current is turned off. The device waits until the input undervoltage (low voltage value) condition is removed (Vin\_min\_start is met) and then starts with output current generation again. There are two hysteretic input voltage values that are used as thresholds during the startup sequence (upper threshold value – parameter Vin\_min\_start, see **Table 3-9**)<sup>1</sup> and during operation (lower threshold value – parameter Vin\_min\_oper, see **Table 3-9**)<sup>1</sup>. If the input voltage is  $V_{IN}$  < Vin\_min\_oper during operation, the buck converter will be shut down and will wait for the  $V_{IN}$  startup condition (when Vin\_min\_start is reached). This event does not affect the error counter.

## 3.6.2 Overvoltage Protection for DC Input Line – V<sub>IN</sub> Overvoltage

Overvoltage protection for the DC input line prevents the device from operating with an excessively high  $V_{IN}$  voltage. After the overvoltage condition on input is detected, the output current is turned off. The device waits for the input overvoltage condition to be removed (Vin\_max\_start is met) and then starts output current generation again. There are two hysteretic input voltage values that are used as thresholds during the startup sequence (lower threshold value – parameter Vin\_max\_start, see **Table 3-9**)<sup>1</sup> and during operation (upper threshold value – parameter Vin\_max\_oper, see **Table 3-9**)<sup>1</sup>. If the input voltage is  $V_{IN} > Vin_max_oper$  during operation, the buck converter will be shut down and will wait for the  $V_{IN}$  startup condition (when Vin\_max\_start is reached). This event does not affect the error counter.

## 3.6.3 Output Undervoltage Protection – V<sub>OUT</sub> Undervoltage

Output undervoltage protection prevents the device from operating with an excessively low output voltage  $V_{LEDmin}$  or when LED output is lowered. If the output voltage is lower than the minimum value  $V_{OUT} < Vout\_min$ , an undervoltage output is detected, and the device enters error auto-restart mode with 4 tries (restarts) – constant Err\_restart\_tries (see Table 3-14). After 4 failed attempts, the device enters latch mode. The minimum output operating voltage value is programmable (parameter Vout\_min, Table 3-9). Undervoltage output is checked during steady-state condition, after completing soft-start. The restart timeout startup delay is predefined by the constant Err\_restart\_time (see Table 3-14).

## 3.6.4 Open Output Protection

Open output protection prevents the device from operating when no load on output is detected. It is detected when the time to achieve  $I_{MAX}$  (see **Figure 11**) exceeds the value of the parameter Open\_out\_timeout (see **Table 3-14**)<sup>2</sup>. If the open output condition is detected, the device enters error auto-restart mode with 4 tries (restarts) – constant Err\_restart\_tries (see **Table 3-14**). In each attempt, the device executes the reference resistor reading procedure (I-set procedure, see Section **3.3.3**). The duration of the I-set procedure is defined by the parameter RC\_measurement\_timeout (duration =  $2 \cdot RC_measurement_timeout$ , see **Table 3-19**). The restart timeout startup delay is predefined by the constant Err\_restart\_time (see **Table 3-14**). After 4 failed attempts, the device enters latch mode. The total duration of the restart attempt can be obtained as the sum of the two above-mentioned times (I-set procedure + restart timeout). If the LED lighting load is connected (or replaced) at the output between two restart attempts, the I-set procedure will detect the new R\_iset resistance and the buck converter will try to start with the newly determined reference current.

<sup>&</sup>lt;sup>1</sup> To minimize the impact of fluctuations on the exact  $V_{IN}$  voltage value, filtering is implemented using a first-order filter whose coefficient is defined by the constant  $V_{IN}$  (see **Table 3-14**)

<sup>&</sup>lt;sup>2</sup> During buck 'on time' T<sub>ON</sub> (see **Figure 11**), the gate driver stays constantly 'high' until I<sub>MAX</sub> is reached, or Open\_out\_timeout expires. This can lead to a long 'high' time. In case there is a 'high side driver' circuit between the ILD2111 gate drive and MOSFET gate, proper functionality for all operating conditions needs to be considered. A stable OCP1 value (I<sub>MAX</sub>) is obtained by filtering defined by the constant Alt\_OCP1\_filt\_stable (see **Table 3-14**)

## 3.6.5 Output Overvoltage Protection – V<sub>OUT</sub> Overvoltage

Output overvoltage protection prevents the device from operating when the high voltage at the output  $V_{\text{OUT}}$  is detected. If the output voltage is higher than the maximum value  $V_{\text{OUT}} > \text{Vout\_max}$ , the device enters error auto-restart mode with 4 tries (restarts) – constant Err\_restart\_tries (see **Table 3-14**). After 4 failed attempts, the device enters latch mode. The maximum output operating voltage value is programmable (parameter Vout\\_max, **Table 3-9**). Output voltage is checked during the steady-state condition, after completing soft-start. The restart timeout startup delay is predefined by the constant Err\_restart\_time (see **Table 3-14**).

## 3.6.6 Output Overpower Protection – P<sub>OUT</sub> Overpower

Output overpower protection prevents damage to output components due to high output power<sup>2</sup>. The maximum allowed output power value (parameter Pout\_max, see Table 3-9) is set by the constants Pout\_corr\_LC and Pout\_corr\_HC (Pout\_max\_lc = Pout\_corr\_LC · Pout\_max and Pout\_max\_hc = Pout\_corr\_HC · Pout\_max) for low current and high current range respectively (see Table 3-14). The parameter Ref\_current\_HCTH decides between the low current and high current range (see Table 3-14). If the output power exceeds the maximum allowed operational value, the device enters error auto-restart mode with 4 tries (restarts) — constant Err\_restart\_tries (see Table 3-14). After 4 failed attempts, the device enters latch mode. Output overpower is checked during the steady-state condition after completing soft-start. The restart timeout startup delay is predefined by the constant Err\_restart\_time (see Table 3-14).

Output voltage is internally calculated, based on VIN and  $T_{ON}$  /  $T_{PWM}$  duty factor. Output voltage can be calculated approximately as  $V_{OUT} = D * V_{IN} = (T_{ON} / T_{PWM}) * V_{IN}$  (all resistances and voltage drops of used components are neglected). To minimize the impact of fluctuations on the exact  $T_{PWM}$  period value, filtering is implemented using a first-order filter whose coefficient is defined by the parameter  $T_{PWM}$  \_filt\_coef (see **Table 3-14**).

<sup>&</sup>lt;sup>2</sup> Output power is internally calculated, based on  $V_{IN}$ ,  $I_{OUT}$  and  $T_{ON}$  /  $T_{PWM}$  ratio. The actual  $T_{ON}$  /  $T_{PWM}$  ratio (for true output power) also depends on parasitic effects (e.g. MOSFET diode reverses recovery time, additional circuit like high side driver). These parasitic effects are unknown to the chip calculation and need to be considered for choosing appropriate Pout\_max values. To minimize the impact of fluctuations on the calculated  $P_{OUT}$  value, filtering is implemented using a first-order filter whose coefficient is defined by the parameter Pout\_filt\_coef (see **Table 3-14**) before comparing the output power against Pout\_max\_lc or Pout\_max\_hc thresholds.

## 3.6.7 Overtemperature Protection

The ILD2111 supports overtemperature protection by means of internal and external temperature sensors. If both internal temperature protection and external temperature protection requests for the current level change, the lower current level will prevail. If the external sensor is not used (disabled by configuration), only the internal temperature protection is processed.

## 3.6.7.1 Internal Temperature Sensor – Internal PWM Dimming 1

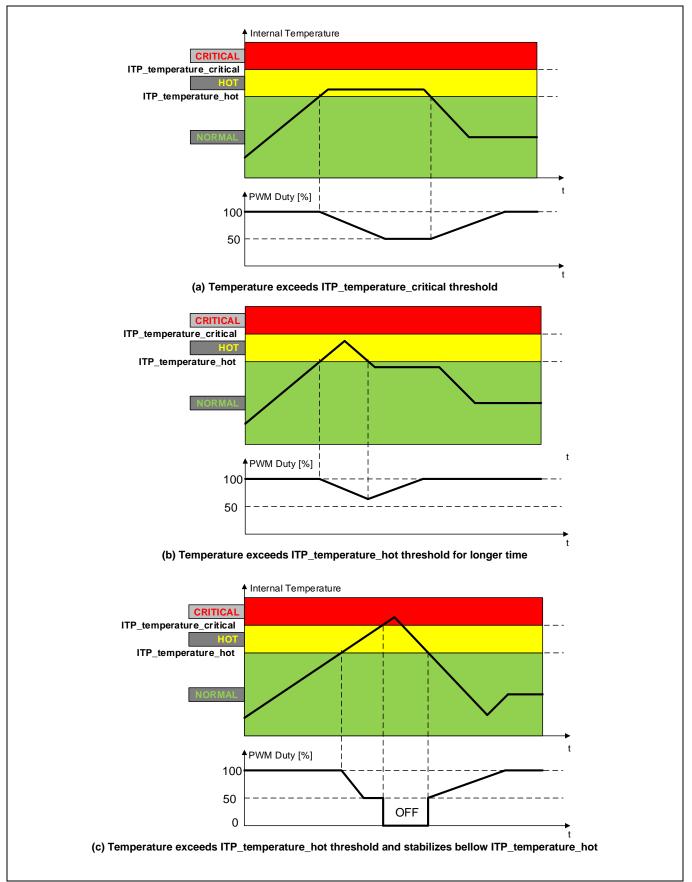

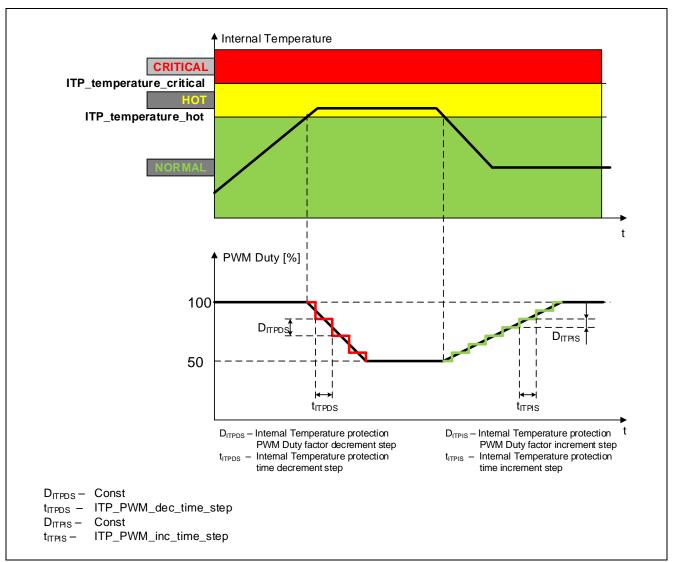

Internal temperature-based protection uses internal temperature sensor measurement for reduction of the output current in the case that device temperature increases. For this purpose, two temperature thresholds - T1 and T2 - are defined (parameters ITP\_temperature\_hot - T1 and ITP\_temperature\_critical - T2 increasing in value - see Table 3-10) as well as one up-slope (constant ITP\_PWM\_inc\_step - Table 3-15 and parameter ITP\_PWM\_inc\_time\_step - Table 3-10) and one down-slope (constant ITP\_PWM\_dec\_step - Table 3-15 and parameter ITP\_PWM\_dec\_time\_step - Table 3-10). Temperature thresholds can be set in steps of 1°C and slopes as percentages of the average current per minute. The output current level is reduced by PWM modulation with a programmable frequency rate - see Figure 28.

There are three temperature-related operating conditions:

Normal T<=T1</li>

Hot T1<T<=T2</li>

Critical T>T2

Temperature measurement may lead to a change of operating state:

- In the critical state, the output current is off. An output current restart could be in hot or normal state (default).

- If the device starts in hot mode, then the current is adjusted with the dedicated constant value (ITP\_startup\_PWM\_hot = 50%, see **Table 3-15**). If it is in normal mode, it will start with 100% of the rated current.

- In the hot state, the current will be reduced (decreased) according to a constant-defined limit (TP\_PWM\_duty\_min = 50%, see **Table 3-18**) and down-slope. If the device starts in hot mode, it will start with 100% of the rated current, but then the current is adjusted with the dedicated parameter (ITP\_startup\_PWM\_hot = 50%). In normal mode, the full current level (100%) is started and kept stable (no change in current level).

The complete device behavior regarding operating temperature conditions is shown in Figure 23, Figure 24 and Figure 28.

Figure 23. Internal Temperature Protection Behavior

Figure 24. Internal Temperature Protection

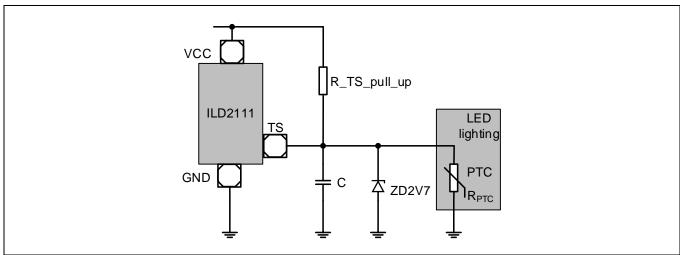

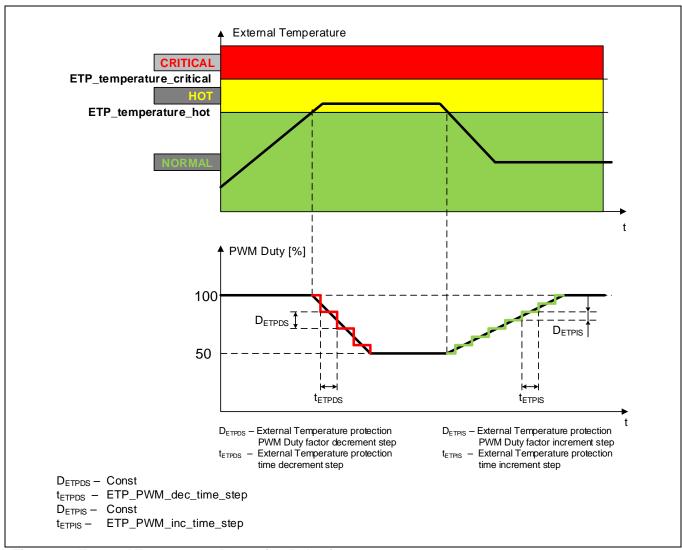

### 3.6.7.2 External Temperature Sensor – Internal PWM Dimming 2

External temperature-based protection uses a PTC resistor connected to the TS pin and GND (2-wire connection – Figure 25). External temperature is meant to reduce the output current in the case that the temperature of the light element increases (see LED lighting in Figure 25). For this purpose, two temperature thresholds, Te1 and Te2, are defined (parameters ETP\_temperature\_hot – Te1 and ETP\_temperature\_critical – Te2 increasing in value – see Table 3-10) as well as one up-slope (constant ETP\_PWM\_inc\_step - Table 3-15 and parameter ETP\_PWM\_inc\_time\_step - Table 3-10) and one down-slope (constant ETP\_PWM\_dec\_step - Table 3-15 and parameter ETP\_PWM\_dec\_time\_step - Table 3-10). Temperature thresholds can be set in steps of 1°C and slopes as percentages of the average current per minute. The output current level is reduced by PWM modulation with a programmable frequency rate – see Figure 28. To minimize the impact of fluctuations on the exact external temperature value, filtering is implemented using a first-order filter whose coefficient is defined by the constant ETP\_filt\_coef (see Table 3-15) before comparing against thresholds.

Figure 25. External Temperature Measurement

The external temperature sensor is supplied by  $V_{CC}$ , whose actual value is read by the on-chip ADC and used to calculate the external temperature value (the reference value for  $V_{CC}$  voltage compensation is defined by the parameter VCC\_reference, see **Table 3-10**)<sup>1</sup>. The TS pin is clamped via a 2.7 V Zener diode for protection reasons

The threshold levels vary according to the PTC resistance/temperature curve.

There are three temperature-related operating conditions:

Normal T<=Te1</li>

Hot Te1<T<=Te2</li>

Critical T>Te2

Temperature measurement may lead to changes in the operating state<sup>2</sup>:

• In the critical state, the output current is off. An output current restart could be in hot or normal state (default).

If the device starts in hot mode, then the current is adjusted with the dedicated parameter (ETP\_startup\_PWM\_hot = 50%, see **Table 3-15**). If it is in normal mode, it will start with 100% of the rated current.

1

<sup>&</sup>lt;sup>1</sup> To minimize the impact of fluctuations on the exact V<sub>CC</sub> voltage value, filtering is implemented using a first-order filter whose coefficient is defined by the parameter Vin\_filt\_coef (see *Table 3-14*)

<sup>&</sup>lt;sup>2</sup> External temperature protection behavior curves have the same shape as internal temperature protection curves – see Figure 23 (a, b and c).

- In the hot state, the current will be reduced (decreased) according to a parameter-defined limit (TP\_PWM\_duty\_min, see Table 3-18) and down-slope. If the device starts in hot mode, then the current is adjusted with the dedicated parameter (ETP\_startup\_PWM\_hot = 50%). If it is in normal mode, it will start with 100% of the rated current.

- In normal mode, the full current level (100%) will be kept (no change in current level). For startup in normal mode, 100% of the rated current will be generated at the output.

There is an additional ADC voltage threshold (constant ETP\_temperature\_disconnected, see **Table 3-13**) to improve existing functionality. It is not the temperature threshold. An ETP\_temperature\_disconnected internal threshold value signals that the ADC (voltage) value is too high – i.e., that the sensor is disconnected. If the sensor is disconnected during operation, PWM duty will be gradually reduced to a value defined by the constant TP\_PWM\_duty\_min = 50% (see **Table 3-18**) as it is at a temperature defined by ETP\_temperature\_hot (see **Figure 26**). If the higher ADC voltage (greater than the ETP\_temperature\_disconnected value) is detected during startup, the sensor will be ignored during operation.

External temperature protection behavior is shown in Figure 26.

Figure 26. External Temperature Protection Behavior

#### 3.6.8 Overcurrent Protection – Level 2 (OCP2)

To avoid damage to the shunt resistor or MOSFET due to the rapid increase (inrush) of the current through the shunt resistor (detected as the voltage at the CS pin), the overcurrent protection OCP2 is implemented as a hardware threshold. If the OCP2 threshold is reached¹ (regardless of the cause of its appearance), the gate driver (power MOSFET) will be turned off automatically and can only be turned on again by firmware intervention. In the case of an OCP2 event, the firmware checks an internal counter of OCP2 events and applies a delay according to the table **Table 3-7**. After the delay the engine is reinitialized and the device starts operation. The OCP2 counter will be reset after a predefined time (constant Err\_cnt\_clear\_time, see **Table 3-14**) in case there are no new OCP2 error events in the meantime. Otherwise, if the OCP2 event occurs again before the counter is reset, the number of errors is increased in increments up to the limit.

Table 3-7. OCP2 Error Restart Delay

| Number of the OCP2 events | Previous value of the OCP2 counter | Next value of the OCP2 counter | Restart delay           |

|---------------------------|------------------------------------|--------------------------------|-------------------------|

| 1                         | 0                                  | 1                              | 100 μs                  |

| 2                         | 1                                  | 2                              | 500 μs                  |

| 3                         | 2                                  | 3                              | 2500 µs                 |

| ≥4                        | 3                                  | 3                              | OCP2_restart_delay [ms] |

The time loop defined by the constant OCP2\_restart\_delay (see **Table 3-14**) is repeated until the device is switched off or when the cause of the OCP2 event is removed.

If the OCP2 condition is removed and the device is in internal or external PWM dimming, the device continues to operate in one of two modes (internal or external dimming), depending on which of the conditions for these modes is fulfilled.

#### 3.6.9 Functional Protections

Beside previous protections related to an application, ILD2111 incorporated the functional protections in order to achieve high reliability of the operation.

#### 3.6.9.1 Code Memory Protections

During the startup of the device, after a reset or power-up, firmware is copied from the OTP memory to the RAM. The firmware is then executed from the RAM. The firmware is signed with a CRC value (Cyclic Redundancy Check). During the process of copying, the CRC value is calculated and then compared to the signed CRC value. In the case of a mismatch the firmware will not start in order to prevent misbehavior.

During run time the RAM is protected by a parity check over one memory cell. RAM parity protection is a hardware feature which detects parity errors when RAM is accessed (read/write). In the event of a parity error, a hardware reset is issued and the device will restart accordingly.

#### 3.6.9.2 Firmware Hang Protection

During run-time, the execution of the firmware can become erratic due to a hardware fault. In order to prevent such firmware "hangs" a watch dog timer (WDT) is utilized. The WDT is a hardware feature and if it is not serviced before a specific timeout, the device will reset and restart accordingly.

### 3.6.9.3 Parameter Memory Protection

The parameter memory is a dedicated part of the RAM. The device blank checks part of this area and also checks for the parameter "CRC error". More details can be found in Section 3.9.2.

Datasheet 39 Revision 1.0, 2015-04-08

<sup>&</sup>lt;sup>1</sup> The digital representative of the OCP2 comparator output is digitally filtered. The number of successive samples that have reached OCP2 level, after which OCP2 event will be acknowledged, is defined by the parameter OCP2\_filt\_stable (see Table 3-14).

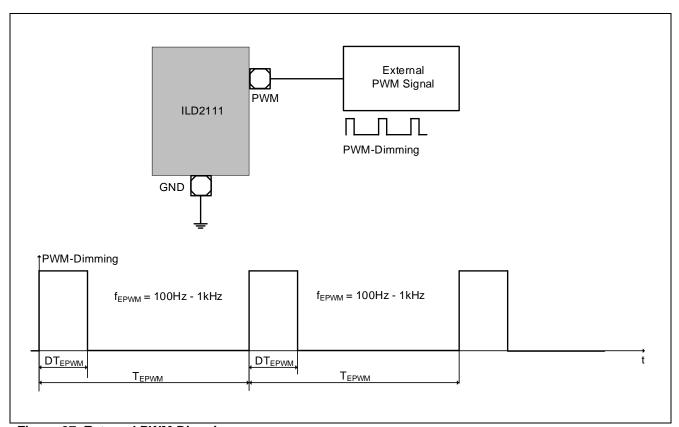

### 3.7 External PWM Dimming

For external dimming, EPWM duty ( $DT_{EPWM}$  - duty factor range 1% to 99%) and EPWM period ( $T_{EPWM}$ ) can be measured at the PWM input pin – see **Figure 27**.

Figure 27. External PWM Dimming

The external PWM duty factor and external PWM frequency are obtained by measuring the on-time  $T_{\text{ON\_EPWM}}$  (DT<sub>EPWM</sub>) and PWM period  $T_{\text{EPWM}}$ . The timeout time for external PWM detection is defined by the constant EPWM\_detection\_timeout (see **Table 3-18**). There are two additional parameters that are used for external PWM processing: 1. LFPWM\_threshold\_divider, which represents the number of divisions by two of the measured  $T_{\text{EPWM}}$  to obtain the hysteretic controller threshold and 2. LFPWM\_flicker\_free\_threshold which represents the number of switching cycles that are considered flicker-free (the threshold divider is then not implemented for the hysteresis controller) – see **Table 3-18**. The complete output current PWM modulation is described in the following section **3.8**.

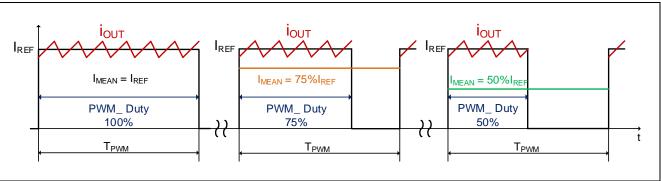

#### 3.8 Output Current PWM Modulation

Modulation of the output current can be requested by either of the following:

- 1. External PWM dimming signal (Section 3.7) and

- 2. Internal PWM dimming signal (internal temperature protection see Section 3.6.7.1 and external temperature protection see Section 3.6.7.2).

The output current dimming PWM frequency,  $f_{PWM}$ , will be defined by the external PWM dimming signal EPWM (the range of  $f_{EPWM}$  is 100 Hz – 1 kHz;  $f_{EPWM}$  = 1 /  $T_{PWM}$ ) or by the internal PWM signal (IPWM – constant value TP\_PWM\_period = 3.2 ms,  $f_{IPWM}$  is 300 Hz,  $f_{IPWM}$  = 1 /  $T_{PWM}$ , see **Table 3-18**), if EPWM is not detected (the external EPWM frequency has a higher priority than the internal IPWM frequency). The final duty factor (PWM\_Duty, see **Figure 28**) of the PWM signal will be determined by a minimum value of one of two calculated values (external epwm\_duty or internal ipwm\_duty).

Figure 28. Output Current PWM Modulation

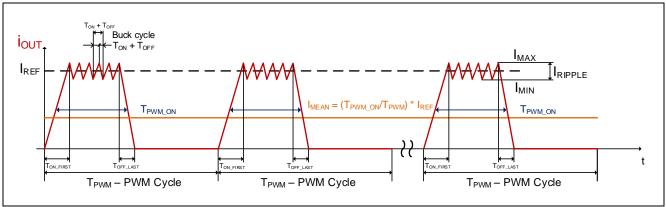

A hysteretic controller is implemented in order to have a flicker-free output even at low dimming levels. This controller monitors the PWM duty and the high switching frequency period (buck cycle,  $T = T_{ON} + T_{OFF}$ ) and uses this information to control a number of switching cycles (N) within the PWM ON time. This number is updated only upon changes that are sufficiently high. The threshold is set to  $T_{old}/2^{\text{LFPWM\_threshold\_divider}}$ . Therefore either the PWM ON time changes to that extent or T changes such that  $|T_{\text{new}} \cdot N| + T_{\text{ON\_FIRST}} - T_{\text{PWM\_oN}}| > T_{\text{old}}/2^{\text{LFPWM\_threshold\_divider}}$ . From the previous description it can be seen that the compensation for the first rising slope time  $(T_{\text{ON\_FIRST}})$  is included in the calculation.

The hysteretic cycle control requires reaching of the OCP1 level ( $I_{MAX}$ ) a minimum of three times, i.e. a minimum of two switching cycles  $2 \cdot (T_{ON} + T_{OFF})$  plus a rising  $T_{ON\_FIRST}$  and falling  $T_{OFF\_LAST}$  times in order to perform proper measurements and to regulate the current and implement protection features. Therefore, the minimum pulse width ( $T_{PWM\_ON}$ ) of the output PWM dimming current is restricted according to this minimum duration (see **Figure 29**). The mean output current is proportional to the duty. However, for low duty, accuracy is lower due to limits mentioned earlier. Furthermore, the higher the output reference current value  $I_{REF}$ , the greater the expected inaccuracy due to longer rising  $T_{ON\_FIRST}$  and falling  $T_{OFF\_LAST}$  times.

Figure 29. Output Current I<sub>MEAN</sub> Dimming Range Limitation

### 3.9 Configuration

This section provides an overview of the parameters that can be configured via the UART interface.

### 3.9.1 Overview of Configurable Parameters

The ILD2111 provides a generic firmware version that includes all parameters set to zero. The parameter values need to be specified by the user according to the target application.

Please refer to the corresponding electrical characteristics in Section 4 for the minimum and maximum tolerances.

#### **Parameter Lists**

The parameter list contains the following groups:

- Configurable parameters (see Section 3.9.1.1) Variable values that can be changed (modified) by the user according to the desired application.

- Design constants (see Section 3.9.1.2) Constant values that cannot be changed and that are specified by the application.

## 3.9.1.1 Configurable Parameters

The configurable parameters are arranged in the following tables:

- 1. Hardware configuration Table 3-8.

- 2. Protections Table 3-9.

- 3. Temperature guard Table 3-10.

- 4. Startup & shutdown Table 3-11.

- 5. Output current set Table 3-12.

Table 3-8. Configurable Parameters – Hardware Configuration