ICL5101

Resonant controller IC with PFC for LED driver

Datasheet

Rev. 1.3, 2016-01-15

### Resonant controller IC with PFC for LED driver

### **Product highlights**

- Resonant Controller and PFC within one IC

- Supports universal input and wide output range

- Low count of external components supporting small form factors and improved reliability

- All parameters set by simple resistors only

- Supports outdoor use by extended junction temperature range from -40 °C to +125 °C

- Stable low load operation mode down to 0.1 % of nominal power rating

- Comprehensive set of protection to increase system safety

- Ultra-fast time to light < 200 ms

- Power Factor Correction > 99 %, THD < 5 %

- High efficiency up to 94 %

#### **PFC** feature set

- PFC in CrCM mode during nominal load and DCM mode in low load condition down to 0.1 % for operation without audible noise

- Adjustable THD compensation of AC input current even in DCM operation for lowest THD

- Adjustable PFC current limitation

### Resonant half bridge feature set

- · Fully integrated 650 V high-side driver

- Self-adaptive dead time control of the integrated half bridge driver 500 ns – 1.0 μs

- Detection of capacitive operation, overload, short circuitry, output overvoltage and external over temperature protection to detecting hot spots in system

- Improved operation control in magnetic saturation during start-up

- Advanced error detection control

### **Applications**

- LED driver, e.g. commercial or residential lighting systems > 50 W

- Integrated electronic control gear for LED luminaires

### **Description**

# The LED Resonant controller ICL5101 is designed to control resonant converter

topologies. The PFC stage operates in CrCM and DCM mode, supporting low load conditions. Integrated high and low side drivers assure a low count of external components, enabling small form factor designs.

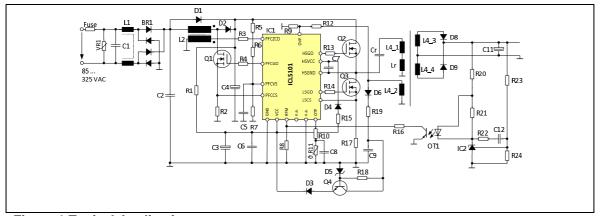

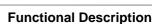

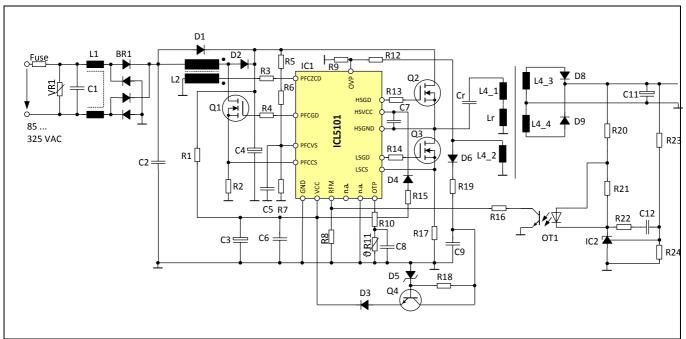

ICL5101 parameters are adjusted by simple resistors only, this being the ideal choice to ease the design-in process. A comprehensive set of protection features ensures that the LED driver detects fault conditions, protecting both the LED driver and the LED load. Figure 1shows a typical application circuit of a 110 W constant voltage LED driver.

Figure 1 Typical Application

| Product type | Package      |

|--------------|--------------|

| ICL5101      | PG-DSO-16-23 |

### **Table of Contents**

# **Table of Contents**

| Resona                     | nt controller IC with PFC for LED driver                             | 2  |

|----------------------------|----------------------------------------------------------------------|----|

| 1                          | Pin Configuration and Description                                    | 4  |

| 1.1                        | PG-DSO-16-23 Package                                                 |    |

| 1.2                        | PIN Configuration for PG-DSO-16-23                                   |    |

| 1.3                        | PIN Set-Up                                                           |    |

| 1.4                        | PIN Functionality                                                    |    |

|                            | •                                                                    |    |

| <b>2</b><br>2.1            | Functional Description                                               |    |

|                            | Introduction                                                         |    |

| 2.1.1                      | UVLO to Soft Start                                                   |    |

| 2.1.2                      | Soft Start to Run Mode                                               |    |

| 2.2                        | Detection Stage                                                      |    |

| 2.2.1                      | Detection of Over Temperature                                        |    |

| 2.2.2                      | Detection of Output Overvoltage                                      |    |

| 2.2.3                      | Detection of Capacitive Mode Operation                               |    |

| 2.2.4                      | Surge Protection                                                     |    |

| 2.2.5<br>2.2.6             | Self-Adapting Dead Time during Gate Drive Activity between HS and LS |    |

| 2.2.6<br>2.2.7             | Short Term Bus Under voltage                                         |    |

| 2.2. <i>1</i><br>2.3       | Long-Term Bus Under voltagePFC Preconverter                          |    |

| 2.3<br>2.3.1               | Operation Modes of the PFC Converter                                 |    |

| 2.3.1<br>2.3.2             | PFC Bus Overvoltage and Open Loop                                    |    |

| 2.3.2<br>2.3.3             | PFC Bus Voltage Levels 95 % and 75 %                                 |    |

| 2.3.3<br>2.3.4             | PFC Structure of Mixed Signals                                       |    |

| 2.3. <del>4</del><br>2.3.5 | THD Correction via Zero Crossing Detection Signal                    | 22 |

| 2.3.5<br>2.4               | State Diagram                                                        |    |

| 2. <del>4</del><br>2.4.1   | Monitoring of Features versus Operating Mode                         |    |

| 2.4.2                      | Fault Condition – Flow Chart Fault F: Latch OFF after Single Restart |    |

| 2.4.3                      | Fault Condition – Flow Chart Fault A: Auto Restart                   |    |

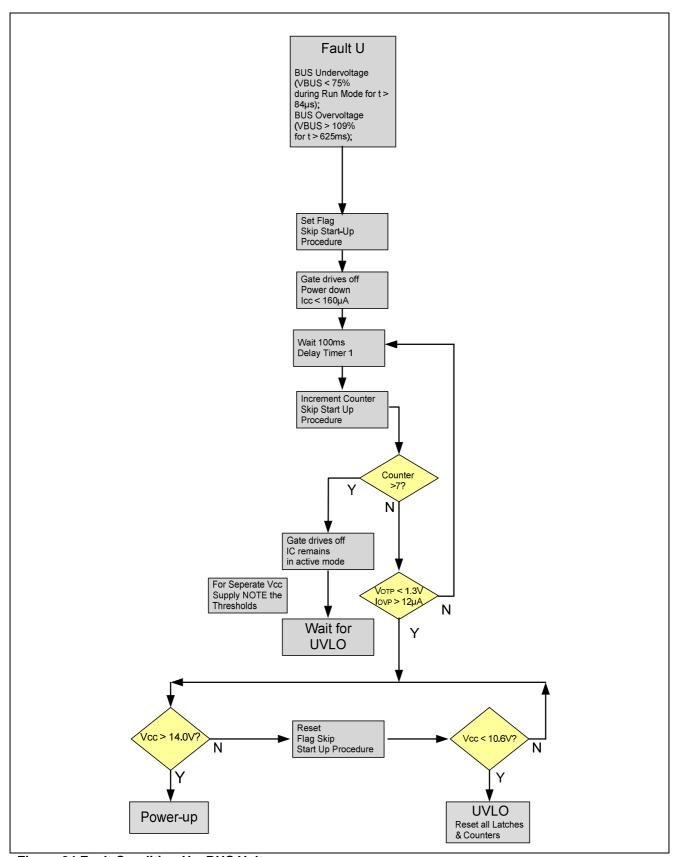

| 2.4.4                      | Fault Condition – Flow Chart Fault U: BUS Voltage                    |    |

| 2.4.5                      | Protection Matrix                                                    |    |

| _                          |                                                                      |    |

| 3                          | Electrical Characteristics                                           |    |

| 3.1                        | Absolute Maximum Ratings                                             |    |

| 3.2                        | Operating Range                                                      |    |

| 3.3                        | Characteristics Power Supply Section                                 |    |

| 3.4<br>3.4.1               | Characteristics of PFC Section                                       |    |

| 3.4.1<br>3.4.2             | PFC Zara Current Peterties (PFCZCR)                                  |    |

| 3.4.2<br>3.4.3             | PFC Zero Current Detection (PFCZCD) PFC Voltage Sensing Bus (PFCVS)  |    |

| 3.4.3<br>3.4.4             | PFC PWM Generation                                                   |    |

| 3.4.4<br>3.4.5             | PFC Gate Drive (PFCGD)                                               |    |

| 3.4.5<br>3.5               | Characteristics of Inverter Section                                  |    |

| 3.5.1                      | Low-Side Current Sense (LSCS)                                        |    |

| 3.5.2                      | Low-Side Gate Drive (LSGD)                                           |    |

| 3.5.3                      | Inverter Minimum Run Frequency (RFM)                                 |    |

| 3.5.4                      | Overtemperature Protection (OTP)                                     |    |

| 3.5.5                      | Overvoltage Protection (OVP)                                         |    |

| 3.5.6                      | High Side Gate Drive (HSGD)                                          |    |

| 3.6                        | Timer Section                                                        |    |

|                            |                                                                      |    |

| 4                          | Application Example                                                  |    |

| 4.1                        | Schematic                                                            | 40 |

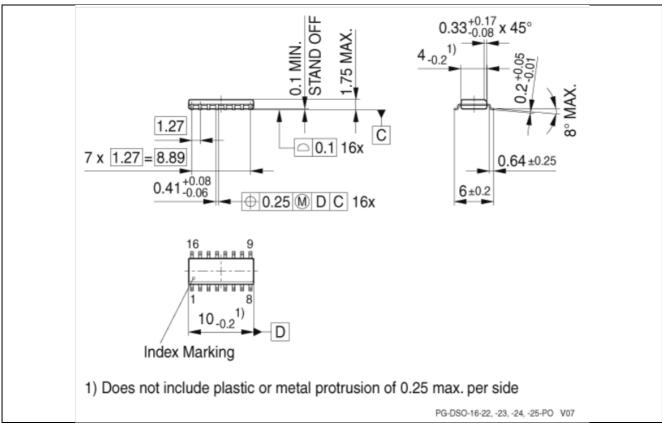

| 5                          | Outline Dimensions                                                   | 41 |

3

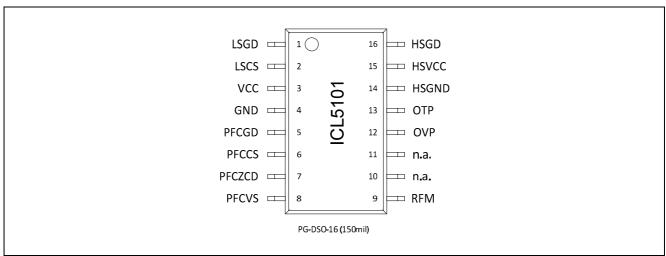

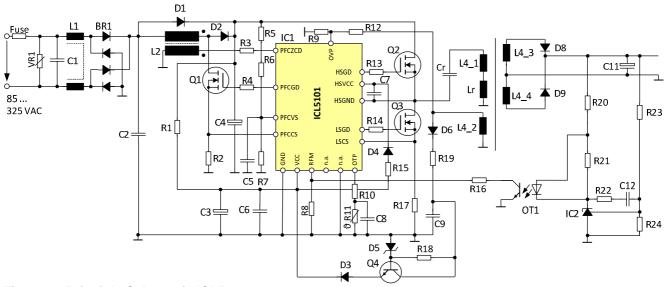

The pin configuration is shown in Figure 2 and PIN Functionality Table 1. Short pin functionality is described below in 1.2.

## 1.1 PG-DSO-16-23 Package

Figure 2 Pin Configuration

### 1.2 PIN Configuration for PG-DSO-16-23

| Symbol | Pin | Function                                   |

|--------|-----|--------------------------------------------|

| LSGD   | 1   | Low-side gate drive                        |

| LSCS   | 2   | Low-side current sense signal              |

| VCC    | 3   | Chip supply voltage                        |

| GND    | 4   | IC GND                                     |

| PFCGD  | 5   | PFC gate drive                             |

| PFCCS  | 6   | PFC current sense signal                   |

| PFCZCD | 7   | PFC zero crossing detection                |

| PFCVS  | 8   | PFC voltage sensing                        |

| RFM    | 9   | Set RUN frequency                          |

| n.a.   | 10  | NOT APPLICABLE: Leave PIN OPEN             |

| n.a.   | 11  | NOT APPLICABLE: SET to GND                 |

| OVP    | 12  | Overvoltage protection of secondary output |

| OTP    | 13  | Over temperature protection                |

| HSGND  | 14  | High-side GND                              |

| HSVCC  | 15  | High-side supply voltage                   |

| HSGD   | 16  | High-side gate drive                       |

### 1.3 PIN Set-Up

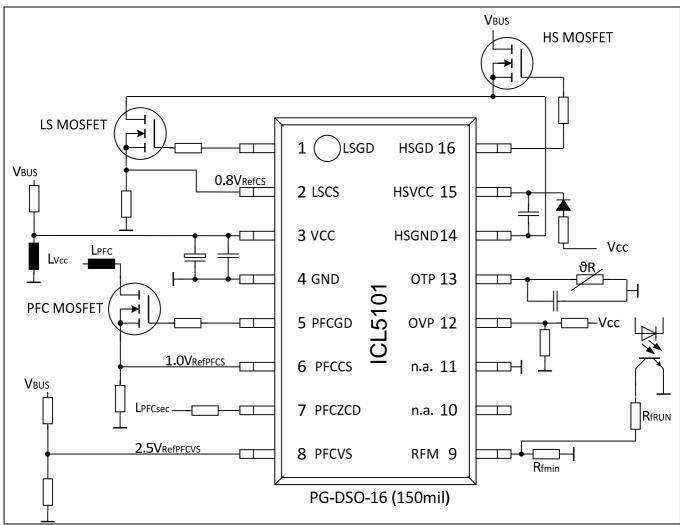

The PIN set-up of ICL5101 is shown in Figure 3.

Figure 3 PIN Set-Up

The schematic in Figure 3 shows a typical PIN set-up for a PFC / LLC converter

# 1.4 PIN Functionality

**Table 1. Pin Definitions and Functions**

| Symbol | Pin | Function                                                                                                                                                   |

|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LSGD   | 1   | Low-side gate drive The gate of the low-side MOSFET in a RESONANT inverter topology is                                                                     |

|        |     | controlled by this pin. There is an active L-level during UVLO (under voltage                                                                              |

|        |     | lockout) and a limitation of the max H-level at 11.0 V during normal operation. In order to turn on the MOSFET softly (with a reduced didentification),    |

|        |     | the gate voltage rises typically within 245 ns from L-level to H-level. The fall                                                                           |

|        |     | time of the gate voltage is less than 50 ns in order to turn off quickly. This                                                                             |

|        |     | measure produces different switching speeds during turn-on and turn-off as it                                                                              |

|        |     | is usually achieved with a diode parallel to a resistor in the gate drive loop. It                                                                         |

|        |     | is recommended to use a resistor of typically 10 $\Omega$ between the drive pin and                                                                        |

|        |     | gate in order to avoid oscillations and in order to shift the power dissipation when discharging the gate capacitance into this resistor. The typical dead |

|        |     | time between the LSGD signal and HSGD signal is self-adapting between                                                                                      |

|        |     | 500 ns and 1.0 μs.                                                                                                                                         |

| SCS    | 2   | Low-side current sense signal                                                                                                                              |

|        |     | This pin is directly connected to the shunt resistor, which is located between                                                                             |

|        |     | the source terminal of the low-side MOSFET of the inverter and ground.                                                                                     |

|        |     | Internal clamping structures and filtering measures allow sensing of the                                                                                   |

|        |     | source current for the low side inverter MOSFET without additional filter                                                                                  |

|        |     | components. There is a first threshold of 0.8 V. If this threshold is exceeded for longer                                                                  |

|        |     | than 500 ns during run mode, an inverter overcurrent is detected, which                                                                                    |

|        |     | causes a latched shutdown of the IC. The saturation control is activated if the                                                                            |

|        |     | sensed slope at the LSCS pin reaches typical values of 205 mV/µs ±                                                                                         |

|        |     | 25 mV/µs and exceeds the 0.8 V threshold. The saturation regulator is now                                                                                  |

|        |     | continuously monitored by the LSCS pin during saturation control mode. In                                                                                  |

|        |     | saturation control mode, the regulator is designed to handle a choke                                                                                       |

|        |     | operation in saturation. If the sensed current signal exceeds a second                                                                                     |

|        |     | threshold of 1.6 V for longer than 500 ns before entering the run mode, the IC changes over into a latched shutdown.                                       |

|        |     | There are further thresholds active at this pin during run mode that detects                                                                               |

|        |     | capacitive mode operation. A voltage level below -50 mV before the high-                                                                                   |

|        |     | side gate is on indicates faulty operation (operation below resonance).                                                                                    |

|        |     | A second threshold at 2.0 V senses even short over currents during turn-on                                                                                 |

|        |     | of the high-side MOSFET such as is typical for reverse recovery currents of                                                                                |

|        |     | a diode. If one of these comparator thresholds indicates incorrect operating                                                                               |

|        |     | conditions for longer than 620 µs in run mode, the IC turns off the gates and changes to fault mode due to detected capacitive mode operation (non-zero    |

|        |     | voltage switching).                                                                                                                                        |

|        |     | The threshold of -50 mV is also used to adjust the dead time between turn-                                                                                 |

|        |     | off and turn-on of the RESONANT drivers in a range of 500 ns to 1.0 µs                                                                                     |

|        |     | during all operating modes.                                                                                                                                |

| CC     | 3   | Chip supply voltage                                                                                                                                        |

|        |     | This pin provides the power supply of the ground-related section of the IC.                                                                                |

|        |     | There is a turn-on threshold at 14.0 V and a UVLO threshold at 10.6 V. The                                                                                 |

|        |     | upper supply voltage level is 17.5 V. There is an internal Zener diode clamping $V_{CC}$ at 16.3 V (at $I_{VCC} = 2$ mA typically). The maximum Zener      |

|        |     | current is internally limited to 5 mA. An external Zener diode is required for                                                                             |

|        |     | higher current levels. Current consumption during UVLO and during fault                                                                                    |

|        |     | mode is less than 170 µA. A ceramic capacitor close to the supply and GND                                                                                  |

|        |     | pin is required in order to act as a low-impedance power source for gate                                                                                   |

|        |     | drive and logic signal currents. In the event of a short interruption to the                                                                               |

|        |     | mains supply, feed the start-up current (160 μA) from the bus voltage.                                                                                     |

| Symbol | Pin | Function                                                                                                                                        |

|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|

| GND    | 4   | IC GND                                                                                                                                          |

|        |     | This pin is connected to ground and represents the ground level of the IC for                                                                   |

|        |     | the supply voltage, gate drive and sense signals.                                                                                               |

| PFCGD  | 5   | PFC gate drive                                                                                                                                  |

|        |     | The gate of the MOSFET in the PFC preconverter designed in boost                                                                                |

|        |     | topology is controlled by this pin. There is an active L-level during UVLO and                                                                  |

|        |     | a limitation of the max H-level at 11.0 V during normal operation. In order to                                                                  |

|        |     | turn on the MOSFET softly (with a reduced di <sub>DRAIN</sub> /dt), the gate drive voltage                                                      |

|        |     | rises within 245 ns from L-level to H-level. The fall time of the gate voltage is                                                               |

|        |     | less than 50 ns in order to turn off quickly. A resistor of typically 10 $\Omega$ is                                                            |

|        |     | recommended between the drive pin and gate in order to avoid oscillations                                                                       |

|        |     | and in order to shift the power dissipation when discharging the gate                                                                           |

|        |     | capacitance into this resistor. The PFC section of the IC controls a boost                                                                      |

|        |     | converter as a PFC preconverter in discontinuous conduction mode (DCM).                                                                         |

|        |     | Typically, the control starts with gate drive pulses with a fixed on-time of                                                                    |

|        |     | typically 4.0 µs at V <sub>ACIN</sub> = 230 V, increasing up to 24 µs and with an off-time                                                      |

|        |     | of 47 µs. As soon as sufficient zero current detector (ZCD) signals are                                                                         |

|        |     | available, the operation mode changes from fixed frequency operation to operation with variable frequency. The PFC works in critical conduction |

|        |     | mode operation (CrCM) when rated and/or medium load conditions are                                                                              |

|        |     | present. That means triangular-shaped currents in the boost converter choke                                                                     |

|        |     | without gaps and variable operating frequency. During low load (detected by                                                                     |

|        |     | an internal compensator) we obtain operation with discontinuous conduction                                                                      |

|        |     | mode (DCM) – that means triangular-shaped currents in the boost converter                                                                       |

|        |     | choke with gaps when reaching the zero current level and variable operating                                                                     |

|        |     | frequency in order to avoid steps in the consumed line current.                                                                                 |

| PFCCS  | 6   | PFC current sense signal                                                                                                                        |

| 11003  |     | The voltage drop across a shunt resistor located between the source of the                                                                      |

|        |     | PFC MOSFET and GND is sensed with this pin. If the level exceeds a                                                                              |

|        |     | threshold of 1.0 V for longer than 200 ns, the PFC gate drive is turned off as                                                                  |

|        |     | long as the zero current detector (ZCD) enables a new cycle. If no ZCD                                                                          |

|        |     | signal is available within 52 µs after turn-off of the PFC gate drive, a new                                                                    |

|        |     | cycle is initiated from an internal start-up timer.                                                                                             |

| PFCZCD | 7   | PFC zero crossing detection                                                                                                                     |

| 110200 | '   | This pin senses the point of time when the current through the boost inductor                                                                   |

|        |     | becomes zero during the off-time of the PFC MOSFET in order to initiate a                                                                       |

|        |     | new cycle.                                                                                                                                      |

|        |     | The moment of interest appears when the voltage of the separate ZCD                                                                             |

|        |     | winding changes from positive to negative level, which represents a voltage                                                                     |

|        |     | of zero at the inductor windings and therefore the end of current flow from                                                                     |

|        |     | the lower input voltage level to the higher output voltage level. There is a                                                                    |

|        |     | threshold with hysteresis, 1.5 V for increasing level, 0.5 V for decreasing                                                                     |

|        |     | level, which detects the change in inductor voltage. A resistor connected                                                                       |

|        |     | between the ZCD winding and PIN 7 limits the sink and source current of the                                                                     |

|        |     | sense pin when the voltage of the ZCD winding exceeds the internal                                                                              |

|        |     | clamping levels (typically 6.3 V and -2.9 V @ 5 mA) of the IC. If the sensed                                                                    |

|        |     | voltage level of the ZCD winding is not sufficient (e.g. during start-up), an                                                                   |

|        |     | internal start-up timer will initiate a new cycle every 52 µs after turn-off of the                                                             |

|        |     | PFC gate drive. The source current out of this pin during the on-time of the                                                                    |

|        |     | PFC-MOSFET indicates the voltage level of the AC supply voltage. During                                                                         |

|        |     | low input voltage levels, the on-time of the PFC-MOSFET is enlarged in                                                                          |

|        |     | order to minimize gaps in the line current during zero crossing of the line                                                                     |

|        |     | voltage and improve the THD (Total Harmonic Distortion) of the line current.                                                                    |

|        |     | Optimization of the THD is possible by trimming of the resistor between this                                                                    |

|        |     | pin and the ZCD winding in combination with the inductance and used PFC                                                                         |

|        |     | MOSFET.                                                                                                                                         |

| Symbol          | Pin | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol<br>PFCVS | 8 8 | <ul> <li>Function</li> <li>PFC voltage sensing</li> <li>The intermediate circuit voltage (bus voltage) at the smoothing capacitor is sensed by a resistive divider at this pin. The internal reference voltage for the rated bus voltage is 2.5 V. There are further thresholds at 0.3125 V (12.5 % of the rated bus voltage) for detection of open control loop and at 1.875 V (75 % of the rated bus voltage) for detection of under voltage, and at 2.725 V (109 % of the rated bus voltage) for detection of overvoltage. The overvoltage threshold operates with a hysteresis of 100 mV (4 % of the rated bus voltage). The bus voltage is sensed at 95 % (2.375 V) for detection of a successful start-up. It is recommended to use a small capacitor between this pin and GND as a spike suppression filter.</li> <li>In run mode, PFC overvoltage stops the PFC gate drive within 5 μs. As soon as the bus voltage is less than 105 % of the rated level, the gate drives are enabled again. If the overvoltage lasts for longer than 625 ms, an inverter overvoltage is detected and turns off the inverter gate drives also. This causes a power-down and a power-up when V<sub>BUS</sub> &lt; 109 %.</li> <li>A bus under- (V<sub>BUS</sub> &gt; 75 %) or inverter overvoltage during run mode is handled as FAULT BUS. In this situation the IC changes to power-down mode and generates a delay of 100 ms with an internal timer. Then start-up conditions are checked and if valid, a further start-up is initiated. If start-up conditions are not valid, a further delay of 100 ms is generated.</li> <li>This procedure is repeated a maximum of seven times. If a start-up is successful within these seven cycles, the situation is interpreted as a short interruption of the mains supply.</li> </ul> |

| RFM             | 9   | Set minimum RUN frequency A resistor from this pin to ground sets the operating frequency of the inverted during run mode. The typical run frequency range is 20 kHz to 120 kHz @ - 40°C and 130kHz @ - 25°C. The set resistor R_RFM can be calculated based on the run frequency $f_{RFM}$ according to the equation: $R_{RFM} = \frac{5 \cdot 10^8  \Omega Hz}{f_{RUN}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| n.a.            | 10  | NOT Applicable: Leave PIN Open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| n.a.            | 11  | NOT Applicable: SET to IC GND as short as possible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OVP             | 12  | Over voltage protection of OUTPUT Voltage  In order to prevent overvoltage at the output stage – in the case of a floating LED –overvoltage protection at pin 12 can be activated. Use a resistor and a ceramic capacitor connected to the auxiliary winding in order to sense the voltage level at the auxiliary winding. During run mode, the auxiliary winding is monitored by a sensing current proportional to the auxiliary voltage. If the peak-to-peak voltage at this pin exceeds a threshold of 210 µApp for longer than 620 µs, overvoltage is detected. This function can be disabled by setting pin 12 to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OTP             | 13  | Over temperature protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 |     | In order to prevent over temperature of the system, activate the over temperature protection at the OTP pin. Use a temperature-dependent resistor and a ceramic capacitor connected to GND for activation. There is a threshold of 3.2 V at the OTP pin during active run mode. If the voltage rises above this threshold for longer than 620 µs, the IC detects over temperature and changes to the latched fault mode. The latch mode is ended automatically by power-up or UVLO. This function can be disabled by setting pin 13 to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Symbol | Pin | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HSGND  | 14  | High-side GND This pin is connected to the source terminal of the high-side MOSFET, which is also the node of high-side and low-side MOSFET. This pin represents the floating ground level of the high-side driver and the high-side supply.                                                                                                                                                                                                                                                                                                                                                                                                              |

| HSVCC  | 15  | High-side supply voltage This pin provides the power supply of the high-side ground-related section of the IC. An external capacitor between pins 14 and 15 acts like a floating battery, which has to be recharged cycle by cycle via a high-voltage diode from the low-side supply voltage during the on-time of the low-side MOSFET. A UVLO threshold with hysteresis enables the high-side section at 10.4 V and disables it at 8.6 V.                                                                                                                                                                                                                |

| HSGD   | 16  | High-side gate drive The gate of the high-side MOSFET in an RESONANT inverter topology is controlled by this pin. There is an active L-level during UVLO and a limitation of the max H-level at 11.0 V during normal operation. The switching characteristics are the same as described for LSGD (pin 1). It is recommended to use a resistor of about 10 $\Omega$ between the drive pin and gate in order to avoid oscillations and in order to shift the power dissipation when discharging the gate capacitance into this resistor. The dead time between the LSGD signal and HSGD signal is self-adapting between 500 ns and 1.0 $\mu$ s (typically). |

## 2 Functional Description

The functional description provides an overview of the integrated functions, features and their relationships. The parameters and equations provided are based on typical values at  $T_A = 25$  °C. The corresponding minimum and maximum values are shown in the Electrical Characteristics.

#### 2.1 Introduction

The ICL5101 is a high-performance mixed-signal controller for LED and SMPS applications. The IC is designed for a Power Factor Correction (PFC) close to 1, low THD below 5 %, a maximum efficiency up to 94 % PLUS and a minimal design-in phase due to use resistors only for setting up the IC. The IC is designed to working in ultra-wide and narrow range designs. Furthermore, all parameters are valid in an extended temperature range from –40 °C up to 125 °C – especially frequency and timing. The controller utilizes a variety of protection features, including saturation control during start-up of the resonant converter, external adjustable over temperature, along with open and short load conditions. The ICL5101 includes also a surge protection feature, provides together with the CoolMOS technology a maximum protection against surges and safe components on board. Nevertheless CoolMOS P6 increases the efficiency by a 30% reduced gate charge and the internal gate resistor improves an easy use. For the half bridge is also a 500V CE CoolMOS recommended.

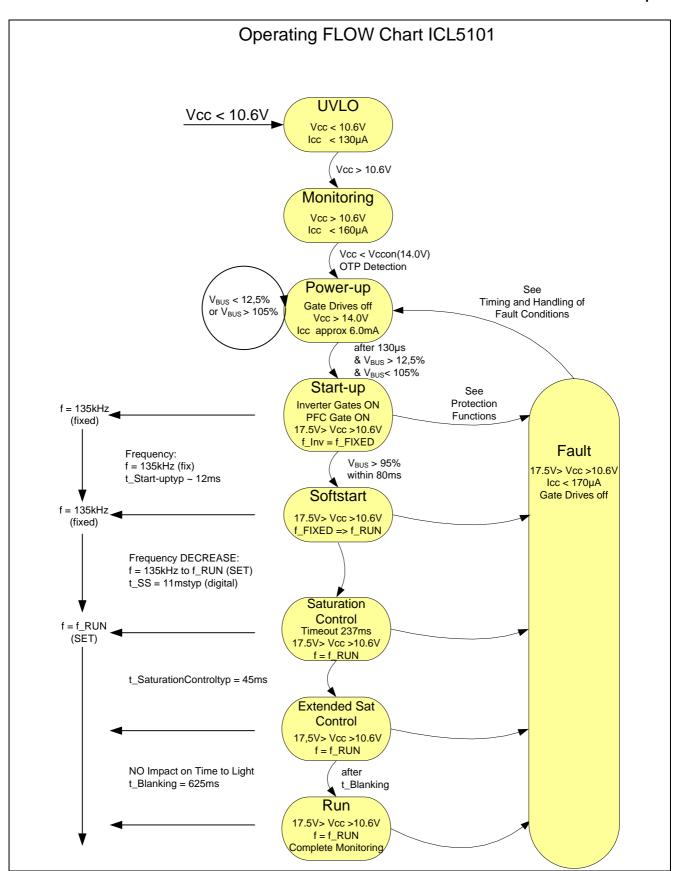

Figure 4 Operating Flowchart for LED Applications

### Start-Up

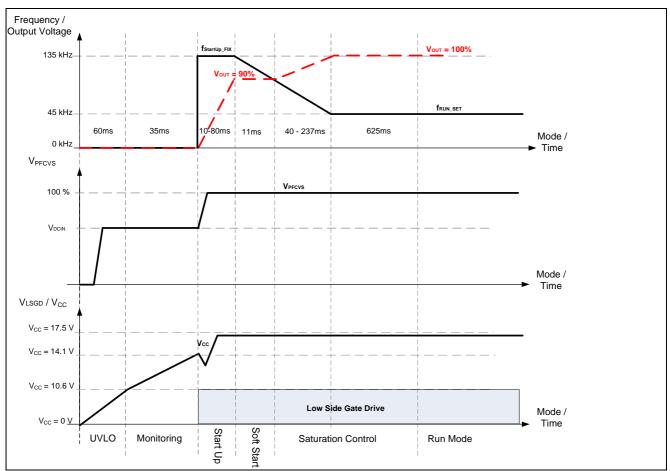

The device is powered through the VCC pin. All device supply voltages are internally generated from VCC voltage. Typical Start-Up Procedure below Figure 5 shows a typical start-up procedure of the device. The following subsections describe the phases in detail.

Figure 5 Typical Start-Up Procedure

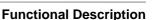

### 2.1.1 UVLO to Soft Start

This section describes the operating flow from UVLO to soft start in detail – Start-Up Procedure from UVLO to Soft Start Figure 6. The control of the LED ballast is able to start the operation in less than 100 ms (Time to Light IC is in active mode). This is achieved by the low current consumption during UVLO ( $I_{VCC}$  = 130  $\mu$ A) and start-up hysteresis ( $I_{VCC}$  = 160  $\mu$ A – defines the start-up resistor) phases. The chip supply stage of the IC is protected against overvoltage via an internal Zener clamping network, which clamps the voltage at 16.3 V and allows a current of 2.5 mA. For clamping currents above 2.5 mA, an external Zener diode from VCC to GND is required.

Figure 6 Start-Up Procedure from UVLO to Soft Start

If  $V_{CC}$  exceeds the 10.6 V level and stays below 14.0 V (start-up hysteresis), the IC checks whether the pcb temperature is experiencing over temperature or an output overvoltage is present. Over temperature is checked from a source current of typically  $I_{OTP3}$  = - 21.3  $\mu$ A out of pin 13 OTP ( $I_{OTP}$ ). This current produces a voltage drop of  $V_{OTP}$  < 1.6 V (temperature is ok). Over temperature is detected if the voltage at the OTP pin exceeds the  $V_{OTP}$  > 1.6V threshold ( $V_{OTP}$ ).

The output overvoltage is checked by a current of typically  $I_{OVP} > 12 \mu A$  via resistors R12 into the OVP pin 12. Output overvoltage is detected if there is no sink current into the OVP pin. This causes a higher source current out of the OTP pin (typically 42.6  $\mu A$  / 35.4  $\mu A$ ) in order to exceed  $V_{OTP} > 1.6 V$ . In the case of over temperature or overvoltage, the IC keeps monitoring until there is an adequate voltage from the OTP or OVP pin.

When  $V_{CC}$  exceeds the 14.0 V threshold – by the end of the start-up hysteresis – the IC waits for 80  $\mu$ s and senses the bus voltage. When the rated bus voltage is in the corridor of 12.5 % <  $V_{BUSrated}$  < 105 %, the IC powers up. The IC initiates an UVLO when the chip supply voltage is below  $V_{CC}$  < 10.6 V. As soon as the condition of a power-up is fulfilled, the IC starts the inverter gate operation with an internal fixed start-up frequency of 135 kHz. The PFC gate drive starts with a delay of app. 300  $\mu$ s. Then the bus voltage will be checked for a rated level above 95 % for duration of 80 ms. Now, the IC enters the soft start phase and shifts the frequency from the internal fixed start-up frequency of 135 kHz down to the set RUN frequency.

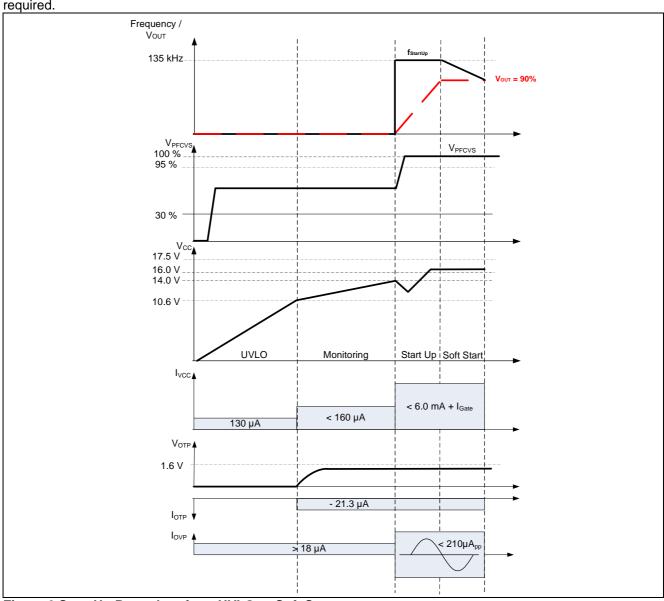

#### 2.1.2 Soft Start to Run Mode

This section describes the operating flow from soft start to run mode in detail. After the soft start phase is finished, the saturation control phase is entered.

Figure 7 Start-Up Procedure from Soft Start to Run Mode

During saturation control ( Start-Up Procedure from Soft Start to Run ModeFigure 7), the operating frequency of the inverter is shifted downward in  $t_{typ} = 40$  ms to the run frequency set by a resistor at the pin RFM to GND. The saturation control is activated if the sensed slope at the LSCS pin reaches typically 205 mV/ $\mu$ s ± 25 mV/ $\mu$ s and exceeds the 0.8 V threshold. This stops the frequency decreasing and signifies waiting for an adequate output voltage. The saturation control is now continuously monitored by the LSCS pin. The maximum duration of the saturation control procedure is limited to 237 ms. If there is still saturation within this time frame, the saturation control is disabled and the IC changes over to the latched fault mode. Furthermore, in order to reduce the choke size, the saturation control is designed to operate with a choke in magnetic saturation of the RESONANT during start-up. For an operation in magnetic saturation during saturation control mode, the voltage at the shunt at the LSCS pin 2 has to be  $V_{LSCS} = 0.80$  V when the output voltage is reached. If the saturation control mode is successfully passed, the IC enters the extended saturation mode The extended saturation mode is a safety mode used in order to prevent a malfunction of the IC due to an instable system. After 625 ms, the IC changes to the run mode (Figure 7). The run mode monitors the complete system regarding bus over- and under voltage, open loop, overcurrent of PFC and/or inverter, output overvoltage, over temperature and capacitive load operation.

### 2.2 Detection Stage

### 2.2.1 Detection of Over Temperature

Force a shut-off of the IC due to over temperature by using a PTC to GND on pin 13. In the event of an over temperature of the system (in run mode), the current out of the OTP pin 13  $I_{OTP3} = -21.3 \,\mu A$  charges up a capacitor. If the voltage at the OTP pin 13 exceeds the  $V_{OTP3} = 3.2 V$  threshold, the controller detects an over temperature and stops the gate drives after a delay of  $t = 620 \mu s$  set by an internal timer. The system restarts automatically. The possibility of a latch of the system is happen when it cools down and heat up within 200ms. When system is too hot before startup, the system prevents a power up.

### 2.2.2 Detection of Output Overvoltage

Overvoltage is detected by measuring the peak levels of the voltage at the AUX winding via an AC current fed into the OVP pin 12. If the sensed AC current exceeds 210  $\mu A_{PP}$  for longer than 620  $\mu s$ , the status of overvoltage is detected. The OVP fault results in a latched power-down mode (after trying a single restart). The controller continuously monitors the status until the overvoltage status changes.

### 2.2.3 Detection of Capacitive Mode Operation

RESONANT converter designs should avoid working in capacitive mode operation – not even under abnormal conditions. ICL5101 provides capacitive mode operation detection and latch-off of the system after a single restart for error verification. Resonant converters work in capacitive mode when their switching frequency falls below a critical value. This depends on the loading condition and the input-to-output ratio. They are especially prone to enter capacitive mode when the input voltage is lower than the minimum specified and/or the output is overloaded or shorted. In order to prevent a malfunction in the area of capacitive load during run mode due to certain deviations from the normal load, the IC senses only via the LSCS pin 2.

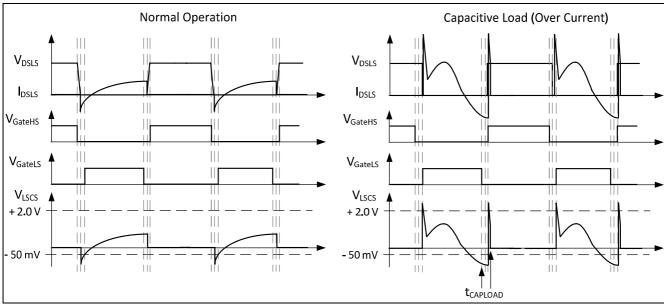

Capacitive load operation is detected if the voltage at the LSCS pin drops below a first threshold of  $V_{LSCSCap1} = -50$  mV directly before the high-side MOSFET is turned on or exceeds a second threshold of  $V_{LSCSCap2} = 2.0$  V during ON switching of the high-side MOSFET (Figure 8). If this overcurrent is present for longer than 620  $\mu$ s, the IC results a latched power-down mode after trying a single restart.

**Figure 8 Capacitive Mode Operation**

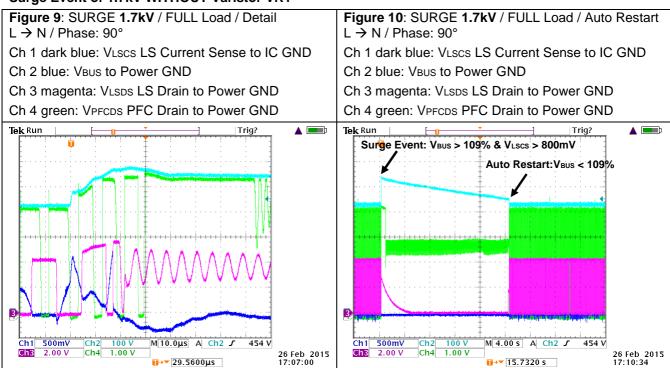

### 2.2.4 Surge Protection

#### **Description SURGE Protection**

In case of a surge event, the voltage at the BUS capacitors C5 & C8 rises up, the driver stages of the ICL5101 are shut off when VLSCS > 0.8V and VBUS > 109% for longer than 500ns. After the surge the controller restarts automatically when VBUS drops below 109% of the rated voltage. This feature allows driving 500V MOSFETs at the half bridge stage when adequate EMI and DC LINK networking is present. For an effective protection use CooMOS<sup>TM</sup> technology.

#### **SURGE Detection**

If the bus voltage exceeds:

VBUS > 109%

and the voltage at the low side current sense pin 2 exceeds:

VLSCS > 0.8V

for longer than

t = 500 ns

#### **SURGE Protection**

All Gate Drives OFF

#### **Auto Restart:**

VBUS < 109%

### **Measurement**

### Surge Event of 1.7kV WITHOUT Varistor VR1

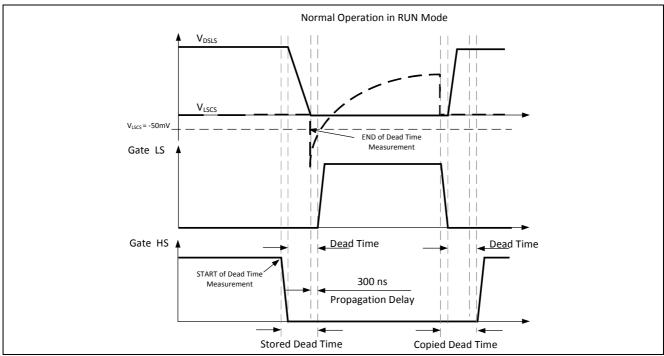

### 2.2.5 Self-Adapting Dead Time during Gate Drive Activity between HS and LS

The dead time between the turn OFF and turn ON of the RESONANT drivers is self-adapting and is detected by means of switch-off of the high-side MOSFET and the –50 mV threshold of the LSCS voltage (see Figure 11). The typical range of the dead time adjustment is 500 ns up to 1.0 µs during all operating modes. The start of the dead time measurement is the OFF switching of the high-side MOSFET. The dead time measurement finishes when V<sub>LSCS</sub> drops below -50 mV for longer than typically 300 ns (internal fixed propagation delay). This time will be stored, the low-side gate driver switches ON. The high-side gate driver turns ON again after OFF switching of the low-side switch and the stored dead time (see copied dead time in Figure 11).

Figure 11 Dead Time ON and OFF of the Inverter Gate Drivers

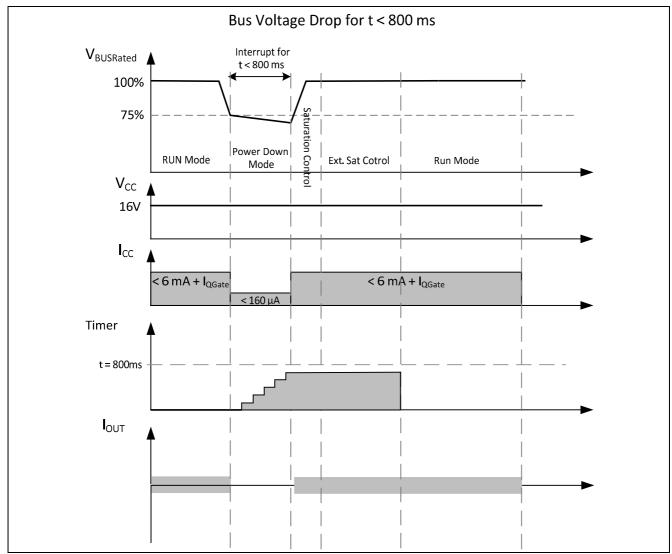

### 2.2.6 Short Term Bus Under voltage

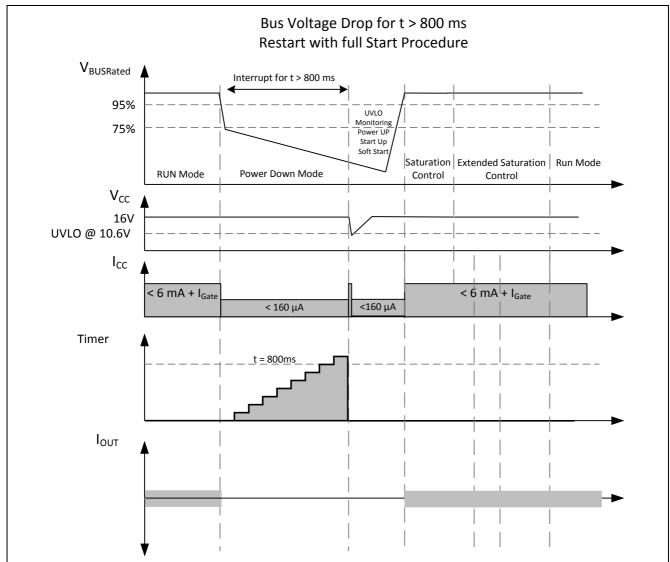

Short-term PFC bus under voltage (Figure 12) is detected if the duration of the under voltage does not exceed 800 ms (timer remains below t < 800 ms). In this case, the PFC and inverter drivers are immediately switched off and the controller continuously monitors the status of the bus voltage in a latched power-down mode ( $I_{CC}$  < 170  $\mu$ A). If the signal at the OVP PIN exceeds 18  $\mu$ A and the rated bus voltage is above 12.5 % while the timer is below t < 800 ms, the controller restarts from power-up. The timer resets to 0 when entering the run mode.

Figure 12 Bus Under voltage - Short

### 2.2.7 Long-Term Bus Under voltage

If the bus under voltage exceeds t > 800 ms (Figure 13) the controller forces an under voltage lock-out (UVLO). The chip supply voltage drops below  $V_{CC}$  = 10.6 V and the chip supply current is below  $I_{CC}$  < 130  $\mu$ A. When the Vcc voltage exceeds the 10.6 V threshold again, the IC current consumption is below  $I_{CC}$  < 160  $\mu$ A. In this case, the controller resets the timer and restarts with the full start-up procedure, including monitoring, power-up, start-up, soft start, saturation control, extended saturation mode and run mode.

Figure 13 Bus Under voltage - Long

#### 2.3 PFC Preconverter

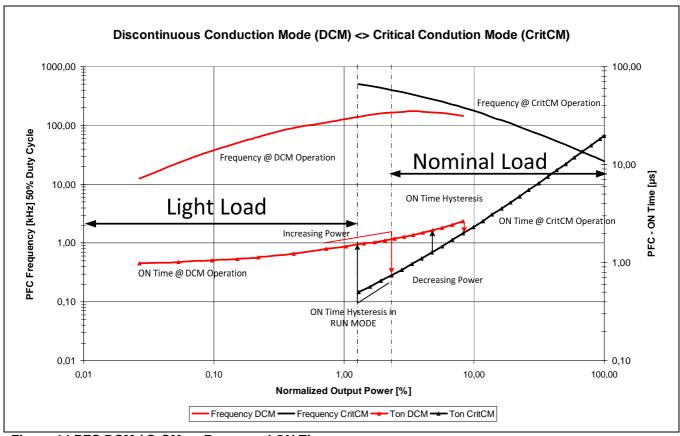

### 2.3.1 Operation Modes of the PFC Converter

The digitally controlled PFC pre-converter starts with an internally fixed ON time of typically  $t_{ON} = 4.0 \mu s$  and variable frequency. The ON time is increased every 280  $\mu s$  (typical) up to a maximum ON time of 24  $\mu s$ . The control switches quite immediately from discontinuous conduction mode (DCM) to critical conduction mode (CrCM) as soon as a sufficient ZCD signal becomes available. The frequency range in CrCM is 22 kHz up to 500 kHz, depending on the power (Figure 14) with a variation in the ON time of 24  $\mu s > t_{ON} > 0.5 \mu s$ .

Figure 14 PFC DCM / CrCM vs Power and ON Time

For lower loads (P<sub>OUTNorm</sub> < 8 % of the normalized load<sup>1</sup>) the controller operates in discontinuous conduction mode (DCM) with an ON time of 4.0 µs and increasing OFF time. The frequency during DCM is variable in a range from 144 kHz down to typically 22 kHz @ 0.1 % load. With this control method, the PFC converter enables stable operation from a 100 % load down to 0.1 %. Figure 14 shows the ON time range in DCM and CrCM (Critical Conduction Mode) operation. In the overlapping area of CrCM and DCM there is a hysteresis of the ON time, which causes a negligible frequency change.

Datasheet 20 Rev. 1.3, 2016-01-15

<sup>&</sup>lt;sup>1</sup> Normalized Power @ Low Line Input Voltage and maximum Lload

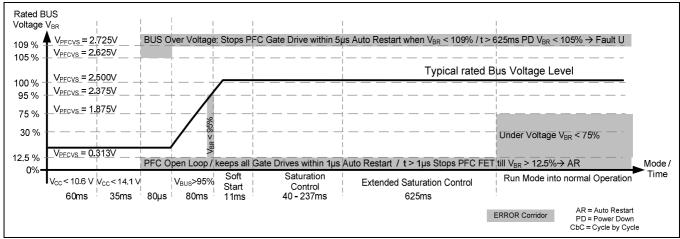

### 2.3.2 PFC Bus Overvoltage and Open Loop

The bus voltage loop control is completely integrated (Figure 15) and provided by an 8-bit sigma-delta A/D converter with a typical sampling rate of 280  $\mu$ s and a resolution of 4 mV/bit. After leaving monitoring, the IC starts to power up (VCC > 14.0 V). After power-up, the IC senses the bus voltage below 12.5 % (open loop) or above 105 % (bus overvoltage) for 80  $\mu$ s – 130  $\mu$ s. In the case of bus overvoltage (V<sub>BUSrated</sub> > 109 %) or open loop (V<sub>BUSrated</sub> < 12.5 %), the IC shuts off the gate drives of the PFC within 5  $\mu$ s or 1  $\mu$ s respectively. In this case, the PFC restarts automatically when the bus voltage is within the corridor (12.5 % < V<sub>BUSrated</sub> < 105 %) again. If the bus voltage is valid after the 130  $\mu$ s, the bus voltage sensing is set to 12.5 % < V<sub>BUSrated</sub> < 109 %. If these thresholds are departed from for longer than 1  $\mu$ s (open loop) or 5  $\mu$ s (overvoltage), the PFC gate drive stops working until the voltage drops below 105 % or exceeds the 12.5 % level. If the bus overvoltage (> 109 %) lasts for longer than 625 ms in run mode, the inverter gates also shut off and a power-down with complete restart is attempted (Figure 15).

Figure 15 PFC Bus Voltage Operating and Error Levels

### 2.3.3 PFC Bus Voltage Levels 95 % and 75 %

When the rated bus voltage is in the corridor of 12.5 % <  $V_{BUSrated}$  < 109 %, the IC will check whether the bus voltage exceeds the 95 % threshold (Figure 15) within 80 ms before entering soft start phase. Another threshold is activated when the IC enters the run mode. If the rated bus voltage drops below 75 % for longer than 84  $\mu$ s, a power-down with a complete restart is attempted if a counter exceeds 800 ms. In the case of short-term bus under voltage (the bus voltage reaches its working level in run mode before exceeding typically 800 ms - min. 500 ms) the IC skips phases and starts up directly in saturation control. The internal reference level of the bus voltage sense  $V_{PFCVS}$  is 2.5 V (100 % of the rated bus voltage) with a high accuracy. Surge protection is activated in the case of a rated bus voltage of  $V_{BUS}$  > 109 % and a low-side current sense voltage of  $V_{LSCS}$  > 1.6 V in extended saturation mode or of  $V_{LSCS}$  > 0.8 V in run mode for longer than 500 ns in RUN Mode.

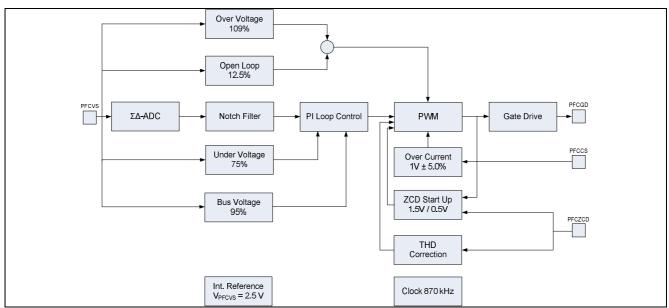

### 2.3.4 PFC Structure of Mixed Signals

A digital NOTCH filter eliminates the input voltage ripple independent of the mains frequency. A subsequent error amplifier with PI characteristic ensures stable operation of the PFC pre-converter (Figure 16)

Figure 16 PFC Mixed Signal Structure

The zero current detection (ZCD) is sensed by the PFC ZCD. Indication of finished current flow during demagnetization is required in CrCM and in DCM as well. The input is equipped with a special filtering, including an extended saturation of typically 500 ns and a large hysteresis of typically V<sub>PFCZCD</sub> between 0.5 V and 1.5 V.

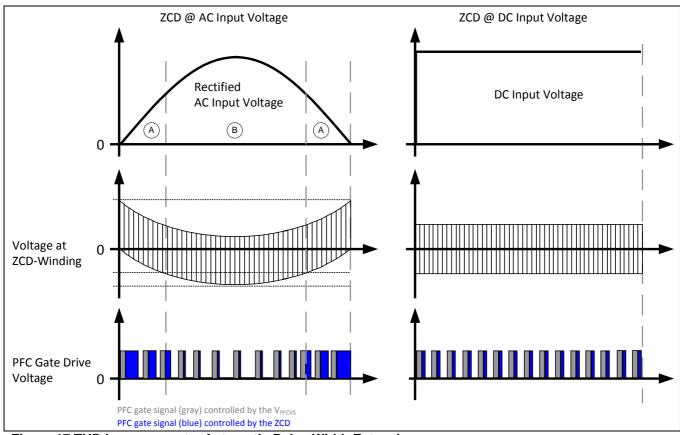

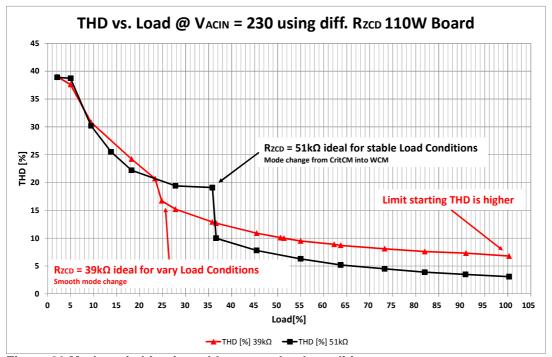

### 2.3.5 THD Correction via Zero Crossing Detection Signal

An additional feature is the THD correction (Figure 17). In order to optimize the THD (especially in the zones A shown in Figure 17, ZCD @ AC input voltage), there is a possibility to extend the pulse width of the gate signal (blue part of the PFC gate signal) via the variable PFC ZCD resistor from the ZCD pin to the PFC choke in addition to the gate signal controlled by the V<sub>PECVS</sub> signal (gray part of the PFC gate signal).

Figure 17 THD Improvement – Automatic Pulse Width Extension

In the case of DC input voltage, the pulse width gate signal is fixed as a combination of the gate signal controlled by the  $V_{PFCVS}$  pin (gray) and the additional pulse width signal controlled by the ZCD pin (blue) ZCD @ DC input voltage.

The PFC current limitation at pin PFCCS interrupts the ON time of the PFC MOSFET if the voltage drop at the PFC shunt resistors exceeds  $V_{PFCCS} = 1.0 \text{ V}$ . This interrupt will restart after the next sufficient signal from ZCD becomes available (auto restart). The first value of the resistor can be calculated as the ratio of the PFC mains choke and ZCD winding times the bus voltage to a current of typically 1.5 mA (Equation 1). An adjustment of the ZCD resistor causes an optimized THD.

$$R_{ZCD} = \frac{\frac{N_{ZCD}}{N_{PFC}} * V_{BUS}}{1.5 mA}$$

Equation 1: R<sub>ZCD</sub> - A Good Practical Value

### **THD Adujstment**

### **Introduction:**

In order to provide an excellent THD result, the THD of the ICL5101 is adjustable. Especially at high line input voltage and low load condition, the THD is a critical value. It doesn't matter in which condition:

- Line input voltage

- Stable load

- Load variation

the ICL5101 is providing best results for all cases – only by trimming a resistor R3 see Figure 18.

Figure 18 Principle Schematic ICL5101

Figure 19 PIN SetUP ICL5101

#### How to do:

To improve the THD the resistor – see R3 Figure 18 or red signed resistor in Figure 19 – at ZCD PIN 7 can be trimmed to an optimal value (several k-ohm ~ 20 up to 100k) in order to reach best THD results.

Step one is to define the inductivity of the PFC choke and the MOSFET. After fixing PFC choke and transistor, two scenarios are happen:

1/ operation in stable load condition e.g. lamp ON / OFF

SET nominal load condition and vary the value of the resistor until you get the best THD results. Outcome sees Figure 20 black curve

2/ operation with load variation e.g. dimming of an LED

Choose a resistor and vary the load. Change value up or down in order to get your best result over the whole load range – outcome sees Figure 20 red curve.

#### Mechanism:

The controller operates in two modes:

- Critical Conduction Mode (CrCM) in a wide load range

- Wait Cycle Mode (WCM a kind of DCM) for low load

### **Switch from CrCM into WCM):**

The ICL5101 has an integrated logic which can be regulated via the resistor at the ZCD PIN 7 in varying the value of the resistor.

#### Limit:

The digital logic of the controller is limited. At high line input voltages, the controller reduces the ON time of the PFC gate driver. If the minimum ON time is reached – physically given by the internal digital stage – the controller switches over from the critical conduction mode CrCM into the wait cycle mode WCM. This switch over can be seen in the THD measurement shown in Figure 20 black curve. Depending on the load (stable or variable) the optimum configuration can be found as shown in Figure 20 red curve. This effect can be prevented by trimming the resistor at the ZCD PIN 7 – lower the resistance leads to a smother cross over from CrCM into WCM (red curve) but increases slightly the THD.

Figure 20 Mode switching in stable or vary load condition

### 2.4 State Diagram

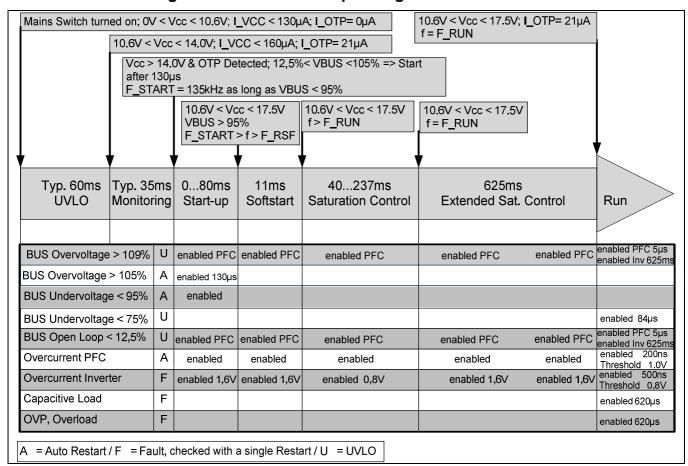

### 2.4.1 Monitoring of Features versus Operating Mode

Figure 21 Monitoring of Features versus Operation Mode

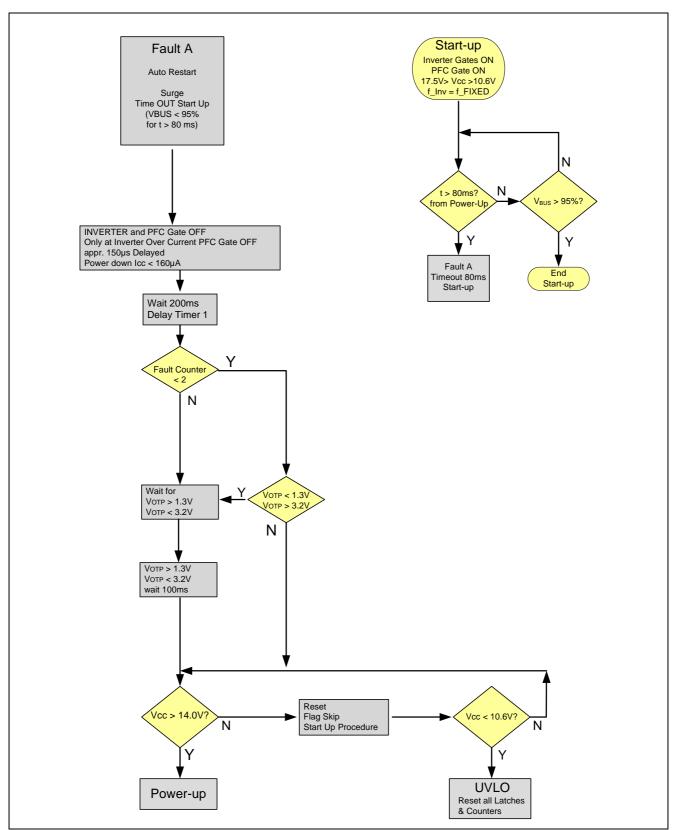

# 2.4.2 Fault Condition – Flow Chart Fault F: Latch OFF after Single Restart

Figure 22 Fault Condition F – Latch OFF after Single Restart

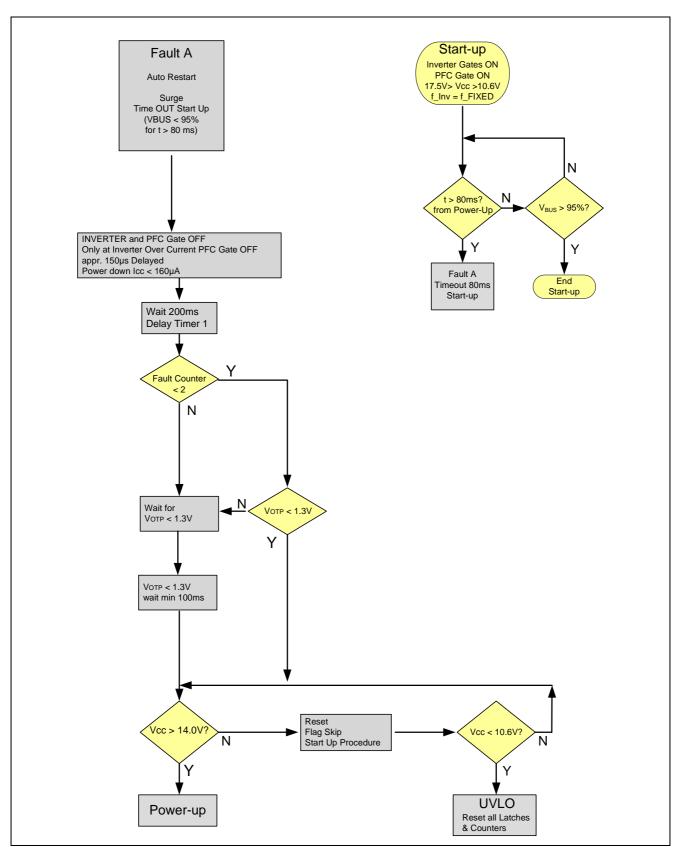

### 2.4.3 Fault Condition – Flow Chart Fault A: Auto Restart

Figure 23 Fault Condition A – Auto Restart

### 2.4.4 Fault Condition – Flow Chart Fault U: BUS Voltage

Figure 24 Fault Condition U - BUS Voltage

### 2.4.5 Protection Matrix

| Description of Fault                                                                                                    | Characteristics of Fault  |               |                                  |            | Operating Mode Detection is active |                              |                   |                                  |                         |          | Consequence                                                             |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------|----------------------------------|------------|------------------------------------|------------------------------|-------------------|----------------------------------|-------------------------|----------|-------------------------------------------------------------------------|

|                                                                                                                         | Name of fault             | Type of fault | Minimum<br>duration<br>of effect | Monitoring | Power-up 130µs                     | Start-up until<br>VBUS > 95% | Softstart<br>11ms | Saturation control<br>40 ms typ. | Ext. Sat. Con.<br>625ms | Run mode |                                                                         |

| Supply voltage Vcc < 14.1V before power up                                                                              | Below start-up threshold  | S             | 1µs                              | X          |                                    |                              |                   |                                  |                         |          | Prevents power up                                                       |

| Supply voltage Vcc < 10.6V after power up                                                                               | Below UVLO<br>threshold   | S             | 5µs                              | X          | X                                  | X                            | X                 | X                                | X                       | X        | Power down,<br>Reset failure latch                                      |

| Voltage at OTP pin > 1.6V before power up                                                                               | Overtemperature           | S             | 100µs                            | X          |                                    |                              |                   |                                  |                         |          | Prevents power up                                                       |

| Voltage at OTP pin > 3.2V                                                                                               | Overtemperature           | F             | 620µs                            |            |                                    |                              |                   |                                  |                         | X        | Power down, latched fault mode, 1 restart                               |

| Bus voltage < 12.5% of rated level 10µs after power up                                                                  | Open loop detection       | S             | 1µs                              |            | X                                  |                              |                   |                                  |                         |          | Keep gate drives off, restart after Vcc hysteresis                      |

| Bus voltage < 12.5% of rated level                                                                                      | Open loop detection       | N             | 1µs                              |            |                                    | X                            | X                 | X                                | Х                       | X        | Stops PFC FET until VBUS > 12.5%                                        |

| Bus voltage < 12.5% of rated level                                                                                      | Shutdown option           | U             | 625ms                            |            |                                    |                              |                   |                                  |                         | X        | Power down, restart<br>when VBUS> 12.5%                                 |

| Bus voltage < 75%<br>of rated level<br>add. shut down delay 120µs                                                       | Under voltage             | U             | 84µs                             |            |                                    |                              |                   |                                  |                         | X        | Power down, 100ms<br>delay, restart directly<br>with saturation control |

| Bus voltage < 95% of rated level during start-up                                                                        | Timeout max start-up time | Α             | 80ms                             |            |                                    | X                            |                   |                                  |                         |          | Power down, 200ms delay, restart                                        |

| Bus voltage > 105% of rated level 10µs after power up                                                                   | PFC overvoltage           | S             | 5µs                              |            | X                                  |                              |                   |                                  |                         |          | Keep gate drives off, restart after Vcc hysteresis                      |

| Bus voltage > 109% of rated level in active operation                                                                   | PFC overvoltage           | N             | 5µs                              |            |                                    | X                            | X                 | X                                | X                       | X        | Stops PFC FET until VBUS< 105%                                          |

| Bus voltage > 109% of rated level in active operation                                                                   | Inverter overvoltage      | U             | 625ms                            |            |                                    |                              |                   |                                  |                         | X        | Power down, restart when VBUS<105%                                      |

| peak level of output voltage at Pin OVP above threshold                                                                 | Output overvoltage        | F             | 620µs                            |            |                                    |                              |                   |                                  |                         | Х        | Power down, latched fault mode, 1 restart                               |

| Capacitive Load operation below resonance                                                                               | Overload                  | F             | 620µs                            |            |                                    |                              |                   |                                  |                         | X        | Power down, latched fault mode, 1 restart                               |

| Voltage at PFCCS pin > 1.0V                                                                                             | PFC overcurrent           | N             | 200ns                            |            |                                    | X                            | X                 | X                                | Х                       | X        | Stops on-time of PFC FET immediately                                    |

| Voltage at LSCS pin > 0.8V                                                                                              | Inverter current lim      | N             | 200ns                            |            |                                    |                              |                   | X                                |                         |          | Activates saturation control                                            |

| Voltage at LSCS pin > 1.2V<br>& 205mV/µs Slope in 0.8V                                                                  | Saturation<br>Time OUT    | F             | 237ms                            |            |                                    |                              |                   | X                                |                         |          | Power down, latched fault mode, 1 restart                               |

| Voltage at LSCS pin > 0.8V<br>& 205mV/µs Slope                                                                          | Ext. Sat. Time<br>OUT     | F             | 625ms                            |            |                                    |                              |                   |                                  | Х                       |          | Power down, latched fault mode, 1 restart                               |

| Voltage at LSCS pin > 0.8V                                                                                              | Inverter overcurrent      | F             | 500ns                            |            |                                    |                              |                   |                                  |                         | X        | Power down, latched fault mode, 1 restart                               |

| Voltage at LSCS pin > 1.6V                                                                                              | Inverter<br>overcurrent   | F             | 500ns                            |            |                                    | X                            | X                 | X                                | X                       |          | Power down, latched fault mode, 1 restart                               |

| Voltage at LSCS pin > 0.8V<br>& VBUS > 109% (Surge)                                                                     | Inverter<br>overcurrent   | Α             | 500ns                            |            |                                    |                              |                   |                                  | X                       | X        | Power down, restart<br>when VBUS<109%                                   |