# User's Manual SYG-70CP-BA & SYG-70CR-BA

| WIRELESS       | S             | tatus 📲 🧟         | SSPv1.2.0         |

|----------------|---------------|-------------------|-------------------|

| SSID:          | Default       | Subscribed?:      | No                |

|                |               | Last Publish:     | 3                 |

| Security Type: | WPA2          | Last Subscribe Ms | g.:               |

| IP Address:    | 192.168.2.192 | CLOUD             |                   |

| DNS Server:    | 75.75.75.75   | Cloud Agent:      | IBM Bluemix       |

|                |               | Organization ID:  | quickstart        |

|                |               | Device Type:      | iotqs-sensor      |

|                |               | Device ID:        | 00_25_ca_07_ab_e9 |

|                | Sensor        |                   |                   |

|                |               |                   |                   |

Copyright ©2017, Future Designs, Inc., All Rights Reserved

#### Important Legal Information

Information in this document is provided solely to enable the use of Future Designs, Inc. (FDI) products. FDI assumes no liability whatsoever, including infringement of any patent or copyright. FDI reserves the right to make changes to these specifications at any time, without notice. No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, for any purpose, without the express written permission of Future Designs, Inc. 996 A Cleaner Way, Huntsville, AL 35805.

**NOTE:** The inclusion of vendor software products in this kit does not imply an endorsement of the product by Future Designs, Inc.

∑yG<sup>™</sup> is a trademark of Future Designs, Inc.

Renesas Synergy<sup>™</sup> is a trademark of Renesas Electronics Corporation.

Microsoft, MS-DOS, Windows, Windows XP, Microsoft Word are registered trademarks of Microsoft Corporation.

Other brand names are trademarks or registered trademarks of their respective owners.

Printed in the United States of America.

For more information on FDI or our products please visit www.TeamFDI.com. © 2017 Future Designs, Inc. All rights reserved.

## **Table of Contents**

| In  | nportan           | t Legal Information                                      | . 2 |  |

|-----|-------------------|----------------------------------------------------------|-----|--|

| 1   | SYG               | -70CP-BA and SYG-70CR-BA Overview                        | . 6 |  |

|     | 1.1               | Introduction                                             | . 6 |  |

|     | 1.2               | ESD Warning                                              | . 6 |  |

|     | 1.3               | Calibrating the Touch Screen                             | . 7 |  |

|     | 1.4               | SYG-70CP-BA Block Diagram                                | . 8 |  |

|     | 1.5               | SYG-70CR-BA Block Diagram                                | 10  |  |

|     | 1.6               | Component Layout                                         | 11  |  |

|     | 1.7               | Specifications                                           | 13  |  |

|     | 1.7.2             | L Display Specifications                                 | 13  |  |

|     | 1.7.2             | 2 Microcontroller and Memory Specifications              | 13  |  |

|     | 1.7.3             | Board Specifications                                     | 14  |  |

|     | 1.7.4             | 4 Overall Specifications                                 | 14  |  |

|     | 1.8               | Board Dimensions                                         | 15  |  |

| 2   | Inpu              | t Power Sources                                          | 16  |  |

|     | 2.1               | 5V input via USB Mini-B (P2)                             | 16  |  |

|     | 2.2               | Alternate Power Connection (J5) 1                        |     |  |

|     | 2.3               | Power Requirements                                       | 17  |  |

|     | 2.3.2             | USB Power (P2)                                           | 17  |  |

|     | 2.3.2             | 2 70-pin Expansion Connectors (J6 & J7)                  | 17  |  |

|     | 2.3.3             | Alternate Power & Communication Interface Connector (J5) | 18  |  |

| 3   | Rene              | esas Synergy S7G2 Microcontroller                        | 19  |  |

| 4   | Development Tools |                                                          | 20  |  |

|     | 4.1               | e2 studio                                                | 20  |  |

| 4.2 |                   | IAR Embedded Workbench® for Synergy                      | 20  |  |

|     | 4.3               | Synergy Software Package (SSP)                           |     |  |

|     | 4.4               | TraceX <sup>®</sup>                                      |     |  |

|     | 4.5               | GUIX Studio™                                             |     |  |

|     | 4.6               | Renesas Verified Software Add-Ons                        | 21  |  |

|     | 4.7               | Renesas Qualified Software Add-Ons                       | 21  |  |

| 5                                      | В   | oard S | upport Package (BSP)                                                | 22 |

|----------------------------------------|-----|--------|---------------------------------------------------------------------|----|

| 6                                      | N   | /lemor | y                                                                   | 23 |

| 6.1 32 MB External SDRAM               |     | 32     | MB External SDRAM                                                   | 23 |

| 6.2 16MB QSPI Flash, MX25L12835FMI-10G |     | 16     | MB QSPI Flash, MX25L12835FMI-10G                                    | 27 |

| 7                                      | Ρ   | eriphe | rals                                                                | 28 |

| -                                      | 7.1 | LC     | D Panel                                                             | 28 |

|                                        | 7   | .1.1   | 7.0" TFT WVGA 800x480 PCAP Touch Screen Display (-70CP models only) | 28 |

|                                        | 7   | .1.2   | 7.0" TFT WVGA 800x480 4WR Touch Screen Display (-70CR models only)  | 29 |

|                                        | 7   | .1.3   | Backlight Generator                                                 | 29 |

|                                        | 7   | .1.4   | LCD Interface                                                       | 30 |

|                                        | 7   | .1.5   | LCD Power Switch                                                    | 31 |

|                                        | 7   | .1.6   | LCD Bias Voltage Generator                                          | 31 |

|                                        | 7   | .1.7   | PCAP Touch Interface (SYG-70CP-BA)                                  | 32 |

|                                        | 7   | .1.8   | Resistive Touch Interface (SYG-70CR-BA)                             | 32 |

|                                        | 7.2 | Wi     | -Fi and Bluetooth Low Energy                                        | 33 |

|                                        | 7   | .2.1   | Wi-Fi Module                                                        | 34 |

|                                        | 7   | .2.2   | BLE Module                                                          | 35 |

|                                        | 7.3 | SD     | card interface                                                      | 35 |

|                                        | 7   | .3.1   | microSD Card Insertion Instructions                                 | 38 |

|                                        | 7   | .3.2   | microSD Card Removal Instructions                                   | 39 |

|                                        | 7.4 | US     | B Device                                                            | 40 |

|                                        | 7.5 | Re     | al-Time Clock                                                       | 41 |

|                                        | 7   | .5.1   | Supercapacitor Backup                                               | 42 |

|                                        | 7   | .5.2   | Off-Board Battery                                                   | 43 |

|                                        | 7.6 | Au     | dio Amplifier                                                       | 44 |

|                                        | 7   | .6.1   | On-Board Speaker                                                    | 46 |

|                                        | 7   | .6.2   | Optional On-Board Buzzer                                            | 47 |

|                                        | 7   | .6.3   | Optional Off-Board Speaker Support                                  | 48 |

|                                        | 7.7 | 3-4    | Axis Accelerometer                                                  | 49 |

|                                        | 7.8 |        | mperature Sensor                                                    |    |

|                                        | 7.9 | An     | nbient Light / Proximity Sensor                                     | 51 |

|                                        |     |        |                                                                     |    |

| 7.10  | PMOD Type 2A Connector with SPI and optional I2C | . 52 |

|-------|--------------------------------------------------|------|

| 7.11  | Cortex-M 9-pin JTAG Debug Connector              | . 53 |

| 7.1   | 11.1 10 Pin Tag-Connect                          | . 55 |

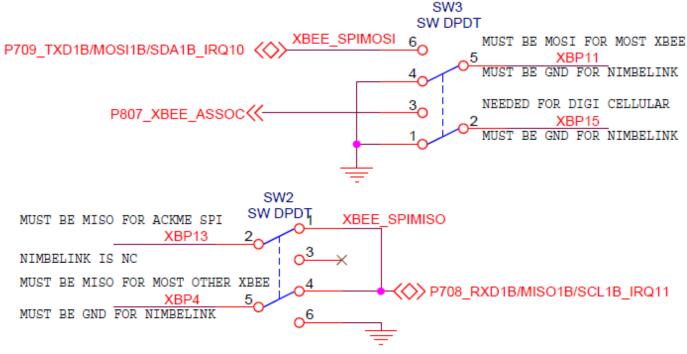

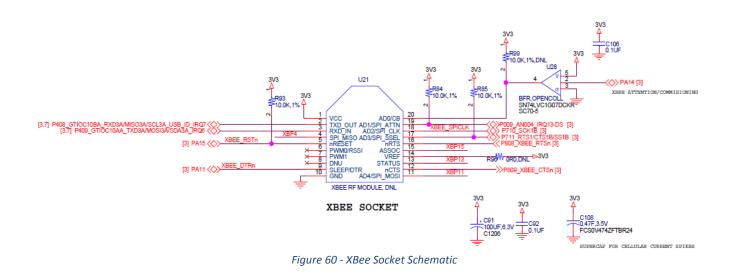

| 7.12  | XBee Expansion Socket                            | . 57 |

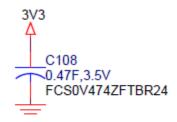

| 7.1   | 12.1 XBee supercapacitor                         | . 59 |

| 7.13  | Expansion Connectors                             | . 60 |

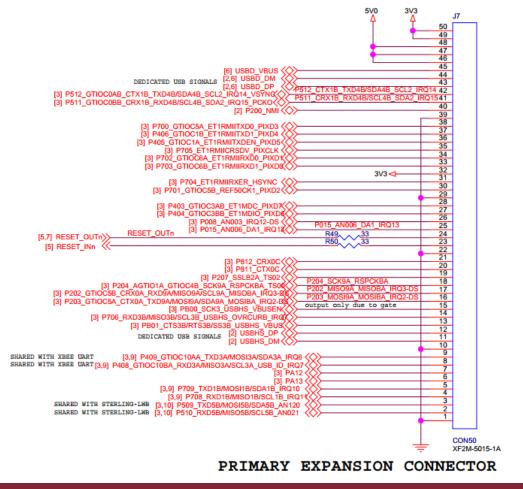

| 7.1   | 13.1 50 Pin Expansion Connector Pin Details      | . 61 |

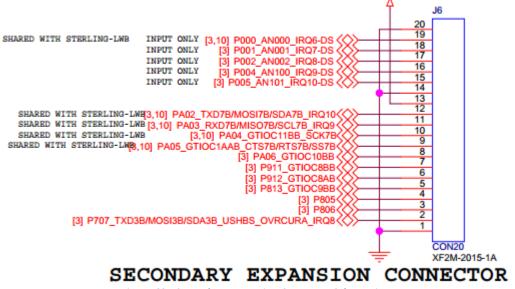

| 7.1   | 13.2 20 Pin Expansion Connector Pin Details:     | . 66 |

| 7.1   | 13.3 50 Pin Primary Expansion Connector (J7)     | . 68 |

| 7.1   | 13.4 20 Pin Secondary Expansion Connector (J6)   | . 71 |

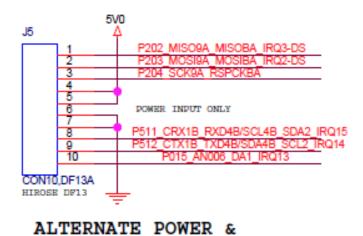

| 7.1   | 13.5 10 Pin Alternate Power & Comm Interface     | . 74 |

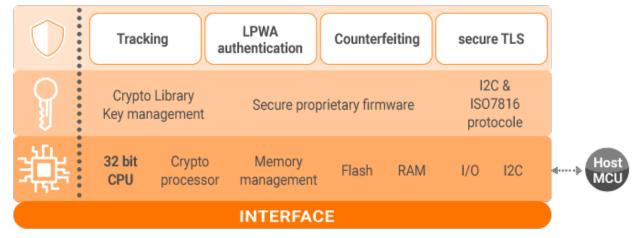

| 8 Se  | curity – TO136 Secure Element                    | . 75 |

| 9 Pro | ogramming Methods                                | . 76 |

| 9.1   | JTAG / SWD                                       | . 76 |

| 9.2   | SCI Boot                                         | . 77 |

| 10    | Additional Information                           | . 79 |

| 10.1  | UbiquiOS Wireless Stack                          | . 79 |

| 10    | .1.1 ubiquiOS License Key                        | . 80 |

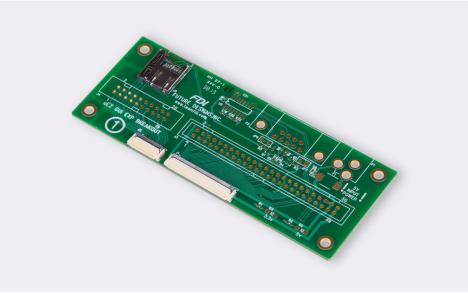

| 10.2  | 70-pin Breakout Expansion Board                  | . 80 |

| 10.3  | Additional Expansion Board Support               | . 81 |

| 10    | .3.1 Configuration Data in Data Flash            | . 82 |

| 11    | Support                                          | . 83 |

| 11.1  | Where to Get Help                                | . 83 |

| 11.2  | Useful Links                                     | . 83 |

# 1 SYG-70CP-BA and SYG-70CR-BA Overview

#### 1.1 Introduction

The Future Designs, Inc.  $\Sigma yG^{TM}$  (pronounced "sig") Family provides a complete and qualified Graphical User Interface (GUI) / Human Machine Interface (HMI) platform for the rapid release of customer products. The core of  $\Sigma yG$  is Renesas Synergy<sup>TM</sup> – a comprehensive and integrated software-based microcontroller platform. FDI adds the Synergy platform to its GUI hardware, systems, and production expertise. The result is a sum of high-quality products that provide a robust and proven source for GUI and HMI solutions:

$\Sigma yG = Renesas Synergy + GUI$

## 1.2 ESD Warning

The SYG-70CP-BA and SYG-70CR-BA are shipped in a protective anti-static package. Do not subject the module to high electrostatic potentials. Exposure to high electrostatic potentials may cause damage to the boards that will not be covered under warranty. General practice for working with static sensitive devices should be followed when working with the kit.

#### 1.3 Calibrating the Touch Screen

Upon first booting the Out of Box (OOB) Demo, Sensor to Cloud, the board will prompt for touch screen calibration. Once calibration is complete, the calibration data is saved into the non-volatile data storage where it is accessed by other programs later. This data persists through power loss so that calibrating will not be necessary on subsequent boots. Reference section 10.3.1 for organization and location of this data.

Figure 1 – Calibration Screen

The screen can be calibrated again at any time by pressing the "Calibration" button on the Status screen.

Status .16 🜀 SSPv1.2.0 CONNECTION WIRELESS SSID: Subscribed?: XXX Last Publish: xxx Security Type: Last Subscribe Msg.: xxx IP Address: CLOUD XXX DNS Server: Cloud Agent: XXX XXX Organization ID: xxx Device Type: XXX Device ID: xxx Sensor Calibration

Figure 2 – Status Screen

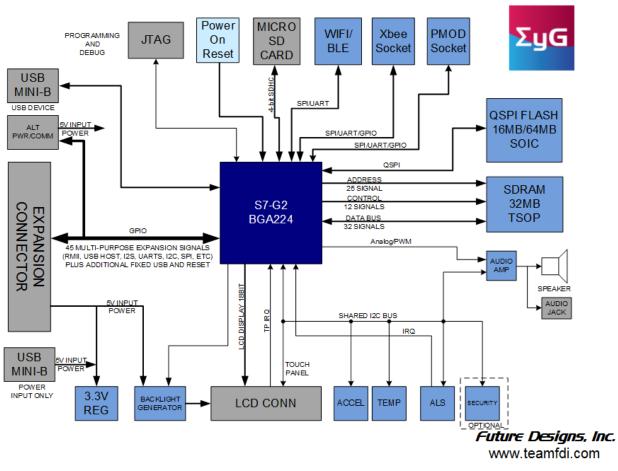

1.4 SYG-70CP-BA Block Diagram

Figure 3 - SYG-70CP-BA Block Diagram

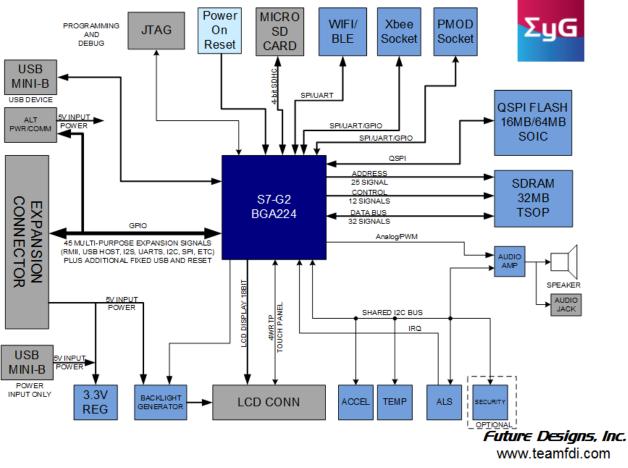

# 1.5 SYG-70CR-BA Block Diagram

Figure 4 - SYG-70CR-BA Block Diagram

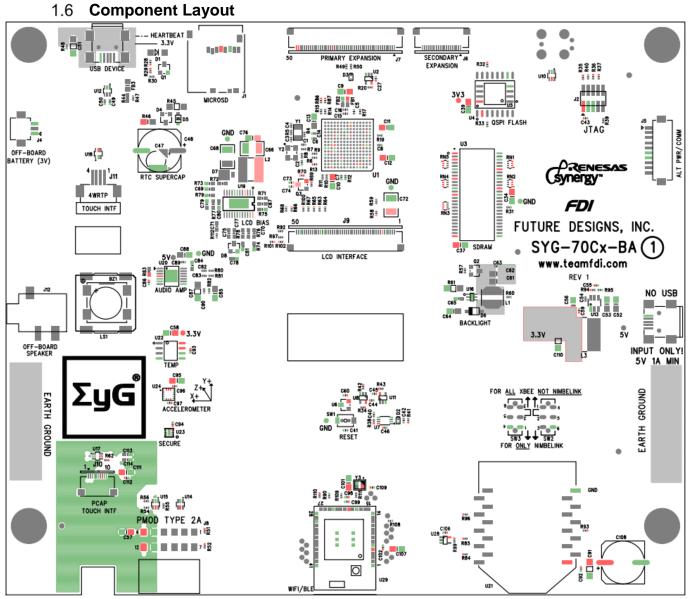

**Board Layout**

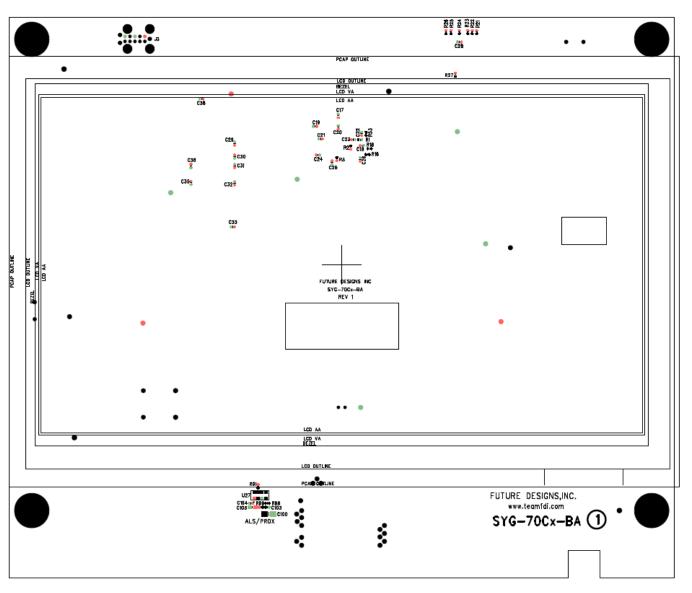

Figure 5 - Component Layer (Top)

**FDI** Copyright ©2017, Future Designs, Inc

Figure 6 – Component Layer (Bottom)

## 1.7 Specifications

## 1.7.1 Display Specifications

| Screen Size (inches)                 |             | 7                |

|--------------------------------------|-------------|------------------|

| Touch Screen Type                    | SYG-70CP-BA | РСАР             |

|                                      | SYG-70CR-BA | 4-Wire Resistive |

| Display Techno                       | logy        | a-si TFT         |

| Brightness (nits typ)                | SYG-70CP-BA | 300              |

|                                      | SYG-70CR-BA | 280              |

| Resolution                           |             | 800x480 (WVGA)   |

| Contrast Ratio                       | (typ)       | 500:1            |

| Aspect Rati                          | 0           | 15:9             |

| Colors                               |             | 262k (18 bit)    |

| Pixel Pitch (W x H                   | Hmm)        | 0.179 x 0.1926   |

| Viewing Angles (U/D L/R) SYG-70CP-BA |             | 60/70° 70/70°    |

| SYG-70CR-BA                          |             | 50/70° 70/70°    |

| Surface Finis                        | sh          | Anti-glare       |

| Touch Panel Hardness                 | SYG-70CP-BA | 5H               |

|                                      | SYG-70CR-BA | 3Н               |

| Active Area (W x H mm)               | SYG-70CP-BA | 154.08 x 85.95   |

|                                      | SYG-70CR-BA | 154.08 x 85.92   |

| Response Time (ms typ)               |             | 25 Tr / 25 Tf    |

| Backlight LEI                        | Ds          | 24 (3S x 8P)     |

| Backlight Life (                     | hrs)        | 20k              |

| Backlight Power Consumption (mW typ) |             | 1536             |

## 1.7.2 Microcontroller and Memory Specifications

| MCU (Microcontroller)          | Renesas S7G2 |  |

|--------------------------------|--------------|--|

| Microcontroller Family         | S7           |  |

| Microcontroller Clock (MHz)    | 240          |  |

| Microcontroller SRAM (KB)      | 640          |  |

| Microcontroller Flash (KB)     | 4092         |  |

| External Flash (MB)            | 16           |  |

| External Flash Type            | QSPI         |  |

| Optional External Flash (MB)   | 64           |  |

| External SDRAM (MB)            | 32           |  |

| Optional External SDRAM (MB)   | 64           |  |

| Non-volatile data storage (KB) | 64           |  |

## 1.7.3 Board Specifications

| SD Card Interface                     | 4-bit SD Card Interface                                   |  |

|---------------------------------------|-----------------------------------------------------------|--|

| USB                                   | Device                                                    |  |

| Accelerometer                         | Yes                                                       |  |

| Temp Sensor                           | Yes                                                       |  |

| Super Cap RTC Backup                  | Yes                                                       |  |

| Ambient Light Sensor                  | Yes                                                       |  |

| On-board Speaker                      | Yes                                                       |  |

| Headphone Jack                        | Yes                                                       |  |

| Additional Features                   | Wi-Fi, Bluetooth LE, Cellular, XBEE                       |  |

| Power Input                           | USB Device Mini-B or Hirose DF13 or Flex Cable            |  |

| Input VDC                             | 5                                                         |  |

| Power Consumption (mA typ/max)        | 800/955                                                   |  |

| Operating Temperature                 | -20° to 70° C                                             |  |

| Storage Temperature                   | -30° to 80° C                                             |  |

| JTAG                                  | J-Link Lite CortexM-9 Debug Connector                     |  |

| Tag Connect                           | Yes                                                       |  |

| Expansion Connector                   | UART, I2C, SPI, USB Host/Device, RMII for Ethernet 10/100 |  |

| Other Expansion Ports                 | UART, SPI, I2C, RTC Ext. Battery                          |  |

| Pmod Interface                        | Type 2A                                                   |  |

| Reverse Scan                          | None                                                      |  |

| Video Playback from microSD Interface | Yes                                                       |  |

| Mounting                              | #6 screws in 4 corners                                    |  |

# 1.7.4 Overall Specifications

| Size (W x H x D mm) | 170.18 x 143.64 x 14.70 |

|---------------------|-------------------------|

| Weight (grams)      | 275                     |

| RoHS Compliant      | Yes                     |

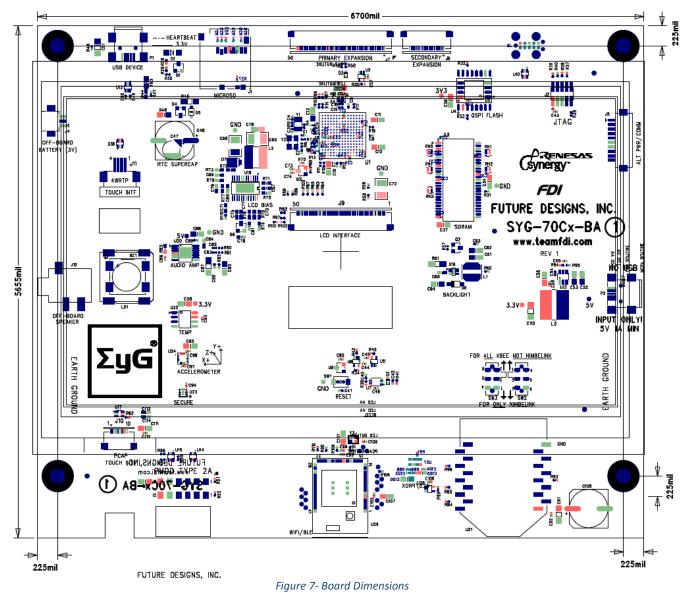

#### 1.8 Board Dimensions

Note: Mounting holes are .167" in diameter and are not threaded, but do provide Earth Ground

Not Pictured: Total Height – 822 mil, Height off PCB – 319 mil

**FDI** Copyright ©2017, Future Designs, Inc

## 2 Input Power Sources

The SYG-70CP-BA and SYG-70CR-BA can both be powered multiple ways depending on your requirements. The various power input methods are described below.

#### Input power requirements are 5V ±5%, 1 A minimum.

## 2.1 5V input via USB Mini-B (P2)

The most convenient power source available is the USB Mini-B connector. This connector is labeled "NO USB" "INPUT ONLY! 5V 1A MIN" so that it cannot be confused with the USB Mini-B Device port. No data is sent over this cable, it is strictly for powering the SYG-70CP.

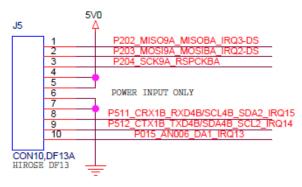

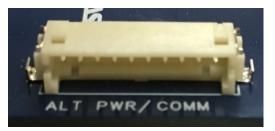

### 2.2 Alternate Power Connection (J5)

The alternate power connector comes in the form of the DF13A-10P-1.25H connector. This connector accepts the DF13-10S-1.25C socket connector. Pins 4 and 5 accept 5V and pins 6 and 7 accept Ground. The remaining lines are for use with COMMs and will be described in the peripheral section of this manual.

ALTERNATE POWER & COMM INTERFACE

#### 2.3 **Power Requirements**

2.3.1 USB Power (P2)

#### Rating: +5VDC ±5%, 1A Minimum Input

+5VDC  $\pm$ 5% is the input power range specification. The +5VDC output level to either the Expansion Board connector or the 5V devices may be affected if the +5VDC input power is not within specifications.

- USB High Power Specifications are 500mA maximum, and 4.75V to 5.25V standard.

- USB Low Power Specifications are 100mA maximum, and 4.4V to 5.25V standard.

2.3.2 70-pin Expansion Connectors (J6 & J7)

Rating: +5VDC ±5%, 300mA Maximum Output (1A Minimum if Input)

The SYG-70CP-BA/SYG-70CR-BA can provide a maximum of 300mA of 3.3V power for "external use" over the expansion connectors J7 (50 pin) and J6 (20 pin).

If more than 300mA of 3.3V is needed for an expansion board:

- Then the primary power input (i.e. 5V) should be located on the expansion board rather than on the SYG-70CP

- The expansion board should include its own 3.3V voltage regulator

- Ensure the 3.3V voltage rails of the SYG-70CP-BA/SYG70CR-BA & Expansion Board are not connected.

- The SYG-70CP-BA/SYG-70CR-BA should be powered using 5V from the expansion board over the 70-pin breakout, instead of powering the expansion board from the SYG-70CP-BA/SYG-70CR-BA USB connector.

More information on this connector can be found in the <u>Expansion Connectors</u> section of this document.

## 2.3.3 Alternate Power & Communication Interface Connector (J5)

Rating: +5VDC ±5%, 1A Minimum Input, 2A Maximum Input

Alternate Power/Communication Interface Connector, J7, is a great alternative to bringing external power onto the SYG-70CP-BA/SYG-70CR-BA in cases where the onboard power regulator isn't sufficient.

More information on this connector can be found in the <u>10 Pin Alternate Power & Comm Interface</u> section of this document.

Note: This is a Power Input only connector. Do not use this connector to power an external device.

# 3 Renesas Synergy S7G2 Microcontroller

The microcontroller unit (MCU) on the SYG-70CP-BA/SYG-70CR-BA is a 32-bit, 240 MHz, Cortex® M4 processor with 4 MB of internal flash and 640 KB of SRAM. MCUs from the Synergy family include qualified commercial-grade software to enable rapid development of applications which require a real-time operating system. The Synergy Software Package (SSP) integrates the full suite of Express Logic® software including the ThreadX RTOS and suite of X-Ware stacks. For more information on Renesas Synergy MCUs visit: <u>https://www.renesas.com/en-us/products/synergy/features.html</u>

# 4 Development Tools

To develop applications for the SYG-70CP-BA/SYG-70CR-BA, it is highly recommended to use one of the two development environments provided with the purchase of SYG-70CP-BA and SYG-70CR-BA. All of the below software is available on the Renesas Synergy Gallery website and includes:

#### 4.1 e2 studio

- The Renesas Synergy<sup>™</sup> Platform's Eclipse-based e2 studio Integrated Solution Development Environment (ISDE) is your workbench, providing you all the tools you need to create differentiated applications for Synergy MCU devices.

- An open tool platform, the Eclipse CDT (C/C++ Development Tooling) standard allows plug-ins for many innovative tool functions. Renesas engineers created solution-based plug-ins for Synergy that guide the design process in three intuitive phases covering Synergy MCUs and software – the Preparation Phase, the Build Phase, and the Debug Phase.

### 4.2 IAR Embedded Workbench® for Synergy

IAR Embedded Workbench, the worlds most widely used embedded development environment, is now completely integrated with the Renesas Synergy<sup>™</sup> Platform. The new product IAR EW for Synergy provides add-on functionality to simplify and accelerate software development, and provide the best performance and smallest code size. Renesas created the Synergy Standalone Configurator (SSC) which is available to IAR EW for Synergy users as a separate download. The SSC includes the Synergy Project Generator as well as the Synergy Project Editor, including configurators like the Clock Configurator, Pin Configurator, RTOS Configurator, and SSP Module Selector/Configurator.

#### 4.3 Synergy Software Package (SSP)

- Part of the Renesas Synergy<sup>™</sup> Platform, the Synergy Software Package (SSP) features software that has been integrated, optimized, tested, and qualified by Renesas for Synergy users and is also maintained and warranted by Renesas on an ongoing basis.

- The SSP includes the ThreadX<sup>®</sup> real-time operating system (RTOS), the X-Ware<sup>™</sup> suite of stacks and middleware (NetX<sup>™</sup>, NetX Duo<sup>™</sup>, USBX<sup>™</sup>, GUIX<sup>™</sup>, FileX<sup>®</sup>) plus other quality stacks, libraries, and drivers all connected by a rich Application Framework for ease of use. A common robust API resides over these components enabling you to focus on your own product application code without delays

#### 4.4 TraceX®

• TraceX<sup>®</sup> is Express Logic's host-based analysis tool that provides developers with a graphical view of real-time system events and enables them to visualize and better understand the behavior of their real-time systems. With TraceX, developers can see clearly the occurrence of system events like interrupts and context switches that occur out of view of standard debugging tools. The ability to identify and study these events, and to pinpoint the timing of their occurrence in the context of the overall system's operation enables developers to resolve programming problems by finding unexpected behavior and letting them investigate specific areas further.

#### 4.5 GUIX Studio™

GUIX Studio<sup>™</sup> provides a complete WYSIWYG screen design environment which allows the user to drag-and-drop graphical elements used to build the UI screens. GUIX Studio automatically generates C code compatible with the GUIX<sup>™</sup> library, ready to be compiled and run on the target. Developers can produce pre-rendered fonts for use within an application using the integrated GUIX Studio font generation tool. Fonts can be generated in monochrome or antialiased formats, and are optimized to save space on the target. Fonts can include any set of characters, including Unicode characters for multi-lingual applications.

#### 4.6 Renesas Verified Software Add-Ons

- A selection of specialty software components developed, licensed, and serviced by Renesas VSA partner companies

- Tested and verified by Renesas to be compatible with the SSP per Renesas SSP interoperability requirements

- Continuously tested for SSP interoperability with each new SSP maintenance release

- Free evaluation version available, full licensing required from the VSA partner company for endproduct production

#### 4.7 Renesas Qualified Software Add-Ons

- A selection of specialty software components, licensed and serviced directly by Renesas

- Developed under the same quality standards and guidelines as the SSP

- Tightly integrated and optimized for use with SSP and API structure

- Free evaluation version available, full licensing required from Renesas for end-product production

# 5 Board Support Package (BSP)

To allow users to begin application development quickly, Board Support Packages have been developed to pre-configure the S7G2 MCU's pins to support the various peripherals on board the SYG-70CP-BA/SYG-70CR-BA. This allows you to focus on application development instead of spending hours tracing signals through schematics. To install the BSP, download the relevant ".pack" files from the TeamFDI website using the links below. The files come packages as a zip and contain both the file for the board and the files for the touch screen. These files can also be found by navigating to the relevant product page under the software tab:

http://www.teamfdi.com/product-details/syg-70cp-ba/#software http://www.teamfdi.com/product-details/syg-70cr-ba/#software

Once you have the files, ensure e2studio or IAR is closed and copy the file into the **Packs** directory of your e2studio or SSC directory.

If you installed e2studio into its default directory, this folder will be located at:

#### C:\Renesas\e2\_studio\internal\projectgen\arm\Packs

If you use IAR Embedded Workbench with SSC, and installed it into its default directory, it will be located at: C:\Renesas\Synergy\SSC\internal\projectgen\arm\Packs

Note: If you use both IAR and e2studio, you must install the pack in BOTH locations.

Once the \*.pack files have been placed into the directory, open e2studio or IAR and either development environment's **New Synergy C Project** wizard will be updated to include the "SYG\_70CP" or "SYG\_70CR" as a new board option to select.

## 6 Memory

#### 6.1 32 MB External SDRAM

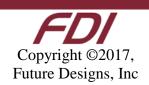

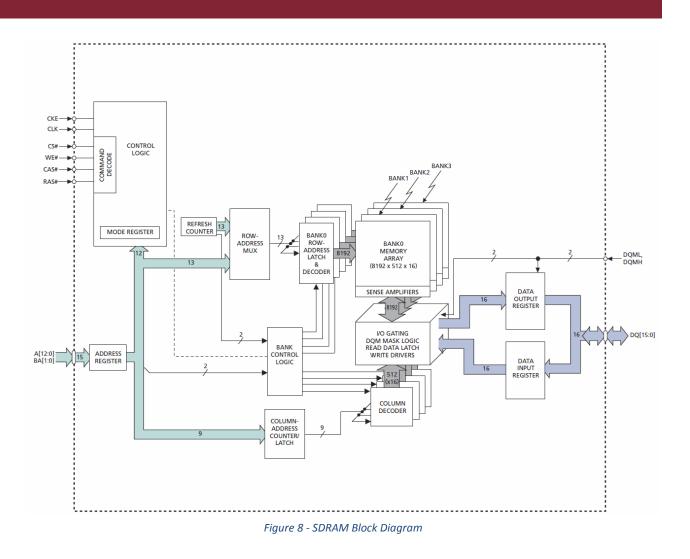

The 32MB 16Mbx16 SDRAM is a high-speed CMOS, dynamic random-access memory in an industry standard 54 ball VFBGA package. It is internally configured as a quad-bank DRAM with a synchronous interface (all signals are registered on the positive edge of the clock signal, CLK). Each of the x16's 67,108,864-bit banks are organized as 8192 rows by 512 columns by 16 bits. The 256Mb SDRAM uses an internal pipelined architecture to achieve high-speed operation. This architecture is compatible with the 2n rule of prefetch architectures, but it also allows the column address to be changed on every clock cycle to achieve a highspeed, fully random access. The 256Mb SDRAM is designed to operate in 3.3V memory systems. An auto refresh mode is provided, along with a power-saving, power-down mode. All inputs and outputs are LVTTL-compatible.

SDRAMs offer substantial advances in DRAM operating performance, including the ability to synchronously burst data at a high data rate with automatic column-address generation, the ability to interleave between internal banks to hide pre-charge time, and the capability to randomly change column addresses on each clock cycle during a burst access.

Micron is a longtime leader in the SDRAM space, offering solutions from 64Mb to 256Mb, as well as a full suite of simulation models and technical support. The MT48LC16M16A2P-6AIT:G is supported on a cost effective 50nm process technology, with assured lifecycle support for years to come.

For more technical information visit http://www.micron.com/

This memory is accessed through the S7G2 microcontroller (MCU) External Memory Interface peripheral which is pre-configured on projects created using the provided Board Support Package (BSP).

Figure 9 - SDRAM Schematic

Pin Configuration

**Pin Configuration**

| Module name:    | BUS0           | A03:        | ✓ P113 |

|-----------------|----------------|-------------|--------|

| Operation Mode: | SDRAM 16bit    | ➡ A04:      | ✓ P112 |

| Input/Output    |                | A05:        | ✓ P111 |

| BCLK_SDCLK:     | ✓ P602         | ◄ A06:      | ✓ P301 |

| RD:             | None           | - A07:      | ✓ P302 |

| WR_WR0_DQM0:    | ✓ P601         | ▼ A08:      | ✓ P303 |

| WR1_BC1:        | None           | - A09:      | ✓ P304 |

| SDCS:           | ✓ P611         | ✓ A10:      | ✓ P305 |

| CS0_WE:         | ✓ P610         | ▼ A11:      | ✓ P306 |

| CS1_CKE:        | ✓ P609         | ✓ A12:      | ✓ P307 |

| CS2_RAS:        | ✓ P311         | ✓ A13:      | ✓ P308 |

| CS3_CAS:        | ✓ P312         | ✓ A14:      | ✓ P309 |

| CS4:            | None           | - A15:      | ✓ P310 |

| CS5:            | None           | ✓ A16:      | None   |

| CS6:            | None           | ▼ A17:      | None   |

| CS7:            | None           | ✓ A18:      | None   |

| A00_BC0_DQM1:   | ✓ P608         | ▼ A19:      | None   |

| A01:            | ✓ P115         |             | None   |

| A02:            | ✓ P114         | ▼ A21:      | None   |

| A22:            | None           | _           |        |

| A22:<br>A23:    |                | ✓ D8_DQ8:   | ✓ P612 |

|                 | Vone<br>V P100 |             |        |

| 00_DQ0:         |                | ▼ D9_DQ9:   |        |

| 01_DQ1:         | ✓ P101         | ▼ D10_DQ10: | ✓ P614 |

| )2_DQ2:         | ✓ P102         | ▼ D11_DQ11: | ✓ P605 |

| 3_DQ3:          | ✓ P103         | ▼ D12_DQ12: | ✓ P604 |

| 04_DQ4:         | ✓ P104         | ▼ D13_DQ13: | ✓ P603 |

| 05_DQ5:         | ✓ P105         | ▼ D14_DQ14: | ✓ P800 |

| 06_DQ6:         | ✓ P106         | ▼ D15_DQ15: | ✓ P801 |

| 07_DQ7:         | ✓ P107         | ▼ WAIT:     | None   |

Figure 10 - Synergy SDRAM Pin Configuration

**FDI** Copyright ©2017, Future Designs, Inc

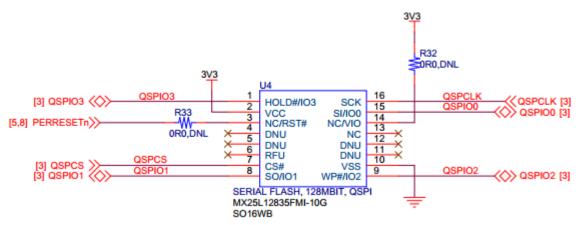

#### 6.2 16MB QSPI Flash, MX25L12835FMI-10G

Macronix Serial Multi I/O (MXSMIO<sup>™</sup>) Flash provides not only Single I/O, but also Multi-I/O interfaces. MX66xxx35 or MX25xxx33/35/39/73/75 series offering Dual I/O or Quad I/O operations which double or quadruple the read performance of systems for high-end consumer applications.

The QSPI Flash provides additional Code Space if needed, but also provides storage for fonts and images (which can be large on WVGA displays such as this one).

This memory is accessed through the S7G2 MCU's dedicated QSPI0 peripheral port.

Figure 11 – QSPI Flash Pin Connections

| Module name:<br>Usage: | QSPI0<br>For QSPI, same Pin Group | Recommended |

|------------------------|-----------------------------------|-------------|

| Pin Group Selection:   | _A only                           | •           |

| Operation Mode:        | Quad                              | •           |

| Input/Output           |                                   |             |

| QSPCLK:                | ✓ P500                            | -           |

| QSSL:                  | ✓ P501                            | -           |

| QIO0:                  | ✓ P502                            | -           |

| QIO1:                  | ✓ P503                            | -           |

| QIO2:                  | ✓ P504                            | -           |

| QIO3:                  | ✓ P505                            | -           |

Figure 12 - Synergy QSPI Flash Pin Configuration

**FDI** Copyright ©2017, Future Designs, Inc

# 7 Peripherals

The SYG-70CP-BA/SYG-70CR-BA has a large variety of peripherals available to use in a wide array of projects. A Board Support Package (BSP) is provided with the purchase of the SYG-70CP-BA/SYG-70CR-BA and is used to greatly simplify the configuration of the specific I/O needed for a given project. After installing the BSP, creating a New Synergy C Project dialog inside of e2 Studio or IAR Embedded Workbench will allow for the selection of the SYG-70CP-BA/SYG-70CR-BA. Creating a new project with this board choice will create a default pin configuration that will be used to configure the S7G2 MCU through the Synergy Configurator in e2 Studio or the Synergy Standalone Configurator (SSC) in IAR Embedded Workbench. There are certain options that are not configured by default, but are optional depending on your project requirements. Refer to the following sections to determine configuration requirements specific to your project and I/O needs.

## 7.1 LCD Panel

7.1.1 7.0" TFT WVGA 800x480 PCAP Touch Screen Display (-70CP models only) The SYG-70CP-BA is equipped with a Tianma TM070RVHG01-01 7.0" TFT WVGA Projected Capacitance Touch screen display. This 800 x 480 touch screen has a 15:9 aspect ratio and 300 nits of brightness and a contrast ratio of 500:1.

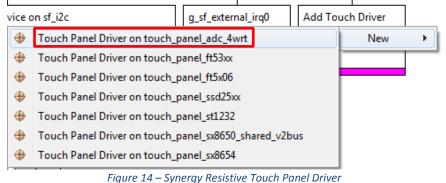

The PCAP Display uses the SSD25XX Touch IC. The correct driver is shown below:

Figure 13 - Synergy Capacitive Touch Panel Driver

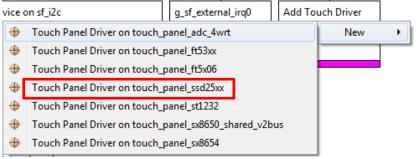

7.1.2 7.0" TFT WVGA 800x480 4WR Touch Screen Display (-70CR models only) The SYG-70CR-BA is equipped with a Tianma TM070RBHG04 7.0" TFT WVGA Projected Capacitance Touch screen display. This 800 x 480 touch screen has a 15:9 aspect ratio and 280 nits of brightness and a contrast ratio of 500:1.

The 4WR Display uses the on-board ADC. The correct driver is shown below:

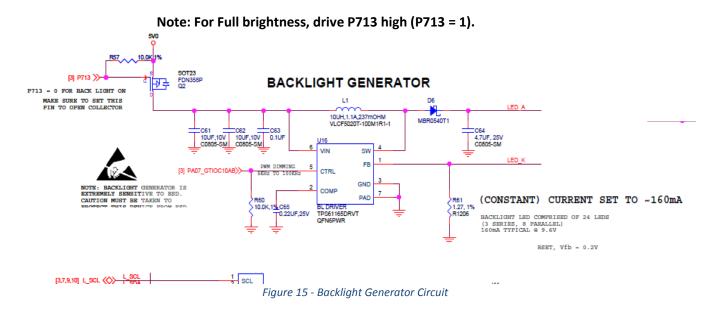

7.1.3 Backlight Generator

Backlight brightness can be controlled using a PWM signal to control the backlight generator circuit. The pin for the PWM signal is configured in the BSP provided with the SYG-70CP-BA/SYG-70CR-BA, and the backlight circuit accepts 5KHz to 100KHz frequencies.

It is also possible to turn off the backlight by setting P713 "low" (Low = 0). See the note on the schematic for more details.

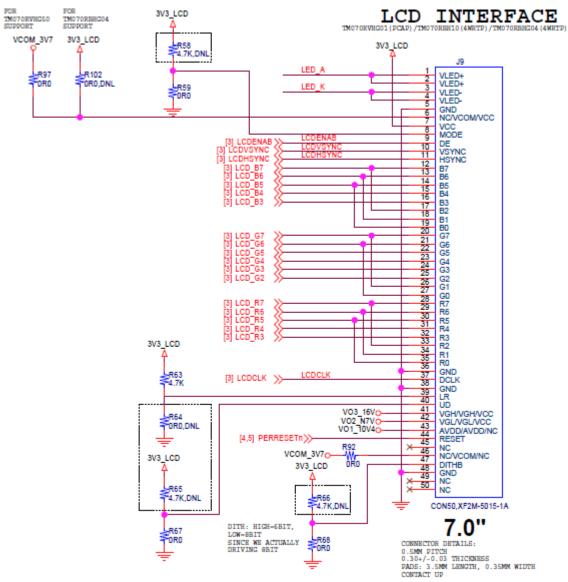

## 7.1.4 LCD Interface

The LCD interfaces with the SYG-70CP-BA/SYG-70CR-BA through connector J9. This 0.5mm pitch flat ribbon cable connector is robust and allows for sturdy connection of the LCD cable to the SYG-70CP-BA/SYG-70CR-BA. Several resistor options are available to support a wide variety of optional LCD displays, if required. The LCD Interface connector schematic is shown below:

Figure 16 - LCD Interface Schematic

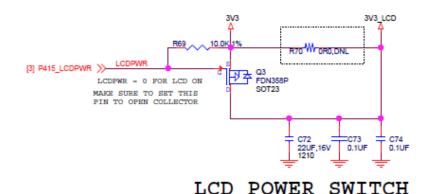

#### 7.1.5 LCD Power Switch

The SYG-70CP-BA/SYG-70CR-BA has an LCD Power Switch circuit that allows for turning off the LCD if desired. This is separate from the backlight control, although the operation of this is similar.

To enable the LCD (which is disabled by default), set P415 (P415\_LCDPWR on the schematic) to "low (Low = 0). See the note on the schematic below for more details.

When Powered Off (P415\_LCDPWR = 1), do not drive any of the LCD control pins on the LCD interface (J9), or damage to the LCD may occur!

Make sure to set P415\_LCDPWR to n-ch open drain for proper operation of the LCD Power Switch circuit.

#### Figure 17 - LCD Power Switch Schematic

#### 7.1.6 LCD Bias Voltage Generator

The SYG-70CP-BA/SYG-70CR-BA features a Bias Voltage Generator that is factory configured to work with either the Tianma TM070RVHG50-00 7.0" TFT WVGA Projected Capacitance Touch screen panel or the Tianma TM070RBHG04 TFT WVGA 4-Wire Resistive Touch screen panel. This bias voltage generation circuit provides accurately calibrated voltages through a highly reliable Texas Instruments TPS65100PWPR LCD Voltage Regulator.

For additional display compatibility, contact FDI at www.teamfdi.com/support

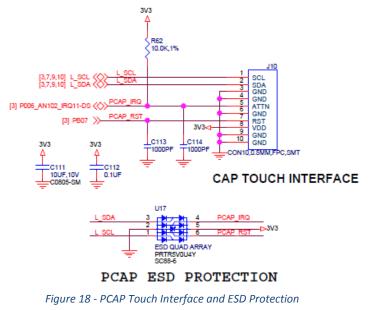

## 7.1.7 PCAP Touch Interface (SYG-70CP-BA)

The 10 pin PCAP Touch Interface connector J10, is a 0.5mm flexible printed circuit cable connection that allows for reliable and robust connections to the touch controller on the LCD. This interface includes an I2C (L\_SCL & L\_SDA) connection, PCAP\_IRQ, and PCAP\_RST to allow for full control over the touch controller on the LCD. It also includes ESD protection to prevent possible damage to the SVG-70CP-RA due to Electrostatic Discharge.

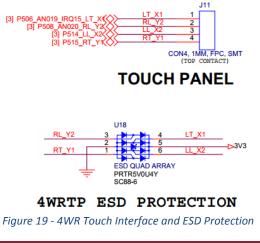

#### 7.1.8 Resistive Touch Interface (SYG-70CR-BA)

The 4 pin Resistive Touch Interface connector J11, is a 1mm flexible printed circuit cable connection that allows for connections to 4 wires from the Resistive Touch Panel. These 4 wires are connected to the S7G2 utilizing the Analog to Digital converter to interpret touch coordinates. It also includes ESD protection to prevent possible damage to the SYG-70CR-BA due to Electrostatic Discharge.

#### 7.2 Wi-Fi and Bluetooth Low Energy

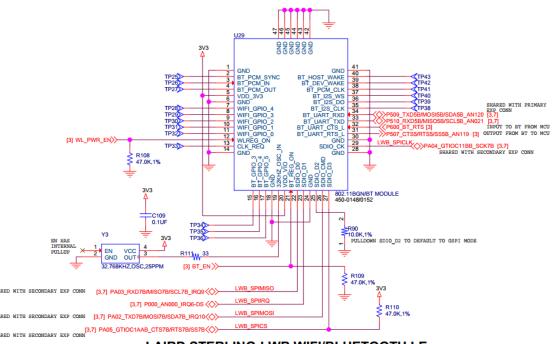

The SYG-70CP-BA/SYG-70CR-BA comes equipped with a Laird/LS Research Sterling-LWB Wi-Fi & Bluetooth Low Energy Module. This Multi-Standard module provides customers with more options, more certifications, and greater flexibility to meet the challenging requirements of many wireless-based designs. This device, which uses a BCM4343W wireless module, is capable of both WIFI and BLE.

#### LAIRD STERLING-LWB WIFI/BLUETOOTH LE

Figure 20 - Laird Wi-Fi & BLE Module Schematic

#### 7.2.1 Wi-Fi Module

The Wi-Fi portion of the Wi-Fi/BLE module is connected to one of the S7G2 MCU's SPI buses (7B). These pins are shared with the secondary expansion connector, detailed later in this document. When connecting to the Secondary Expansion connector and using the Wi-Fi portion of the Wi-Fi/BLE module, be sure that you do not have any conflicting signals

| Module name:                            | SCI7                                                                                                                                          |  |  |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Usage:                                  | When using Simple I2C mode, ensure port pins output type is n-ch<br>open drain.<br>When switching between I2C and other modes, first disable. |  |  |

| Pin Group Selection:<br>Operation Mode: | Mixed   Simple SPI                                                                                                                            |  |  |

| Input/Output                            |                                                                                                                                               |  |  |

| TXD_MOSI:                               | ✓ PA02                                                                                                                                        |  |  |

| RXD_MISO:                               | ✓ PA03                                                                                                                                        |  |  |

| SCK:                                    | ✓ PA04                                                                                                                                        |  |  |

| CTS_RTS_SS:                             | ✓ PA05                                                                                                                                        |  |  |

| SDA:                                    | None 👻                                                                                                                                        |  |  |

| SCL:                                    | None 👻                                                                                                                                        |  |  |

Figure 21 - Wi-Fi SPI Configuration

#### 7.2.2 BLE Module

The BLE portion of the module is connected via UART. The Synergy Configuration software in e2 Studio (or in the standalone Synergy Software Configurator, used with IAR) provides a unique and flexible way to handle the CTS (Clear-to-Send) and RTS (Request-to-Send) signals for asynchronous UART communications. Instead of setting the CTS and RTS pins individually in the UART Peripheral section of the Synergy Configurator, a single pin is selected for CTS/RTS. Once the UART driver module is added to the Threads tab of the Synergy Configurator, then the properties must be adjusted to select whether a RTS signal is needed. If it is, then the GPIO for the RTS line is selected within the software that initialized the UART driver (the default setting is that CTS is used, RTS disabled).

| Module name:         | SCI5                                                                                                                                          |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Usage:               | When using Simple I2C mode, ensure port pins output type is n-ch<br>open drain.<br>When switching between I2C and other modes, first disable. |  |

| Pin Group Selection: | Mixed                                                                                                                                         |  |

| Operation Mode:      | Custom 👻                                                                                                                                      |  |

| Input/Output         |                                                                                                                                               |  |

| TXD_MOSI:            | ✓ P509                                                                                                                                        |  |

| RXD_MISO:            | ✓ P510                                                                                                                                        |  |

| SCK:                 | None -                                                                                                                                        |  |

| CTS_RTS_SS:          | ✓ P507                                                                                                                                        |  |

| SDA:                 | None -                                                                                                                                        |  |

| SCL:                 | None 👻                                                                                                                                        |  |

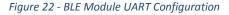

#### 7.3 SD card interface

The SD card interface is connected to the micro SD socket (J1). These signals are dedicated to the microSD Card and are not shared with any other functions on the SYG-70CP. This interface is capable of 4-bit SD mode up to 50 MHz.

MicroSD cards are common, cost effective, and provide a large amount of user-changeable memory.

| 1 | DAT2/RSV    |

|---|-------------|

| 2 | CD_DAT3/CS# |

| 3 | CMD/SDI     |

| 4 | VDD         |

| 5 | CLK/SCLK    |

| 6 | VSS         |

| 7 | DAT0/SDO    |

| 8 | DAT1/RSV    |

| 9 | CD          |

The microSD card must be removed using the spring loaded "push-pull" mechanism on the microSD socket. Forceful removal of a microSD card will result in permanent damage to the socket that is not covered under warranty. To insert the card, push it into the socket until a "click" sound is heard. Similarly, to remove the card, push the card into the socket. The push-pull mechanism will "click" again and eject the card from the socket. The card is now available for safe removal.

Figure 23 - microSD Card Socket

| Module name:         |   | SDHI0                                                                               |   |  |

|----------------------|---|-------------------------------------------------------------------------------------|---|--|

| Usage:               |   | For SDHI, use same Pin Group for signals<br>-Please refer to the MCU User's Manual. |   |  |

| Pin Group Selection: |   | _A only                                                                             | • |  |

| Operation Mode:      |   | SD_MMC 4-Bit                                                                        | • |  |

| Input/Output         |   |                                                                                     |   |  |

| CLK:                 | ~ | P413                                                                                | - |  |

| CMD:                 | ~ | P412                                                                                | - |  |

| DAT0:                | ~ | P411                                                                                | ~ |  |

| DAT1:                | ~ | P410                                                                                | - |  |

| DAT2:                | ~ | P206                                                                                | - |  |

| DAT3:                | ~ | P205                                                                                | - |  |

| DAT4:                |   | None                                                                                | - |  |

| DAT5:                |   | None                                                                                | - |  |

| DAT6:                |   | None                                                                                | - |  |

| DAT7:                |   | None                                                                                | - |  |

| CD:                  | ~ | P903                                                                                | • |  |

| WP:                  |   | None                                                                                | • |  |

Figure 24 - microSD Card Configuration

| 7.3.1 microSD Card Insertion Insertion                                                                                                                                                          | structions                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>1) First, prepare to insert the microSD card into the socket by positioning it with its text facing up. Position the ridge, or "lip", of the card furthest from the socket.</li> </ul> | 2) Next, partially insert the card into the socket.                                                                                 |

| 3) Then, use your finger to gently push the card into the socket. When the card "clicks" into place it is in its final, locked position. The card is now ready for use.                         | <ul> <li>4) Note: Once the microSD card is fully inserted it should not fall out, even if the unit is shaken vigorously.</li> </ul> |

| 7.3.2 microSD Card Removal Ins                                                                                                                  | structions                                                                         |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|

| <ul> <li>1) Begin to remove the microSD card by gently pushing the card into the socket. The socket will "click" and eject the card.</li> </ul> | 2) Once the microSD card is ejected, it will partially extend out from the socket. |  |

| <ul> <li>3) Carefully grab the ridged edge or sides of the microSD card to gently pull it out.</li> </ul>                                       | 4) The microSD card is now fully removed from the socket.                          |  |

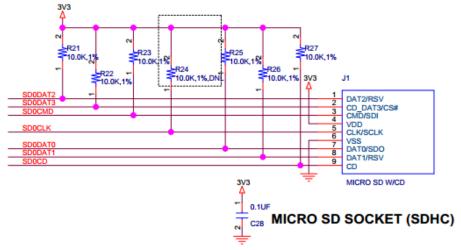

# 7.4 USB Device

The SYG-70CP-BA/SYG-70CR-BA features a USB Device port (P1). This Mini-B connector allows for connecting the SYG-70CP-BA/SYG-70CR-BA to a USB Host device (such as a PC). This port is not meant to power the SYG-70CP-BA/SYG-70CR-BA and it is not recommended to connect this port to a power source (such as a mini-USB wall adapter).

The operational mode of the port is dependent on the software utilized (i.e. Mass Storage or Human-Interface).

|           | Pin Number | Description   |

|-----------|------------|---------------|

|           | 1          | USB 5V        |

|           | 2          | D-            |

|           | 3          | D+            |

|           | 4          | NC            |

| 1 2 3 4 5 | 5          | Signal Ground |

Note: Do not try to power the SYG-70CP-BA/SYG-70CR-BA through this USB Device port (P1). To power the SYG-70CP-BA/SYG-70CR-BA, use either P2 (mini-B USB) or one of the expansion connectors (J5, J6, J7).

# 7.5 Real-Time Clock

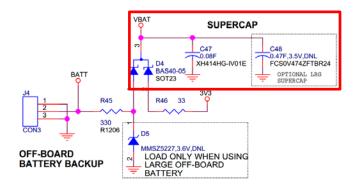

The SYG-70CP-BA/SYG-70CR-BA features a Real-Time Clock (RTC) with an onboard supercapacitor and a 32.768 KHz crystal to accurately track time for a variety of application uses. The onboard supercapacitor 0.08F (C47) allows the RTC to continue to operate even if power is disconnected from the SYG-70CP-BA/SYG-70CR-BA for a short time. An optional 0.47F supercapacitor (C48) is available for a longer backup hold time.

| Settings    | Property                            | Value         |

|-------------|-------------------------------------|---------------|

| Information | ⊿ Common                            |               |

|             | Parameter Checking Enable           | Default (BSP) |

|             | Module g_rtc0 RTC Driver on r_rtc   |               |

|             | Name                                | g_rtc0        |

|             | Clock Source                        | Sub-Clock     |

|             | Error Adjustment Value [DEPRECATED] | 0             |

|             | Error Adjustment Type [DEPRECATED]  | None          |

|             | Callback                            | NULL          |

|             | Alarm Interrupt Priority            | Disabled      |

|             | Period Interrupt Priority           | Disabled      |

|             | Carry Interrupt Priority            | Disabled      |

Figure 26 - RTC Synergy Configuration

#### 7.5.1 Supercapacitor Backup

The RTC supercapacitor (C47) allows for the RTC to continue to when main power is disconnected. The RTC supercapacitor is rated for 3.5V at 70C.

The RTC supercapacitor voltage is connected to the VBAT supply pin to the S7G2 MCU, and allows the MCU to continue to run the RTC even when the main power is disconnected.

The default RTC supercapacitor is 0.08F, but there is an optional 0.47F RTC supercapacitor footprint that allows for longer RTC operating times while the unit is disconnected from power.

Figure 27- RTC Supercapacitor and Off-board Battery Backup Schematic

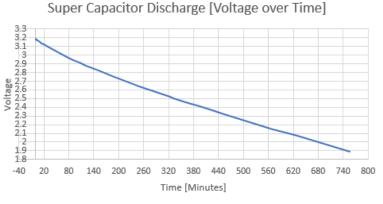

The RTC supercapacitor discharge graph shown below indicates the expected discharge curve when the unit has been plugged in for 24 hours before power was removed. The test unit was set to low power mode with all peripherals set to high impedance.

Figure 28 - Supercapacitor Voltage vs. Time

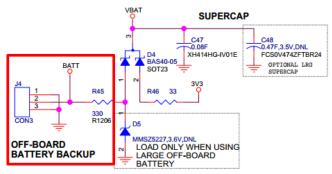

# 7.5.2 Off-Board Battery

The SYG-70CP-BA/SYG-70CR-BA features a three-pin connector that allows for the use of an off-board battery backup. This battery should ideally be no larger than 3.6 Volts (3.3 Volts recommended). When using an off-board battery backup, D5 should also be loaded as a precautionary measure (to prevent high-voltage spikes from reaching the MCU and the RTC supercapacitor).

Figure 29 - Off-board Battery Backup Schematic

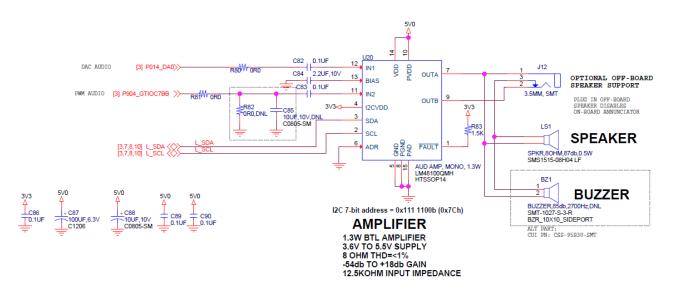

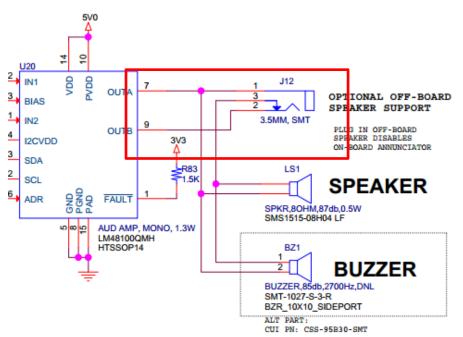

#### 7.6 Audio Amplifier

The SYG-70CP-BA/SYG-70CR-BA features an onboard LM48100Q-Q1 audio amplifier rated at 1.3 Watts. This audio amplifier allows applications to output a wide range of audio types through either a speaker, buzzer, or off-board speaker.

The audio amplifier features volume and mode control via I2C, and has dial audio inputs (for the SYG-70CP-BA/SYG-70CR-BA, these are DAC and PWM audio inputs) that can be mixed/multiplexed to the device output. Each input path has its own independent, 32-step volume control.

The audio amplifier I2C bus, PWM, and DAC pins are configured in the BSP included with the SYG-70CP-BA/SYG-70CR-BA.

#### Figure 30 - Audio Amplifier Schematic

| Module name:    | DAC120    |

|-----------------|-----------|

| Operation Mode: | Enabled 💌 |

| Input/Output    |           |

| DA:             | ✓ P014    |

| Module name:         | GPT7             |

|----------------------|------------------|

| Pin Group Selection: | _B only          |

| Operation Mode:      | GTIOCA or GTIOCB |

| Input/Output         |                  |

| GTIOCA:              | None             |

| GTIOCB:              | ✓ P904           |

| Module name:<br>Usage:                  | IIC0<br>For IIC, use same Pin Group for SDA/SCL signals<br>-Please refer to the MCU User's Manual. |        |  |

|-----------------------------------------|----------------------------------------------------------------------------------------------------|--------|--|

| Pin Group Selection:<br>Operation Mode: | _A only<br>Enabled                                                                                 | ▼<br>▼ |  |

| Input/Output                            |                                                                                                    |        |  |

| SDA:                                    | ✔ P401                                                                                             | -      |  |

| SCL:                                    | ✓ P400                                                                                             | ▼      |  |

Figure 33 - Audio Amp I2C Configuration

# 7.6.1 On-Board Speaker

The on-board speaker on the SYG-70CP-BA/SYG-70CR-BA is a 0.5 Watt 8 Ohm surface mount speaker manufactured by BeStar. This speaker is rated for 87 dBA.

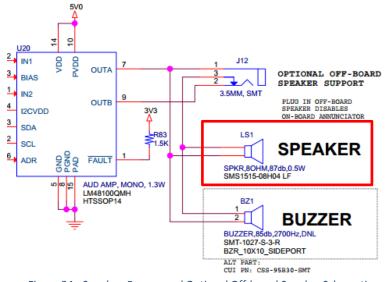

Figure 34 - Speaker, Buzzer, and Optional Off-board Speaker Schematic

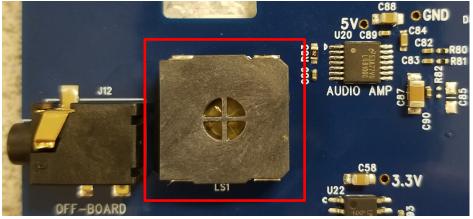

Figure 35 - Onboard Speaker

### 7.6.2 Optional On-Board Buzzer

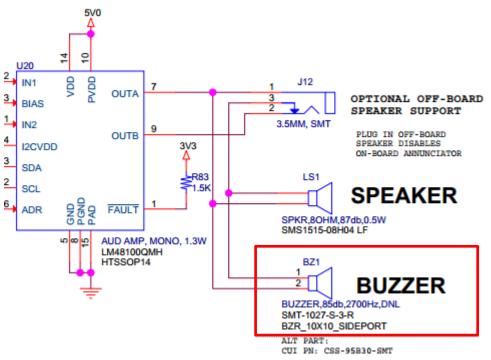

The SYG-70CP-BA/SYG-70CR-BA features an optional on-board buzzer manufactured by PUI Audio, Inc. This surface mount buzzer is rated at 85dB and produces a 2.7 KHz tone.

Figure 36 - Speaker, Buzzer, and Optional Off-board Speaker Schematic

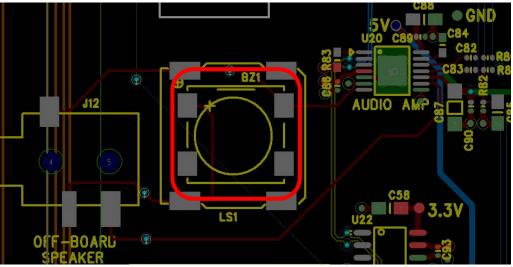

Figure 37 - Optional Footprint for Buzzer on PCB

**FDI** Copyright ©2017, Future Designs, Inc

# 7.6.3 Optional Off-Board Speaker Support

Also available on the SYG-70CP-BA/SYG-70CR-BA is an optional off-board speaker connector (J12). This connector allows for connecting 3.5mm speaker devices to the audio amplifier output. This is useful if your design includes external speakers or has a need to bring the audio output off-board.

Figure 38 - Speaker, Buzzer, and Off-board Speaker Schematic

Figure 39 - Off-board Speaker Connector

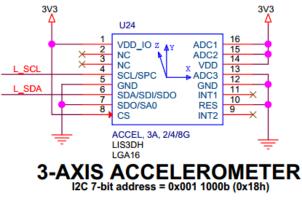

# 7.7 3-Axis Accelerometer

The SYG-70CP-BA/SYG-70CR-BA features the LIS3DH 3-Axis accelerometer, an ultra-low-power highperformance linear accelerometer with an I2C output. The accelerometer has dynamically userselectable full scales of  $\pm 2/\pm 4/\pm 8/\pm 16$  g and is capable of measuring accelerations with output data rates from 1 Hz to 5.3 kHz. It also features a 32-level first-in, first-out (FIFO) buffer allowing the user to store data to limit intervention by the S7G2 MCU.

Figure 41 - 3 Axis Accelerometer Schematic

| Value                                                              |

|--------------------------------------------------------------------|

|                                                                    |

| Default (BSP)                                                      |

|                                                                    |

| g_i2c3                                                             |

| 0                                                                  |

| Standard                                                           |

| 0x18                                                               |

| 7-Bit                                                              |

| NULL                                                               |

| Priority 3 (CM4: valid, CM0+: lowest - not valid if using ThreadX) |

| Priority 3 (CM4: valid, CM0+: lowest - not valid if using ThreadX) |

| Priority 3 (CM4: valid, CM0+: lowest - not valid if using ThreadX) |

| Priority 3 (CM4: valid, CM0+: lowest - not valid if using ThreadX) |

|                                                                    |

*Figure 42 - Accelerometer I2C Driver Configuration Example*

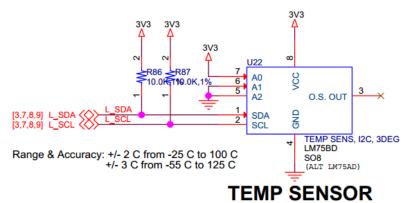

#### 7.8 Temperature Sensor

The SYG-70CP-BA/SYG-70CR-BA features a LM75DB Temperature Sensor. This I2C-based temperature sensor has a range of -55 Celsius to 125 Celsius, with an accuracy of  $\pm$ 2C from -25C to 100 C, and  $\pm$ 3C from -55 C to 125 C.

I2C 7-bit address = 0x100 1001b (0x49h)

Figure 43 - Temperature Sensor Schematic

| Property                                  | Value                                                              |  |

|-------------------------------------------|--------------------------------------------------------------------|--|

| Common                                    |                                                                    |  |

| Parameter Checking                        | Default (BSP)                                                      |  |

| Module g_i2c2 I2C Master Driver on r_riic |                                                                    |  |

| Name                                      | g_i2c2                                                             |  |

| Channel                                   | 0                                                                  |  |

| Rate                                      | Standard                                                           |  |

| Slave Address                             | <u>0x49</u>                                                        |  |

| Address Mode                              | 7-Bit                                                              |  |

| Callback                                  | NULL                                                               |  |

| Receive Interrupt Priority                | Priority 3 (CM4: valid, CM0+: lowest - not valid if using ThreadX) |  |

| Transmit Interrupt Priority               | Priority 3 (CM4: valid, CM0+: lowest - not valid if using ThreadX) |  |

| Transmit End Interrupt Priority           | Priority 3 (CM4: valid, CM0+: lowest - not valid if using ThreadX) |  |

| Error Interrupt Priority                  | Priority 3 (CM4: valid, CM0+: lowest - not valid if using ThreadX) |  |

Figure 44 - Temperature Sensor I2C Configuration Example

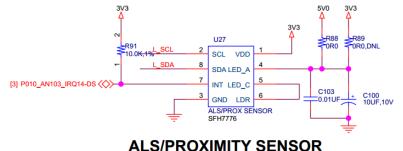

#### 7.9 Ambient Light / Proximity Sensor

The SYG-70CP-BA/SYG-70CR-BA features a SFH7776 Ambient Light & Proximity Sensor that allows for easy control of the LCD Backlight by sensing the amount of ambient light around the LCD display. The Ambient Light Sensor also features a proximity detection sensor.

The Proximity sensor delivers output values within the range of 0 up to 4095 (12 bit, linear).

The Ambient Light Sensor delivers output values in the range from 0 to 65545 (16 bit). The range of the ambient light sensor sensitivity can be set by the user and covers more than 4 ½ decades in each setting. Two threshold levels for the ambient light sensor can be set via the I2C bus, an upper and lower threshold.

The ALS/Prox sensor is connected to the MCU via I2C as well as an interrupt signal, allowing for MCU interrupts to occur when thresholds are reached.

Note: The ALS/Proximity sensor was designed to be used as a supplement for LCD backlight control and placement of the sensor on the SYG-70CP-BA/SYG-70CR-BA may not be indicative of a final design placement. Special consideration should be used when considering the ALS/Proximity sensor in your design, especially if a housing or enclosure is used.

I2C 7-bit address = 0x011 1001b (0x39h)

Figure 45 - ALS/Proximity Sensor Schematic

| Default (BSP)                                                      |

|--------------------------------------------------------------------|

| Default (BSP)                                                      |

|                                                                    |

|                                                                    |

| g_i2c1                                                             |

| 0                                                                  |

| Standard                                                           |

| 0x39                                                               |

| 7-Bit                                                              |

| NULL                                                               |

| Priority 3 (CM4: valid, CM0+: lowest - not valid if using ThreadX) |

| Priority 3 (CM4: valid, CM0+: lowest - not valid if using ThreadX) |

| Priority 3 (CM4: valid, CM0+: lowest - not valid if using ThreadX) |

| Priority 3 (CM4: valid, CM0+: lowest - not valid if using ThreadX) |

|                                                                    |

Figure 46 - ALS/Proximity Sensor Synergy Configuration

**FDI** Copyright ©2017, Future Designs, Inc

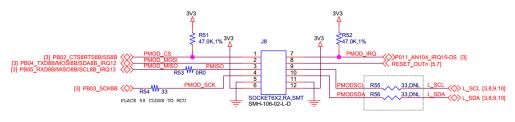

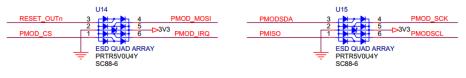

# 7.10 PMOD Type 2A Connector with SPI and optional I2C

A Pmod Type 2A Connector is available on the SYG-70CP-BA/SYG-70CR-BA. This 12 pin connector features SPI signals connected to the MCU, and has a load option available to connect I2C devices via Pmod. This connector also features a Reset Out signal allowing for peripheral reset control and an IRQ signal to allow for MCU interrupts from the Pmod peripheral.

Pmod expansion connectors can be used with the large array of sensors and add-on modules available from many different suppliers. Some modules communicate via the I2C protocol, while others use SPI or UART. For details about the different Pmod specifications, see the Pmod specification manual (https://www.digilentinc.com/Pmods/Digilent-Pmod %20Interface Specification.pdf). More information about the Pmod Standard can also be

Pmod\_%20Interface\_Specification.pdf) . More information about the Pmod Standard can also be found here (https://reference.digilentinc.com/reference/pmod/specification).

The Pmod connector includes ESD Protection as well to ensure the SYG-70CP-BA/SYG-70CR-BA remains safe from any potential ESD.

Pmod CONNECTOR (TYPE 2A) RIGHT ANGLE SMT Figure 47 - Pmod Type 2A Connector Schematic

#### Pmod ESD PROTECTION

Figure 48 - Pmod Connector ESD Protection Schematic

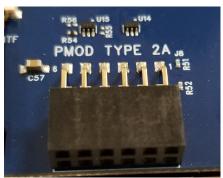

Figure 49 - Pmod Type 2A Connector

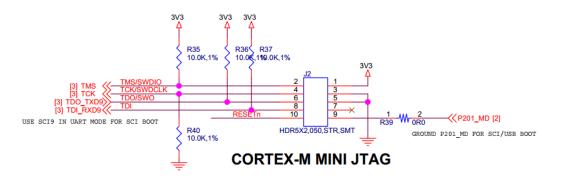

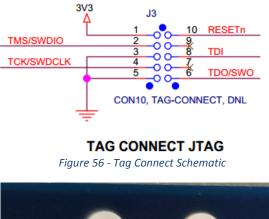

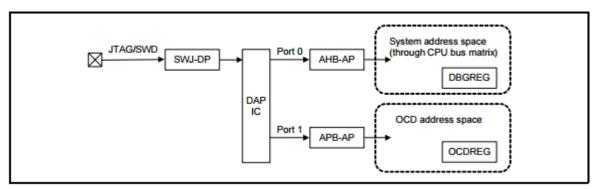

### 7.11 Cortex-M 9-pin JTAG Debug Connector

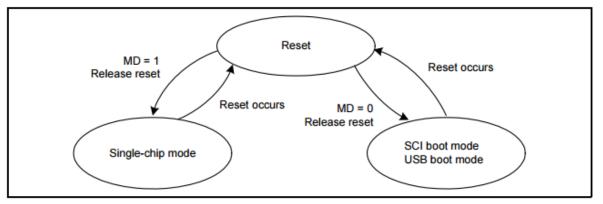

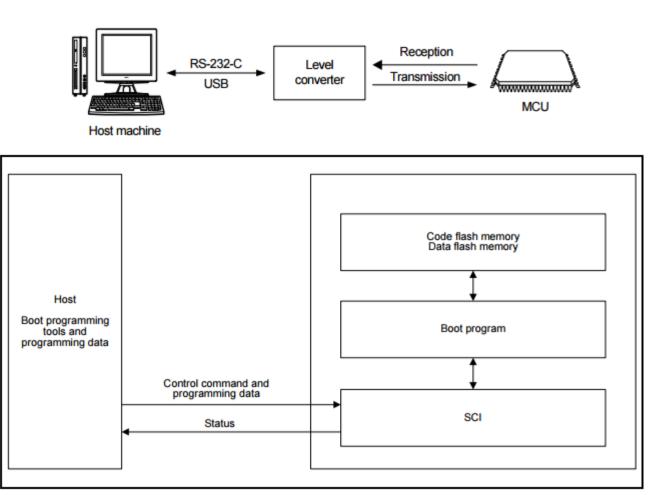

The Cortex-M 9-pin JTAG Debug Connector (J2) included on the SYG-70CP-BA/SYG-70CR-BA allows for JTAG and Single Wire Debugging (SWD) through the IDE of your choice. This connector includes a Reset signal (active LOW) for MCU resets, and can be configured to allow for SCI Boot mode for the S7G2 MCU.

This smaller connector provides 100% of the functionality of the standard 20-pin JTAG connector, but utilizes 70% less board space.

| Pin Number | Description | Pin Number | Description |

|------------|-------------|------------|-------------|

| 1          | VCC         | 6          | TDO         |

| 2          | TMS         | 7          | Х           |

| 3          | GND         | 8          | TDI         |

| 4          | TCK         | 9          | GND         |

| 5          | GND         | 10         | RST#        |

Pin 7 on the JTAG Debug Connector is keyed to ensure correct connector orientation.

Kits come with the SEGGER J-Link Lite Cortex-M shown below. With the J-Link Lite no adapter is required.

Figure 50 - Segger J-Link Lite Cortex M 10-pin Adapter

| VTref |     |    |    | SWDIO/TMS |

|-------|-----|----|----|-----------|

| GND   | _ з | •• | 4  | SWCLK/TCK |

| GND   | 5   | •• | 6  | SWO/TDO   |

|       | 7   |    | 8  | TDI       |

| NC    | 9   | •• | 10 | nRESET    |

|       |     |    |    |           |

Figure 51- J-Link Lite 10 pin Schematic

SEGGER and OLIMEX both provide adapters to convert the standard 20-pin JTAG to the new ARM 9pin JTAG. The SEGGER adapter also allows for connecting TRST using a solder bridge if needed. These adapters have female pins, and are only compatible with 20-pin JTAG units that have male pins. Each of these adapters comes with the required cable.

SEGGER 9-pin adapter - http://www.SEGGER.com/jlink-adapters.html#CM\_9pin OLIMEX 9-pin adapter - https://www.olimex.com/Products/ARM/JTAG/ARM-JTAG-20-10/

Figure 52 - J-Link Lite Cortex-M Schematic

| Module name:<br>Usage: |   | DEBUG0<br>When switching between modes, | first disable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------|---|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation Mode:        |   | JTAG                                    | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Input/Output           |   |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |