# **Data Sheet** HSCDHD005A

□ Electronic Compass function □Accelerometer function

Phone+81 3-3726-1211 FAX+81 3-3728-1741 Nagaoka Plant 1-3-5, Higashitakamimachi, Nagaoka-city, Niigata-pref.940-0006, JAPAN Phone+81 258-24-4111 FAX+81 258-24-4110

This specification is subject to change without notice.

### **HSCDHD005A**

2 / 46 Rev.1.5 Sep. 2016

#### 1. OVERVIEW

HSCDHD series is integrated digital output three axis terrestrial magnetism sensor and three axis acceleration sensor in one package.

A high sensitivity magnetic sensor that detects the terrestrial magnetism element and a low-noise linear acceleration sensor that compensates tilt, detects motion input are mounted. It provides with the drive circuit, the signal processing circuit, and the serial interface.

The electronic compass function and the angular velocity calculate function are achieved by combining with our software.

#### 2. FEATURES

#### ☐Function:

- 3-Axis magnetic sensor has magnetic field full-scale of ±2.4mT, 0.15µT/LSB resolution.

- 3-Axis acceleration sensor has  $\pm 2$ ,  $\pm 4$ ,  $\pm 8$ ,  $\pm 12$ ,  $\pm 16$ g ranges and 8, 10 or 14bit resolution.

- Digital Output, X, Y, Z axis magnetic field strength and X, Y, Z axis acceleration.

- I2C Serial interface

6-axis sensor acts as two slave devices that are a magnetometer and a accelerometer. Magnetic sensor has I2C slave interface (SS, FS, FS+, HS) PhilipsI2C revision .2.1 and NXP UM10204 I2C-bus specification and user manual Rev.03-19 June 2007 is supported. Acceleration sensor has I2C(SS,FS).

- Magnetic Function

- Initialization Function (Power on reset)Functional Mode Stand-by Mode

Active Mode

- Measurement Force State

Normal State (Data Rate 0.5,10,20,100Hz Selectable)

- Temperature Compensation Function

- Offset Calibration Function

- Offset Drift Function

- Self Test Function

- Acceleration Function

- Tap Detection

| ☐ Operating temperatures:                | -40 to +85°C                       |

|------------------------------------------|------------------------------------|

| ☐ Operating supply voltage: - VDD        | 1.7 to 3.6 V                       |

| ☐ Package: - Package type - Package size | 12 pin, LGA<br>2mm x 2mm x t0.95mm |

| ☐ Lead free, RoHS instruction            | , Halogen free conformed           |

# HSCDHD005A

3 / 46 Rev.1.5 Sep. 2016

### 3. Table of Contents

|    | Overviews                                                | 2     |

|----|----------------------------------------------------------|-------|

|    | Features                                                 | 2     |

|    | Table of Contents                                        | 3-4   |

| 4. | Circuit Configrations                                    | 5     |

|    | 4.1. Block Daigram                                       | 5     |

|    | 4.2. Pin Assignment                                      | 6     |

|    | 4.3. Typical Application Circuit                         | 7     |

|    | 4.4. Package Directions                                  | 8     |

| 5. | Overall Characteristics                                  | 9     |

|    | 5.1. Absolute Maximum Ratings                            | 9     |

|    | 5.2. Recommended Operating Conditions                    | 9     |

|    | 5.3. Electrical Characteristics                          | 9     |

|    | 5.3.1. Magnetic Sensor Characteristics                   | 9     |

|    | 5.3.2. Acceleration Sensor Characteristics               | 10    |

|    | 5.3.3. I2C Electrical Characteristics                    | 10    |

| 6. | Magnetic Sensor Functional Specifications                | 11    |

|    | 6.1. Function List                                       | 11    |

|    | 6.1.1. Initialization                                    | 12    |

|    | 6.1.2. Selftest                                          | 12    |

|    | 6.1.3. Functional Modes                                  | 13    |

|    | 6.1.4. Data ready function                               | 14    |

|    | 6.1.5 Offset calibration function                        | 15    |

|    | 6.1.6. Offset drift function                             | 15    |

|    | 6.1.7. Temperature Measurement and Compensation Function | 15    |

|    | 6.1.8. Control Timing Specifications                     | 16-18 |

| 7. | Acceleration Sensor Functional Specifications            | 19    |

|    | 7.1. Function List                                       | 19    |

|    | 7.1.1. Functional Modes                                  | 20    |

|    | 7.1.2. Sensor Sampling                                   | 21    |

|    | 7.1.3. Offset and Gain Calibration                       | 21    |

|    | 7.1.4. TAP Detection                                     | 21    |

|    | 7.1.5. Interrupts                                        | 22    |

| 8. | I2C Interface                                            | 23    |

|    | 8.1. I2C Slave Interface                                 | 23    |

|    | 8.2. I2C Timing Characteristics                          | 23-24 |

|    | 8.3. I2C Protocol Format                                 | 25    |

| 9. | Magnetic Sensor Register Interface                       | 26    |

|    | 9.1. Register MAP                                        | 26    |

|    | 9.2. Self Test Response Register (STB)                   | 27    |

|    | 9.3. Information Registers                               | 27    |

|    | 9.4. Output Data Register (OUTX, OUTY, OUTZ)             | 28    |

|    | 9.5. Status Register (STAT)                              | 28    |

|    | 9.6. Control 1 Register (CTRL1)                          | 29    |

|    | 9.7. Control 2 Register (CTRL2)                          | 29    |

|    | 9.8. Control 3 Register (CTRL3)                          | 30    |

|    | 9.9. Control 4 Register (CTRL4)                          | 30    |

|    | 9.10. Offset Drift Value Register (OFFX, OFFY, OFFZ)     | 31    |

|    | 9.11. Temperature Data Register (TEMP)                   | 31    |

|    |                                                          |       |

# HSCDHD005A

4 / 46 Rev.1.5

Sep. 2016

### 3. Table of Contents

| 10. Acceleration Sensor Register Interface                                 | 32    |

|----------------------------------------------------------------------------|-------|

| 10.1. Register MAP                                                         | 32-33 |

| 10.2. Status Register (SR)                                                 | 34    |

| 10.3. Device Status Register (OPSTAT)                                      | 35    |

| 10.4. Interrupt Enable Register (INTEN)                                    | 36    |

| 10.5. MODE Register (MODE)                                                 | 37    |

| 10.6. Sample Rate and Tap Feature Register (SRTFR)                         | 38    |

| 10.7. Tap Control Register (TAPEN)                                         | 39    |

| 10.8. X, Y and Z Tap Duration and Threshold Registers (TTTRX,TTTRY, TTTRZ) | 40    |

| 10.9. X, Y, Z-Axis Acceleration Registers(XOUT_EX, YOUT_EX & ZOUT_EX)      | 41    |

| 10.10. Output Configuration Register (OUTCFG)                              | 41    |

| 10.11. X-Axis Offset Registers (XOFFL, XOFFH)                              | 42    |

| 10.12. Y-Axis Offset Registers (YOFFL, YOFFH)                              | 42    |

| 10.13. Z-Axis Offset Registers (ZOFFL, ZOFFH)                              | 42    |

| 10.14. X-Axis Gain Registers (XGAIN)                                       | 43    |

| 10.15. Y-Axis Gain Registers (YGAIN)                                       | 43    |

| 10.16. Z-Axis Gain Registers (ZGAIN)                                       | 43    |

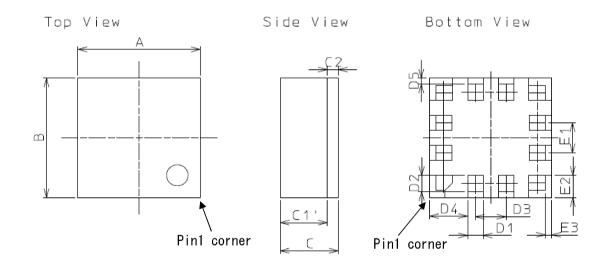

| 11. Package Dimensions                                                     | 44    |

| 12. Asking that exports this product                                       | 45    |

| 13. History of revision                                                    | 46    |

### HSCDHD005A

5 / 46 Rev.1.5 Sep. 2016

### 4. Circuit Configrations

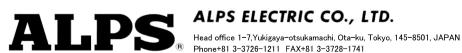

#### 4.1. Block Daigram

# HSCDHD005A

6 / 46 Rev.1.5 Sep. 2016

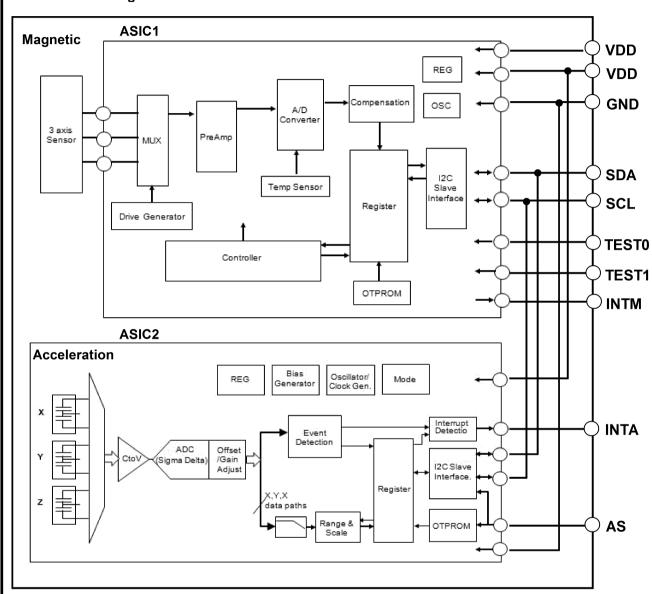

### 4.2. Pin Assignment

| Pin | Symbol | Туре                                | Description                                                                        | Connect Pin |

|-----|--------|-------------------------------------|------------------------------------------------------------------------------------|-------------|

| 1   | AS     | Input, CMOS                         | Accel I2C Address Select and Factory Program(VPPA)                                 | VDD/GND     |

| 2   | SDA    | Input / Output<br>CMOS / Open drain | Control data input/output pin. <sup>1</sup>                                        | SDA         |

| 3   | VDD    | Power                               | Power supply pin.                                                                  | VDD         |

| 4   | NC     | -                                   | Not Internally Connected                                                           | NC/VDD/GND  |

| 5   | INTA   | Output, CMOS                        | Accel Interrupt Active Low and Factory Test <sup>2</sup>                           | INT/NC      |

| 6   | INTM   | Output, CMOS                        | Data ready signal for geomagnetic sensor The active is selectable with LOW or HIGH | INT/NC      |

| 7   | VDD    | Power                               | Power supply pin.                                                                  | VDD         |

| 8   | TEST0  | Input, CMOS                         | Magnetometer Factory Test <sup>3</sup>                                             | NC/GND      |

| 9   | GND    | Power                               | Ground pin.                                                                        | GND         |

| 10  | TEST1  | Input, CMOS                         | Magnetometer Factory Program <sup>3</sup>                                          | NC/VDD/GND  |

| 11  | NC     | -                                   | Not Internally Connected                                                           | NC/VDD/GND  |

| 12  | SCL    | Input, CMOS<br>CMOS / Open drain    | Control data clock <sup>1</sup>                                                    | SCL         |

Notes

- 1) I2C pin requires a pull-up resistor, typically  $4.7k\Omega$  to DVDD.

- 2) Output mode is programable to open-drain output or push-pull output (MODE: Register). If set to open-drain, then it requires a pull-up resistor, typically  $4.7k\Omega$  to DVDD.

- 3) Test pin uses only the Manufacturing test.

# HSCDHD005A

7 / 46 Rev.1.5 Sep. 2016

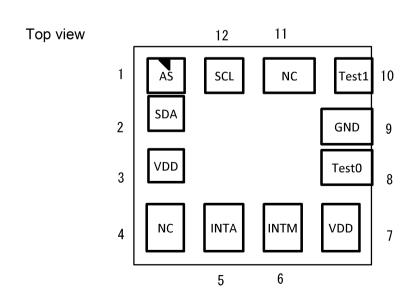

### 4.3. Typical Application Circuit

### Connection ie at I2C Interface

#### Notes

- Capaciter recommendation : C1, C2 = 100nF (0.1µ F)

- Resistors recommendation : Rp = 4.7Kohm

# HSCDHD005A

8 / 46 Rev.1.5 Sep. 2016

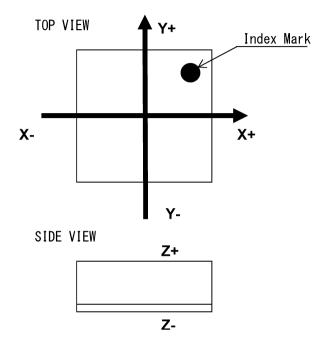

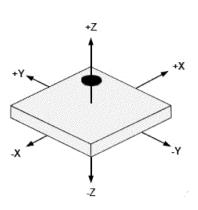

### 4.4. Package Directions

- X, Y, Z presents measurement directions of 3 axis sensor.

- Magnetic sensor output value of each axis is positive when turned toward magnetic north.

### **Direction of sensing axes**

Direction of

Earth gravity

Acceleration

Magnetic field

Xout= 0g, 0uT Yout= -1g, -|B|uT Zout= 0g, 0uT TILT= LEFT

Xout= +1g, +|B|uT Yout= 0g, 0uT Zout= 0g, 0uT TILT= UP

Xout= -1g, -|B|uT Yout= 0g, 0uT Zout= 0g, 0uT TILT= DOWN

Xout= 0g, 0uT Yout= +1g, +|B|uT Zout= 0g, 0uT TILT= RIGHT

Xout= 0g, 0uT Yout= 0g, 0uT Zout= +1g, +|B|uT TILT= FRONT

Xout= 0g, 0uT Yout= 0g, 0uT Zout= -1g, -|B|uT TILT= BACK

### HSCDHD005A

9 / 46 Rev.1.5 Sep. 2016

#### 5. Overall Characteristics

5.1. Absolute Maximum Ratings

| Characteristics                        | Symbol | Min. | Тур. | Max.   | Unit         |

|----------------------------------------|--------|------|------|--------|--------------|

| Supply Voltage                         | VDD    | -0.3 | -    | +3.6   | V            |

| Input Voltage                          | VIN    | -0.3 | -    | +3.6   | V            |

| Acceleration, any axis, duration 100us | gmax   | -    | -    | 10,000 | g            |

| Strage Temperature                     | Tstg   | -40  | -    | +125   | $^{\circ}$ C |

### 5.2. Recommended Operating Conditions

Unless otherwise specified: VDD = 2.8V, Ta = 25°C

| Characteristics                | Symbol | Min. | Тур. | Max. | Unit |

|--------------------------------|--------|------|------|------|------|

| Supply Voltage                 | VDD    | 1.7  | 2.8  | 3.6  | V    |

| Operating Temperature          | Та     | -40  | -    | +85  | °C   |

| External capacitance : VDD-GND | -      | -    | 100  | 470  | nF   |

| Pull-up Resistor for SDA, SCL  | -      | -    | 4.7  | -    | KOhm |

Note: Pin 3 and Pin 7 must be supplied same voltage as VDD.

#### 5.3. Electrical Characteristics

### **5.3.1. Magnetic Sensor Characteristics**

Unless otherwise specified: VDD = 2.8V, Ta = 25°C

| Characteristics                         | Symbol | Min. | Тур.  | Max. | Unit   |

|-----------------------------------------|--------|------|-------|------|--------|

| Measurement Range (x, y, z) 4           | Brg    | -2.4 | -     | +2.4 | mT     |

| Measurement Nonlinearity (±1.2mT)       |        | -2   | -     | +2   | %FS    |

| Measurement Sensitivity                 |        | -    | 0.150 | -    | μT/LSB |

| Supply Current Consumption (Total)      |        |      |       |      |        |

| Stand-by Mode                           | IDD    | -    | 3     | 10   | μΑ     |

| Active Mode, Average (ODR = 10Hz)       | IDD    | -    | 60    | 85   | μA     |

| Active Mode, Maximum                    | IDD    | -    | 2.5   | 3    | mA     |

| Output Data Rate (Normal State) 4       | ODR    | 0.5  | -     | 100  | Hz     |

| Output Resolution 4                     |        | -    | -     | 15   | bit    |

| Measurement Time 4                      |        | -    | -     | 5    | msec   |

| Control Timing <sup>4</sup>             |        |      |       |      |        |

| Turn On Time (Off to Stand-by Mode)     |        | -    | -     | 3    | msec   |

| Turn On Time (Stand-by to Active Mode)  |        | -    | -     | 5    | µsec   |

| Turn Off Time (Active to Stand-by Mode) |        | -    | -     | 5    | µsec   |

Note 4) Values are based on device characterization, not tested in production.

# HSCDHD005A

10 / 46 Rev.1.5 Sep. 2016

### 5.3.2. Acceleration Sensor Characteristics

Unless otherwise specified: VDD = 2.8V, Ta = 25°C

| Characteristics                                                                                                         | Symbol     | Min. | Тур.                         | Max. | Unit     |

|-------------------------------------------------------------------------------------------------------------------------|------------|------|------------------------------|------|----------|

| Measurement Range *Resolution and range set in OUTCFG: Output Configuration Register                                    |            |      | ±2<br>±4<br>±8<br>±12<br>±16 |      | g        |

| Measurement Sensitivity  *Depends on settings in OUTCFG: Output                                                         |            | 16   |                              | 4096 | LSB/g    |

| Output Data Rate  *Depends on settings in SRTFR: Sample Rate and Tap Feature                                            | ODR        | 0.25 | -                            | 256  | Hz       |

| Supply Current Consumption (Total) <sup>5</sup> Stand-by Mode Wake Mode (ODR = 128Hz) (highly dependent on sample rate) | IDD<br>IDD | -    | 4<br>85                      | -    | μA<br>μA |

| Sensitivity Temperature Drift <sup>5</sup> -40≦Ta≦+85°C                                                                 | TCSg       | -    | ±0.025                       | -    | %/°C     |

| Zero-g Offset <sup>5</sup>                                                                                              | OFF0g      | -    | ±40                          | -    | mg       |

| Zero-g Offset Temperature Drift <sup>5</sup> -40≦Ta≦+85°C                                                               | TCOg       | -    | ±1                           | -    | mg/°C    |

| Noise Density <sup>5</sup>                                                                                              | Nrms       | -    | 200                          | -    | µg/√Hz   |

| Nonlinearity <sup>5</sup>                                                                                               |            | -    | ±0.5                         | -    | %FS      |

| Cross-axis Sensitivity 5 Between any two axes                                                                           |            | -    | 2                            | -    | %        |

Note 5) Values are based on device characterization, not tested in production.

### 5.3.3. I2C Electrical Characteristics

Unless otherwise specified: VDD = 2.8V, Ta = 25°C

| Characteristics                  | Symbol | Min.       | Тур. | Max.       | Unit |

|----------------------------------|--------|------------|------|------------|------|

| Input Voltage High               | VIH    | 0.8 x DVDD | -    | DVDD       | V    |

| Low                              | VIL    | 0          | -    | 0.2 x DVDD | V    |

| Output Voltage High              | VOH    | 0.9 x DVDD | -    | DVDD       | V    |

| Low Iol ≦1mA                     | VOL    | 0          | -    | 0.1 x DVDD | V    |

| Output Voltage pin INT, Iol ≦2mA | VOH    | 0          | -    | 0.9 x DVDD | V    |

|                                  | VOL    | 0          | -    | 0.4        | V    |

| Capacitance, pin SDA and SCL     | Ci     | -          | -    | 10         | рF   |

# HSCDHD005A

11 / 46 Rev.1.5 Sep. 2016

# 6. Magnetic Sensor Functional Specifications

### 6.1. Function List

| Name Description      |                 | Description                                                                    |  |  |  |

|-----------------------|-----------------|--------------------------------------------------------------------------------|--|--|--|

| Initialization        |                 | Power on reset is performed by turning on the power.                           |  |  |  |

|                       |                 | All circuits and registers are set to default and mode is                      |  |  |  |

|                       |                 | set to stand-by mode automatically by POR.                                     |  |  |  |

|                       |                 | Software reset is performed by writing to control register.                    |  |  |  |

|                       |                 | All register is reloaded form OTP and internal compensation table is reloaded. |  |  |  |

| Self Test             |                 | Self test confirm the operation on sensor by register command                  |  |  |  |

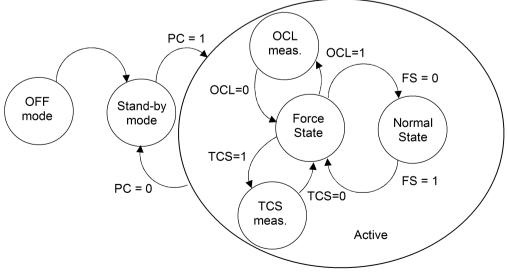

| Functional M          | Modes           | This sensor has stand-by mode and active mode for power control.               |  |  |  |

|                       |                 | There are two states in active mode.                                           |  |  |  |

| Off m                 | node            | The sensor is not active when AVDD and/or DVDD_IO are disable.                 |  |  |  |

| Stand                 | d-by Mode       | Low power waiting state. Stand-by mode can access to register.                 |  |  |  |

|                       |                 | Reading/Writing register is enable on stand-by mode.                           |  |  |  |

| Active                | e Mode          | Change from stand-by to active mode by register command                        |  |  |  |

|                       |                 | to control register.                                                           |  |  |  |

|                       | Force State     | Start to measure and output data by register command.                          |  |  |  |

|                       |                 | Force state is default.                                                        |  |  |  |

|                       | Normal State    | Perform to measure and output data by using the internal                       |  |  |  |

|                       |                 | timer trigger.                                                                 |  |  |  |

| Data Ready            | Function        | Informs when new measured results are updated.                                 |  |  |  |

|                       |                 | It is possible that data ready inform the signal to the INTM pin when          |  |  |  |

|                       |                 | updated output data.                                                           |  |  |  |

| Offset Calibr         | ration Function | Sensor offset can be canceled by using internal ADC circuit and digital        |  |  |  |

|                       |                 | compensation function when the register command is set.                        |  |  |  |

| Offset Drift Function |                 | When magnetic field strength have offset drift, output data values can be      |  |  |  |

|                       |                 | compensated by writing in the offset value registers.                          |  |  |  |

| Temperature           | e Measurement   | Retrieve temperature data from internal temperature sensor.                    |  |  |  |

| Function              |                 | Temperature data is used for internal compensation for output data.            |  |  |  |

| Temperature           | e Compensation  | Compensate gain in digital circuit by temperature measurement results.         |  |  |  |

| Function              |                 |                                                                                |  |  |  |

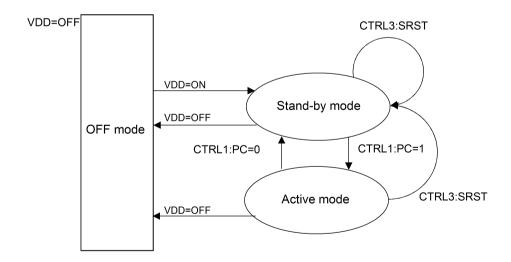

State Machine

### 6.1.1. Initialization

- All internal circuits and all register values are initialized with POR (Power On Reset) after power-on.

- After initialization, the functional mode move to standby mode automatically.

- The software reset set by the register command SRST=1 makes all register value to defaults and reload the compensation values for internal sensor calculation.

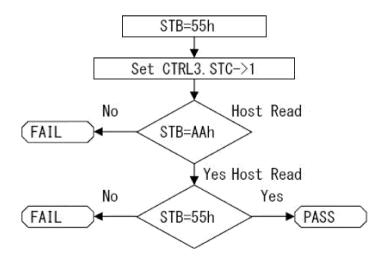

#### 6.1.2. Selftest

- -Selftest can be used to confirm with the inner I/F and the digital logic.

- -Selftest is performed with reading the STB register and setting the register command CTRL3 STC bit to Hi.

- -The following chart show the procedure of selftest .

- -The value of response register STB is back to 55h after reading it.

The flow chart of selftest

#### 6.1.3. Functional Modes

#### **OFF** mode

- -The sensor is not active when VDD are disable.

- -The following table show the each status of off mode.

| VDD          | Operation State                                                    |

|--------------|--------------------------------------------------------------------|

| 0V           | Sensor is not active, There are no inference on the interface bus. |

| 1.7V to 3.6V | Sensor is active, There are inference on the interface bus.        |

#### Stand-by mode

- -After loading the POR (Power On Reset), internal state is moved to the standby mode automatically.

- -Read and Write access function is limitative as follows at the stand-by mode.

- -Write: (CTRL3) FORCE, TCS and STC are disable

- -Read: All resister can be read.

- -Register is cannged form the Active mode to the Stand-by mode by set PC=0(CNTL1) as follows.

#### **Active mode**

- -At active mode, each function can be performed by setting control register 3(CTRL3).

- -To transfer to active mode, it sets the PC=1(CTRL1).

- -There are two types of measurement state. One is periodical measurement "Normal state " controlled by inner timer. and the other is "Force state" controlled by register command form outside.

- -The measurement state is selectable with FS bit on control register 1(CTRL1)

- -The default of measurement state is the force state (FS=1) after POR or reset running.

The diagram on mode transfer

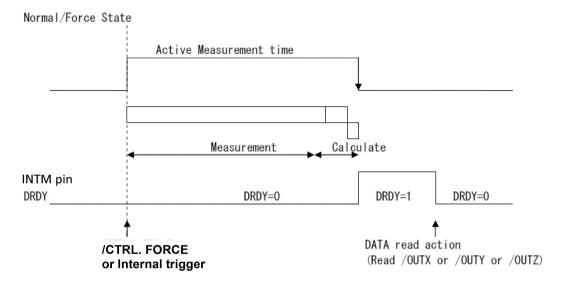

### 6.1.4. Data ready function

- -This function is used for notice that output data was updated.

- -Data ready output is enable on the outside terminal (INTM pin), when the data was updated.

- Information of data ready can be read with the status register (STAT).

- -DRDY is changed to LOW after reading data on the output register.

- Conditions of data ready function can be set on the control register (CTRL2).

Control function for Data Ready terminal with CTRL2 register

| CTRL2 bit | Bit Name | Default | Condition                        |

|-----------|----------|---------|----------------------------------|

| 3         | DEN      | 0       | Output control on INTM pin       |

|           |          |         | 0 = Disable                      |

|           |          |         | 1 = Enable                       |

| 2         | DRP      | 1       | The polarity setting on INTM pin |

|           |          |         | 0 = Active Low                   |

|           |          |         | 1 = Active High                  |

### **HSCDHD005A**

15 / 46 Rev.1.5 Sep. 2016

#### 6.1.5 Offset calibration function

- -This function is enable when the control register (CNTL3:OCL) was set to Hi during the Force State.

- -The offset value for inner ADC output is calculated with the measured sensor offset, and then set compensation values for the amplitude offset and also the digital offset automatically.

- -The OCL bit is changed to be low after updating the compensation offset value, and then the status is back to before measurement.

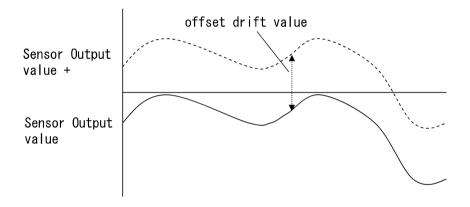

#### 6.1.6. Offset drift function

- -This function can make the digital compensation output that is add with values wrote by the host CPU on the offset drift register (OFFX,OFFY,OFFZ).

- -Offset drift values can be set with 15bit signed value.

#### 6.1.7. Temperature Measurement and Compensation Function

- The temperature measurement function will be executed when the register command TCS is set "1" during the Force State. After measurement, TCS bit change to "0" and back to before measurement.

- -The measurement result is wet on the temperature value register (TEMP).

- -Sensor output values are compensated with the temperature value register(TEMP)

# HSCDHD005A

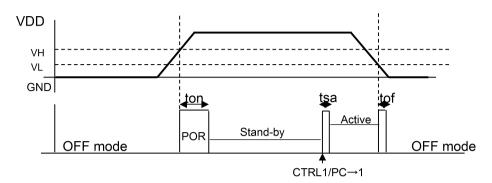

### 6.1.8. Control Timing Specifications

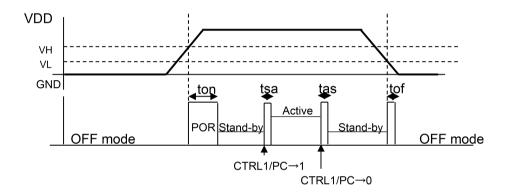

### **Power Supply Sequence**

Parameters on Supply voltage sequence (All Condition)

| Transition             | Symbol | Тур. | Max. | Unit |

|------------------------|--------|------|------|------|

| OFF→Stand-by           | ton    | ı    | 3    | ms   |

| Stand-by→Active        | tsa    | -    | 5    | μs   |

| Active→Stand-by        | tas    | -    | 5    | μs   |

| Active or Stand-by→OFF | tof    | -    | 10   | ms   |

Parameters on Supply voltage sequence (All Condition)

| T GIGINOTOTO ON OC | arametere en euppry vertage esquence (, in esmanten) |      |      |      |  |  |  |  |  |  |  |

|--------------------|------------------------------------------------------|------|------|------|--|--|--|--|--|--|--|

| Characteristics    | Symbol                                               | Min. | Max. | Unit |  |  |  |  |  |  |  |

| VDD ON             | VH                                                   | 1.53 | -    | V    |  |  |  |  |  |  |  |

| VDD OFF            | VL                                                   | -    | 0.17 | V    |  |  |  |  |  |  |  |

### **HSCDHD005A**

17 / 46 Rev.1.5 Sep. 2016

#### 6.1.8. Control Timing Specifications

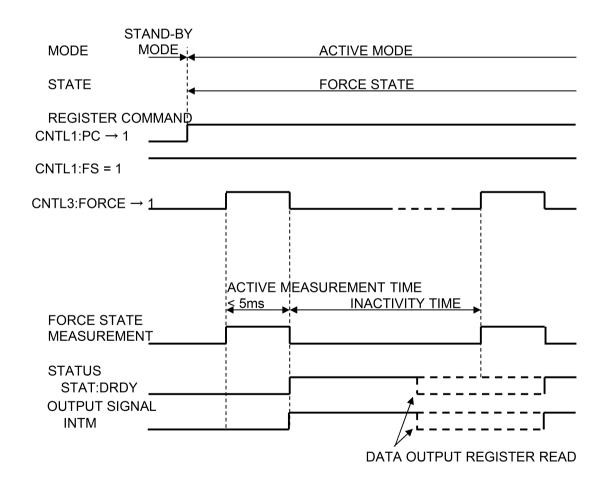

#### Force state

- Force state is used for synchronous measurement (selected from register CTRL3, bit FRC), and measurement starts after forced register command to register via bus.

- Functional mode changes from Stand-by mode to Active mode by setting register (Control1: bit PC) to "1".

- Force state is set by control register (CNTL1: bit FS) "1".

- Acquired data stored to output register (OUTX, OUTY, OUTZ), and status register (STAT: bit DRDY) is set to "1" and output signal (INTM pin) are set to active.

- -Output on external INTM pin is set by control register (CNTL2)

- -During reading data, out put register is not updating. After reading is complete, reading data is updated.

- Change of state from Normal to Force is valid after measurement if control register is set during the Active measuring in Normal state.

Measurement control timing (Force state)

#### 6.1.8. Control Timing Specifications

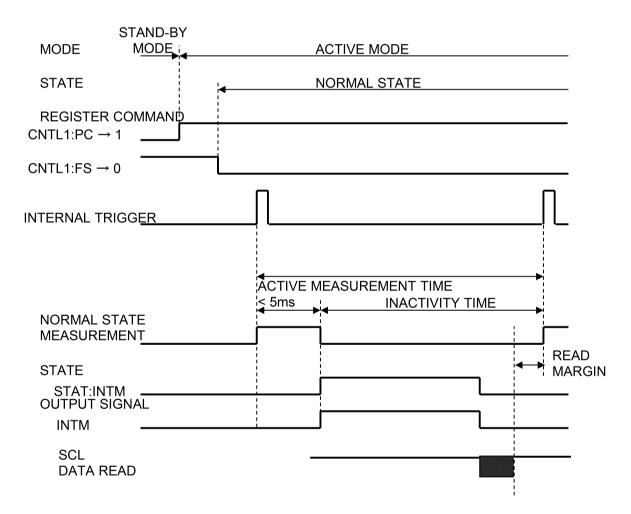

#### **Normal state**

- Normal state is continuous measurement state, and when Normal state is set by setting "0" to control register (CNTL1: bit FS), channels measurement is started.

- Measurement time and interval are managed with internal clock.

- Functional mode changes from Stand-by mode to Active mode by setting register (CNTL1: bit PC) to "1".

- Output data rate (ODR) is selectable with 0.5Hz or 100Hz by register (CNTL1: bit ODR).

- Acquired data are stored to register (OUTX, OUTY, OUTZ), status register (STAT: bit DRDY) is set to "1" and output PIN signal are control with (CNTL2:bit DEN).

Note: READ MARGIN is need more than "0msec" in normal state.

. DATA READ Time should be set less than 1msec including clock starch. Minimum case is happen in ODR=11(100Hz) on measurement function.

Measurement control timing (Normal state)

# **HSCDHD005A**

19 / 46 Rev.1.5 Sep. 2016

# 7. Acceleration Sensor Functional Specifications

### 7.1. Function List

|         | Name                   | Description                                                                        |  |  |  |  |  |

|---------|------------------------|------------------------------------------------------------------------------------|--|--|--|--|--|

| Initial | ization                | Power on reset is performed by turning on the power.                               |  |  |  |  |  |

|         |                        | All circuits and registers are set to default and mode is                          |  |  |  |  |  |

|         |                        | set to stand-by mode automatically by POR.                                         |  |  |  |  |  |

|         |                        | Software reset is performed by writing to control register.                        |  |  |  |  |  |

|         |                        | All register is reloaded form OTP and internal compensation table is reloaded.     |  |  |  |  |  |

| Func    | tional Modes           | This sensor has stand-by mode and wake mode for power control.                     |  |  |  |  |  |

|         | Stand-by Mode          | Low power waiting state. Stand-by mode is the default state after power-up.        |  |  |  |  |  |

|         |                        | Reading/Writing register and is enable, but interrupts cannot be serviced.         |  |  |  |  |  |

|         |                        | Internal clocking is disabled.                                                     |  |  |  |  |  |

|         |                        |                                                                                    |  |  |  |  |  |

|         | Wake Mode              | Change from stand-by to active mode by register command to control register.       |  |  |  |  |  |

|         |                        | Continuous sampling and reading data of sensor.                                    |  |  |  |  |  |

|         |                        | Only writing register is enable to the MODE: Register.                             |  |  |  |  |  |

|         |                        | Full read access is enable in all states.                                          |  |  |  |  |  |

| Sens    | or Sampling Function   | The internal sampling rate range can be selected between 0.25 Hz and 256 Hz.       |  |  |  |  |  |

|         |                        | The sensor readings data appear as selected resolution upto 14-bit.                |  |  |  |  |  |

| Offse   | t and Gain Calibration | Digital offset and gain calibration can be performed on the sensor, if necessary,  |  |  |  |  |  |

| Func    | tion                   | in order to reduce the effects of assembly influences and stresses                 |  |  |  |  |  |

|         |                        | which may cause the sensor readings to be offset from their factory values.        |  |  |  |  |  |

| Tap D   | etection Functon       | The tap detection allows the device to detect user events such as pressing         |  |  |  |  |  |

|         |                        | button on-screen.                                                                  |  |  |  |  |  |

| Interr  | upts Function          | The sensor device utilizes output pin INTA to signal to an external microprocessor |  |  |  |  |  |

|         |                        | that an event has been sensed.                                                     |  |  |  |  |  |

|         |                        | The event detections are TAP event and sensor update.                              |  |  |  |  |  |

# **HSCDHD005A**

20 / 46 Rev.1.5 Sep. 2016

#### 7.1.1. Functional Modes

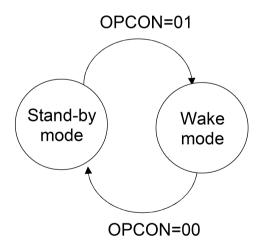

- -The device has two states of operation: STANDBY (the default state after power-up), and WAKE.

- -The STANDBY state offers the lowest power consumption.

- The I2C interface allows write access to all registers only in the STANDBY state.

- -In WAKE state, the only I2C register write access permitted is to the MODE: Mode Control Register. Full read access is allowed in all states.

| state   | I2C Bus                              | Description                                                                                                                                             |

|---------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| STANDBY | Device responds to I2C bus (R/W)     | •Device is powered; Registers can be accessed via I2C. Lowest power state. No interrupt generation, internal clocking disabled. Default power-on state. |

| WAKE    | Device responds to<br>I2C bus (Read) | •Continuous sampling and reading of sense data. All registers except the MODE: Register are read-only.                                                  |

#### **Accelerometer Operational State Flow**

-The operational state may be forced to a specific state by writing into the OPCON bits, as shown below.

-The operational state will stay in the mode specified until changed.

| The spectational state this state specifical artificial gear |                 |                                                                                                    |  |  |  |  |  |  |  |

|--------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| state                                                        | Set             | Description                                                                                        |  |  |  |  |  |  |  |

| Force Wake mode                                              | OPCON[1:0] = 01 | <ul><li>Switch to Wake mode and stay there</li><li>Continuous sampling data</li></ul>              |  |  |  |  |  |  |  |

| Force stand-by mode                                          | OPCON[1:0] = 00 | <ul><li>Switch to Stand-by mode and stay there</li><li>Disable sensor and event sampling</li></ul> |  |  |  |  |  |  |  |

State Machine

### **HSCDHD005A**

21 / 46 Rev.1.5 Sep. 2016

#### 7.1.2. Sensor Sampling

- -The sampling rate can be selected between 0.25 Hz and 256 Hz.

- -This register can be used to set the range and resolution of the accelerometer measurements.

- -Measurement data is stored in the "extended" registers XOUT\_EX, YOUT\_EX, and ZOUT\_EX.

- -The byte with the lower address of the byte pair is the least significant byte while the byte with the next higher address is the most significant byte.

- -The measurement data is represented as 2's complement format.

- For example, 10-bit samples occupy bits [9:0], with bits [15:9] occupied by the sign bit.

- 14-bit samples occupy bits [13:0], with bits [15:13] occupied by the sign bit.

- -The desired resolution and full scale acceleration range of  $\pm 2g$ ,  $\pm 4g$ ,  $\pm 8g$ ,  $\pm 12g$ ,  $\pm 16g$  are set in OUTCFG: Output Configuration Register.

- -The device sample rate is set in SRTFR(SAMPLE RATE AND TAP REGISTER).

#### 7.1.3. OFFSET AND GAIN CALIBRATION

-Digital offset and gain calibration can be performed on the sensor.

If necessary, in order to reduce the effects of post-assembly influences and stresses which may cause the sensor readings to be offset from their factory values.

#### 7.1.4. TAP DETECTION

- -The device supports directional tap detection in ±X, ±Y or ±Z.

- -Each axis is independent, although only one direction per axis is supported simultaneously.

- -The threshold, duration, and dead-time of tap detection can be set for each axis, and six flag/status bits are maintained in a status register.

- -The tap uses a second order high-pass filter to detect fast impulse/transition acceleration events.

- -The external interrupt pin can be used to indicate that a tap event has been detected.

### **HSCDHD005A**

22 / 46 Rev.1.5 Sep. 2016

#### 7.1.5. INTERRUPTS

- -The INTA pin is used in order to tell to an external microprocessor that the event occurred.

- If interrupts are used, the microprocessor must set up the registers due to detect a event.

- If polling is used, no need to setup the interrupt registers.

#### **Accelerometer Enabling and Clearing Interrupts**

- -The SR (Status Register) contains the flag bits for the sample acquisition interrupt ACQ\_INT.

- -The INTEN (Interrupt Enable Register) determines which events generate interrupts.

- When an event is detected, it is masked with an interrupt enable bit in this register and the corresponding status bit is set in the SR (Status Register).

- -The INTA pin is cleared during the next I2C bus cycle.

- -When an interrupt is triggered, the first I2C read access to the device clears INTA pin.

- The condition which generated the interrupt will remain held in the SR until it is read.

- -The polarity and the mode of INTA pin may be chosen by setting IPP and IAH bits in the MODE Register.

#### Accelerometer ACQ\_INT Interrupt

-The ACQ\_INT flag bit in the SR (Status Register) is always active. This bit is cleared when it is read. The frequency of this ACQ\_INT bit being set active is always the same as the sample rate.

#### **Accelerometer Continuous Sampling**

-The device has the ability to read in a continuous sampling mode.

The device always updates the XOUT, YOUT, and ZOUT registers at the chosen ODR. An optional interrupt can be generated each time the sample registers have been updated (ACQ\_INT interrupt bit in the INTEN).

### HSCDHD005A

23 / 46 Rev.1.5 Sep. 2016

#### 8. I2C Interface

#### 8.1. I2C Slave Interface

- Conformable to Philips I2C-Bus Specification Version 2.1 and NXP UM10204 I2C-bus specification and user manual Rev.03-19 June 2007

- Slave address of magnetic sensor is fixed '0001100'. (7bit device address 0x0C)

- Slave address of acceleration sensor are selectable with '1001100' and '1101100' (0x4C and 0x6C)

- The acceleration sensor I2C device address depends upon the state of the pin AS during power-up as shown in the table below.

| 7-bit Device ID     | 8-bit Address –<br>Write | 8-bit Address –<br>Read | Pin AS level<br>power-up |

|---------------------|--------------------------|-------------------------|--------------------------|

| 0x4C<br>(0b1001100) | 0x98                     | 0x99                    | GND                      |

| 0x6C<br>(0b1101100) | 0xD8                     | 0xD9                    | VDD                      |

### 8.2. I2C Timing Characteristics

- Acceleration sensor supports Standard mode and Fast mode.

- Magnetic sensor supports Standard mode, Fast mode , Fast mode Plus and Hi speed mode.

- It is seemless change from Fast mode to Hi speed mode to use the master code (00001XXX)

- Support Multiple Read and Write mode.

- Clock stretch function is not available.

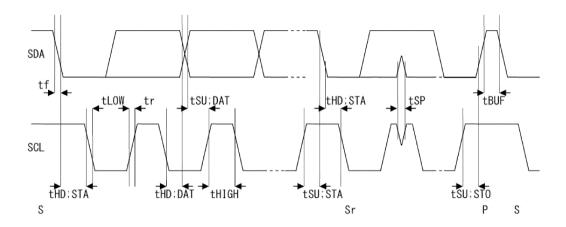

### I2C bus interface timing diagram 1

| Parameters                                       | Symbol              | Standa        | ard Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Fast m        | ode  | Fast m        | Fast mode Plus |     |

|--------------------------------------------------|---------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|---------------|----------------|-----|

|                                                  |                     | Min.          | Max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Min.          | Max. | Min.          | Max.           | 1   |

| SCL clock frequency                              | f <sub>SCL</sub>    | 0             | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0             | 400  | 0             | 1000           | kHz |

| Hold time (re)start condition                    | t <sub>HD:STA</sub> | 4. 0          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.6           | _    | 0. 26         | _              | us  |

| Low period of the SCL clock                      | t <sub>LOW</sub>    | 4. 7          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.3           | _    | 0.5           | -              | us  |

| High period of the SCL clock                     | t <sub>HIGH</sub>   | 4.0           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.6           | -    | 0. 26         | _              | us  |

| Set-up time for (re)start condition              | t <sub>su:sta</sub> | 4. 7          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.6           | -    | 0. 26         | _              | us  |

| Data hold time                                   | t <sub>HD:DAT</sub> | 0             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0             | -    | 0             | _              | us  |

| Data set-up time                                 | t <sub>su:dat</sub> | 250           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 100           | _    | 50            | _              | ns  |

| Rise time of SDA and SCL                         | t <sub>r</sub>      | T -           | 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _             | 300  | _             | 120            | ns  |

| Fall time of SDA and SCL                         | t <sub>f</sub>      | -             | 300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -             | 300  | _             | 120            | ns  |

| Set-up time for stop condition                   | t <sub>su:sto</sub> | 4. 0          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.6           | -    | 0. 26         | _              | us  |

| Bus free time between a stop and start condition | t <sub>BUF</sub>    | 4. 7          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.3           | -    | 0.5           | -              | us  |

| Capcacitive load for SDA/SCL                     | C <sub>b</sub>      | -             | 400                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -             | 400  | _             | 300            | pF  |

| Data valid time                                  | t <sub>VD:DAT</sub> | -             | 3. 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _             | 0.9  | _             | 0. 45          | us  |