# Data Sheet Five Output Universal PMIC

# **General Description**

The MxL7704-B is a five output Universal PMIC optimized for powering low power FPGAs, DSPs, and microprocessors from 5V inputs. Four synchronous step down buck regulators range from 1.5A system power to 4A core power.

A 100mA LDO provides a clean 3.3V power for auxiliary devices. All of the outputs support ±10% margining. The two highest power outputs also support dynamic voltage control which saves power in processors that can use this function. You can monitor an input voltage flag and PGOOD flags for each output through a 400kHz I<sup>2</sup>C interface. The I<sup>2</sup>C port can enable you to modify the power up and down sequencing options, assign PGOOD outputs to the PGOOD pins, enable outputs, and select switching frequency.

The high switching frequency and current mode architecture with internal compensation enable a very fast transient response to line and load changes without sacrificing stability and keeping board space to a minimum.

The MxL7704-B built-in one-time programmable (OTP) memory stores key startup configurations. It reduces the external components typically used to set output voltage and sequence of regulators. Regulator parameters are adjustable through high-speed I<sup>2</sup>C after the start up which offers flexibility for different system states.

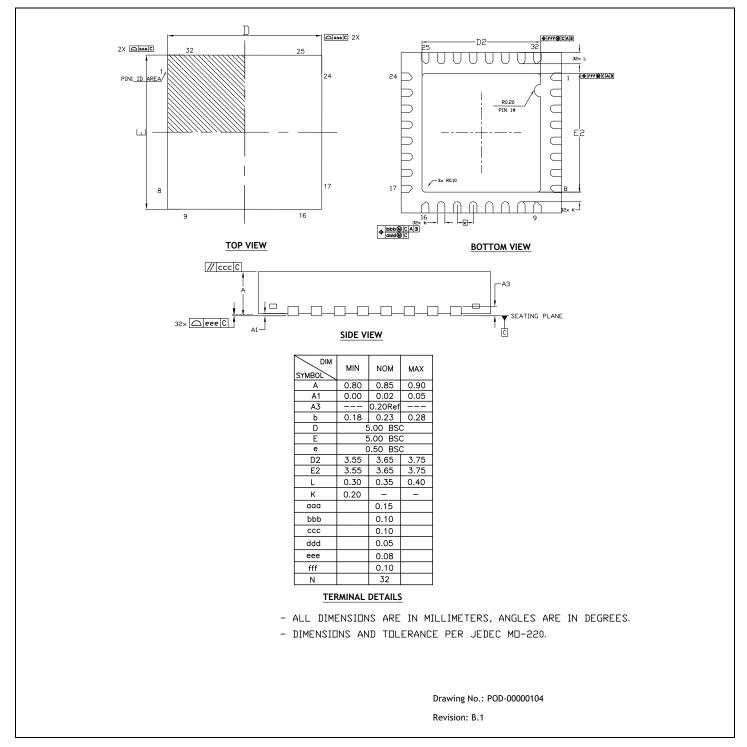

The fault protection features include input undervoltage lockout, overcurrent protection, and thermal protection. The MxL7704-B is offered in a 5mm x 5mm QFN package.

### **Features**

- Input voltage range from 4.0V to 5.5V

- Four synchronous buck regulators

- Internally compensated current mode

- From 1MHz to 2.1MHz switching frequency

- Buck 1: 3.0V-3.6V, 20mV step, 1.5A

- Buck 2: 1.3V-1.92V, 20mV step, 1.5A

- Buck 3: 0.8V-1.6V, 6.25mV step, 2.5A

- Buck 4: 0.6V-1.4V, 6.25mV step, 4A

- 100mA LDO 3.3V

- ±2% maximum total DC output error over line, load, and temperature

- 3.3V/5V 400kHz I<sup>2</sup>C interface

- Dynamic voltage scaling

- Status monitoring by channel

- Sequencing control

- Input voltage status register

- Highly flexible conditional sequencing engine with external input

- Two configurable PGOOD outputs

- Adjustable switching frequency

- 5mm x 5mm 32-pin QFN package

# **Applications**

- Low power processor, ASIC, and FPGA power

- Industrial control

- Test equipment

- POS terminals

For more information about the ordering information, see "Ordering Information" on page 32.

ii

# **Revision History**

| Document No.   | Release Date       | Change Description                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 200-7704BDSR02 | September 20, 2023 | Updated:                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                |                    | <ul> <li>"MxL7704-BQB" occurrences replaced with "MxL7704-B" throughout the document (except in "Ordering Information" table).</li> <li>In "Default Values" table:         <ul> <li>Default value of "0x17" address.</li> <li>Default value and value description of "0x19" address.</li> </ul> </li> <li>In "SEQ EN Assign and PG1 Routing (0x17)—Read/Write" table under "Register Descriptions" section, description of bit 5.</li> </ul> |

|                |                    | In "Fault Actions, Down Sequencing, Frequency (0x19)—Read/Write" table under<br>"Register Descriptions" section, description of bit 5. Added:                                                                                                                                                                                                                                                                                                |

|                |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                |                    | "Output Voltages Outside Ranges Guaranteed in Electrical Table" section. Removed:                                                                                                                                                                                                                                                                                                                                                            |

|                |                    | ■ In "Ordering Information" table, "MxL7704-B-EVB" obsolete part number.                                                                                                                                                                                                                                                                                                                                                                     |

| 200-7704BDSR01 | January 26, 2022   | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                             |

# **Table of Contents**

| General Description                                       | i  |

|-----------------------------------------------------------|----|

| Features                                                  | i  |

| Applications                                              | i  |

| MxL7704-B Specifications                                  | 1  |

| Absolute Maximum Ratings                                  | 1  |

| ESD Ratings                                               | 1  |

| Operating Conditions                                      | 1  |

| Electrical Characteristics                                | 2  |

| Pin Information                                           | 7  |

| Pin Configuration                                         | 7  |

| Pin Description                                           | 8  |

| Typical Performance Characteristics                       | 9  |

| Typical Performance Characteristics (Continued)           | 10 |

| Functional Block Diagram                                  | 11 |

| Applications Information                                  | 12 |

| Operation                                                 | 12 |

| Output Voltage Scaling                                    | 12 |

| Sequencing                                                | 13 |

| Power Down Sequencing of Channels                         | 13 |

| SEQ EN and Channel Enable Bits                            | 14 |

| Changing Sequencing Registers While Operating             | 15 |

| PGOOD                                                     | 15 |

| Input Voltage Monitor Flag                                | 15 |

| Hot Start                                                 | 15 |

| Faults                                                    | 16 |

| Under Voltage Protection (UVP)                            | 16 |

| Output Over Voltage Protection (OVP)                      | 16 |

| Over Current Protection (OCP)                             | 16 |

| Channel/Chip Fault Actions                                | 17 |

| Thermal Design                                            | 17 |

| Layout Guidelines                                         | 17 |

| I <sup>2</sup> C Operation                                | 18 |

| Minimum t <sub>ON</sub> and Minimum Duty Cycle Limitation | 18 |

| Buck 1 Operation at Low V <sub>IN</sub>                   | 19 |

iii

| Minimum Effective C <sub>OUT</sub>                            | 19 |

|---------------------------------------------------------------|----|

| Dynamic Voltage Scaling                                       | 20 |

| Output Voltages Outside Ranges Guaranteed in Electrical Table | 20 |

| Analog to Digital Converter and Temperature Sensor            | 22 |

| Typical Application                                           | 23 |

| Register Information                                          | 24 |

| Slave I <sup>2</sup> C Address                                | 24 |

| Register Map                                                  | 24 |

| Default Values                                                | 25 |

| Register Descriptions                                         | 26 |

| Mechanical Dimensions                                         | 30 |

| 5mm x 5mm 32-Pin QFN                                          | 30 |

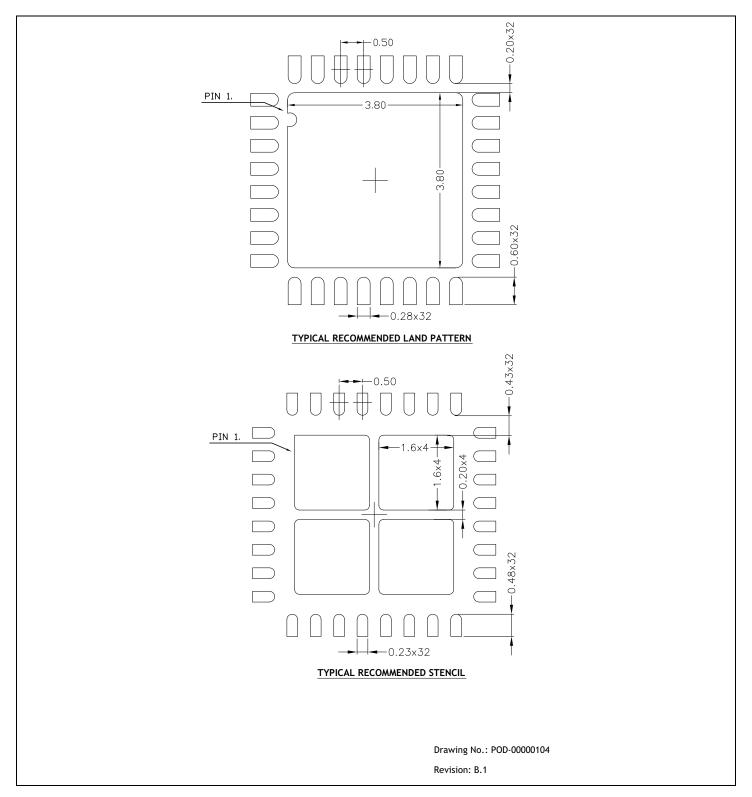

| Recommended Land Pattern and Stencil                          | 31 |

| 5mm x 5mm 32-Pin QFN                                          | 31 |

| Ordering Information                                          | 32 |

# List of Figures

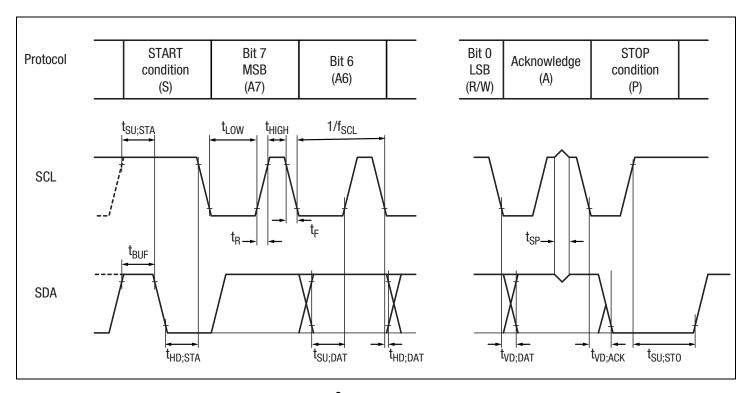

| Figure 1: I <sup>2</sup> C Bus Timing Diagram           | 6  |

|---------------------------------------------------------|----|

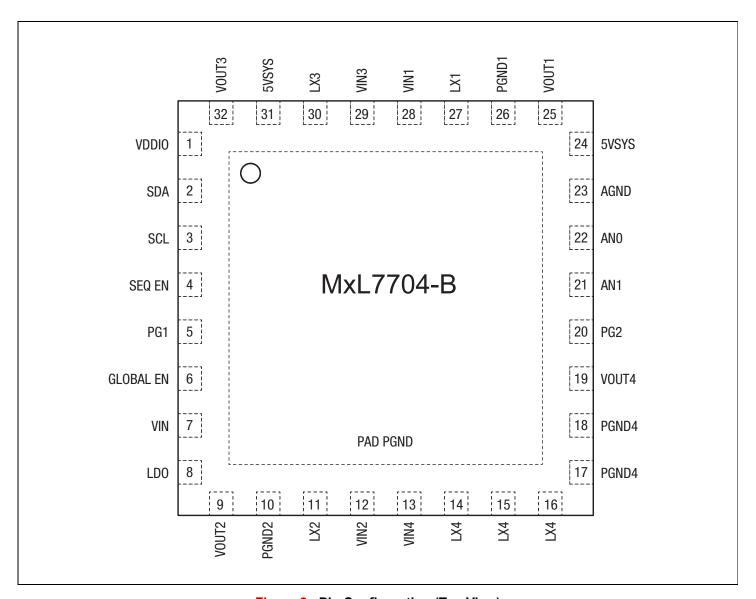

| Figure 2: Pin Configuration (Top View)                  | 7  |

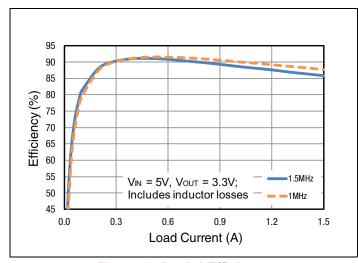

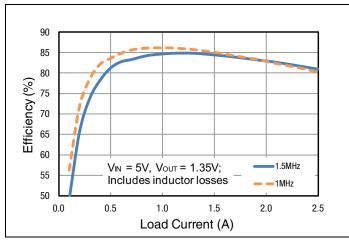

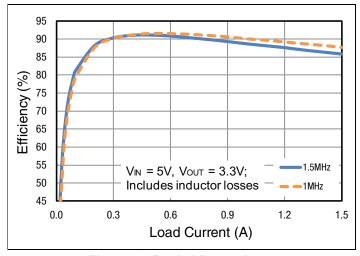

| Figure 3: Buck 1 Efficiency                             | 9  |

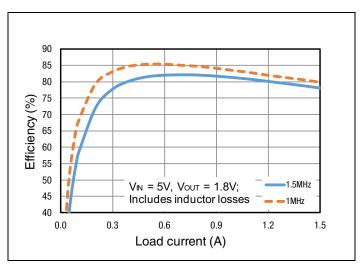

| Figure 4: Buck 2 Efficiency                             | 9  |

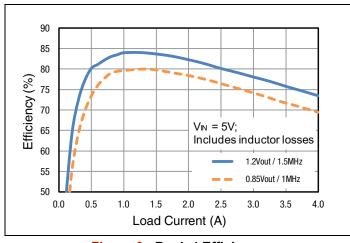

| Figure 5: Buck 3 Efficiency                             | 9  |

| Figure 6: Buck 4 Efficiency                             | 9  |

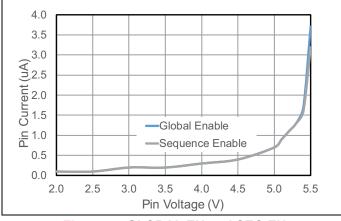

| Figure 7: GLOBAL EN and SEQ EN Input Current vs Voltage | 9  |

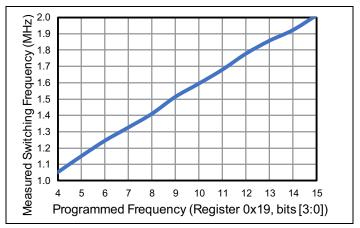

| Figure 8: Measured vs Programmed Frequency              | 9  |

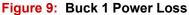

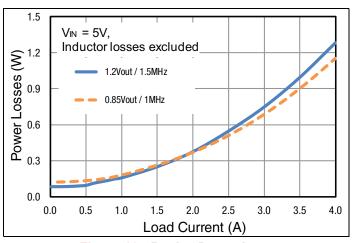

| Figure 9: Buck 1 Power Loss                             | 10 |

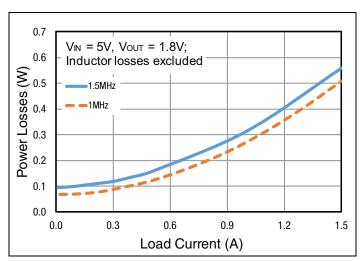

| Figure 10: Buck 2 Power Loss                            | 10 |

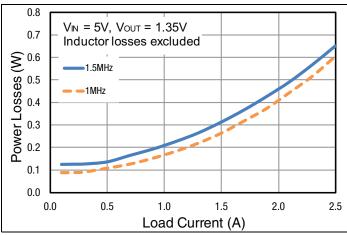

| Figure 11: Buck 3 Power Loss                            | 10 |

| Figure 12: Buck 4 Power Loss                            | 10 |

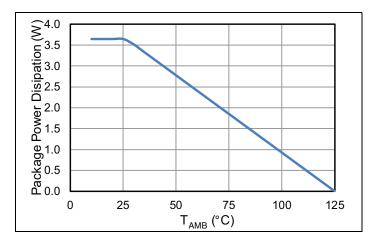

| Figure 13: Package Derating                             | 10 |

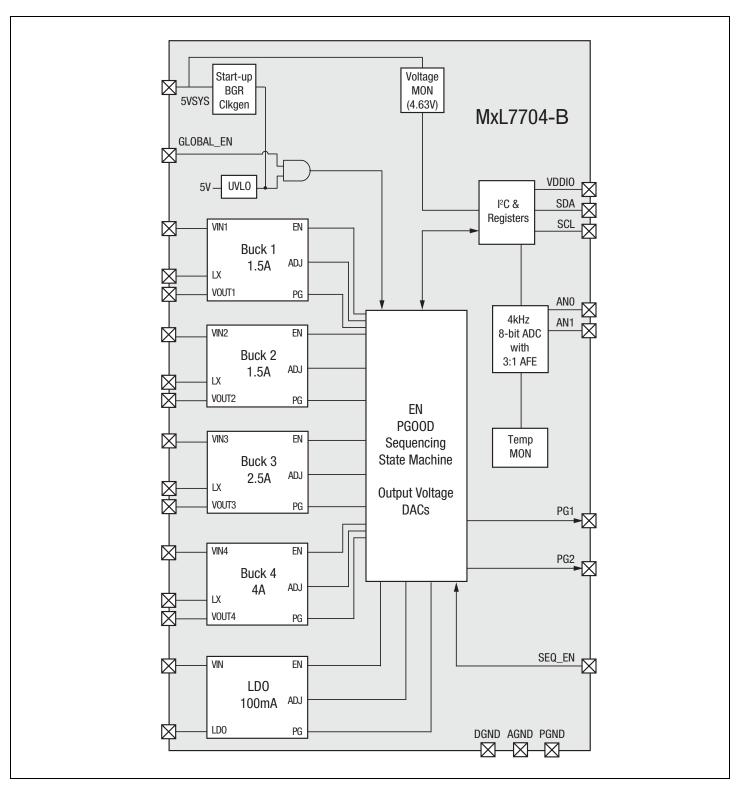

| Figure 14: Functional Block Diagram                     | 11 |

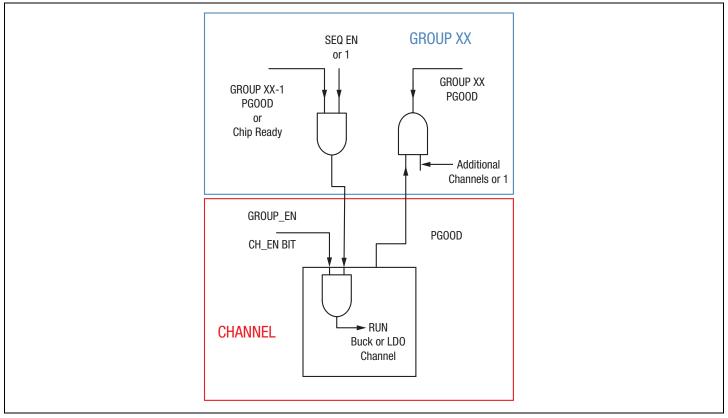

| Figure 15: Sequencing                                   | 14 |

| Figure 16: Power Good Timing                            | 16 |

| Figure 17: MxL7704-B Control Loop Architecture          | 21 |

| Figure 18: Damped Response without Ringing              | 21 |

| Figure 19: MxL7704-B Typical Application                | 23 |

| Figure 20: Mechanical Dimensions                        | 30 |

| Figure 21: Recommended Land Pattern and Stencil         | 31 |

# List of Tables

| Table 1: Absolute Maximum Ratings             | 1  |

|-----------------------------------------------|----|

| Table 2: ESD Ratings                          | 1  |

| Table 3: Operating Conditions                 | 1  |

| Table 4: Electrical Characteristics           | 2  |

| Table 5: Pin Names and Description            | 8  |

| Table 6: Minimum Permissible V <sub>OUT</sub> | 18 |

| Table 7: Recommended L and C <sub>OUT</sub>   | 19 |

| Table 8: Slave I <sup>2</sup> C Address       | 24 |

| Table 9: Register Map                         | 24 |

| Table 10: Default Values                      | 25 |

| Table 11: Ordering Information                | 32 |

# MxL7704-B Specifications

# **Absolute Maximum Ratings**

**Important:** The stresses above what is listed under Table 1 may cause permanent damage to the device. This is a stress rating only—functional operation of the device above what is listed under Table 1 or any other conditions beyond what MaxLinear recommends is not implied. Exposure to conditions above what is listed under Table 3 for extended periods of time may affect device reliability. Solder reflow profile is specified in the *IPC/JEDEC J-STD-020C* standard.

**Table 1: Absolute Maximum Ratings**

| Parameter                                                                                           | Minimum | Maximum                                | Units |

|-----------------------------------------------------------------------------------------------------|---------|----------------------------------------|-------|

| V <sub>IN</sub> , V <sub>IN1</sub> , V <sub>IN2</sub> , V <sub>IN3</sub> , V <sub>IN4</sub> , 5VSYS | -0.3    | 6                                      | V     |

| SDA, SCL, VDDIO                                                                                     | -0.3    | 6                                      | V     |

| ANO, AN1                                                                                            | -0.3    | 6                                      | V     |

| PG1, PG2, GLOBAL EN, SEQ EN                                                                         | -0.3    | 6                                      | V     |

| LDO                                                                                                 | -0.3    | 6                                      | V     |

| $V_{\text{OUT1}}, V_{\text{OUT2}}, V_{\text{OUT3}}, V_{\text{OUT4}}$                                | -0.3    | V <sub>INx</sub> - 0.3V <sup>(1)</sup> | V     |

| Storage Temperature Range                                                                           | -55     | 150                                    | °C    |

| Peak Package Body Temperature                                                                       | -       | 260                                    | °C    |

<sup>1.</sup> x = Buck number

### **ESD Ratings**

Table 2: ESD Ratings

| Parameter                  | Minimum | Maximum | Units |

|----------------------------|---------|---------|-------|

| Human body model (HBM)     | -       | 2.5     | kV    |

| Charged device model (CDM) | -       | 750     | V     |

# **Operating Conditions**

**Table 3: Operating Conditions**

| Parameter                                                                                           | Minimum | Maximum                               | Units |

|-----------------------------------------------------------------------------------------------------|---------|---------------------------------------|-------|

| V <sub>IN</sub> , V <sub>IN1</sub> , V <sub>IN2</sub> , V <sub>IN3</sub> , V <sub>IN4</sub> , 5VSYS | 4.0     | 5.5                                   | V     |

| SDA, SCL, VDDIO                                                                                     | 3.3     | 5.5                                   | V     |

| ANO, AN1                                                                                            | 0       | 3                                     | V     |

| PG1, PG2, GLOBAL EN, SEQ EN                                                                         | 0       | 5.5                                   | V     |

| LDO                                                                                                 | 0       | V <sub>IN</sub> - 0.3V <sup>(1)</sup> | V     |

| LX1, LX2, LX3, LX4                                                                                  | -1      | 5.5 <sup>(2)</sup>                    | V     |

| Switching frequency                                                                                 | 1000    | 2100                                  | kHz   |

| Junction temperature range (T <sub>J</sub> )                                                        | -40     | 125                                   | °C    |

| Package power dissipation max at 25°C                                                               | -       | 3.65                                  | W     |

| Package thermal resistance $\Theta_{JA}$                                                            | -       | 27                                    | °C/W  |

<sup>1.</sup> LDO set to 3.3V.

<sup>2.</sup> LX pin's DC range is -1V for less than 50ns.

### **Electrical Characteristics**

The specifications listed in this section only apply for operating junction temperature of  $T_J$  = 25°C only. The limits that apply to the full operating junction temperature range are denoted by a "•". The typical values represent the most common parametric norm at  $T_J$  = 25°C and are provided for reference purposes only unless otherwise indicated,  $V_{IN}$  = 5VSYS = 5.0V

**Table 4: Electrical Characteristics**

| Symbol                                     | Parameter                                   | Conditions                                                                     | • | Minimum              | Typical | Maximum | Units |

|--------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------|---|----------------------|---------|---------|-------|

| DC Specifications                          |                                             |                                                                                |   |                      |         |         |       |

| V <sub>IN</sub>                            | Input DC voltage                            | -                                                                              | • | 4.0                  | 5.0     | 5.5     | V     |

|                                            | Under voltage lockout                       | Rising                                                                         |   | -                    |         | 3.9     | V     |

| UVLO                                       | Under voltage lockout hysteresis            | Falling                                                                        |   | -                    | 210     | -       | mV    |

| I <sub>Q_SHUTDOWN</sub>                    | Shutdown quiescent current                  | GLOBAL EN = logic LOW. All outputs <20% of set point or initial power applied. |   | -                    | 10      | -       | μА    |

| I <sub>Q_OPERATING_5VS</sub><br>YS         | 5VSYS operating quiescent current           | GLOBAL EN = logic HIGH. All outputs in regulation no load. $f_{OSC} = 1.5MHz$  |   | -                    | 8       | -       | mA    |

| T <sub>SD</sub>                            | Thermal shutdown threshold                  | Temperature rising                                                             |   | -                    | 145     | -       | °C    |

| T <sub>SDH</sub>                           | Thermal shutdown hysteresis                 | Temperature falling                                                            |   | -                    | 20      | -       | °C    |

| Buck Regulators 1                          | - 4                                         |                                                                                | · |                      |         |         | •     |

| V <sub>IN</sub>                            | Operational voltage range                   | -                                                                              | • | 4.0                  | -       | 5.5     | V     |

| V <sub>OUT</sub> accuracy                  | Output voltage accuracy                     | Load current = 10mA to full load<br>V <sub>IN</sub> = 5VSYS = 4.0V-5.5V        | • | -2                   | -       | +2      | %     |

| V <sub>OUT</sub> initial<br>accuracy       | Output voltage accuracy                     | Load current = 10mA<br>V <sub>IN</sub> = 5VSYS = 4.5V-5.5V                     |   | -0.5                 | -       | +0.5    | %     |

| Buck 1 V <sub>OUT</sub>                    | Output voltage set point range              | 20mV resolution, 8 bit                                                         |   | 3.0                  | -       | 3.6     | V     |

| Buck 2 V <sub>OUT</sub>                    | Output voltage set point range              | 20mV resolution, 8 bit                                                         |   | 1.30                 | -       | 1.92    | V     |

| Buck 3 V <sub>OUT</sub> range              | Output voltage set point range              | 6.25mV resolution, 8 bit                                                       |   | 0.800 <sup>(1)</sup> | -       | 1.59375 | V     |

| Buck 4 V <sub>OUT</sub> range              | Output voltage set point range              | 6.25mV resolution, 8 bit                                                       |   | 0.600 <sup>(1)</sup> | -       | 1.39375 | V     |

| V <sub>OUT_DYN</sub>                       | Dynamic output slew rate                    | Closed loop controlled                                                         |   | -                    | 10      | -       | V/ms  |

| V <sub>OUT_SS</sub><br>V <sub>OUT_SO</sub> | soft-start slew rate and soft off slew rate | Closed loop controlled                                                         |   | -                    | 1       | -       | V/ms  |

| V <sub>OUT_DISCHARGE</sub>                 | Pre-bias discharge threshold                | Output falling                                                                 |   | -                    | 200     | -       | mV    |

| $R_{AD}$                                   | Output active discharge resistance          | Converter disabled and option selected                                         |   | -                    | 78      | -       | Ω     |

**Table 4: Electrical Characteristics (Continued)**

| Symbol                    | Parameter                                         | Conditions                                              | • | Minimum | Typical | Maximum | Units |

|---------------------------|---------------------------------------------------|---------------------------------------------------------|---|---------|---------|---------|-------|

|                           |                                                   | Buck 1                                                  | • | 1.5     | -       | -       | Α     |

|                           | Full load rated current                           | Buck 2                                                  | • | 1.5     | -       | -       | Α     |

| lout                      |                                                   | Buck 3                                                  | • | 2.5     | -       | -       | Α     |

|                           |                                                   | Buck 4                                                  | • | 4.0     | -       | -       | Α     |

|                           | Peak current limit                                | Buck 1                                                  | • | 2.5     | 3.4     | 4.5     | Α     |

| 1.                        | These current limits help define maximum inductor | Buck 2                                                  | • | 2.5     | 3.4     | 4.5     | Α     |

| I <sub>CLIM</sub>         | ripple and to protect the internal power switches | Buck 3                                                  | • | 3.5     | 4.5     | 5.5     | A     |

|                           | from an EOS event.                                | Buck 4                                                  | • | 5.5     | 6.5     | 9.0     | Α     |

| V <sub>UVP</sub>          | Under voltage protection (UVP) threshold          | soft-start completed, DVS inactive                      |   | -       | 70      | -       | %     |

|                           | UVP deglitch                                      |                                                         |   |         | 10      |         | μs    |

| f <sub>OSC_RANGE</sub>    | Switching frequency programmable range            | See Figure 8 on page 9                                  |   | 1000    | -       | 2000    | kHz   |

|                           | Oscillator accuracy                               | At 1.5MHz b1001                                         | • | -10     | -       | 10      | %     |

| t <sub>ON-MIN</sub>       | Minimum controllable on-<br>time                  | Full load                                               |   | -       | 92      | 120     | ns    |

|                           |                                                   | Buck 1                                                  |   | -       | 146     | -       | mΩ    |

| D (D)                     | Pin to pin resistance PFET                        | Buck 2                                                  |   | -       | 146     | -       | mΩ    |

| R <sub>DSON</sub> (P)     | High-side MOSFET                                  | Buck 3                                                  |   | -       | 67      | -       | mΩ    |

|                           |                                                   | Buck 4                                                  |   | -       | 60      | -       | mΩ    |

|                           | Pin to pin resistance<br>NFET<br>Low-side MOSFET  | Buck 1                                                  |   | -       | 103     | -       | mΩ    |

| R <sub>DSON</sub> (N)     |                                                   | Buck 2                                                  |   | -       | 103     | -       | mΩ    |

| · DSON (· ·)              |                                                   | Buck 3                                                  |   | -       | 32      | -       | mΩ    |

|                           |                                                   | Buck 4                                                  |   | -       | 27      | -       | mΩ    |

| Low Dropout Reg           | ulator, LDO                                       |                                                         |   |         | _       |         |       |

| $V_{IN}$                  | Operational voltage range                         | -                                                       | • | 4.0     | -       | 5.5     | V     |

| V <sub>OUT</sub> accuracy | Output voltage accuracy                           | Load current = 1mA-100mA<br>V <sub>IN</sub> = 4.0V-5.5V | • | -2      | -       | 2       | %     |

| V <sub>OUT</sub> default  | Default set point                                 |                                                         |   | -       | 3.3     | -       | V     |

| V <sub>OUT_DYN</sub>      | Dynamic output slew rate                          | Closed loop controlled, load = 25mA                     |   | -       | 10      | -       | V/ms  |

| V <sub>OUT_SS</sub>       | soft-start slew rate                              | Closed loop controlled                                  |   | -       | 1       | -       | V/ms  |

| I <sub>SC</sub>           | Short circuit current limit                       | 3v3LDO = 0V                                             | • | 120     | 230     | 260     | mA    |

| $V_{DO}$                  | Dropvout voltage                                  | Load current = 10mA                                     | • | -       | 11      | 30      | mV    |

|                           | (defined as a drop of 2% from initial value)      | Load current = 100mA                                    | • | -       | 210     | 300     | mV    |

**Table 4: Electrical Characteristics (Continued)**

| Symbol                  | Parameter                                       | Conditions                                                                   | • | Minimum | Typical | Maximum | Units |

|-------------------------|-------------------------------------------------|------------------------------------------------------------------------------|---|---------|---------|---------|-------|

|                         |                                                 | f = 1kHz, I <sub>OUT</sub> = 10mA,                                           |   | -       | 56      | -       | dB    |

| DODD                    | Power supply rejection                          | $V_{IN} = 4.3V, V_{OUT} = 3.3V$                                              |   |         |         |         |       |

| PSRR                    | ratio                                           | f = 10kHz, I <sub>OUT</sub> = 10mA,                                          |   | -       | 40      | -       | dB    |

|                         |                                                 | $V_{IN} = 4.3V, V_{OUT} = 3.3V$                                              |   |         |         |         |       |

| C <sub>OUT</sub>        | Output capacitor                                | Capacitance (effective capacitance)                                          |   | 0.68    | 1.0     | -       | μF    |

|                         | (ceramic)                                       | ESR                                                                          |   | 1       | -       | 100     | mΩ    |

| $\Theta_{N}$            | Supply output noise                             | $10Hz \le f \le 100kHz$ ,<br>V <sub>IN</sub> = 4.3V, V <sub>OUT</sub> = 3.3V |   | -       | 470     | -       | μVrms |

| R <sub>AD</sub>         | Output active discharge resistance              | Converter disabled and option selected                                       |   | -       | 78      | -       | Ω     |

| Power Good Ou           | ıtputs                                          |                                                                              | , | 1       |         |         |       |

|                         | Power good threshold                            | V <sub>OUT</sub> rising as a % of Vout                                       | • | 85      | 90      | 95      | %     |

|                         | Power good hysteresis<br>Buck 1 and LDO         | V <sub>OUT</sub> falling                                                     |   | -       | 122     | -       | mV    |

|                         | Power good hysteresis<br>Buck 3 and Buck 4      | V <sub>OUT</sub> falling                                                     |   | -       | 38      | -       | mV    |

|                         | Power good hysteresis<br>Buck 2                 | V <sub>OUT</sub> falling                                                     |   | -       | 67      | -       | mV    |

|                         | Power good assertion delay, FB rising           | -                                                                            |   | -       | 2       | -       | ms    |

|                         | Power good<br>de-assertion delay,<br>FB falling | -                                                                            |   | -       | 65      | -       | μs    |

| V <sub>OL</sub>         | Output level low                                | I <sub>SINK</sub> = 1mA                                                      | • | -       | -       | 0.4     | V     |

| GLOBAL EN an            | nd SEQ EN Input                                 |                                                                              |   |         |         |         | -     |

| V <sub>IL</sub>         | Input low level                                 | -                                                                            |   | -       | -       | 0.8     | V     |

| V <sub>IH</sub>         | Input high level                                | -                                                                            |   | 2.0     | -       | -       | V     |

|                         | GLOBAL EN input current                         | GLOBAL EN = 5.5V                                                             |   | -       | 4       | 30      | μΑ    |

|                         | SEQ EN input current                            | SEQ EN = 5.5V                                                                |   | -       | 4       | 30      | μA    |

| Input Voltage M         | onitor Flag                                     | 1                                                                            |   |         |         |         |       |

| V <sub>TH_RISING</sub>  | Input voltage good threshold                    | Voltage rising                                                               |   | 4.59    | 4.63    | 4.7     | V     |

| V <sub>TH_FALLING</sub> | Input voltage good threshold                    | Voltage falling                                                              |   | 4.52    | 4.57    | 4.65    | V     |

**Table 4: Electrical Characteristics (Continued)**

| Symbol                       | Parameter                                                | Conditions                                           | • | Minimum | Typical                 | Maximum                         | Units      |

|------------------------------|----------------------------------------------------------|------------------------------------------------------|---|---------|-------------------------|---------------------------------|------------|

| ADC, Tempera                 | ture Monitoring                                          |                                                      |   |         |                         |                                 | '          |

|                              | Input range                                              | 5VSYS ≥ 4.2V                                         | • | 0       | -                       | 2.55 +<br>offset <sup>(1)</sup> | V          |

|                              | Input range                                              | 5VSYS ≥ 4.0V                                         | • | 0       | -                       | 2.35                            | V          |

|                              | Nominal Resolution                                       | 8 bit                                                |   | -       | 10                      | -                               | mV/<br>LSB |

|                              | INL                                                      | -                                                    |   | -       | -                       | ±2                              | LSB        |

|                              | DNL, differential nonlinearity                           | -                                                    |   | -       | -                       | ±1                              | LSB        |

|                              | Full scale error                                         | -                                                    |   | -       | -                       | ±2                              | LSB        |

|                              | Zero error (offset)                                      | -                                                    |   | -       | +1                      | -                               | LSB        |

|                              | Full scale error temperature coefficient                 | -                                                    |   | -       | ±0.03                   | ±0.05                           | %/°C       |

|                              | ADC conversion frequency                                 | -                                                    |   | -       | 5.56                    | -                               | kHz        |

|                              | Input capacitance                                        | -                                                    |   | -       | 4                       | -                               | pF         |

|                              | AN0/1 DC input impedance                                 | -                                                    |   | -       | 10                      | -                               | ΜΩ         |

| T <sub>RANGE</sub>           | Temperature monitoring range                             | -                                                    |   | -40     | -                       | Thermal<br>Shutdown             | °C         |

| T <sub>RES</sub>             | Temperature monitoring range                             | -                                                    |   | -       | 1.06                    | -                               | °C         |

| T <sub>ACCURACY</sub>        | Temperature monitoring                                   | 25°C (h'5F)                                          |   | -2      | -                       | 2                               | °C         |

| ACCURACT                     | accuracy                                                 | 105°C (h'B4)                                         |   | -7      | -                       | 7                               | °C         |

| I <sup>2</sup> C Interface - | Default Address 7'b0011101 (0)                           | (1D), see Figure 8 on page 9                         |   |         |                         |                                 |            |

| V <sub>IL</sub>              | Input low level                                          | -                                                    |   | -       | -                       | 8.0                             | V          |

| V <sub>IH</sub>              | Input high level                                         | -                                                    |   | 2.0     | -                       | -                               | V          |

| $V_{L}$                      | VDDIO supply voltage                                     | -                                                    |   | 3.0     | -                       | 5.5                             | V          |

| V <sub>OL_I2C</sub>          | SDA logic output low voltage                             | 3mA sink current                                     | • | -       | -                       | 0.8                             | V          |

| f <sub>SCL</sub>             | SCL clock frequency                                      | -                                                    | • | -       | -                       | 400                             | kHz        |

| t <sub>SCL_H</sub>           | SCL clock high period                                    | -                                                    | • | 0.6     | -                       | -                               | μs         |

| t <sub>SCL_L</sub>           | SCL clock low period                                     | -                                                    | • | 1.3     | -                       | -                               | μs         |

| t <sub>SP</sub>              | I <sup>2</sup> C spike rejection filter pulse width 1    | -                                                    | • | 0       | -                       | 50                              | ns         |

| t <sub>SU_DAT</sub>          | I <sup>2</sup> C data setup time                         | -                                                    | • | 100     | -                       | -                               | ns         |

| t <sub>HD_DAT</sub>          | I <sup>2</sup> C data hold time                          | -                                                    | • | 0       |                         | 900                             | ns         |

| t <sub>R_I2C</sub>           | SDA, SCL rise time                                       | C <sub>B</sub> = total capacitance of bus line in pF | • | -       | 20 + 0.1*C <sub>B</sub> | 300                             | ns         |

| t <sub>F_I2C</sub>           | SDA, SCL fall time                                       | C <sub>B</sub> = total capacitance of bus line in pF | • | -       | 20 + 0.1*C <sub>B</sub> | 300                             | ns         |

| t <sub>BUF</sub>             | I <sup>2</sup> C bus free time<br>between stop and start | -                                                    | • | 1.3     | -                       | -                               | μs         |

**Table 4: Electrical Characteristics (Continued)**

| Symbol              | Parameter                                            | Conditions | • | Minimum | Typical | Maximum | Units |

|---------------------|------------------------------------------------------|------------|---|---------|---------|---------|-------|

| t <sub>SU_STA</sub> | I <sup>2</sup> C repeated start condition setup time | -          | • | 0.6     | -       | -       | μs    |

| t <sub>HD_STA</sub> | I <sup>2</sup> C repeated start condition hold time  | -          | • | 0.6     | -       | -       | μs    |

| t <sub>SU_STO</sub> | I <sup>2</sup> C stop condition setup time           | -          | • | 0.6     | -       | -       | μs    |

| C <sub>B</sub>      | I <sup>2</sup> C bus capacitive load                 | -          | • | -       | -       | 400     | pF    |

| C <sub>SDA</sub>    | SDA input capacitance                                | -          | • | -       | -       | 10      | pF    |

| C <sub>SCL</sub>    | SCL input capacitance                                | -          | • | -       | -       | 10      | pF    |

<sup>1.</sup> Limited by minimum  $t_{ON}$ . For minimum permissible  $V_{OUT}$  versus frequency, see Table 6 on page 18.

Figure 1: I<sup>2</sup>C Bus Timing Diagram

# Pin Information

# Pin Configuration

Figure 2: Pin Configuration (Top View)

# Pin Description

**Table 5: Pin Names and Description**

| Pin Number | Pin Name  | Description                                                                                                                                                                                                                   |

|------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VDDIO     | Supply for I <sup>2</sup> C Interface, from 3.3V to 5V nominal.                                                                                                                                                               |

| 2          | SDA       | I <sup>2</sup> C data.                                                                                                                                                                                                        |

| 3          | SCL       | I <sup>2</sup> C clock.                                                                                                                                                                                                       |

| 4          | SEQ EN    | Sequence enable. Input which can be added as an external gate to the power up sequencing. It Is ANDed to the power up sequencing. It has no effect on power down sequencing. See register map. If not used, tie to 5VSYS pin. |

| 5          | PG1       | Power good output 1, open drain. It can consist of any ANDed output of all of the five regulators. See register map.                                                                                                          |

| 6          | GLOBAL EN | Device enable. When pulled low, shuts down entire chip after power down sequencing complete.                                                                                                                                  |

| 7          | VIN       | Input supply to the LDO.                                                                                                                                                                                                      |

| 8          | LDO       | Output of the 100mA LDO.                                                                                                                                                                                                      |

| 9          | VOUT2     | Feedback pin for Buck 2. Buck 2 can be programmed from 1.3V to 1.92V in 20mV steps.                                                                                                                                           |

| 10         | PGND2     | Power ground. Source of the low-side MOSFET for Buck 2.                                                                                                                                                                       |

| 11         | LX2       | Switch node of Buck 2. Connect to the output inductor.                                                                                                                                                                        |

| 12         | VIN2      | Input supply to Buck 2. Bypass to the PGND.                                                                                                                                                                                   |

| 13         | VIN4      | Input supply to Buck 4. Bypass to the PGND.                                                                                                                                                                                   |

| 14, 15, 16 | LX4       | Switch node of Buck 4. Connect to the output inductor.                                                                                                                                                                        |

| 17, 18     | PGND4     | Power ground. Source of the low-side MOSFET for Buck 4.                                                                                                                                                                       |

| 19         | VOUT4     | Feedback pin for Buck 4. Buck 4 can be programmed from 0.6V to 1.39375V in 6.25mV steps.                                                                                                                                      |

| 20         | PG2       | Power good output 2, open drain. It can consist of any ANDed output of all of the five regulators. See register map.                                                                                                          |

| 21         | AN1       | Input to ADC. If not used, tie to the AGND.                                                                                                                                                                                   |

| 22         | AN0       | Input to ADC. If not used, tie to the AGND.                                                                                                                                                                                   |

| 23         | AGND      | Signal analog ground. Connect to the system ground.                                                                                                                                                                           |

| 24         | 5VSYS     | Filtered from VIN through an RC to provide internal circuits with clean 5V. Place a 100nF capacitor between this pin and the AGND as close as possible to the device.                                                         |

| 25         | VOUT1     | Feedback pin for Buck 1. Buck 1 can be programmed from 3.0V to 3.6V in 20mV steps.                                                                                                                                            |

| 26         | PGND1     | Power ground. Source of the low-side MOSFET for Buck 1.                                                                                                                                                                       |

| 27         | LX1       | Switch node of Buck 1. Connect to the output inductor.                                                                                                                                                                        |

| 28         | VIN1      | Input supply to Buck 1. Bypass to the PGND.                                                                                                                                                                                   |

| 29         | VIN3      | Input supply to Buck 3. Bypass to the PGND.                                                                                                                                                                                   |

| 30         | LX3       | Switch node of Buck 3. Connect to the output inductor.                                                                                                                                                                        |

| 31         | 5VSYS     | Connect to 5V input. Unlike Pin 24, bypassing is unimportant.                                                                                                                                                                 |

| 32         | VOUT3     | Feedback pin for Buck 3. Buck 3 can be programmed from 0.8V to 1.59375V in 6.25mV steps.                                                                                                                                      |

| PAD        | PGND      | Package central pad. Connect to the PGND.                                                                                                                                                                                     |

# **Typical Performance Characteristics**

Figure 3: Buck 1 Efficiency

Figure 4: Buck 2 Efficiency

Figure 5: Buck 3 Efficiency

Figure 6: Buck 4 Efficiency

Figure 7: GLOBAL EN and SEQ EN Input Current vs Voltage

Figure 8: Measured vs Programmed Frequency

# Typical Performance Characteristics (Continued)

Figure 10: Buck 2 Power Loss

Figure 11: Buck 3 Power Loss

Figure 12: Buck 4 Power Loss

Figure 13: Package Derating

# **Functional Block Diagram**

Figure 14: Functional Block Diagram

# **Applications Information**

### Operation

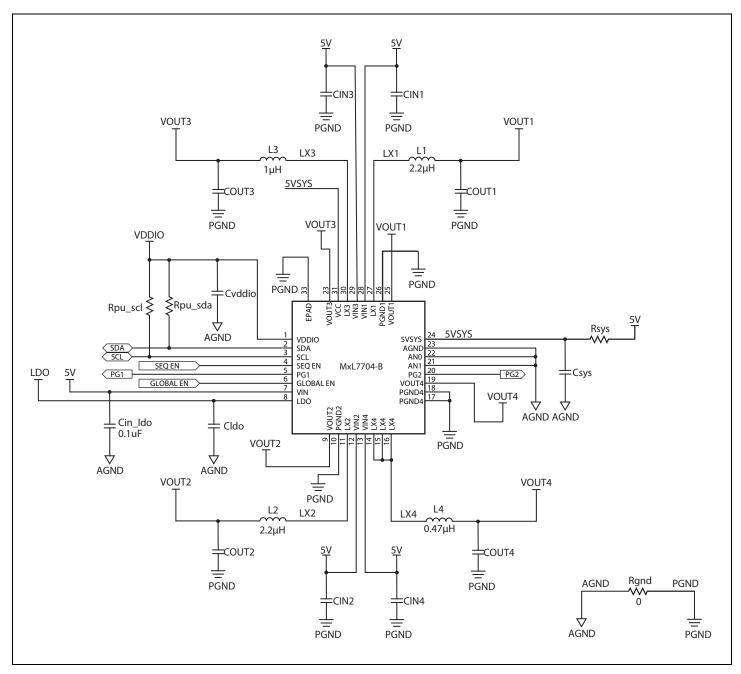

The MxL7704-B device is a 5-output universal PMIC optimized for powering low power FPGAs, DSPs, and microprocessors from a 5V input. Four independent buck the regulators provide load currents of 1.5A for the system power, 1.5A for I/O, 2.5A for memory, and 4A for core power. A 100mA LDO provides a clean 3.3V power for auxiliary devices. All outputs support margining where the initial set point can be changed by an 8-bit code. All outputs also support dynamic voltage scaling (DVS) where the output voltage can be dynamically ramped up or down at a preset rate to save power in processors that can use this function.

The I<sup>2</sup>C interface allows you to monitor an input voltage flag and PGOOD flags for each output. The I<sup>2</sup>C port can be also used to modify the power up and power down sequencing options, assign power good outputs to PG1 and PG2 pins, enable the PMIC outputs, and select the switching frequency.

All buck regulators employ peak current mode control architecture with internal compensation and high switching frequency. This provides fast transient response to load and line changes without sacrificing stability and keeping small component sizes on board.

Fault protection features include input undervoltage lockout (UVLO), output overcurrent protection (OCP), undervoltage protection (UVP), and over temperature (OTP) or thermal protection.

Two power good outputs are available (PG1, PG2).

Each channel has a soft-start, soft stop function and a DVS.

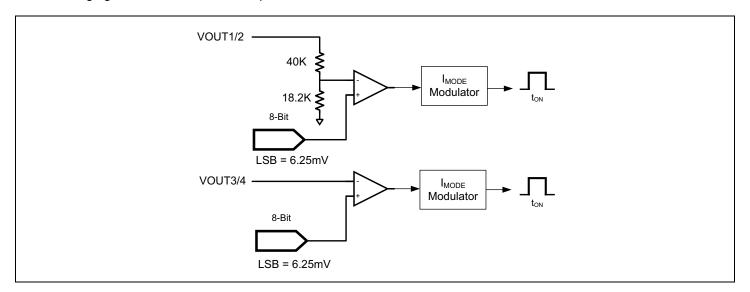

### **Output Voltage Scaling**

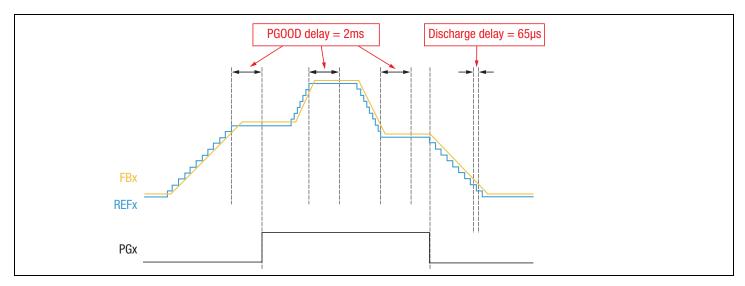

All outputs support margining where the initial set point can be changed by an 8-bit code. Back to back voltage commands are not supported. You must wait for PGOOD blanking (2.2ms maximum) to complete before a subsequent DVS command can be sent. For reference, see Figure 16 on page 16.

The channel 1 range is from 3.0V to 3.6V with 20mV resolution.

Note: The channel 1 regulation is limited by maximum duty cycle.

The channel 2 dynamic range is from 1.3V to 1.92V with 20mV resolution, the channel 3 from 0.8V to 1.6V with 6.25mV resolution, and the channel 4 from 0.6V to 1.4V with 6.25mV resolution.

The channel 3 and 4 lower regulation range is limited by the minimum on time of 120ns.

The LDO dynamic range is from 1.5V to 3.3V with 20mV resolution. Rather than change the voltage divider resistances in the feedback path, the error amplifier reference is changed. This ensures that the gain of the control loop remains unchanged as the voltage is changed. When a voltage change is requested, the output slews at 10V/ms which minimizes the latency when moving from low power states to high power states.

Although the 8-bit register accepts values outside those within the ranges previously listed, the accuracy of the output is not guaranteed.

# Sequencing

Power up and down sequencing is controlled by setting registers 0x15, 0x16, 0x17 and 0x19. Each channel (BUCK or LDO) can be assigned to be in any of four groups (group 0 thru 3) by programing register 0x15 and 0x16 (each of them has a 2-bit group register that assigns them to each of the four groups). When enabled through GLOBAL EN or the input voltage rising above the UVLO point, all outputs are discharged by enabling the  $78\Omega$  discharge resistors. This ensures proper sequencing after an input voltage glitch.

The sequencing state machine starts with group 0 and looks for any channels if assigned to it by their respective 2-bit group settings.

If any channels are assigned to group 0, the state machine starts them up at the same time, provided 5VSYS UVLO is cleared and the outputs assigned to GROUP 0 are discharged by the  $78\Omega$  resistor to <200mV.

Once all group 0 channels are up (all PGOODs are found with the 2ms blanking time added), the sequencing state machine moves to group 1 and repeats the same process, omitting the wait of the output to be discharged to <200mV. It continues to group and then group 3.

If one group is not up (at least one channel in the group is at fault or disabled thru register setting 0x16), all subsequent groups are not started. If a group does not have any channels, it is ignored and the sequencing state machine moves to the next one.

### Power Down Sequencing of Channels

After a normal power up sequence is completed, the power down sequencing can be controlled by pulling GLOBAL EN LOW. Power down sequencing of channels follows the reverse order of the power up sequencing of channels (group 3 thru 0). Depending on the soft off enable setting (bit 6 of 0x19), channels are sequenced down in the method:

Soft off enabled: Channels dynamically slewed down for Xms (where X = Vout) and discharged through the 78Ω resistor (default).

The LDO cannot slew negative by default. Thus it is immediately considered soft-off complete.

The MxL7704-B uses a digitally controlled soft-start and soft off. Each output, including the LDO, has an 8-bit reference DAC feeding the error amplifier input. Although the registers accept a value across the entire DAC range, the outputs are optimized for the output voltage ranges listed in Table 4 on page 2.

Note that after all channels are sequencing down by pulling GLOBAL EN LOW, the device is in a hard-reset mode.

When the device is shut down via thermal shutdown (TSD), the channels are immediately tri-stated and discharged by the  $78\Omega$  active discharge resistance. Bit 6 at register address 0x19 is ignored.

Figure 15: Sequencing

### SEQ EN and Channel Enable Bits

The SEQ EN pin input can be assigned to any of the sequence groups and an external signal can gate sequencing. This is accomplished by setting bits [7:6] of register 0x17, which acts as an enabler to that group and all other subsequently higher groups. Therefore each channel has its own channel enable (bits [4:0] of register 0x16), group enable needs to be enabled as well to effectively enable a channel.

- If SEQ EN is LOW at start, it gates the startup of the group that is assigned to it, and hence all other subsequent higher groups.

- Having SEQ EN HIGH at startup, it voids its effect (all group enabled are ON) on the soft-start sequencing.

You can always use SEQ EN (pulling HIGH/LOW) to turn on/off multiple groups/channels at any time by moving/setting SEQ EN group assign (bit [7:6] of register 0x17).

- If SEQ EN is LOW, the group/channel(s) assigned to the SEQ EN shuts down according to the soft off enable setting (bit 6 of 0x19) without any power down sequencing.

- If SEQ EN is HIGH, when GLOBAL EN is driven low, it does not gate the sequential power down of the sequencing groups.

You can always use channel enable bits (bits [4:0] of the register 0x16) to gate sequencing through the  $I^2C$  interface. However once power up sequencing is completed, the channel enable bits can only turn on or off particular channels.

### Changing Sequencing Registers While Operating

Sequencing registers can be changed during chip operation. Therefore, you can change the power down behavior versus the startup behavior.

Note: MaxLinear recommends that you do not write to these registers when the device is powering up or down.

#### **PGOOD**

The state of the PGOOD of each channel gates power up of subsequent higher groups. The state of the PGOOD signals are reported in the status register 0x1A bits [4:0].

At the end of the soft-start, the PGOOD increases after the 2ms PGOOD assertion delay. If a channel goes out of the regulation window for more than 65μs during regulation, the PGOOD decreases. It asserts again after the 2ms assertion delay, assuming the channel is back into the regulation window. If the glitch is faster than 65μs, PGOOD does not record it.

During the DVS, the PGOOD is blanked and held HIGH. Once the DVS is done, the PGOOD is re-evaluated and an effective PGOOD is updated.

In the event of a fault, the PGOOD is pulled low immediately.

The registers 0x17 and 0x18 are used to route the PGOOD signals from all channels to the PG1 and the PG2 outputs respectively. Multiple channels can be assigned and the PG1 or PG2 signals is logic function AND of the selected PGOOD signals. If no channels are assigned to a PG pin, the pin is high impedance.

### Input Voltage Monitor Flag

The device is continually monitoring voltage at the 5VSYS pin. The status of this pin is kept in register 0x1A (bit [6:5]).

Bit 5 provides the current status of this pin while bit 6 is *sticky* set once the 5VSYS pin is above 4.63V. If the voltage at the 5VSYS pin is above 4.63V, bit 5 is set or vice versa. The host can poll these two bits to check the status of this pin.

Bit 6 can only be cleared by the host writing 1 to it.

#### Hot Start

If chip fault action is selected and a fault occurs, the start-up sequencing varies from a cold start where the GLOBAL EN or UVLO enables the device.

Only the outputs in sequencing group 0 is discharged; instead of discharging all outputs in all sequencing groups to <200mV.

Figure 16: Power Good Timing

#### **Faults**

#### Under Voltage Protection (UVP)

A fault condition is reported by the switching regulators and a restart is initiated when an under voltage is detected on the output. That channel immediately tri-states and applies the  $78\Omega$  discharge. If a device fault action is selected, all of the other outputs simultaneously power down based on their power down settings. Once all of the channels are powered down, a 1ms delay gates the restart of the channel or the device. In a restart, just as in initial power up, the first sequencing GROUP channels is discharged to <200mV before power up sequence initiates.

### Output Over Voltage Protection (OVP)

When an output is accidentally connected to a source higher than the target voltage of the buck regulator, the buck regulator can clamp that voltage. It is the natural response of the control loop to turn on the low side MOSFET and tries to clamp the output voltage. The buck regulator tries to protect the lower voltage, higher value circuitry to the point of destruction.

### Over Current Protection (OCP)

A current limit event occurs when the over current threshold exceeds for eight or more switching cycles. Once detected, the switches are placed into tri-state. As it happens with UVP, that channel tri-states and applies the  $78\Omega$  discharge. If a device fault action is selected, all of the other outputs simultaneously power down based on their power down settings. Once all of the channels are powered down, a 1ms delay gates the restart of the channel or the device.

Unlike the initial power up where all of the outputs are discharged before sequencing initiates with sequencing group 0, during any *hot* restart, the outputs for a given group are discharged before to that group that is enabled.

During soft-start, the OCP is disabled for the first 25% of the soft-start time period. If the output voltage is 1V, then the soft-start time is 1ms and thus the current limit is enabled after the first 250µs. The LDO OCP is activated after its soft-start timer expires.

#### Channel/Chip Fault Actions

The register 0x19 bit 7 allows you to choose whether a fault on a given channel only affects that channel or causes an entire restart of the power system. If *channel* is selected, 0x19 bit 7 = 0, then when a fault occurs on any channel, that channel faults and initiates a restart without affecting any of the other outputs.

If *chip* is selected, 0x19 bit 7 = 1, a fault on any channel causes the other channels to down sequence together based on the register 0x19 bit 6 setting and subsequently initiate power up sequence once channels discharge and the 1ms hiccup timer expires.

This register can be changed during chip operation. If the fault action is changed from the channel to the chip while the outputs are enabled and a fault previously occurs, then the chip detects that fault and initiates a chip fault action. If the outputs are shut down when this change is made to the register no restart occurs.

### Thermal Design

Proper thermal design is critical when you control the device temperatures and develop robust designs. One key factor that affects the thermal performance is the temperature rise of the devices in the package. It is a function of the thermal resistances of the package and the power that is internally dissipated.

"Operating Conditions" on page 1 describes the thermal resistance of MxL7704-B (27°C/W). The  $\Theta_{JA}$  thermal resistance specification is based on the MxL7704-B evaluation board that operates without forced airflow.

The package thermal derating and power loss curves are shown in Figure 9 on page 10 through Figure 13 on page 10.

### **Layout Guidelines**

The PCB layout determines a good thermal and electrical performance.

For thermal considerations, it is essential to use more thermal vias to connect the central thermal pad to the ground layer(s).

To achieve good electrical and noise performance, MaxLinear recommends the following steps:

- 1. Place the output inductor close to the LX pins and minimize the connection area. MaxLinear recommends that you do this on the top layer.

- 2. Connect the central thermal pad of the power ground connections to as many layers as possible. It improves the thermal conduction.

- Ensure that the output filtering capacitor shares the same power ground connection as the input filtering capacitor of the same buck converter. This should be connected to the signal ground plane with vias placed at the output filtering capacitors.

- **4.** Minimize the AC current loops formed by input filtering capacitors, output filtering capacitors, output inductors, and the regulator pins.

- 5. Connect the AGND pins to the signal ground plane.

- Place a low pass filter in front of the 5VSYS pin.

- 7. Place also a 100nF capacitor between the 5VSYS and AGND as close as possible to the device.

# I<sup>2</sup>C Operation

The interface is 3.3V with tolerance to 5.5V.

Since there is no clock stretching allowed, the MxL7704-B responds by not acknowledging (NAK) some I<sup>2</sup>C commands. It informs the host that it cannot service them.

The MxL7704-B device responds with a NAK if the delay between writing to the same LDO or soft-start register is less than 2.2ms (2ms + 10% internal oscillator accuracy). In addition, if multiple LDO or Buck outputs are changed within 2.2ms of each other, then each output can only be changed once within those 2.2ms. The I<sup>2</sup>C master must wait at least 2.2ms after the last I<sup>2</sup>C write to the LDO or VBuckx register before writing to them again.

Example 1: Changing outputs for VBuck3 and VBuck4.

If writing to VBuck3 followed by VBuck4, then the I<sup>2</sup>C master must wait at least 2.2ms after the write to VBuck4 before writing to VBuck3 or VBuck4 again.

**Example 2:** Changing all outputs.

If writing to VLDO, VBuck1, VBuck2, VBuck3 and VBuck4, then the I<sup>2</sup>C master must wait for at least 2.2ms after the last write to these registers before writing to any of these registers again.

# Minimum toN and Minimum Duty Cycle Limitation

The minimum on-time  $t_{ON}$  of the MxL7704-B device is at 120ns. If a low duty cycle application requires a shorter  $t_{ON}$ , the regulation is lost. The minimum permissible  $V_{OUT}$  corresponding to switching frequency f with an assumed efficiency of <85% can be calculated as follows:

$$0.85 \times \frac{V_{OUT}}{V_{IN}} = \frac{t_{ON}}{T} = t_{ON} \times f$$

$$V_{OUT} = V_{IN} \times f \times 120 ns \times 0.85$$

Where  $V_{IN(MAX)} = 5.5V$ .

Table 6: Minimum Permissible Vout

| f (MHz) | V <sub>OUT(MIN)</sub> (V) |

|---------|---------------------------|

| 1       | 0.600                     |

| 1.1     | 0.617                     |

| 1.2     | 0.673                     |

| 1.3     | 0.729                     |

| 1.4     | 0.785                     |

| 1.5     | 0.842                     |

| 1.6     | 0.898                     |

| 1.7     | 0.954                     |

| 1.8     | 1.010                     |

| 1.9     | 1.066                     |

| 2       | 1.122                     |

| 2.1     | 1.178                     |

# Buck 1 Operation at Low V<sub>IN</sub>

When  $V_{\text{IN}}$  -  $V_{\text{OUT}}$  is lower than 0.8V (for example,  $V_{\text{OUT}}$  = 3.6V,  $V_{\text{IN}}$  < 4.4V) the controller skips pulses to maintain regulation. Under steady-state operation, the controller typically regulates with  $V_{\text{IN}}$  as low as 4.0V. If conditions result in a dropout, the upper MOSFET can operate at 100% duty cycle. Operating at or near the dropout can affect the dynamic performance including a load transient response and a positive dynamic voltage scaling.

# Minimum Effective C<sub>OUT</sub>

The MxL7704-B device has internal feedback loop compensation. Each channel requires a minimum COUT to have a sufficient phase margin and stable feedback loop. The effective COUT for a couple of different use cases is listed in Table 7. The 1MHz case is that shown in Figure 19 on page 23. The nominal capacitance for a given set of operating conditions must be calculated from manufacturer's data sheet by using applicable derating curves.

Table 7: Recommended L and COUT

| f (MHz) | Channel | V <sub>OUT</sub> (V) | L (µH) | Effective COUT (μF) |

|---------|---------|----------------------|--------|---------------------|

|         | 1       | 3.3                  | 2.2    | 15                  |

| 1.5     | 2       | 1.8                  | 1      | 20                  |

| 1.5     | 3       | 1.35                 | 0.47   | 90                  |

|         | 4       | 1.2                  | 0.47   | 110                 |

|         | 1       | 3.3                  | 2.2    | 22                  |

| 1       | 2       | 1.8                  | 2.2    | 27                  |

| ı       | 3       | 1.35                 | 1      | 110                 |

|         | 4       | 0.85                 | 0.47   | 210                 |

You can calculate the inductor value for different V<sub>OUT</sub> as follows:

$$L \ge \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{\Delta i \times f \times V_{IN}}$$

$V_{IN}$  = Typical input voltage.

V<sub>OUT</sub> = Desired output voltage.

f = Switching frequency of the converter.

$\Delta i$  = inductor ripple current.

An expected estimate for the inductor ripple current ( $\Delta i$ ) is from 20% to 40% of the maximum output current. For more information, see I<sub>OLT</sub> in Table 4 on page 2.

If you do not use an output at the maximum output current, MaxLinear recommends that you use an inductor value that do not exceed 50% of the calculated inductor value with the maximum output current.

Note that the inductor must always have a higher rating than the maximum current because the current increases with decreasing inductance.

### **Dynamic Voltage Scaling**

All four buck regulators support DVS. The dynamic output slew rate is 10V/ms (nominal).

**Note:** MaxLinear recommends that you do not ramp up DVS (that is, increase V<sub>OUT</sub>) at the maximum rated current. It can cause a premature over-current protection (OCP) event caused by the high inrush current due to the high slew rate of 10V/ms.

As an example, consider Buck 4 of MxL7704-B operating at 1MHz with L =  $0.47\mu$ H and COUT (effective) =  $210\mu$ F. The inrush current corresponding to the DVS can be calculated as follows:

$$I_{INRIJSH} = 210 \mu F \times 10 V/ms = 2.1 A$$

$$I_{INRUSH} = C_{OUT} \times \frac{\Delta V_{OUT}}{\Delta t}$$

Therefore, peak inrush current is:

$$I_{INRUSHPEAK} = 2.1A + (0.5 \times 1.52A) = 2.86A$$

The minimum current limit is 5.5A for Buck 4. Therefore, the maximum permissible output current while using the DVS is as follows:

$$I_{OUT} = 5.5A - 2.86A = 2.64A$$

The actual analysis should be carried out to ensure that the inrush current of a large C<sub>OUT</sub> does not result in a premature OCP.

### Output Voltages Outside Ranges Guaranteed in Electrical Table

The MxL7704-B has four internally compensated current-mode synchronous buck regulators that are characterized from 1MHz to 2.1MHz switching frequency according to the electrical table:

- Buck 1: 3.0V–3.6V, 20mV step, 1.5A

- Buck 2: 1.3V–1.92V, 20mV step, 1.5A

- Buck 3: 0.8V-1.6V, 6.25mV step, 2.5A

- Buck 4: 0.6V-1.4V, 6.25mV step, 4A

The accuracy of the output voltages is guaranteed over these ranges and the internal compensation is optimized for these operating points. However, the programmable range for the Buck 1 and Buck 2 voltage set point register is 20mV to 3.6V and for Buck 3 and Buck 4 it is 6.25mV to 1.59375V.

Although accuracy is not guaranteed outside the limits of the data sheet, the DACs are tested across the entire settable range. Testing the DACs is necessary because they are used to implement the startup (soft-start) and shutdown sequencing. Figure 16 on page 16 shows *REFx*, which is the DAC output. As such, at each startup, the device is demonstrated to operate properly across the entire DAC range.

The MxL7704-B can operate across this range because it changes the DAC voltage into the error amplifier rather than changing the feedback resistors. The control loop gain is thus held constant across the entire DAC range.

$$H(s)\alpha - \frac{V_{REF}}{V_{OUT}}$$

The control loop gain is proportional to the ratio between V<sub>REF</sub> and V<sub>OUT</sub>.

The following figure shows the control loop architecture of the MxL7704-B.

Figure 17: MxL7704-B Control Loop Architecture

If you wish to use the MxL7704-B outside the voltage limits stated on the data sheet, MaxLinear recommends that you perform simple transient tests to check stability before releasing a design to production. These tests are:

- 25% to 75% load change at 1A/μs

- 75% to 25% load change at 1A/μs

The result should show a damped response without ringing like the example shown in Figure 18. This is Buck 3 set to 1.2V output at 1MHz switching frequency using a  $1\mu$ H inductor and three JMK212BBJ476MG ceramic capacitors with an effective capacitance of  $110\mu$ F. The load step is from 0A to 2.5A. If the output shows ringing during the transient test, reducing the inductance generally improves the results.

Figure 18: Damped Response without Ringing

### Analog to Digital Converter and Temperature Sensor

The MxL7704-B device has a built in 8-bit analog-to-digital converter (ADC) and a temperature sensor. The ADC has three analog inputs: AN0, AN1, and TEMP. The AN0 and AN1 inputs are external analog signals that you can apply for conversion. The TEMP input internally monitors the temperature sensor output. Temperature data can be read from the register address 0x1B and is calculated as follows:

$$DECIMAL = [(T_{SENSOR} - 25^{\circ}C) \times 1.06LSB/^{\circ}C] + 95$$

#### Where:

$T_{SENSOR}$  = Temperature of the internal sensor.

1.06LSB/°C = Nominal resolution of the DAC.

Therefore, at an ambient of 25°C the register should typically return a value of 95 (decimal) or 0x5F (hex) when the four bucks are turned off to reduce internal heating.

The register addresses 0x1C and 0x1D contain the outputs that correspond to the analog inputs AN0 and AN1 respectively. The ADC has a nominal zero error (offset) of typically +3 LSB. Therefore, an input voltage of 30mV is required to produce an output transition of 00 to 01. INL is calibrated at (1.75V + offset) and specified  $\pm 2$  LSB. For best ADC performance, the 5VSYS pin must be bypassed to the AGND with a  $10\mu F$ ,  $1\mu F$  and  $0.1\mu F$  capacitor. You must place the  $0.1\mu F$  as close to the device as possible. MaxLinear recommends that you use a lowpass filter  $0.1\mu F/100\Omega$  at the AN0 and AN1 inputs.

The default ADC EN bit in MxL7704-B is enabled and automatically calibrated every time when the PMIC is powered.

# **Typical Application**

Figure 19: MxL7704-B Typical Application

# **Register Information**

# Slave I<sup>2</sup>C Address

Table 8: Slave I<sup>2</sup>C Address

| Device    | 7-Bit Address |

|-----------|---------------|

| MxL7704-B | 0x2D          |

### Register Map

The runtime registers can be changed through the I<sup>2</sup>C.

Table 9: Register Map

| Address | Register                                          | R/W | Bit 7            | Bit 6          | Bit 5            | Bit 4              | Bit 3       | Bit 2       | Bit 1                 | Bit 0     |

|---------|---------------------------------------------------|-----|------------------|----------------|------------------|--------------------|-------------|-------------|-----------------------|-----------|

| 0x01    | ADC enable                                        | R/W | -                | -              | -                | -                  | -           | -           | -                     | ADC<br>EN |

| 0x11    | Vout Buck 1                                       | R/W |                  |                |                  | VBuck*             | 1[7:0]      |             |                       |           |

| 0x12    | Vout Buck 2                                       | R/W |                  |                |                  | VBuck2             | 2[7:0]      |             |                       |           |

| 0x13    | Vout Buck 3                                       | R/W |                  |                |                  | VBuck3             | 3[7:0]      |             |                       |           |

| 0x14    | Vout Buck 4                                       | R/W |                  |                |                  | VBuck <sup>2</sup> | 1[7:0]      |             |                       |           |

| 0x15    | Buck sequence group assignment                    | R/W | Buck 4           | 1 [1:0]        | Buck 3           | [1:0]              | Buck        | 2 [1:0]     | Buck                  | 1 [1:0]   |