## **Data Sheet**

MxL7204

**Dual 4A Power Module**

# **General Description**

The MxL7204 power module is a complete dual 4A or single 8A output switch mode DC/DC power supply with an input voltage of 4.5V to 20V. It offers higher efficiency and improved thermal performance than the competition while matching pinout and functionality. Power modules integrate the switching controller, power FETs, inductors and all supporting components. The MxL7204 supports two outputs each with an output voltage range of 0.6V to 5.0V, set by a single external resistor. Its high efficiency design delivers up to 4A continuous current (5A peak) for each output. Only a few input and output capacitors are needed.

The device supports frequency synchronization, multiphase operation, and output voltage tracking for supply rail sequencing. High Switching frequency and a current mode architecture enable a very fast transient response to line and load changes without sacrificing stability.

Fault protection features include overvoltage, overcurrent and over temperature protection. The power module is offered in a space saving and thermally enhanced 15mm × 15mm × 2.82mm LGA package.

## **Features**

- Dual 4A output (5A peak)

- Input Voltage Range: 4.5V to 20V

- Output Voltage Range: 0.6V to 5.0V

- Current mode control / fast transient response

- Adjustable switching frequency

- Frequency synchronization (250kHz to 780kHz)

- Overcurrent protection

- Output overvoltage protection

- Thermally enhanced (15mm x 15mm x 2.82mm) LGA package

## **Applications**

- Telecom and Networking Equipment

- Industrial Equipment

Ordering Information - Back Page

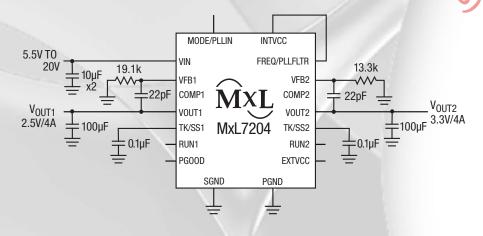

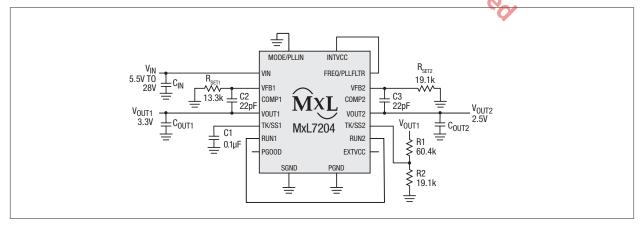

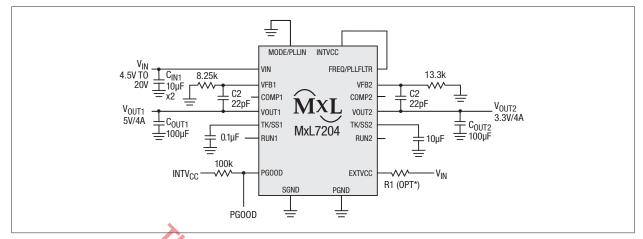

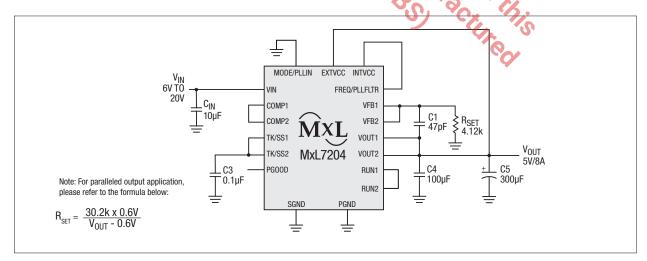

Figure 1: Typical Application Circuit

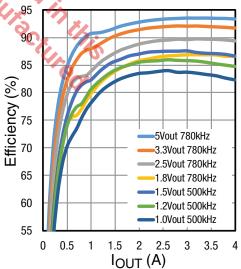

Figure 2: Efficiency 12V<sub>IN</sub>

MxL7204 Data Sheet Revision History

## **Revision History**

| Revision | Release Date | Change Description                                                                                                                                                                                                                                           |

|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1A       | 2/20/18      | Initial Release                                                                                                                                                                                                                                              |

| 1B       | 8/8/18       | Added paralleled output voltage programming equations and Table 7. Renamed $R_{FB}$ resistors to $R_{SET}$ . Corrected TK/SS and VFB pin numbers in Pin Description. Harmonized name of TR/SS, FREQ/PLL-FLTR, MODE/PLLIN and PGND pins. Corrected Figure 30. |

## **Table of Contents**

| General Description                                  | i  |

|------------------------------------------------------|----|

| Features                                             | i  |

| Applications                                         | i  |

| Specifications                                       | 1  |

| Absolute Maximum Ratings                             | 1  |

| ESD Ratings                                          | 1  |

| Operating Conditions 🔉                               | 2  |

| Electrical Characteristics                           | 3  |

| Pin Information Pin Configuration                    | 7  |

| Pin Configuration                                    | 7  |

| Pin Description                                      | 7  |

| Typical Performance Characteristics                  | 10 |

| Functional Block Diagram                             | 12 |

| Applications Information                             | 13 |

| Power Module Description                             | 13 |

| Typical Application Circuit                          | 13 |

| V <sub>IN</sub> to V <sub>OUT</sub> Step-Down Ratios |    |

| Output Voltage Programming                           | 14 |

| Input Capacitors                                     | 14 |

| Output Capacitors                                    | 14 |

| Pulse-Skipping Mode Operation                        | 14 |

| Forced Continuous Operation                          |    |

| Multiphase Operation                                 | 14 |

| Input RMS Ripple Current Cancellation                | 15 |

| Minimum On-Time                                      | 17 |

| Output Voltage Tracking                              | 17 |

| Power Good                                           | 18 |

| Stability Compensation                               | 18 |

## **Table of Contents**

| Run Enable                                         | 18           |

|----------------------------------------------------|--------------|

| INTV <sub>CC</sub> and EXTV <sub>CC</sub>          | 18           |

| Thermal Considerations and Output Current Derating | 19           |

| Fault Protection                                   | 21           |

| Layout Checklist and Example                       | 22           |

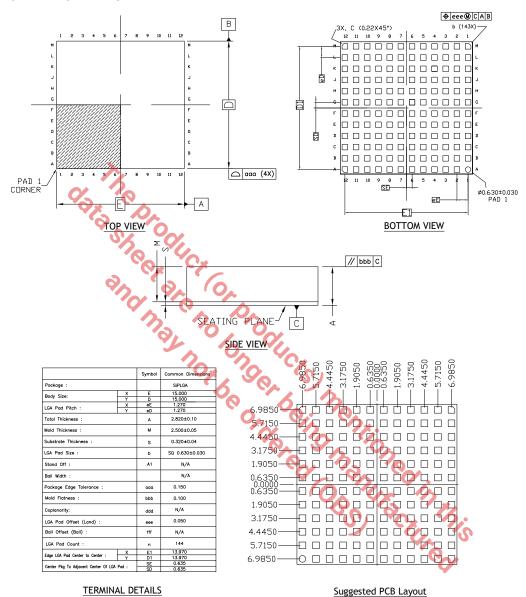

| Mechanical Dimensions                              | 24           |

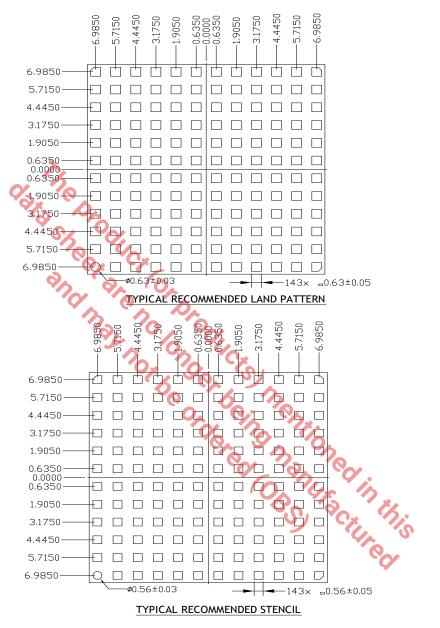

| Recommended Land Pattern and Stencil               | 25           |

| Ordering Information                               | 26           |

| Precommended Land Pattern and Stencil              | in this real |

## **List of Tables**

| Table 1: Absolute Maximum Ratings                                                                               | 1  |

|-----------------------------------------------------------------------------------------------------------------|----|

| Table 2: ESD Ratings                                                                                            | 1  |

| Table 3: Operating Conditions                                                                                   | 2  |

| Table 4: Electrical Characteristics                                                                             | 3  |

| Table 5: Pin Description                                                                                        | 7  |

| Table 6: VFB Resistor Table vs Various Output Voltages                                                          | 14 |

| Table 7: VFB Resistor Table vs Various Output Voltages for Paralleled Output Mode                               | 14 |

| Table 8: Capacitor Selection                                                                                    | 18 |

| Table 9: Ordering Information                                                                                   | 26 |

| Table 7: VFB Resistor Table vs Various Output Voltages for Paralleled Output Mode  Table 8: Capacitor Selection |    |

MxL7204 Data Sheet List of Figures

# List of Figures

| Figure 1: Typical Application Circuit                                                                 | i  |

|-------------------------------------------------------------------------------------------------------|----|

| Figure 2: Efficiency 12V <sub>IN</sub>                                                                | i  |

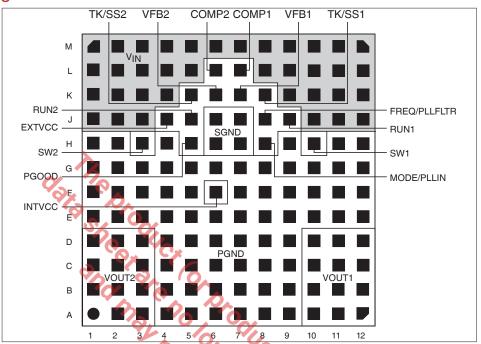

| Figure 3: Pin Configuration                                                                           | 7  |

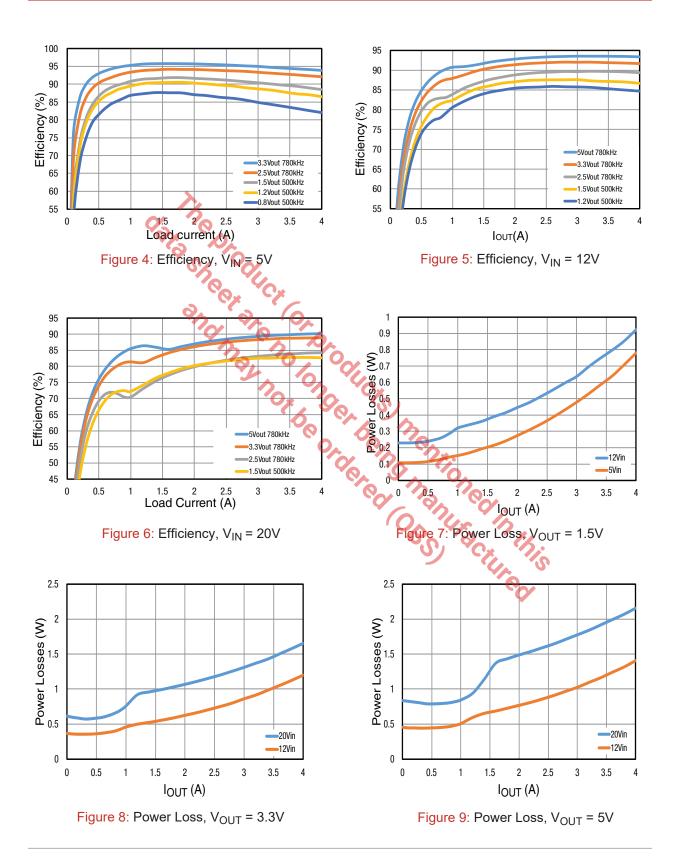

| Figure 4: Efficiency, V <sub>IN</sub> = 5V                                                            | 10 |

| Figure 5: Efficiency, V <sub>IN</sub> = 12V                                                           | 10 |

| Figure 6: Efficiency, V <sub>IN</sub> 20V                                                             | 10 |

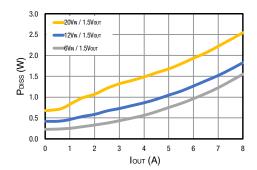

| Figure 7: Power Loss, Vour = 1.5V                                                                     | 10 |

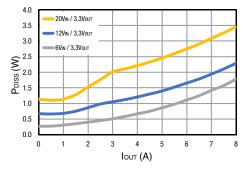

| Figure 8: Power Loss, V <sub>OUT</sub> = 3.3V                                                         | 10 |

| Figure 9: Power Loss, V <sub>OUT</sub> = 5V.C.                                                        | 10 |

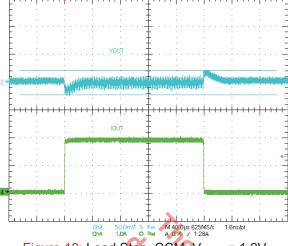

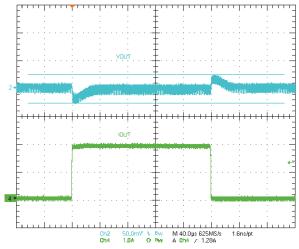

| Figure 10: Load Step, CCM, V <sub>OUT</sub> = 1.2V                                                    | 11 |

| Figure 11: Load Step, CCM, V <sub>OUT</sub> = 1.5V                                                    | 11 |

| Figure 12: Load Step, CCM, Vout = 2.5V                                                                |    |

| Figure 13: Load Step, CCM, V <sub>OUT</sub> = 3.3V.O                                                  | 11 |

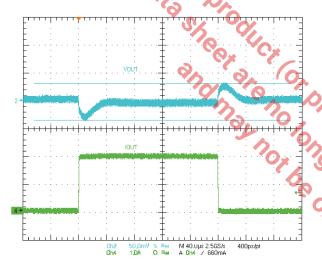

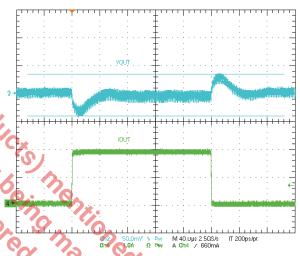

| Figure 14: Start-Up, I <sub>OUT</sub> = 0A                                                            | 11 |

| Figure 15: Start-Up, I <sub>OUT</sub> = 4A                                                            | 11 |

| Figure 16: Functional Block Diagram                                                                   | 12 |

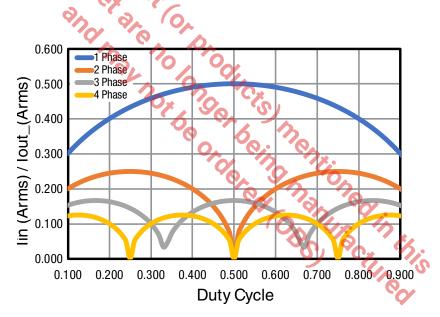

| Figure 17: Normalized Input RMS Ripple Current vs Duty Cycle for One to Four Phases                   | 15 |

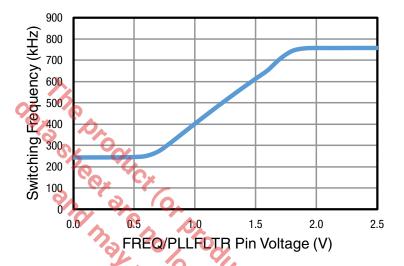

| Figure 18: Operation Frequency vs. FREQ Pin Voltage                                                   |    |

| Figure 19: Example of Output Tracking Application Circuit                                             | 17 |

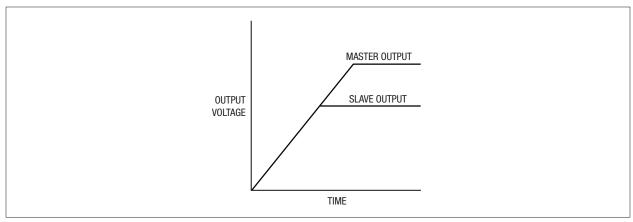

| Figure 20: Output Coincident Tracking Waveform                                                        | 18 |

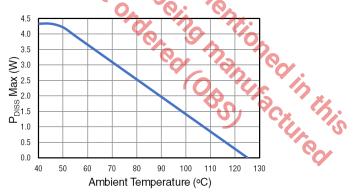

| Figure 21: Package Pmax Derating vs. Ambient Temperature                                              | 19 |

| Figure 22: Power Loss, V <sub>OUT</sub> = 1.5V, 500kHz                                                | 19 |

| Figure 23: Power Loss, V <sub>OUT</sub> = 3.3V, 780kHz                                                | 19 |

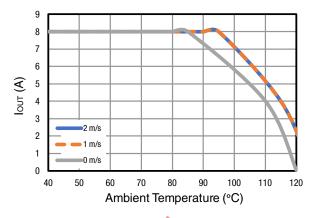

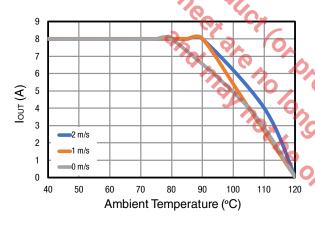

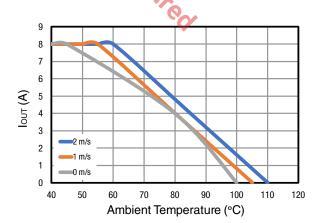

| Figure 24: Output Current Derating vs. T <sub>AMBIENT</sub> , 6V <sub>IN</sub> , 1.5V <sub>OUT</sub>  | 20 |

| Figure 25: Output Current Derating vs. T <sub>AMBIENT</sub> , 6V <sub>IN</sub> , 3.3V <sub>OUT</sub>  | 20 |

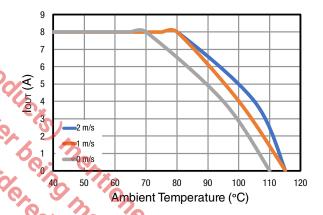

| Figure 26: Output Current Derating vs. T <sub>AMBIENT</sub> , 12V <sub>IN</sub> , 1.5V <sub>OUT</sub> | 20 |

| Figure 27: Output Current Derating vs. T <sub>AMBIENT</sub> , 12V <sub>IN</sub> , 3.3V <sub>OUT</sub> | 20 |

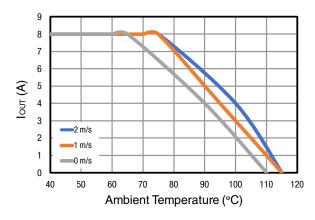

| Figure 28: Output Current Derating vs. T <sub>AMBIENT</sub> , 20V <sub>IN</sub> , 1.5V <sub>OUT</sub> | 20 |

| Figure 29: Output Current Derating vs. T <sub>AMBIENT</sub> , 20V <sub>IN</sub> , 3.3V <sub>OUT</sub> | 20 |

| Figure 30: Recommended PCB Layout                                                                     | 22 |

MxL7204 Data Sheet List of Figures

## List of Figures

| Figure 31: Typical 4.5V to 20V Input, 5V and 3.3V Outputs at 4A Design        | 23 |

|-------------------------------------------------------------------------------|----|

| Figure 32: Typical 4.5V to 20V Input, 1.2V and 1.5V Outputs at 4A Design with |    |

| Adjusted Frequency at 500kHz                                                  | 23 |

| Figure 33: Output Paralleled for 5V at 8A Design                              | 23 |

| Figure 34: Mechanical Dimensions                                              | 24 |

| Figure 34: Mechanical Dimensions                                              | 25 |

Specifications MxL7204 Data Sheet

## **Specifications**

### **Absolute Maximum Ratings**

Important! The stresses above what is listed under Table 1 may cause permanent damage to the device. This is a stress rating only—functional operation of the device above what is listed under Table 1 or anyother conditions beyond what MaxLinear recommends is not implied. Exposure to conditions above what is listed under Table 3 for extended periods of time may affect device reliability. Solder reflow profile is specified in the IPC/JEDEC J-STD-020C standard.

**Table 1: Absolute Maximum Ratings**

| Parameter                                | Minimum   | Maximum            | Units |

|------------------------------------------|-----------|--------------------|-------|

| V <sub>IN</sub>                          | -0.3      | 22                 | V     |

| V <sub>SW1</sub> , V <sub>SW2</sub>      | <b>-1</b> | 22                 | V     |

| PGOOD, COMP1, COMP2                      | -0.3      | 6                  | V     |

| INTV <sub>CC</sub> , EXTV <sub>CC</sub>  | -0.3      | 6                  | V     |

| MODE/PLLIN, FREQ/PLLFLTR, TK/SS1, TK/SS2 | -0.3      | INTV <sub>CC</sub> | V     |

| V <sub>OUT1</sub> , V <sub>OUT2</sub>    | -0.3      | 6                  | V     |

| RUN1, RUN2, VFB1, VFB2                   | -0.3      | INTV <sub>CC</sub> | V     |

| INTV <sub>CC</sub> Peak Output Current   |           | 100mA              | V     |

| Internal Operating Temperature Range     | -40       | 125                | °C    |

| Storage Temperature Range                | -65       | 150                | °C    |

| Lead Temperature (soldering 10 seconds)  | 0 0       | 245                | °C    |

| ESD Ratings  Table 2: ESD Ratings        | tole in a | Pio.               |       |

| Parameter                                | Minimum   | Maximum            | Units |

| HBM (Human Body Model)                   | 6         | 3k                 | V     |

#### **ESD Ratings**

**Table 2: ESD Ratings**

| Parameter                  | Minimum Maximum | Units |

|----------------------------|-----------------|-------|

| HBM (Human Body Model)     | 3k              | V     |

| CDM (Charged Device Model) | 500             | V     |

Specifications MxL7204 Data Sheet

#### **Operating Conditions**

**Table 3: Operating Conditions**

| V <sub>IN</sub>                                                                                                                                                         | Minimum  | Maximum | Units |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|-------|

| • IIV                                                                                                                                                                   | 4.5      | 20      | V     |

| INTV <sub>CC</sub>                                                                                                                                                      | 4.5      | 5.5     | V     |

| PGOOD                                                                                                                                                                   | 0        | 5.0     | V     |

| Junction Temperature Range (T <sub>J</sub> )                                                                                                                            | -40      | 125     | °C    |

| Package Power Dissipation max at 25°C                                                                                                                                   |          | 4.33    | W     |

| Package Thermal Resistance Θ <sub>JA</sub> <sup>(1)</sup>                                                                                                               |          | 14.4    | °C/W  |

| Package Thermal Resistance Θ <sub>JB</sub> <sup>(1)</sup>                                                                                                               |          | 7       | °C/W  |

| Package Thermal Resistance $\Theta_{JA}^{(1)}$ NOTE: $\Theta_{JB} = \Theta_{JC BOTTOM} = 7^{\circ}C/W, \Theta_{BA} = 7.4^{\circ}C/W, \Theta_{JA} = \Theta_{JB} + 60.00$ | Or Drody |         |       |

MxL7204 Data Sheet Specifications

#### **Electrical Characteristics**

Specifications are for Operating Junction Temperature of  $T_J$  = 25°C only; limits applying over the full Operating Junction Temperature range are denoted by a "•". Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only. Unless otherwise indicated,  $V_{IN}$ =12V. Per Figure 31.

**Table 4: Electrical Characteristics**

| Symbol                                         | Parameter                           | Conditions                                                                                                                          |                          | •  | Min   | Тур  | Max   | Units |

|------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----|-------|------|-------|-------|

| DC Specification                               | S                                   |                                                                                                                                     |                          |    |       |      |       |       |

| V <sub>IN(DC)</sub>                            | Input DC voltage                    | $V_{\rm IN} \le 5.5 {\rm V},$<br>Connect $V_{\rm IN}$ and ${\rm INTV}_{\rm CC}$ Tog                                                 | jether                   | •  | 4.5   |      | 20.0  | V     |

| V <sub>OUT1, 2</sub> (RANGE)                   | Output voltage range                | V <sub>IN</sub> = 5.5V to 20.0V                                                                                                     |                          | •  | 0.6   |      | 5.0   | V     |

| V <sub>OUT1, 2(DC)</sub>                       | Output voltage                      | C <sub>IN</sub> = 10μF x 1,  C <sub>OUT</sub> = 22μF Ceramic, 220μF POSCAP,  FREQ/PLLFLTR tied to                                   | I <sub>OUT</sub><br>= 0A | •  | 2.463 | 2.5  | 2.537 | V     |

|                                                | nd ma                               | V <sub>IN</sub> = 12V,<br>Vout = 2.5V                                                                                               | I <sub>OUT</sub><br>= 4A | •  | 2.450 | 2.5  | 2.550 |       |

| Input Specification                            | ns                                  | The series                                                                                                                          |                          |    |       |      |       |       |

| V <sub>RUN1</sub> , V <sub>RUN2</sub>          | RUN pin on/off<br>threshold         | RUN rising                                                                                                                          | 0,                       |    | 1.1   | 1.25 | 1.40  | V     |

| V <sub>RUN1HYS</sub> ,<br>V <sub>RUN2HYS</sub> | RUN pin on hysteresis               | OP, S                                                                                                                               |                          | 2  |       | 200  |       | mV    |

| I <sub>INRUSH(VIN)</sub>                       | Input inrush<br>current at start-up | I <sub>OUT</sub> = 0 <b>A,</b><br>C <sub>IN</sub> = 10μF, C <sub>OUT</sub> = 100μ<br>V <sub>OUT</sub> = 2.5V, V <sub>IN</sub> = 12V | F, N                     | 23 | din   | 0.25 |       | Α     |

|                                                |                                     | V <sub>IN</sub> = 12V, V <sub>OUT1</sub> = 2.5V<br>switching continuous                                                             | (0)                      |    |       | 30   |       |       |

|                                                | Input supply bias<br>current        | V <sub>IN</sub> = 12V, V <sub>OUT2</sub> = 2.5V,<br>switching continuous                                                            |                          |    | .6    | 30   | νος Λ |       |

| $I_{Q(VIN)}$                                   |                                     | V <sub>IN</sub> = 20V, V <sub>OUT1</sub> = 2.5V,<br>switching continuous                                                            |                          |    |       | 35   |       | mA    |

|                                                |                                     | V <sub>IN</sub> = 20V, V <sub>OUT2</sub> = 2.5V<br>switching continuous                                                             | ′,                       |    |       | 35   |       |       |

|                                                |                                     | Shutdown, RUN = 0, V <sub>IN</sub> = 2                                                                                              | 20V                      |    |       | 50   |       | μΑ    |

| la.                                            | Input supply                        | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 2.5V, I <sub>OUT</sub>                                                                    | = 4A                     |    |       | 0.93 |       | A     |

| I <sub>S(VIN)</sub>                            | current                             | V <sub>IN</sub> = 20V, V <sub>OUT</sub> = 2.5V, I <sub>OUT</sub>                                                                    | = 4A                     |    |       | 0.59 |       |       |

MxL7204 Data Sheet Specifications

#### **Electrical Characteristics (continued)**

Specifications are for Operating Junction Temperature of  $T_J$  = 25°C only; limits applying over the full Operating Junction Temperature range are denoted by a "•". Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only. Unless otherwise indicated,  $V_{IN}$ =12V. Per Figure 31.

Table 4: Electrical Characteristics (continued)

| Symbol                                            | Parameter                           | Conditions                                                                                                        |                                            | •        | Min | Тур          | Max | Units |

|---------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------|-----|--------------|-----|-------|

| Output Specifica                                  | tions                               |                                                                                                                   |                                            |          |     |              |     |       |

| I <sub>OUT1, 2(DC)</sub>                          | Output continuous current range     | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 2                                                                       | 2.5V <sup>(1)</sup>                        |          | 0   |              | 4   | А     |

| Δ <sup>V</sup> OUT1(LINE)<br>VOUT(NOM)            | Line regulation accuracy            | V <sub>OUT</sub> = 2.5V, V <sub>IN</sub> from 0<br>I <sub>OUT</sub> = 0A for each 0                               |                                            | •        |     | 0.15<br>0.25 | 0.3 | %     |

| ΔV <sub>OUT2(LINE)</sub><br>V <sub>OUT(NOM)</sub> | Line regulation accuracy            | V <sub>OUT</sub> = 2.5V, V <sub>IN</sub> from 0                                                                   |                                            | •        |     | 0.15<br>0.25 | 0.3 | %     |

| $\frac{\Delta V_{OUT1(LOAD)}}{V_{OUT(NOM)}}$      | Load regulation accuracy            | For each output, V <sub>OU</sub> -<br>0A to 4A, V <sub>IN</sub> = 12                                              | <sub>r</sub> = 2.5V,                       | •        |     | 0.23         | 0.8 | ±%    |

| $\frac{\Delta V_{OUT2(LOAD)}}{V_{OUT(NOM)}}$      | Load regulation accuracy            | For each output, V <sub>OU</sub> -<br>0A to 4A, V <sub>IN</sub> = 12                                              | <sub>r</sub> = 2.5V,                       | •        |     | 0.6          | 0.8 | ±%    |

| Volume out o                                      | Output ripple voltage               | C <sub>OUT</sub> = 0A,                                                                                            | V <sub>IN</sub> = 12V                      |          |     | 15           |     | - mV  |

| V <sub>OUT1</sub> , 2(AC)                         | Culput rippie voltage               | Ceramic,<br>V <sub>OUT</sub> = 2.5V                                                                               | V <sub>IN</sub> = 20V                      |          |     | 20           |     |       |

| f <sub>S</sub>                                    | Output ripple voltage frequency     | I <sub>OUT</sub> = 2A, V <sub>IN</sub> = 12V, V <sub>O</sub><br>FREQ/PLLFLTR = II                                 | <sub>OUT</sub> = 2.5V<br>NTV <sub>CC</sub> | <b>A</b> |     | 780          |     | kHz   |

| V                                                 | Turn-on overshoot                   | C <sub>OUT</sub> = 100μF X5R<br>Ceramic,                                                                          | V <sub>IN</sub> = 12V                      | × 0      | di. | 5            |     |       |

| V <sub>OUTSTART</sub>                             | Turn-orr overshoot                  | $V_{OUT} = 2.5V,$ $I_{OUT} = 0A$                                                                                  | V <sub>IN</sub> = 20V                      | Q.       | Ty. | 3            |     | mV    |

|                                                   |                                     | C <sub>OUT</sub> = 100μF X5R<br>Ceramic,<br>V <sub>OUT</sub> = 2.5V,                                              | V <sub>IN</sub> = 12V                      |          | 0   | 0.25         |     |       |

| <sup>t</sup> start                                | Turn-on time                        | I <sub>OUT</sub> = 0A,                                                                                            | V <sub>IN</sub> = 20V                      |          |     | 0.13         |     | ms    |

| Voutls                                            | Peak deviation for dynamic load     | Resistive Load  Load: 0% to 50% to 0%  C <sub>OUT</sub> = 100µF X5R C  V <sub>OUT</sub> = 2.5V, V <sub>IN</sub> = | eramic,                                    |          |     | 15           |     | mV    |

| tsettle                                           | Settling time for dynamic load step | Load: 0% to 50% to 0%<br>C <sub>OUT</sub> = 100µF X5R C<br>V <sub>OUT</sub> = 2.5V, V <sub>IN</sub> =             | eramic,                                    |          |     | 10           |     | μs    |

| I <sub>OUTPK</sub>                                | Output current limit                | C <sub>OUT</sub> = 22µF Ceramio<br>POSCAP, V <sub>IN</sub> = 12V, V <sub>C</sub>                                  |                                            |          |     | 9            |     | А     |

MxL7204 Data Sheet Specifications

#### **Electrical Characteristics (continued)**

Specifications are for Operating Junction Temperature of  $T_J$  = 25°C only; limits applying over the full Operating Junction Temperature range are denoted by a "•". Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only. Unless otherwise indicated,  $V_{IN}$ =12V. Per Figure 31.

Table 4: Electrical Characteristics (continued)

| Symbol                                 | Parameter                                                                                        | Conditions                                                                          | •  | Min     | Тур           | Max   | Units |

|----------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----|---------|---------------|-------|-------|

| Control Section                        |                                                                                                  |                                                                                     |    |         |               |       |       |

| V <sub>FB1</sub> , V <sub>FB2</sub>    | Voltage at V <sub>FB</sub> pins                                                                  | I <sub>OUT</sub> = 0A, V <sub>OUT</sub> = 1.5V                                      | •  | 0.594   | 0.600         | 0.606 | V     |

| I <sub>FB</sub>                        | Current at V <sub>FB</sub> pins                                                                  |                                                                                     |    |         | -5            | -20   | nA    |

| $V_{OVL}$                              | Feedback overvolt-<br>age lockout                                                                |                                                                                     | •  | 0.654   | 0.66          | 0.666 | V     |

| TRACK1 (I),<br>TRACK2 (I),             | Track pin soft-start pull-up current                                                             | TRACK1 (I),TRACK2 (I) start at 0V                                                   |    | 1.00    | 1.25          | 1.50  | μΑ    |

| UVLO                                   | Undervoltage lockout                                                                             | V <sub>IN</sub> Falling                                                             |    |         | 3.65          |       | V     |

| UVLO                                   | Orider voltage lockout                                                                           | V <sub>IN</sub> Rising                                                              |    |         | 4.25          |       | V     |

| UVLO<br>Hysteresis                     |                                                                                                  | on pr                                                                               |    |         | 600           |       | mV    |

| $t_{ON(MIN)}$                          | Minimum on-time                                                                                  | 40/00/                                                                              |    |         | 90            |       | ns    |

| R <sub>FBHI1,</sub> R <sub>FBHI2</sub> | Resistor between V <sub>OUTS1</sub> , V <sub>OUTS2</sub> and V <sub>FB1</sub> , V <sub>FB2</sub> | Each output                                                                         |    | 60.3    | 60.4          | 60.5  | kΩ    |

| V <sub>PGOOD Low</sub>                 | PGOOD voltage low                                                                                | I <sub>PGOOD</sub> 2mA                                                              |    |         | 0.1           | 0.3   | V     |

| I <sub>PGOOD</sub>                     | PGOOD leakage current                                                                            | V <sub>PGOOD</sub> = 5V                                                             |    |         |               | ±5    | μA    |

| V                                      | PGOOD trip level                                                                                 | V <sub>FB</sub> with respect to set output voltage V <sub>FB</sub> ramping negative | 16 | 9       | -10           |       | %     |

| $V_{PGOOD}$                            | FGOOD (lip level                                                                                 | V <sub>FB</sub> with respect to set output voltage V <sub>FB</sub> ramping positive | 0  | 7<br>2* | 10            |       | %     |

| INTV <sub>CC</sub> Linear R            | egulator                                                                                         |                                                                                     |    | 4/      | ~~            |       |       |

| V <sub>INTVCC</sub>                    | Internal V <sub>CC</sub><br>voltage                                                              | 6V < V <sub>IN</sub> < 20V                                                          |    | 4.8     | <b>&gt;</b> 5 | 5.2   | V     |

| V <sub>INTVCC</sub><br>Load Regulation | INTV <sub>CC</sub><br>load regulation                                                            | I <sub>CC</sub> = 0mA to 50mA                                                       |    |         | 1             | 2     | %     |

| V <sub>EXTVCC</sub>                    | EXTV <sub>CC</sub> switchover voltage                                                            | EXTV <sub>CC</sub> ramping positive                                                 | •  | 4.5     | 4.7           |       | V     |

| V <sub>EXTVCC(DROP)</sub>              | EXTV <sub>CC</sub> dropout                                                                       | I <sub>CC</sub> = 20mA, V <sub>EXTVCC</sub> = 5V                                    |    |         | 50            | 100   | mV    |

| V <sub>EXTVCC(HYST)</sub>              | EXTV <sub>CC</sub> hysteresis                                                                    |                                                                                     |    |         | 180           |       | mV    |

Specifications MxL7204 Data Sheet

#### **Electrical Characteristics (continued)**

Specifications are for Operating Junction Temperature of  $T_J = 25$ °C only; limits applying over the full Operating Junction Temperature range are denoted by a "•". Typical values represent the most likely parametric norm at T<sub>J</sub> = 25°C, and are provided for reference purposes only. Unless otherwise indicated, V<sub>IN</sub>=12V. Per Figure 31.

Table 4: Electrical Characteristics (continued)

| Parameter                   | Conditions                                    | Mi                                                            | n Typ                                                            | Max                                                                   | Units                                                   |

|-----------------------------|-----------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------|

| nase-Locked Loop            |                                               |                                                               |                                                                  |                                                                       |                                                         |

| Nominal frequency           | FREQ/PLLFLTR tied to 1.2V                     | 45                                                            | 500                                                              | 550                                                                   | kHz                                                     |

| Lowest frequency            | FREQ/PLLFLTR tied to 0V                       | 21                                                            | 0 250                                                            | 290                                                                   | kHz                                                     |

| Highest frequency           | FREQ/PLLFLTR > 1.8V, up to INTV <sub>CC</sub> | 70                                                            | 780                                                              | 790                                                                   | kHz                                                     |

| Frequency set current       | <b>Y.</b> .                                   | 9                                                             | 10                                                               | 11                                                                    | μA                                                      |

| MODE/PLLIN input resistance | Ck                                            |                                                               | 235                                                              |                                                                       | kΩ                                                      |

|                             |                                               |                                                               |                                                                  |                                                                       |                                                         |

|                             | Nominal frequency                             | nase-Locked Loop  Nominal frequency FREQ/PLLFLTR tied to 1.2V | nase-Locked Loop  Nominal frequency FREQ/PLLFLTR tied to 1.2V 45 | nase-Locked Loop  Nominal frequency FREQ/PLLFLTR tied to 1.2V 450 500 | Nominal frequency FREQ/PLLFLTR tied to 1.2V 450 500 550 |

8/8/18 Rev 1B 6

Pin Information MxL7204 Data Sheet

## **Pin Information**

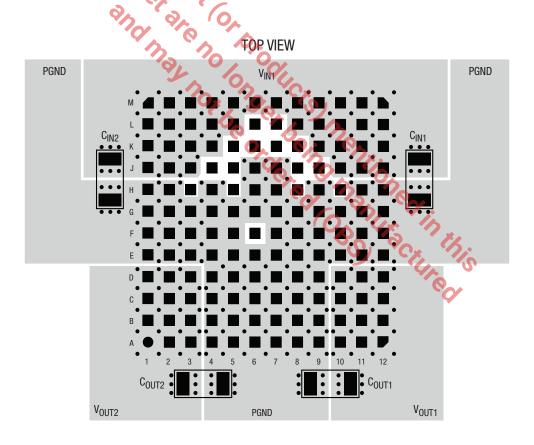

### **Pin Configuration**

Top View, 15mm x 15mm x 2.82mm LGA

### Pin Description

Table 5: Pin Description

|                                                                                                                                    |                                                                   | В     |     |                        |                                                 |                    |                |                     |               |        |         |          |        |       |         |      |        |     |

|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------|-----|------------------------|-------------------------------------------------|--------------------|----------------|---------------------|---------------|--------|---------|----------|--------|-------|---------|------|--------|-----|

|                                                                                                                                    |                                                                   | Α     |     |                        |                                                 |                    |                |                     |               |        |         |          |        |       |         |      |        |     |

|                                                                                                                                    |                                                                   |       | 1   | 2 3                    | 4 5                                             | 6 7                | 8              | 9                   | 10            | 11     | 12      |          |        |       |         |      |        |     |

|                                                                                                                                    |                                                                   |       |     | Top Vie                | w, 15mr                                         | n x 15r            | mm x           | 2.82                | 2mm           | LGA    | 4       |          |        |       |         |      |        |     |

|                                                                                                                                    |                                                                   |       |     |                        | Figure 3                                        | Pin (              | Config         | urat                | ion           |        |         |          |        |       |         |      |        |     |

|                                                                                                                                    |                                                                   |       |     |                        | 9 •                                             | 0,                 |                |                     | 0             | ۵.     |         |          |        |       |         |      |        |     |

| Din Door                                                                                                                           | rintiar                                                           | _     |     |                        |                                                 | "C                 | % `            | ?                   |               |        |         |          |        |       |         |      |        |     |

| Pin Desc                                                                                                                           | ripuor                                                            | 1     |     |                        |                                                 |                    | 0              |                     | 3             |        | 170     |          |        |       |         |      |        |     |

| Table 5: Pin D                                                                                                                     | Descrint                                                          | ion   |     |                        |                                                 |                    | •              |                     | . '(          | Y)     |         | 9        |        |       |         |      |        |     |

|                                                                                                                                    |                                                                   |       |     |                        |                                                 |                    |                | '                   | R             |        | 100     | <u> </u> | 7 1    |       |         |      |        |     |

|                                                                                                                                    |                                                                   |       |     |                        |                                                 |                    |                |                     |               |        |         |          |        |       |         |      |        |     |

| Pin Numb                                                                                                                           | ber                                                               | Pin N | ame |                        | ription                                         |                    |                |                     |               | 5      | 90      | 3x       | 4      | 2/:   |         |      |        |     |

| A10 - D1                                                                                                                           | 0,                                                                |       |     | Outp                   | t of the cl                                     |                    | i pow          | CI SI               | aye.          | COIII  | ICCL L  | 1100     | OFF CS |       |         |      |        |     |

|                                                                                                                                    | 0,<br>1,                                                          | VOU   |     | Outpu                  | -                                               | 1 pins t           | to the         | PGN                 | age.<br>D pir | ns. Di | irect   | 1100     | OFF CS |       |         |      |        |     |

| A10 - D10<br>A11 - D1                                                                                                              | 0,<br>1,<br>12                                                    |       |     | Outpu                  | t of the cl                                     | 1 pins t           | to the         | PGN                 | age.<br>D pir | ns. Di | irect   | 1100     | OFF CS |       |         |      |        |     |

| A10 - D10<br>A11 - D11<br>A12 - D1<br>A4 - A9, B4<br>C4 - C9, D4                                                                   | 0,<br>1,<br>12<br>- B9,<br>- D9,                                  |       |     | Outpu                  | t of the cl                                     | 1 pins t           | to the         | PGN                 | age.<br>D pir | ns. Di | irect   | 1100     | OFF CS |       |         |      |        |     |

| A10 - D10<br>A11 - D10<br>A12 - D1<br>A4 - A9, B4                                                                                  | 0,<br>1,<br>12<br>- B9,<br>- D9,<br>I - F5,                       |       | JT1 | Output from from       | t of the cl                                     | 1 pins t<br>to PGN | to the ND is r | PGN<br>recon        | D pir         | ns. Di | irect   | outp     | ut de  | coup  | oling o | apad | citan  | ce  |

| A10 - D10<br>A11 - D11<br>A12 - D1<br>A4 - A9, B4<br>C4 - C9, D4<br>E1 - E12, F1<br>F7 - F12, G                                    | 0,<br>1,<br>12<br>- B9,<br>- D9,<br>I - F5,<br>G1 -               | VOU   | JT1 | Output from from       | it of the cl<br>he VOUT<br>he V <sub>OUT1</sub> | 1 pins t<br>to PGN | to the ND is r | PGN<br>recon        | D pir         | ns. Di | irect   | outp     | ut de  | coup  | oling o | apad | citan  | ce  |

| A10 - D10<br>A11 - D11<br>A12 - D1<br>A4 - A9, B4<br>C4 - C9, D4<br>E1 - E12, F1<br>F7 - F12, G<br>G12,<br>H1, H2, H4,             | 0,<br>1,<br>12<br>- B9,<br>- D9,<br>I - F5,<br>G1 -               | VOU   | JT1 | Output from from       | it of the cl<br>he VOUT<br>he V <sub>OUT1</sub> | 1 pins t<br>to PGN | to the ND is r | PGN<br>recon        | D pir         | ns. Di | irect   | outp     | ut de  | coup  | oling o | apad | citan  | ce  |

| A10 - D10<br>A11 - D11<br>A12 - D1<br>A4 - A9, B4<br>C4 - C9, D4<br>E1 - E12, F1<br>F7 - F12, G<br>G12,<br>H1, H2, H4,<br>H11, H12 | 0,<br>1,<br>12<br>- B9,<br>- D9,<br>I - F5,<br>G1 -<br>, H9,      | VOU   | JT1 | Output<br>from<br>from | it of the cl<br>he VOUT<br>he V <sub>OUT1</sub> | 1 pins to PGN      | to the ND is r | PGN<br>recor<br>Cor | D pir         | ns. Di | irect   | outp     | ut de  | s pov | oling o | ounc | d plai | ne. |

| A10 - D10<br>A11 - D11<br>A12 - D1<br>A4 - A9, B4<br>C4 - C9, D4<br>E1 - E12, F1<br>F7 - F12, G<br>G12,<br>H1, H2, H4,             | 0,<br>1,<br>12<br>- B9,<br>- D9,<br>I - F5,<br>G1 -<br>, H9,<br>2 | VOU   | JT1 | Output from Ground     | it of the cl<br>he VOUT<br>he V <sub>OUT1</sub> | 1 pins to PGN      | to the ND is r | PGN<br>recor<br>Cor | nnect         | to th  | irect i | plica    | tion's | s pov | ver gr  | ounc | t loa  | ne. |

MxL7204 Data Sheet Pin Information

Table 5: Pin Description (Continued)

| Pin Number     | Pin Name         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J8             | FREQ/<br>PLLFLTR | Frequency Set pin. A 10µA current is sourced from this pin. A resistor from this pin to ground sets a voltage that in turn programs the operating frequency. Alternatively, this pin can be driven with a DC voltage that can set the operating frequency. The nominal frequency is 500kHz although it can be modified as long as the inductor ripple current is kept smaller than 40% to 50% of the output current. $I_{RIPPLE} = \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{L \times f_{SW} \times V_{IN}}$ |

|                |                  | f <sub>SW</sub> is the selected operating frequency and L is the value of the inductor.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| J6, J7, H6, H7 | SGND             | Ground pin for all analog signals and low power circuits. Connect to PGND in one place. See layout guidelines in Figure 30.                                                                                                                                                                                                                                                                                                                                                                                 |

| K6, K7         | VFB2, VFB1       | Feedback input to the negative side of error amplifier for each channel. These pins are internally connected to their respective Vout, each via a precision $60.4 k\Omega$ resistor. The setting of each output voltage can be varied by selecting and adding a feedback resistor from its respective VFB pin to SGND.                                                                                                                                                                                      |

| K5             | TK/SS2           | Output Voltage Tracking pin and Soft-Start pins. Each channel has a 1.25µA pull-up current source. When one channel is configured to be master of the two channels, then a capacitor from this pin to ground will set a soft-start ramp rate. The remaining channel can be set up as the slave, and have the master's                                                                                                                                                                                       |

| K8             | TK/SS1           | output applied through a voltage divider to the slave output's track pin. This voltage divider is equal to the slave output's feedback divider for coincidental tracking.                                                                                                                                                                                                                                                                                                                                   |

| L7             | COMP1            | Current control threshold and error amplifier compensation point for each channel. The current comparator threshold increases with this control voltage.                                                                                                                                                                                                                                                                                                                                                    |

| L6             | COMP2            | The device is internally compensated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| H8             | MODE/<br>PLLIN   | Force Continuous Mode or Pulse-Skipping Mode Selection pin and External Synchronization Input to Phase Detector pin. Connect this pin to SGND to force both channels into forced continuous mode of operation. Connect to $INTV_{CC}$ or float to enable pulse-skipping mode of operation. A clock on the pin will force both channels into continuous mode of operation synchronized to the external clock applied to this pin.                                                                            |

| J9             | RUN1             | Run Control pins. A voltage above 1,25V will turn on each channel in the module. A voltage below 1.25V on the RUN pin will turn off the related channel.                                                                                                                                                                                                                                                                                                                                                    |

| J5             | RUN2             | Each RUN pin has a 1µA pull-up current, once the RUN pin reaches 1.25V an additional 4.5µA pull-up current is added to this pin.                                                                                                                                                                                                                                                                                                                                                                            |

| H10            | SW1              | Switching node of each channel that is used for testing purposes. Also an R-C snubber network can be applied to reduce switch noise or leave floating with a                                                                                                                                                                                                                                                                                                                                                |

| Н3             | SW2              | via to the bottom of the board for probing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| H5             | PGOOD            | Power-good output. This open-drain output is pulled low when Vout is more than ±10% outside of its regulation point.                                                                                                                                                                                                                                                                                                                                                                                        |

| F6             | INTVCC           | Internal 5V Regulator Output. The control circuits and internal gate driver are powered from this voltage. This pin should be decoupled to SGND with a 4.7µF low ESR tantalum or ceramic capacitor. INTVCC is activated when either RUN1 or RUN2 is activated.                                                                                                                                                                                                                                              |

Pin Information MxL7204 Data Sheet

Table 5: Pin Description (Continued)

| Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Name             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

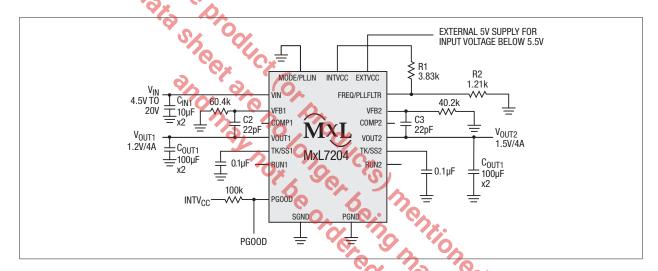

| J4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | EXTVCC               | External power input that is enabled through a switch to INTVCC whenever EXTVCC is greater than 4.7V. Do not exceed 6V on this input, and connect this pin to $V_{IN}$ when operating $V_{IN}$ on 5V. An efficiency increase will occur that is a function of the $(V_{IN}-INTV_{CC})$ multiplied by power MOSFET driver current when the feature is used. $V_{IN}$ must be applied before EXTV $_{CC}$ , and EXTV $_{CC}$ must be removed before $V_{IN}$ . A 5V output can be tied to this pin to increase efficiency. |

| J1 - J3, J10 - J12,<br>K1 - K4, K9 - K12,<br>L1 - L5, L8 - L12,<br>M1 - M12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | VIN                  | IC supply input. Connect input voltage from these pins to PGND. Direct input decoupling capacitance from Vin to PGND is recommended. For $V_{\rm IN}$ < 5.5V, VIN should be connect to INTVCC.                                                                                                                                                                                                                                                                                                                           |

| NOTE:  1. Use test points to monitor  1. Use test points to mo | or signal pin connec | VIN should be connect to INTVCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### NOTE:

Use test points to monitor signal pin connections.

## **Typical Performance Characteristics**

Figure 10: Load Step, CCM, V<sub>OUT</sub> = 1.2V

Figure 12: Load Step, CCM, V<sub>OUT</sub> = 2.5V

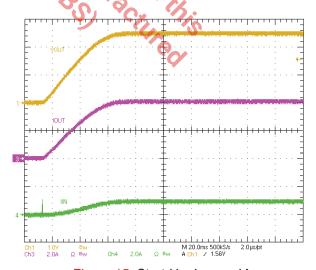

Figure 14: Start-Up, I<sub>OUT</sub> = 0A

Figure 11: Load Step, CCM, V<sub>OUT</sub> = 1.5V

Figure 13: Load Step, CCM, V<sub>OUT</sub> = 3.3V

Figure 15: Start-Up, I<sub>OUT</sub> = 4A

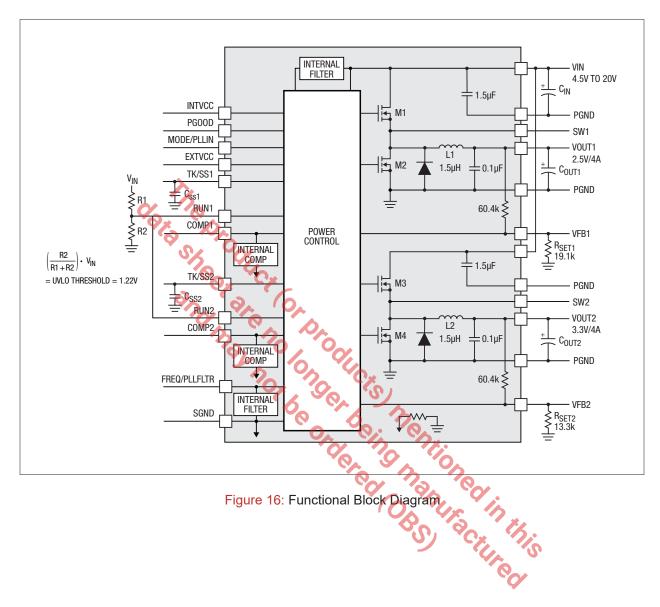

## **Functional Block Diagram**

## **Applications Information**

#### **Power Module Description**

The MxL7204 is a dual-output, standalone, synchronous step-down power module. This power module will have a continuous input voltage range of 4.5V to 20V optimized for 12  $V_{IN}$  conversions. Output currents are up to 4A per channel. The module provides precisely regulated output voltages from 0.6V to 5.0V programmable via a single external resistor. See typical application schematic.

The module employs a constant frequency, peak current mode control loop architecture. With the current mode control and internal feedback loop compensation, the module has sufficient stability margins and good transient performance with a wide range of output capacitors including low ESR ceramic capacitors.

Current mode control provides cycle by cycle fast current limit and the current limit hiccup response in an overcurrent or output short circuit condition. Internal overvoltage and under voltage comparators pull the open drain PGOOD output low if the output voltage exits the ±10% regulation window around the output voltage set point. As the output voltage exceeds the +10% threshold, the low side FET will turn on to clamp the output voltage while keeping the high side MOSFET off. The overvoltage and under voltage detection is feedback pin referred.

The RUN pin enables and disables the respective channel of the module. Pulling RUN pin below 1.1V forces the respective regulator into shutdown mode and turns off both the high side and low side MOSFETs. The TRACK pins are used for programming the output voltage ramp and voltage tracking during start-up.

The typical switching frequency is 780kHz. The switching frequency can be programmed from 250kHz to 780kHz using the external programming resistor. For noise sensitive applications, the module can be synchronized to an external clock.

High efficiency at light loads is accomplished via the pulse-skip mode of operation using the MODE/PLLIN pin that accommodates battery operation to extend battery life.

The EXTVCC pin allows an external 5V supply to power the module and reduce the power dissipation in the internal 5V LDO. The EXTVCC has a threshold of 4.7V for activation and a max rating of 6V and must sequence on after  $V_{IN}$  and sequence off before  $V_{IN}$ .

#### **Typical Application Circuit**

The typical MxL7204 application circuit is shown in Figure 1. External component selection is primarily determined by the maximum load current and output voltage.

#### V<sub>IN</sub> to V<sub>OUT</sub> Step-Down Ratios

There are restrictions in the maximum  $V_{\text{IN}}$  and  $V_{\text{OUT}}$  stepdown ratio that can be achieved for a given input voltage.

Each output of the MxL7204 is capable of 95% duty cycle at 500kHz, but the  $V_{IN}$  to  $V_{OUT}$  minimum dropout is still shown as a function of its load current and will limit output current capability related to high duty cycle on the top side switch. Minimum on-time  $t_{ON(MIN)}$  is another consideration in operating at a specified duty cycle while operating at a certain frequency due to the fact that  $t_{ON(MIN)} < D/f_{SW}$ , where D is duty cycle and  $f_{SW}$  is the switching frequency.  $t_{ON(MIN)}$  is specified in the electrical parameters as 90ns.

#### **Output Voltage Programming**

The PWM controller has an internal 0.6V reference voltage. As shown in the Block Diagram, a  $60.4k\Omega$  internal feedback resistor connects between the VOUT1 to VFB1 and VOUT2 to VFB2. Adding a resistor R<sub>SETx</sub> from VFB pin to SGND programs the output voltage:

$$V_{OUT} = 0.6 V \; x \; \frac{60.4 k \, + \, R_{SETx}}{R_{SETx}} \qquad , \; \; R_{SETx} = \; \frac{60.4 k \; x \; 0.6 V}{V_{OUT} - 0.6 V} \label{eq:Vout}$$

Table 6: VFB Resistor Table vs Various Output Voltages

| $V_{OUT}$         | 0.6V | 1.0V  | 1.2V  | 1.5V  | 1.8V  | 2.5V  | 3.3V  | 5V    |

|-------------------|------|-------|-------|-------|-------|-------|-------|-------|

| R <sub>SETx</sub> | Open | 90.9k | 60.4k | 40.2k | 30.1k | 19.1k | 13.3k | 8.25k |

Note that when used in paralleled output mode (see Figure 33 for 5V example), the internal  $60.4k\Omega$  feedback resistor of both VOUT are in parallel. Therefore the following equations and table should be used for this mode.

$$V_{OUT} = 0.6V \text{ x} \frac{30.2k + R_{SET}}{R_{SET}}$$

,  $R_{SET} = \frac{30.2k \times 0.6V}{V_{OUT} - 0.6V}$

Table 7: VFB Resistor Table vs Various Output Voltages for Paralleled Output Mode

|                  |      |       |       |       | 1.8V  |       |       |       |

|------------------|------|-------|-------|-------|-------|-------|-------|-------|

| R <sub>SET</sub> | Open | 45.3k | 30.1k | 20.0k | 15.0k | 9.53k | 6.65k | 4.12k |

#### **Input Capacitors**

The MxL7204 module should be connected to a low AC impedance DC source. For the regulator input, two 22µF input ceramic capacitors are used for RMS ripple current.

A  $47\mu F$  to  $150\mu F$  surface mount aluminum electrolytic bulk capacitor can be used for more input bulk capacitance.

### **Output Capacitors**

The MxL7204 is designed for low output voltage ripple noise and good transient response. The bulk output capacitors defined as  $C_{OUT}$  are chosen with low enough effective series resistance (ESR) to meet the output voltage ripple and transient requirements.  $C_{OUT}$  can be a low ESR tantalum capacitor, the low ESR polymer capacitor or ceramic capacitor. The typical output capacitance range for each output is from  $100\mu F$  to  $220\mu F$ .

### Pulse-Skipping Mode Operation

In applications where low output ripple and high efficiency at intermediate currents are desired, pulse-skipping mode should be used. Pulse-skipping operation allows the MxL7204 to skip cycles at low output loads, thus increasing efficiency by reducing switching loss. Tying the MODE/PLLIN pin to INTVCC enables pulse-skipping operation.

#### **Forced Continuous Operation**

In applications where fixed frequency operation is more critical than low current efficiency, and where the lowest output ripple is desired, forced Continuous Conduction Mode (CCM) should be used. Forced continuous operation can be enabled by tying the MODE/PLLIN pin to GND.

#### **Multiphase Operation**

A multiphase power supply significantly reduces the amount of ripple current in both the input and output capacitors. The RMS input ripple current is reduced by, and the effective ripple frequency is multiplied by, the number of phases used (assuming that the input voltage is greater than the number of phases used times the output voltage). The output ripple amplitude is also reduced by the number of phases used when all of the outputs are tied together to achieve a single high output current design. Figure 33 is an example of a two phase application.

#### Input RMS Ripple Current Cancellation

The input RMS ripple current cancellation effects of multi-phased interleaved operation are presented, and a graph is displayed representing the RMS ripple current reduction as a function of the number of interleaved phases as shown in Figure 17.

Figure 17: Normalized Input RMS Ripple Current vs Duty Cycle for One to Four Phases

#### Frequency Selection and Phase-Lock Loop (MODE/PLLIN and fSET Pins)

The MxL7204 device is operated over a range of frequencies to improve power conversion efficiency. It is recommended to operate the lower output voltages or lower duty cycle conversions at lower frequencies to improve efficiency by lowering power MOSFET switching losses. Higher output voltages or higher duty cycle conversions can be operated at higher frequencies to limit inductor ripple current. The efficiency graphs will show an operating frequency chosen for that condition. Select frequency in reference to the highest output voltage.

Figure 18: Operation Frequency vs. FREQ/PLLFLTR Pin Voltage

The MxL7204 switching frequency can be set with an external resistor from the FREQ/PLLFLTR pin to SGND. An accurate 10µA current source into the resistor will set a voltage that programs the frequency or a DC voltage can be applied. Figure 18 shows a graph of frequency setting versus programming voltage. An external clock can be applied to the MODE/PLLIN pin from 0V to INTV<sub>CC</sub> over a frequency range of 400kHz to 780kHz. The clock input high threshold is 1.6V and the clock input low threshold is 1V. The MxL7204 has the PLL loop filter components on board. The frequency setting resistor should always be present to set the initial switching frequency before locking to an external clock. Both regulators will operate in continuous mode while being synchronized to an externally clock signal.

The output of the PLL phase detector has a pair of complementary current sources that charge and discharge the internal filter network. When the external clock is applied, then the FREQ/PLLFLTR frequency resistor is disconnected with an internal switch and the current sources control the frequency adjustment to lock to the incoming external clock. When no external clock is applied, then the internal switch is on, thus connecting the external FREQ/PLLFLTR frequency set resistor for free run operation.

#### Minimum On-Time

Minimum on-time  $t_{ON}$  is the smallest time duration that the MxL7204 is capable of turning on the top MOSFET on either channel. Low duty cycle applications may approach this minimum on-time limit and care should be taken to ensure that:

$$\frac{V_{OUT}}{V_{IN} x FREQ} > t_{ON(MIN)}$$

If the duty cycle falls below what can be accommodated by the minimum on-time, the controller will begin to skip cycles. The output voltage will continue to be regulated, but the output ripple will increase. The on-time can be increased by lowering the switching frequency. A good rule of thumb is to keep on-time longer than 110ns.

### Output Voltage Tracking