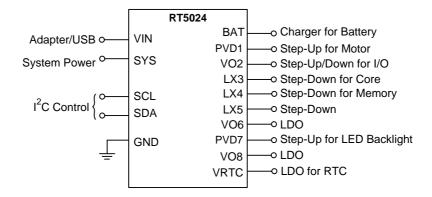

# I<sup>2</sup>C Programmable Multi-Channel PMU with Battery Charger for CMOS DSC/DV

### **General Description**

The RT5024 is a complete power supply solution for digital still cameras and other hand held devices. The RT5024 is composed of multi-channel DC-DC power converter unit, a single-cell linear Li+ ion battery charger, a charger type detector, and an I<sup>2</sup>C control interface.

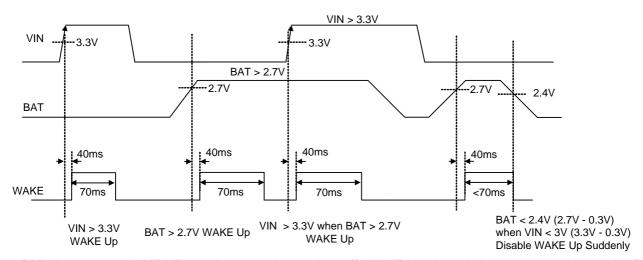

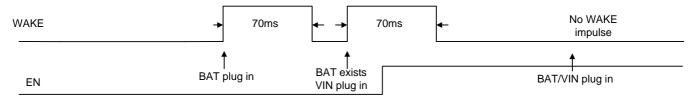

The power converter unit includes one synchronous step-up converter (CH1), one synchronous step-up/down converter (CH2), three synchronous step-down converters (CH3/4/5), two LDOs with input power as low as 1.5V (CH6/8), one WLED driver in synchronous high-voltage step-up mode or low-voltage current regulator mode (CH7), and a keep-alive LDO (CH9) for RTC application. All converters are internally frequency compensated and integrate power MOSFETs. The power converter unit provides complete protection functions: over current, thermal shutdown, over voltage and under voltage protection. The RT5024 has a WAKEUP impulse generation circuitry to monitor VIN or BAT installation event. To fulfill most of applications, the RT5024 has six preset power on/off sequences.

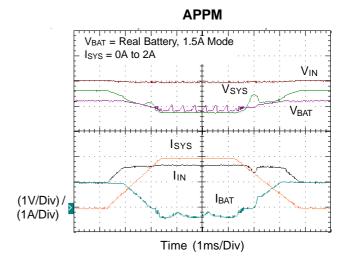

The battery charger includes Auto Power Path Management (APPM). No external MOSFETs are required. The charger can enter sleep mode when power is removed.

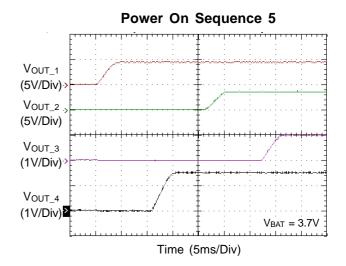

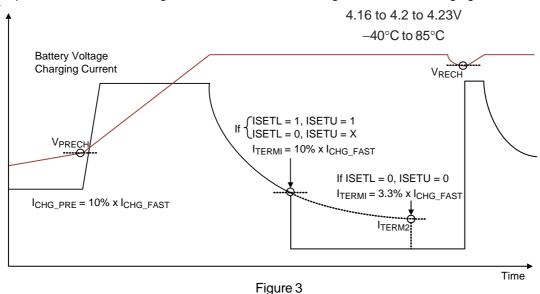

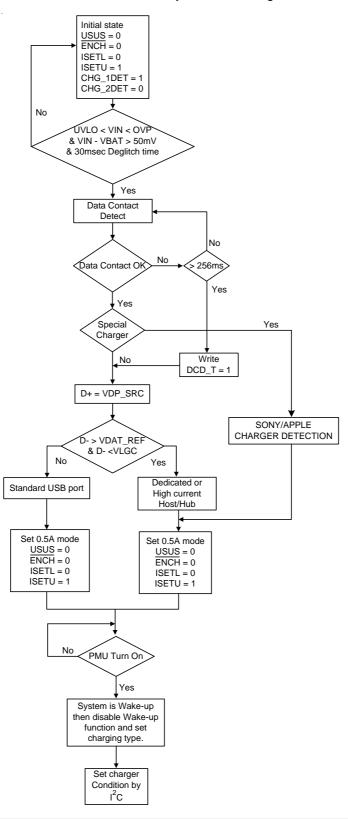

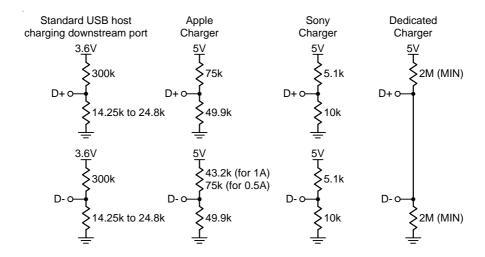

Charging tasks are optimized by using a control algorithm to vary the charge rate, including pre-charge mode, fast charge mode and constant voltage mode. The charge current can also be programmed by the I<sup>2</sup>C control interface. The battery regulation voltage and current can be adjusted by JEITA standard temperature control or other schemes set by the I<sup>2</sup>C interface. The internal thermal feedback circuitry regulates the die temperature to optimize the charge rate for all ambient temperatures. The charging task will always be terminated in constant voltage mode when the charging current reduces to the termination current of 10% x I<sub>CHG</sub> FAST. The charger includes under voltage and over voltage protection for the supply input voltage, VIN. The charger includes USB charger detection circuitry via D+ and D- pins of USB interface to detect USB Standard Downstream Ports (SDP), USB Charging Downstream Port (CDP), Dedicated Charger Port (DCP), or Apple/Sony charger ports. The RT5024 uses some indicators to show charger states: one open drain port CHG (charger status), and an interrupt (INT) to immediately notify the state change.

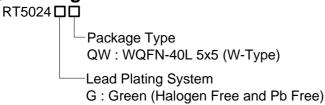

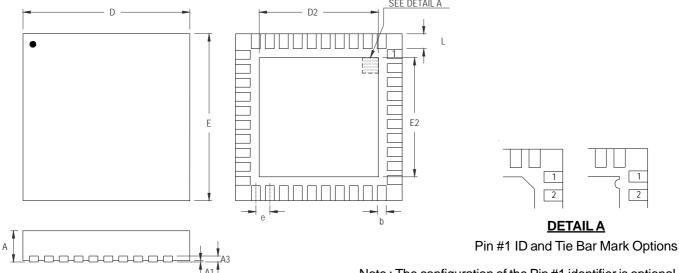

The RT5024 is available in the WQFN-40L 5x5 package.

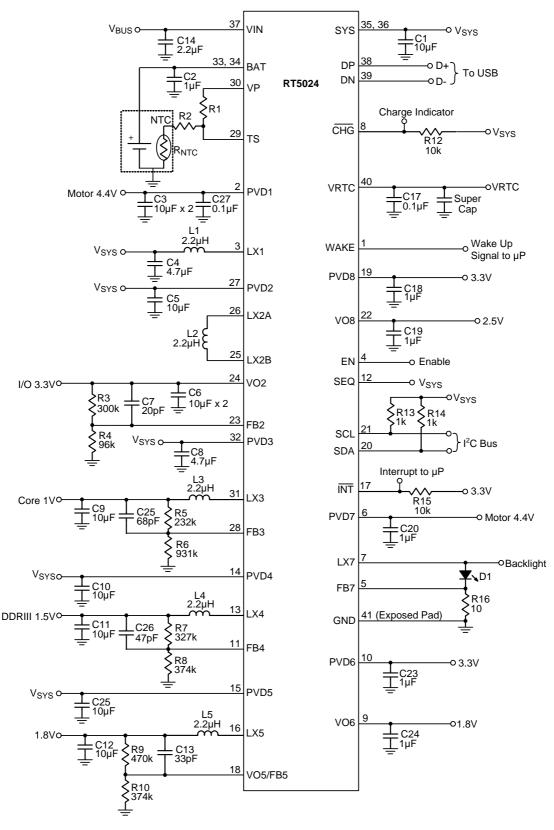

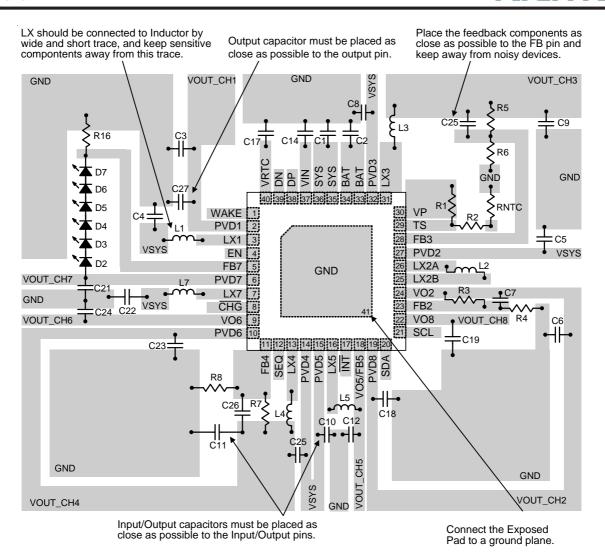

### **Simplified Application Circuit**

Copyright ©2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

### **Features**

#### **Power Converter Unit**

- CH1 LV Sync Step-Up

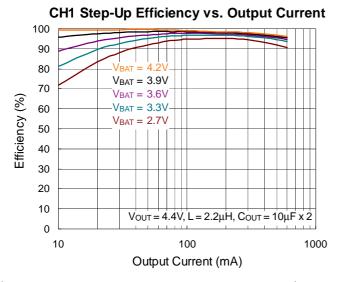

- ► Support Up to 1A Loading, DVS (Dynamic Voltage Scaling), Load-Disconnect, Up to 95% Efficiency, PSM/PWM Selectable

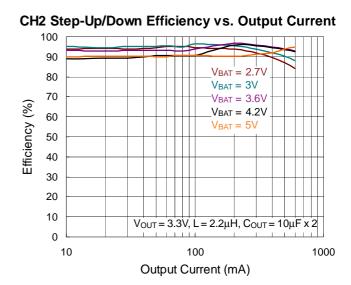

- CH2 LV Sync Step-Up/Down

- ▶ Support Up to 1A Loading, DVS, Up to 95% Efficiency, PSM/PWM Selectable

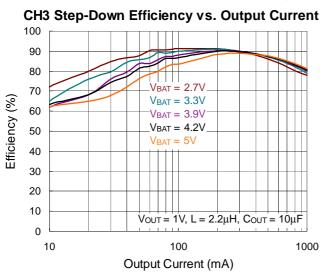

- CH3/4 LV Sync Step-Down

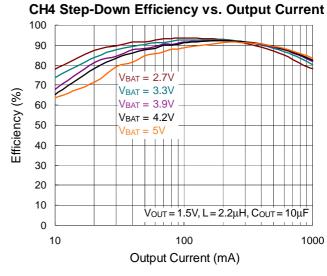

- ► Support Up to 1.3A Loading, DVS, Up to 95% Efficiency, 100% (max) Duty Cycle, PSM/PWM Selectable

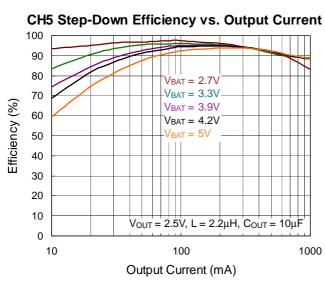

- CH5 LV Sync Step-Down

- Support Up to 0.6A Loading, Up to 95% Efficiency, 100% (max) Duty Cycle

- Output Voltage can be Selected from Preset List or Set by External Feedback Network.

- CH6 Low Input Power LDO

- ▶ VIN Range 1.5V to 5.5V

- ▶ Output Voltage Level Selectable in I<sup>2</sup>C Register

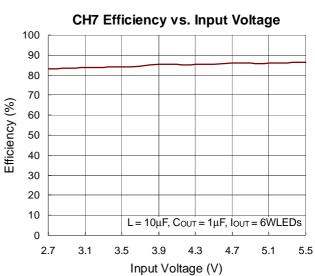

- CH7 WLED Driver in Either Sync Step-Up Operation or Current Regulator Operation

- Step-Up Mode with LED Open Protection (OVP7 16V or 25V, Selectable in I<sup>2</sup>C Register)

- ▶ Step-Up Mode Support Series 2 to 6 WLED and Load Disconnect Function

- **▶ Current Regulator Mode for 1 WLED**

- ▶ 31 WLED Dimming Levels

- Automatic Mode Selection by External Circuit Topology

- CH8 Generic LDO

- ▶ VIN Range 1.5V to 5.5V

- ▶ Output Voltage Level Selectable in I<sup>2</sup>C Register

- CH9 Low Quiescent LDO with Reverse Leakage Prevention for RTC Power Supply

- ▶ Fixed 3.25V Output

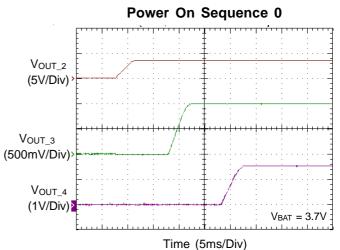

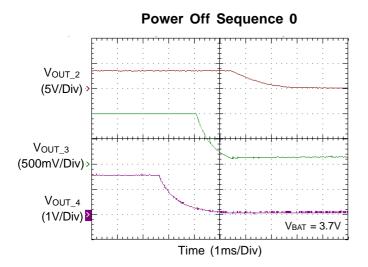

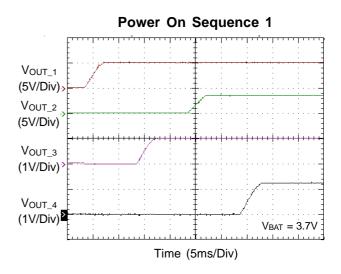

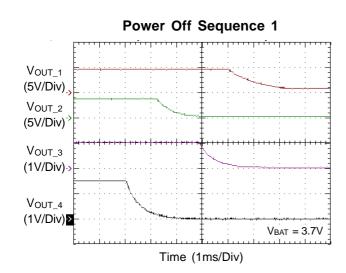

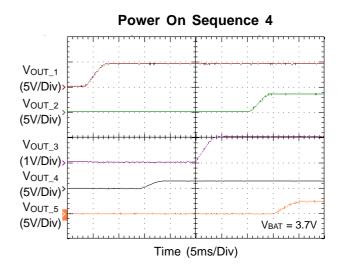

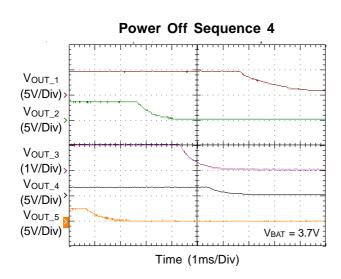

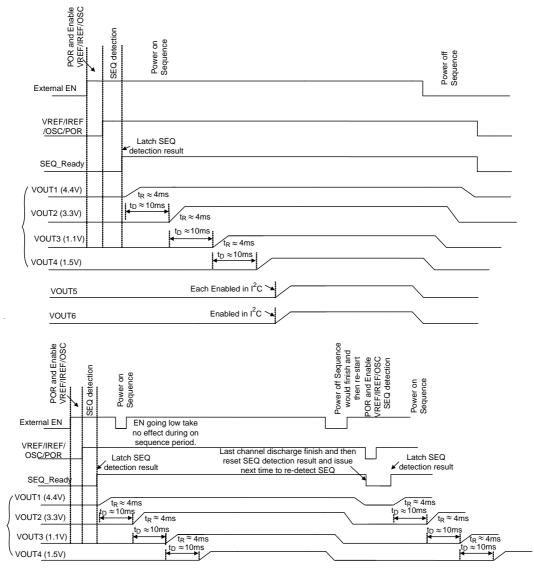

- Six Preset Power On/Off Sequences by One Pin SEQ

- ▶ SEQ # 0 : CH2→CH3→CH4

- ► SEQ #1: CH1→CH3→CH2→CH4

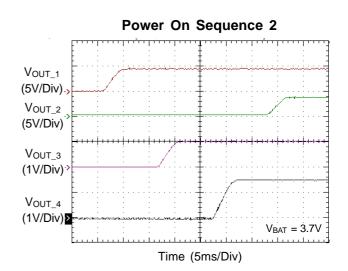

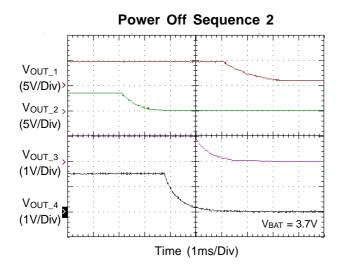

- ightharpoonup SEQ # 2 : CH1ightharpoonup CH3ightharpoonup CH4ightharpoonup CH2

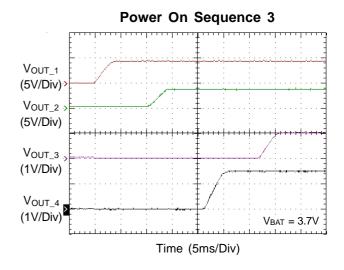

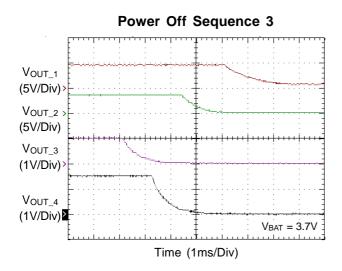

- ► SEQ # 3 : CH1→CH2→CH4→CH3

- ► SEQ # 4 : CH1→CH4→CH3→CH2→CH5

- ► SEQ # 5 : CH1→CH4→CH2→CH3

- All Power Switches Integrated with Internal Compensation

- Discharge Output of Every Channels when Turning Off

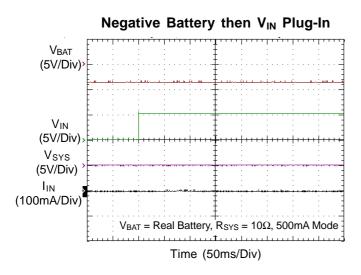

- Wake Up Impulse to Monitor BAT and VIN Plug-In

- Fixed 2MHz Switching Frequency for CH1/3/4/5,

Fixed 1MHz Switching Frequency for CH2/7

### **Charger Unit**

- 28V Maximum Rating for VIN Power

- Selectable Power Input Current Limit (0.1A / 0.5A / 1A / 1.5A)

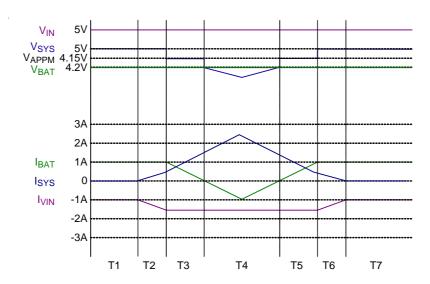

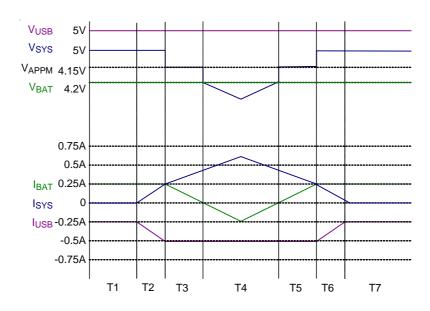

- Auto Power Path Management (APPM) with Integrated Power MOSFETs

- Battery Charging Current Control and Regulation

Voltage Control

- Programmable Charging Current and Safe Charge Timer

- Optimized Charge Rate via Thermal Feedback

- Under Voltage Protection, Over Voltage Protection

- Charger Status Indicator

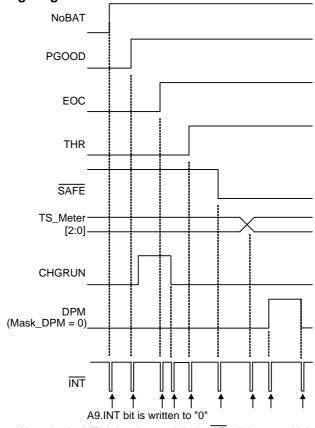

- Interrupt Indicator to JEITA Temperature/Fault/ Status Events when PMU is Enabled

- ▶ Battery Temperature Events

- ▶ Battery Removing Event

- ▶ Charger in Thermal Regulation Control

- **▶** Safety Timer Timeout

- ▶ End of Charging

- **▶ VIN Power Good**

- ▶ VIN < DPM Threshold 4.35V</p>

- **▶** Charger Type Detection Finishing

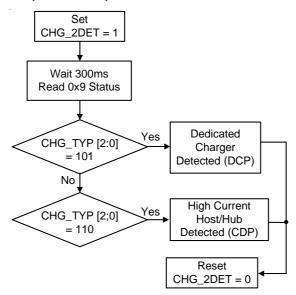

- Charger Type Detection

- Dedicated Charger : Support Apple and Sony Charger

- ▶ Secondary Charger Detection to Distinguish CDP and DCP

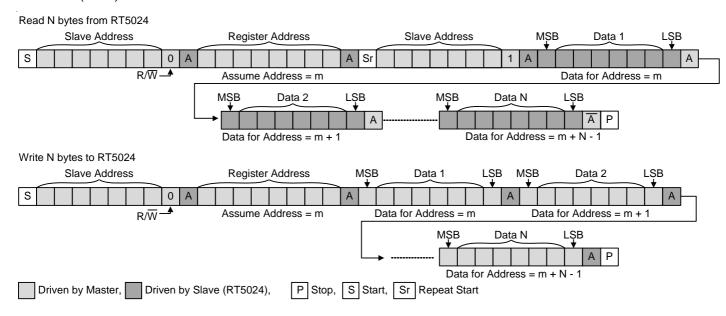

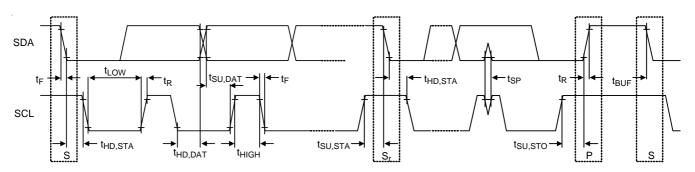

- I<sup>2</sup>C Control Interface : Support Fast Mode up to 400kb/s

- Small 40-Lead WQFN 5x5 Package

- RoHS Compliant and Halogen Free

### **Applications**

- DSC Power Supply System

- CMOS-Sensor DV

- Portable Instruments

### **Ordering Information**

#### Note:

Richtek products are:

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

### **Marking Information**

RT5024 GQW YMDNN RT5024GQW : Product Number

YMDNN: Date Code

### **Pin Configuration**

(TOP VIEW) ۷P WAKE PVD1 TS FB3 LX1 PVD2 ΕN FB7 LX2A **GND** PVD7 LX2B LX7 VO2 CHG FB2 VO<sub>6</sub> VO8 PVD6 SCL

WQFN-40L 5x5

### **Functional Pin Description**

| Pin No. | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                             |

|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | WAKE     | Wake-Up Impulse Push Pull Output. If VIN or BAT plug in, WAKE pin generates one 90ms width high pulse to notify micro processor.                                                                                                                                                                                                         |

| 2       | PVD1     | Power Output of CH1. To make CH1 stable, the power path from the pin PVD1 to its output capacitors must be as short ( $\leq$ 1mm is better) and wide as possible to reduce its parasitic inductance. The output capacitor must be ceramic capacitor ( $\geq$ 20 $\mu$ F).                                                                |

| 3       | LX1      | Switch Node of CH1.                                                                                                                                                                                                                                                                                                                      |

| 4       | EN       | Enable Control Input of Power Converter.                                                                                                                                                                                                                                                                                                 |

| 5       | FB7      | Feedback Input of CH7 in Step-Up Mode or Current Regulator Mode.                                                                                                                                                                                                                                                                         |

| 6       | PVD7     | Power Output of CH7 in Step-up or Power input pin of CH7 in current regulator mode.                                                                                                                                                                                                                                                      |

| 7       | LX7      | Switch Node of CH7 in Step-Up Mode.  LX7 initial voltage determine CH7 operation mode.                                                                                                                                                                                                                                                   |

| 8       | CHG      | Charger Status Output. Open-drain port.                                                                                                                                                                                                                                                                                                  |

| 9       | VO6      | Power Output of CH6.                                                                                                                                                                                                                                                                                                                     |

| 10      | PVD6     | Power Input of CH6.                                                                                                                                                                                                                                                                                                                      |

| 11      | FB4      | Feedback Input of CH4.                                                                                                                                                                                                                                                                                                                   |

| 12      | SEQ      | Power Sequence Selection for CH1 to CH4. SEQ #4 included CH5.                                                                                                                                                                                                                                                                            |

| 13      | LX4      | Switch Node of CH4.                                                                                                                                                                                                                                                                                                                      |

| 14      | PVD4     | Power Input of CH4.                                                                                                                                                                                                                                                                                                                      |

| 15      | PVD5     | Power Input of CH5.                                                                                                                                                                                                                                                                                                                      |

| 16      | LX5      | Switch Node of CH5.                                                                                                                                                                                                                                                                                                                      |

| 17      | ĪNT      | Interrupt Indicator Open Drain Output. If events of NoBAT, THR, EOC, Battery Temperature Change (TS_METER), PGOOD, SAFE, VIN DPM, or Charge Type Detection Finishing (CHGRUN) happen, the output INT goes low and the INT bit in I <sup>2</sup> C register bank 0x9 is set to be "1". After INT bit is written to be "0", INT goes high. |

| 18      | VO5/FB5  | Output Voltage Sense or Feedback Network Input of CH5. The function is selected by I <sup>2</sup> C register.                                                                                                                                                                                                                            |

| 19      | PVD8     | Power Input of CH8.                                                                                                                                                                                                                                                                                                                      |

| 20      | SDA      | Data Signal of I <sup>2</sup> C Interface.                                                                                                                                                                                                                                                                                               |

| 21      | SCL      | Clock Signal of I <sup>2</sup> C Interface.                                                                                                                                                                                                                                                                                              |

| 22      | VO8      | Power Output of CH8.                                                                                                                                                                                                                                                                                                                     |

| 23      | FB2      | Feedback Input Pin of CH2.                                                                                                                                                                                                                                                                                                               |

| 24      | VO2      | Power Output of CH2.                                                                                                                                                                                                                                                                                                                     |

| 25      | LX2B     | Switch Node B of CH2.                                                                                                                                                                                                                                                                                                                    |

| 26      | LX2A     | Switch Node A of CH2.                                                                                                                                                                                                                                                                                                                    |

| 27      | PVD2     | Power Input of CH2.                                                                                                                                                                                                                                                                                                                      |

| 28      | FB3      | Feedback Input of CH3.                                                                                                                                                                                                                                                                                                                   |

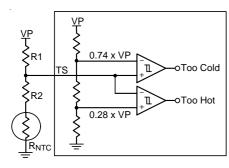

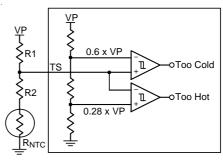

| 29      | TS       | Temperature Sense Input. The TS pin connects to a battery's thermistor to determine if the battery is too hot or too cold to charge. If the battery's temperature is out of range, charging is paused until it re-enters the valid range. TS also detects whether the battery (with NTC) is present or not.                              |

| Pin No.          | Pin Name | Pin Function                                                                                                 |

|------------------|----------|--------------------------------------------------------------------------------------------------------------|

| 30               | VP       | Power Output Pin of 3.3V Buffer for Battery Temperature Sensing.                                             |

| 31               | LX3      | Switch Node of CH3.                                                                                          |

| 32               | PVD3     | Power Input Pin of CH3.                                                                                      |

| 33, 34           | BAT      | Charger Output for Battery.                                                                                  |

| 35, 36           | SYS      | Power Output for System. Connect this pin to System with a minimum $10\mu\text{F}$ ceramic capacitor to GND. |

| 37               | VIN      | Supply Voltage Input.                                                                                        |

| 38               | DP       | USB D+ Input for Charger Type Detection.                                                                     |

| 39               | DN       | USB D- Input for Charger Type Detection.                                                                     |

| 40               | VRTC     | RTC LDO Power Output Pin.                                                                                    |

| 41 (Exposed pad) | GND      | Exposed PAD Should be Soldered to PCB and Connected to GND.                                                  |

Copyright ©2021 Richtek Technology Corporation. All rights reserved.

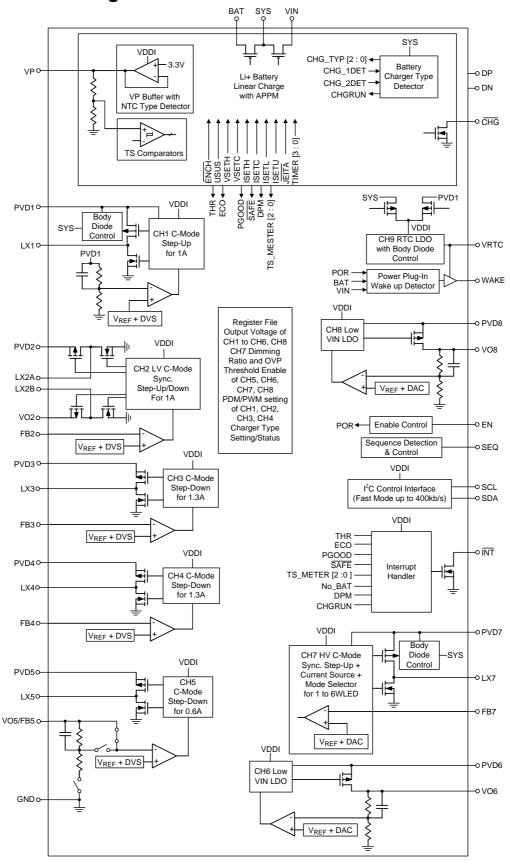

### **Functional Block Diagram**

### **Operation**

The RT5024 is an integrated power solution for digital still cameras and other small handheld devices. It includes six DC-DC converters, a WLED driver, a RTC LDO and a fully integrated single-cell Li-ion battery charger.

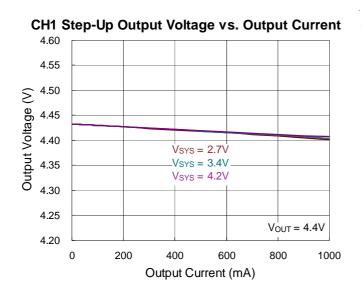

### CH1: Step-Up DC-DC Converter

CH1 is a step-up converter for motor driver power. The converter operates at PFM or PWM current mode which can be set by I<sup>2</sup>C interface.

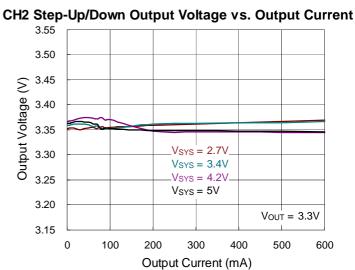

### CH2: Step-Up/Down DC-DC Converter

CH2 is a step-up/down converter for I/O power. The converter operates at PFM or PWM current mode which can be set by I<sup>2</sup>C interface.

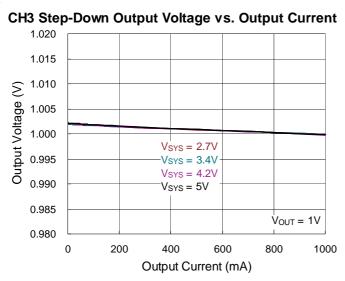

### CH3: Step-Down DC-DC Converter

CH3 is a step-down converter for core power. The converter operates at PFM or PWM current mode which can be set by I<sup>2</sup>C interface.

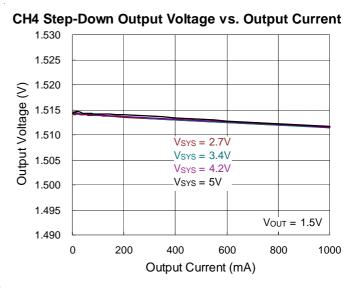

### CH4: Step-Down DC-DC Converter

CH4 is a step-down converter for memory power. The converter operates at PFM or PWM current mode which can be set by I<sup>2</sup>C interface.

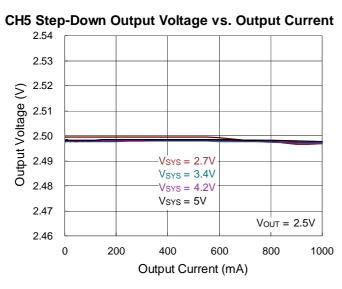

#### CH5: Step-Down DC-DC Converter

CH5 is a step-down converter. The converter operates at PFM/PWM current mode.

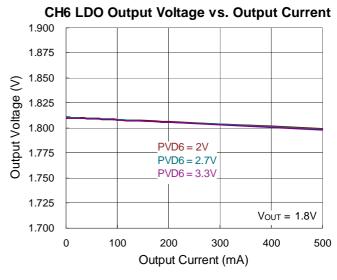

### CH6: Generic LDO

CH6 is a generic low voltage LDO for multiple purpose power.

#### CH7: WLED Driver

CH7 is a WLED driver that can operate in either current source mode or synchronous step-up mode which is determined by I<sup>2</sup>C interface control signal.

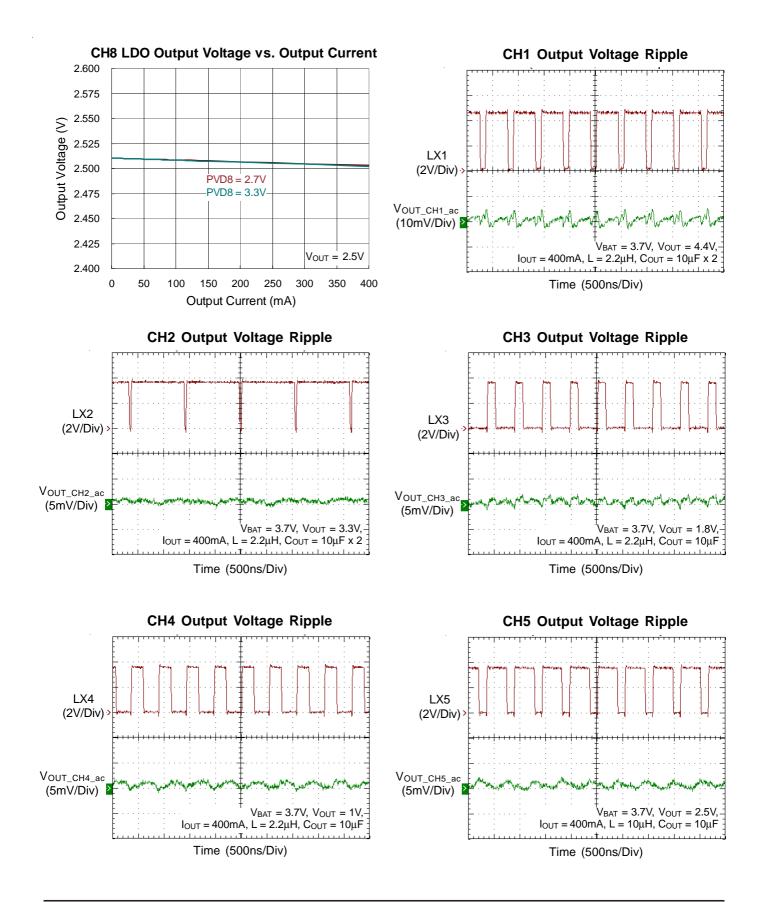

#### CH8: Generic LDO

CH8 is a generic low voltage LDO for multiple purpose power.

#### CH9: Keep Alive LDO and RTC

CH9 is a LDO providing a 3.25V output for real time clock.

#### **Charger Unit**

A Li-ion battery charger with automatic power path management is designed to operate in below modes.

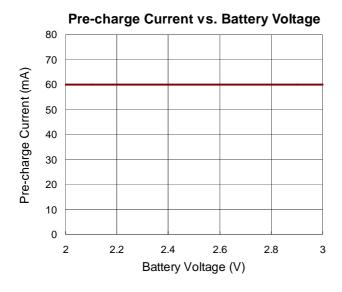

### **Pre-Charge Mode**

When the output voltage is lower than 2.8V, the charging current will be reduced to a ratio of fast-charge current set by A8.ISETA [3:0] to protect the battery life-time.

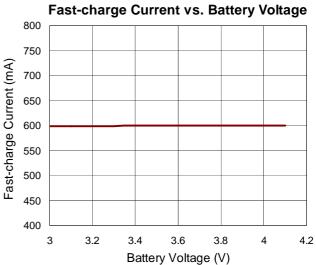

### **Fast-Charge Mode**

When the output voltage is higher than 3V, the charging current will be equal to the fast-charge current set by A8.ISETA [3:0].

### **Constant Voltage Mode**

When the output voltage is near 4.2V and the charging current falls below the termination current for a <u>deglitch</u> time of 25ms, the charger will be turned off and CHG will go to high.

### Re-Charge Mode

When the chip is in charge termination mode, the charging current gradually goes down to zero. Once the battery voltage drops to below 4.1V for 100ms, the charger will resume charging operation.

Copyright ©2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

| Absolute Maximum Ratings (Note 1 | 1) |

|----------------------------------|----|

|----------------------------------|----|

| • Supply Voltage, SYS                                                       | 0.3V to 6V     |

|-----------------------------------------------------------------------------|----------------|

| Supply Input Voltage, VIN                                                   | 0.3V to 28V    |

| • Switch Node Voltage, LX1, LX2, LX3, LX4, LX5                              | 0.3V to 6V     |

| • PVD7, LX7                                                                 | 0.3V to 25V    |

| • CHG                                                                       | 0.3V to 28V    |

| • Other Pins                                                                | 0.3V to 6V     |

| • INT, CHG Continuous Current                                               | - 20mA         |

| BAT Continuous Current (Total in two pins)                                  | - 2.5A         |

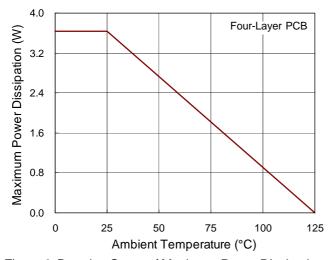

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                |

| WQFN-40L 5x5                                                                | - 3.64W        |

| Package Thermal Resistance (Note 2)                                         |                |

| WQFN-40L 5x5, $\theta_{JA}$                                                 | - 27.5°C/W     |

| WQFN-40L 5x5, $\theta_{JC}$                                                 |                |

| Junction Temperature                                                        |                |

| Lead Temperature (Soldering, 10 sec.)                                       |                |

| Storage Temperature Range                                                   | 65°C to 125°C  |

| ESD Susceptibility (Note 3)                                                 |                |

| HBM (Human Body Model)                                                      |                |

| MM (Machine Model)                                                          | - 200V         |

| Recommended Operating Conditions (Note 4)                                   |                |

| Supply Input Voltage, BAT                                                   | - 1.8V to 5.5V |

| • Supply Input Voltage Range, VIN (A7.ISETL = 1)                            | - 4.4V to 6V   |

| • Supply Input Voltage Range, VIN (A7.ISETL = 0)                            | - 4.5V to 6V   |

| Junction Temperature Range                                                  | 40°C to 125°C  |

### **Electrical Characteristics**

**Power Converter Unit:**

( $V_{SYS} = 3.3V$ ,  $T_A = 25$ °C, unless otherwise specified)

| Parameter                                            | Symbol           | Test Conditions                                      | Min  | Тур   | Max  | Unit |

|------------------------------------------------------|------------------|------------------------------------------------------|------|-------|------|------|

| Supply Voltage                                       |                  |                                                      |      |       |      |      |

| PMU Startup Voltage at SYS                           | V <sub>ST</sub>  | For bootstrap                                        | 2.4  |       |      | V    |

| SYS Operating Voltage for PMU                        | V <sub>SYS</sub> |                                                      | 2.7  |       | 5.5  | V    |

| VDDI Over Voltage Protection (OVP) (Hysteresis High) |                  |                                                      | 5.82 | 6     | 6.18 | V    |

| VDDI OVP Hysteresis (Gap)                            |                  |                                                      |      | -0.25 | -    | V    |

| VDDI UVLO (Hysteresis High)                          |                  | VDDI UVLO takes effect once<br>CH2 soft-start finish | 2.2  | 2.4   | 2.6  | V    |

| VDDI UVLO Hysteresis (Gap)                           |                  |                                                      |      | -0.3  |      | V    |

• Ambient Temperature Range ----- --- -40°C to 85°C

| Parameter                                                              | Symbol                  | Test Conditions                                  | Min   | Тур             | Max   | Unit  |

|------------------------------------------------------------------------|-------------------------|--------------------------------------------------|-------|-----------------|-------|-------|

| Supply Current                                                         | •                       |                                                  |       | •               |       |       |

| Shutdown Supply Current into BAT (Include I <sub>DDQ</sub> of RTC LDO) | I <sub>OFF-BAT</sub>    | EN = L, and PMU off,<br>BAT = 4.2V               |       | 10              | 20    | μΑ    |

| CH1 + CH2 + CH3 + CH4 Supply<br>Current                                | I <sub>Q1234</sub>      | Non switching, EN = 3.3V                         |       |                 | 2000  | μΑ    |

| CH5 Supply Current                                                     | $I_{Q5}$                | Non switching, A2.EN5 = 1                        |       |                 | 500   | μΑ    |

| CH6 Supply Current                                                     | I <sub>Q6</sub>         | A2.EN6 = 1                                       |       |                 | 100   | μА    |

| CH7 in Step-Up Mode Supply<br>Current                                  | I <sub>Q7b</sub>        | Non switching,<br>A2.EN7_DIM7 [4 : 0] = 5'b11111 |       |                 | 500   | μΑ    |

| CH7 in Current Source mode Supply Current                              | I <sub>Q7c</sub>        | A2.EN7_DIM7 [4 : 0] = 5'b11111<br>PVD7 = 5V      | 1     |                 | 400   | μΑ    |

| CH8 Supply Current                                                     | I <sub>Q8</sub>         | A2.EN8 = 1                                       |       |                 | 100   | μΑ    |

| Oscillator                                                             |                         |                                                  |       |                 |       |       |

| CH1, 3, 4, 5 Operation Frequency                                       | f <sub>OSC_1345</sub>   |                                                  | 1800  | 2000            | 2200  | kHz   |

| CH2, 7 Operation Frequency                                             | f <sub>OSC_27</sub>     | CH7 in Step-Up mode                              | 900   | 1000            | 1100  | kHz   |

| CH1 LV Sync Step-Up                                                    |                         |                                                  |       |                 |       |       |

| Output Voltage Accuracy at PVD1                                        |                         | Target voltage defined at A4.VOUT1 [3:0]         | -1.5  |                 | 1.5   | %     |

| Minimum On-Time for PSM                                                |                         |                                                  | -     | 100             |       | ns    |

| Soft-Start Time                                                        |                         | PVD1 = 0 to 5V                                   |       | 4               |       | ms    |

| Maximum Duty Cycle (Step-Up)                                           |                         | PVD1 < Target defined in A4.VOUT1 [3:0]          | 80    | 83              | 86    | %     |

|                                                                        | R <sub>DS(ON)_P</sub>   | P-MOSFET, PVD1 = 3.3V                            |       | 200             | 300   |       |

| On Resistance of MOSFET                                                | R <sub>DS(ON)_N</sub>   | N-MOSFET, PVD1 = 3.3V                            | -     | 150             | 250   | mΩ    |

| Current Limitation (Step-Up)                                           | I <sub>LIM_1</sub>      |                                                  | 2.2   | 3               | 4     | Α     |

| Over Voltage Protection at PVD1                                        |                         |                                                  | 5.82  | 6               | 6.18  | V     |

| Under Voltage Protection -1 at PVD1                                    |                         |                                                  | 1     | SYS<br>- 0.8    |       | ٧     |

| Under Voltage Protection -2 at PVD1                                    |                         | Target Voltage is defined in A4.VOUT1 [3:0]      |       | Target<br>x 0.5 |       | ٧     |

| Over Load Protection at PVD1                                           |                         | Target Voltage is defined in A4.VOUT1 [3:0]      |       | Target<br>- 0.6 |       | V     |

| Off Discharge Current at PVD1                                          |                         | PVD1 = 5V, SYS = 3.3V                            |       | 20              |       | mA    |

| Discharge Finishing Threshold at PVD1                                  |                         |                                                  |       | 0.6             |       | V     |

| CH2 LV Sync Step-Up/Down                                               | _                       |                                                  |       |                 |       |       |

| Feedback Regulation Voltage at FB2                                     |                         | A4.FB2 [2:0] = 3'b100                            | 0.788 | 0.8             | 0.812 | V     |

| Soft-Start Time                                                        |                         | FB2 = 0 to 0.8V                                  |       | 4               |       | ms    |

| Maximum Duty Cycle                                                     |                         | LX2B                                             |       | 55              |       | %     |

| Maximum Daty Cycle                                                     |                         | LX2A                                             |       |                 | 100   | /0    |

| On Resistance of MOSFET                                                | R <sub>DS</sub> (ON)_2A | LX2A – GND, N-MOSFET<br>PVD2 = 3.3V              |       | 200             | 300   | mΩ    |

| CHROSICIATION OF WOOD ET                                               | TNDS(UN)_ZA             | PVD2 – LX2A, P-MOSFET<br>PVD2 = 3.3V             |       | 150             | 250   | 11122 |

| Parameter                            | Symbol                 | Test Conditions                                  | Min   | Тур             | Max   | Unit        |

|--------------------------------------|------------------------|--------------------------------------------------|-------|-----------------|-------|-------------|

|                                      |                        | VO2 – LX2B, P-MOSFET,                            |       | 200             | 300   |             |

| On Resistance of MOSFET              | R <sub>DS(ON)_2B</sub> | VO2 = 3.3V<br>LX2B – GND, N-MOSFET               |       |                 |       | mΩ          |

|                                      |                        | VO2 = 3.3V                                       |       | 150             | 250   |             |

|                                      |                        | Both P-MOSFET                                    |       |                 |       |             |

| Current Limitation                   | I <sub>LIM_2</sub>     | (PVD2 – LX2A) and<br>N-MOSFET (LX2B – GND)       | 2     | 2.5             | 3     | Α           |

| Over Voltage Protection at VO2       |                        | IN-IVIOSPET (LAZB - GIND)                        | 5.82  | 6               | 6.18  | V           |

|                                      |                        | Target voltage is the chosen                     |       |                 |       |             |

| Under Voltage Protection at FB2      |                        | one in A4.FB2 [2 : 0]                            |       | 0.4             |       | V           |

| Over Load Protection at FB2          |                        |                                                  |       | Target<br>– 0.1 |       | V           |

| Off Discharge Current at VO2         |                        | VO2 = 3.3V, SYS = 3.3V                           |       | 20              |       | mA          |

| Discharge Finishing Threshold at VO2 |                        |                                                  |       | 0.1             |       | V           |

| CH3 LV Sync Step-Down                |                        |                                                  |       |                 |       |             |

| Feedback Regulation Voltage at FB3   |                        | A5.FB3 [2:0] = 3'b100                            | 0.788 | 0.8             | 0.812 | <b>V</b>    |

| Minimum On-Time for PSM              |                        |                                                  |       | 50              |       | ns          |

| Maximum Duty Cycle                   |                        | FB3 = 0.75V                                      |       |                 | 100   | %           |

| Soft-Start Time                      |                        | FB3 = 0 to 0.8V                                  |       | 4               |       | ms          |

| On Registered of MOSEET              | R <sub>DS(ON)_P</sub>  | P-MOSFET, PVD3 = 3.3V                            |       | 200             | 300   | mΩ          |

| On Resistance of MOSFET              | R <sub>DS(ON)_N</sub>  | N-MOSFET, PVD3 = 3.3V                            |       | 150             | 250   | 11122       |

| Current Limitation                   | I <sub>LIM_3</sub>     |                                                  | 1.3   | 1.8             | 2.4   | Α           |

| Under Voltage Protection at FB3      |                        |                                                  | 0.35  | 0.4             | 0.45  | <b>V</b>    |

| Over Load Protection at FB3          |                        | Target voltage is the chosen one in A5.FB3 [2:0] |       | Target<br>- 0.1 | -     | ٧           |

| Off Discharge Current at LX3         |                        | LX3 = 1V, SYS = 3.3V                             |       | 20              |       | mA          |

| Discharge Finishing Threshold at FB3 |                        |                                                  |       | 0.1             |       | V           |

| CH4 LV Sync Step-Down                |                        |                                                  |       |                 |       |             |

| Feedback Regulation Voltage at FB4   |                        | A5.FB4 [2:0] = 3'b100                            | 0.788 | 0.8             | 0.812 | V           |

| Minimum On-Time for PSM              |                        |                                                  |       | 50              |       | ns          |

| Maximum Duty Cycle                   |                        | FB4 = 0.75V                                      |       |                 | 100   | %           |

| Soft-Start Time                      |                        | FB4 = 0 to 0.8V                                  |       | 4               |       | ms          |

| On Registeries of MOSEFT             | R <sub>DS(ON)_P</sub>  | P-MOSFET, PVD4 = 3.3V                            |       | 300             | 400   | <b>m</b> () |

| On Resistance of MOSFET              | R <sub>DS(ON)_N</sub>  | N-MOSFET, PVD4 = 3.3V                            |       | 200             | 300   | mΩ          |

| Current Limitation                   | I <sub>LIM_4</sub>     |                                                  | 1.3   | 1.8             | 2.4   | Α           |

| Under Voltage Protection at FB4      |                        |                                                  | 0.35  | 0.4             | 0.45  | V           |

| Over Load Protection at FB4          |                        | Target voltage is the chosen one in A5.FB4 [2:0] |       | Target<br>- 0.1 | -     | ٧           |

| Off Discharge Current at LX4         |                        | LX4 = 1V, SYS = 3.3V                             |       | 20              |       | mA          |

| Discharge Finishing Threshold at FB4 |                        |                                                  |       | 0.1             |       | V           |

| Parameter                                                     | Symbol                | Test Conditions                                                       | Min   | Тур              | Max   | Unit   |  |

|---------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------|-------|------------------|-------|--------|--|

| CH5 LV Sync Step-Down                                         | •                     |                                                                       |       |                  | '     |        |  |

| Output Voltage Accuracy at                                    |                       | Target voltage defined at A6.VOUT5 [3 : 0] = 4'b1000 to 4'b1111       | -1.5  |                  | 1.5   | %      |  |

| VO5                                                           |                       | Target voltage defined at A6.VOUT5 [3 : 0] = 4'b0001 to 4'b0111       | -2    |                  | 2     | %      |  |

| Feedback Regulation Voltage at FB5                            |                       | A6.VOUT5 [3 : 0 ] = 4'b0000                                           | 0.788 | 0.8              | 0.812 | V      |  |

| Maximum Duty Cycle                                            |                       |                                                                       |       |                  | 100   | %      |  |

| Soft-Start Time                                               |                       | VO5 = 0V to Target                                                    |       | 4                |       | ms     |  |

| On Resistance of MOSFET                                       | R <sub>DS(ON)_P</sub> | P-MOSFET, PVD5 = 3.3V                                                 | -     | 400              | 550   | mΩ     |  |

| Off Resistance of WOSFET                                      | R <sub>DS(ON)_N</sub> | N-MOSFET, PVD5 = 3.3V                                                 |       | 250              | 400   | 1115.2 |  |

| Current Limitation                                            | I <sub>LIM_5</sub>    |                                                                       | 1     | 1.5              | 2     | Α      |  |

|                                                               |                       |                                                                       |       | Target<br>x 0.5  |       |        |  |

| Under Voltage Protection at                                   |                       | Target voltage is the chosen one in A6.VOUT5 [3:0] = 0000 (FB5 = 0.8) |       | Target<br>– 0.1  |       | W      |  |

| VO5                                                           |                       | Target voltage is the chosen one in A6.VOUT5 [3:0] = 0001 to 0111     |       | Target – 0.167   |       | V      |  |

|                                                               |                       | Target voltage is the chosen one in A6.VOUT5 [3:0] = 0111 to 1111     |       | Target<br>- 0.25 |       |        |  |

| Over Load Protection at VO5                                   |                       |                                                                       |       | TBD              |       | V      |  |

| Off Discharge Current at VO5                                  |                       | VO5 = 1.8V, SYS = 3.3V                                                |       | 30               |       | mA     |  |

| Discharge Finishing Threshold at VO5                          |                       |                                                                       |       | 0.1              |       | V      |  |

| CH6 LDO                                                       |                       |                                                                       |       |                  |       |        |  |

| Input Voltage Range (PVD6)                                    |                       |                                                                       | 1.5   |                  | 5.5   | V      |  |

| Quiescent Current into PVD6                                   |                       | PVD6 = 3.3V, I <sub>OUT</sub> = 0mA                                   |       |                  | 75    | μΑ     |  |

| Regulation Voltage Accuracy                                   |                       | A6.VOUT6 [3 : 0] = 4'b1000 to<br>4'b1111                              | -1.5  |                  | 1.5   | %      |  |

| at VO6                                                        |                       | A6.VOUT6 [3 : 0] = 4'b0000 to 4'b0111                                 | -2    |                  | 2     | /0     |  |

| Drop Out Voltage (PVD6 – VO6)                                 |                       | I <sub>OUT</sub> = 300mA, VO6 = 1.3V                                  |       |                  | 0.15  | V      |  |

| PSRR+                                                         |                       | I <sub>OUT</sub> = 10mA, PVD8 = 3.3V at 1kHz                          |       | -40              |       | dB     |  |

| Max Output Current (Current Limit)                            |                       | PVD6 = 3.3V                                                           | 400   | 550              | 700   | mA     |  |

| Off Discharge Current at VO6                                  |                       | SYS = 3.3V                                                            |       |                  | 10    | mΑ     |  |

| CH7 WLED Driver                                               |                       |                                                                       |       |                  |       |        |  |

| Feedback Regulation Voltage at FB7 (Both Step-Up and Current) |                       | A2.EN7_DIM7 [4 : 0] = 5'b11111                                        | 0.237 | 0.25             | 0.263 | V      |  |

| Minimum On-Time for PSM (Step-Up)                             |                       |                                                                       |       | 300              |       | ns     |  |

| Maximum Duty Cycle (Step-Up mode)                             |                       | FB7 = 0.15V                                                           | 91    | 93               | 97    | %      |  |

| Parameter                                    | Symbol                | Test Conditions                                                             | Min  | Тур           | Max  | Unit |

|----------------------------------------------|-----------------------|-----------------------------------------------------------------------------|------|---------------|------|------|

| 0 . D                                        | R <sub>DS(ON)_P</sub> | P-MOSFET, PVD7 = 10V                                                        |      | 2             | 3    |      |

| On Resistance of MOSFET                      | R <sub>DS(ON)_N</sub> | N-MOSFET, SYS = 3.3V                                                        |      | 0.9           | 1.1  | Ω    |

| Current Limitation (Step-Up mode)            | , ,                   | N-MOSFET, SYS = 3.3V                                                        | 0.6  | 0.8           | 1    | Α    |

| Over Voltage Protection at PVD7              |                       | A0.OVP7 = 0                                                                 | 15   | 16            | 17   | V    |

| (Step-Up mode)                               |                       | A0.OVP7 = 1                                                                 | 24   | 25            | 26   | V    |

| Off Discharge Current at PVD7 (Step-Up mode) |                       | PVD7 = 10V, SYS = 3.3V                                                      | -    | 20            |      | mA   |

| Discharge Finishing Threshold at PVD7        |                       | (Step-Up Mode)                                                              |      | SYS-<br>0.4   |      | V    |

| CH8 LDO                                      |                       |                                                                             |      | •             |      |      |

| Input Voltage Range (PVD8)                   |                       |                                                                             | 1.5  |               | 5.5  | V    |

| Quiescent Current into PVD8                  | I <sub>Q_PVD8</sub>   | PVD8 = 3.3V, I <sub>OUT</sub> = 0mA                                         |      |               | 75   | μΑ   |

| Regulation Voltage Accuracy at               |                       | A3.VOUT8 [3 : 0] = 4'b1000 to<br>4'b1111                                    | -1.5 |               | 1.5  | %    |

| VO8                                          |                       | A3.VOUT8 [3 : 0] = 4'b0000 to<br>4'b0111                                    | -2   |               | 2    | 70   |

| Drop Out Voltage (PVD8 - VO8)                |                       | I <sub>OUT</sub> = 300mA, VO8 = 2.5V                                        |      |               | 0.2  | V    |

| PSRR+                                        |                       | I <sub>OUT</sub> = 10mA, PVD8 = 3.3V at<br>1kHz                             |      | -40           |      | dB   |

| Max Output Current (Current Limit)           |                       | PVD8 = 3.3V                                                                 | 300  | 450           | 600  | mA   |

| Off Discharge Current at VO8                 |                       | SYS = 3.3V                                                                  |      |               | 10   | mA   |

| CH9 RTC LDO                                  |                       |                                                                             |      |               |      |      |

| Standby Quiescent Current                    |                       | BAT = 4.2V                                                                  |      | 3             | 6    | μΑ   |

| Lockout Current into VRTC                    | I <sub>LO-VRTC</sub>  | EN = L, and PMU off, BAT = 0V, VRTC = 3.25V, SYS = 0V                       |      |               | 1    | μΑ   |

| Regulation Voltage at VRTC                   |                       | I <sub>OUT</sub> = 0mA                                                      | 3.2  | 3.25          | 3.3  | V    |

| Max Output Current (Current Limit)           |                       | BAT = 4.2V                                                                  | 60   | 130           | 200  | mA   |

|                                              |                       | I <sub>OUT</sub> = 50mA                                                     |      |               | 1000 |      |

| Dropout Voltage at (BAT-VRTC)                |                       | I <sub>OUT</sub> = 10mA                                                     | 1    |               | 150  | mV   |

|                                              |                       | I <sub>OUT</sub> = 3mA                                                      |      |               | 60   |      |

| Wake Up Detector                             |                       |                                                                             |      |               |      |      |

| WAKE Impulse High Duration                   | twakeup               | VIN or BAT plug in,<br>VRTC = 3.25V                                         | 47   | 70            | 93   | ms   |

| WAKE UP High Level                           | V <sub>WAKE_H</sub>   | Source Current 0.5mA,<br>VRTC = 3.25V                                       |      | VRTC<br>-0.3V | VRTC | V    |

| WAKE UP Low Level                            | V <sub>WAKE_L</sub>   | Sink Current 0.5mA,<br>VRTC = 3.25V                                         | 0    | 0.3           |      | V    |

| WAKE UP Rising Time                          | twake_r               | C <sub>LOAD</sub> 100pF at WAKE pin,<br>10% to 90% of VRTC,<br>VRTC = 3.25V | 1    |               | 1    | μS   |

| BAT Wake Up Threshold Voltage                |                       | VRTC = 3.25V                                                                | 2.6  | 2.7           | 2.8  | V    |

| BAT Wake Up Threshold<br>Hysteresis Gap      |                       | VRTC = 3.25V                                                                |      | -0.3          |      | V    |

| Parameter                                      |            | Symbol          | Test Conditions                                         | Min  | Тур   | Max  | Unit |

|------------------------------------------------|------------|-----------------|---------------------------------------------------------|------|-------|------|------|

| VIN Wake Up Threshold Voltage                  |            |                 | VRTC = 3.25V                                            | 3.15 | 3.3   | 3.45 | V    |

| VIN Wake Up Thre                               | shold Gap  |                 | VRTC = 3.25V                                            |      | -0.24 |      | V    |

| Control                                        |            |                 |                                                         |      |       | !    |      |

| CN logest Valtage                              | High-Level |                 |                                                         | 1.3  |       |      | .,   |

| EN Input Voltage                               | Low-Level  |                 |                                                         |      |       | 0.4  | V    |

| EN Pull Down Curr                              | ent        |                 |                                                         |      | 1     | 3    | μΑ   |

| SEQ Pull High Three Power Sequence #           |            |                 |                                                         | 0.2  |       |      | V    |

| SEQ Pull Down Resistance for Power Sequence #1 |            |                 | BAT = SYS = 2.7V                                        | 25   | 40    | 64   | kΩ   |

| SEQ Pull Down Resistance for Power Sequence #2 |            |                 | BAT = SYS = 2.7V                                        | 6.25 | 10    | 16   | kΩ   |

| SEQ Pull Down Resistance for Power Sequence #3 |            |                 | BAT = SYS = 2.7V                                        | 1.56 | 2.5   | 4    | kΩ   |

| SEQ Pull Down Resistance for Power Sequence #4 |            |                 | BAT = SYS = 2.7V                                        |      | 0.63  | 1    | kΩ   |

| SEQ Pull Low Three Power Sequence #            |            |                 |                                                         |      |       | 0.2  | V    |

| SEQ Pull Down Re<br>Power Sequence #           |            |                 | BAT = SYS = 2.7V                                        | 100  | 160   |      | kΩ   |

| Power Sequence Time Gap                        |            |                 | From previous channel starting to next channel starting | 9    | 10    | 11   | ms   |

| Protection                                     |            | •               |                                                         | •    | •     |      |      |

| Protection Fault Delay                         |            |                 |                                                         |      | 100   |      | ms   |

| Thermal Shutdown                               |            | T <sub>SD</sub> |                                                         | 125  | 155   |      | °C   |

| Thermal Shutdown                               | Hysteresis | $\Delta T_{SD}$ |                                                         |      | 20    |      | °C   |

**Charger Unit:**

( $V_{IN} = 5V$ ,  $V_{BAT} = 4V$ ,  $T_A = 25$ °C, unless otherwise specified)

| Parameter                               | Symbol               | Test Conditions                                                                              | Min  | Тур   | Max    | Unit |

|-----------------------------------------|----------------------|----------------------------------------------------------------------------------------------|------|-------|--------|------|

| Supply Input                            |                      |                                                                                              |      |       |        |      |

| VIN Under Voltage Lockout<br>Threshold  | V <sub>UVLO</sub>    | V <sub>IN</sub> = 0V to 4.5V                                                                 | 3.1  | 3.3   | 3.5    | V    |

| VIN Under Voltage Lockout<br>Hysteresis | $\Delta V_{UVLO}$    | $V_{IN} = 4.5V \text{ to } 0V$                                                               |      | 240   | 1      | mV   |

| VIN Committee Comment                   |                      | $I_{SYS} = I_{BAT} = 0mA, A7.\overline{ENCH} = 0$<br>( $V_{BAT} > V_{REGx}$ )                |      | 1     | 2      | 0    |

| VIN Supply Current                      | ISUPPLY              | $I_{SYS} = I_{BAT} = 0mA, A7.\overline{ENCH} = 1$<br>(V <sub>BAT</sub> > V <sub>REGx</sub> ) |      | 0.8   | 1.5 mA | mA   |

| VIN Suspend Current                     | lusus                | V <sub>IN</sub> = 5V, A7.USUS = 1                                                            |      | 195   | 300    | μΑ   |

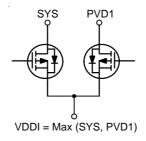

| VIN – BAT VOS Rising                    | V <sub>OS_H</sub>    |                                                                                              |      | 200   | 300    | mV   |

| VIN – BAT VOS Falling                   | V <sub>OS_L</sub>    |                                                                                              | 10   | 50    |        | mV   |

| Voltage Regulation                      | •                    |                                                                                              |      |       |        |      |

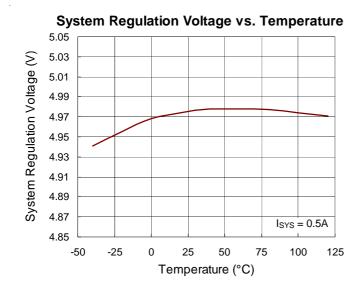

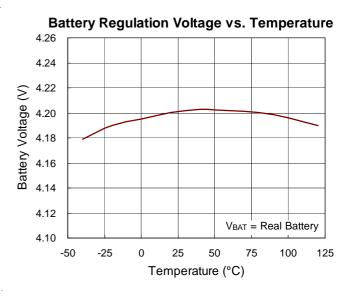

| System Regulation Voltage               | V <sub>SYS</sub>     | I <sub>SYS</sub> = 800mA, V <sub>IN</sub> = 5.5V                                             | 4.9  | 5     | 5.1    | V    |

| Battery Regulation Voltage              | VREG1                | 0 to 85°C, Loading = 20mA,<br>When A9.VSETH = 1 and<br>A9.VSETC = 1                          | 4.16 | 4.2   | 4.23   | V    |

| Battery Regulation Voltage              | V <sub>REG2</sub>    | 0 to 85°C, Loading = 20mA, When A9.VSETH = 0 and A9.VSETC = 0                                | 4.01 | 4.05  | 4.08   | V    |

| APPM Regulation Voltage                 | V <sub>APPM</sub>    |                                                                                              | 4.05 | 4.15  | 4.25   | V    |

| DPM Regulation Voltage                  | V <sub>DPM</sub>     |                                                                                              | 4.25 | 4.35  | 4.45   | V    |

| VIN to VSYS MOSFET Ron                  | R <sub>DS(ON)</sub>  | I <sub>VIN</sub> = 1000mA                                                                    |      | 0.2   | 0.35   | Ω    |

| BAT to VSYS MOSFET Ron                  | R <sub>DS(ON)</sub>  | V <sub>BAT</sub> = 4.2V, I <sub>SYS</sub> = 1A                                               |      | 0.05  | 0.1    | Ω    |

| Re-Charge Threshold                     | $\Delta V_{REGCHG}$  | Battery Regulation - Recharge level                                                          | 60   | 100   | 140    | mV   |

| Current Regulation                      |                      |                                                                                              |      |       |        |      |

| Charge Current Setting Range            | I <sub>CHG</sub>     |                                                                                              | 100  |       | 1200   | mA   |

| Charge Current Accuracy1                | I <sub>CHG1</sub>    | V <sub>BAT</sub> = 4V,<br>A8.ISETA [3 : 0] = 4'b0101                                         | 570  | 600   | 630    | mA   |

| Charge Current Accuracy2                | I <sub>CHG2</sub>    | V <sub>BAT</sub> = 3.8V,<br>A8.ISETA [3 : 0] = 4'b0010                                       | 285  | 300   | 315    | mA   |

|                                         |                      | A7.ISETL = 1, A7.ISETU = 1<br>(1.5A Mode)                                                    | 1.5  | 1.8   | 2.1    | А    |

| VIN Current Limit                       | 1                    | A7.ISETL = 1, A7.ISETU = 0<br>(1.0A Mode)                                                    | 0.85 | 0.925 | 1      | Α    |

| VIII Current Limit                      | ILIM_VIN             | A7.ISETL = 0, A7.ISETU = 1<br>(500mA mode)                                                   | 450  | 475   | 500    | mA   |

|                                         |                      | A7.ISETL = 0, A7.ISETU = 0<br>(100mA Mode)                                                   | 90   | 95    | 100    | mA   |

| Pre-Charge                              |                      |                                                                                              |      |       |        |      |

| BAT Pre-Charge Threshold                | V <sub>PRECH</sub>   | BAT Falling                                                                                  | 2.7  | 2.8   | 2.9    | V    |

| BAT Pre-Charge Threshold<br>Hysteresis  | $\Delta V_{PRECH}$   |                                                                                              |      | 200   |        | mV   |

| Pre-Charge Current                      | I <sub>CHG_PRE</sub> | V <sub>BAT</sub> = 2V                                                                        | 5    | 10    | 15     | %    |

| Parameter                                                      | Symbol               | Test Conditions                                             | Min   | Тур  | Max   | Unit       |

|----------------------------------------------------------------|----------------------|-------------------------------------------------------------|-------|------|-------|------------|

| Charge Termination Detection                                   | on                   |                                                             | ļ     |      |       |            |

| Termination Current Ratio to Fast Charge (Except USB 100 Mode) | I <sub>TERM</sub>    | A7.ISETL = 0, A7.ISETU = 1<br>or A7.ISETL = 1, A7.ISETU = X | 5     | 10   | 15    | %          |

| Termination Current Ratio to Fast Charge (USB100 Mode)         | I <sub>TERM2</sub>   | A7.ISETL = 0, A7.ISETU = 0                                  |       | 3.3  |       | %          |

| Login Input/Output                                             |                      |                                                             |       |      |       |            |

| CHG Pull Down Voltage                                          | V <del>CHG</del>     | I <del>CHG</del> = 5mA                                      |       | 200  |       | mV         |

| INT Pull Down Voltage                                          | VINT                 | l <sub>INT</sub> = 5mA                                      |       | 200  |       | mV         |

| Protection                                                     | •                    |                                                             | •     | •    | •     |            |

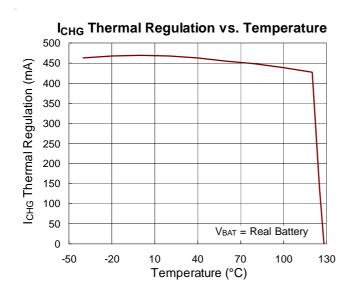

| Thermal Regulation Point                                       | T <sub>REG</sub>     |                                                             |       | 125  |       | °C         |

| Thermal Shutdown<br>Temperature                                | T <sub>SD</sub>      |                                                             |       | 155  |       | °C         |

| Thermal Shutdown Hysteresis                                    | $\Delta T_{SD}$      |                                                             |       | 20   |       | °C         |

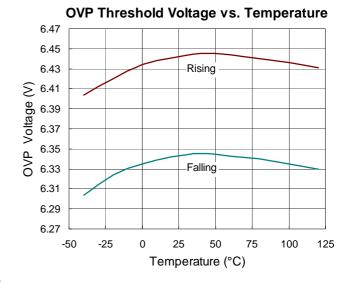

| Over Voltage Protection                                        | V <sub>OVP</sub>     | V <sub>IN</sub> Rising                                      | 6.25  | 6.5  | 6.75  | V          |

| Over Voltage Protection<br>Hysteresis                          | ΔV <sub>OVP</sub>    | $V_{IN} = 7V \text{ to } 5V, VOVP - \Delta VOVP$            |       | 100  |       | mV         |

| Output Short Circuit Detection<br>Threshold                    | V <sub>SHORT</sub>   | VBAT – VSYS                                                 |       | 300  |       | mV         |

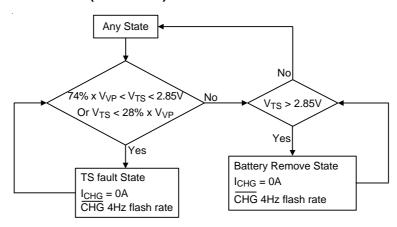

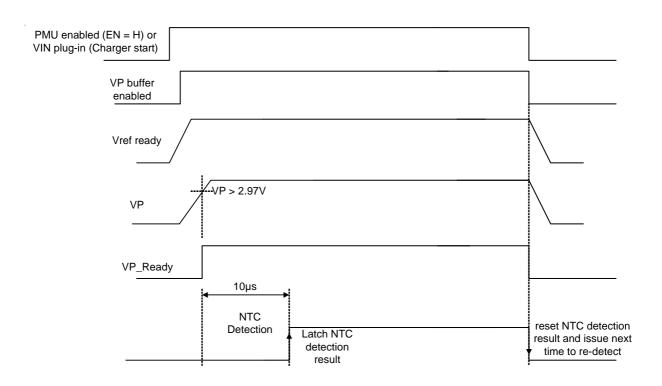

| Battery Installation Detection<br>Threshold at TS              |                      | EN = H (PMU enabled), report at A10. NoBAT bit              |       | 90   |       | % of<br>VP |

| Time                                                           | •                    |                                                             | •     |      |       |            |

| Input Over Voltage Blanking<br>Time                            | t <sub>OVP</sub>     |                                                             |       | 50   |       | μS         |

| Pre-Charge to Fast-Charge<br>Deglitch Time                     | t <sub>PF</sub>      |                                                             |       | 25   |       | ms         |

| Fast-Charge to Pre-Charge Deglitch Time                        | t <sub>FP</sub>      |                                                             |       | 25   |       | ms         |

| Termination Deglitch Time                                      | t <sub>TERMI</sub>   |                                                             |       | 25   |       | ms         |

| Recharge Deglitch Time                                         | tRECHG               |                                                             |       | 100  |       | ms         |

| Input Power Loss to SYS LDC<br>Turn-Off Delay Time             | t <sub>NO_IN</sub>   |                                                             |       | 25   |       | ms         |

| Pack Temperature Fault Detection Deglitch Time                 | t <sub>TS</sub>      |                                                             |       | 25   |       | ms         |

| Short Circuit Deglitch Time                                    | tSHORT               |                                                             |       | 250  |       | μS         |

| Short Circuit Recovery Time                                    | t <sub>SHORT-R</sub> |                                                             |       | 64   |       | ms         |

| Other                                                          |                      |                                                             |       |      |       |            |

| VP Regulation Voltage                                          | V <sub>VP</sub>      | V <sub>SYS</sub> = 4.2V                                     | 3.234 | 3.3  | 3.366 | V          |

| VP Load Regulation                                             | V <sub>VP</sub>      | VP source out 2mA                                           |       |      | -0.1  | V          |

| VP Under Voltage Lockout<br>Threshold                          |                      | Falling Threshold                                           |       | 0.8  |       | V          |

| TS Battery Detect Threshold                                    | V <sub>TS</sub>      |                                                             | 2.75  | 2.85 | 2.95  | V          |

| Parameter                                        | Symbol                | Test Conditions                                 | Min   | Тур | Max  | Unit       |

|--------------------------------------------------|-----------------------|-------------------------------------------------|-------|-----|------|------------|

| NTC Temperature Sense                            |                       |                                                 |       |     | •    |            |

| Low Temperature Trip Point                       | V <sub>TOO_COLD</sub> | NTC = 100kΩ                                     | 73    | 74  | 75   | %          |

| (0°C)                                            | VTOO_COLD             | NTC = $10k\Omega$                               | 59    | 60  | 61   | of VP      |

| Low Temperature Trip Point                       | Vcold                 | NTC = $100$ k $\Omega$                          | 63    | 64  | 65   | %          |

| (10°C) for JEITA                                 | V <sub>COLD</sub>     | NTC = $10k\Omega$                               | 51    | 52  | 53   | of VP      |

| High Temperature Trip Point                      | V <sub>HOT</sub>      | NTC = $100$ k $\Omega$                          | 34    | 35  | 36   | %          |

| (45°C) for JEITA                                 | V <sub>HOT</sub>      | $NTC = 10k\Omega$                               | 31    | 32  | 33   | of VP      |

| High Temperature Trip Point                      | Vтоо_нот              | NTC = $100k\Omega$ ,<br>A8.TSHT [1 : 0] = 2'b00 | 27    | 28  | 29   | %          |

| (60°C)                                           |                       |                                                 | 27    | 28  | 29   | of VP      |

| High Temperature Trip Point Hysteresis for JEITA |                       |                                                 |       | 1   |      | %<br>of VP |

| Charger Detection                                |                       |                                                 |       |     |      |            |

| VDP_SRC Voltage                                  | VDP_SRC               | With IDAT_SRC = 0 to 200μA                      | 0.5   |     | 0.7  | V          |

| VDAT_REF Voltage                                 | VDAT_REF              |                                                 | 0.25  |     | 0.4  | V          |

| VLGC Voltage                                     | VLGC                  |                                                 | 0.8   |     | 2    | V          |

| IDP_SRC Current                                  | IDP_SRC               |                                                 | 6.6   |     | 11   | μА         |

| D+ and D- Sink Current                           | ICD+_SINK<br>ICDSINK  |                                                 | 50    |     | 150  | μА         |

| D- Pull down Resistor                            | RDDWN                 |                                                 | 14.25 |     | 24.8 | kΩ         |

| Data Contact Detect<br>Debounce                  | TDCD_DBNC             |                                                 | 10    | 15  | 20   | ms         |

| DCD Time OUT                                     | TDCD_TO               |                                                 | 150   |     | 450  | ms         |

| VDAT_SRC ON Time                                 | TDP SRC ON            |                                                 | 50    |     | 100  | ms         |

( $V_{SYS} = 3.3V$ ,  $T_A = 25$ °C, unless otherwise specified)

| Parameter                                                           |                 | Symbol              | Test Conditions           | Min | Тур | Max | Unit |

|---------------------------------------------------------------------|-----------------|---------------------|---------------------------|-----|-----|-----|------|

| ı²c                                                                 |                 |                     |                           | •   |     |     |      |

| SDA, SCLK                                                           | High-Level      |                     |                           | 1.4 |     |     | V    |

| Input Voltage                                                       | Low-Level       |                     |                           |     |     | 0.6 | ľ    |

| SCLK Clock Rate                                                     | е               | f <sub>SCL</sub>    |                           |     |     | 400 | kHz  |

| Hold Time (repeated Condition. After this period, pulse is generate | the first clock | thd,sta             |                           | 0.6 |     |     | μS   |

| LOW Period of the                                                   | ne SCL Clock    | t <sub>LOW</sub>    |                           | 1.3 |     |     | μS   |

| HIGH Period of t                                                    | he SCL Clock    | tHIGH               |                           | 0.6 |     |     | μS   |

| Set-Up Time for START Condition                                     |                 | t <sub>SU,STA</sub> |                           | 0.6 |     |     | μS   |

| Data Hold Time                                                      |                 | t <sub>HD,DAT</sub> |                           | 0   |     | 0.9 | μS   |

| Data Set-Up Tim                                                     | ie              | t <sub>SU,DAT</sub> |                           | 100 |     |     | ns   |

| Set-Up Time for Condition                                           | STOP            | t <sub>SU,STO</sub> |                           | 0.6 |     |     | μS   |

| Bus Free Time b                                                     |                 | t <sub>BUF</sub>    |                           | 1.3 |     |     | μS   |

| Rise time of both SCL signals                                       | SDA and         | t <sub>R</sub>      |                           | 20  |     | 300 | ns   |

| Fall Time of Both SCL Signals                                       | SDA and         | t <sub>F</sub>      |                           | 20  |     | 300 | ns   |

| SDA and SCL O                                                       | utput Low Sink  | I <sub>OL</sub>     | SDA or SCL voltage = 0.4V | 2   |     |     | mA   |

- **Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

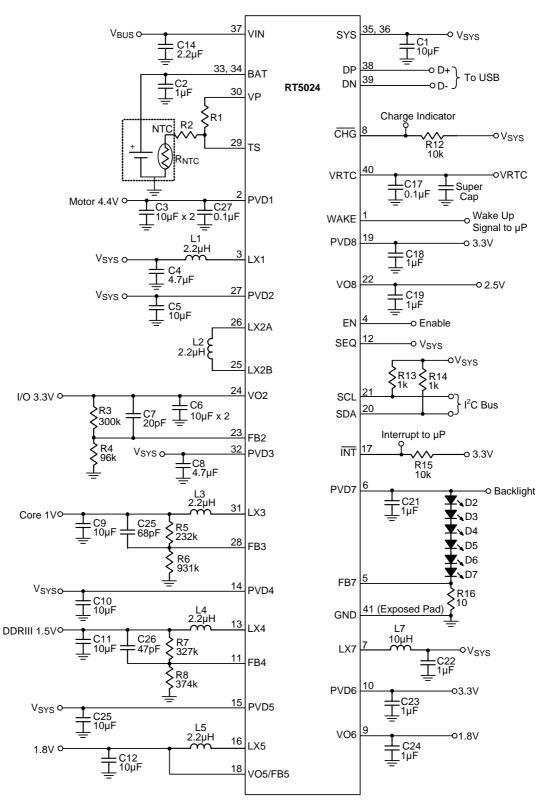

### **Typical Application Circuit**

Note: To make CH1 stable, C27 must be close to PVD1.

Figure 1. Typical Application Circuit for DSC with 6-LED Backlight

Note: To make CH1 stable, C27 must be close to PVD1.

Figure 2. Typical Application Circuit for DSC with One LED Backlight

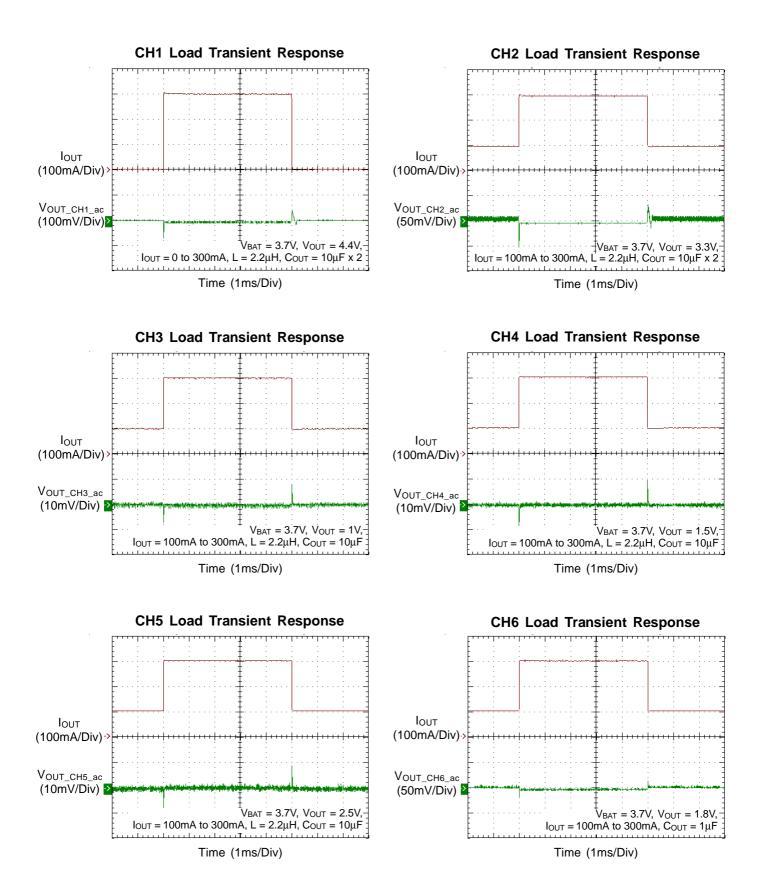

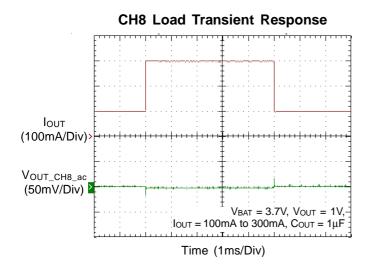

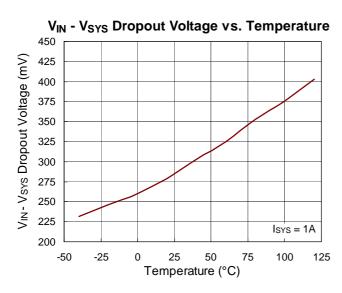

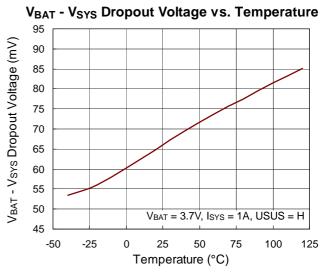

### **Typical Operating Characteristics**

$V_{IN}$  = 5V, unless otherwise specified.

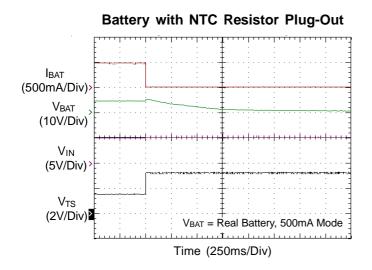

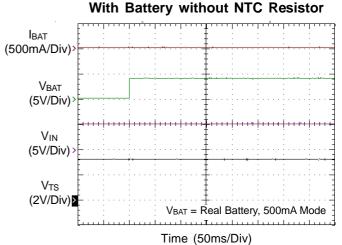

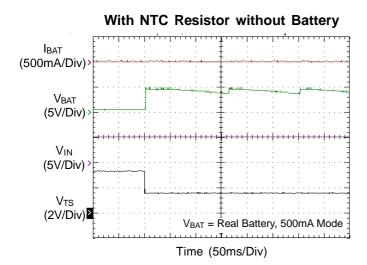

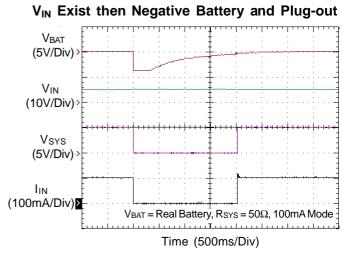

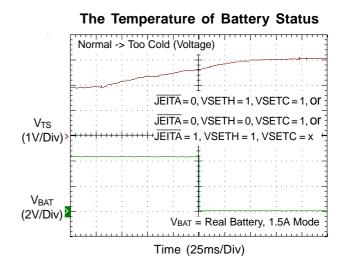

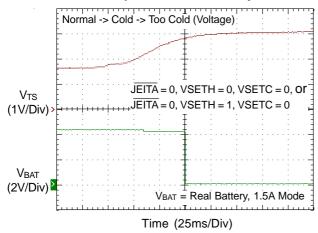

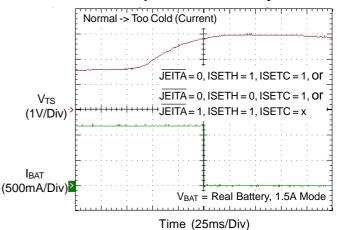

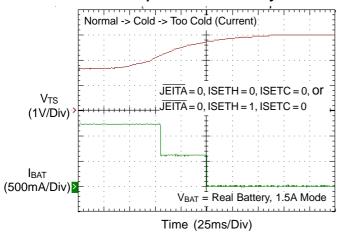

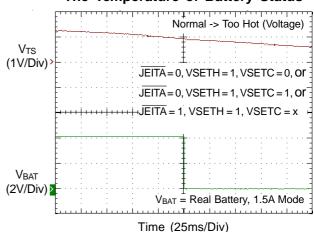

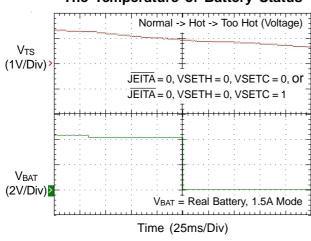

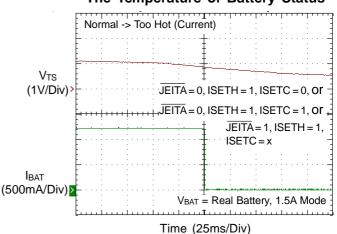

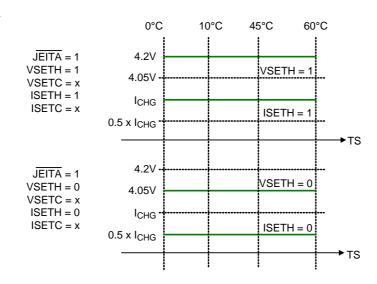

### The Temperature of Battery Status

### The Temperature of Battery Status

### The Temperature of Battery Status

### The Temperature of Battery Status

### The Temperature of Battery Status

### The Temperature of Battery Status

$V_{TS}$

**I**BAT

(500mA/Div)2

## Normal -> Hot -> Too Hot (Current) (1V/Div) $\overline{\text{JEITA}} = 0$ , ISETH = 0, ISETC = 0, Or $\overline{\text{JEITA}} = 0$ . ISETH = 0. ISETC = 1.

Time (25ms/Div)

The Temperature of Battery Status

Copyright ©2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

### **Application Information**

#### **Power Converter Unit**

The RT5024 is an integrated power solution for digital still cameras and other small handheld devices. It includes six DC-DC converters, a WLED driver, two low output LDO, a RTC LDO and a fully integrated single-cell Li-ion battery charger that is ideal for portable applications.

### CH1: Synchronous Step-Up DC-DC Converter

The synchronous step-up DC-DC converter can be operated in either PFM or Sync-PWM mode by setting  $I^2C$ . It includes internal power MOSFETs, compensation network and feedback resistors. The P-MOSFET can be controlled to disconnect output loading. It is suitable for providing power to the motor. The output voltage of CH1 can be adjusted by the  $I^2C$  interface in the range of 3.6V to 5.5V.

|             | CH1 regul | ation voltag | je can be s | elected by I | <sup>2</sup> C interfac | e. The defa | ult voltage | is 4.4V. |

|-------------|-----------|--------------|-------------|--------------|-------------------------|-------------|-------------|----------|

|             | Code      | Voltage      | Code        | Voltage      | Code                    | Voltage     | Code        | Voltage  |

| VOUT1 [3:0] | 0000      | 3.6V         | 0001        | 3.7V         | 0010                    | 3.8V        | 0011        | 3.9V     |

| VOOTT[0.0]  | 0100      | 4V           | 0101        | 4.4V         | 0110                    | 4.6V        | 0111        | 4.7V     |

|             | 1000      | 4.8V         | 1001        | 4.9V         | 1010                    | 5V          | 1011        | 5.1V     |

|             | 1100      | 5.2V         | 1101        | 5.3V         | 1110                    | 5.4V        | 1111        | 5.5V     |

### CH2: Synchronous Step-Up/Down (Buck-Boost) DC-DC Converter

The synchronous step-up/down (Buck-Boost) DC-DC converter can be operated in either PFM or Sync-PWM mode by setting I<sup>2</sup>C. It includes internal power MOSFETs, compensation network and feedback resistors. This channel supplies the power for I/O. The FB voltage of CH2 can be adjusted by the I<sup>2</sup>C interface in the range of 0.72V to 0.86V.

|            | FB2 regulation | FB2 regulation voltage can be selected by I <sup>2</sup> C interface. The default voltage is 0.8V. |                  |                |                  |  |  |  |

|------------|----------------|----------------------------------------------------------------------------------------------------|------------------|----------------|------------------|--|--|--|