#### 1. Features

#### GaNFast™ Power IC

- · Monolithically-integrated gate drive

- · Wide logic input range range with hysteresis

- 5 V / 15 V input-compatible

- Wide Vcc range (10 to 30 V)

- Programmable turn-on dV/dt

- 200 V/ns dV/dt immunity

- 800 V Transient Voltage Rating

- 650 V Continuous Voltage Rating

- Low 300 mΩ resistance

- · Zero reverse recovery charge

- ESD protection 2 kV (HBM), 1 kV (CDM)

- 2 MHz operation

#### Small, low-profile SMT QFN

- 6 x 8 mm footprint, 0.85 mm profile

- · Minimized package inductance

#### Sustainability

- · RoHS, Pb-free, REACH-compliant

- Up to 40% energy savings vs Si solutions

- System level 4kg CO<sub>2</sub> Carbon Footprint reduction

#### **Product Reliability**

20-year limited product warranty (see Section 14 for details)

#### 2. Topologies / Applications

- · AC-DC, DC-DC, DC-AC

- QR Flyback, PFC, AHB, Buck, Boost, Half bridge, Full bridge, LLC resonant, Class D

- Wireless power, Solar Micro-inverters, LED lighting, TV SMPS, Server, Telecom

# GaNFast™ Power IC

QFN 5 x 6 mm

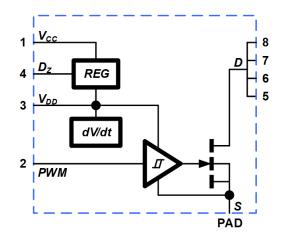

Simplified schematic

#### 3. Description

This GaNFast power IC is optimized for high frequency, soft-switching topologies.

Monolithic integration of FET, drive and logic creates an easy-to-use 'digital-in, power-out' high-performance powertrain building block, enabling designers to create the fastest, smallest, most efficient power converters in the world.

The highest dV/dt immunity, high-speed integrated drive and industry-standard low-profile, low-inductance, 5 x 6 mm SMT QFN package allow designers to exploit Navitas GaN technology with simple, quick, dependable solutions for breakthrough power density and efficiency.

GaNFast power ICs extend the capabilities of traditional topologies such as flyback, half-bridge, resonant, etc. to MHz+ and enable the commercial introduction of breakthrough designs.

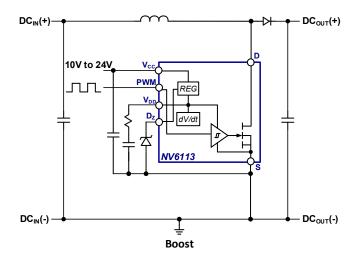

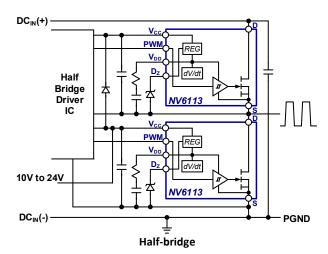

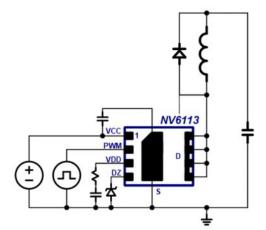

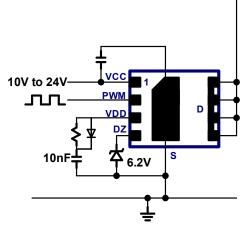

# 4. Typical Application Circuits

#### 5. Table of Contents

| 1. Features                                          | 22 |

|------------------------------------------------------|----|

| 2. Description                                       | 2  |

| 3. Topologies / Applications                         | 2  |

| 4. Typical Application Circuits                      | 2  |

| 5. Table of Contents                                 | 2  |

| 6. Specifications                                    | 3  |

| 6.1. Absolute Maximum Ratings <sup>(1)</sup>         | 3  |

| 6.2. Recommended Operating Conditions <sup>(3)</sup> | 3  |

| 6.3. ESD Ratings                                     | 4  |

| 6.4. Thermal Resistance                              | 4  |

| 6.5. Electrical Characteristics                      | 5  |

| 6.6. Switching Waveforms                             | 6  |

| 6.7. Characteristic Graphs                           | 7  |

| 7. Internal Schematic, Pin Configurations Functions  |    |

| 8. Functional Description                            | 11 |

| 8.1. Start Up                                        | 11 |

| 8.2. Normal Operating Mode                           | 12 |

| 8.3. Standby Mode                                    | 12 |

| 8.4. Programmable Turn-on dV/dt Control      | 12 |

|----------------------------------------------|----|

| 8.5. Current Sensing                         | 13 |

| 8.6. Paralleling Devices                     | 13 |

| 8.7. 3.3V PWM Input Circuit                  | 14 |

| 8.8. PCB Layout Guidelines                   | 14 |

| 8.9. Recommended Component Values            | 15 |

| 8.9.1. Zener Selection                       | 15 |

| 8.10. Drain-to-Source Voltage Considerations | 16 |

| 9. Recommended PCB Land Pattern              | 17 |

| 10. PCB Layout Guidelines                    | 18 |

| 11. QFN Package Outline                      | 20 |

| 12. Tape and Reel Dimensions                 | 21 |

| 13. Ordering Information                     | 22 |

| 14. 20-Year Limited Warranty                 | 22 |

| 15. Revision History                         | 22 |

#### 6. Specifications

#### 6.1. Absolute Maximum Ratings(1)

(with respect to Source (pad) unless noted)

| SYMBOL                 | PARAMETER                                             | MAX        | UNITS |

|------------------------|-------------------------------------------------------|------------|-------|

| V <sub>DS</sub> (TRAN) | Transient Drain-to-Source Voltage <sup>(2)</sup>      | 800        | V     |

| V <sub>DS</sub> (CONT) | Continuous Drain-to-Source Voltage                    | -7 to +650 | V     |

| V <sub>cc</sub>        | Supply Voltage                                        | 30         | V     |

| V <sub>PWM</sub>       | PWM Input Pin Voltage                                 | -3 to +30  | V     |

| V <sub>DZ</sub>        | V <sub>DD</sub> Setting Pin Voltage                   | 6.6        | V     |

| V <sub>DD</sub>        | Drive Supply Voltage                                  | 7.2        | V     |

| I <sub>D</sub>         | Continuous Drain Current (@ T <sub>C</sub> = 100°C)   | 5          | А     |

| I <sub>D</sub> PULSE   | Pulsed Drain Current (10 μs @ T <sub>J</sub> = 25°C)  | 10         | А     |

| I <sub>D</sub> PULSE   | Pulsed Drain Current (10 μs @ T <sub>J</sub> = 125°C) | 7.5        | А     |

| dV/dt                  | Slew Rate on Drain-to-Source                          | 200        | V/ns  |

| T <sub>J</sub>         | T <sub>J</sub> Operating Junction Temperature         |            | °C    |

| T <sub>STOR</sub>      | Storage Temperature                                   | -55 to 150 | °C    |

<sup>(1)</sup> Absolute maximum ratings are stress ratings; devices subjected to stresses beyond these ratings may cause permanent damage.

### 6.2. Recommended Operating Conditions(3)

| SYMBOL              | PARAMETER                                                | MIN | TYP | MAX                                | UNITS |

|---------------------|----------------------------------------------------------|-----|-----|------------------------------------|-------|

| V <sub>DZ</sub>     | Drive Supply Set Zener Voltage <sup>(4)</sup>            | 5.8 | 6.2 | 6.6                                | V     |

| V <sub>DD</sub>     | Drive Supply Voltage                                     | 5.5 |     | 7.0                                | V     |

| I <sub>DD_EXT</sub> | I <sub>DD_EXT</sub> Regulator External Load Current      |     |     | 3.0                                | mA    |

| R <sub>DD</sub>     | Gate Drive Turn-On Current Set Resistance <sup>(5)</sup> | 10  | 25  |                                    | Ω     |

| V <sub>PWM</sub>    |                                                          |     | 5   | Min. of<br>(V <sub>CC</sub> or 20) | V     |

| V <sub>CC</sub>     | V <sub>CC</sub> Supply Voltage                           |     |     | 24                                 | V     |

| T <sub>C</sub>      | T <sub>C</sub> Operating Case Temperature                |     |     | 125                                | °C    |

<sup>(3)</sup> Exposure to conditions beyond maximum recommended operating conditions for extended periods of time may affect device reliability.

Final Datasheet 3 Rev Apr. 11, 2022

<sup>(2)</sup> V<sub>DS.(TRAN)</sub>allows for surge ratings during non-repetitive events that are <100us (for example start-up, line interruption) and repetitive events that are <100ns (for example repetitive leakage inductance spikes). Refer to Section 8.10 for detailed recommended design guidelines.

<sup>(4)</sup> Use of Zener diode other than 6.2 V is not recommended. See Table I for recommended part numbers of 6.2 V Zener diodes.

<sup>(5)</sup> RDD resistor must be used. Minimum 10 Ohm to ensure application and device robustness.

# 6.3. ESD Ratings

| SYMBOL | PARAMETER                              | MAX   | UNITS |

|--------|----------------------------------------|-------|-------|

| НВМ    | Human Body Model (per JS-001-2014)     | 2,000 | V     |

| CDM    | Charged Device Model (per JS-002-2014) | 1,000 | V     |

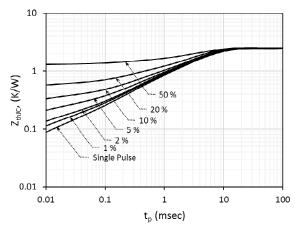

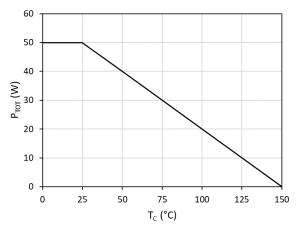

# 6.4. Thermal Resistance

| SYMBOL               | PARAMETER           | TYP | UNITS |

|----------------------|---------------------|-----|-------|

| R <sub>eJC</sub> (6) | Junction-to-Case    | 2.5 | °C/W  |

| R <sub>eJA</sub> (6) | Junction-to-Ambient | 50  | °C/W  |

<sup>(6)</sup> R<sub>e</sub> measured on DUT mounted on 1 square inch 2 oz Cu (FR4 PCB)

Final Datasheet 4 Rev Apr. 11, 2022

#### 6.5. Electrical Characteristics

Typical conditions:  $V_{DS}$  = 400 V,  $V_{CC}$  = 15 V,  $V_{DZ}$  = 6.2 V,  $F_{SW}$  = 1 MHz,  $T_{AMB}$  = 25 °C,  $I_D$  = 2.5 A,  $R_{DD}$  = 10  $\Omega$  (or specified)

| SYMBOL                                 | PARAMETER                                       | MIN     | TYP      | MAX        | UNITS | CONDITIONS                                                                    |  |  |

|----------------------------------------|-------------------------------------------------|---------|----------|------------|-------|-------------------------------------------------------------------------------|--|--|

| V <sub>cc</sub> Supply Characteristics |                                                 |         |          |            |       |                                                                               |  |  |

| l <sub>QCC</sub>                       | V <sub>CC</sub> Quiescent Current               |         | 0.65     | 1.25       | mA    | V <sub>PWM</sub> = 0 V                                                        |  |  |

| l<br>QCC-SW                            | V <sub>CC</sub> Operating Current               |         | 1.5      |            | mA    | F <sub>SW</sub> = 1 MHz, V <sub>DS</sub> = Open                               |  |  |

|                                        | Low-Side Logic Input Characteristics            |         |          |            |       |                                                                               |  |  |

| $V_{_{\mathrm{PWMH}}}$                 | Input Logic High Threshold (rising edge)        |         |          | 4          | V     |                                                                               |  |  |

| $V_{_{\mathrm{PWML}}}$                 | Input Logic Low Threshold (falling edge)        | 1       |          |            | V     |                                                                               |  |  |

| V <sub>I-HYS</sub>                     | Input Logic Hysteresis                          |         | 0.5      |            | ٧     |                                                                               |  |  |

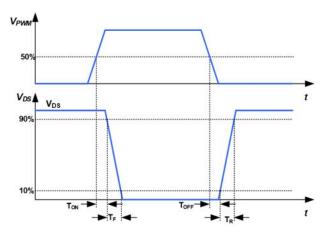

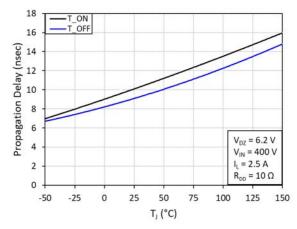

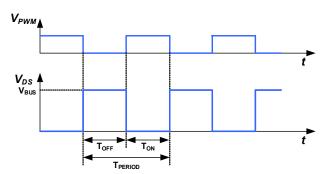

| $T_{ON}$                               | Turn-on Propagation Delay                       |         | 11       |            | ns    | Fig.1, Fig.2                                                                  |  |  |

| T <sub>OFF</sub>                       | Turn-off Propagation Delay                      |         | 9        |            | ns    | Fig.1, Fig.2                                                                  |  |  |

| $T_{R}$                                | Drain rise time                                 |         | 8        |            | ns    | Fig.1, Fig.2                                                                  |  |  |

| $T_{_{F}}$                             | Drain fall time                                 |         | 3        |            | ns    | Fig.1, Fig.2                                                                  |  |  |

|                                        |                                                 | Switchi | ng Chara | cteristics | 3     |                                                                               |  |  |

| F <sub>sw</sub>                        | Switching Frequency                             |         |          | 2          | MHz   |                                                                               |  |  |

| t <sub>PW</sub>                        | Pulse width                                     | 0.02    |          | 1000       | μs    |                                                                               |  |  |

|                                        |                                                 | GaN FE  | T Chara  | cteristics |       |                                                                               |  |  |

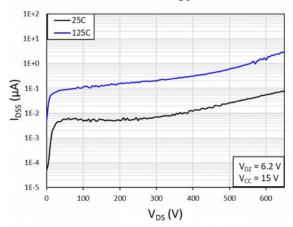

| l<br>DSS                               | Drain-Source Leakage Current                    |         | 0.1      | 25         | μΑ    | $V_{DS} = 650 \text{ V}, V_{PWM} = 0 \text{ V}$                               |  |  |

| l<br>DSS                               | Drain-Source Leakage Current                    |         | 3        | 50         | μΑ    | $V_{DS} = 650 \text{ V}, V_{PWM} = 0 \text{ V}, T_{C} = 125 ^{\circ}\text{C}$ |  |  |

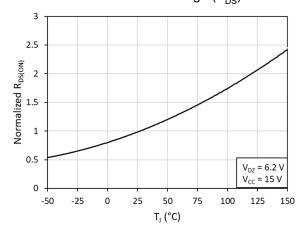

| R <sub>DS(ON)</sub>                    | Drain-Source Resistance                         |         | 300      | 420        | mΩ    | $V_{PWM} = 6 \text{ V}, I_{D} = 2.5 \text{ A}$                                |  |  |

| R <sub>DS(ON)</sub>                    | Drain-Source Resistance                         |         | 621      |            | mΩ    | $V_{PWM} = 6 \text{ V}, I_{D} = 2.5 \text{ A}, T_{C} = 125 ^{\circ}\text{C}$  |  |  |

| V <sub>SD</sub>                        | Source-Drain Reverse Voltage                    |         | 3.2      | 5          | V     | V <sub>PWM</sub> = 0 V, I <sub>SD</sub> = 2.5 A                               |  |  |

| Q <sub>oss</sub>                       | Output Charge                                   |         | 10       |            | nC    | $V_{DS} = 400 \text{ V}, V_{PWM} = 0 \text{ V}$                               |  |  |

| $Q_{RR}$                               | Reverse Recovery Charge                         |         | 0        |            | nC    |                                                                               |  |  |

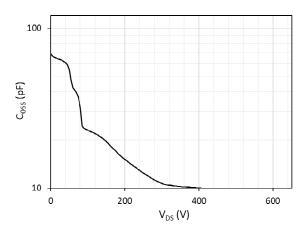

| C <sub>oss</sub>                       | Output Capacitance                              |         | 11       |            | pF    | $V_{DS} = 400 \text{ V}, V_{PWM} = 0 \text{ V}$                               |  |  |

| C <sub>O(er)</sub> (7)                 | Effective Output Capacitance, Energy<br>Related |         | 15       |            | pF    | V <sub>DS</sub> = 400 V, V <sub>PWM</sub> = 0 V                               |  |  |

| $C_{O(tr)}^{(8)}$                      | Effective Output Capacitance, Time Related      |         | 24       |            | pF    | V <sub>DS</sub> = 400 V, V <sub>PWM</sub> = 0 V                               |  |  |

<sup>(7)</sup>  $C_{O(er)}$  is a fixed capacitance that gives the same stored energy as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 400 V

Final Datasheet 5 Rev Apr. 11, 2022

<sup>(8)</sup>  $C_{\text{O(tr)}}$  is a fixed capacitance that gives the same charging time as  $C_{\text{OSS}}$  while  $V_{\text{DS}}$  is rising from 0 to 400 V

# 6.6. Switching Waveforms

$(T_C = 25 \, {}^{\circ}C \text{ unless otherwise specified})$

Fig. 1. Inductive switching circuit

Fig. 2. Propagation delay and rise/fall time definitions

Final Datasheet 6 Rev Apr. 11, 2022

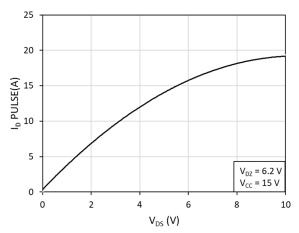

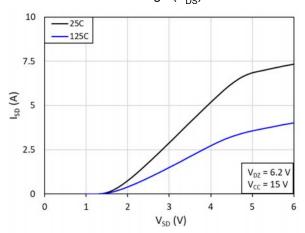

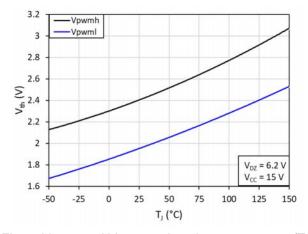

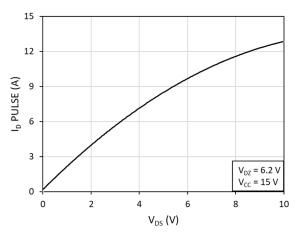

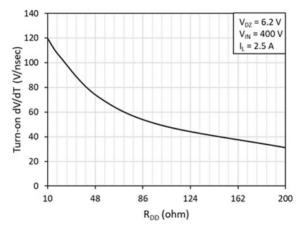

#### 6.7. Characteristic Graphs

(GaN FET,  $T_C = 25$  °C unless otherwise specified)

Fig. 3. Pulsed Drain current ( $I_D$  PULSE) vs. drain-to-source voltage ( $V_{DS}$ ) at T = 25 °C

Fig. 5. Source-to-drain reverse conduction voltage

Fig. 7.  $V_{PWMH}$  and  $V_{PWML}$  vs. junction temperature  $(T_J)$

Fig. 4. Pulsed Drain current ( $I_D$  PULSE) vs. drain-to-source voltage ( $V_{DS}$ ) at T = 125 °C

Fig. 6. Drain-to-source leakage current ( $I_{DSS}$ ) vs. drain-to-source voltage ( $V_{DS}$ )

Fig. 8. Normalized on-resistance  $(R_{DS(ON)})$  vs. junction temperature  $(T_i)$

Final Datasheet 7 Rev Apr. 11, 2022

#### **Characteristic Graphs (Cont.)**

Fig. 9. Output capacitance  $(C_{OSS})$  vs. drain-to-source voltage  $(V_{DS})$

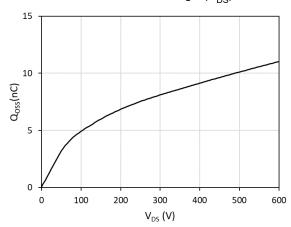

Fig. 11. Charge stored in output capacitance ( $Q_{OSS}$ ) vs. drain-to-source voltage ( $V_{DS}$ )

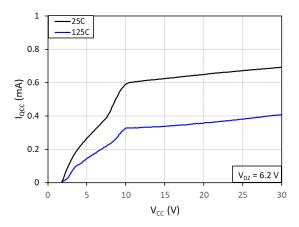

Fig. 13.  $V_{CC}$  quiescent current ( $I_{QCC}$ ) vs. supply voltage ( $V_{CC}$ )

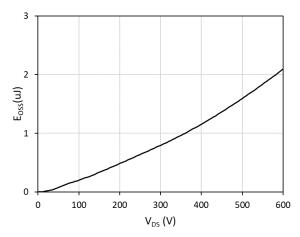

Fig. 10. Energy stored in output capacitance ( $E_{OSS}$ ) vs. drain-to-source voltage ( $V_{DS}$ )

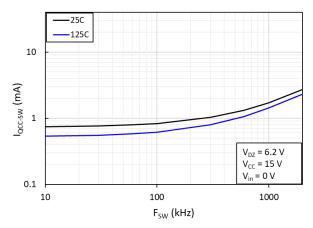

Fig. 12.  $V_{CC}$  operating current ( $I_{QCC-SW}$ ) vs. operating frequency ( $F_{SW}$ )

Fig. 14. Propagation delay ( $T_{ON}$  and  $T_{OFF}$ ) vs. junction temperature ( $T_{,J}$ )

Final Datasheet 8 Rev Apr. 11, 2022

# **Characteristic Graphs (Cont.)**

Fig. 15. Slew rate (dV/dt) vs. gate drive turn-on current set resistance ( $R_{\rm DD}$ ) at T = 25 °C

Fig. 17. Max. thermal transient impedance ( $Z_{\text{thJC}}$ ) vs. pulse width ( $t_{\rm p}$ )

Fig. 16. Power dissipation ( $P_{TOT}$ ) vs. case temperature ( $T_{C}$ )

Final Datasheet 9 Rev Apr. 11, 2022

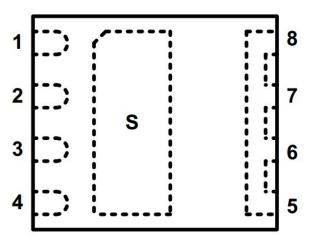

# 7. Internal Schematic, Pin Configurations and Functions

Package Top View

| F       | Pin             | I/O <sup>(1)</sup> | Description                                                                             |

|---------|-----------------|--------------------|-----------------------------------------------------------------------------------------|

| Number  | Symbol          | 1/0(**/            | Description                                                                             |

| 1       | V <sub>cc</sub> | Р                  | Supply voltage (10V to 24V)                                                             |

| 2       | PWM             | I                  | PWM input                                                                               |

| 3       | V <sub>DD</sub> | I                  | Gate drive supply voltage. Gate drive turn-on current set pin (using R <sub>DD</sub> ). |

| 4       | D <sub>z</sub>  | I                  | Gate drive supply voltage set pin (6.2 V Zener to GND).                                 |

| 5,6,7,8 | D               | Р                  | Drain of power FET                                                                      |

| PAD     | S               | O, G               | Source of power FET & GaN IC supply ground. Metal pad on bottom of package.             |

(1) I = Input, O = Output, P = Power, G = GaN IC Ground

Final Datasheet 10 Rev Apr. 11, 2022

#### 8. Functional Description

The following functional description contains additional information regarding the IC operating modes and pin functionality.

#### 8.1. Start Up

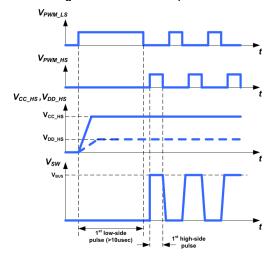

When the  $V_{CC}$  supply is first applied, care should be taken such that the  $V_{DD}$  and  $D_Z$  pins are up at their correct voltage levels before the PWM input signal starts. The  $V_{DD}$  pin ramp up time is determined by the internal regulator current at this pin and the external  $C_{VDD}$  capacitor.  $C_{VDD}$  time constant should be calculated such that there is sufficient time to charge up the  $C_{VDD}$  capacitor to  $\sim$ 6V. In some scenarios, where fast startup is required, an optional diode in parallel with the  $R_{DD}$  can be used to ensure the  $C_{VDD}$  capacitor is fully charged before the first PWM pulse is applied. Also, since the  $D_Z$  pin voltage sets the  $V_{DD}$  voltage level, the  $V_{DD}$  pin will ramp up together with the  $D_Z$  pin (Fig. 18).

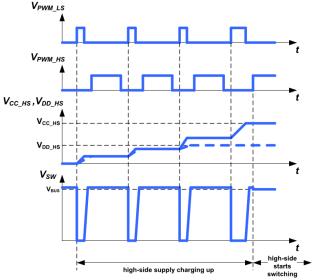

For half-bridge configurations, it is important that the  $V_{CC}$  supply, the  $D_Z$  pin, and the  $V_{DD}$  supply of the high-side GaNFast power IC are all charged up to their proper levels before the first high-side PWM pulses start. For LLC applications, a long on-time PWM pulse to the low-side (> 10  $\mu$ s) is typically provided by the LLC controller to allow the supply pins of the high-side device to charge up (through the external bootstrap diode) to their correct levels before the first high-side PWM pulses start (Fig. 19).

For active clamp flyback (ACF) applications, the halfbridge must be ready very quickly due to the soft-start mode of the ACF controller. When the first few PWM pulses are generated by the ACF controller, the highside supply pins of the power IC will require a few lowside pulses to charge up (through the external bootstrap diode) before the high-side starts to switch (Fig. 20).

Fig. 18. Quick start-up circuit

Fig. 19. LLC half-bridge start-up timing diagram

Fig. 20. ACF half-bridge start-up timing diagram

#### 8.2. Normal Operating Mode

During Normal Operating Mode, all of the internal circuit blocks are active.  $V_{CC}$  is operating within the recommended range of 10 V to 24 V, the  $V_{DD}$  pin is at the voltage set by the Zener diode at the  $D_Z$  pin (6.2 V), and the internal gate drive and power FET are both enabled. The external PWM signal at the PWM pin determines the frequency and duty-cycle of the internal gate of the power FET. As the PWM voltage toggles above and below the rising and falling input thresholds (4 V and 1 V), the internal gate of the power FET toggles on and off between  $V_{DD}$  and 0 V (Fig. 21). The drain of the power FET then toggles between the source voltage (typically power ground) and a higher voltage level (650 V max), depending on the external power conversion circuit topology.

Fig. 21. Normal operating mode timing diagram

#### 8.3. Standby Mode

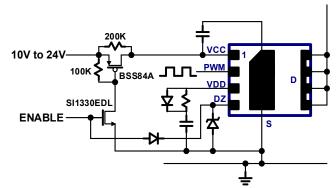

For applications where a low standby power is required, an external series cut-off circuit (Fig. 22) can be used to disconnect V<sub>CC</sub> of the GaNFast power IC from the main  $V_{CC}$  supply of the power supply. This will reduce  $V_{CC}$ current consumption when the converter is in burst mode during light-load or open load conditions. The V<sub>CC</sub> cut-off circuit consists of a series PMOS FET that is turned on and off with a pull-down NMOS FET. The gate of the NMOS is controlled by an external ENABLE signal that should be provided by the main controller of the power supply. The capacitor value at the V<sub>CC</sub> pin should then be selected according to the desired start-up speed, each time the ENABLE signal toggles high. A 22 nF capacitor at V<sub>CC</sub>, for example, will give a typical start-up time of approximately 2  $\mu$ s. An additional 200 k $\Omega$  resistor is placed across the PMOS cut-off FET to provide a small V<sub>CC</sub> voltage level for proper start-up.

Fig. 22. Standby mode V<sub>CC</sub> cut-off circuit

#### 8.4. Programmable Turn-on dV/dt Control

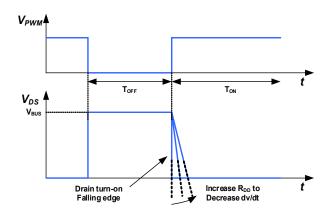

During first start-up pulses or during hard-switching conditions, it is desirable to limit the slew rate (dV/dt) of the drain of the power FET during turn-on. This is necessary to reduce EMI or reduce circuit switching noise. To program the turn-on dV/dt rate of the internal power FET, a resistor ( $R_{\rm DD}$ ) is placed in between the  $V_{\rm DD}$  capacitor and the  $V_{\rm DD}$  pin. This resistor ( $R_{\rm DD}$ ) sets the turn-on current of the internal gate driver and therefore sets the turn-on falling edge dV/dt rate of the drain of the power FET (Fig. 23). A typical turn-on slew-rate change with respect to  $R_{\rm DD}$  is shown in Fig. 15.

#### Minimum 10 $\Omega$ R<sub>DD</sub> is required.

Fig. 23. Turn-on dV/dt slew rate control

Final Datasheet 12 Rev Apr. 11, 2022

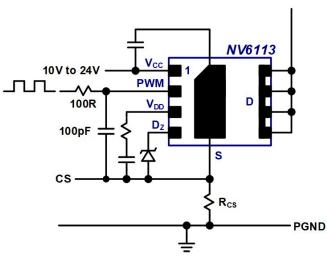

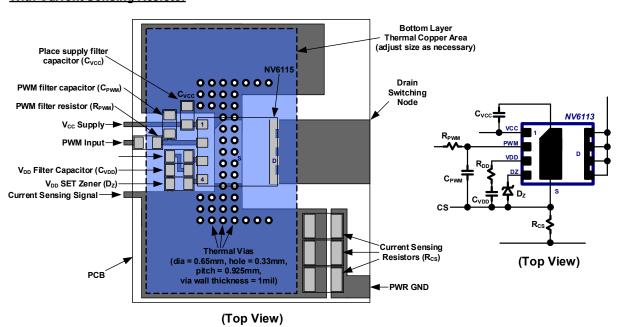

#### 8.5. Current Sensing

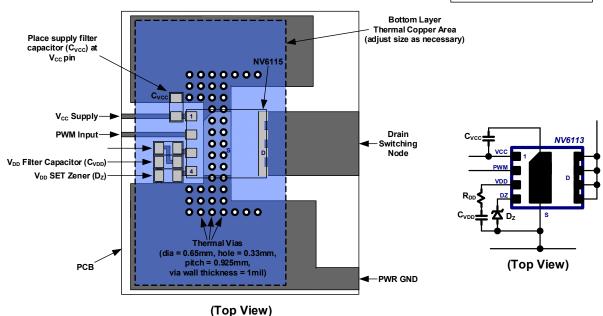

For many applications it is necessary to sense the cycle-by-cycle current flowing through the power FET. To sense the current flowing through the power IC, a standard current-sensing resistor can be placed in between the source and power ground (Fig. 24). In this configuration, all of the surrounding components ( $C_{\text{VCC}}$ ,  $C_{\text{VDD}}$ ,  $D_{\text{Z}}$ , etc.) should be grounded with a single connection at the source. Also, an additional RC filter can be inserted between the PWM signal and the PWM pin (100  $\Omega$ , 100 pF typical). This filter is necessary to prevent false triggering due to high-frequency voltage spikes occurring at the source node due to external parasitic inductance from the source PCB trace or the current-sensing resistor itself.

Fig. 24. Current sensing circuit

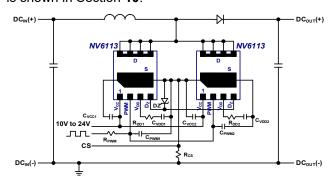

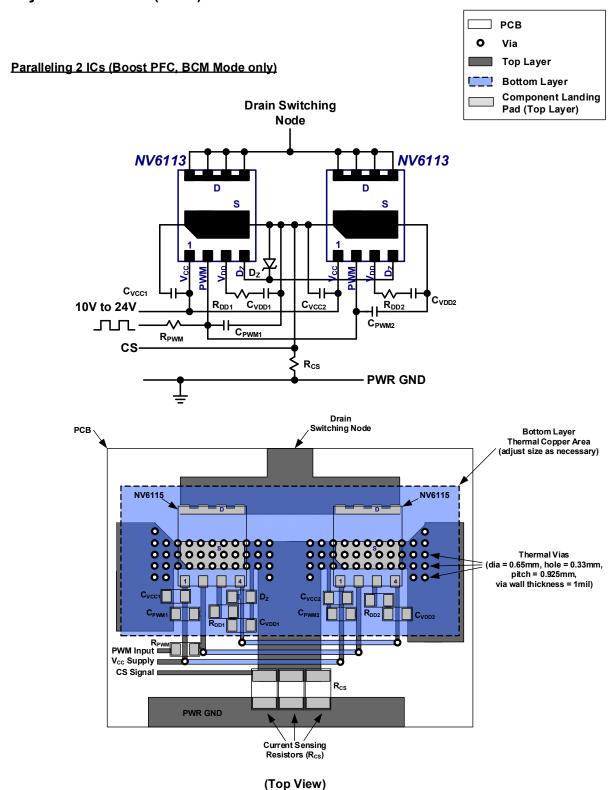

#### 8.6. Paralleling Devices

For some applications it is desirable to parallel ICs in order to reduce conduction losses and temperatures. Two GaNFast power ICs can be connected in parallel in a PFC boost application working in boundaryconduction mode (BCM) only. This configuration is shown in Fig. 25. The paired pins that are connected together include the drain pins (D), the source pins (S), the  $V_{CC}$  pins, the PWM pins, and the  $D_Z$ . A single  $D_Z$ diode can be shared by both ICs. The V<sub>DD</sub> pins are not connected together and require separate V<sub>DD</sub> supply capacitors ( $C_{\text{VDD1}}$ ,  $C_{\text{VDD2}}$ ) and separate turn-on current set resistors ( $R_{DD1}$ ,  $R_{DD2}$ ). Each IC should have its own local  $V_{CC}$  supply filter capacitor ( $C_{VCC1}$ ,  $C_{VCC2}$ ). The PWM pins can have a single filter resistor (R<sub>PWM</sub>) but separate filter capacitors ( $C_{PWM1}$ ,  $C_{PWM2}$ ) should be placed at the PWM pin of each IC. When designing the PCB layout for the two paralleled ICs, the drain and source connections should be made as symmetrical as possible to avoid any parasitic inductance or capacitance mismatch. A proper PCB layout example for paralleling is shown in Section 10.

Fig. 25. Boost schematic using two parallel ICs

Final Datasheet 13 Rev Apr. 11, 2022

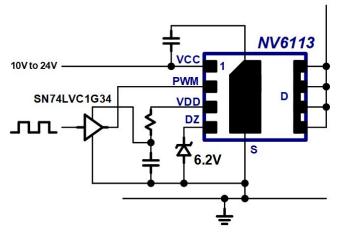

#### 8.7. 3.3V PWM Input Circuit

For some applications where a 3.3 V PWM signal is required (DSP, MCU, etc.) an additional buffer can be placed before the PWM input pin (Fig. 26) with the buffer supply voltage connected to the  $V_{DD}$  capacitor.

Fig. 26. 3.3 V PWM input buffer circuit

#### 8.8. PCB Layout Guidelines

The design of the PCB layout is critical for good noise immunity, sufficient thermal management, and proper operation of the IC. Typical PCB layout examples for without current sensing resistor, with current sensing resistor, and paralleling, are all shown in Section 10.

The following rules should be followed carefully during the design of the PCB layout:

- Place all IC filter and programming components directly next to the IC. These components include (C<sub>VCC</sub>, C<sub>VDD</sub>, R<sub>PWM</sub>, C<sub>PWM</sub>, R<sub>DD</sub> and D<sub>7</sub>).

- 2) Keep ground trace of IC filter and programming components separate from power GND trace. Do not run power GND currents through ground trace of filter components!

- 3) For best thermal management, place thermal vias in the source pad area to conduct the heat out through the bottom of the package and through the PCB board to other layers (see Section 10 for correct layout examples).

- 4) Use large PCB thermal planes (connected with thermal vias to the source pad) and additional PCB layers to reduce IC temperatures as much as possible (see Section 10 for correct layout examples).

- 5) For half-bridge layouts, do not extend copper planes from one IC across the components or pads of the other IC!

- 6) For high density designs, use a 4-layer PCB and 2 oz. copper to route signal connections. This allows layout to maintain large thermal copper planes and reduce power device temperature.

Final Datasheet 14 Rev Apr. 11, 2022

#### 8.9. Recommended Component Values

The following table (Table I) shows the recommended component values for the external filter capacitors, Zener diode, and  $R_{DD}$  connected to the pins of this GaNFast power IC. These components should be placed as close as possible to the IC. Please see PCB Layout guidelines for more information. The Zener diode at the  $D_Z$  pin should be a low-current type with a flat Zener, and the min/max limits must be followed.  $R_{DD}$  must be a minimum of 10  $\Omega$  to ensure application and device robustness.

| SYM              | DESCRIPTION                              | MIN | TYP  | MAX | UNITS |

|------------------|------------------------------------------|-----|------|-----|-------|

| C <sub>vcc</sub> | Maximum V <sub>cc</sub> supply capacitor |     | 0.1  |     | μF    |

| $C_{_{VDD}}$     | V <sub>DD</sub> supply capacitor         |     | 0.01 |     | μF    |

| R <sub>DD</sub>  | Gate drive turn-on current set resistor  | 10  | 25   |     | Ω     |

| $R_{_{PWM}}$     | PWM filter resistor                      |     | 100  |     | Ω     |

| $C_{_{PWM}}$     | PWM filter capacitor                     |     | 100  |     | pF    |

Table I. Recommended component values.

#### 8.9.1. Zener Selection

The Zener voltage is a critical parameter that sets the internal reference for gate drive voltage and other circuitry. The Zener diode needs to be selected such that the voltage on the  $D_Z$  pin is within recommended operating conditions (5.8 V to 6.6 V) across operating temperature (-40°C to 125°C) and bias current (10  $\mu$ A to 1 mA). To ensure effective operation, the current vs. voltage characteristics of the Zener diode should be measured down to 10  $\mu$ A to ensure flat characteristics across the current operating range (10  $\mu$ A to 1 mA). The recommended part numbers meet these requirements (See Table II). If the Zener selected by user does not ensure that the voltage on the Zener pin is always within the recommended operating range, the functionality and reliability of the GaNFast power IC can be impacted.

Only the following Zener diodes are to be used (Table II).

| SYM | DESCRIPTION                                                         | PART NO.      | SUPPLIER                            | MIN | TYP | MAX | UNITS |

|-----|---------------------------------------------------------------------|---------------|-------------------------------------|-----|-----|-----|-------|

|     |                                                                     | BZT52B6V2 RHG | Taiwan Semiconductor<br>Corporation |     |     |     |       |

| D   | D <sub>Z</sub> V <sub>DD</sub> set Zener diode (D <sub>Z</sub> pin) | MM3Z6V2ST1G   | ON-Semiconductor                    | 5.8 | 6.2 | 6.6 | V     |

| Z   |                                                                     | PDZ6.2B.115   | Nexperia (NXP)                      | 0.0 | 0.2 | 0.0 | , i   |

|     |                                                                     | PLVA662A.215  | Nexperia (NXP)                      |     |     |     |       |

|     |                                                                     | LM3Z6V2T1     | Leshan Radio Company                |     |     |     |       |

Table II. Qualified Zener diode components

Final Datasheet 15 Rev Apr. 11, 2022

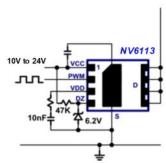

An external resistor ( $\sim$ 47 k $\Omega$ ) between V<sub>CC</sub> and D<sub>Z</sub> can improve Zener voltage stability by adding bias current to the Zener pin to ensure the voltage on the D<sub>Z</sub> pin is always within the recommended operating range (Fig. 27) This will add  $\sim$ 200  $\mu$ A of quiescent current.

Fig. 27. Increasing Zener bias current for stable Zener voltage

#### 8.10. Drain-to-Source Voltage Considerations

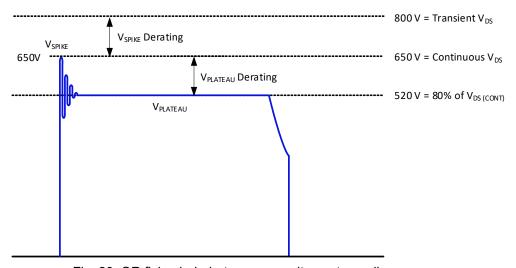

GaN Power ICs have been designed and tested to provide significant design margin to handle transient and continuous voltage conditions that are commonly seen in single-ended topologies, such as quasi-resonant (QR) flyback applications. The different voltage levels and recommended margins in a typical QR flyback can be analyzed using Fig. 28. When the device is switched off, the energy stored in the transformer leakage inductance will cause V<sub>DS</sub> to overshoot to the level of V<sub>SPIKE</sub>. The clamp circuit should be designed to control the magnitude of V<sub>SPIKE</sub>. It is recommended to apply an 80% derating from V<sub>DS (TRAN)</sub> rating (800V) to 650 V max for repetitive V<sub>DS</sub> spikes under the worst case steady-state operating conditions. After dissipation of the leakage energy, the device V<sub>DS</sub> will settle to the level of the bus voltage plus the reflected output voltage which is defined in Fig. 28 as V<sub>PLATEAU</sub>. It is recommended to design the system such that V<sub>PLATEAU</sub> follows a typical derating of 80% (520V) from V<sub>DS (CONT)</sub> (650V). Finally, V<sub>DS (TRAN)</sub> (800V) rating is also provided for events that occur on a non-repetitive basis, such as line surge, lightning strikes, start-up, over-current, short-circuit, load transient, and output voltage transition. 800V V<sub>DS(TRAN)</sub> ensures excellent device robustness and no-derating is needed for these non-repetitive events, assuming the surge duration is < 100 μs. For half-bridge based topologies, such as LLC, V<sub>DS</sub> voltage is clamped to the bus voltage. V<sub>DS</sub> should be designed such that it meets the V<sub>PLATEAU</sub> derating guideline (520V).

Fig. 28. QR flyback drain-to-source voltage stress diagram

Final Datasheet 16 Rev Apr. 11, 2022

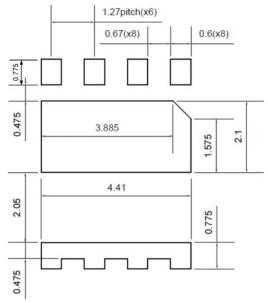

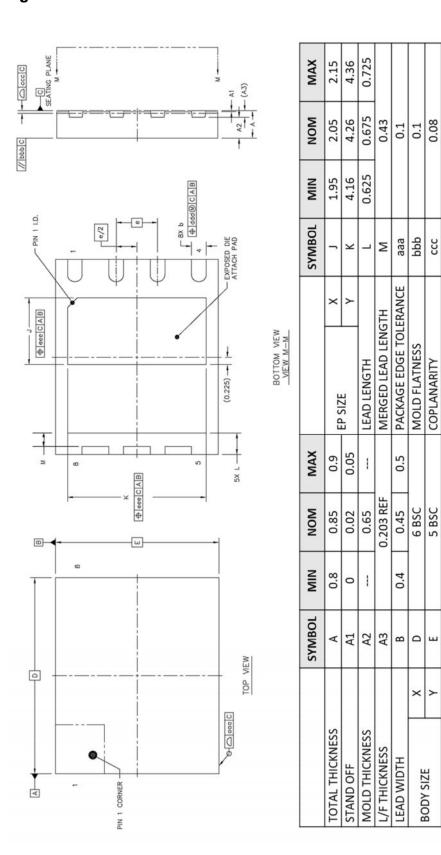

#### 9. Recommended PCB Land Pattern

All dimensions are in mm

#### 10. PCB Layout Guidelines

# PCB Via Top Layer Bottom Layer Component Landing Pad (Top Layer)

#### **Without Current Sensing Resistor**

#### With Current Sensing Resistor

Final Datasheet 18 Rev Apr. 11, 2022

# **PCB Layout Guidelines (cont.)**

0.1

ddd

**EXPOSED PAD OFFSET**

**LEAD OFFSET**

1.27 BSC

LEAD PITCH

#### 11. QFN Package Outline

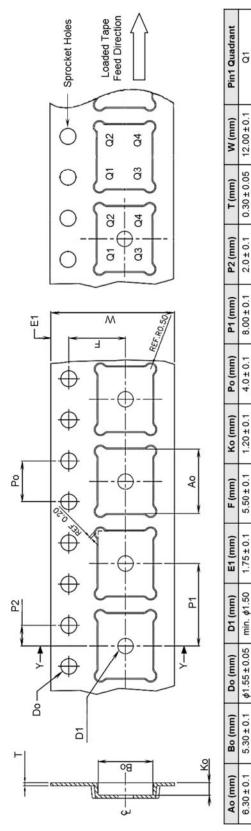

# 12. Tape and Reel Dimensions

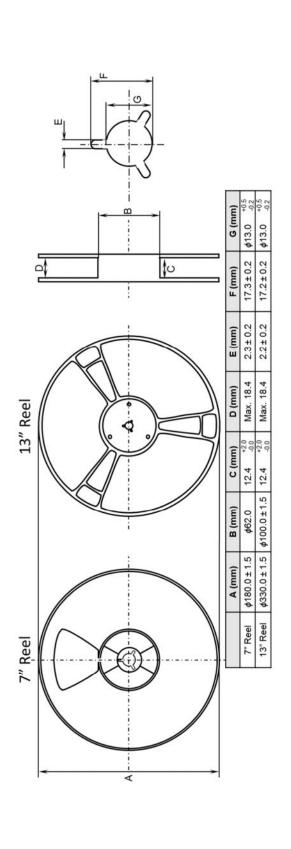

#### 13. Ordering Information

| Part Number | Operating Temperature Grade         | Storage<br>Temperature Range        | Package      | MSL<br>Rating | Packing<br>(Tape & Reel) |

|-------------|-------------------------------------|-------------------------------------|--------------|---------------|--------------------------|

| NV6113 RA   | -40 °C to +125 °C T <sub>CASE</sub> | -55 °C to +150 °C T <sub>CASE</sub> | 5 x 6 mm QFN | 1             | 1,000 : 7" Reel          |

| NV6113      | -40 °C to +125 °C TCASE             | -55 °C to +150 °C TCASE             | 5 x 6 mm QFN | 1             | 5,000 : 13" Reel         |

#### 14. 20-Year Limited Product Warranty

The 20-year limited warranty applies to all packaged Navitas GaNFast Power ICs in mass production, subject to the terms and conditions of, Navitas' express limited product warranty, available at <a href="https://navitassemi.com/terms-conditions">https://navitassemi.com/terms-conditions</a>. The warranted specifications include only the MIN and MAX values only listed in Absolute Maximum Ratings, ESD Ratings and Electrical Characteristics sections of this datasheet. Typical (TYP) values or other specifications are not warranted.

#### 15. Revision History

| Date         | Status          | Notes                                                                                                                                                      |

|--------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Aug 28, 2018 | Initial Release | First publication                                                                                                                                          |

| Nov 22, 2019 | Revised         | Updated MSL rating, added Section 8.10, updated Section 8.3 and figure 22.                                                                                 |

| Jun 22, 2020 | Revised         | Updated guidelines in Section 8.1: Fast startup. Updated R <sub>DD</sub> specification. This datasheet revision applies to product prior to PCN2020-09-15. |

| Oct 27, 2020 | Revised         | Datasheet updated in alignment with PCN2020-09-15. Product is marked with Lot Code ending in Z for traceability                                            |

| Apr 11, 2022 | Revised         | Added 20-Year Limited Product Warranty                                                                                                                     |

#### **Additional Information**

DISCLAIMER Navitas Semiconductor Inc. (Navitas) reserves the right to modify the products and/or specifications described herein at any time and at Navitas' sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied. This document is presented only as a guide and does not convey any license under intellectual property rights of Navitas or any third parties.

Navitas' products are not intended for use in applications involving extreme environmental conditions or in life support systems.

Products supplied under Navitas Terms and Conditions.

Navitas Semiconductor, Navitas, GaNFast and associated logos are registered trademarks of Navitas.

Copyright ©2022 Navitas Semiconductor Inc. All rights reserved

Contact info@navitassemi.com

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Navitas Semiconductor:

NV6113 NV6113-RA