# Preliminary Product Specification

| Rev. 0.85|

G2 Silver

Embedded Multimedia Card 153 Ball eMMC 5.1

(16GB - 128GB)

## Content

| 1 | PR   | RODUCT SUMMARY                         | 5  |

|---|------|----------------------------------------|----|

| 2 | OF   | RDER INFORMATION                       | 6  |

| 3 | PR   | RODUCT INTRODUCTION                    | 7  |

|   | 3.1  | DEVICE PERFORMANCE                     | 7  |

|   | 3.2  | USER DENSITY AND PARTITION             |    |

|   | 3.3  | TEMPERATURE                            |    |

|   | 3.4  | Power Consumption                      |    |

| 4 |      | MMC DEVICE AND SYSTEM                  |    |

| 4 |      |                                        | _  |

|   | 4.1  | EMMC SYSTEM OVERVIEW                   |    |

|   | 4.2  | MEMORY ADDRESSING                      |    |

|   | 4.3  | EMMC DEVICE OVERVIEW                   |    |

|   | 4.4  | Bus Protocol                           |    |

|   | 4.5  | BUS SPEED MODES                        |    |

| 5 | EN   | MMC FUNCTION DESCRIPTION               |    |

|   | 5.1  | EMMC OVERVIEW                          |    |

|   | 5.2  | BOOT OPERATION MODE                    |    |

|   | 5.3  | DEVICE IDENTIFICATION MODE             |    |

|   | 5.4  | INTERRUPT MODE                         |    |

|   | 5.5  | Data Transfer Mode                     |    |

|   | 5.6  | INACTIVE MODE                          |    |

|   | 5.7  | FIELD FIRMWARE UPDATE(FFU)             |    |

|   | 5.8  | Power off Notification for sleep       |    |

|   | 5.9  | ENHANCED USER DATA AREA                |    |

|   | 5.10 |                                        |    |

|   | 5.11 | CACHE ENHANCEMENT BARRIER              |    |

|   | 5.12 |                                        |    |

|   | 5.13 | ,                                      |    |

|   | 5.14 | PRODUCTION STATE AWARENESS (PSA)       | 21 |

| 6 | RE   | EGISTER SETTINGS                       | 22 |

|   | 6.1  | OCR REGISTER                           | 22 |

|   | 6.2  | CID REGISTER                           | 22 |

|   | 6.3  | CSD REGISTER                           |    |

|   | 6.4  | EXTENDED CSD REGISTER                  | 24 |

|   | 6.5  | RCA REGISTER                           | 27 |

|   | 6.6  | DSR REGISTER                           | 27 |

| 7 | TH   | HE EMMC BUS                            | 28 |

|   | 7.1  | Power-up                               |    |

|   | 7.2  | BUS OPERATING CONDITIONS               | 30 |

|   | 7.3  | BUS SIGNAL LEVELS                      | 34 |

|   | 7.4  | Bus Timing                             |    |

|   | 7.5  | BUS TIMING SPECIFICATION IN HS200 MODE |    |

|   | 7.6  | BUS TIMING SPECIFICATION IN HS400 MODE | 44 |

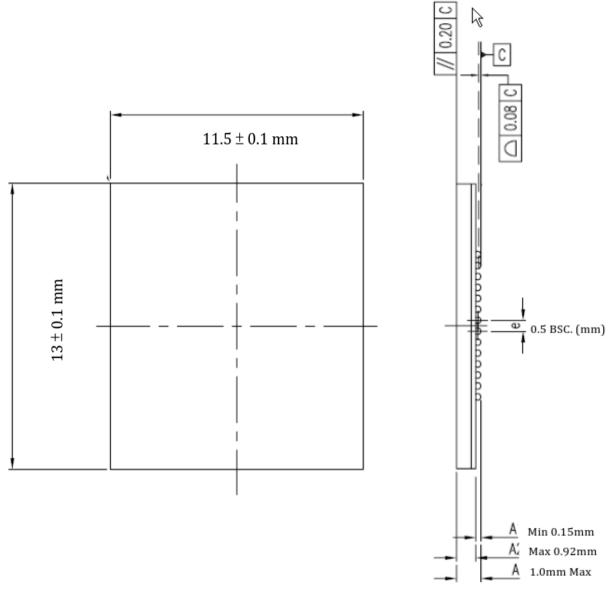

| 8 | PA   | ACKAGE DIMENSIONS                      | 47 |

|   | 8.1  | PACKAGE DIMENSIONS                     |    |

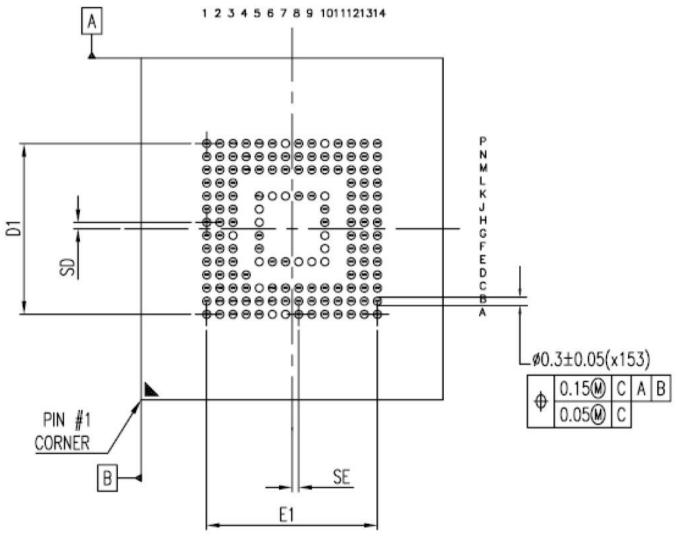

|   | 8.2  | BALL PATTERN DIMENSIONS (BOTTOM VIEW)  | 48 |

|   | 8.3  | BALL ASSIGNMENT (153 BALLS)            | 49 |

| 9 | EN   | MMC DEVICE SIGNAL                      | 50 |

|   |      |                                        |    |

#### DATASHEET

| ISION HISTORY | 51 |

|---------------|----|

|               |    |

# List of Figures

| FIGURE 1 – EMMC SYSTEM OVERVIEW                                             |    |

|-----------------------------------------------------------------------------|----|

| FIGURE 2 – HS200 BLOCK DIAGRAM                                              | 13 |

| FIGURE 3 – HS400 BLOCK DIAGRAM                                              |    |

| FIGURE 4 – H/W RESET WAVEFORM                                               |    |

| FIGURE 5 – NOISE FILTERING TIMING FOR H/W RESET                             |    |

| FIGURE 6 – BUS CIRCUITRY DIAGRAM                                            |    |

| FIGURE 7 – EMMC POWER-UP DIAGRAM                                            |    |

| FIGURE 8 – THE EMMC POWER CYCLE                                             |    |

| FIGURE 9 – EMMC INTERNAL POWER DIAGRAM                                      |    |

| FIGURE 10 – HS400 REFERENCE LOAD                                            |    |

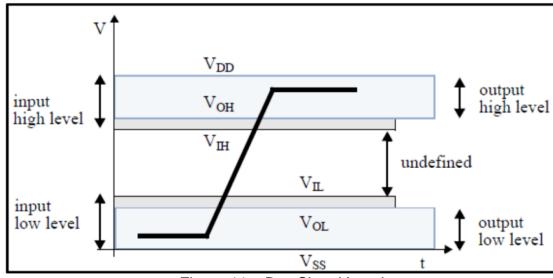

| FIGURE 11 – BUS SIGNAL LEVELS                                               |    |

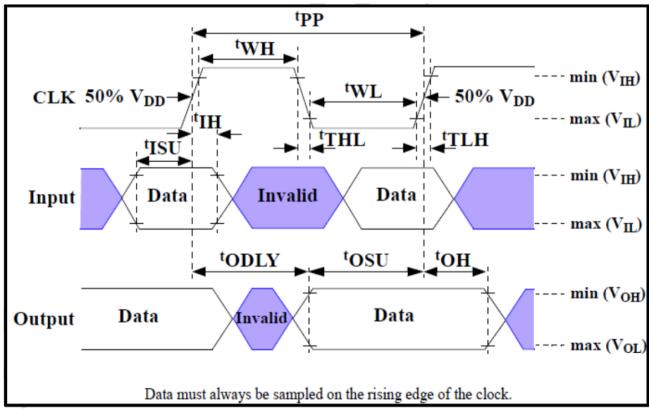

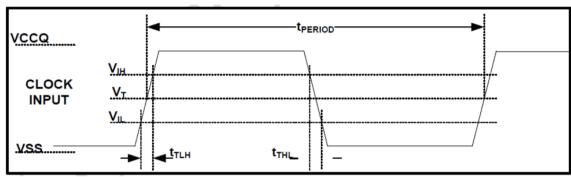

| FIGURE 12 – TIMING DIAGRAM                                                  |    |

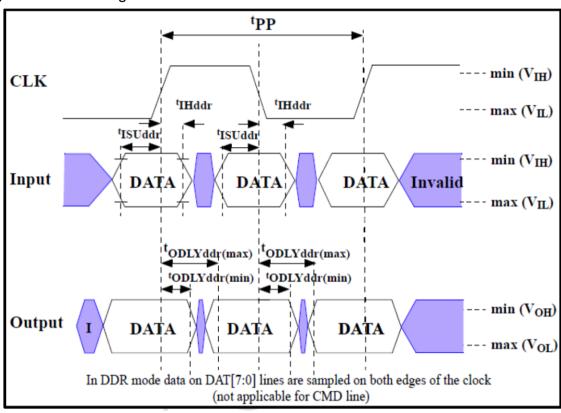

| FIGURE 13 – TIMING DIAGRAM: DATA INPUT/OUTPUT IN DUAL DATA RATE MODE        |    |

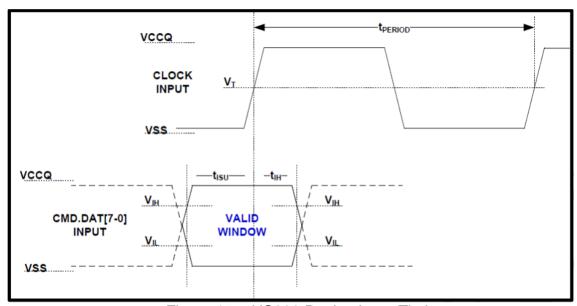

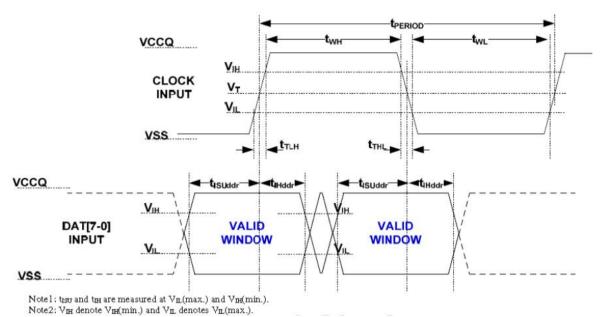

| FIGURE 14 – HS200 CLOCK SIGNAL TIMING                                       |    |

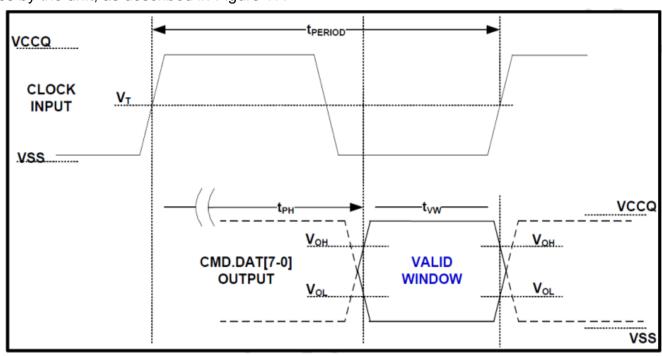

| FIGURE 15 – HS200 DEVICE INPUT TIMING                                       |    |

| FIGURE 16 – HS200 DEVICE OUTPUT TIMING                                      |    |

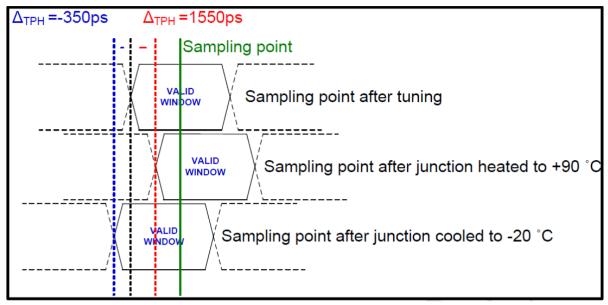

| FIGURE 17 – ΔT <sub>PH</sub> CONSIDERATION                                  |    |

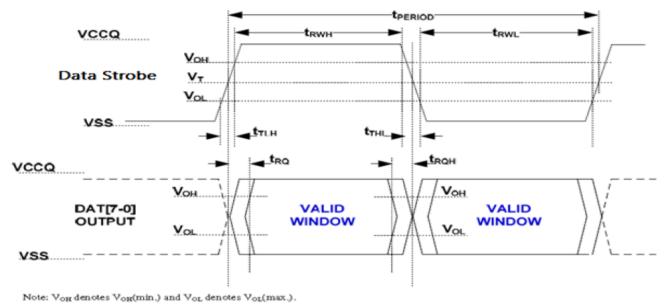

| FIGURE 18 – HS400 DEVICE DATA INPUT TIMING                                  |    |

| FIGURE 19 – HS400 DEVICE OUTPUT TIMING                                      |    |

| FIGURE 20 – OUTLINE DIMENSION                                               |    |

| FIGURE 21 – BALL PATTERN DIMENSIONS                                         |    |

| FIGURE 22 – BALL ASSIGNMENT (TOP VIEW)                                      | 49 |

| List of Tables  TABLE 1 – PART NUMBER                                       |    |

| TABLE 2 – READ/WRITE PERFORMANCE                                            |    |

| TABLE 3 – USER DENSITY AND PARTITION                                        |    |

| TABLE 4 – TEMPERATURE RANGE                                                 |    |

| TABLE 5 – POWER CONSUMPTION                                                 |    |

| TABLE 6 – COMMUNICATION INTERFACE                                           |    |

| TABLE 7 – EMMC REGISTERS                                                    |    |

| TABLE 8 – BUS SPEED MODE                                                    |    |

| TABLE 9 - H/W RESET TIMING PARAMETERS                                       |    |

| TABLE 10 – CID REGISTER                                                     |    |

| TABLE 11 – CSD REGISTER                                                     |    |

| TABLE 12 – EXTENDED CSD REGISTER                                            |    |

| TABLE 13 – GENERAL OPERATING CONDITIONS                                     |    |

| TABLE 14 – EMMC OPERATING VOLTAGE                                           |    |

| TABLE 15 – EMMC VOLTAGE COMBINATIONS                                        |    |

| TABLE 16 – SIGNAL LINE LOAD                                                 | 32 |

| TABLE 17 – OPEN-DRAIN BUS SIGNAL LEVEL                                      |    |

| TABLE 18 – PUSH-PULL SIGNAL LEVEL—HIGH-VOLTAGE EMMC                         |    |

| TABLE 19 – PUSH-PULL SIGNAL LEVEL—1.70 -1.95 V <sub>CCQ</sub> VOLTAGE RANGE |    |

| TABLE 20 – HIGH-SPEED DEVICE INTERFACE TIMING                               |    |

| TABLE 21 – BACKWARD-COMPATIBLE DEVICE INTERFACE TIMING                      |    |

| TABLE 22 – HIGH-SPEED DUAL DATA RATE INTERFACE TIMING                       |    |

| TABLE 23 – HS200 CLOCK SIGNAL TIMING                                        |    |

| TABLE 24 – HS200 DEVICE INPUT TIMING                                        |    |

| TABLE 25 – OUTPUT TIMING                                                    |    |

| TABLE 26 – HS400 DEVICE INPUT TIMING                                        |    |

| TABLE 27 – HS400 DEVICE OUTPUT TIMING                                       |    |

| TABLE 28 – HS400 CAPACITANCE                                                |    |

| TABLE 29 – DEVICE SIGNAL                                                    | 50 |

## 1 Product Summary

<u>Capacity Range</u> **16GB – 128GB**

<u>Form Factor</u> **FBGA 153** (11.5x13.0mm, 0.5mm pitch)

Interface eMMC 5.1

Backward compatible eMMC Specification Ver.4.4, 4.41, 4.5, 5.0

Bus Mode High-speed eMMC protocol, Clock frequency: 0-200MHz

<u>Transfer Rate</u> Data transfer rate: up to 52Mbyte/s (8 data lines @52 MHz)

Single data rate: up to 200Mbyte/s @ 200MH Dual data rate: up to 400Mbyte/s @ 200MHz

Performance Sequential read: up to 315 MB/s

Sequential write: up to 240 MB/s

Operation Voltage VCCQ = 3.3 /1.8 V or 1.8 V\*

VCC = 3.3 V

**Operating Temperature**

Industrial Grade : -40°C ~ 85°C

Automotive Grade 2: -40°C ~ 105°C

Storage Temperature -40°C ~ 85°C

Quality RoHS compliant \*\*

Note: \* refer to detail Vccq description of each part number in Chapter 2.

\*\* for detailed RoHS declaration, please contact your I'M representative.

## 2 Order Information

Table 1 – Part Number

| Product Part Number     | Density | Operating Voltage | Operation<br>Temperature        |

|-------------------------|---------|-------------------|---------------------------------|

| IMC1B1A6C1A0A1I3A5A0000 | 16GB    |                   |                                 |

| IMC1B1A6C1A0A1I3A6A0000 | 32GB    | Vcc=3.3V          | -40°C ~ 85°C                    |

| IMC1B1A8C1A0A1I3A8A0000 | 64GB    | Vccq=1.8V/3.3V    | 10 0 00 0                       |

| IMC1B1B1C1A0A1I3B1A0000 | 128GB   |                   |                                 |

| IMC1B1A6C1A0A1A3A5A0000 | 16GB    |                   |                                 |

| IMC1B1A6C1A0A1A3A6A0000 | 32GB    | Vcc=3.3V          | -40°C ~ 105°C<br>AEC-Q100 Grade |

| IMC1B1A8C1A0A1A3A8A0000 | 64GB    | Vccq=1.8V         | 2 2                             |

| IMC1B1B1C1A0A1A3B1A0000 | 128GB   |                   |                                 |

## 3 Product Introduction

I'M eMMC product family provides the ideal embedded storage solution for the Industrial and Medical applications, which require high performance, endurance across a wide range of operating temperatures, and good technical support. I'M eMMC integrates NAND Flash memory and a sophisticated eMMC controller inside a standard package, providing a standard interface to the host. The controller directly manages the NAND flash, implementing functions like bad block management, error handling (ECC), static and dynamic wear-leveling, IOPS optimization and read sensing. I'M eMMC supports Enhanced User Data Area feature which allows the User Data Area of eMMC to be configured for higher read/write performance, endurance and reliability.

#### 3.1 Device Performance

Table 2 – Read/Write Performance

| Doving Canacity | Typical value          |                         |  |  |  |

|-----------------|------------------------|-------------------------|--|--|--|

| Device Capacity | Read Sequential (MB/s) | Write Sequential (MB/s) |  |  |  |

| 16GB            | 320                    | 135                     |  |  |  |

| 32GB            | 320                    | 135                     |  |  |  |

| 64GB            | 320                    | 255                     |  |  |  |

| 128GB           | 320                    | 265                     |  |  |  |

Notes: 1. Values given for an 8-bit bus width, running HS400 mode from I'M proprietary tool, Vcc =3.3V, Vccq =1.8V.

<sup>2.</sup> Performance numbers might be subject to changes without notice.

## 3.2 User Density and Partition

Table 3 – User Density and Partition

| Device   | Partition             |         |         |         |  |  |  |

|----------|-----------------------|---------|---------|---------|--|--|--|

| Capacity | User Density          | Boot 1  | Boot 2  | RPMB    |  |  |  |

| 16GB     | 15,552,479,232 Bytes  | 4096 KB | 4096 KB | 4096 KB |  |  |  |

| 32GB     | 31,268,536,320 Bytes  | 4096 KB | 4096 KB | 4096 KB |  |  |  |

| 64GB     | 62,537,072,640 Bytes  | 4096 KB | 4096 KB | 4096 KB |  |  |  |

| 128GB    | 125,074,145,280 Bytes | 4096 KB | 4096 KB | 4096 KB |  |  |  |

## 3.3 Temperature

Table 4 – Temperature Range

| Parameter             | Grade      | Range       | Remark           |

|-----------------------|------------|-------------|------------------|

| Operating Temperature | Industrial | -40~+85 °C  |                  |

| Operating Temperature | Automotive | -40~+125 °C | AEC-Q100 Grade 2 |

| Storage Temperature   | All        | -40~+85 °C  |                  |

## 3.4 Power Consumption

Table 5 – Power Consumption

| Products                   | Read (mA) |           | Write (mA) |           | Standby (mA) |           |

|----------------------------|-----------|-----------|------------|-----------|--------------|-----------|

| Device Capacity VCCQ(1.8V) |           | VCC(3.3V) | VCCQ(1.8V) | VCC(3.3V) | VCCQ(1.8V)   | VCC(3.3V) |

| 16GB                       | 220       | 55        | 90         | 50        | 0.24         | 0.03      |

| 32GB                       | 220       | 55        | 90         | 50        | 0.24         | 0.03      |

| 64GB                       | 230       | 60        | 100        | 90        | 0.25         | 0.05      |

| 128GB                      | 245       | 60        | 105        | 160       | 0.25         | 0.08      |

Note 1: Values given for an 8-bit bus width, a clock frequency of 200MHz DDR mode, Vcc = 3.3V±5%, Vccq =1.8V±5%

Note 2: Standby current is measured at  $Vcc=3.3V\pm5\%$ , 8-bit bus width without clock frequency.

Note 3: Current numbers might be subject to changes without notice.

Note 4: The measurement for max RMS current is done as average RMS current consumption over a period of 100ms.

## 4 eMMC Device and System

#### 4.1 eMMC System Overview

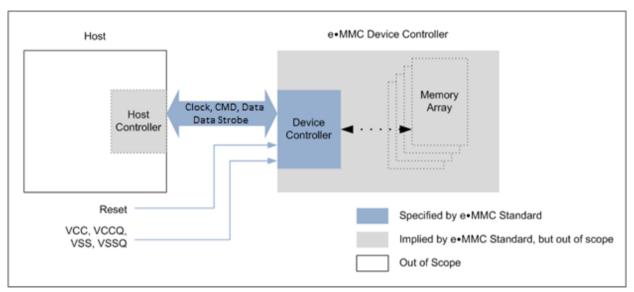

The eMMC specification covers the behavior of the interface and the Device controller. As part of this specification the existence of a host controller and a memory storage array are implied, but the operation of these pieces is not fully specified. **I'M** eMMC Device consists of a single chip MMC controller and NAND flash memory module. The micro-controller interfaces with a host system allowing data to be written to and read from the NAND flash memory module. The controller allows the host to be independent from details of erasing and programming the flash memory.

Figure 1 – eMMC System Overview

## 4.2 Memory Addressing

Previous implementations of the eMMC specification are following byte addressing with 32 bit field. This addressing mechanism permitted for eMMC densities up to and including 2 GB. To support larger densities the addressing mechanism was update to support sector addresses (512 Bytes sectors). The sector addresses shall be used for all devices with capacity larger than 2 GB. To determine the addressing mode use the host should read bit [30:29] in the OCR register.

#### 4.3 eMMC Device Overview

The eMMC device transfers data via a configurable number of data bus signals. The communication signals are:

#### 4.3.1 Clock (CLK)

Each cycle of this signal directs a one bit transfer on the command and either a one bit (1x) or a two bits transfer (2x) on all the data lines. The frequency may vary between zero and the maximum clock frequency.

#### 4.3.2 Data Strobe(DS)

This signal is generated by the device and used for output in HS400 mode. The frequency of this signal follows the frequency of CLK. For data output each cycle of this signal directs two bits transfer(2x) on the data – one bit for positive edge and the other bit for negative edge. For CRC status response output and CMD response output (enabled only HS400 enhanced strobe mode), the CRC status is latched on the positive edge only, and don't care on the negative edge.

#### 4.3.3 Command (CMD)

This signal is a bidirectional command channel used for Device initialization and transfer of commands. The CMD signal has two operation modes: open-drain for initialization mode, and push-pull for fast command transfer. Commands are sent from the eMMC host controller to the eMMC Device and responses are sent from the Device to the host.

#### 4.3.4 Input/Outputs (DAT0-DAT7)

These are bidirectional data channels. The DAT signals operate in push-pull mode. Only the Device or the host is driving these signals at a time. By default, after power up or reset, only DAT0 is used for data transfer. A wider data bus can be configured for data transfer, using either DAT0-DAT3 or DAT0-DAT7, by the eMMC host controller. The eMMC Device includes internal pull-ups for data lines DAT1-DAT7. Immediately after entering the 4-bit mode, the Device disconnects the internal pull ups of lines DAT1, DAT2, and DAT3. Correspondingly, immediately after entering to the 8-bit mode the Device disconnects the internal pull-ups of lines DAT1-DAT7.

Table 6 - Communication Interface

| Name  | Type1     | Description                    |  |  |

|-------|-----------|--------------------------------|--|--|

| CLK   | I         | Clock                          |  |  |

| DAT0  | I/O/PP    | Data                           |  |  |

| DAT1  | I/O/PP    | Data                           |  |  |

| DAT2  | I/O/PP    | Data                           |  |  |

| DAT3  | I/O/PP    | Data                           |  |  |

| DAT4  | I/O/PP    | Data                           |  |  |

| DAT5  | I/O/PP    | Data                           |  |  |

| DAT6  | I/O/PP    | Data                           |  |  |

| DAT7  | I/O/PP    | Data                           |  |  |

| CMD   | I/O/PP/OD | Command/Response               |  |  |

| RST_n | I         | Hardware reset                 |  |  |

| VCC   | S         | Supply voltage for Core        |  |  |

| VCCQ  | S         | Supply voltage for I/O         |  |  |

| VSS   | S         | Supply voltage ground for Core |  |  |

| VSSQ  | S         | Supply voltage ground for I/O  |  |  |

| DS    | O/PP      | Data strobe                    |  |  |

Notes: 1.I: input; O: output; PP: push-pull; OD: open-drain; NC: Not connected (or logical high); S: power supply.

#### Table 7 – eMMC Registers

| Name    | Width<br>(Bytes) | Description                                                                                                              | Implementation |

|---------|------------------|--------------------------------------------------------------------------------------------------------------------------|----------------|

| CID     | 16               | Device Identification number, an individual number for identification.                                                   | Mandatory      |

| RCA     | 2                | Relative Device Address is the Device system address, dynamically assigned by the host during initialization.            | Mandatory      |

| DSR     | 2                | Driver Stage Register, to configure the Device's output drivers.                                                         | Optional       |

| CSD     | 16               | Device Specific Data, information about the Device operation conditions.                                                 | Mandatory      |

| OCR     | 4                | Operation Conditions Register. Used by a special broadcast command to identify the voltage type of the Device.           | Mandatory      |

| EXT_CSD | 512              | Extended Device Specific Data. Contains information about the Device capabilities and selected modes. Introduced in stan | Mandatory      |

The host may reset the device by:

- Switching the power supply off and back on. The device shall have its own power-on detection circuitry which puts the device into a defined state after the power-on Device.

- A reset signal

- By sending a special command

#### 4.4 Bus Protocol

After a power-on reset, the host must initialize the device by a special message based on eMMC bus protocol. For more details, refer to section 5.3.1 of the JEDEC Standard Specification No.JESD84-B51.

#### 4.5 Bus Speed Modes

eMMC defines several bus speed modes as shown in Table 8.

Table 8 - Bus Speed Mode

| Mode Name                                                      | Data Rate | IO Voltage | Bus Width | Frequency | Max Data Transfer (implies x8 bus width) |  |

|----------------------------------------------------------------|-----------|------------|-----------|-----------|------------------------------------------|--|

| Backwards Compatibility with legacy MMC card                   | Single    | 3.3/1.8V*  | 1, 4, 8   | 0-26MHz   | 26MB/s                                   |  |

| High speed SDR                                                 | Single    | 3.3/1.8V*  | 4, 8      | 0-52MHz   | 52MB/s                                   |  |

| High speed DDR                                                 | Dual      | 3.3/1.8V*  | 4, 8      | 0-52MHz   | 104MB/s                                  |  |

| HS200                                                          | Single    | 1.8V       | 4, 8      | 0-200MHz  | 200MB/s                                  |  |

| HS400                                                          | Dual      | 1.8V       | 8         | 0-200MHz  | 400MB/s                                  |  |

| Note: I/O voltage 3.3V is only available for Industrial grade. |           |            |           |           |                                          |  |

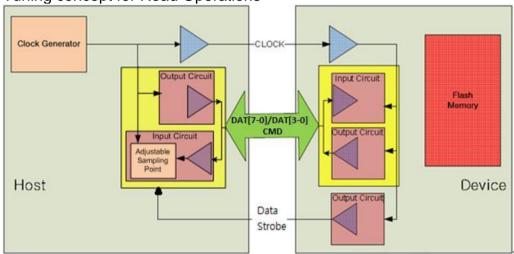

#### 4.5.1. HS200 Bus Speed Mode

Figure 2 shows a typical HS200 Host and Device system. The host has a clock generator, which supplies CLK to the Device. For write operations, clock and data direction are the same, write data can be transferred synchronous with CLK, regardless of transmission line delay. For read operations, clock and data direction are opposite; the read data received by Host is delayed by round-trip delay, output

delay and latency of Host and Device. For reads, the Host needs to have an adjustable sampling point to reliably receive the incoming data.

The HS200 mode offers the following features:

- SDR Data sampling method

- CLK frequency up to 200MHz Data rate up to 200MB/s

- 8-bits bus width supported

- Single ended signaling with 4 selectable Drive Strength

- Signaling levels of 1.8V

- Tuning concept for Read Operations

Figure 2 – HS200 Block Diagram

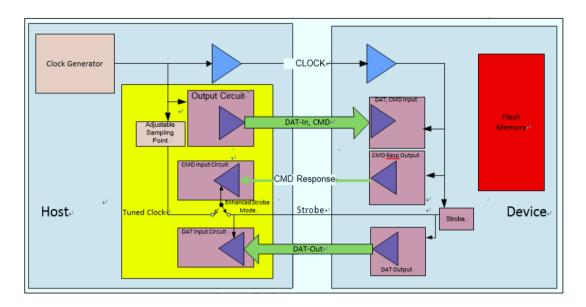

#### 4.5.2. HS400 Bus Speed Mode

Figure 3 shows a typical HS400 Host and Device system. The host has a clock generator, which supplies CLK to the Device. For read operations, Data Strobe is generated by device output circuit. Host receives the data which is aligned to the edge of Data Strobe.

The HS400 mode offers the following features:

- DDR Data sampling method

- CLK frequency up to 200MHz, Data rate is up to 400MB/s

- Only 8-bit bus width supported

- Signaling levels of 1.8V

- Support up to 5 selective Drive Strength

- Data strobe signal is toggled only for Data out and CRC response

Figure 3 – HS400 Block Diagram

## 5 eMMC Function Description

#### 5.1 eMMC Overview

All communication between host and device are controlled by the host (main chip). The host sends a command, which results in a device response. For more details, refer to section 6.1 of the JEDEC Standard Specification No.JESD84-B51.

Five operation modes are defined for eMMC system:

- Boot operation mode

- Device identification mode

- Interrupt mode

- Data transfer mode

- Inactive mode

### 5.2 Boot Operation Mode

In boot operation mode, the master (eMMC host) can read boot data from the slave (eMMC device) by keeping CMD line low or sending CMD0 with argument + 0xFFFFFFA, before issuing CMD1. The data can be read from either boot area or user area depending on register setting. For more details, refer to section 6.3 of the JEDEC Standard Specification No.JESD84-B51.

#### 5.3 Device Identification Mode

While in device identification mode the host resets the device, validates operation voltage range and access mode, identifies the device and assigns a Relative device Address (RCA) to the device on the bus. All data communication in the Device Identification Mode uses the command line (CMD) only. For more details, refer to section 6.4 of the JEDEC Standard Specification No.JESD84-B51.

#### 5.4 Interrupt Mode

The interrupt mode on the eMMC system enables the master (eMMC host) to grant the transmission allowance to the slaves (Device) simultaneously. This mode reduces the polling load for the host and hence, the power consumption of the system, while maintaining adequate responsiveness of the host to a Device request for service. Supporting eMMC interrupt mode is an option, both for the host and the Device. For more details, refer to section 6.5 of the JEDEC Standard Specification No.JESD84-B51.

#### 5.5 Data Transfer Mode

When the Device is in Stand-by State, communication over the CMD and DAT lines will be performed in push-pull mode. For more details, refer to section 6.6 of the JEDEC Standard Specification No.JESD84-B51.

#### 5.6 Inactive Mode

The device will enter inactive mode if either the device operating voltage range or access mode is not valid. The device can also enter inactive mode with GO\_INACTIVE\_STATE command (CMD15). The device will reset to Pre-idle state with power cycle. For more details, refer to section 6.1 of the JEDEC Standard Specification No.JESD84-B51.

#### 5.6.1 H/W Reset Operation

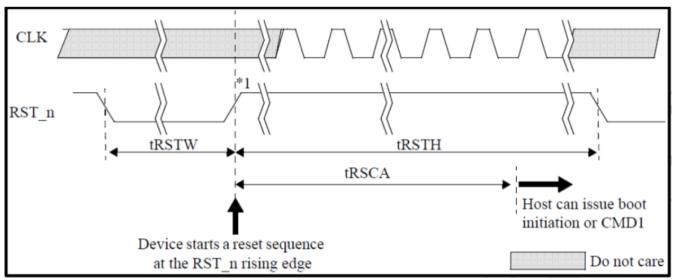

Figure 4 - H/W Reset Waveform

Notes: 1. Device will detect the rising edge of RST\_n signal to trigger internal reset sequence

Table 9 – H/W Reset Timing Parameters

| Symbol           | Commont                                                                                         | Min  | Max  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------|------|------|--|--|--|--|

| Symbol           | Comment                                                                                         |      | (us) |  |  |  |  |

| tRSTW            | RST_n pulse width                                                                               | 1    |      |  |  |  |  |

| tRSCA            | RST_n to Command time                                                                           | 200¹ |      |  |  |  |  |

| tRSTH            | RST_n high period (interval time)                                                               | 1    |      |  |  |  |  |

| Notes: 1 74 cvcl | Notes: 1 74 cycles of clock signal required before issuing CMD1 or CMD0 with argument 0xFFFFFFA |      |      |  |  |  |  |

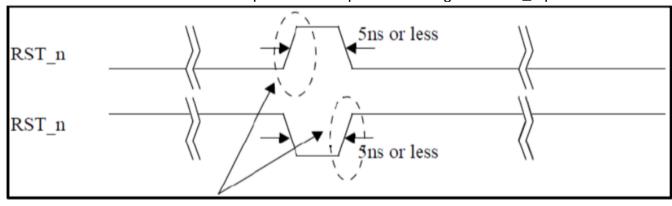

#### 5.6.2 Noise Filtering Timing for H/W

Device must filter out 5ns or less pulse width for noise immunity

Device must not detect these rising edge.

Device must not detect 5ns or less of positive or negative RST\_n pulse.

Device must detect more than or equal to 1us of positive or negative RST\_n pulse width.

Figure 5 – Noise Filtering Timing for H/W Reset

### 5.7 Field Firmware Update(FFU)

Field Firmware Updates (FFU) enables features enhancement in the field. Using this mechanism the host downloads a new version of the firmware to the eMMC device and, following a successful download, instructs the eMMC device to install the new downloaded firmware into the device.

In order to start the FFU process the host first checks if the eMMC device supports FFU capabilities by reading SUPPPORTED\_MODES and FW\_CONFIG fields in the EXT\_CSD. If the eMMC device supports the FFU feature the host may start the FFU process. The FFU process starts by switching to FFU Mode in MODE\_CONFIG field in the EXT\_CSD. In FFU Mode host should use closed-ended or open ended commands for downloading the new firmware and reading vendor proprietary data. In this mode, the host should set the argument of these commands to be as defined in FFU\_ARG field. In case these commands have a different argument the device behavior is not defined and the FFU process may fail. The host should set Block Length to be DATA\_SECTOR\_SIZE. Downloaded firmware bundle must be DATA\_SECTOR\_SIZE size aligned (internal padding of the bundle might be required). Once in FFU Mode the host may send the new firmware bundle to the device using one or more write commands.

The host could regain regular Functionality of write and read commands by setting MODE\_CONFIG field in the EXT\_CSD back to Normal state. Switching out of FFU Mode may abort the firmware download operation. When host switched back to FFU Mode, the host should check the FFU Status to get indication about the number of sectors which were downloaded successfully by reading the NUMBER\_OF\_FW\_SECTORS\_CORRECTLY\_PROGRAMMED in the extended CSD. In case the number of sectors which were downloaded successfully is zero the host should re-start downloading the new firmware bundle from its first sector. In case the number of sectors which were downloaded successfully is positive the host should continue the download from the next sector, which would resume the firmware download operation.

In case MODE\_OPERATION\_CODES field is not supported by the device the host sets to NORMAL state and initiates a CMD0/HW\_Reset/Power cycle to install the new firmware. In such case the device doesn't need to use NUMBER\_OF\_FW\_SECTORS\_CORRECTLY\_PROGRAMMED. In both cases occurrence of a CMD0/HW\_Reset/Power occurred before the host successfully downloaded the new firmware bundle to the device may cause the firmware download process to be aborted.

#### 5.8 Power off Notification for sleep

The host should notify the device before it powers the device off. This allows the device to better prepare itself for being powered off. Power the device off means to turn off all its power supplies. In particular, the host should issue a power off notification (POWER\_OFF\_LONG, POWER\_OFF\_SHORT) if it intends to turn off both VCC and VCCQ power I or it may use to a power off notification (SLEEP\_NOTIFICATION) if it intends to turn-off VCC after moving the device to Sleep state.

To indicate to the device that power off notification is supported by the host, a supporting host shall first set the POWER\_OFF\_NOTIFICATION byte in EXT\_CSD [34] to POWERED\_ON (0x01). To execute a power off, before powering the device down the host will changes the value to either POWER\_OFF\_SHORT (0x02) or POWER\_OFF\_LONG (0x03). Host should waits for the busy line to be de-asserted. Once the setting has changed to either 0x02 or 0x03, host may safely power off the device.

The host may issue SLEEP\_AWAKE (CMD5) to enter or to exit from Sleep state if

POWER\_OFF\_NOTIFICATION byte is set to POWERED\_ON. Before moving to Standby state and then to Sleep state, the host sets POWER\_OFF\_NOTIFICATION to SLEEP\_NOTIFICATION and

waits for the DAT0 line de-assertion. While in Sleep (slp) state VCC (Memory supply) may be turned off as defined in 7.1.2 Removing power supplies other than VCC while the device is in the Sleep (slp) state may result in undefined device behavior. Before removing all power supplies, the host should transition the device out of Sleep (slp) state back to Transfer state using CMD5 and CMD7 and then execute a power off notification setting POWER\_OFF\_NOTIFICATION byte to either POWER\_OFF\_SHORT or POWER\_OFF\_LONG.

If host continues to send commands to the device after switching to the power off setting (POWER\_OFF\_LONG, POWER\_OFF\_SHORT or SLEEP\_NOTIFICATION) or performs HPI during its busy condition, the device shall restore the POWER\_OFF\_NOTIFICATION byte to POWERED\_ON. If host tries to change POWER\_OFF\_NOTIFICATION to 0x00 after writing another value there, a SWITCH ERROR is generated.

The difference between the two power-off modes is how urgent the host wants to turn power off. The device should respond to POWER\_OFF\_SHORT quickly under the generic CMD6 timeout. If more time is acceptable, POWER\_OFF\_LONG may be used and the device shall respond to it within the POWER\_OFF\_LONG\_TIME timeout.

While POWER\_OFF\_NOTIFICATION is set to POWERED\_ON, the device expects the host to host shall:

- Keep the device power supplies alive (both VCC and VCCQ) and in their active mode

- Not power off the device intentionally before changing POWER\_OFF\_NOTIFICATION to either POWER\_OFF\_LONG or POWER\_OFF\_SHORT

- Not power off VCC intentionally before changing POWER\_OFF\_NOTIFICATION to SLEEP\_NOTIFICATION and before moving the device to Sleep state

Before moving to Sleep state hosts may set the POWER\_OFF\_NOTIFICATION byte to SLEEP\_NOTIFICATION (0x04) if aware that the device is capable of autonomously initiating background operations for possible performance improvements. Host should wait for the busy line to be de-asserted. Busy line may be asserted up the period defined in SLEEP\_NOTIFICATION\_TIME byte in EXT\_CSD [216]. Once the setting has changed to 0x04 host may set the device into Sleep mode (CMD7+CMD5). After getting out from Sleep the POWER\_OFF\_NOTIFICATION byte will restore its value to POWERED\_ON. HPI may interrupt the SLEEP\_NOTIFICATION operation. In that case POWER\_OFF\_NOTIFICATION byte will restore to POWERED\_ON.

#### 5.9 Enhanced User Data Area

This eMMC series supports Enhanced User Data Area feature which allows the User Data Area of eMMC to be configured. Therefore when host set the Enhanced User Data Area, the area will occupy 4 times of original set up size. The Max Enhanced User Data Area size is defined as – (MAX\_ENH\_SIZE\_MULT x HC\_WP\_GRP\_SIZE x HC\_ERASE\_GRP\_SIZE x 512 Kbytes). The Enhanced use data area size is defined as – (ENH\_SIZE\_MULT x HC\_WP\_GRP\_SIZE x HC\_ERASE\_GRP\_SIZE x 512 Kbytes). The host shall follow the flow chart of JEDEC spec for configuring the parameters of General Purpose Area Partitions and Enhanced User Data Area.

#### 5.10 Write Cache

Cache is a temporary storage space in an eMMC device. The cache should in typical case reduce the access time and increase the speed (compared to an access to the main nonvolatile storage). The cache is not directly accessible by the host. This temporary storage space may be utilized also for some implementation specific operations like as an execution memory for the memory controller and/or as storage for an address mapping table etc. However, there is data

inconsistence risk when using nonvolatile cache. It's recommend only turning on the cache for the application which requires not too high reliability.

The cache shall be OFF by default after power up, RST\_n assertion or CMD0. All accesses shall be directed to the nonvolatile storage like defined elsewhere in this specification. The cache function can be turned ON and OFF by writing to the CACHE\_CTRL byte (EXT\_CSD byte [33]). Turning the cache ON shall enable behavior model defined in this section. Turning the cache OFF shall trigger flushing of the data to the nonvolatile storage.

#### 5.11 Cache Enhancement Barrier

Barrier function provides a way to perform a delayed in-order flushing of a cached data. The main motivation for using barrier commands is to avoid the long delay that is introduced by flush commands. There are cases where the host is not interested in flushing the data right away, however it would like to keep an order between different cached data batches. The barrier command enables the host achieving the in-order goal but without paying the flush delay, since the real flushing can be delayed by the device to some later idle time. The formal definition of the barrier rule is as follows:

Denote a sequence of requests Ri, i=0,...,N. Assuming a barrier is set between requests Rx and Rx+1 (0<x<N) then all the requests R0..Rx must be flushed to the non-volatile memory before any of the requests Rx+1..RN.

Between two barriers the device is free to write data into the non-volatile memory in any order. If the host wants to preserve a certain order it shall flush the cache or set another barrier at a point where order is important.

The barrier is set by writing to the BARRIER bit of the FLUSH\_CACHE byte (EXT\_CSD byte [32]). Any error resulted can be read from the status register by CMD13 after the completion of the programming as defined for a normal write request. The error could affect any data written to the cache since the previous flush operation.

The device shall support any number of barrier commands between two flush commands. In case of multiple barrier commands between two flush commands a subset of the cached data may be committed to the non-volatile memory according to the barrier rule. Internally, a device may have an upper limit on the barrier amount it can absorb without flushing the cache. That is, if the host exceeds this barrier amount, the device may issue, internally, a normal flush.

The device shall expose its barrier support capability via the BARRIER\_SUPPORT byte (EXT\_CSD byte [486]). If a device does not support barrier function this register shall be zero. If a device supports barrier function this register shall be one.

Assuming the device supports barrier function, if the BARRIER bit of the FLUSH\_CACHE byte is set, a barrier operation shall be executed.

If the cache gets totally full and/or the cache is not able to receive the data of the next access (per block count indicated in CMD23 or per initiated single / open ended multiple block write in general) then it shall still be the responsibility of the eMMC device to store the data of the next access within the timeouts that are specified elsewhere in this specification. The actual algorithm to handle the new data and possible flush of some older cached data is left for the implementation.

Note: When issuing a force-programming write request (CMD23 with bit 24 on) or a reliable write request (CMD23 with bit 31 on), the host should be aware that the data will be written to the non-volatile memory, potentially, before any cached data, even if a barrier command was issued. Therefore, if the writing order to the non-volatile memory is important, it is the responsibility of the host to issue a flush command before the force-programming or the reliable-write request.

In order to use the barrier function, the host shall set bit 0 of BARRIER\_EN (EXT\_CSD byte [31]). The barrier feature is optional for an eMMC device.

#### 5.12 Cache Flush Policy

The host may require the device to flush data from the cache in an in-order manner. From time to time, to guarantee in-order flushing, the host may command the device to flush the device cache or may use a barrier command.

However, if the eMMC device flushing policy is to flush data from the cache in an in-order manner, cache barrier commands or flush commands operations (In case goal is to guarantee the flushing order) are redundant and impose a needless overhead to the device and host.

FIFO bit in CACHE\_FLUSH\_POLICY field (EXT\_CSD byte [240]) is used by the device to indicate to the host that the device cache flushing policy is First-In-First-Out; this means that the device guarantees that the order of the flushing of data would be the in same order which data was written to the cache. When the FIFO bit is set it is recommended for the host not to send cache barrier commands or flush operations which goal is to guarantee the flushing order as they are redundant and impose a burden to the system.

However, if the FIFO bit is set to 1b and the device supports the cache barrier mechanism, the host may still send barrier commands without getting an error. Sending these commands will not change the device behavior as device flushes cache in-order anyway.

The CACHE\_FLUSH\_POLICY field is read-only field and never change its value either by the host or device.

#### 5.13 Command Queuing (Disabled by default)

To facilitate command queuing in eMMC, the device manages an internal task queue to which the host can queue data transfer tasks.

Initially the task queue is empty. Every task is issued by the host and initially queued as pending. The device controller works to prepare pending tasks for execution. When a task is ready for execution its state changes to "ready for execution". The exact meaning of "ready for execution" is left for device implementation.

The host tracks the state of all queued tasks and may order the execution of any task, which is marked as "ready for execution" by sending a command indicating its task ID. When the execute command is received (CMD46/CMD47) the device executes the data transfer transaction.

For example, in order to queue a write transaction the host sends a CMD44 indicating the task's parameters. The device responds and the host sends a CMD45, indicating the start block address.

The device regards the two commands as a single task in the queue and sends a response indicating success if no error is detected. This exchange may be executed on the CMD line while a data transfer, or busy state, is ongoing on the DAT lines. The host tracks the state of the queue using CMD13.

At a later time, when data transfer is not in progress, the host issues a CMD47, ordering the device to execute a task from the queue, providing the Task ID in its argument. The device responds with an R1 response and the data transfer starts.

Note that if hosts need to access RPMB partition, the host should disable the Command Queue mechanism and access RPMB partition not through the command queue.

General Purpose partitions may be accessed when command queuing is enabled. The queue must be empty when CMD6 is sent (to switch partitions or to disable command queuing). Sending CMD6 while the queue is not empty shall be regarded as illegal command (as explained Supported Commands). Prior to enabling command queuing, the block size shall be set to 512B. Device may respond with an error to CMD46/CMD47 if block size is not 512B.

#### 5.14 Production State Awareness (PSA)

eMMC device could utilize the information of whether it is in production environment and operate differently than it operates in the field. For example, content that was loaded into the storage device prior to soldering might get corrupted, at higher probability, during device soldering. The eMMC device could use "special" internal operations for loading content prior to device soldering that would reduce production failures and use "regular" operations post- soldering.

PRODUCTION\_STATE\_AWARENESS [133] field in extended CSD is used as a mechanism through which the host should report to the device whether it is pre or post soldering state. This standard defines two methods, Manual Mode and Auto Mode, to manage the device production state.

The trigger for starting or re-starting the process is setting correctly PRE\_LOADING\_DATA\_SIZE field. Before setting this field the host is expected to make sure that the device is clean and any data that was written before to the device is expected to be erased using CMD35, CMD36 and CMD38.

In case the host erased data, overrode existing data or performed re-partition during production state awareness it should restart the production state awareness process by re-setting PRE\_LOADING\_DATA\_SIZE.

## 6 Register Settings

Within the Device interface six registers are defined: OCR, CID, CSD, EXT\_CSD, RCA and DSR. These can be accessed only by corresponding commands (see Section 6.10 of JESD84-B51).

#### 6.1 OCR Register

The 32-bit operation conditions register (OCR) stores the VDD voltage profile of the Device and the access mode indication. In addition, this register includes a status information bit. This status bit is set if the Device power up procedure has been finished. The OCR register shall be implemented by all Devices. For more details, refer to section 7.1 of the JEDEC Standard Specification No.JESD84-B51.

### 6.2 CID Register

The Card Identification (CID) register is 128 bits wide. It contains the Device identification information used during the Device identification phase (eMMC protocol). For details, refer to section 7.2 of JEDEC Standard Specification No.JESD84-B51.

Table 10 – CID Register

| Field    | Byte      | Value                                                                                 |

|----------|-----------|---------------------------------------------------------------------------------------|

| MID      | [127:120] | 0x9E                                                                                  |

| Reserved | [119:114] | 0x00                                                                                  |

| CBX      | [113:112] | 0x01                                                                                  |

| OID      | [111:104] | 0x00                                                                                  |

| PNM      | [103:56]  | "IM016G" for 16GB,<br>"IM032G" for 32GB,<br>"IM064G" for 64GB,<br>"IM128G" for 128GB, |

| PRV      | [55:48]   | 0x51                                                                                  |

| PSN      | [47:16]   | Random                                                                                |

| MDT      | [15:8]    | month, year                                                                           |

| CRC      | [7:1]     | Follow JEDEC Standard                                                                 |

| Reserved | [0:0]     | 0x01                                                                                  |

## 6.3 CSD Register

The Card-Specific Data (CSD) register provides information on how to access the contents stored in eMMC. The CSD registers are used to define the error correction type, maximum data access time, data transfer speed, data format...etc. For details, refer to section 7.3 of the JEDEC Standard Specification No.JESD84-B51.

Table 11 – CSD Register

| Field              | Byte      | Value                                     |

|--------------------|-----------|-------------------------------------------|

| CSD_Structure      | [127:126] | 0x03                                      |

| SPEC_VER           | [125:122] | 0x04 (V4.0~5.1)                           |

| Reserved           | [121:120] | 0x00                                      |

| TAAC               | [119:112] | 0x4F (40ms)                               |

| NSAC               | [111:104] | 0x01                                      |

| TRAN_SPEED         | [103:96]  | 0x32 (26Mbit/s)                           |

| CCC                | [95:84]   | 0x8F5                                     |

| READ_BL_LEN        | [83:80]   | 0x09 (512 Bytes)                          |

| READ_BL_PARTIAL    | [79:79]   | 0x00                                      |

| WRITE_BLK_MISALIGN | [78:78]   | 0x00                                      |

| READ_BLK_MISALIGN  | [77:77]   | 0x00                                      |

| DSR_IMP            | [76:76]   | 0x00                                      |

| Reserved           | [75:74]   | 0x00                                      |

| C_SIZE             | [73:62]   | 0xfff                                     |

| VDD_R_CURR_MIN     | [61:59]   | 0x07 (100mA)                              |

| VDD_R_CURR_MAX     | [58:56]   | 0x07 (200mA)                              |

| VDD_W_CURR_MIN     | [55:53]   | 0x07 (100mA)                              |

| VDD_W_CURR_MAX     | [52:50]   | 0x07 (200mA)                              |

| C_SIZE_MULT        | [49:47]   | 0x07 (512 Bytes)                          |

| ERASE_GRP_SIZE     | [46:42]   | 0x1F                                      |

| ERASE_GRP_MULT     | [41:37]   | 0x1F                                      |

| WP_GRP_SIZE        | [36:32]   | 0x1F (16GB)<br>0x1F (32GB)<br>0x1F (64GB) |

| WP_GRP_ENABLE      | [31:31]   | 0x01                                      |

| DEFAULT_ECC        | [30:29]   | 0x00                                      |

| R2W_FACTOR         | [28:26]   | 0x02                                      |

| WRITE_BL_LEN       | [25:22]   | 0x09 (512 Bytes)                          |

| WRITE_BL_PARTIAL   | [21:21]   | 0x00                                      |

| Reserved           | [20:17]   | 0x00                                      |

| CONTENT_PROT_APP   | [16:16]   | 0x00                                      |

| FILE_FORMAT_GRP    | [15:15]   | 0x00                                      |

| COPY               | [14:14]   | 0x00                                      |

| PERM_WRITE_PROTECT | [13:13]   | 0x00                                      |

| TMP_WRITE_PROTECT  | [12:12]   | 0x00                                      |

| FILE_FORMAT        | [11:10]   | 0x00                                      |

| ECC                | [9:8]     | 0x00                                      |

| CRC                | [ 7:1 ]   | Follow JEDEC Standard                     |

| Reserved           | [ 0:0 ]   | 0x01                                      |

## 6.4 Extended CSD Register

The Extended CSD register defines the Device properties and selected modes. It is 512 bytes long. The most significant 320 bytes are the Properties segment, which defines the Device capabilities and cannot be modified by the host. The lower 192 bytes are the Modes segment, which defines the configuration the Device is working in. These modes can be changed by the host by means of the SWITCH command. For details, refer to section 7.4 of the JEDEC Standard Specification No.JESD84-B51.

Table 12 - Extended CSD Register

| Field                                     | Byte      | Value |

|-------------------------------------------|-----------|-------|

| Reserved                                  | [511:506] | 0     |

| EXT_SECURITY_ERR                          | [505:505] | 0x00  |

| S_CMD_SET                                 | [504:504] | 0x01  |

| HPI_FEATURES                              | [503:503] | 0x01  |

| BKOPS_SUPPORT                             | [502:502] | 0x01  |

| MAX_PACKED_READS                          | [501:501] | 0x20  |

| MAX_PACKED_WRITES                         | [500:500] | 0x20  |

| DATA_TAG_SUPPORT                          | [499:499] | 0x01  |

| TAG_UNIT_SIZE                             | [498:498] | 0x03  |

| TAG_RES_SIZE                              | [497:497] | 0x00  |

| CONTEXT_CAPABILITIES                      | [496:496] | 0x05  |

| LARGE_UNIT_SIZE_M1                        | [495:495] | 0x18  |

| EXT_SUPPORT                               | [494:494] | 0x03  |

| SUPPORTED_MODES                           | [493:493] | 0x03  |

| FFU_FEATURES                              | [492:492] | 0x00  |

| OPERATION_CODE_TIMEOUT                    | [491:491] | 0x00  |

| FFU_ARG                                   | [490:487] | 0x00  |

| Barrier support                           | [486:486] | 0x00  |

| Reserved                                  | [485:309] | 0x00  |

| CMDQ_SUPPORT                              | [308:308] | 0x01  |

| CMQD_DEPTH                                | [307:307] | 0x0F  |

| Reserved                                  | [306:306] | 0x00  |

| NUMBER_OF_FW_SECTORS_CORRECTLY_PROGRAMMED | [305:302] | 0x00  |

| VENDOR_PROPRIETARY_HEALTH_REPORT          | [301:270] | 0x00  |

| DEVICE_LIFE_TIME_EST_TYP_B                | [269:269] | 0x01  |

| DEVICE_LIFE_TIME_EST_TYP_A                | [268:268] | 0x01  |

| PRE_EOL_INFO                              | [267:267] | 0x01  |

| OPTIMAL_READ_SIZE                         | [266:266] | 0x01  |

| OPTIMAL_WRITE_SIZE                        | [265:265] | 80x0  |

| OPTIMAL_TRIM_UNIT_SIZE                    | [264:264] | 0x01  |

| DEVICE_VERSION                            | [263:262] | 0x00  |

| FIRMWARE_VERSION                          | [261:254] | 0x01  |

| PWR_CL_DDR_200_360                        | [253:253] | 0x00* |

| CACHE_SIZE                                | [252:249] | 0x600 |

| GENERIC_CMD6_TIME                         | [248:248] | 0x0A  |

| POWER_OFF_LONG_TIME                       | [247:247] | 0x32  |

| BKOPS_STATUS                              | [246:246] | 0x00  |

| CORRECTLY_PRG_SECTORS_NUM                 | [245:242] | 0x00  |

| INI_TIMEOUT_AP                            | [241:241] | 0x1E  |

| Reserved                                  | [240:240] | 0x01  |

| PWR_CL_DDR_52_360                         | [239:239] | 0x00  |

| PWR_CL_DDR_52_195                         | [238:238] | 0x00  |

|                                    | ra        |                                                                              |

|------------------------------------|-----------|------------------------------------------------------------------------------|

| PWR_CL_200_195                     | [237:237] | 0x00                                                                         |

| PWR_CL_200_130                     | [236:236] | 0x00                                                                         |

| MIN_PERF_DDR_W_8_52                | [235:235] | 0x4B                                                                         |

| MIN_PERF_DDR_R_8_52                | [234:234] | 0x00                                                                         |

| Reserved                           | [233:233] | 0x00                                                                         |

| TRIM_MULT                          | [232:232] | 0x12                                                                         |

| SEC_FEATURE_SUPPORT                | [231:231] | 0x55                                                                         |

| SEC_ERASE_MULT                     | [230:230] | 0x64                                                                         |

| SEC_TRIM_MULT                      | [229:229] | 0x64                                                                         |

| BOOT_INFO                          | [228:228] | 0x07                                                                         |

| Reserved                           | [227:227] | 0x00                                                                         |

| BOOT_SIZE_MULT                     | [226:226] | 0x20                                                                         |

| ACC_SIZE                           | [225:225] | 0x07:<br>(16/32GB)<br>0x08:<br>(64GB)<br>0x09:<br>(128GB)                    |

| HC_ERASE_GRP_SIZE                  | [224:224] | 0x01                                                                         |

| ERASE_TIMEOUT_MULT                 | [223:223] | 0x02                                                                         |

| REL_WR_SEC_C                       | [222:222] | 0x01                                                                         |

| HC_WP_GRP_SIZE                     | [221:221] | 0x10                                                                         |

| S_C_VCC                            | [220:220] | 0x08                                                                         |

| S_C_VCCQ                           | [219:219] | 0x08                                                                         |

| PRODUCTION_STATE_AWARENESS_TIMEOUT | [218:218] | 0x00                                                                         |

| S_A_TIMEOUT                        | [217:217] | 0x15                                                                         |

| SLEEP NOTIFICATION TIME            | [216:216] | 0x0F                                                                         |

| SEC_COUNT                          | [215:212] | 0x1CF8000 (16GB)<br>0x3A3E000 (32GB)<br>0x747C000 (64GB)<br>0xE8F8000(128GB) |

| Reserved                           | [211:211] | 0x01                                                                         |

| MIN_PERF_W_8_52                    | [210:210] | 0x4B                                                                         |

| MIN_PERF_R_8_52                    | [209:209] | 0x00                                                                         |

| MIN PERF W 8 26 4 52               | [208:208] | 0x2B                                                                         |

| MIN_PERF_R_8_26_4_52               | [207:207] | 0x00                                                                         |

| MIN_PERF_W_4_26                    | [206:206] | 0x1E                                                                         |

| MIN_PERF_R_4_26                    | [205:205] | 0x00                                                                         |

| Reserved                           | [204:204] | 0x00                                                                         |

| PWR_CL_26_360                      | [203:203] | 0x00                                                                         |

| PWR_CL_52_360                      | [202:202] | 0x00                                                                         |

| PWR CL 26 195                      | [201:201] | 0x00                                                                         |

| PWR_CL_52_195                      | [200:200] | 0x00                                                                         |

| PARTITION_SWITCH_TIME              | [199:199] | 0x03                                                                         |

| OUT_OF_INTERRUPT_TIME              | [198:198] | 0x0A                                                                         |

| DRIVER_STRENGTH                    | [197:197] | 0x1F                                                                         |

| DEVICE_TYPE                        | [196:196] | 0x57                                                                         |

| Reserved                           | [195:195] | 0x00                                                                         |

| CSD_STRUCTURE                      | [194:194] | 0x02                                                                         |

| Reserved                           | [193:193] | 0x00                                                                         |

| EXT_CSD_REV                        | [192:192] | 0x08                                                                         |

| CMD_SET                            | [191:191] | 0x00                                                                         |

| Reserved                           | [190:190] | 0x00                                                                         |

| CMD_SET_REV                        | [189:189] | 0x00                                                                         |

| Reserved                           | [188:188] | 0x00                                                                         |

| DOWED CLASS                   | [407,407] | 0x00          |

|-------------------------------|-----------|---------------|

| POWER_CLASS                   | [187:187] | 0x00<br>0x00  |

| Reserved                      | [186:186] |               |

| HS_TIMING                     | [185:185] | 0x01          |

| Strobe Support                | [184:184] | 0x01          |

| BUS_WIDTH                     | [183:183] | 0x02          |

| Reserved                      | [182:182] | 0x00          |

| ERASED_MEM_CONT               | [181:181] | 0x00          |

| Reserved                      | [180:180] | 0x00          |

| PARTITION_CONFIG              | [179:179] | 0x00          |

| BOOT_CONFIG_PROT              | [178:178] | 0x00          |

| BOOT_BUS_CONDITIONS           | [177:177] | 0x00          |

| Reserved                      | [176:176] | 0x00          |

| ERASE_GROUP_DEF               | [175:175] | 0x00          |

| BOOT_WP_STATUS                | [174:174] | 0x00          |

| BOOT_WP                       | [173:173] | 0x00          |

| Reserved                      | [172:172] | 0x00          |

| USER_WP                       | [171:171] | 0x00          |

| Reserved                      | [170:170] | 0x1E          |

| FW_CONFIG                     | [169:169] | 0x00          |

| RPMB_SIZE_MULT                | [168:168] | 0x80          |

| WR_REL_SET                    | [167:167] | 0x1F          |

| WR_REL_PARAM                  | [166:166] | 0x15          |

| SANITIZE_START                | [165:165] | 0x00          |

| BKOPS_START                   | [164:164] | 0x00          |

| BKOPS_EN                      | [163:163] | 0x02          |

| RST_n_FUNCTION                | [162:162] | 0x00          |

| HPI MGMT                      | [161:161] | 0x00          |

| PARTITIONING_SUPPORT          | [160:160] | 0x07          |

|                               | •         | 0x264 (16GB)  |

| MANY ENILL OLZE MULT          | [450 457] | 0x4DA (32GB)  |

| MAX_ENH_SIZE_MULT             | [159:157] | 0x9B4 (64GB)  |

|                               |           | 0x1368(128GB) |

| PARTITIONS ATTRIBUTE          | [156:156] | 0x00          |

| PARTITION_SETTING_COMPLETED   | [155:155] | 0x00          |

| GP_SIZE_MULT_4                | [154:152] | 0x00          |

| GP SIZE MULT 3                | [151:149] | 0x00          |

| GP_SIZE_MULT_2                | [148:146] | 0x00          |

| GP_SIZE_MULT_1                | [145:143] | 0x00          |

| ENH SIZE MULT                 | [142:140] | 0x00          |

| ENH_START_ADDR                | [139:136] | 0x00          |

| Reserved                      | [135:135] | 0x00          |

| SEC BAD BLK MGMNT             | [134:134] | 0x00          |

| PRODUCTION STATE AWARENESS    | [133:133] | 0x00          |

|                               |           | 0x00          |

| TCASE_SUPPORT PERIODIC WAKEUP | [132:132] | 0x00<br>0x00  |

|                               | [131:131] |               |

| PROGRAM CIDCSDDDRSUPPORT      | [130:130] | 0x01          |

| Reserved                      | [129:128] | 0x00          |

| VENDOR_SPECIFIC_FIELD         | [127:67]  | -             |

| ERROR_CODE                    | [ 66:65 ] | 0x00          |

| ERROR_TYPE                    | [ 64:64 ] | 0x00          |

| NATIVE_SECTOR_SIZE            | [ 63:63 ] | 0x00          |

| USE_NATIVE_SECTOR             | [62:62]   | 0x00          |

| DATA_SECTOR_SIZE              | [ 61:61 ] | 0x00          |

| INI_TIMEOUT_EMU               | [ 60:60 ] | 0x00          |

| CLASS_6_CTRL                       | [ 59:59 ] | 0x00 |

|------------------------------------|-----------|------|

| DYNCAP_NEEDED                      | [ 58:58 ] | 0x00 |

| EXCEPTION_EVENTS_CTRL              | [ 57:56 ] | 0x00 |

| EXCEPTION_EVENTS_STATUS            | [ 55:54 ] | 0x00 |

| EXT_PARTITIONS_ATTRIBUTE           | [ 53:52 ] | 0x00 |

| CONTEXT_CONF                       | [ 51:37 ] | 0x00 |

| PACKED_COMMAND_STATUS              | [ 36:36 ] | 0x00 |

| PACKED_FAILURE_INDEX               | [ 35:35 ] | 0x00 |

| POWER_OFF_NOTIFICATION             | [ 34:34 ] | 0x00 |

| CACHE_CTRL                         | [ 33:33 ] | 0x00 |

| FLUSH_CACHE                        | [ 32:32 ] | 0x00 |

| Reserved                           | [ 31:31 ] | 0x00 |

| MODE_CONFIG                        | [ 30:30 ] | 0x00 |

| MODE_OPERATION_CODES               | [ 29:29 ] | 0x00 |

| Reserved                           | [ 28:27 ] | 0x00 |

| FFU_STATUS                         | [ 26:26 ] | 0x00 |

| PRE_LOADING_DATA_SIZE              | [ 25:22 ] | 0x00 |

| MAX_PRE_LOADING_DATA_SIZE          | [ 21:18 ] | 0x00 |

| PRODUCT_STATE_AWARENESS_ENABLEMENT | [ 17:17 ] | 0x00 |

| SECURE_REMOVAL_TYPE                | [ 16:16 ] | 0x01 |

| Reserved                           | [ 15:0 ]  | 0    |

|                                    |           |      |

#### 6.5 RCA Register

The writable 16-bit Relative Device Address (RCA) register carries the Device address assigned by the host during the Device identification. This address is used for the addressed host-Device communication after the Device identification procedure. The default value of the RCA register is 0x0001. The value 0x0000 is reserved to set all Devices into the Stand-by State with CMD7.

### 6.6 DSR Register

The 16-bit driver stage register (DSR) is described in detail in Section 10.2 of the JEDEC Standard Specification No.JESD84-B51. It can be optionally used to improve the bus performance for extended operating conditions (depending on parameters like bus length, transfer rate or number of Devices). The CSD register carries the information about the DSR register usage.

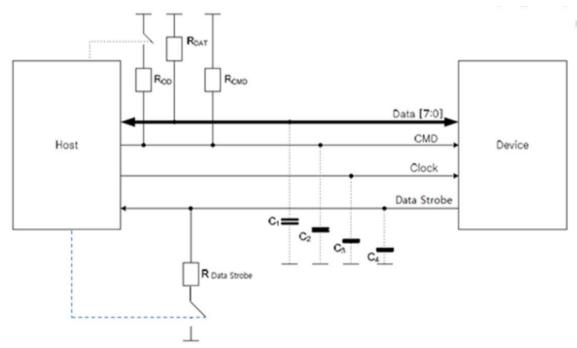

#### 7 The eMMC bus

The eMMC bus has ten communication lines and three supply lines:

- CMD: Command is a bidirectional signal. The host and Device drivers are operating in two modes, open drain and push/pull.

- DAT0-7: Data lines are bidirectional signals. Host and Device drivers are operating in pushpull mode

- CLK: Clock is a host to Device signal. CLK operates in push-pull mode

- Data Strobe: Data Strobe is a Device to host signal. Data Strobe operates in push-pull mode.

Figure 6 – Bus Circuitry Diagram

The Rod is switched on and off by the host synchronously to the open-drain and push-pull mode transitions. The host does not have to have open drain drivers, but must recognize this mode to switch on the Rod. Rdat and Rcmd are pull-up resistors protecting the CMD and the DAT lines against bus floating device when all device drivers are in a high-impedance mode.

A constant current source can replace the ROD by achieving a better performance (constant slopes for the signal rising and falling edges). If the host does not allow the switchable ROD implementation, a fixed RCMD can be used). Consequently the maximum operating frequency in the open drain mode has to be reduced if the used RCMD value is higher than the minimal one given in.

Rdata strobe is pull-down resistor used in HS400 device.

## 7.1 Power-up

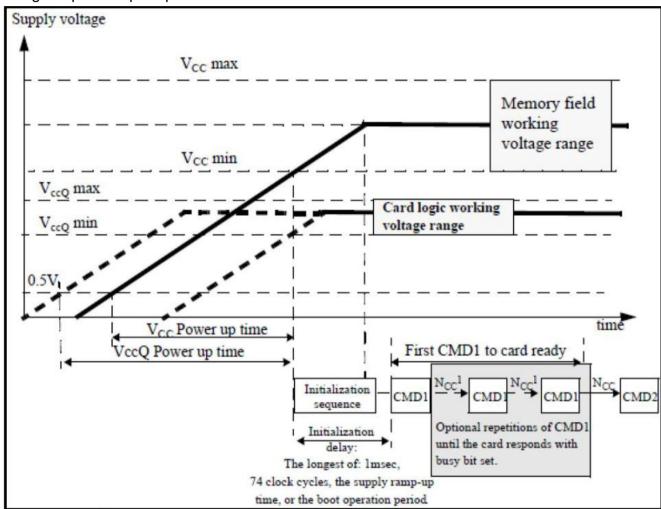

#### 7.1.1 eMMC power-up

An eMMC bus power-up is handled locally in each device and in the bus master. Figure7 shows the power-up sequence and is followed by specific instructions regarding the power-up sequence. Refer to section 10.1 of the JEDEC Standard Specification No.JESD84-B51 for specific instructions regarding the power-up sequence.

Figure 7 – eMMC Power-up Diagram

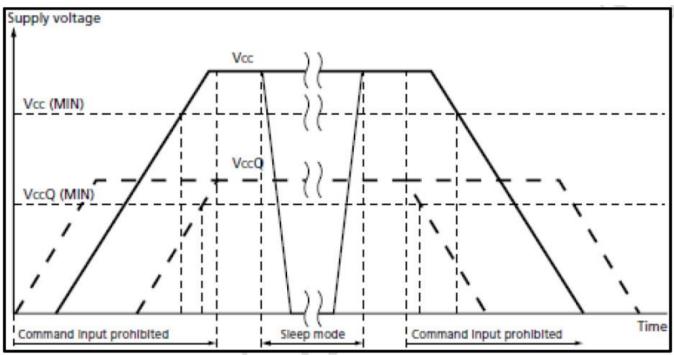

#### 7.1.2 eMMC Power Cycling

The master can execute any sequence of VCC and VCCQ power-up/power-down. However, the master must not issue any commands until VCC and VCCQ are stable within each operating voltage range. After the slave enters sleep mode, the master can power-down VCC to reduce power consumption. It is necessary for the slave to be ramped up to VCC before the host issues CMD5 (SLEEP\_AWAKE) to wake the slave unit. For more information about power cycling see Section 10.1.3 of the JEDEC Standard Specification No.JESD84-B51.

Figure 8 – The eMMC Power Cycle

## 7.2 Bus Operating Conditions

Table 13 – General Operating Conditions

| Parameter                                                                                                           | Symbol   | Min  | Max.         | Unit |

|---------------------------------------------------------------------------------------------------------------------|----------|------|--------------|------|

| Peak voltage on all lines                                                                                           |          | -0.5 | VCCQ<br>+0.5 | V    |

| All Inputs                                                                                                          |          |      |              |      |

| Input Leakage Current (before initialization sequence <sup>1</sup> and/or the internal pull up resistors connected) |          | tbd  | tbd          | μΑ   |

| Input Leakage Current (after initialization sequence and the internal pull up resistors disconnected)               |          | tbd  | tbd          | μΑ   |

| All Outputs                                                                                                         |          |      |              |      |

| Output Leakage Current (before initialization sequence)                                                             |          | tbd  | tbd          | μΑ   |

| Output Leakage Current (after initialization sequence) <sup>2</sup>                                                 |          | tbd  | tbd          | μΑ   |

| Notes: 1. Initialization sequence is defined in section 10.1 2. DS (Data strobe) pin is excluded.                   | <u> </u> |      | l            |      |

DS (Data strobe) pin is excluded

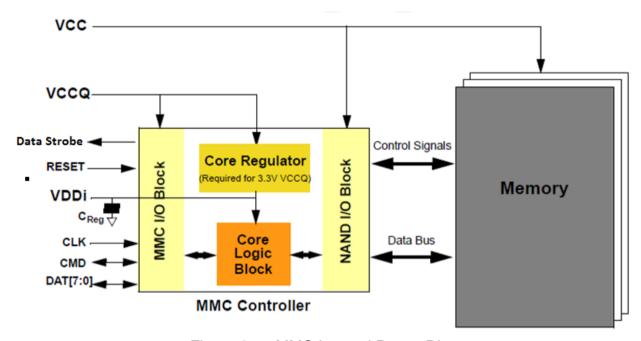

#### 7.2.1 Power supply: eMMC

In the eMMC, VCC is used for the NAND flash device and its interface voltage; VCCQ is for the controller and the MMC interface voltage as shown in Figure 8. The core regulator is optional and only required when internal core logic voltage is regulated from VCCQ. A Creg capacitor must be connected to the VDDi terminal to stabilize regulator output on the system.

Figure 9 - eMMC Internal Power Diagram

#### 7.2.2 eMMC Power Supply Voltages

The eMMC supports one or more combinations of  $V_{CC}$  and  $V_{CCQ}$  as shown in Table 8. The  $V_{CCQ}$  must be defined at equal to or less than  $V_{CC}$ .

| Parameter                | Symbol           | MIN | MAX  | Unit |

|--------------------------|------------------|-----|------|------|

| Supply voltage (NAND)    | V <sub>CC</sub>  | 2.7 | 3.6  | V    |

| Supply voltage (I/O)     | \/               | 2.7 | 3.6  | V    |

|                          | V <sub>CCQ</sub> | 1.7 | 1.95 | V    |

| Supply power-up for 3.3V | <b>t</b> PRUH    |     | tbd  | ms   |

| Supply power-up for 1.8V | <b>t</b> PRUL    |     | tbd  | ms   |

Table 14 – eMMC Operating Voltage

The eMMC must support at least one of the valid voltage configurations, and can optionally support all valid voltage configurations (see Table15).

Table 15 – eMMC Voltage Combinations

|          |                                                                             | Vccq                              |       |  |  |  |  |

|----------|-----------------------------------------------------------------------------|-----------------------------------|-------|--|--|--|--|

|          |                                                                             | 1.7V-1.95V 2.7V-3.6V <sup>1</sup> |       |  |  |  |  |

| Vcc      | 2.7V-3.6V                                                                   | Valid                             | Valid |  |  |  |  |

| Notes: 1 | Notes: 1. CCQ (I/O) 3.3 volt range is not supported in HS200 /HS400 devices |                                   |       |  |  |  |  |

## 7.2.3 Bus Signal Line Load

The total capacitance  $C_{\text{L}}$  of each line of the eMMC bus is the sum of the bus master capacitance  $C_{\text{HOST}}$ , the bus capacitance  $C_{\text{BUS}}$  itself and the capacitance  $C_{\text{DEVICE}}$  of eMMC connected to this line:

$$C_L = C_{HOST} + C_{BUS} + C_{DEVICE}$$

The sum of the host and bus capacitances must be under 20pF.

Table 16 - Signal Line Load

| Parameter                                | Symbol                                    | Min     | Max     | Тур     | Unit | Remark                                                                                                                                                                                                                              |

|------------------------------------------|-------------------------------------------|---------|---------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pull-up resistance for CMD               | Rcmd                                      | 4.7     | 50      | 10      | Kohm | to prevent bus floating                                                                                                                                                                                                             |

| Pull-up resistance for DAT0–7            | R <sub>DAT</sub>                          | 10      | 50      | 10      | Kohm | to prevent bus floating                                                                                                                                                                                                             |

| Pull-up resistance for RST_n             | R <sub>RST_n</sub>                        | 4.7     | 50      | 10      | Kohm | It is not necessary to put pull-up resistance on RST_n (H/W rest) line if host does not use H/W reset. (Extended CSD register [162] = 0 b )                                                                                         |

| Bus signal line capacitance              | C <sub>L</sub>                            |         | 30      | 30      | pF   | Single Device                                                                                                                                                                                                                       |

| Single Device capacitance                | C <sub>DEVICE</sub>                       |         | 6       | 6       | pF   |                                                                                                                                                                                                                                     |

| Maximum signal line inductance           |                                           |         | 16      | 16      | nH   |                                                                                                                                                                                                                                     |

| Impedance on<br>CLK / CMD / DAT0~7       |                                           | 45      | 55      | 50      | ohm  | Impedance match                                                                                                                                                                                                                     |

| Serial's resistance on CLK line          | SR <sub>CLK</sub>                         | 0       | 47      | 0       | ohm  |                                                                                                                                                                                                                                     |

| Serial's resistance on CMD / DAT0~7 line | SR <sub>CMD</sub><br>SR <sub>DAT0~7</sub> | 0       | 47      | 0       | ohm  |                                                                                                                                                                                                                                     |

|                                          |                                           | 2.2+0.1 | 10+0.22 | 2.2+0.1 | μF   | It should be located as close as possible to<br>the balls defined in order to minimize<br>connection parasitic                                                                                                                      |

| V <sub>CCQ</sub> decoupling capacitor    | CH1                                       | 1       | 2.2     | 1       | μF   | CH1 is only for HS200. It should be placed adjacent to VCCQ-VSSQ balls (#K6 and #K4 accordingly, next to DAT [70] balls). It should be located as close as possible to the balls defined in order to minimize connection parasitic. |

| V <sub>CC</sub> capacitor value  | 2.2+0.1 | 10+0.22 | 4.7+0.1 |    | It should be located as close as possible to<br>the balls defined in order to minimize<br>connection parasitic                                                    |

|----------------------------------|---------|---------|---------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>Ddi</sub> capacitor value | 1+0.1   | 2.2+0.1 | 1+0.1   | μΓ | To stabilize regulator output to controller core logics. It should be located as close as possible to the balls defined in order to minimize connection parasitic |

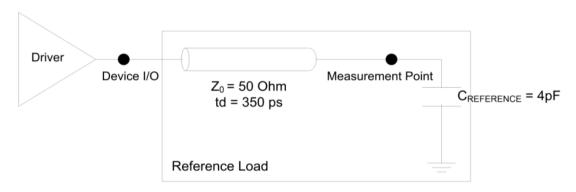

#### 7.2.4 Bus Signal Line Load

The circuit in Figure 10 shows the reference load used to define the HS400 Device Output Timings and overshoot / undershoot parameters. The reference load is made up by the transmission line and the CREFERENCE capacitance.