MRAM

#### **FEATURES**

• Non-volatile 256Mb (32Mb x 8, 16Mb x 16) DDR3

- Supports standard DDR3 SDRAM features

- V<sub>DD</sub> = 1.5v +/- 0.075v

- Up to 667MHz <sup>f</sup>CK (1333MT/sec/pin)

- Page size of 512 bits (x8) or 1024 bits (x16)

256Mb ST-DDR3 Spin-transfer Torque

- On-Chip DLL aligns DQ, DQS, DQS transition with CK transition

- All addresses and control inputs are latched on rising edge of Clock

- Burst length of 8 with programmable Burst Chop length of 4

- Standard 10x13mm 78-Ball (x8) or 96-ball (x16) BGA Package

#### **INTRODUCTION**

The EMD3D256M08/16B 256Mb DDR3 Spin-transfer Torque MRAM (STT-MRAM) is a nonvolatile memory that offers non-volatility and high endurance at DDR3 speeds. The device is capable of DDR3 operation at rates of up to 1333MT/Sec/Pin. It is designed to comply with all DDR3 DRAM features including on-device termination (ODT) and internal ZQ calibration but with the benefit of data persistence and extremely high write cycle endurance. With Spin-Torque MRAM technology, cell refresh is not required, which greatly simplifies system design and reduces overhead.

All control and address inputs are synchronized with a pair of externally supplied differential clocks, with input latching at clock crosspoints. I/Os are synchronized with a pair of bidirectional strobes (DQS,  $\overline{DQS}$ ). The device uses a  $\overline{RAS}/\overline{CAS}$  multiplexing scheme and operates at 1.5V.

## **DDR3 DRAM COMPATIBILITY**

Everspin DDR3 Spin-Torque MRAMs are fully compatible with DDR3 standards for DRAM operation defined in JEDEC Standard JESD79-3F, with exceptions and improvements as noted and defined in this data sheet.

- The Spin-Torque MRAM is a non-volatile memory. All data in closed/precharged banks are retained in memory whenever device power is removed for any reason.

- Command timing will be different in some cases. See "Table 11 Timing Parameters" on page 20.

- The DDR3 standard applies to densities higher than 256Mb resulting in addressing and page size differences.

- Burst Type/Burst Order supports only the sequential burst type for CA<2:0 = 000 or 100. See "Burst Length, Type and Order" on page 30.

- This data sheet will make references to JESD79-3F when the function, timing, parameter or condition is identical between the MRAM and this standard. The JESD79-3F standard is available on the JEDEC website, registration is required.

# **TABLE OF CONTENTS**

| DDR3 DRAM COMPATIBILITY                               |

|-------------------------------------------------------|

| FUNCTIONAL DESCRIPTION                                |

| Basic Functionality                                   |

| Figure 1 – Simplified State Diagram STT-MRAM7         |

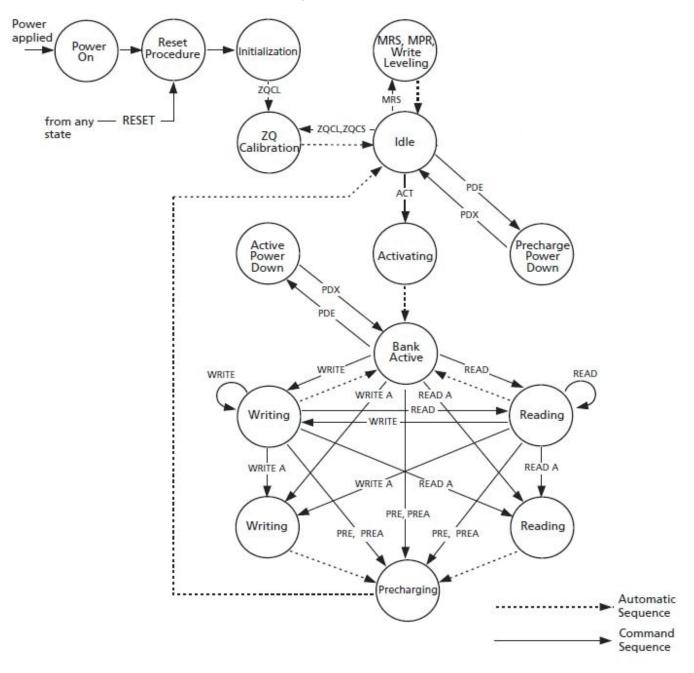

| Figure 2 – Block Diagram (32Mb x 8) STT-MRAM8         |

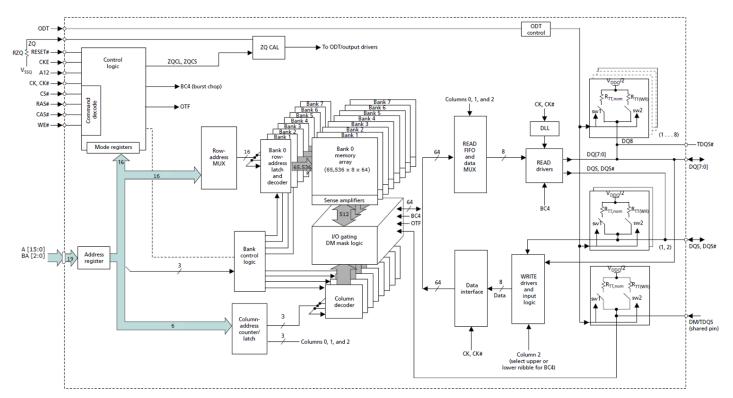

| Figure 3 – Block Diagram (16Mb x 16) STT-MRAM8        |

| Table 1 – Addressing Scheme by I/O Width9             |

| PACKAGE BALL ASSIGNMENTS                              |

| Table 2 – 32Mb x 8 in 78-Ball BGA - Top View10        |

| Table 3 – 16Mb x 16 in 96-Ball BGA - Top View11       |

| BALL FUNCTIONS AND DESCRIPTIONS 12                    |

| Table 4 – Ball Functions and Descriptions12           |

| ABSOLUTE MAXIMUM RATINGS 15                           |

| Table 5 – Absolute Maximum Ratings15                  |

| THERMAL CHARACTERISTICS                               |

| Table 6 – Thermal Characteristics 78-ball BGA Package |

| Table 7 – Thermal Characteristics 96-ball BGA Package |

| DC CHARACTERISTICS                                    |

| Table 8 – Power Supply and Input Leakage 17           |

| Table 9 – Input / Output Capacitance                  |

| Table 10 – I <sub>DD</sub> Maximum Limits19           |

| TIMING PARAMETERS                                     |

| Table 11 – Timing Parameters                          |

| TRUTH TABLES                                          |

| Command Truth Table                                   |

# Table of Contents (Cont'd)

| Table 12 – Command Truth Table                                                               | 21 |

|----------------------------------------------------------------------------------------------|----|

| CKE Truth Table                                                                              |    |

| Table 13 – CKE Truth Table                                                                   | 23 |

| FUNCTIONAL PARAMETERS                                                                        |    |

| COMMAND DESCRIPTIONS                                                                         |    |

| ACTIVE Command                                                                               |    |

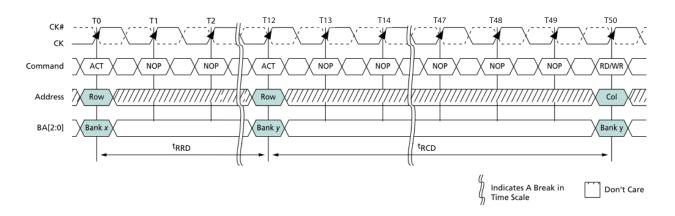

| Figure 4 – ACTIVE Command Example: Meeting <sup>t</sup> RRD (MIN) and <sup>t</sup> RCD (MIN) |    |

| PRECHARGE Command                                                                            |    |

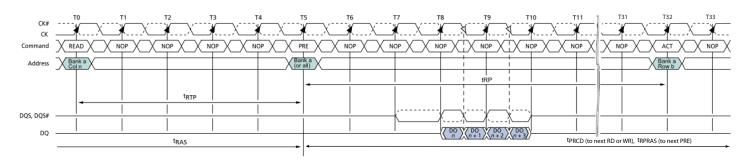

| Figure 5 – PRECHARGE Command Timing                                                          |    |

| READ Command                                                                                 | 27 |

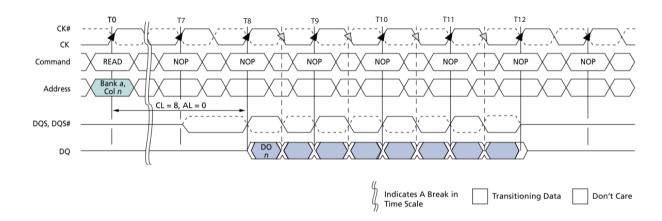

| Figure 6 – READ Command Timing                                                               | 27 |

| WRITE Command                                                                                |    |

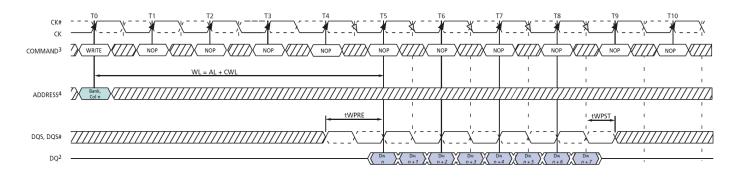

| Figure 7 – WRITE Burst Operation WL = 5 (AL = 0 CWL = 5, BL8)                                |    |

| Burst Length, Type and Order                                                                 |    |

| Table 14 – Burst Length, Type and Order                                                      |    |

| PART NUMBER DECODER                                                                          |    |

| Table 15 – 256Mb x8 / x16 STT-MRAM Ordering Part Number Decoder                              |    |

| ORDERING PART NUMBERS                                                                        |    |

| Table 16 – Ordering Part Numbers                                                             |    |

# Table of Contents (Cont'd)

| PACKAGE OUTLINE DRAWING                                  | 33  |

|----------------------------------------------------------|-----|

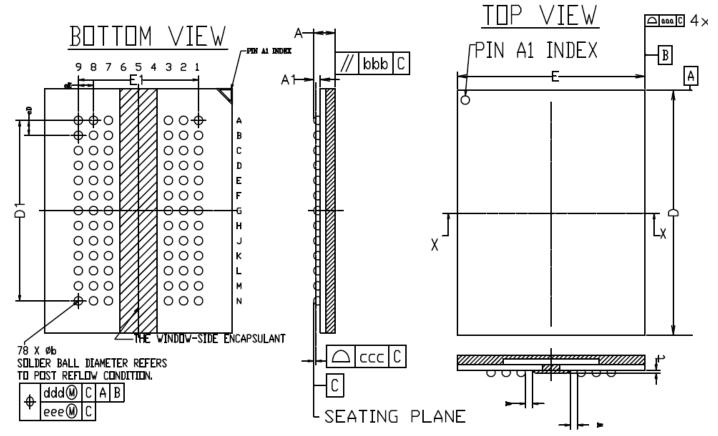

| Figure 8 – 78-Ball BGA Package Outline (x8)              | .33 |

| Figure 9 – 78-Ball BGA Package Outline (x8) Dimensions   | .34 |

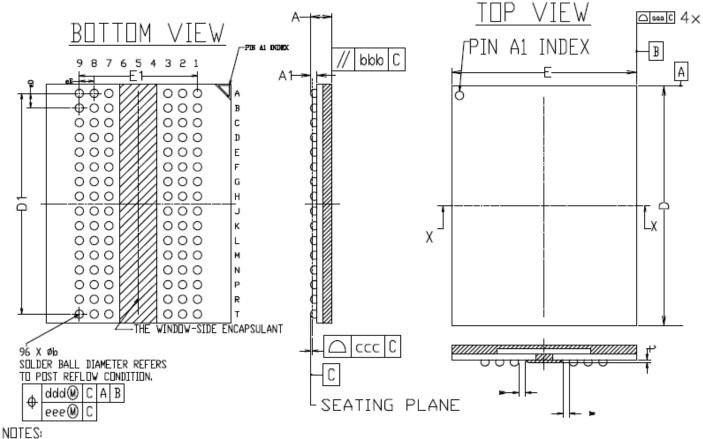

| Figure 10 – 96-Ball BGA Package Outline (x16)            | .35 |

| Figure 11 – 96-Ball BGA Package Outline (x16) Dimensions | .36 |

| Table 17 – Revision History                              | .37 |

| HOW TO CONTACT US                                        | 38  |

## **FUNCTIONAL DESCRIPTION**

#### **Basic Functionality**

The DDR3 STT-MRAM is a high-speed Spin-Torque Magnetoresistive Random Access Memory internally configured as an eight-bank RAM. It uses an 8n prefetch architecture to achieve high-speed operation. The 8n prefetch architecture is combined with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write operation for the DDR3 MRAM consists of a single 8n-bit wide, four clock data transfer at the internal STT-MRAM core and two corresponding n-bit wide, one-half clock cycle data transfers at the I/O pins.

READ and write operations to the DDR3 STT-MRAM are burst oriented, start at a selected location, and continue for a burst length of eight or a "chopped" burst of four in a programmed sequence. Operation begins with the registration of an Active command, which is then followed by a READ or WRITE command. The address bits registered coincident with the Active command are used to select the bank and row to be activated ([BA0:BA2] select the bank; A0-A13 select the row); refer to "Table 1 – Addressing Scheme by I/O Width" on page 9" for specific requirements. The address bits registered coincident with the select the starting column location for the burst operation, determine if the auto precharge command is to be issued (via A10), and select BC4 or BL8 mode on the fly' (via A12) if enabled in the mode register.

Prior to normal operation, the DDR3 STT-MRAM must be powered up and initialized in a predefined manner.

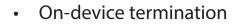

### Figure 1 – Simplified State Diagram STT-MRAM

This simplified State Diagram is intended to provide an overview of the possible state transitions and the commands to control them. Situations involving more than one bank, the enabling or disabling of on-die termination, and some other events are not captured in full detail.

Figure 3 – Block Diagram (16Mb x 16) STT-MRAM

### Table 1 – Addressing Scheme by I/O Width

The addressing scheme is shown in the Table 1 below. The Bank and Row Address is presented during an ACTIVE command. The Column Address is selected during a READ or WRITE command. Further explanation is given in the COMMAND section.

| Configuration        | 32Mb x 8 | 16Mb x 16 |

|----------------------|----------|-----------|

| # of Banks           | 8        | 8         |

| Bank Address         | BA0 - 2  | BA0 - 2   |

| Auto Precharge       | A10/AP   | A10/AP    |

| BC Switch on the fly | A12/BC   | A12/BC    |

| # Rows               | 64K      | 32К       |

| Row Address          | A0 - A15 | A0 - A14  |

| # Columns            | 64       | 64        |

| Column Address       | A0 - A5  | A0 - A5   |

| Page Size            | 512 bits | 1024 bits |

### **PACKAGE BALL ASSIGNMENTS**

256Mb x8 and x16 package ball assignments conform to JESD79-3F Standard DDR3 SDRAM footprints and pin assignments.

| Row | 1                  | 2                | 3   | 4 | 5 | 6 | 7               | 8                  | 9                | Row |

|-----|--------------------|------------------|-----|---|---|---|-----------------|--------------------|------------------|-----|

| А   | V <sub>SS</sub>    | V <sub>DD</sub>  | NC  |   |   |   | NF/TDQS         | V <sub>SS</sub>    | V <sub>DD</sub>  | А   |

| В   | V <sub>SS</sub>    | V <sub>SSQ</sub> | DQ0 |   |   |   | DM/TDQS         | V <sub>SSQ</sub>   | V <sub>DDQ</sub> | В   |

| С   | V <sub>DDQ</sub>   | DQ2              | DQS |   |   |   | DQ1             | DQ3                | V <sub>SSQ</sub> | С   |

| D   | V <sub>SSQ</sub>   | DQ6              | DQS |   |   |   | V <sub>DD</sub> | V <sub>SS</sub>    | V <sub>SSQ</sub> | D   |

| E   | V <sub>REFDQ</sub> | V <sub>DDQ</sub> | DQ4 |   |   |   | DQ7             | DQ5                | V <sub>DDQ</sub> | E   |

| F   | NC                 | V <sub>SS</sub>  | RAS |   |   |   | СК              | V <sub>SS</sub>    | NC               | F   |

| G   | ODT                | V <sub>DD</sub>  | CAS |   |   |   | CK              | V <sub>DD</sub>    | CKE              | G   |

| Н   | NC                 | CS               | WE  |   |   |   | A10/AP          | ZQ                 | NC               | Н   |

| J   | V <sub>SS</sub>    | BAO              | BA2 |   |   |   | A15             | V <sub>REFCA</sub> | V <sub>SS</sub>  | J   |

| К   | V <sub>DD</sub>    | A3               | A0  |   |   |   | A12/BC          | BA1                | V <sub>DD</sub>  | К   |

| L   | V <sub>SS</sub>    | A5               | A2  |   |   |   | A1              | A4                 | V <sub>SS</sub>  | L   |

| М   | V <sub>DD</sub>    | A7               | A9  |   |   |   | A11             | A6                 | V <sub>DD</sub>  | М   |

| Ν   | V <sub>SS</sub>    | RESET            | A13 |   |   |   | A14             | A8                 | V <sub>SS</sub>  | Ν   |

|     | 1                  | 2                | 3   | 4 | 5 | 6 | 7               | 8                  | 9                | -   |

### Table 2 – 32Mb x 8 in 78-Ball BGA - Top View

## Table 3 – 16Mb x 16 in 96-Ball BGA - Top View

| Row | 1                  | 2                | 3               | 4 | 5 | 6 | 7               | 8                  | 9                | Row |

|-----|--------------------|------------------|-----------------|---|---|---|-----------------|--------------------|------------------|-----|

| А   | V <sub>DDQ</sub>   | DQU5             | DQU7            |   |   |   | DQU4            | V <sub>DDQ</sub>   | V <sub>SS</sub>  | А   |

| В   | V <sub>SSQ</sub>   | V <sub>DD</sub>  | V <sub>SS</sub> |   |   |   | DQSU            | DQU6               | V <sub>SSQ</sub> | В   |

| С   | V <sub>DDQ</sub>   | DQU3             | DQU1            |   |   |   | DQSU            | DQU2               | V <sub>DDQ</sub> | С   |

| D   | V <sub>SSQ</sub>   | V <sub>DDQ</sub> | DMU             |   |   |   | DQU0            | V <sub>SSQ</sub>   | V <sub>DD</sub>  | D   |

| Е   | V <sub>SS</sub>    | V <sub>SSQ</sub> | DQL0            |   |   |   | DML             | V <sub>SSQ</sub>   | V <sub>DDQ</sub> | Е   |

| F   | V <sub>DDQ</sub>   | DQL2             | DQSL            |   |   |   | DQL1            | DQL3               | V <sub>SSQ</sub> | F   |

| G   | V <sub>SSQ</sub>   | DQL6             | DQSL            |   |   |   | V <sub>DD</sub> | V <sub>SS</sub>    | V <sub>SSQ</sub> | G   |

| Н   | V <sub>REFDQ</sub> | V <sub>DDQ</sub> | DQL4            |   |   |   | DQL7            | DQL5               | V <sub>DDQ</sub> | Н   |

| J   | NC                 | V <sub>SS</sub>  | RAS             |   |   |   | СК              | V <sub>SS</sub>    | NC               | J   |

| К   | ODT                | V <sub>DD</sub>  | CAS             |   |   |   | CK              | V <sub>DD</sub>    | CKE              | К   |

| L   | NC                 | CS               | WE              |   |   |   | A10/AP          | ZQ                 | NC               | L   |

| М   | V <sub>SS</sub>    | BAO              | BA2             |   |   |   | A15             | V <sub>REFCA</sub> | V <sub>SS</sub>  | М   |

| Ν   | V <sub>DD</sub>    | A3               | A0              |   |   |   | A12/BC          | BA1                | V <sub>DD</sub>  | N   |

| Р   | V <sub>SS</sub>    | A5               | A2              |   |   |   | A1              | A4                 | V <sub>SS</sub>  | Р   |

| R   | V <sub>DD</sub>    | A7               | A9              |   |   |   | A11             | A6                 | V <sub>DD</sub>  | R   |

| Т   | V <sub>SS</sub>    | RESET            | A13             |   |   |   | A14             | A8                 | V <sub>SS</sub>  | Т   |

|     | 1                  | 2                | 3               | 4 | 5 | 6 | 7               | 8                  | 9                | •   |

## **BALL FUNCTIONS AND DESCRIPTIONS**

### Table 4 – Ball Functions and Descriptions

| Symbol                                          | Туре      | Name                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------|-----------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ск, ск                                          | Input     | Clock                   | Clock: CK and $\overline{CK}$ are differential clock inputs. All control and address input signals are sampled on the crossing of the positive edge of CK and the negative edge of $\overline{CK}$ . Output data strobe (DQS, $\overline{DQS}$ ) is referenced to the crossings of CK and $\overline{CK}$ .                                                                                                                                                                                                                    |

| СКЕ                                             | Input     | Clock Enable            | Clock enable: CKE enables (registered HIGH) and disables (registered LOW) internal circuitry and clocks on the STT-MRAM. The specific circuitry that is enabled/ disabled is dependent upon the DDR3 STT-MRAM configuration and operating mode. Taking CKE LOW provides PRECHARGE POWER-DOWN, or active power-down (row active in any bank). CKE is synchronous for power-down entry and exit. Input buffers (excluding CK, CK, CKE, RESET, and ODT) are disabled during POWER-DOWN. CKE is referenced to V <sub>REFCA</sub> . |

| cs                                              | Input     | Chip Select             | Chip Select: All commands are masked when $\overline{CS}$ is registered HIGH. $\overline{CS}$ provides for external Rank selection on systems with multiple Ranks. $\overline{CS}$ is considered part of the command code.                                                                                                                                                                                                                                                                                                     |

| ODT                                             | Input     | On-Die Termi-<br>nation | On Die Termination: ODT (registered HIGH) enables termination resistance internal to the DDR3 STT-MRAM. When enabled, ODT is only applied to each DQ, DQS, DQS and DM/TDQS, NU/TDQS (When TDQS is enabled via Mode Register A11=1 in MR1) signal for x8 configurations. The ODT pin will be ignored if MR1 is programmed to disable ODT.                                                                                                                                                                                       |

| $\overline{RAS}, \overline{CAS}, \overline{WE}$ | Input     | Command<br>Inputs       | Command Inputs: $\overline{RAS}$ , $\overline{CAS}$ and $\overline{WE}$ (along with $\overline{CS}$ ) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                        |

| DM                                              | Input     | Input Data<br>Mask      | Input Data Mask: DM is an input mask signal for write data. Input data is masked<br>when DM is sampled HIGH coincident with that input data during a WRITE access.<br>DM is sampled on both edges of DQS. For x8 device, the function of DM or TDQS/<br>TDQS is enabled by Mode Register A11 setting in MR1. For x16 DML is associated<br>with DQ0-7 while DMU is associated with DQ8-15.                                                                                                                                      |

| BA0, BA1, BA2                                   | Input     | Bank Address<br>Inputs  | Bank address inputs: BA[2:0] define the bank to which an ACTIVE, READ, WRITE, or PRECHARGE command is being applied. BA[2:0] define which mode register (MR0, MR1, MR2, or MR3) is loaded during the LOAD MODE command. BA[2:0] are referenced to V <sub>REFCA</sub> .                                                                                                                                                                                                                                                         |

| A0-A15                                          | Input     | Address<br>Inputs       | Address Inputs: Provide the row address for Active commands and the column<br>address for READ/WRITE commands to select one location out of the memory array<br>in the respective bank. (A10/AP and A12/BC have additional functions, see below).<br>The address inputs also provide the op-code during Mode Register Set commands.<br>In using the device in x16 mode A15 needs to be pulled to logic HIGH.                                                                                                                   |

| Table continu                                   | es on the | e next page.            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Table continues on the next page.

## **Ball Functions and Descriptions (Continued)**

| Symbol             | Туре             | Name                                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------|------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A10/AP             | Input            | Auto Pre-<br>charge                                              | Auto-precharge: A10 is sampled during READ/WRITE commands to determine<br>whether Autoprecharge should be performed to the accessed bank after the READ/<br>WRITE operation. (HIGH: Autoprecharge; LOW: no Autoprecharge). A10 is sampled<br>during a Precharge command to determine whether the Precharge applies to one<br>bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the<br>bank is selected by bank addresses. |

| A12/BC             | Input            | Burst Chop                                                       | Burst Chop: A12 / BC is sampled during READ and WRITE commands to determine if burst chop (on-the-fly) will be performed. (HIGH, no burst chop; LOW: burst chopped). See command truth table for details.                                                                                                                                                                                                                                             |

| RESET              | Input            | Acitve Low<br>Asynchro-<br>nous Reset                            | Active Low Asynchronous Reset: Reset is active when RESET is LOW, and inactive when RESET is HIGH. RESET must be HIGH during normal operation. RESET is a CMOS rail-to-rail signal with DC high and low at 80% and 20% of VDD, i.e. 1.20V for DC high and 0.30V for DC low.                                                                                                                                                                           |

| DQ                 | Input/<br>Output | Data Input/<br>Output                                            | Data Input/ Output: Bi-directional data bus. DQ0-7 (x8) and DQ8-15 (x16) are referenced to $\rm V_{REFDQ}$ in $\rm \cdot$                                                                                                                                                                                                                                                                                                                             |

| DQS/DQS            | Input/<br>Output | Data Strobe                                                      | Data strobe: Output with read data. Edge-aligned with read data. Input with write data. Center-aligned to write data. For x16 operation DQSL/ $\overline{DQSL}$ is associated with DQ0-7 and DQSU/ $\overline{DQSU}$ is associated with DQ8-15.                                                                                                                                                                                                       |

| TDQS, TDQS         | Output           | Termination<br>Data Strobe                                       | Termination data strobe: Applies to the x8 configuration only. When enabled via<br>Mode Register A11=1 in MR1, STT-MRAM will enable the same termination resis-<br>tance function on TDQS/TDQS that is applied to DQS/DQS. When disabled via<br><u>mode</u> register A11=0 in MR1, DM/TDQS will provide the data mask function and<br>TDQS is not used.                                                                                               |

| V <sub>DD</sub>    | Supply           | Power Supply                                                     | Power supply: 1.5V ±0.075V.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>DDQ</sub>   | Supply           | DQ Power<br>Supply                                               | DQ power supply: 1.5V $\pm$ 0.075V. Isolated on the device for improved noise immunity.                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>ss</sub>    | Supply           | Ground                                                           | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>ssq</sub>   | Supply           | DQ Ground                                                        | DQ ground: Isolated on the device for improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>REFCA</sub> | Supply           | Reference<br>Voltage for<br>Control, Com-<br>mand and<br>Address | Reference voltage for control, command, and address: V <sub>REFCA</sub> must be maintained at all times for proper device operation.                                                                                                                                                                                                                                                                                                                  |

Table continues on the next page.

## **Ball Functions and Descriptions (Concluded)**

| Symbol             | Туре           | Name                                                            | Description                                                                                                                                             |

|--------------------|----------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>REFDQ</sub> | Supply         | Reference<br>Voltage for<br>Data                                | Reference voltage for data: V <sub>REFDQ</sub> must be maintained at all times for proper device operation.                                             |

| ZQ                 | Refer-<br>ence | External Ref-<br>erence Ball for<br>Output Drive<br>Calibratoin | External reference ball for output drive calibration: This ball is tied to an external 240 $\Omega$ resistor (RZQ), which is tied to V <sub>SSQ</sub> . |

| NC                 | -              | No Connect                                                      | No Connect: These balls should be left unconnected (the ball has no connection).                                                                        |

| NF                 | -              | No Function                                                     | No Function                                                                                                                                             |

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 5 – Absolute Maximum Ratings

| Symbol                             | Parameter                                                        | Min  | Мах   | Unit | Notes |

|------------------------------------|------------------------------------------------------------------|------|-------|------|-------|

| V <sub>DD</sub>                    | $V_{DD}$ supply voltage relative to $V_{SS}$                     |      |       |      |       |

| V <sub>DDQ</sub>                   | V <sub>DD</sub> supply voltage relative to V <sub>SSQ</sub>      | -0.4 | 1.975 | V    | 1     |

| V <sub>IN</sub> , V <sub>OUT</sub> | Voltage on any pin relative to V <sub>SS</sub>                   |      |       |      |       |

| T <sub>OPER</sub>                  | Normal operating temperature                                     | 0    | 85    | °C   | 2     |

| T <sub>stg</sub>                   | Storage temperature                                              | -55  | 150   | °C   | -     |

| H <sub>max</sub>                   | Maximum magnetic field during read, write, standby or power off. | -    | 2,000 | A/m  |       |

Notes:

- 1.  $V_{DD}$  and  $V_{DDQ}$  must be within 300mV of each other at all times, and  $V_{REF}$  must not be greater than  $0.6 \times V_{DDQ}$ . When  $V_{DD}$  and  $V_{DDQ}$  are <500mV,  $V_{REF}$  can be ≤300mV.

- 2. The normal temperature range specifies the temperature at which all STT-MRAM specifications will be supported. During operation, the STT-MRAM case temperature must be maintained between 0°C to 85°C under all operating conditions.

## **THERMAL CHARACTERISTICS**

### Table 6 – Thermal Characteristics 78-ball BGA Package

| Symbol            | Parameter                              | Value   | Unit    |

|-------------------|----------------------------------------|---------|---------|

| T <sub>OPER</sub> | Maximum Operating Temperature          | 0 to 85 | °C      |

| Θ <sub>JA</sub>   | Thermal Resistance Junction to Ambient | 26.4    | °C/watt |

| Θ <sub>JC</sub>   | Thermal Resistance Junction to Case    | 2.3     | °C/watt |

### Table 7 – Thermal Characteristics 96-ball BGA Package

| Symbol            | Parameter                              | Value   | Unit    |

|-------------------|----------------------------------------|---------|---------|

| T <sub>OPER</sub> | Maximum Operating Temperature          | 0 to 85 | °C      |

| Θ <sub>JA</sub>   | Thermal Resistance Junction to Ambient | 25.6    | °C/watt |

| Θ <sub>JC</sub>   | Thermal Resistance Junction to Case    | 2.3     | °C/watt |

## **DC CHARACTERISTICS**

DC Characteristics are defined under standard measurement conditions specified in JEDEC Standard JESD79-3F.

|                   | All voltages referenced to V <sub>ss</sub>                                                                                                  |       |     |       |      |       |  |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|-------|--|--|--|--|--|--|

| Symbol            | Parameter/Condition                                                                                                                         | Min   | Nom | Мах   | Unit | Notes |  |  |  |  |  |  |

| V <sub>DD</sub>   | Supply Voltage                                                                                                                              | 1.425 | 1.5 | 1.575 | V    | 1, 2  |  |  |  |  |  |  |

| V <sub>DDQ</sub>  | I/O supply voltage                                                                                                                          | 1.425 | 1.5 | 1.575 | V    | 1, 2  |  |  |  |  |  |  |

| I,                | Input leakage current<br>Any input $0V \le V_{IN} \le V_{DD'} V_{REF}$ pin $0V \le V_{IN} \le 1.1V$<br>(All other pins not under test = 0V) | -2    | -   | 2     | μΑ   | 3     |  |  |  |  |  |  |

| I <sub>VREF</sub> | $V_{REF}$ supply leakage current<br>$V_{REFDQ} = V_{DD}/2$ or $V_{REFCA} = V_{DD}/2$<br>(All other pins not under test = 0V)                | -1    | -   | 1     | μΑ   | 3, 4  |  |  |  |  |  |  |

### Table 8 - Power Supply and Input Leakage

Notes:

1.  $V_{DD}$  and  $V_{DDQ}$  must track one another.  $V_{DDQ}$  must be  $\leq V_{DD}$ .  $V_{SS} = V_{SSQ}$ .

V<sub>DD</sub> and V<sub>DDQ</sub> may include AC noise of ±50mV (250 kHz to 20 MHz) in addition to the DC (0 Hz to 250 kHz) specifications. V<sub>DD</sub> and V<sub>DDQ</sub> must be at same level for valid AC timing parameters.

3. V<sub>REF</sub> (see JESD79-3F Section 8, AC and DC Input Measurement Levels)

4. The minimum limit requirement is for testing purposes. The leakage current on the V<sub>RFF</sub> pin should be minimal.

| Note 1 applies to        | Note 1 applies to the entire Table.                      |       |      |      |       |  |  |  |  |  |

|--------------------------|----------------------------------------------------------|-------|------|------|-------|--|--|--|--|--|

| Combol                   | Demonster                                                | DDR3- |      | tes  |       |  |  |  |  |  |

| Symbol                   | Parameter                                                | Min   | Мах  | Unit | Notes |  |  |  |  |  |

| С <sub>ск</sub>          | CK and $\overline{CK}$                                   | 0.8   | 1.6  | pF   |       |  |  |  |  |  |

| С <sub>DCK</sub>         | $\Delta C: CK \text{ to } \overline{CK}$                 | 0     | 0.15 | pF   |       |  |  |  |  |  |

| C                        | Single-end I/O: DQ, DM                                   | 1.5   | 3.0  | pF   | 2     |  |  |  |  |  |

| C <sub>IO</sub>          | Differential I/O: DQS, DQS, TDQS, TDQS                   | 1.5   | 3.0  | pF   | 3     |  |  |  |  |  |

| C <sub>DQQS</sub>        | $\Delta C: DQS to \overline{DQS}, TDQS, \overline{TDQS}$ | 0     | 0.2  | рF   | 3     |  |  |  |  |  |

| C <sub>DIO</sub>         | ΔC: DQ to DQS                                            | -0.5  | 0.3  | pF   | 4     |  |  |  |  |  |

| C <sub>I</sub>           | Inputs (CTRL, CMD, ADDR)                                 | 0.75  | 1.5  | pF   | 5     |  |  |  |  |  |

| C <sub>DI_CTRL</sub>     | ΔC: CTRL to CK                                           | -0.5  | 0.3  | рF   | 6     |  |  |  |  |  |

| C <sub>DI_CMD_ADDR</sub> | ΔC: CMD_ADDR to CK                                       | -0.5  | 0.5  | рF   | 7     |  |  |  |  |  |

| C <sub>ZQ</sub>          | ZQ pin capacitance                                       | -     | 3.0  | рF   |       |  |  |  |  |  |

| C <sub>RE</sub>          | Reset pin capacitance                                    | -     | 3.0  | pF   |       |  |  |  |  |  |

### Table 9 – Input / Output Capacitance

#### Notes:

1.  $V_{DD} = 1.5V \pm 0.075 \text{mV}, V_{DDO} = V_{DD'} V_{REF} = V_{SS'} f = 100 \text{ MHz}, T_C = 25^{\circ}\text{C}. V_{OUT(DC)} = 0.5 \times V_{DDO'} V_{OUT} = 0.1V \text{ (peak-to-peak)}.$

- 2. DM input is grouped with I/O pins, reflecting the fact that they are matched in loading.

- 3. Includes TDQS, TDQS. C<sub>DDOS</sub> is for DQS vs. DQS and TDQS vs. TDQS separately.

- 4.  $C_{\text{DIO}} = C_{\text{IO}(\text{DQ})} 0.5 \times (C_{\text{IO}(\text{DQS})} + C_{\text{IO}(\text{DQS})}).$

- 5. Excludes CK,  $\overline{CK}$ ; CTRL = ODT,  $\overline{CS}$ , and CKE; CMD =  $\overline{RAS}$ ,  $\overline{CAS}$ , and  $\overline{WE}$ ; ADDR = A[n:0], BA[2:0].

- 6.  $C_{DI\_CTRL} = C_{I(CTRL)} 0.5 \times (C_{CK(CK)} + C_{CK(CK)}).$

- 7.  $C_{DI\_CMD\_ADDR} = C_{I(CMD\_ADDR)} 0.5 \times (C_{CK(CK)} + C_{CK(CK)}).$

## Table 10 – I<sub>DD</sub> Maximum Limits

| . 1                           | 1333MT/s | Unite |       |

|-------------------------------|----------|-------|-------|

| I <sub>DD</sub> <sup>1</sup>  | x8       | x16   | Units |

| I <sub>DD0</sub>              | 220      | 220   | mA    |

| I <sub>DD1</sub>              | 220      | 220   | mA    |

| I <sub>DD2P0</sub> (slow)     | 55       | 55    | mA    |

| I <sub>DD2P1</sub> (fast)     | 60       | 60    | mA    |

| I <sub>DD2Q</sub>             | 90       | 90    | mA    |

| I <sub>DD2N</sub>             | 90       | 90    | mA    |

| I <sub>DD2NT</sub>            | 90       | 90    | mA    |

| I <sub>DD3P</sub>             | 60       | 60    | mA    |

| I <sub>DD3N</sub>             | 90       | 90    | mA    |

| I <sub>DD4R</sub>             | 135      | 135   | mA    |

| I <sub>DD4W</sub>             | 165      | 185   | mA    |

| I <sub>DD5B</sub>             | 90       | 90    | mA    |

| I <sub>DD6</sub>              | 45       | 45    | mA    |

| I <sub>DD7</sub> <sup>2</sup> | 490      | 667   | mA    |

| I <sub>DD8</sub>              | 45       | 45    | mA    |

Notes:

- 1. Refer to JESD79-3F Section 10, I<sub>DD</sub> and I<sub>DDQ</sub> Specification Parameters and Test Conditions, with some patterns that are STT-MRAM specific.

- In order to limit power dissipation, I<sub>DD7</sub><sup>2</sup> is specified with <sup>t</sup>FAW = 190ns for the x8 and <sup>t</sup>FAW = 230ns for the x16. The <sup>t</sup>FAW can be reduced per Table 11 but I<sub>DD7</sub> will increase.

### **TIMING PARAMETERS**

### Table 11 – Timing Parameters

| Parameter          |                                             |                      | Symbol                | I/O     | Min      | Max      | Unit | Notes |

|--------------------|---------------------------------------------|----------------------|-----------------------|---------|----------|----------|------|-------|

| Internal READ to t | Internal READ to first data                 |                      | <sup>t</sup> AA       | x8, x16 | 14       | -        | ns   |       |

|                    | ACTIVE to internal READ or WRITE delay time |                      | t <sub>RCD</sub>      | x8      | 95       | -        | ns   | 4     |

| ACTIVE to Interna  |                                             | E delay time         | 'RCD                  | x16     | 190      | -        | ns   | 4     |

| Precharge comm     | and period                                  |                      | t <sub>RP</sub>       | x8      | 66       | -        | ns   | 4     |

|                    |                                             |                      |                       | x16     | 134      | -        | ns   | 4     |

| ACTIVE to ACTIVE   | command per                                 | iod                  | <sup>t</sup> RC       | x8      | 170      | -        | ns   | 4     |

|                    |                                             |                      |                       | x16     | 332      | -        | ns   | 4     |

| ACTIVE to Precha   | rao command i                               | aariad               | <sup>t</sup> RAS      | x8      | 103      | -        | ns   | 4     |

| ACTIVE to Flecha   | rge command j                               | penou                | TAS                   | x16     | 198      | -        | ns   | 4     |

| ACT to ACT Comr    | ACT to ACT Command Period, different banks  |                      | <sup>t</sup> RRD      | x8, x16 | 30       | -        | ns   | 4     |

|                    |                                             | <sup>t</sup> FAW     | x8                    | 120     | -        | ns       | 4    |       |

| Four ACTIVE Wind   | Four ACTIVE Window                          |                      | TAW                   | x16     | 160      | -        | ns   | 4     |

| Output slew rate   | Output slew rate                            |                      | SRQ                   | x8, x16 | -        | 8.5      | V/ns | 4     |

| DQS, DQS# Outp     | ut high time fo                             | r 1333 speed bin     | <sup>t</sup> QSH      | x8, x16 | -        | .38      | nCK  | 4     |

| DQS, DQS# Outp     | ut low time for                             | 1333 speed bin       | <sup>t</sup> QSL      | x8, x16 | -        | .38      | nCK  | 4     |

| Speed Bin          | CL                                          | CWL                  | Sym                   | nbol    | Min      | Мах      | Unit | Notes |

| 800                |                                             | CWL = 5              | <sup>t</sup> CK (     | Avg)    | 2.5      | 3.3      | ns   | 2     |

| 800                | CL= 6                                       | CWL = 6,7,8,9        |                       |         | Reserved |          |      | 3     |

| 1066 <sup>1</sup>  |                                             | CWL = 6              | <sup>t</sup> CK (     | Avg)    | 1.875    | < 2.5    | ns   | 2     |

| 1066               | CL = 8                                      | CL = 8 CWL = 5,7,8,9 |                       |         | Reserved | <u>^</u> |      | 3     |

| 1333 <sup>1</sup>  | CL=10                                       | CWL=7                | <sup>t</sup> CK (     | Avg)    | 1.5      | <1.875   | ns   | 2     |

| 1333 '             |                                             | CWL= 5,6,8,9         | Reserved              |         |          |          |      |       |

|                    |                                             | Supported            | CL settings 6,8,10 CK |         |          |          |      |       |

|                    |                                             | Supported C          | WL settings           |         | 5,6,7    |          | СК   |       |

1. The 1333 and 1066 speed grade ordering options are backward compatible with lower speed grade operation.

2. The CL and CWL settings result in <sup>t</sup>CK requirements. When making a selection of <sup>t</sup>CK, both CL and CWL requirement settings need to be fulfilled.

- 3. Reserved settings are not allowed.

- 4. Parameter is different than Standard DDR3 due to STT-MRAM design

Note: Dynamic ODT timings are intended to follow the JEDEC specification but have not been characterized.

### **TRUTH TABLES**

### **Command Truth Table**

| Notes 1-5 apply to the entire                 | Notes 1-5 apply to the entire Table. |                                 |      |    |     |         |          |       |      |      |      |        |       |

|-----------------------------------------------|--------------------------------------|---------------------------------|------|----|-----|---------|----------|-------|------|------|------|--------|-------|

| Function                                      | Symbol                               | С                               | CKE  |    | RAS |         | WE       | BA    | A13- | A12/ | A10/ | A0-A9, | Notes |

| Function                                      | Symbol                               | Prev.                           | Next | CS | KAS | CAS     | VVE      | [2:0] | A15  | BC   | AP   | A11    | Notes |

| Mode Register Set                             | MRS                                  | Н                               | н    | L  | L   | L       | L        | BA    |      | Op.  | Code |        |       |

| Refresh                                       | REF                                  |                                 |      |    |     |         |          |       |      |      |      |        |       |

| Self Refresh Entry                            | SRE                                  |                                 |      |    | Not | used fo | or STT-I | MRAM  |      |      |      |        |       |

| Self Refresh Exit                             | SRX                                  |                                 |      |    |     |         |          |       |      |      |      |        |       |

| Single Bank Precharge                         | PRE                                  | Н                               | н    | L  | L   | Н       | L        | BA    | V    | V    | L    | V      |       |

| Precharge All Banks                           | PREA                                 | н                               | н    | L  | L   | н       | L        | L     | L    | L    | н    | V      |       |

| Bank ACTIVE                                   | ACT                                  | H H L L H H BA Row Address (RA) |      |    |     | RA)     |          |       |      |      |      |        |       |

| WRITE (Fixed BL8 pr BC4)                      | WR                                   | н                               | н    | L  | н   | L       | L        | BA    | RFU  | V    | L    | V, CA  | 7     |

| WRITE (BC4 on the Fly)                        | WRS4                                 | н                               | н    | L  | н   | L       | L        | BA    | RFU  | L    | L    | V, CA  | 7     |

| WRITE (BL8 on the Fly)                        | WRS8                                 | н                               | н    | L  | н   | L       | L        | BA    | RFU  | н    | L    | V, CA  | 7     |

| WRITE w/ Auto Precharge<br>(Fixed BL8 or BC4) | WRAP                                 | Н                               | н    | L  | н   | L       | L        | BA    | RFU  | v    | н    | V, CA  | 7     |

| WRITE w/ Auto Precharge<br>(BC4 On the Fly)   | WRAPS4                               | н                               | н    | L  | н   | L       | L        | BA    | RFU  | L    | н    | V, CA  | 7     |

| WRITE w/ Auto Precharge<br>(BL8 On the Fly)   | WRAPS8                               | Н                               | н    | L  | н   | L       | L        | BA    | RFU  | н    | н    | V, CA  | 7     |

| READ (Fixed BL8 or BC4)                       | RD                                   | Н                               | н    | L  | н   | L       | Н        | BA    | RFU  | V    | L    | V, CA  | 7     |

| READ (BC4, on the Fly)                        | RDS4                                 | Н                               | н    | L  | н   | L       | н        | BA    | RFU  | L    | L    | V, CA  | 7     |

| READ (BL8, on the Fly)                        | RDS8                                 | н                               | н    | L  | н   | L       | н        | BA    | RFU  | н    | L    | V, CA  | 7     |

### Table 12 – Command Truth Table

Table continues with notes next page.

### **Command Truth Table (Continued)**

| Function                                       | Cumhal | СК    | E    |   | RAS |     | WE | BA             | A13- | A12/ | A10/ | A0-A9, | Notes |

|------------------------------------------------|--------|-------|------|---|-----|-----|----|----------------|------|------|------|--------|-------|

| Function                                       | Symbol | Prev. | Next |   | KAS | CAS | WE | [ <b>2:0</b> ] | A15  | BC   | AP   | A11    | Notes |

| READ with Auto Precharge<br>(Fixed BL8 or BC4) | RDAP   | Н     | Н    | L | н   | L   | Н  | BA             | RFU  | V    | Н    | V, CA  | 7     |

| READ with Auto Precharge<br>(BC4, on the Fly)  | RDAPS4 | Н     | Н    | L | н   | L   | Н  | BA             | RFU  | L    | Н    | V, CA  | 7     |

| READ (BL8, on the Fly)                         | RDAPS8 | н     | Н    | L | н   | L   | н  | BA             | RFU  | Н    | н    | V, CA  | 7     |

| No Operation                                   | NOP    | Н     | Н    | L | н   | Н   | н  | V              | V    | V    | V    | V      | 8     |

| Device Deselected                              | DES    | Н     | Н    | н | Х   | Х   | Х  | Х              | Х    | х    | х    | х      | 9     |

|                                                | DDE    |       |      | L | Н   | Н   | Н  | v              | v    | V    | v    | V      |       |

| Power Down Entry                               | PDE    | Н     | L    | н | V   | V   | V  | V              | V    | V    | V    | V      |       |

|                                                | DDV    |       |      | L | н   | Н   | Н  | v              | V    | V    | v    | N      | 6     |

| Power Down Exit                                | PDX    | L     | Н    | н | V   | V   | V  | V              | V    | V    | V    |        | 6     |

| ZQ Calibration Long                            | ZQCL   | Н     | Н    | L | н   | Н   | L  | х              | х    | х    | н    | х      | 10    |

| ZQ Calibration Short                           | ZQCS   | Н     | Н    | L | н   | Н   | L  | Х              | Х    | Х    | L    | Х      |       |

Notes:

1. Commands are defined by states of CS, RAS, CAS, WE, and CKE at the rising edge of the clock. The MSB of BA, RA, and CA are device-, density-, and configuration-dependent.

2. RESET is LOW enabled and used only for asynchronous reset. Thus, RESET must be held HIGH during any normal operation.

- 3. The state of ODT does not affect the states described in this table.

- 4. Operations apply to the bank defined by the bank address, BA[2:0]. For MRS, BA selects one of four mode registers.

- 5. "V" means "H" or "L" (a defined logic level), and "X" means "Don't Care."

- 6. See the CKE Truth Table below for additional information on CKE transition.

- 7. Burst READ's or WRITE's cannot be terminated or interrupted. MRS (fixed) and OTF BL/BC are defined in MR0.

- 8. The purpose of the NOP command is to prevent the MRAM from registering any unwanted commands. A NOP will not terminate an operation that is executing.

- 9. The DES and NOP commands perform similarly.

- 10. ZQ CALIBRATION LONG is used for either ZQinit (first ZQCL command during initialization) or ZQoper (ZQCL command after initialization).

### **CKE Truth Table**

### Table 13 – CKE Truth Table

| Notes 1,2 apply to the entire Table. |                                                                                                  |   |                            |                            |  |  |  |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------|---|----------------------------|----------------------------|--|--|--|--|--|

| 2                                    | СК                                                                                               | Έ | Command <sup>5</sup> (RAS, |                            |  |  |  |  |  |

| Current State <sup>3</sup>           | Tate <sup>3</sup> Previous Cycle Present Cycle (n-1) <sup>4</sup> (n) <sup>4</sup> (CAS, WE. CS) |   |                            | Action <sup>5</sup>        |  |  |  |  |  |

| Power Down                           | L                                                                                                | L | Х                          | Maintain Power Down        |  |  |  |  |  |

| Power Down                           | L H                                                                                              |   | DES or NOP                 | Power Down Exit            |  |  |  |  |  |

| Bank(s) Active                       | Н                                                                                                | L | DES or NOP                 | Active Power Down Entry    |  |  |  |  |  |

| Reading                              | Н                                                                                                | L | DES or NOP                 | Power Down Entry           |  |  |  |  |  |

| Writing                              | Н                                                                                                | L | DES or NOP                 | Power Down Entry           |  |  |  |  |  |

| Precharging                          | н                                                                                                | L | DES or NOP                 | Power Down Entry           |  |  |  |  |  |

| All Banks Idle <sup>6</sup>          | Н                                                                                                | L | x                          | Precharge Power Down Entry |  |  |  |  |  |

|                                      | Н                                                                                                | L | Χ                          | -                          |  |  |  |  |  |

Notes:

1. All states and sequences not shown are illegal or reserved unless explicitly described elsewhere in this document.

<sup>t</sup>CKE (MIN) means CKE must be registered at multiple consecutive positive clock edges. CKE must remain at the valid input level the entire time it takes to achieve the required number of registration clocks. Thus, after any CKE transition, CKE may not transition from its valid level during the time period of <sup>t</sup>IS + <sup>t</sup>CKE (MIN) + <sup>t</sup>IH.

3. Current state = The state of the STT-MRAM immediately prior to clock edge n.

4. CKE (n) is the logic state of CKE at clock edge n; CKE (n - 1) was the state of CKE at the previous clock edge.

- 5. COMMAND is the command registered at the clock edge (must be a legal command as defined in Table 12 on page 21) Action is a result of COMMAND. ODT does not affect the states described in this table and is not listed.

- 6. Idle state = All banks are closed, no data bursts are in progress, CKE is HIGH, and all timings from previous operations are satisfied. All power-down exit parameters are also satisfied.

### **FUNCTIONAL PARAMETERS**

| Functional<br>Parameter                      | Level                                 | Description                                                                                                                                                                                                                                   |

|----------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit Error Rate (BER)<br>Limit to End of Life | 6.3 x 10 <sup>-8</sup>                | It is expected that bit fails will be soft and distributed through-<br>out the address space so the system ECC built into your control-<br>ler should correct them. BER is after maximum page cycles, or at<br>the end of the endurance life. |

| Cycle Endurance                              | 1 x10 <sup>10</sup>                   | A cycle is defined as a page access. After this number of cycles,<br>the bit error rate may start to increase above the BER limit. Sys-<br>tem level ECC is recommended.                                                                      |

| Data Retention                               | T <sub>OPER</sub> = 70°C,<br>3 months | The data retention time starts from the last read or write cycle<br>and does not differ between powered up and powered down<br>conditions.                                                                                                    |

## **COMMAND DESCRIPTIONS**

The 256Mb STT-MRAM is fully compatible with the command descriptions of JESD79-3F, section 4, with the following additional considerations:

- 1. Timing for Active, Precharge, Read, and Write commands are as described in JESD79-3F, with some exceptions due to the timing differences between DRAM and MRAM. These exceptions are noted in the description sections for each command.

- To ensure the non-volatility of any data stored in the MRAM, it is necessary to close any open page by issuing a PRECHARGE command to any open banks or all banks (PRE or PREA). The PRECHARGE must be completed and <sup>t</sup>RP met with V<sub>DD</sub> within the specified operating range.

### **ACTIVE Command**

Before any READ or WRITE commands can be issued to a bank within the MRAM, a row in that bank must be opened (activated). This is accomplished via the ACTIVE command, which selects both the bank and the row to be activated.

After a row is opened with an ACTIVE command, a READ or WRITE command may be issued to that row, subject to the <sup>t</sup>RCD specification. However, if the additive latency is programmed correctly, a READ or WRITE command may be issued prior to <sup>t</sup>RCD (MIN). In this operation, the MRAM enables a READ or WRITE command to be issued after the ACTIVE command for that bank, but prior to <sup>t</sup>RCD (MIN) with the requirement that (ACTIVE-to-READ/WRITE) + AL  $\geq$  <sup>t</sup>RCD (MIN) (see Posted CAS Additive Latency). <sup>t</sup>RCD (MIN) should be divided by the clock period and rounded up to the next whole number to determine the earliest clock edge after the ACTIVE command on which a READ or WRITE command can be entered. The same procedure is used to convert other specification limits from time units to clock cycles.

When at least one bank is open, any READ-to-READ command delay or WRITE-to-WRITE command delay is restricted to <sup>t</sup>CCD (MIN).

A subsequent ACTIVE command to a different row in the same bank can only be issued after the previous active row has been closed (precharged). The minimum time interval between successive ACTIVE commands to the same bank is defined by <sup>t</sup>RC. A subsequent ACTIVE command to another bank can be issued while the first bank is being accessed, which results in a reduction of total row-access overhead. The minimum time interval between successive ACTIVE commands to different banks is defined by <sup>t</sup>RRD. No more than four bank ACTIVE commands may be issued in a given <sup>t</sup>FAW (MIN) period, and the <sup>t</sup>RRD (MIN) restriction still applies. The <sup>t</sup>FAW (MIN) parameter applies, regardless of the number of banks already opened or closed.

### Figure 4 – ACTIVE Command Example: Meeting <sup>t</sup>RRD (MIN) and <sup>t</sup>RCD (MIN)

- 1. In this example, <sup>f</sup>CK=533MHz, 1066 MT/sec/pin, CL <sup>t</sup>RCD <sup>t</sup>RP = 8- 47-36, a READ or WRITE command may be issued 47 nCK (clock cycles) after the Bank is Activated.

- 2. The minimum time interval between successive ACTIVE commands to different banks is defined by <sup>t</sup>RRD.

- 3. After a row is opened with an ACTIVE command, a READ or WRITE command may be issued to that row, subject to the <sup>t</sup>RCD specification.

#### **PRECHARGE Command**

Input A10 determines whether one bank or all banks are to be precharged and, in the case where only one bank is to be precharged, inputs BA[2:0] select the bank.

When all banks are to be precharged, inputs BA[2:0] are treated as "Don't Care." After a bank is precharged, it is in the idle state and must be activated prior to any READ or WRITE commands being issued.

### Figure 5 – PRECHARGE Command Timing

#### Notes:

- 1. In this example,  ${}^{f}CK = 533$  MHz, 1066 MT/sec/pin, AL=0, CL=8 with BC4 selected.

- 2. The minimum READ command to PRECHARGE command spacing to the same bank is equal to AL+ <sup>t</sup>RTP, with <sup>t</sup>RTP being the internal READ to PRECHARGE delay, 5 nCK (clock cycles).

- 3. Following the PRECHARGE command, a subsequent command to the same bank cannot be issued until <sup>t</sup>RP is met. This is 36 nCK (clock cycles) from the PRECHARGE command.

- 4. <sup>t</sup>RAS min and <sup>t</sup>RC min must be satisfied from the previous ACTIVE command.

### **READ Command**

READ bursts are initiated with a READ command. The starting column and bank addresses are provided with the READ command and auto precharge is either enabled or disabled for that burst access. If auto precharge is enabled, the row being accessed is automatically precharged at the completion of the burst. If auto precharge is disabled, the row will be left open after the completion of the burst.

During READ bursts, the valid data-out element from the starting column address is available READ latency (RL) clocks later. RL is defined as the sum of posted CAS additive latency (AL) and CAS latency (CL) (RL = AL + CL). The value of AL and CL is programmable in the mode register via the MRS command. Each subsequent data-out element is valid nominally at the next positive or negative clock edge (that is, at the next crossing of CK and  $\overline{CK}$ ) Figure 6 below illustrates an example of RL based on a CL setting of 8 and an AL setting of 0.

Figure 6 – READ Command Timing

#### Notes:

- Read Latency (RL) is defined as the sum of POSTED CAS ADDITIVE latency (AL) and CAS latency (CL), (RL = AL + CL). -The value of AL and CL is programmable in the mode register via the MRS command. In this example, <sup>f</sup>CK = 533MHz, 1066 speed bin, CL=8, AL=0.

- 2. DO n=data-out from column n. Subsequent elements of data-out appear in the programmed order following DO n. -The burst length is selected by MRO and A12 during the READ command.

- 3. Bank "a" was previously opened with an ACTIVE Command.

DQS, DQS is driven by the MRAM along with the output data. The initial LOW state on DQS and HIGH state on DQS is known as the READ preamble (<sup>t</sup>RPRE). The LOW state on DQS and the HIGH state on DQS, coincident with the last data-out element, is known as the READ postamble (<sup>t</sup>RPST). Upon completion of a burst, assuming no other commands have been initiated, the DQ goes High-Z. A detailed explanation of <sup>t</sup>DQSQ (valid data-out skew), <sup>t</sup>QH (data-out window hold), and the valid data window are depicted in Section 4.13.2.1 of JESD79-3F. A detailed explanation of <sup>t</sup>DQSCK (DQS transition skew to CK) is depicted in the same section.

Data from any READ burst may be concatenated with data from a subsequent READ command to provide a continuous flow of data. The first data element from the new burst follows the last element of a completed burst. The new READ command should be issued <sup>t</sup>CCD cycles after the first READ command. This is shown for BL8 in Standard JESD79-3F Figure 33. If BC4 is enabled, <sup>t</sup>CCD must still be met, which will cause a gap in the data output, as shown in JESD79-3F Figure 34. The DDR3 MRAM does not allow interrupting or truncating any READ burst. Data from any READ burst must be completed before a subsequent WRITE burst is allowed. An example of a READ burst followed by a WRITE burst for BL8 can be found in JESD79-3F Figure 35, *READ (BL8) to WRITE (BL8).* READ to WRITE timing for BC4 can be found in JESD79-3F Figure 36, *READ (BC4) to WRITE (BC4) OTF.* To ensure the READ data is completed before the WRITE data is on the bus, the minimum READ-to-WRITE timing is RL + <sup>t</sup>CCD - WL + 2<sup>t</sup>CK.

For additional information on the READ command, please refer to JESD79-3F Section 4.13. Please note that in READ followed by a PRECHARGE, the MRAM <sup>t</sup>RP needs to be observed for a given CL.

### WRITE Command

WRITE bursts are initiated with a WRITE command. The starting column and bank addresses are provided with the WRITE command, and auto precharge is either enabled or disabled for that access. If auto-precharge is selected, the row being accessed is precharged at the end of the WRITE burst. If auto-precharge is not selected, the row will remain open for subsequent accesses. After a WRITE command has been issued, the WRITE burst may not be interrupted.

During WRITE bursts, the first valid data-in element is registered on the first rising edge of DQS immediately following the WRITE latency (WL) clock time. Data elements will continue to be registered on successive edges of DQS.

WRITE latency (WL) is defined as the sum of posted CAS additive latency (AL) and CAS WRITE latency (CWL): WL = AL + CWL. The values of AL and CWL are programmed in the MR0 and MR2 registers respectively. Only AL=0 is supported. Prior to the first valid DQS edge, a full cycle is needed (including a dummy crossover of DQS,  $\overline{DQS}$ ) and specified as the WRITE preamble shown in "Figure 7 – WRITE Burst Operation WL = 5 (AL = 0 CWL = 5, BL8)" on page 29. The half cycle on DQS following the last data-in element is known as the WRITE postamble.

The time between the WRITE command and the first valid edge of DQS is WL clocks ±<sup>t</sup>DQSS. Standard JESD79-3F Figure 43 includes <sup>t</sup>DQSS (MIN), <sup>t</sup>DQSS (NOM) and <sup>t</sup>DQSS (MAX) cases.

Data may be masked from completing a WRITE using data mask. The data mask occurs on the DM ball aligned to the WRITE data. If DM is LOW, the WRITE completes normally. If DM is HIGH, that bit of data is masked.

Upon completion of a burst, assuming no other commands have been initiated, the DQ will remain High-Z,

and any additional input data will be ignored.

Data for any WRITE burst may be concatenated with a subsequent WRITE command to provide a continuous flow of input data. The new WRITE command can be <sup>t</sup>CCD clocks following the previous WRITE command. The first data element from the new burst is applied after the last element of a completed burst. Standard JESD79-3F Figure 51, *WRITE(BL8) to WRITE(BL8)* and Figure 52, *WRITE (BC4) to WRITE (BC4) OTF* illustrate concatenated bursts.

Data for any WRITE burst may be followed by a subsequent READ command after <sup>t</sup>WTR has been met (see Standard JESD79-3F Figure 53, *WRITE (BL8) to READ (BC4/BL8) OTF*.) Additional WRITE burst diagrams are given in Section 4.14, *WRITE Operation*.

Data for any WRITE burst may be followed by a subsequent PRECHARGE command, providing <sup>t</sup>WR has been met, as shown in Standard JESD79-3F Figures 49 and 50. Please note that in Write followed by a PRE-CHARGE, the MRAM <sup>t</sup>RP needs to be observed for a given CL.

Both <sup>t</sup>WTR and <sup>t</sup>WR starting time may vary, depending on the mode register settings (fixed BC4, BL8 versus OTF).

#### Figure 7 – WRITE Burst Operation WL = 5 (AL = 0 CWL = 5, BL8)

TRANSITIONING DATA 🛛 DON'T CARE

Notes:

- 1. BL8, WL= 5; AL=0, CWL=5

- 2.  $D_{IN} n = data-in from column n.$

- 3. NOP commands are shown for ease of illustration; other commands may be valid at these times.

- 4. BL8 setting activated by either MR0 [A1:0= 00] or MR0 [A1:0 = 01] and A12 = 1 during WRITE command at T0

### Burst Length, Type and Order

Accesses within a given burst may be programmed only in a sequential order which is selected via bit A3 of Mode Register MR0=0. The ordering of accesses within a burst is determined by the burst length and the starting column address as shown in Table 14 below. The burst length is defined by bits A1:A0 of Mode Register MR0. Burst length options include fixed BC4, fixed BL8, and "on the fly" which allows BC4 or BL8 to be selected coincident with the registration of a Read or Write command via A12/BC\_n.

| Burst<br>Length | READ/<br>WRITE | Starting Column Address<br>A[2,1,0] | Burst Type = Sequencial<br>(Decimal) |

|-----------------|----------------|-------------------------------------|--------------------------------------|

|                 |                | 000                                 | 0, 1, 2, 3, T, T, T, T               |

| DCA             | READ           | 100                                 | 4, 5, 6, 7, T, T, T, T               |

| BC4             | WRITE          | 0, V, V                             | 0, 1, 2, 3, X, X, X, X               |

|                 | VVRITE         | 1, V, V                             | 4, 5, 6, 7, X, X, X, X               |

|                 |                | 000                                 | 0, 1, 2, 3, 4, 5, 6, 7               |

| BL8             | READ           | 100                                 | 4, 5, 6, 7, 0, 1, 2, 3               |

|                 | WRITE          | V, V, V                             | 0, 1, 2, 3, 4, 5, 6, 7               |

### Table 14 – Burst Length, Type and Order

Burst Type/Burst Order supports only the sequential burst type for CA<2:0 = 000 or 100

### PART NUMBER DECODER

#### Table 15 – 256Mb x8 / x16 STT-MRAM Ordering Part Number Decoder

|                        |                              | Vendor    | Category | Family | Voltage | Density | IO Width | Package | Timing | Temp | Rev | Class | Packing |

|------------------------|------------------------------|-----------|----------|--------|---------|---------|----------|---------|--------|------|-----|-------|---------|

|                        | Example Ordering Part Number | E         | м        | D3     | D       | 256M    | 8        | G1      | -150   | С    | В   | S1    | R       |

| Everspin               | E                            |           |          |        |         |         |          |         |        |      |     |       |         |

| Magneto-resistive      | М                            |           |          |        |         |         |          |         |        |      |     |       |         |

| DDR3                   | D3                           |           |          |        |         |         |          |         |        |      |     |       |         |

| SSTL: Vcc & Vdd = 1.5v | D                            |           |          |        |         |         |          |         |        |      |     |       |         |

| 256 Mb                 | 256M                         |           |          |        |         |         |          |         |        |      |     |       |         |

| x8                     | 08                           |           |          |        |         |         | -        |         |        |      |     |       |         |

| x16                    | 16                           |           |          |        |         |         |          |         |        |      |     |       |         |

| 10x13 BGA 78-ball      | G1                           |           |          |        |         |         |          |         |        |      |     |       |         |

| 1333 MT/s              | -150                         |           |          |        |         |         |          |         |        |      |     |       |         |

| Commercial             | С                            | 0 to 85°C |          |        |         |         |          |         |        |      |     |       |         |

| Device Version         | Note 1                       |           |          |        |         |         |          |         |        |      |     |       |         |

| Device Class           | Note 2                       |           |          |        |         |         |          |         |        |      |     |       |         |

| Tray                   | <blank></blank>              |           |          |        |         |         |          |         |        |      |     |       |         |

| Tape and Reel          | R                            |           |          |        |         |         |          |         |        |      |     |       |         |

| Note 1         |                |  |  |  |  |  |  |  |

|----------------|----------------|--|--|--|--|--|--|--|

| Device Version | Definition     |  |  |  |  |  |  |  |

| A              | First Version  |  |  |  |  |  |  |  |

| В              | Second Version |  |  |  |  |  |  |  |

| Note 2       |             |  |  |  |  |  |  |

|--------------|-------------|--|--|--|--|--|--|

| Device Class | Definition  |  |  |  |  |  |  |

| S1           | Storage DEC |  |  |  |  |  |  |

### **ORDERING PART NUMBERS**

### Table 16 – Ordering Part Numbers

| Org       | Temp     | Package                   | Speed<br>Bin | Shipping<br>Container | Part Number            |

|-----------|----------|---------------------------|--------------|-----------------------|------------------------|

| 32Mb x 8  | 0 - 85°C | 10x13mm<br>78-ball<br>BGA | 1333         | Trays                 | EMD3D256M08G1-150CBS1  |

|           |          |                           |              | Tape and<br>Reel      | EMD3D256M08G1-150CBS1R |

| 16Mb x 16 | 0 - 85°C | 10x13mm<br>96-ball<br>BGA | 1333         | Trays                 | EMD3D256M16G2-150CBS1  |

|           |          |                           |              | Tape and<br>Reel      | EMD3D256M16G2-150CBS1R |

### **PACKAGE OUTLINE DRAWING**

#### NDTES

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. 'eE' & 'eD' REPRESENT THE BASIC SOLDER BALL GRID PITCH

- 3. 'b' IS MEASURABLE AT THE MAXIMUN SOLDER BALL DIAMETER PARALLEL TO PRIMARY DATUM C. THE SOLDER BALL DIAMETER IS Ø0.45mm BEFORE REFILOW.THE SOLDER BALL PAD Ø0.40mm

- 4, PRIMARY DATUM C ARE DEFINED BY THE SPHERICAL,

- 5, THE DVERALL PACKAGE THICKNESS 'A' ALREADY CONSIDER COLLAPSE,

- 6, PACKAGE DIMENSIONS CONFORM TO JEDEC MO-207,

- 7. THE DISTANCE BETWEEN THE TOP SURFACE OF SMALLEST SOLDER BALL (BALL HEIGHT) AND WINDOW-SIDE ENCAPSULANT MUST > 0.10mm,

- 8. THE HEIGHT OF WINDOW-SIDE ENCAPSULANT 't' COULD CHANGED ASSEMBLY HOUSE'S DESIGN, BUT IT MUST SATISFY THE REQUEST OF ITEM 7.

- 9. 'W' DEFINES THE DISTANCE BETWEEN THE EDGE OF SOLDER BALL AND WINDOW-SIDE ENCAPSULANT.

#### Figure 9 – 78-Ball BGA Package Outline (x8) Dimensions

| DIMENSI | Units mm |       |       |

|---------|----------|-------|-------|

| REF.    | MIN.     | NDM.  | MAX.  |

| A       |          |       | 1.20  |

| A1      | 0.25     |       | 0,40  |

| b       | 0.40     |       | 0.50  |

| D       | 12.90    | 13.00 | 13.10 |

| E       | 9,90     | 10.00 | 10.10 |

| D1      | 9.60 BSC |       |       |

| E1      | 6.40 BSC |       |       |

| еE      | 0.80 BSC |       |       |

| eD      | 0.80 BSC |       |       |

| ۵۵۵     |          |       | 0.15  |

| bbb     |          |       | 0.20  |

| CCC     |          |       | 0.10  |

| ddd     |          |       | 0.15  |

| eee     |          |       | 0,08  |

| W       | 0.1      |       |       |

| t       |          |       | 0.20  |

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. 'eE' & 'eD' REPRESENT THE BASIC SOLDER BALL GRID PITCH

- 3. 'b' IS MEASURABLE AT THE MAXIMUN SOLDER BALL DIAMETER PARALLEL TO PRIMARY DATUM C. THE SOLDER BALL DIAMETER IS Ø0.45mm BEFORE REFILOW.THE SOLDER BALL PAD Ø0.40mm

- 4. PRIMARY DATUM C ARE DEFINED BY THE SPHERICAL.

- 5. THE OVERALL PACKAGE THICKNESS 'A' ALREADY CONSIDER COLLAPSE.

- 6. PACKAGE DIMENSIONS CONFORM TO JEDEC MD-207.

- 7. THE DISTANCE BETWEEN THE TOP SURFACE OF SMALLEST SOLDER BALL (BALL HEIGHT) AND WINDOW-SIDE ENCAPSULANT MUST > 0.10mm.

- THE HEIGHT OF WINDOW-SIDE ENCAPSULANT 't' COULD CHANGED ASSEMBLY HOUSE'S DESIGN, BUT IT MUST SATISFY THE REQUEST OF ITEM 7.

- 'W' DEFINES THE DISTANCE BETWEEN THE EDGE OF SOLDER BALL AND WINDOW-SIDE ENCAPSULANT.

### Figure 11 – 96-Ball BGA Package Outline (x16) Dimensions

| DIVIENSION REFERENCES Units m |          |       |       |  |

|-------------------------------|----------|-------|-------|--|

| REF.                          | MIN.     | NDM.  | MAX.  |  |

| A                             |          |       | 1.20  |  |

| <u>A1</u>                     | 0,25     |       | 0,40  |  |

| b                             | 0.40     |       | 0,50  |  |

| D                             | 12.90    | 13.00 | 13.10 |  |

| E                             | 9,90     | 10.00 | 10.10 |  |