# S1C17M12/M13 (rev1.0)

### **16-bit Single Chip Microcontroller**

- 16KB Flash ROM: Read/program protection function, 2KB RAM

- Supports 1.8V to 5.5V wide range operating voltage.

- Five-digit seven-segment LED controller (8SEG × 1–5COM (max.))

- Supports various kinds of interfaces (UART, SPI, I<sup>2</sup>C)

### **■ DESCRIPTIONS**

The S1C17M12/M13 is a 16-bit embedded Flash MCU that features low power consumption. It includes various serial interfaces and a seven-segment LED controller on the compact die. It is suitable for control panels with a seven-segment display for housing equipment and FA equipment.

### **■ FEATURES**

| Model                                        | S1C17M12                                                                                           | S1C17M13                                  |

|----------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------|

| CPU                                          | ·                                                                                                  |                                           |

| CPU core                                     | Seiko Epson original 16-bit RISC CPU core S1                                                       | IC17                                      |

| Other                                        | On-chip debugger                                                                                   |                                           |

| Embedded Flash memory                        |                                                                                                    |                                           |

| Capacity                                     | 16K bytes (for both instructions and data)                                                         |                                           |

| Erase/program count                          | 1,000 times (min.)                                                                                 |                                           |

| Other                                        | Security function to protect from reading/prog                                                     | ramming by ICDmini                        |

|                                              | On-board programming function using ICDmir                                                         | ni                                        |

| Embedded RAM                                 |                                                                                                    |                                           |

| Capacity                                     | 2K bytes                                                                                           |                                           |

| Clock generator (CLG)                        |                                                                                                    |                                           |

| System clock source                          | 3 sources (IOSC/OSC3/EXOSC)                                                                        |                                           |

| System clock frequency (operating frequency) | 16.8 MHz (max.)                                                                                    |                                           |

| IOSC oscillator circuit (boot clock source)  | 700 kHz (typ.) embedded oscillator                                                                 |                                           |

|                                              | 23 µs (max.) starting time (time from cancelation                                                  | on of SLEEP state to vector table read by |

|                                              | the CPU)                                                                                           |                                           |

| OSC3 oscillator circuit                      | 16.8 MHz (max.) crystal/ceramic oscillator                                                         |                                           |

|                                              | 4, 8, 12, and 16 MHz-switchable embedded of                                                        | scillator                                 |

| EXOSC clock input                            | 16.8 MHz (max.) square or sine wave input                                                          |                                           |

| Other                                        | Configurable system clock division ratio                                                           |                                           |

|                                              | Configurable system clock used at wake up from                                                     | om SLEEP state                            |

|                                              | Operating clock frequency for the CPU and all                                                      | peripheral circuits is selectable.        |

| I/O port (PPORT)                             |                                                                                                    |                                           |

| Number of general-purpose I/O ports          | Input/output port: 38 bits (max.)                                                                  |                                           |

|                                              | Output port: 1 bit (max.)                                                                          |                                           |

|                                              | Pins are shared with the peripheral I/O.                                                           |                                           |

| Number of input interrupt ports              | 34 bits (max.)                                                                                     |                                           |

| Number of ports that support universal port  | 21 bits                                                                                            |                                           |

| multiplexer (UPMUX)                          | A peripheral circuit I/O function selected via so                                                  | oftware can be assigned to each port.     |

| Number of high drive-capability Nch outputs  | 8 bits (max.)                                                                                      |                                           |

|                                              | 7 mA output (max.)                                                                                 |                                           |

| Number of high drive-capability Pch outputs  | 5 bits (max.)                                                                                      |                                           |

|                                              | 56 mA output (max., Total sum of 5 bits)                                                           |                                           |

| Timers                                       |                                                                                                    |                                           |

| Watchdog timer (WDT2)                        | Generates NMI or watchdog timer reset.                                                             |                                           |

|                                              | Programmable NMI/reset generation cycle                                                            |                                           |

| 16-bit timer (T16)                           | 4 channels                                                                                         |                                           |

|                                              | Generates the SPIA master clock and the ADC                                                        | C12A trigger signal.                      |

| 16-bit PWM timer (T16B)                      | 1 channel                                                                                          |                                           |

|                                              | Event counter/capture function                                                                     |                                           |

|                                              | PWM waveform generation function                                                                   |                                           |

|                                              | Number of PWM output or capture input ports                                                        | s: 2 ports/channel                        |

| Supply voltage detector (SVD3)               |                                                                                                    |                                           |

|                                              |                                                                                                    |                                           |

| Detection voltage                            | VDD or external voltage (two external voltage in                                                   | nput ports are provided.)                 |

| Detection voltage Detection level            | VDD or external voltage (two external voltage in VDD: 28 levels (1.8 to 5.0 V)/external voltage: 3 | · · · · /                                 |

|                                              | 9 1                                                                                                | · · · · /                                 |

| Model                                       | S1C17M12                                | S1C17M13                                                 |  |  |  |

|---------------------------------------------|-----------------------------------------|----------------------------------------------------------|--|--|--|

|                                             | SICIAMIZ                                | SICIAMIS                                                 |  |  |  |

| Serial interfaces                           | A channels                              |                                                          |  |  |  |

| UART (UART3)                                | 4 channels                              |                                                          |  |  |  |

|                                             | Baud-rate generator included, IrDA      |                                                          |  |  |  |

|                                             |                                         | and baud rate division ratio are configurable.           |  |  |  |

|                                             | Infrared communication carrier mo       | dulation output function                                 |  |  |  |

| Serial interfaces                           | T                                       |                                                          |  |  |  |

| Synchronous serial interface (SPIA)         | 2 channels                              |                                                          |  |  |  |

|                                             | 2 to 16-bit variable data length        |                                                          |  |  |  |

|                                             |                                         | for the baud-rate generator in master mode.              |  |  |  |

| I <sup>2</sup> C (I2C)                      | 1 channel                               |                                                          |  |  |  |

|                                             | Baud-rate generator included            |                                                          |  |  |  |

| IR remote controller (REMC2)                |                                         |                                                          |  |  |  |

| Number of transmitter channels              | 1 channel                               |                                                          |  |  |  |

| Other                                       | EL lamp drive waveform can be ge        | nerated for an application example.                      |  |  |  |

| Seven-segment LED controller (LEDC)         | <u> </u>                                |                                                          |  |  |  |

| LED control output                          | Seven-segment LED outputs up to         | five digits (8SEG × 1–5COM(max.))                        |  |  |  |

|                                             | COM time-division dynamic drive of      | control                                                  |  |  |  |

|                                             | Software configurable anode/catho       | ode common mode and off-state pin status                 |  |  |  |

|                                             | Four-level brightness adjustment fu     | unction                                                  |  |  |  |

| 12-bit A/D converter (ADC12A)               |                                         |                                                          |  |  |  |

| Conversion method                           | -                                       | Successive approximation type                            |  |  |  |

| Resolution                                  |                                         | 12 bits                                                  |  |  |  |

| Number of conversion channels               |                                         | 1 channel                                                |  |  |  |

| Number of analog signal inputs              |                                         | 8 ports/channel                                          |  |  |  |

| Multiplier/divider (COPRO2)                 |                                         |                                                          |  |  |  |

| Arithmetic functions                        | 16-bit × 16-bit multiplier              |                                                          |  |  |  |

|                                             | 16-bit × 16-bit + 32-bit multiply and   | d accumulation unit                                      |  |  |  |

|                                             | 32-bit ÷ 32-bit divider                 |                                                          |  |  |  |

| Reset                                       |                                         |                                                          |  |  |  |

| #RESET pin                                  | Reset when the reset pin is set to le   | OW.                                                      |  |  |  |

| Power-on reset                              | Reset at power on.                      |                                                          |  |  |  |

| Brownout reset                              | Reset when the power supply volta       | age drops.                                               |  |  |  |

| Key entry reset                             |                                         | 03 keys are pressed simultaneously (can be enabled/      |  |  |  |

| ,,                                          | disabled using a register).             |                                                          |  |  |  |

| Watchdog timer reset                        | · · · · · · · · · · · · · · · · · · ·   | rerflows (can be enabled/disabled using a register).     |  |  |  |

| Supply voltage detector reset               |                                         | ector detects the set voltage level (can be enabled/dis- |  |  |  |

| 1 2 4 4 5 5 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 | abled using a register).                |                                                          |  |  |  |

| Interrupt                                   | , , , , , , , , , , , , , , , , , , ,   |                                                          |  |  |  |

| Non-maskable interrupt                      | 4 systems (Reset, address misalign      | ned interrupt, debug, NMI)                               |  |  |  |

| Programmable interrupt                      | External interrupt: 1 system (8 leve    | , ,                                                      |  |  |  |

|                                             | Internal interrupt: 14 systems (8 le    |                                                          |  |  |  |

| Power supply voltage                        |                                         | ,                                                        |  |  |  |

| V <sub>DD</sub> operating voltage           | 1.8 to 5.5 V                            |                                                          |  |  |  |

| VDD operating voltage for Flash programi    |                                         | ower supply is required.)                                |  |  |  |

| Operating temperature                       | 5, 10 12 112 1 (11. 7.10 1 0.00) mar pr |                                                          |  |  |  |

| Operating temperature range                 | -40 to 85 °C                            |                                                          |  |  |  |

| Current consumption (Typ. value)            | 1 .0 .0 00                              |                                                          |  |  |  |

| SLEEP mode                                  | 0.5 μA (TBD)                            |                                                          |  |  |  |

| OLLE MOGE                                   | IOSC = OFF, OSC3 = OFF                  |                                                          |  |  |  |

| HALT mode                                   | 180 µA (TBD)                            |                                                          |  |  |  |

| TO LET THOUS                                | OSC3 = 4 MHz (internal oscillator)      |                                                          |  |  |  |

| RUN mode                                    | 600 μA (TBD)                            |                                                          |  |  |  |

| Tion Tillouc                                | OSC3 = 4 MHz (internal oscillator),     | CPU = OSC3 (1 wait cycle)                                |  |  |  |

|                                             | 1,700 µA (TBD)                          | or o = 5000 (1 wait byolo)                               |  |  |  |

|                                             | OSC3 = 16 MHz (internal oscillator)     | ), CPU = OSC3 (2 wait cycles)                            |  |  |  |

| Shipping form                               | 10000 - 10 Mil iz (internal oscillator) | ,, c. c – 6000 (2 wait byolos)                           |  |  |  |

| 1                                           | TQFP12-48pin (Lead pitch: 0.5 mm        | n)                                                       |  |  |  |

| <u>'</u>                                    | practice topin (Leau pilon, 0.3 illin   | 'y                                                       |  |  |  |

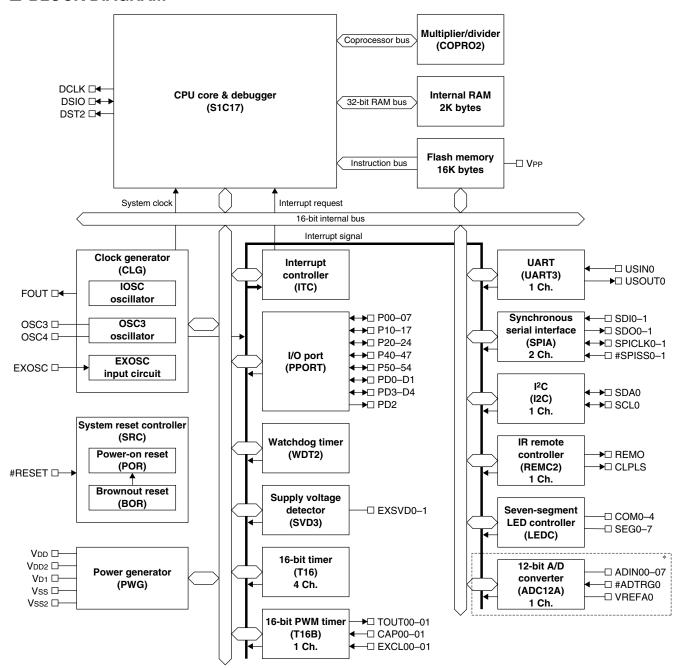

### **■ BLOCK DIAGRAM**

\* Not available in the S1C17M12.

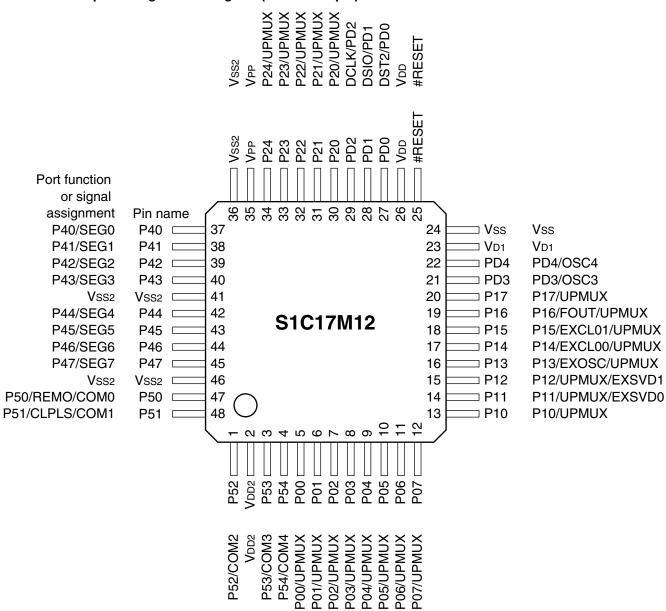

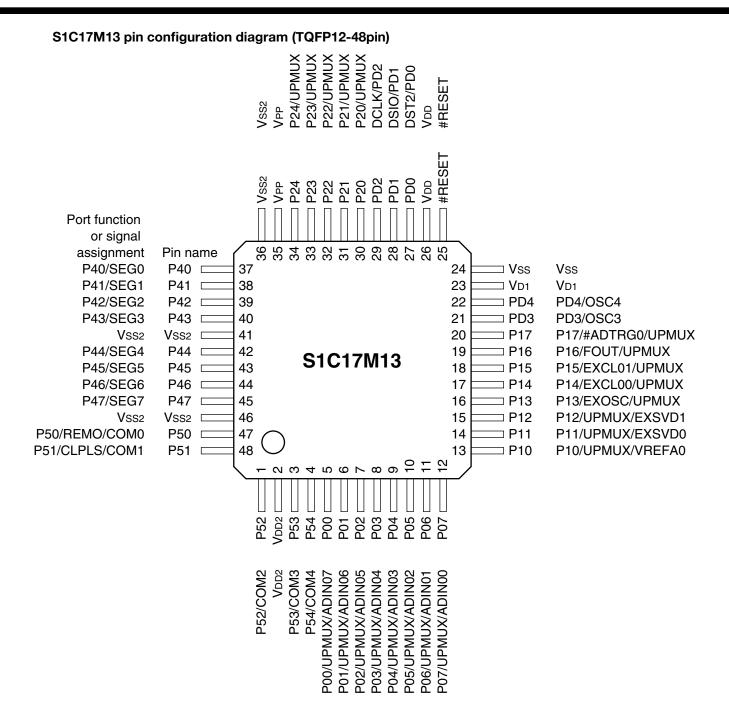

### **■ PIN CONFIGURATION DIAGRAMS**

S1C17M12 pin configuration diagram (TQFP12-48pin)

### **■ PIN DESCRIPTIONS**

#### Symbol meanings

Assigned signal: The signal listed at the top of each pin is assigned in the initial state. The pin function must be

switched via software to assign another signal (see the "I/O Ports" chapter).

I/O: I = Input

O = Output

I/O = Input/output

P = Power supply

A = Analog signal

Hi-Z = High impedance state

Initial state: I (Pull-up) = Input with pulled up

I (Pull-down) = Input with pulled down

Hi-Z = High impedance state

O (H) = High level output

O (L) = Low level output

Tolerant fail-safe structure:

= Over voltage tolerant fail-safe type I/O cell included (see the "I/O Ports" chapter)

The over voltage tolerant fail-safe type I/O cell allows interfacing without passing unnecessary current even if a voltage exceeding V<sub>DD</sub> is applied to the port. Also unnecessary current is not consumed when the port is externally biased without supplying V<sub>DD</sub>.

| Pin/pad<br>name  | Assigned signal  | I/O | Initial<br>state | Tolerant<br>fail-safe<br>structure | Function                                               | S1C17M12 | 111111        | S1C17M13 |

|------------------|------------------|-----|------------------|------------------------------------|--------------------------------------------------------|----------|---------------|----------|

| V <sub>DD</sub>  | V <sub>DD</sub>  | Р   | _                | _                                  | Power supply (+), I/O power supply (except for P50–54) | 1        | 7             | 7        |

| V <sub>DD2</sub> | V <sub>DD2</sub> | Р   | _                | _                                  | I/O power supply (P50–54)                              | 1        | 7             | /        |

| Vss              | Vss              | Р   | _                | _                                  | GND (except for P40–47, P50–54)                        | 1        | 7             | /        |

| Vss2             | Vss2             | Р   | _                | _                                  | GND (P40-47, P50-54)                                   | /        | 7             | /        |

| VPP              | VPP              | Р   | _                | _                                  | Power supply for Flash programming                     | /        | 7             | /        |

| V <sub>D1</sub>  | V <sub>D1</sub>  | Α   | _                | _                                  | V <sub>D1</sub> regulator output                       | /        | 7             | /        |

| #RESET           | #RESET           | ī   | I (Pull-up)      | _                                  | Reset input                                            | /        | $\rightarrow$ | _        |

| P00              | P00              | 1/0 | Hi-Z             | _                                  | I/O port                                               | /        | $\rightarrow$ | /        |

|                  | UPMUX            | 1/0 |                  |                                    | User-selected I/O (universal port multiplexer)         | /        | -             | /        |

|                  | ADIN07           | A   | -                |                                    | 12-bit A/D converter Ch.0 analog signal input 7        |          | -             | /        |

| P01              | P01              | 1/0 | Hi-Z             | _                                  | I/O port                                               |          | +             | <u>'</u> |

| 101              | UPMUX            | 1/0 |                  |                                    | User-selected I/O (universal port multiplexer)         |          | $\rightarrow$ | <u>/</u> |

|                  | ADIN06           | Α   | -                |                                    | 12-bit A/D converter Ch.0 analog signal input 6        |          | -             | /        |

| P02              | P02              | 1/0 | Hi-Z             |                                    | I/O port                                               |          | $\rightarrow$ | <u>/</u> |

| FU2              | UPMUX            | 1/0 | ⊓1-∠             | _                                  | User-selected I/O (universal port multiplexer)         | <i>'</i> | -             | ✓<br>✓   |

|                  | ADIN05           | A   |                  |                                    |                                                        |          | +             | ✓<br>✓   |

| Doo              |                  |     | 11: 7            |                                    | 12-bit A/D converter Ch.0 analog signal input 5        | -        | _             | •        |

| P03              | P03              | 1/0 | Hi-Z             | _                                  | I/O port                                               | <b>✓</b> | -             | <u>/</u> |

|                  | UPMUX            | 1/0 |                  |                                    | User-selected I/O (universal port multiplexer)         |          | $\rightarrow$ | <u>/</u> |

| <b></b>          | ADIN04           | A   |                  |                                    | 12-bit A/D converter Ch.0 analog signal input 4        | -        | +             | <u>/</u> |

| P04              | P04              | 1/0 | Hi-Z             | _                                  | I/O port                                               | <b>✓</b> | -             | /        |

|                  | UPMUX            | I/O |                  |                                    | User-selected I/O (universal port multiplexer)         | <b>✓</b> | +             | ✓        |

|                  | ADIN03           | Α   |                  |                                    | 12-bit A/D converter Ch.0 analog signal input 3        | -        | +             | ✓        |

| P05              | P05              | I/O | Hi-Z             | _                                  | I/O port                                               | <b>✓</b> | +             | /        |

|                  | UPMUX            | I/O |                  |                                    | User-selected I/O (universal port multiplexer)         | <b>✓</b> | $\rightarrow$ | ✓        |

|                  | ADIN02           | Α   |                  |                                    | 12-bit A/D converter Ch.0 analog signal input 2        | -        | -             | /        |

| P06              | P06              | I/O | Hi-Z             | _                                  | I/O port                                               | ✓        | 1             | <b>✓</b> |

|                  | UPMUX            | I/O |                  |                                    | User-selected I/O (universal port multiplexer)         | <b>✓</b> |               | /        |

|                  | ADIN01           | Α   |                  |                                    | 12-bit A/D converter Ch.0 analog signal input 1        |          | -             | /        |

| P07              | P07              | I/O | Hi-Z             | _                                  | I/O port                                               | 1        |               | /        |

|                  | UPMUX            | I/O | ]                |                                    | User-selected I/O (universal port multiplexer)         | 1        | 7             | /        |

|                  | ADIN00           | Α   |                  |                                    | 12-bit A/D converter Ch.0 analog signal input 0        | -        | -T            | /        |

| P10              | P10              | I/O | Hi-Z             | _                                  | I/O port                                               | 1        | 7             | /        |

|                  | UPMUX            | I/O | 1                |                                    | User-selected I/O (universal port multiplexer)         | 1        | 7             | /        |

|                  | VREFA0           | Α   | 1                |                                    | 12-bit A/D converter Ch.0 reference voltage input      | -        | -             | /        |

| P11              | P11              | I/O | Hi-Z             | _                                  | I/O port                                               | 1        | 7             | /        |

|                  | UPMUX            | 1/0 | _                |                                    | User-selected I/O (universal port multiplexer)         | /        | +             | /        |

|                  | EXSVD0           | A   | 1                |                                    | External power supply voltage detection input Ch.0     | 1/       | +             | 7        |

| Pin/pad<br>name | Assigned signal | I/O | Initial<br>state | Tolerant<br>fail-safe<br>structure | Function                                       |                       | S1C17M12 | S1C17M13 |

|-----------------|-----------------|-----|------------------|------------------------------------|------------------------------------------------|-----------------------|----------|----------|

| P12             | P12             | 1/0 | Hi-Z             | _                                  | I/O port                                       |                       | 1        | +        |

| 1 12            | UPMUX           | 1/0 | 2                |                                    | User-selected I/O (universal port multiplexer) |                       | 1        | 1        |

|                 | EXSVD1          | A   |                  |                                    | External power supply voltage detection input  | Ch.1                  | 1        | 1        |

| P13             | P13             | I/O | Hi-Z             | _                                  | I/O port                                       |                       | 1        | 1        |

|                 | EXOSC           | ı   |                  |                                    | Clock generator external clock input           |                       | 1        | 1        |

|                 | UPMUX           | 1/0 | 1                |                                    | User-selected I/O (universal port multiplexer) |                       | 1        | 1        |

| P14             | P14             | 1/0 | Hi-Z             | _                                  | I/O port                                       |                       | 1        | 1        |

|                 | EXCL00          | ı   | ĺ                |                                    | 16-bit PWM timer Ch.0 event counter input 0    |                       | 1        | 1        |

|                 | UPMUX           | I/O |                  |                                    | User-selected I/O (universal port multiplexer) |                       | 1        | 1        |

| P15             | P15             | I/O | Hi-Z             | _                                  | I/O port                                       |                       | 1        | 1        |

|                 | EXCL01          | I   |                  |                                    | 16-bit PWM timer Ch.0 event counter input 1    |                       | 1        | 1        |

|                 | UPMUX           | I/O |                  |                                    | User-selected I/O (universal port multiplexer) |                       | 1        | 1        |

| P16             | P16             | I/O | Hi-Z             | _                                  | I/O port                                       |                       | 1        | 1        |

|                 | FOUT            | 0   | ]                |                                    | Clock external output                          |                       | 1        | 1        |

|                 | UPMUX           | I/O | ]                |                                    | User-selected I/O (universal port multiplexer) |                       | 1        | 1        |

| P17             | P17             | I/O | Hi-Z             | _                                  | I/O port                                       |                       | 1        | 1        |

|                 | #ADTRG0         | ı   | ]                |                                    | 12-bit A/D converter Ch.0 trigger input        |                       | -        | 1        |

|                 | UPMUX           | I/O |                  |                                    | User-selected I/O (universal port multiplexer) |                       | 1        | 1        |

| P20             | P20             | I/O | Hi-Z             | -                                  | I/O port                                       |                       | 1        | 1        |

|                 | UPMUX           | I/O |                  |                                    | User-selected I/O (universal port multiplexer) |                       | 1        | 1        |

| P21             | P21             | I/O | Hi-Z             | _                                  | I/O port                                       |                       | 1        | 1        |

|                 | UPMUX           | I/O |                  |                                    | User-selected I/O (universal port multiplexer) |                       | 1        | 1        |

| P22             | P22             | I/O | Hi-Z             | _                                  | I/O port                                       |                       | 1        | 1        |

|                 | UPMUX           | I/O | ]                |                                    | User-selected I/O (universal port multiplexer) |                       | 1        | 1        |

| P23             | P23             | I/O | Hi-Z             | _                                  | I/O port                                       |                       | 1        | 1        |

|                 | UPMUX           | I/O |                  |                                    | User-selected I/O (universal port multiplexer) |                       | 1        | 1        |

| P24             | P24             | I/O | Hi-Z             | _                                  | I/O port                                       |                       | 1        | 1        |

|                 | UPMUX           | I/O |                  |                                    | User-selected I/O (universal port multiplexer) |                       | 1        | 1        |

| P40             | P40             | I/O | Hi-Z             | -                                  | I/O port                                       | High drive-capability | 1        | 1        |

|                 | SEG0            | 0   |                  |                                    | LED segment output                             | Nch output            | 1        | 1        |

| P41             | P41             | I/O | Hi-Z             | _                                  | I/O port                                       | High drive-capability | 1        | 1        |

|                 | SEG1            | 0   |                  |                                    | LED segment output                             | Nch output            | 1        | 1        |

| P42             | P42             | I/O | Hi-Z             | _                                  | I/O port                                       | High drive-capability | 1        | 1        |

|                 | SEG2            | 0   |                  |                                    | LED segment output                             | Nch output            | 1        | 1        |

| P43             | P43             | I/O | Hi-Z             | _                                  | I/O port                                       | High drive-capability | 1        | 1        |

|                 | SEG3            | 0   |                  |                                    | LED segment output                             | Nch output            | 1        | 1        |

| P44             | P44             | I/O | Hi-Z             | _                                  | I/O port                                       | High drive-capability | 1        | 1        |

|                 | SEG4            | 0   |                  |                                    | LED segment output                             | Nch output            | 1        | 1        |

| P45             | P45             | I/O | Hi-Z             | _                                  | I/O port                                       | High drive-capability | 1        | 1        |

|                 | SEG5            | 0   |                  |                                    | LED segment output                             | Nch output            | 1        | 1        |

| P46             | P46             | I/O | Hi-Z             | _                                  | I/O port                                       | High drive-capability | 1        |          |

|                 | SEG6            | 0   |                  |                                    | LED segment output                             | Nch output            | 1        | 1        |

| P47             | P47             | I/O | Hi-Z             | _                                  | I/O port                                       | High drive-capability | 1        | _        |

|                 | SEG7            | 0   |                  |                                    | LED segment output                             | Nch output            | 1        | _        |

| P50             | P50             | I/O | Hi-Z             | -                                  | I/O port                                       | High drive-capability | 1        | 1        |

|                 | REMO            | 0   |                  |                                    | IR remote controller transmit data output      | Pch output            | 1        | +        |

|                 | COM0            | 0   |                  |                                    | LED common output                              |                       | 1        | 1        |

| P51             | P50             | I/O | Hi-Z             | _                                  | I/O port                                       | High drive-capability | 1        | 1        |

|                 | CLPLS           | 0   |                  |                                    | IR remote controller clear pulse output        | Pch output            | 1        | 1        |

|                 | COM1            | 0   |                  |                                    | LED common output                              |                       | 1        | +        |

| P52             | P50             | I/O | Hi-Z             | _                                  | I/O port                                       | High drive-capability | 1        | 1        |

|                 | COM2            | 0   |                  |                                    | LED common output                              | Pch output            | 1        | 1        |

| P53             | P50             | I/O | Hi-Z             | _                                  | I/O port                                       | High drive-capability | 1        | _        |

|                 | СОМЗ            | 0   |                  |                                    | LED common output                              | Pch output            | 1        | 1        |

| P54             | P50             | I/O | Hi-Z             | _                                  | I/O port                                       | High drive-capability | 1        | 1        |

|                 | COM4            | 0   |                  |                                    | LED common output                              | Pch output            | 1        | 1        |

| PD0             | DST2            | 0   | O (L)            | _                                  | On-chip debugger status output                 |                       | 1        | 1        |

|                 | PD0             | I/O |                  |                                    | I/O port                                       |                       | 1        | +        |

| PD1             | DSIO            | I/O | I (Pull-up)      | -                                  | On-chip debugger data input/output             |                       | 1        | -        |

|                 | PD1             | I/O |                  |                                    | I/O port                                       |                       | 1        | 1        |

| PD2             | DCLK            | 0   | O (H)            | _                                  | On-chip debugger clock output                  |                       | 1        | 1        |

|                 | PD2             | 0   |                  |                                    | Output port                                    |                       | 1        | 1        |

| Pin/pad<br>name | Assigned signal | I/O | Initial<br>state | Tolerant<br>fail-safe<br>structure | Function                       | M<br>M |   | S1C17M13 |

|-----------------|-----------------|-----|------------------|------------------------------------|--------------------------------|--------|---|----------|

| PD3             | PD3             | I/O | Hi-Z             | -                                  | I/O port                       | 1      | 1 | 7        |

|                 | OSC3            | Α   |                  |                                    | OSC3 oscillator circuit input  | 1      | 1 | /        |

| PD4             | PD4             | I/O | Hi-Z             | -                                  | I/O port                       | 1      | 1 | /        |

|                 | OSC4            | Α   |                  |                                    | OSC3 oscillator circuit output | 1      | 7 | /        |

### **Universal port multiplexer (UPMUX)**

The universal port multiplexer (UPMUX) allows software to select the peripheral circuit input/output function to be assigned to each pin from those listed below. Note, however, that a function cannot be assigned to two or more pins simultaneously.

| Peripheral circuit           | Signal to be assigned | I/O | Channel number n | Function                             |

|------------------------------|-----------------------|-----|------------------|--------------------------------------|

| Synchronous serial interface | SDI <i>n</i>          |     | n = 0, 1         | SPIA Ch.n data input                 |

| (SPIA)                       | SDOn                  | 0   |                  | SPIA Ch.n data output                |

|                              | SPICLKn               | I/O |                  | SPIA Ch.n clock input/output         |

|                              | #SPISSn               | - 1 |                  | SPIA Ch.n slave-select input         |

| I <sup>2</sup> C             | SCLn                  | 1/0 | n = 0            | I2C Ch.n clock input/output          |

| (I2C)                        | SDAn                  | I/O |                  | I2C Ch.n data input/output           |

| UART                         | USINn                 | - 1 | n = 0            | UART3 Ch.n data input                |

| (UART3)                      | USOUTn                | 0   |                  | UART3 Ch.n data output               |

| 16-bit PWM timer             | TOUTn0/CAPn0          | I/O | n = 0            | T16B Ch.n PWM output/capture input 0 |

| (T16B)                       | TOUTn1/CAPn1          | I/O |                  | T16B Ch.n PWM output/capture input 1 |

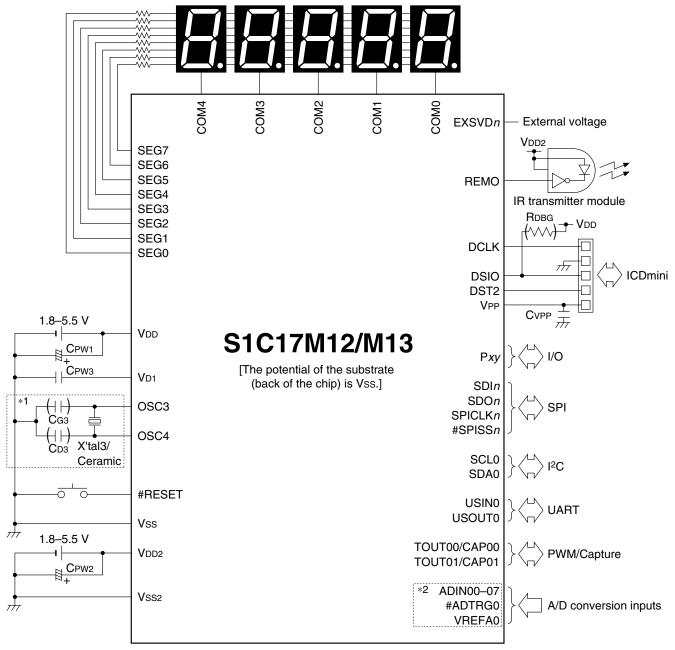

### **■** Basic External Connection Diagram

- \*1:When OSC3 crystal/ceramic oscillator is selected

- \*2:Available only in the S1C17M13

- ( ): Do not mount components if unnecessary.

#### Sample external components

| Symbol           | Name                                   | Recommended components                                         |  |  |

|------------------|----------------------------------------|----------------------------------------------------------------|--|--|

| X'tal3           | Crystal resonator                      | CA-301 (4 MHz) manufactured by Seiko Epson Corporation         |  |  |

| Ceramic          | Ceramic resonator                      | CSBLA_J (1 MHz) manufactured by Murata Manufacturing Co., Ltd. |  |  |

| Cgз              | OSC3 gate capacitor                    | Ceramic capacitor                                              |  |  |

| Срз              | OSC3 drain capacitor                   | Ceramic capacitor                                              |  |  |

| C <sub>PW1</sub> | Bypass capacitor between Vss and VDD   | Ceramic capacitor or electrolytic capacitor                    |  |  |

| CPW2             | Bypass capacitor between Vss2 and VDD2 | Ceramic capacitor or electrolytic capacitor                    |  |  |

| Срwз             | Capacitor between Vss and VD1          | Ceramic capacitor                                              |  |  |

| Rdbg             | DSIO pull-up resistor                  | Thick film chip resistor                                       |  |  |

| Сурр             | Capacitor between Vss and VPP          | Ceramic capacitor                                              |  |  |

### NOTICE:

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. When exporting the products or technology described in this material, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You are requested not to use, to resell, to export and/or to otherwise dispose of the products (and any technical information furnished, if any) for the development and/or manufacture of weapon of mass destruction or for other military purposes.

All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies. ©Seiko Epson Corporation 2016, All rights reserved

#### **SEIKO EPSON CORPORATION**

MICRODEVICES OPERATIONS DIVISION

EPSON semiconductor website

http://global.epson.com/products/semicon/

**Device Sales & Marketing Department**421-8 Hino, Hino-shi, Tokyo 191-8501, JAPAN

Phone: +81-42-587-5816 FAX: +81-42-587-5117

Document Code: 413284400 Issue June 2016 in JAPAN ©

### **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

### Epson:

\$1C17M12F101100 \$1C17M13F101100 \$1C17M12F101100-250 \$1C17M13F101100-250