## 512M (32M x16 bit) Mobile DDR SDRAM

Confidential

(Rev. 2.0, Feb. /2014)

# LPDDR MEMORY

512M (32Mx16bit) Mobile DDR SDRAM

# 512M (32M x16 bit) Mobile DDR SDRAM

### Confidential

## (Rev. 2.0, Feb. /2014)

#### **Revision History**

| <b>Revision No</b> | Description                                                                     | Date       |

|--------------------|---------------------------------------------------------------------------------|------------|

| 1.0                | Initial Release                                                                 | 2014/02/04 |

| 2.0                | Clock frequency to 200MHz - data rate: 400Mbps - 5ns access speed option update | 2014/02/17 |

# AS4C32M16MD1

## 512M (32M x16 bit) Mobile DDR SDRAM

#### Confidential

(Rev. 2.0, Feb. /2014)

## **1. FEATURES**

- Density : 512Mbit

- Organization

- x16 bit : 8M words x 16bits x 4banks

- Power supply : VDD, VDDQ = 1.7 to 1.95V

- Speed

- Clock frequency : 200MHz (max.)

- Data rate : 400Mbps (max.)

- 2KB page size

- Row address : A0 to A12

- Column address : A0 to A9 (x16 bits)

- Four internal banks for concurrent operation

- Interface : LVCMOS

- Burst lengths (BL) : 2, 4, 8, 16

- Burst type (BT)

- Sequential : 2, 4, 8, 16

- Interleave : 2, 4, 8, 16

- CAS# latency (CL) : 3

- **Precharge :** auto precharge option for each burst access

- Driver strength : normal, 1/2, 1/4, 1/8

- Refresh : auto-refresh, self-refresh

- Refresh cycles : 8192 cycles/64ms - Average refresh period : 7.8us

- Operating junction temperature range

- Tj= -30°C to +85°C

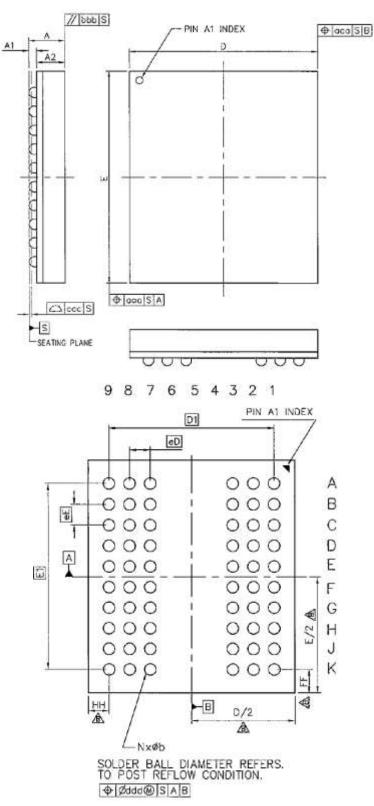

- Package: 60-ball FBGA (8x9mm)

- All parts are ROHS Compliant

- Low power consumption

- Partial Array Self-Refresh (PASR)

- Auto Temperature Compensated Self-Refresh (ATCSR) by built-in temperature sensor

- Deep power down mode

- Burst termination by burst stop command and precharge command

- DDL is not implemented

- Double-data-rate architecture : Two data transfers per one clock cycle

- The high speed data transfer is realized by the 2bits prefetch pipelined architecture

- Bi-directional data strobe (DQS) is transmitted/ received with data for capturing data at the receiver

- DQS is edge-aligned with data for READs; center-aligned with data for WRITEs

- Differential clock inputs (CK and CK#)

- Commands entered on each positive CK edge; data and data mask referenced to both edges of DQS

- Data mask (DM) for write data

## 2. GENERAL DESCRIPTION

This device is 536,870,912 bits of double data rate synchronous DRAM organized as 4 banks of 8,388,608 words by 16 bits. The synchronous operation with Data Strobe allows extremely high performance. JSC is applied to reduce leakage and refresh currents while achieving very high speed. I/O transactions are possible on both edges of the clock. The ranges of operating frequencies, programmable burst length and programmable latencies allow the device to be useful for a variety of high performance memory system applications.

#### Table 1. Speed Grade Information

| Speed Grade – Data rate | <b>Clock Frequency</b> | CAS Latency | t <sub>RCD</sub> (ns) | t <sub>RP</sub> (ns) |

|-------------------------|------------------------|-------------|-----------------------|----------------------|

| 400Mbps (max)           | 200 MHz (max)          | 3           | 15                    | 15                   |

#### Table 2 – Ordering Information for ROHS Compliant Products

| Product part No   | Org     | Temperature   | Max Clock (MHz) | Package      |

|-------------------|---------|---------------|-----------------|--------------|

| AS4C32M16MD1-5BCN | 32 x 16 | -30°C to 85°C | 200             | 60-ball FBGA |

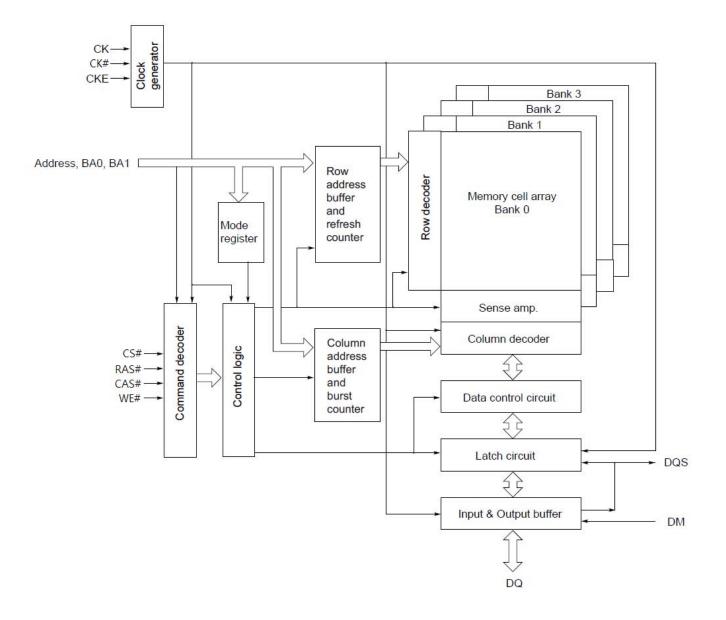

## 2.1 Block Diagram

#### Figure 2.1 Block Diagram

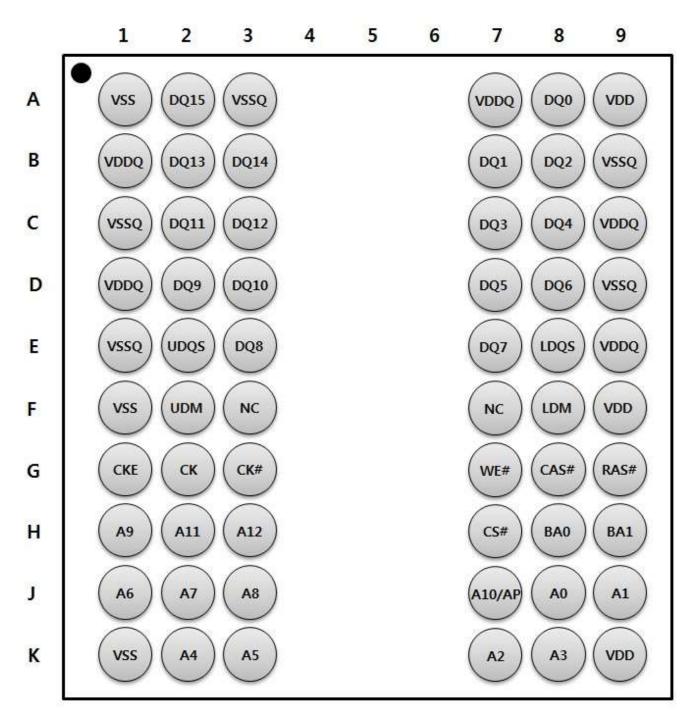

## 2.2 Package Pin Configurations

#### Figure 2.2 Pin configurations

## 2.4 Pin Description

#### CK, CK# (input pins)

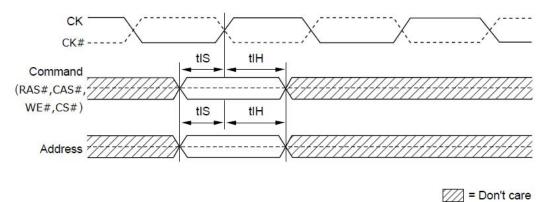

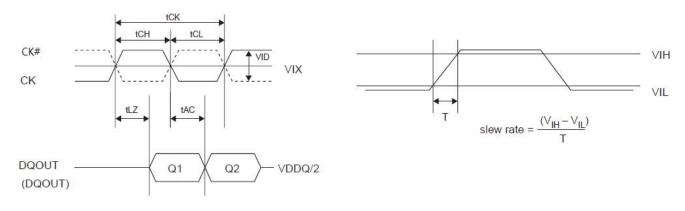

The CK and the CK# are the master clock inputs. All inputs except DMs, DQSs and DQs are referred to the cross point of the CK rising edge and the CK# falling edge. When a read operation, DQSs and DQs are referred to the cross point of the CK and the CK#. When a write operation, DMs and DQs are referred to the cross point of the DQS and the VDDQ/2 level. DQSs for write operation are referred to the cross point of the CK and the CK#. The other input signals are referred at CK rising edge.

#### CS# (input pin)

When CS# is low, commands and data can be input. When CS# is high, all inputs are ignored. However, internal operations (bank active, burst operations, etc.) are held.

#### RAS#, CAS#, and WE# (input pins)

These pins define operating commands (read, write, etc.) depending on the combinations of their voltage levels. See "Command operation".

#### A0 to A12 (input pins)

Row address (AX0 to AX12) is determined by the A0 to the A12 level at the cross point of the CK rising edge and the CK# falling edge in a bank active command cycle. Column address is loaded at the cross point of the CK rising edge and the CK# falling edge in a read or a write command cycle (See Table 2.1). This column address becomes the starting address of a burst operation.

#### Table 2.1 Address Pins

|           | Organization | Address ( A0 to A12 ) |                |  |  |  |

|-----------|--------------|-----------------------|----------------|--|--|--|

| Page size | Organization | Row address           | Column address |  |  |  |

| 2КВ       | x16 bits     | AX0 to AX12           | AYO to AY9     |  |  |  |

#### A10 (AP) (input pin)

A10 defines the precharge mode when a precharge command, a read command or a write command is issued. If A10 = high when a precharge command is issued, all banks are pre-charged. If A10 = low when a precharge command is issued, only the bank that is selected by BA1/BA0 is pre-charged. If A10 = high when read or write command, auto precharge function is enabled.

#### BA0 and BA1 (input pins)

BAO and BA1 are bank select signals (BA). The memory array is divided into bank 0, bank 1, bank 2 and bank 3. (See Table 2.2)

#### Table 2.2 Bank Select Signal

|        | BAO | BA1 |

|--------|-----|-----|

| Bank 0 | L   | L   |

| Bank 1 | Н   | L   |

| Bank 2 | L   | Н   |

| Bank 3 | Н   | Н   |

Note : H = VIH , L = VIL

#### CKE (input pin)

CKE controls power-down mode, self-refresh function and deep power-down function with other command inputs. The CKE level must be kept for 2 clocks at least, that is, if CKE changes at the cross point of the CK rising edge and the CK# falling edge with proper setup time tIS, by the next CK rising edge CKE level must be kept with proper hold time tIH.

#### DQ0 to DQ15 (input/output pins)

Data are input to and output from these pins.

#### UDQS and LDQS (input and output pin)

DQS provides the read data strobes (as output) and the write data strobes (as input). Each DQS pin corresponds to eight DQ pins, respectively (See Table 2.3).

#### UDM and LDM (input pin)

DM is the reference signals of the data input mask function. DM is sampled at the cross point of DQS and VDDQ/2. When DM = high, the data input at the same timing are masked while the internal burst counter will be counting up. Each DM pin corresponds to eight DQ pins, respectively (See Table 2.3).

#### Table 2.3 DQS and DM Correspondence

| Organization | DQS  | Data mask | DQs         |

|--------------|------|-----------|-------------|

|              | LDQS | LDM       | DQ0 to DQ7  |

| x16 bits     | UDQS | UDM       | DQ8 to DQ15 |

#### VDD, VSS, VDDQ, VSSQ (Power supply)

VDD and VSS are power supply pins for internal circuits. VDDQ and VSSQ are power supply pins for the output buffers. VDD must be equal to VDDQ.

## **3. Command Operation**

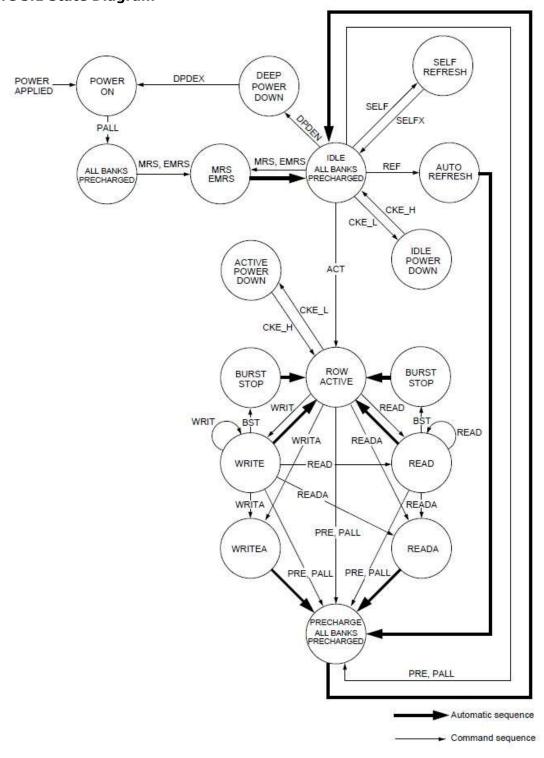

#### 3.1 Simplified State Diagram Figure 3.1 State Diagram

## **3.2 Command Truth Table**

The DDR Mobile RAM recognizes the following commands specified by the CS#, RAS#, CAS#, WE# and address pins.

| Command                            | Symbol | Cł<br>n-1 | KE<br>n | CS# | RAS# | CAS# | WE# | BA1 | BA0 | АР | Addr. |

|------------------------------------|--------|-----------|---------|-----|------|------|-----|-----|-----|----|-------|

| Ignore command                     | DESL   | Н         | н       | Н   | Х    | Х    | Х   | Х   | Х   | Х  | Х     |

| No operation                       | NOP    | Н         | Н       | L   | Н    | Н    | Н   | Х   | Х   | Х  | Х     |

| Burst stop command                 | BST    | Н         | Н       | L   | Н    | Н    | L   | Х   | Х   | Х  | Х     |

| Column address and read command    | READ   | Н         | Н       | L   | Н    | L    | Н   | V   | V   | L  | V     |

| Read with auto<br>precharge        | READA  | Н         | н       | L   | Н    | L    | Н   | V   | V   | Н  | V     |

| Column address and write command   | WRIT   | Н         | Н       | L   | Н    | L    | L   | V   | V   | L  | V     |

| Write with auto<br>precharge       | WRITA  | Н         | Н       | L   | Н    | L    | L   | V   | V   | Н  | V     |

| Row address strobe and bank active | ACT    | Н         | Н       | L   | L    | Н    | Н   | V   | V   | V  | V     |

| Precharge select bank              | PRE    | Н         | Н       | L   | L    | Н    | L   | V   | V   | L  | Х     |

| Precharge all bank                 | PALL   | Н         | Н       | L   | L    | Н    | L   | Х   | Х   | Н  | Х     |

| Refresh                            | REF    | Н         | Н       | L   | L    | L    | Н   | Х   | Х   | Х  | Х     |

| 1/211/2211                         | SELF   | Н         | L       | L   | L    | L    | Н   | Х   | Х   | Х  | Х     |

| Mode register set                  | MRS    | Н         | Н       | L   | L    | L    | L   | L   | L   | L  | V     |

| mode register set                  | EMRS   | Н         | Н       | L   | L    | L    | L   | Н   | L   | L  | V     |

### Table 3.1 Command Truth Table

Note :

- 1. H : VIH , L : VIL , X : Don't care , V : Valid address input

- 2. The CKE level must be kept for 1 CK cycle at least.

### Ignore command [DESL]

When CS# is high at the cross point of the CK rising edge and the CK# falling edge, all input signals are neglected and internal state is held.

#### No operation [NOP]

As long as this command is input at the cross point of the CK rising edge and the CK# falling edge, address and data input are neglected and internal state is held.

#### Burst stop command [BST]

This command stops a current burst operation.

#### Column address strobe and read command [READ]

This command starts a read operation. The start address of the burst read is determined by the column address (See Table 2.1) and the bank select address. After the completion of the read operation, all output buffers become high-Z.

#### Read with auto precharge [READA]

This command starts a read operation. After completion of the read operation, precharge is automatically executed.

#### Column address strobe and write command [WRIT]

This command starts a write operation. The start address of the burst write is determined by the column address (See Table 2.1) and the bank select address.

#### Write with auto precharge [WRITA]

This command starts a write operation. After completion of the write operation, precharge is automatically executed.

#### Row address strobe and bank activate [ACT]

This command activates the bank that is selected by BAO and BA1 (See Table 2.2) and determines the row address (See Table 2.1).

#### Precharge selected bank [PRE]

This command starts precharge operation for the bank selected by BAO and BA1. (See Table 2.2)

#### Precharge all banks [PALL]

This command starts a precharge operation for all banks.

#### Refresh [REF/SELF]

This command starts a refresh operation. There are two types of refresh operation, one is autorefresh, and another is self-refresh. For details, refer to the CKE truth table section.

#### Mode register set/Extended mode register set [MRS/EMRS]

The DDR Mobile RAM has the two mode registers, the mode register and the extended mode register, to define how it works. The both mode registers are set through the address pins in the mode register set cycle. For details, refer to "Mode register and extended mode register set"

11

## **3.3 Function Truth Table**

The following tables show the operations that are performed when each command is issued in each state of the DDR Mobile RAM.

| Table 3 | .2 Comman | d Truth Table |

|---------|-----------|---------------|

|         |           |               |

| Current state                           | CS# | RAS# | CAS# | WE# | Address   | Command    | Operation                                 |

|-----------------------------------------|-----|------|------|-----|-----------|------------|-------------------------------------------|

|                                         | н   | Х    | Х    | X   | Х         | DESL       | NOP                                       |

|                                         | L   | Н    | Н    | Н   | Х         | NOP        | NOP                                       |

|                                         | L   | Н    | Н    | L   | Х         | BST        | ILLEGAL*11                                |

| Due <b>* 1</b>                          | L   | Н    | L    | Н   | BA,CA,A10 | READ/READA | ILLEGAL*11                                |

| Pre-charging <sup>*1</sup>              | L   | Н    | L    | L   |           | WRIT/WRITA | ILLEGAL <sup>*11</sup>                    |

|                                         | L   | L    | Н    | Н   |           | ACT        | ILLEGAL*11                                |

|                                         | L   | L    | Н    | L   |           | PRE, PALL  | NOP                                       |

|                                         | L   | L    | L    | х   | Х         |            | ILLEGAL                                   |

|                                         | Н   | Х    | Х    | Х   | Х         | DESL       | NOP                                       |

|                                         | L   | Н    | Н    | Н   | Х         | NOP        | NOP                                       |

|                                         | L   | Н    | Н    | L   | Х         | BST        | NOP                                       |

|                                         | L   | Н    | L    | Н   | BA,CA,A10 | READ/READA | ILLEGAL <sup>*11</sup>                    |

| Idle*2                                  | L   | Н    | L    | L   | BA,CA,A10 | WRIT/WRITA | ILLEGAL*11                                |

|                                         | L   | L    | Н    | Н   | BA, RA    | ACT        | Activating                                |

|                                         | L   | L    | Н    | L   | BA, A10   | PRE, PALL  | NOP                                       |

|                                         | L   | L    | L    | н   | Х         | REF, SELF  | Refresh / Self-<br>refresh <sup>*12</sup> |

|                                         | L   | L    | L    | L   | MODE      | MRS        | Mode register set <b>*12</b>              |

|                                         | Н   | Х    | Х    | Х   | Х         | DESL       | NOP                                       |

|                                         | L   | Н    | Н    | Н   | Х         | NOP        | NOP                                       |

| Refresh<br>(auto refresh) <sup>*3</sup> | Н   | Н    | Н    | L   | Х         | BST        | ILLEGAL                                   |

| · · · · ·                               | L   | Н    | L    | х   | Х         |            | ILLEGAL                                   |

|                                         | L   | L    | Х    | Х   | Х         |            | ILLEGAL                                   |

| Current state        | CS# | RAS# | CAS# | WE# | Address   | Command    | Operation                                                   |

|----------------------|-----|------|------|-----|-----------|------------|-------------------------------------------------------------|

|                      | н   | Х    | Х    | Х   | Х         | DESL       | NOP                                                         |

|                      | L   | Н    | Н    | Н   | Х         | NOP        | NOP                                                         |

|                      | L   | Н    | Н    | L   | Х         | BST        | ILLEGAL <sup>*11</sup>                                      |

| <u> </u>             | L   | Н    | L    | Н   | BA,CA,A10 | READ/READA | ILLEGAL*11                                                  |

| Activating*4         | L   | Н    | L    | L   | BA,CA,A10 | WRIT/WRITA | ILLEGAL*11                                                  |

|                      | L   | L    | Н    | Н   | BA, RA    | ACT        | ILLEGAL*11                                                  |

|                      | L   | L    | Н    | L   | BA, A10   | PRE, PALL  | ILLEGAL*11                                                  |

|                      | L   | L    | L    | х   | Х         |            | ILLEGAL                                                     |

|                      | Н   | Х    | Х    | х   | Х         | DESL       | NOP                                                         |

|                      | L   | Н    | Н    | Н   | Х         | NOP        | NOP                                                         |

|                      | L   | Н    | Н    | L   | Х         | BST        | NOP                                                         |

| Active <sup>*5</sup> | L   | Н    | L    | Н   | BA,CA,A10 | READ/READA | Starting read operation                                     |

| Active -             | L   | Н    | L    | L   | BA,CA,A10 | WRIT/WRITA | Starting read operation                                     |

|                      | L   | L    | Н    | Н   | BA, RA    | ACT        | ILLEGAL*11                                                  |

|                      | L   | L    | Н    | L   | BA, A10   | PRE, PALL  | Pre-charge                                                  |

|                      | L   | L    | L    | Х   | Х         |            | ILLEGAL                                                     |

|                      | Н   | Х    | Х    | Х   | Х         | DESL       | NOP                                                         |

|                      | L   | Н    | Н    | Н   | Х         | NOP        | NOP                                                         |

|                      | L   | Н    | Н    | L   | Х         | BST        | Burst stop                                                  |

| Dood*6               | L   | Н    | L    | Н   | BA,CA,A10 | READ/READA | Interrupting burst<br>read operation to start<br>new read   |

| Read* <sup>6</sup>   | L   | Н    | L    | L   | BA,CA,A10 | WRIT/WRITA | ILLEGAL*13                                                  |

|                      | L   | L    | Н    | Н   | BA, RA    | ACT        | ILLEGAL*11                                                  |

|                      | L   | L    | Н    | L   | BA,A10    | PRE, PALL  | Interrupting burst<br>read operation to start<br>pre-charge |

|                      | L   | L    | L    | Х   | Х         |            | ILLEGAL                                                     |

| Current state                  | CS# | RAS# | CAS# | WE# | Address   | Command    | Operation                                                                |

|--------------------------------|-----|------|------|-----|-----------|------------|--------------------------------------------------------------------------|

|                                | Н   | Х    | Х    | Х   | Х         | DESL       | NOP                                                                      |

|                                | L   | Н    | Н    | Н   | Х         | NOP        | NOP                                                                      |

|                                | L   | Н    | Н    | L   | Х         | BST        | ILLEGAL                                                                  |

| Read with auto                 | L   | Н    | L    | Н   | BA,CA,A10 | READ/READA | ILLEGAL                                                                  |

| pre-charge*7                   | L   | Н    | L    | L   | BA,CA,A10 | WRIT/WRITA | ILLEGAL                                                                  |

|                                | L   | L    | Н    | Н   | BA, RA    | ACT        | ILLEGAL <sup>*11</sup>                                                   |

|                                | L   | L    | Н    | L   | BA, A10   | PRE, PALL  | ILLEGAL*11                                                               |

|                                | L   | L    | L    | Х   | Х         |            | ILLEGAL                                                                  |

|                                | Н   | Х    | Х    | Х   | Х         | DESL       | NOP                                                                      |

|                                | L   | Н    | Н    | Н   | Х         | NOP        | NOP                                                                      |

|                                | L   | Н    | Н    | L   | Х         | BST        | Burst stop                                                               |

|                                | L   | Н    | L    | Н   | BA,CA,A10 | READ/READA | Interrupting burst<br>write operation to<br>start read operation         |

| Write <sup>*8</sup>            | L   | Н    | L    | L   | BA,CA,A10 | WRIT/WRITA | Interrupting burst<br>write operation to<br>start new write<br>operation |

|                                | L   | L    | Н    | Н   | BA, RA    | ACT        | ILLEGAL <sup>*11</sup>                                                   |

|                                | L   | L    | Н    | L   | BA,A10    | PRE,PALL   | Interrupting write<br>operation to start pre-<br>charge                  |

|                                | L   | L    | L    | Х   | Х         |            | ILLEGAL                                                                  |

|                                | Н   | Х    | Х    | Х   | Х         | DESL       | NOP                                                                      |

|                                | L   | Н    | Н    | Н   | Х         | NOP        | NOP                                                                      |

|                                | L   | Н    | Н    | L   | Х         | BST        | ILLEGAL                                                                  |

|                                | L   | Н    | L    | Н   | BA,CA,A10 | READ/READA | Starting read operation                                                  |

| Write recovering <sup>*9</sup> | L   | н    | L    | L   | BA,CA,A10 | WRIT/WRITA | Starting new write operation                                             |

|                                | L   | L    | Н    | Н   | BA, RA    | ACT        | ILLEGAL <sup>*11</sup>                                                   |

|                                | L   | L    | Н    | L   | BA, A10   | PRE, PALL  | ILLEGAL <sup>*11</sup>                                                   |

|                                | L   | L    | L    | Х   | Х         |            | ILLEGAL                                                                  |

| Current state             | CS# | RAS# | CAS# | WE# | Address   | Command    | Operation  |

|---------------------------|-----|------|------|-----|-----------|------------|------------|

|                           | Н   | Х    | Х    | Х   | Х         | DESL       | NOP        |

|                           | L   | Н    | Н    | Н   | Х         | NOP        | NOP        |

|                           | L   | Н    | Н    | L   | Х         | BST        | ILLEGAL    |

| Write with auto           | L   | Н    | L    | Н   | BA,CA,A10 | READ/READA | ILLEGAL    |

| pre-charge <sup>*10</sup> | L   | Н    | L    | L   | BA,CA,A10 | WRIT/WRITA | ILLEGAL    |

|                           | L   | L    | Н    | Н   | BA, RA    | ACT        | ILLEGAL*11 |

|                           | L   | L    | Н    | L   | BA,A10    | PRE, PALL  | ILLEGAL*11 |

|                           | L   | L    | L    | Х   | Х         |            | ILLEGAL    |

Note :

- 1. The DDR Mobile RAM is in "Pre-charging" state for tRP after precharge command is issued.

- 2. The DDR Mobile RAM reaches "IDLE" state tRP after precharge command is issued.

- 3. The DDR Mobile RAM is in "Refresh" state for tRFC after auto-refresh command is issued.

- 4. The DDR Mobile RAM is in "Activating" state for tRCD after ACT command is issued.

- 5. The DDR Mobile RAM is in "Active" state after "Activating" is completed.

- 6. The DDR Mobile RAM is in "READ" state until burst data have been output and DQ output circuits are turned off.

- 7. The DDR Mobile RAM is in "READ with auto precharge" from READA command until burst data has been output and DQ output circuits are turned off.

- 8. The DDR Mobile RAM is in "WRITE" state from WRIT command to the last burst data are input.

- 9. The DDR Mobile RAM is in "Write recovering" for tWR after the last data are input.

- 10. The DDR Mobile RAM is in "Write with auto precharge" until tWR after the last data has been input.

- 11. This command may be issued for other banks, depending on the state of the banks.

- 12. Not bank-specific; requires that all banks are idle and no bursts are in progress.

- 13. Before executing a write command to stop the preceding burst read operation, BST command must be issued.

- 14. H : VIH , L : VIL , X : Don't care

## 3.4 CKE Truth Table

#### Table 3.3 CKE Truth Table

| Current            | 6                                | Cł  | (E | <b>66</b> <i>4</i> | <b>DAC</b> # | <b>616</b> # | <b>1</b> |         |      |

|--------------------|----------------------------------|-----|----|--------------------|--------------|--------------|----------|---------|------|

| state              | Command                          | n-1 | n  | CS#                | RAS#         | CAS#         | WE#      | Address | Note |

| Idle               | Auto refresh command<br>(REF)    | Н   | Н  | L                  | L            | L            | Н        | Х       | 2    |

| Idle               | Self refresh entry (SELF)        | Н   | L  | L                  | L            | L            | Н        | Х       | 2    |

| Active / Idle      | Power down entry (PDEN)          | Н   | L  | L                  | Н            | Н            | Н        | Х       |      |

| Active / Tule      | Fower down entry (FDEN)          | Н   | L  | Н                  | Х            | Х            | Х        | Х       |      |

| Idle               | Deep power down entry<br>(DPDEN) | Н   | L  | L                  | Н            | Н            | L        | Х       | 2    |

| Colfrofroob        | Colf refreeb out (CELEV)         |     |    | L                  | Н            | Н            | Н        | Х       |      |

| Self refresh       | Self refresh exit (SELFX)        | L   | Н  | Н                  | Х            | Х            | Х        | Х       |      |

| Power down         | Power down avit (PDEX)           | L   | Н  | L                  | Н            | н н н х      |          | Х       |      |

|                    | Power down exit (PDEX)           |     | Н  | Н                  | Х            | Х            | Х        | Х       |      |

| Deep<br>power down | Power down exit (DPDEX)          | L   | Н  | Х                  | Х            | Х            | Х        | Х       |      |

Note :

- 1. H: VIH, L: VIL, X: Don't care.

- 2. All the banks must be in IDLE and no bursts in progress before executing this command.

- 3. The CKE level must be kept for 1 CK cycle at least.

#### Auto-refresh command [REF]

This command executes auto-refresh. The bank and the ROW addresses to be refreshed are internally determined by the internal refresh controller. The output buffer becomes high-Z after auto-refresh start. Precharge has been completed automatically after the auto-refresh. The ACT or MRS command can be issued tRFC after the last auto-refresh command.

The average refresh interval is  $7.8\mu$ s. To allow for improved efficiency in scheduling, some flexibility in the absolute refresh interval is provided. A maximum of eight auto-refresh commands can be posted to the DDR Mobile RAM or the maximum absolute interval between any auto-refresh command and the next auto-refresh command is  $8 \times tREFI$ .

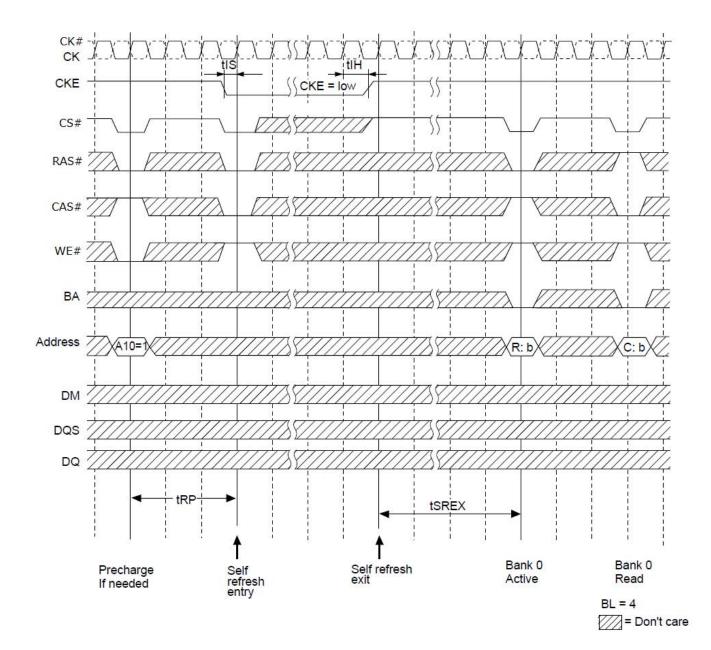

#### Self-refresh entry [SELF]

This command starts self-refresh. The self-refresh operation continues as long as CKE is held low. During the self-refresh operation, all ROW addresses are repeated refreshing by the internal refresh controller. A self-refresh is terminated by a self-refresh exit command.

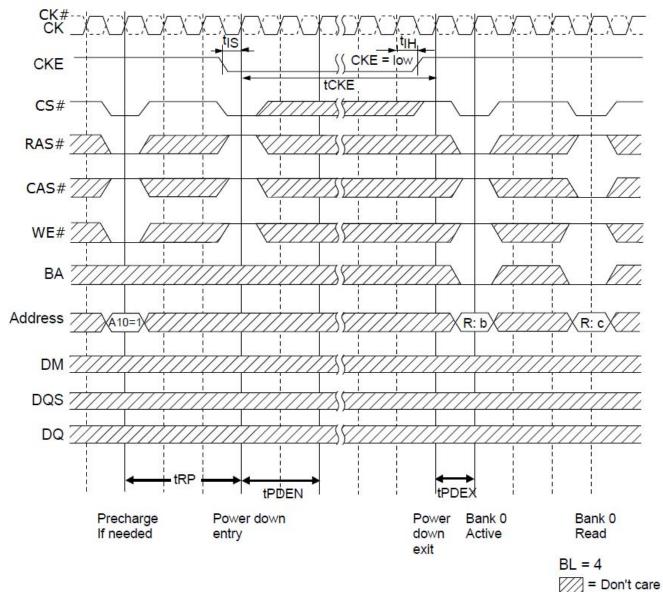

#### Power-down mode entry [PDEN]

tPDEN (= 2 clocks) after the cycle when [PDEN] is issued, the DDR Mobile RAM enters into powerdown mode. In power-down mode, power consumption is suppressed by deactivating the input initial circuit. Power-down mode continues while CKE is held low. No internal refresh operation occurs during the power-down mode.

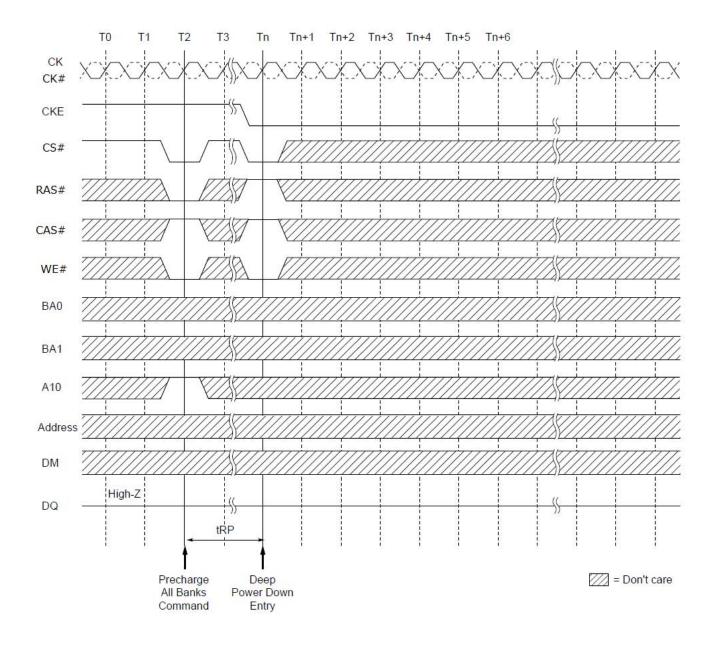

#### Deep power-down entry [DPDEN]

After the command execution, deep power-down mode continues while CKE remains low. Before executing deep power-down, all banks must be pre-charged or in idle state.

#### Self-refresh exit [SELFX]

This command is executed to exit from self-refresh mode. tSREX after [SELFX], the device will be into idle state.

#### Power-down exit [PDEX]

The DDR Mobile RAM can exit from power-down mode tPDEX (1 cycle min.) after the cycle when [PDEX] is issued.

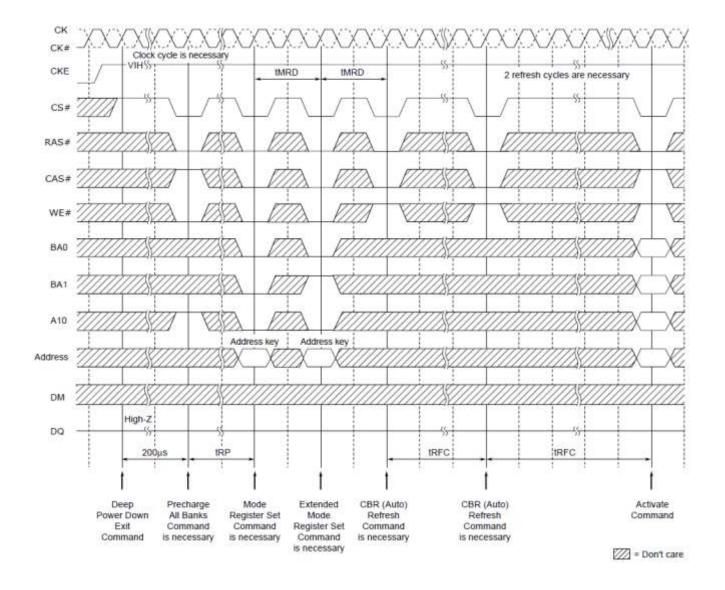

#### Deep power-down exit [DPDEX]

As CKE goes high in the deep power-down mode, the DDR Mobile RAM exit from the deep powerdown mode through deep power-down exiting sequence.

## 4. DEVICE OPERATION

## 4.1 Initialization

The DDR Mobile RAM is initialized in the power-on sequence according to the following.

- 1. Provide power, the device core power (VDD) and the device I/O power (VDDQ) must be brought up simultaneously to prevent device latch-up. Although not required, it is recommended that VDD and VDDQ are from the same power source. Also assert and hold Clock Enable (CKE) to a LV-CMOS logic high level.

- 2. Once the system has established consistent device power and CKE is driven high, it is safe to apply stable clock.

- 3. There must be at least **200µs** of valid clocks before any command may be given to the DRAM. During this time NOP or deselect (DESL) commands must be issued on the command bus.

- 4. Issue a precharge all command.

- 5. Provide NOPs or DESL commands for at least tRP time.

- 6. Issue an auto-refresh command followed by NOPs or DESL command for at least tRFC time. Issue the second auto-refresh command followed by NOPs or DESL command for at least tRFC time. Note as part of the initialization sequence there must be two auto-refresh commands issued. The typical flow is to issue them at Step 6, but they may also be issued between steps 10 and 11.

- 7. Using the MRS command, load the base mode register. Set the desired operating modes.

- 8. Provide NOPs or DESL commands for at least tMRD time.

- 9. Using the MRS command, program the extended mode register for the desired operating modes.

- 10. Provide NOP or DESL commands for at least tMRD time.

- 11. The DRAM has been properly initialized and is ready for any valid command.

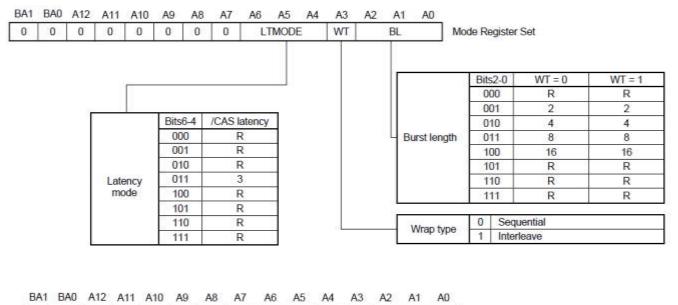

### 4.2 Mode Register and Extended Mode Register Set

There are two mode registers, the mode register and the extended mode register so as to define the operating mode. Parameters are set to both through the A0 to the A12 and BA0 and BA1 pins by the mode register set command [MRS] or the extended mode register set command [EMRS]. The mode register and the extended mode register are set by inputting signal via the A0 to the A12 and BA0 and BA1 pins during mode register set cycles.

BAO and BA1 determine which one of the mode register or the extended mode register are set. Prior to a read or a write operation, the mode register must be set.

#### 4.2.1 Mode Register

The mode register has four fields;

- Reserved : A12 through A7

- CAS latency : A6 through A4

- Wrap type : A3

- Burst length : A2 through A0

Following mode register programming, no command can be issued before at least 2 clocks have elapsed.

#### CAS# Latency

CAS# latency must be set to 3.

#### **Burst Length**

Burst Length is the number of words that will be output or input in a read or write cycle. After a read burst is completed, the output bus will become high-Z. The burst length is programmable as 2, 4, 8 and 16.

#### Wrap Type (Burst Sequence)

The wrap type specifies the order in which the burst data will be addressed. This order is programmable as either "Sequential" or "Interleave". "Burst Operation" shows the addressing sequence for each burst length for each wrap type.

#### 4.2.2 Extended Mode Register

The extended mode register has three fields;

| Reserved                   | : A12 through A7, A4, A3 |

|----------------------------|--------------------------|

| Driver Strength            | : A6 through A5          |

| Partial Array Self-Refresh | : A2 through A0          |

Following extended mode register programming, no command can be issued before at least 2 clocks have elapsed.

#### **Driver Strength**

By setting specific parameter on A6 and A5, driving capability of data output drivers is selected.

#### Auto Temperature Compensated Self-Refresh (ATCSR)

The DDR Mobile RAM automatically changes the self-refresh cycle by on die temperature sensor. No extended mode register program is required. Manual TCSR (Temperature Compensated Self-Refresh) is not implemented.

#### **Partial Array Self-Refresh**

Memory array size to be refreshed during self-refresh operation is programmable in order to reduce power. Data outside the defined area will not be retained during self-refresh.

### 4.3 Power Down & Deep Power Down

#### **4.3.1 Deep Power Down Exit Sequence**

In order to exit from the deep power-down mode and enter into the idle mode, the following sequence is needed, which is similar to the power-on sequence.

- 1. A 200µs or longer pause must precede any command other than ignore command (DESL).

- 2. After the pause, all banks must be pre-charged using the precharge command (the precharge all banks command is convenient).

- 3. Once the precharge is completed and the minimum tRP is satisfied, two or more Auto-refresh must be performed.

- 4. Both the mode register and the extended mode register must be programmed. After the mode register set cycle or the extended mode register set cycle, tMRD (2 clocks minimum) pause must be satisfied.

Remarks:

- 1. The sequence of Auto-refresh, mode register programming and extended mode register programming above may be transposed.

- 2. CKE must be held high.

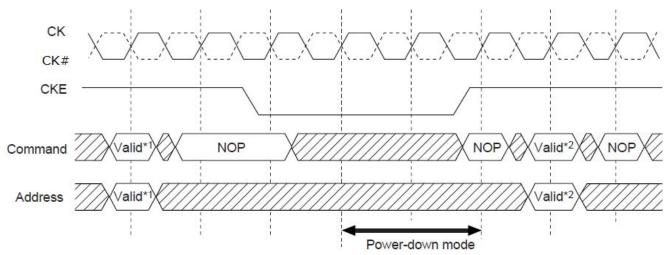

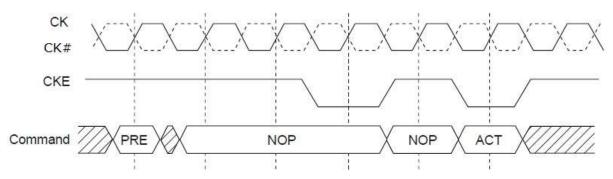

#### 4.3.2 Power Down Mode and CKE Control

DDR Mobile RAM will be into power-down mode at the second CK rising edge after CKE to be low level with NOP or DESL command at first CK rising edge after CKE signal to be low.

Notes:

- 1. Valid\*1 can be either Activate command or Precharge command, When Valid\*1 is Activate command, power-down mode will be active power-down mode, while it will be precharge power down mode, if Valid\*1 will be Precharge command.

- Valid\*2 can be any command as long as all of specified AC parameters are satisfied. However, if the CKE has one clock cycle high and on clock cycle low just as below, even DDR Mobile RAM will not enter power-down mode, this command flow does not hurt any data and can be done.

#### Figure 4.2 CKE Control

Note: Assume PRE and ACT command is closing and activating same bank.

### 4.4 Mode Register Definition

#### Figure 4.3 Mode Register

| Ŭ | 0 | 0 | 0               | 0   | 0    | 0       | 0            | DS      | 0 | 0 | PASR          | Extended Mode Register Set |                         |  |

|---|---|---|-----------------|-----|------|---------|--------------|---------|---|---|---------------|----------------------------|-------------------------|--|

|   |   |   |                 |     |      |         |              |         |   |   |               | Bits2-0                    | Refresh Array           |  |

|   |   |   |                 |     |      |         |              |         |   |   |               | 000                        | All banks               |  |

|   |   |   |                 | _   |      |         |              | -       |   |   |               | 001                        | Bank A & Bank B (BA1=0) |  |

|   |   |   |                 |     |      |         |              |         |   |   |               | 010                        | Bank A (BA0=BA1=0)      |  |

|   |   |   |                 |     |      | Bits6-5 | Stree        | ngth    |   |   | Partial Array | 011                        | R                       |  |

|   |   |   | Driver Strength |     | F    | 00      | Nom          | nal     |   |   | Self Refresh  | 100                        | R                       |  |

|   |   |   |                 |     | th [ | 01      | 1/2 s        | trength |   |   |               | 101                        | R                       |  |

|   |   |   |                 | 8 1 | 10   | 1/4 s   | trength      |         |   |   | 110           | R                          |                         |  |

|   |   |   |                 |     |      | 11      | 1/8 strength |         |   |   | 111           | R                          |                         |  |

Note: R = Reserved.

## 4.5 Burst Operation

The burst type (BT) and the first three bits of the column address determine the order of a data out.

#### Table 4.1 Burst length = 2

| Starting Address | Addressing (decimal) |            |  |  |  |

|------------------|----------------------|------------|--|--|--|

| AO               | Sequence             | Interleave |  |  |  |

| 0                | 0, 1                 | 0, 1       |  |  |  |

| 1                | 1, 0                 | 1, 0       |  |  |  |

### Table 4.2 Burst length = 4

| Starting | Address | Addressing (decimal) |            |  |

|----------|---------|----------------------|------------|--|

| A1       | A0      | Sequence             | Interleave |  |

| 0        | 0       | 0, 1, 2, 3           | 0, 1, 2, 3 |  |

| 0        | 1       | 1, 2, 3, 0           | 1, 0, 3, 2 |  |

| 1        | 0       | 2, 3, 0, 1           | 2, 3, 0, 1 |  |

| 1        | 1       | 3, 0, 1, 2           | 3, 2, 1, 0 |  |

#### Table 4.3 Burst length = 8

| Sta | nting Addr | ess | Addressing (decimal)   |                        |  |  |

|-----|------------|-----|------------------------|------------------------|--|--|

| A2  | A1         | A0  | Sequence               | Interleave             |  |  |

| 0   | 0          | 0   | 0, 1, 2, 3, 4, 5, 6, 7 | 0, 1, 2, 3, 4, 5, 6, 7 |  |  |

| 0   | 0          | 1   | 1, 2, 3, 4, 5, 6, 7, 0 | 1, 0, 3, 2, 5, 4, 7, 6 |  |  |

| 0   | 1          | 0   | 2, 3, 4, 5, 6, 7, 0, 1 | 2, 3, 0, 1, 6, 7, 4, 5 |  |  |

| 0   | 1          | 1   | 3, 4, 5, 6, 7, 0, 1, 2 | 3, 2, 1, 0, 7, 6, 5, 4 |  |  |

| 1   | 0          | 0   | 4, 5, 6, 7, 0, 1, 2, 3 | 4, 5, 6, 7, 0, 1, 2, 3 |  |  |

| 1   | 0          | 1   | 5, 6, 7, 0, 1, 2, 3, 4 | 5, 4, 7, 6, 1, 0, 3, 2 |  |  |

| 1   | 1          | 0   | 6, 7, 0, 1, 2, 3, 4, 5 | 6, 7, 4, 5, 2, 3, 0, 1 |  |  |

| 1   | 1          | 1   | 7, 0, 1, 2, 3, 4, 5, 6 | 7, 6, 5, 4, 3, 2, 1, 0 |  |  |

#### Table 4.4 Burst length = 16

| Star | rting | Addr | ess | Addressing (decimal)                  |                                       |  |  |  |

|------|-------|------|-----|---------------------------------------|---------------------------------------|--|--|--|

| А3   | A2    | A1   | A0  | Sequence                              | Interleave                            |  |  |  |

| 0    | 0     | 0    | 0   | 0,1,2,3,4,5,6,7,8,9,10,11,12,13,14,15 | 0,1,2,3,4,5,6,7,8,9,10,11,12,13,14,15 |  |  |  |

| 0    | 0     | 0    | 1   | 1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,0 | 1,0,3,2,5,4,7,6,9,8,11,10,13,12,15,14 |  |  |  |

| 0    | 0     | 1    | 0   | 2,3,4,5,6,7,8,9,10,11,12,13,14,15,0,1 | 2,3,0,1,6,7,4,5,10,11,8,9,14,15,12,13 |  |  |  |

| 0-   | 0     | 1    | 1   | 3,4,5,6,7,8,9,10,11,12,13,14,15,0,1,2 | 3,2,1,0,7,6,5,4,11,10,9,8,15,14,13,12 |  |  |  |

| 0    | 1     | 0    | 0   | 4,5,6,7,8,9,10,11,12,13,14,15,0,1,2,3 | 4,5,6,7,0,1,2,3,12,13,14,15,8,9,10,11 |  |  |  |

| 0    | 1     | 0    | 1   | 5,6,7,8,9,10,11,12,13,14,15,0,1,2,3,4 | 5,4,7,6,1,0,3,2,13,12,15,14,9,8,11,10 |  |  |  |

| 0    | 1     | 1    | 0   | 6,7,8,9,10,11,12,13,14,15,0,1,2,3,4,5 | 6,7,4,5,2,3,0,1,14,15,12,13,10,11,8,9 |  |  |  |

| 0    | 1     | 1    | 1   | 7,8,9,10,11,12,13,14,15,0,1,2,3,4,5,6 | 7,6,5,4,3,2,1,0,15,14,13,12,11,10,9,8 |  |  |  |

| 1    | 0     | 0    | 0   | 8,9,10,11,12,13,14,15,0,1,2,3,4,5,6,7 | 8,9,10,11,12,13,14,15,0,1,2,3,4,5,6,7 |  |  |  |

| 1    | 0     | 0    | 1   | 9,10,11,12,13,14,15,0,1,2,3,4,5,6,7,8 | 9,8,11,10,13,12,15,14,1,0,3,2,5,4,7,6 |  |  |  |

| 1    | 0     | 1    | 0   | 10,11,12,13,14,15,0,1,2,3,4,5,6,7,8,9 | 10,11,8,9,14,15,12,13,2,3,0,1,6,7,4,5 |  |  |  |

| 1    | 0     | 1    | 1   | 11,12,13,14,15,0,1,2,3,4,5,6,7,8,9,10 | 11,10,9,8,15,14,13,12,3,2,1,0,7,6,5,4 |  |  |  |

| 1    | 1     | 0    | 0   | 12,13,14,15,0,1,2,3,4,5,6,7,8,9,10,11 | 12,13,14,15,8,9,10,11,4,5,6,7,0,1,2,3 |  |  |  |

| 1    | 1     | 0    | 1   | 13,14,15,0,1,2,3,4,5,6,7,8,9,10,11,12 | 13,12,15,14,9,8,11,10,5,4,7,6,1,0,3,2 |  |  |  |

| 1    | 1     | 1    | 0   | 14,15,0,1,2,3,4,5,6,7,8,9,10,11,12,13 | 14,15,12,13,10,11,8,9,6,7,4,5,2,3,0,1 |  |  |  |

| 1    | 1     | 1    | 1   | 15,0,1,2,3,4,5,6,7,8,9,10,11,12,13,14 | 15,14,13,12,11,10,9,8,7,6,5,4,3,2,1,0 |  |  |  |

### 4.6 Read / Write Operation

#### **Bank Active**

A read or a write operation begins with the bank active command [ACT]. The bank active command determines a bank address and a row address. For the bank and the row, a read or a write command can be issued tRCD after the ACT is issued.

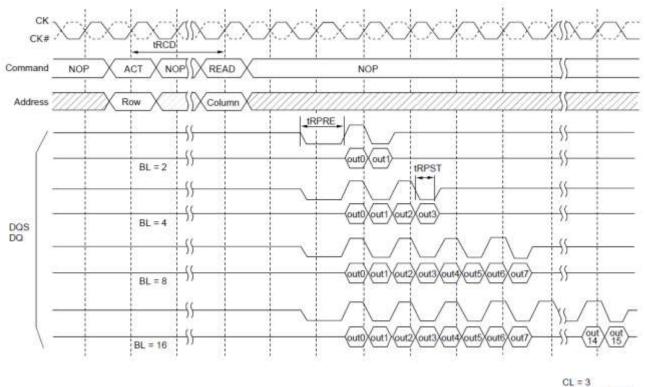

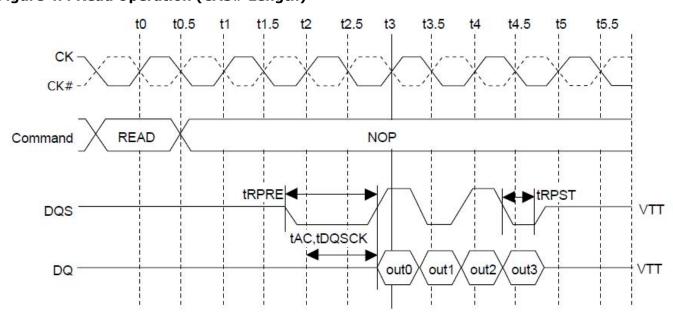

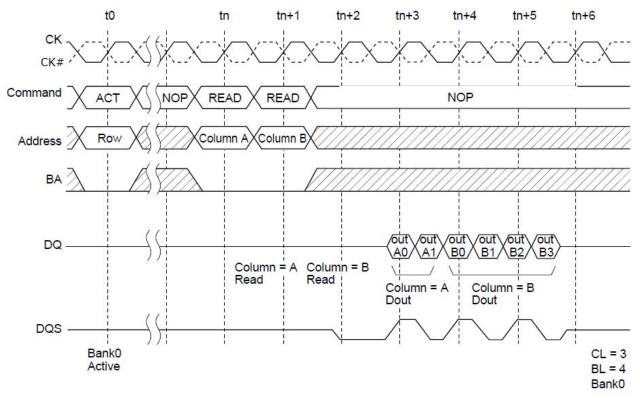

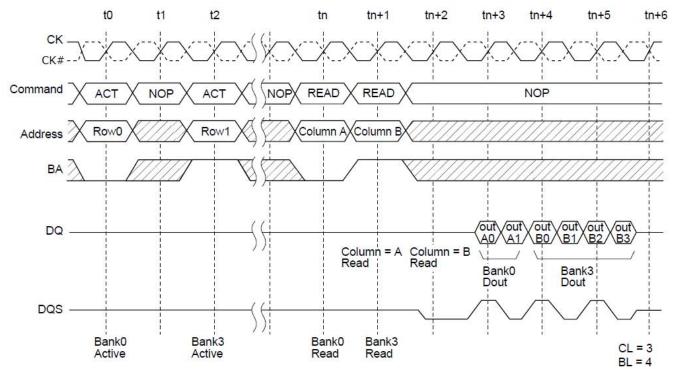

#### **Read operation**

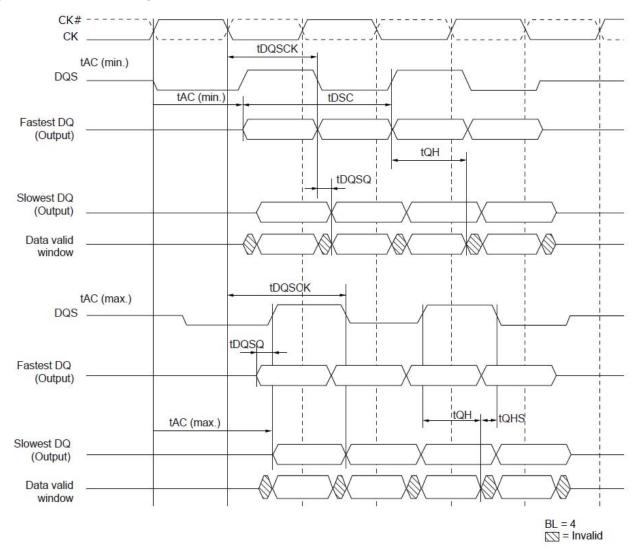

The burst length (BL), the CAS# latency (CL) and the burst type (BT) of the mode register are referred when a read command is issued. The burst length (BL) determines the length of a sequential output data by the read command that can be set to 2, 4, 8 or 16. The starting address of the burst read is defined by the column address, the bank select address (See 2.4 Pin Description) in the cycle when the read command is issued. The data output timing is characterized by CL and tAC. The read burst start (CL-1)  $\times$  tCK + tAC (ns) after the clock rising edge where the read command is latched. The DDR Mobile RAM outputs the data strobe through DQS pins simultaneously with data. tRPRE prior to the first rising edge of the data strobe, the DQS pins are driven low from high-Z state. This low period of DQS is referred as read preamble. The burst data are output coincidentally at both the rising and falling edge of the data strobe. The DQ pins become high-Z in the next cycle after the burst read operation completed. tRPST from the last falling edge of the data strobe, the DQS pins become high-Z. This low period of DQS is referred as read postamble.

#### Figure 4.4 Read Operation (Burst Length)

CL = 3 BL: Burst length

#### Figure 4.4 Read Operation (CAS# Length)

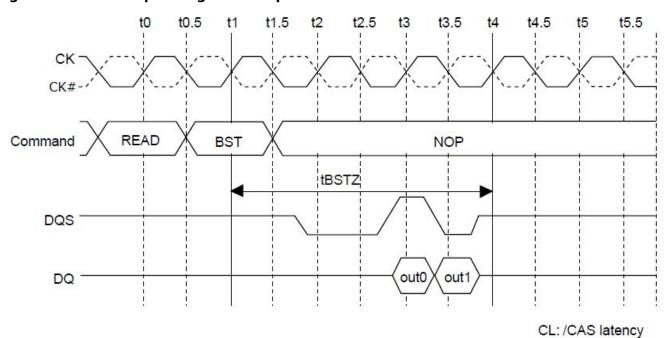

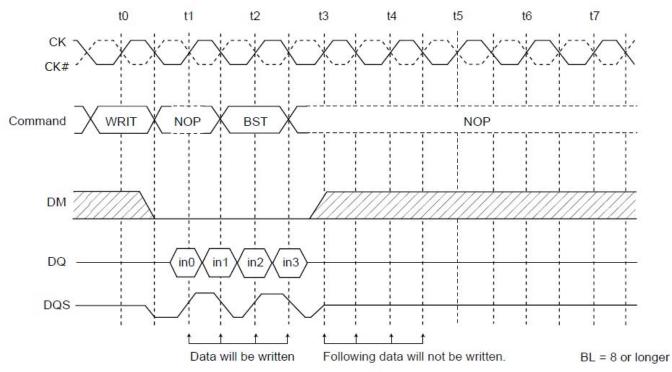

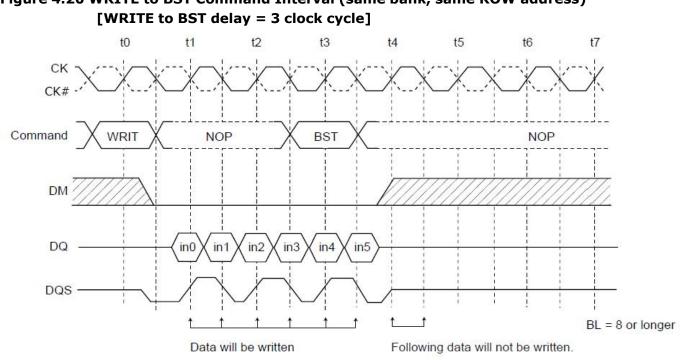

#### Burst stop command during burst operation

The burst stop (BST) command stops the burst read and sets all output buffers to high-Z. tBSTZ (= CL) cycles after a BST command issued, all DQ and DQS pins become high-Z.

The BST command is also supported for the burst write operation. No data will be written in subsequent cycles.

Note that bank address is not referred when this command is executed.

### Figure 4.5 Burst Stop during a Read Operation

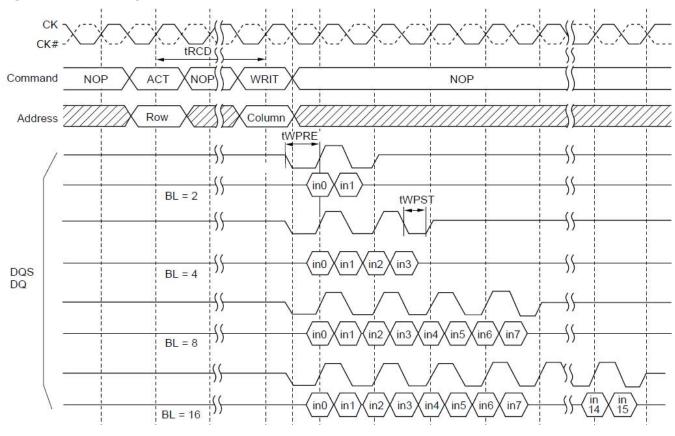

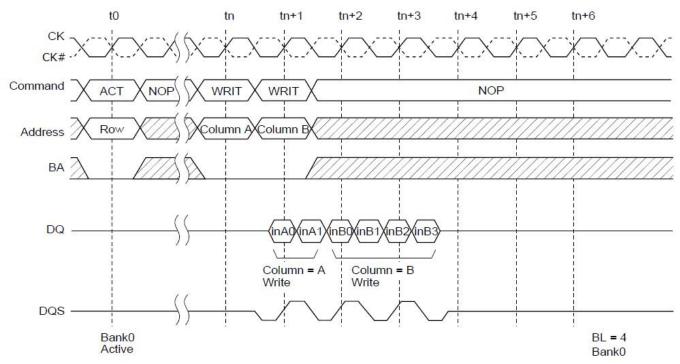

#### Write operation

The burst length (BL) and the burst type (BT) of the mode register are referred when a write command is issued. The burst length (BL) determines the length of a sequential data input by the write command that can be set to 2, 4, 8 or 16. The latency from write command to data input is fixed to 1. The starting address of the burst write is defined by the column address, the bank select address (See 2.4 Pin Description) in the cycle when the write command is issued. DQS should be input as the strobe for the input-data and DM as well during burst operation. tWPRE prior to the first rising edge of DQS, DQS must be set to low. tWPST after the last falling edge of DQS, the DQS pins can be changed to high-Z. The leading low period of DQS is referred as write preamble. The last low period of DQS is referred as write post-amble.

#### Figure 4.6 Write Operation

BL: Burst length

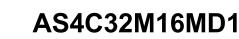

#### Read with auto precharge

The precharge is automatically performed after completing a read operation. The precharge starts BL/2 (= tRPD) clocks after READA command input. tRAS lock out mechanism for READA allows a read command with auto precharge to be issued to a bank that has been activated (opened) but has not yet satisfied the tRAS (min) specification. A column command to the other active bank can be issued the next cycle after the last data output.

Read with auto precharge command does not limit row commands execution for other bank.

#### Figure 4.7 Read with auto precharge

Note: Internal auto-precharge starts at the timing indicated by "

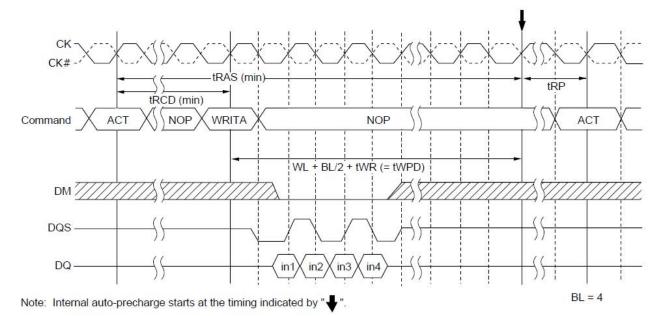

#### Write with auto precharge

The precharge is automatically performed after completing a burst write operation. The precharge operation is started Write latency (WL) + BL/2 + tWR (= tWPD) clocks after WRITA command issued. A column command to the other banks can be issued the next cycle after the internal precharge command issued.

Write with auto precharge command does not limit row commands execution for other bank.

#### Figure 4.8 Burst Write (BL = 4)

#### The Concurrent Auto Precharge

The DDR Mobile RAM supports the concurrent auto precharge feature, a read with auto precharge or a write with auto precharge, can be followed by any command to the other banks, as long as that command does not interrupt the read or write data transfer, and all other related limitations apply (e.g. contention between READ data and WRITE data must be avoided.) The minimum delay from a read or write command with auto precharge, to a command to a different bank, is summarized below.

| From Command                 | To command (different bank,<br>non-interrupting command) | Minimum delay<br>(Concurrent AP supported) | Unit |

|------------------------------|----------------------------------------------------------|--------------------------------------------|------|

|                              | Read or Read w/AP                                        | BL / 2                                     |      |

| Read with<br>Auto Precharge  | Write or Write w/AP                                      | CL (rounded up) + (BL/2)                   |      |

|                              | Precharge or Activate                                    | 1                                          | +01/ |

|                              | Read or Read w/AP                                        | 1 + (BL/2) + tWTR                          | tCK  |

| Write with<br>Auto Precharge | Write or Write w/AP                                      | BL / 2                                     |      |

|                              | Precharge or Activate                                    | 1                                          |      |

#### Table 4.5 The minimum delay from a read or write command with auto precharge

## 4.7 Command Intervals

#### 4.7.1 Read command to the consecutive Read command Interval

#### Table 4.6 A Read command to the consecutive Read command Interval

|   | Destination row of the<br>consecutive read command |                |        | Operation                                                                                                                                                                                                                                                         |

|---|----------------------------------------------------|----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Bank<br>address                                    | Row<br>address | State  | Operation                                                                                                                                                                                                                                                         |

| 1 | Same                                               | Same           | ACTIVE | The consecutive read can be performed after an interval of no less than 1 cycle to interrupt the preceding read operation.                                                                                                                                        |

| 2 | Same                                               | Different      | -      | Precharge the bank to interrupt the preceding read operation. tRP after the precharge command, issue the ACT command. tRCD after the ACT command, the consecutive read command can be issued. See 'A read command to the consecutive precharge interval' section. |

|   |                                                    |                | ACTIVE | The consecutive read can be performed after an interval of<br>no less than 1 cycle to interrupt the preceding read<br>operation.                                                                                                                                  |

| 3 | Different                                          | Any            | IDLE   | Precharge the bank without interrupting the preceding read<br>operation. tRP after the precharge command, issue the<br>ACT command. tRCD after the ACT command, the<br>consecutive read command can be issued.                                                    |

#### Figure 4.9 READ to READ Command Interval (same ROW address in the same bank)

#### Figure 4.10 READ to READ Command Interval (different bank)

#### **4.7.2 A Write command to the consecutive Write command Interval**

#### Table 4.7 A Write command to the consecutive Write command Interval

|   | Destination row of<br>consecutive write cor |                |        | Operation                                                                                                                                                                                                                                                            |  |  |

|---|---------------------------------------------|----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|   | Bank<br>address                             | Row<br>address | State  | Operation                                                                                                                                                                                                                                                            |  |  |

| 1 | Same                                        | Same           | ACTIVE | The consecutive write can be performed after an interval of no less than 1 cycle to interrupt the preceding write operation.                                                                                                                                         |  |  |

| 2 | Same                                        | Different      | -      | Precharge the bank to interrupt the preceding write operation. tRP after the precharge command, issue the ACT command. tRCD after the ACT command, the consecutive write command can be issued. See 'A write command to the consecutive precharge interval' section. |  |  |

|   | Different Any                               |                | ACTIVE | The consecutive write can be performed after an interval of<br>no less than 1 cycle to interrupt the preceding write<br>operation.                                                                                                                                   |  |  |

| 3 |                                             | Any            | IDLE   | Precharge the bank without interrupting the preceding write operation. tRP after the precharge command, issue the ACT command. tRCD after the ACT command, the consecutive write command can be issued.                                                              |  |  |

#### Figure 4.11 WRITE to WRITE Command Interval (same ROW address in the same bank)

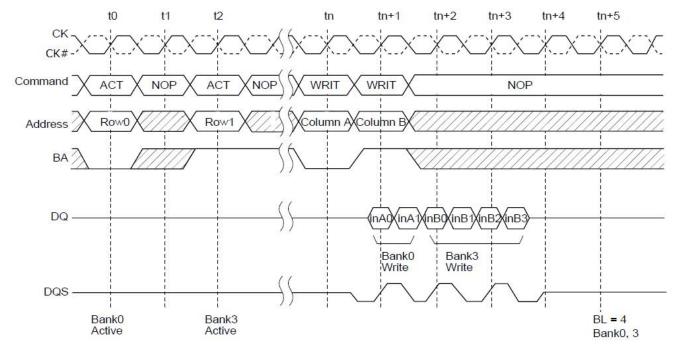

Figure 4.12 WRITE to WRITE Command Interval (different bank)

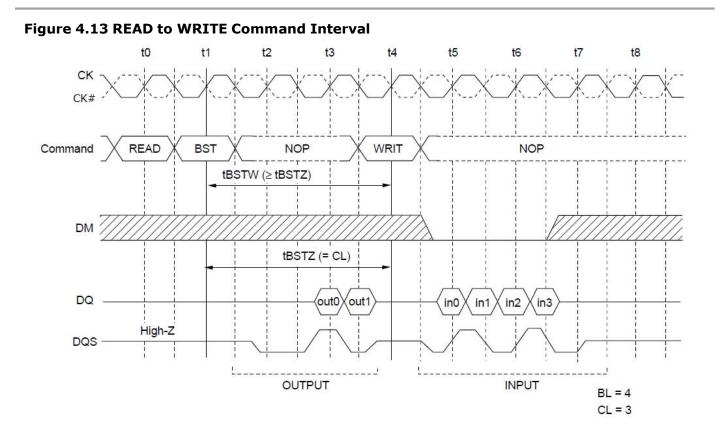

#### 4.7.3 A Read command to the consecutive Write command interval with BST command

#### Table 4.8 A Read command to the consecutive Write command interval with BST command

|   | Destination row of the consecutive write command |                |        | Operation                                                                                                                                                                                                                                                          |  |  |  |  |  |

|---|--------------------------------------------------|----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|   | Bank<br>address                                  | Row<br>address | State  | epe.adon                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 1 | Same                                             | Same           | ACTIVE | Issue the BST command. tBSTW ( $\geq$ tBSTZ) after the BST command, the consecutive write command can be issued.                                                                                                                                                   |  |  |  |  |  |

| 2 | Same                                             | Different      | -      | Precharge the bank to interrupt the preceding read operation. tRP after the precharge command, issue the ACT command. tRCD after the ACT command, the consecutive write command can be issued. See 'A read command to the consecutive precharge interval' section. |  |  |  |  |  |

|   |                                                  |                | ACTIVE | Issue the BST command. tBSTW ( $\geq$ tBSTZ) after the BST command, the consecutive write command can be issued.                                                                                                                                                   |  |  |  |  |  |

| 3 | Different                                        | ferent Any     | IDLE   | Precharge the bank independently of the preceding read operation. tRP after the precharge command, issue the ACT command. tRCD after the ACT command, the consecutive write command can be issued.                                                                 |  |  |  |  |  |

AS4C32M16MD1

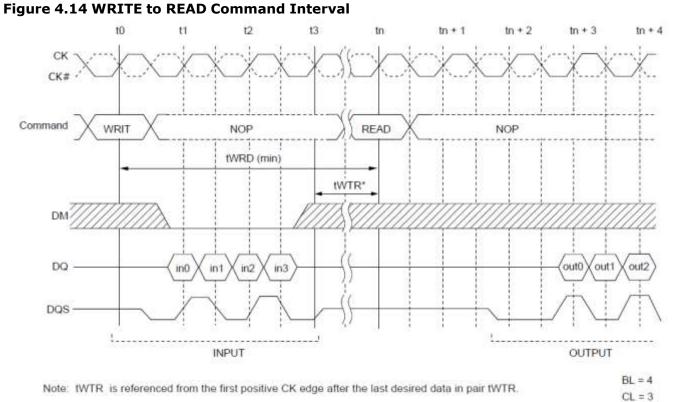

#### 4.7.4 A Write command to the consecutive Read command interval : To complete the burst operation

# Table 4.9 A Write command to the consecutive Read command interval :To complete the burst operation

|   | Destination row of the<br>consecutive read command |                      |        | Operation                                                                                                                                                                                                                                                      |  |  |  |  |  |

|---|----------------------------------------------------|----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|   | Bank<br>address                                    | Row<br>address State |        | operation                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 1 | Same                                               | Same                 | ACTIVE | To complete the burst operation, the consecutive read command should be performed tWRD after the write command.                                                                                                                                                |  |  |  |  |  |

| 2 | Same                                               | Different            | -      | Precharge the bank tWPD after the preceding write command. tRP after the precharge command, issue the ACT command. tRCD after the ACT command, the consecutive read command can be issued. See 'A read command to the consecutive precharge interval' section. |  |  |  |  |  |

|   |                                                    |                      | ACTIVE | To complete a burst operation, the consecutive read command should be performed tWRD after the write command.                                                                                                                                                  |  |  |  |  |  |

| 3 | Different                                          | Any                  | IDLE   | Precharge the bank independently of the preceding write<br>operation. tRP after the precharge command, issue the<br>ACT command. tRCD after the ACT command, the<br>consecutive read command can be issued.                                                    |  |  |  |  |  |

AS4C32M16MD1

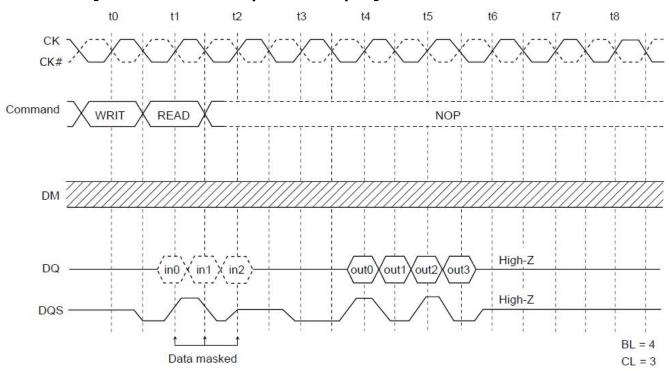

#### **4.7.5 A Write command to the consecutive Read command interval :** To interrupt the write operation

# Table 4.10 A Write command to the consecutive Read command interval :To interrupt the write operation

|   |                                   | ation row<br>tive read co |        | Operation                                                                                                                                                                                                     |  |  |  |

|---|-----------------------------------|---------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|   | Bank Row<br>address address State |                           | State  | operation                                                                                                                                                                                                     |  |  |  |

| 1 | Same                              | Same                      | ACTIVE | DM must be input 1 cycle prior to the read command input<br>to prevent from being written invalid data. In case, the<br>read command is input in the next cycle of the write<br>command, DM is not necessary. |  |  |  |

| 2 | Same                              | Different                 | -      | Note 1                                                                                                                                                                                                        |  |  |  |

| 3 | Different                         | Any                       | ACTIVE | DM must be input 1 cycle prior to the read command input<br>to prevent from being written invalid data. In case, the<br>read command is input in the next cycle of the write<br>command, DM is not necessary. |  |  |  |

|   |                                   |                           | IDLE   | Note 1                                                                                                                                                                                                        |  |  |  |

Note :

1. Precharge must be preceded to read command. Therefore read command cannot interrupt the write operation in this case.

#### Figure 4.15 WRITE to READ Command Interval (same bank, same ROW address) [WRITE to READ delay = 1 clock cycle]

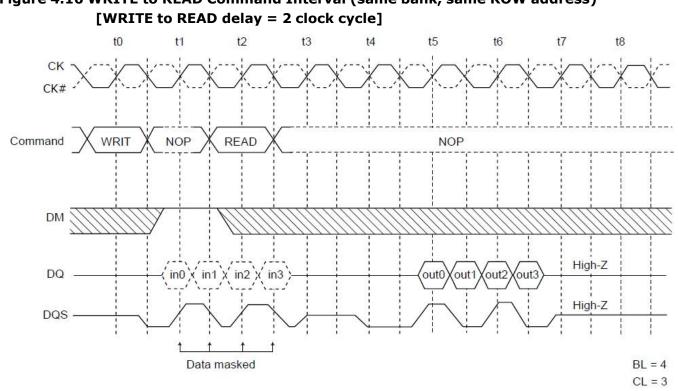

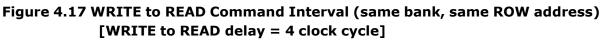

Figure 4.16 WRITE to READ Command Interval (same bank, same ROW address)

Note : tWTR is referenced from the first positive CK edge after the last desired data in pair tWTR.

#### 4.7.6 A Write command to the Burst stop command interval : To interrupt the write operation

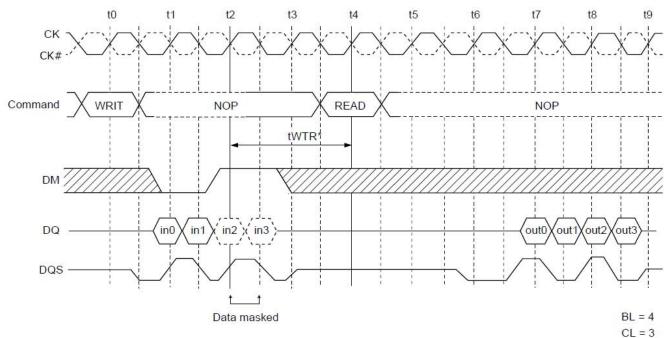

Figure 4.18 WRITE to BST Command Interval (same bank, same ROW address) [WRITE to BST delay = 1 clock cycle]

Figure 4.19 WRITE to BST Command Interval (same bank, same ROW address) [WRITE to BST delay = 2 clock cycle]

# Figure 4.20 WRITE to BST Command Interval (same bank, same ROW address)

#### 4.7.7 A Read command to the consecutive Precharge command interval

Operation by each case of destination bank of the consecutive Precharge command.

| Table 4.11 A Read | command to the | consecutive Precharge | command interval |

|-------------------|----------------|-----------------------|------------------|

|                   |                |                       |                  |

|   | Bank address | Operation                                                                                                                                                                                                   |

|---|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

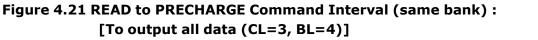

| 1 | Same         | The PRE and PALL command can interrupt a read operation.<br>To complete a burst read operation, tRPD is required between the read<br>and the precharge command. Please refer to the following timing chart. |

| 2 | Different    | The PRE command does not interrupt a read command.<br>No interval timing is required between the read and the precharge<br>command.                                                                         |

#### READ to PRECHARGE Command Interval (same bank) : To output all data

To complete a burst read operation and get a burst length of data, the consecutive precharge command must be issued tRPD (= BL/2 cycles) after the read command is issued.

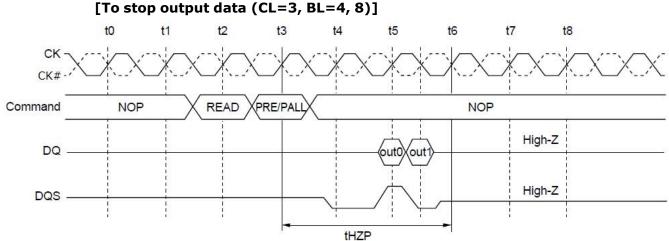

#### READ to PRECHARGE Command Interval (same bank): To stop output data

A burst data output can be interrupted with a precharge command. All DQ pins and DQS pins become high-Z tHZP (= CL) after the precharge command.

# Figure 4.22 READ to PRECHARGE Command Interval (same bank) :

#### 4.7.8 A Write command to the consecutive Precharge command interval (same bank)

Operation by each case of destination bank of the consecutive Precharge command.

#### Table 4.12 A Write command to the consecutive Precharge command interval (same bank)

|                                                                | Bank address | Operation                                                                                                                                                                                                      |

|----------------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 Same To complete a burst write operation, tWPD is required b |              | The PRE and PALL command can interrupt a write operation.<br>To complete a burst write operation, tWPD is required between the write<br>and the precharge command. Please refer to the following timing chart. |

| 2                                                              | Different    | The PRE command does not interrupt a write command.<br>No interval timing is required between the write and the precharge<br>command.                                                                          |

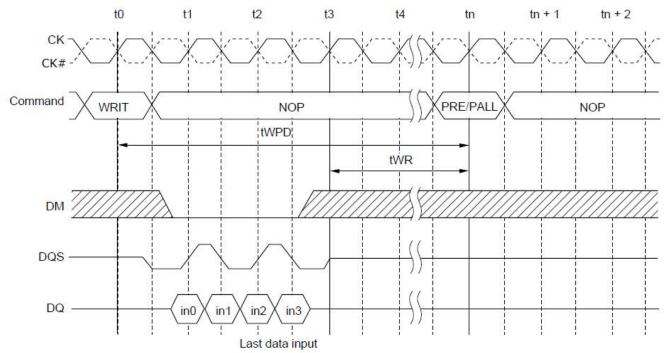

#### WRITE to PRECHARGE Command Interval (same bank)

The minimum interval tWPD is necessary between the write command and the precharge command.

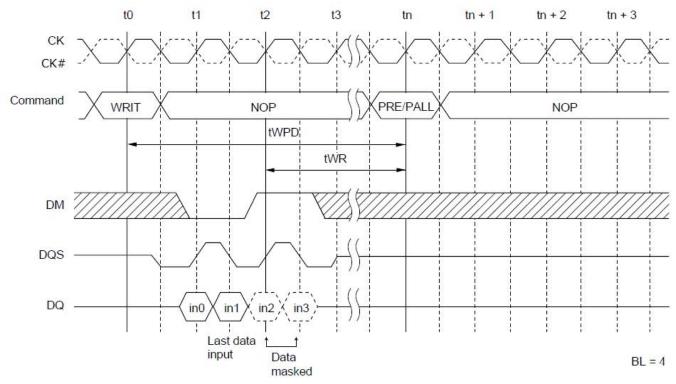

#### Figure 4.24 WRITE to PRECHARGE Command Interval(same bank):BL=4, DM to mask data

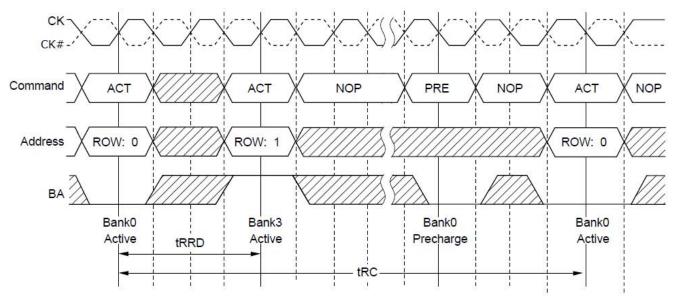

#### 4.7.9 Bank active command interval

#### Table 4.13 Bank active command interval

|   | Destination row of the<br>consecutive ACT command |       |        | Operation                                                                                                                                  |  |  |  |

|---|---------------------------------------------------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|   | Bank<br>address                                   | State |        | operation                                                                                                                                  |  |  |  |

| 1 | Same                                              | Any   | ACTIVE | Two successive ACT commands can be issued at tRC interval. In between two successive ACT operations, precharge command should be executed. |  |  |  |

| 2 |                                                   |       | ACTIVE | Precharge the bank. tRP after the precharge command, the consecutive ACT command can be issued.                                            |  |  |  |

|   | Binorent                                          | Any   | IDLE   | tRRD after an ACT command, the next ACT command can be issued.                                                                             |  |  |  |

#### Figure 4.25 Bank Active

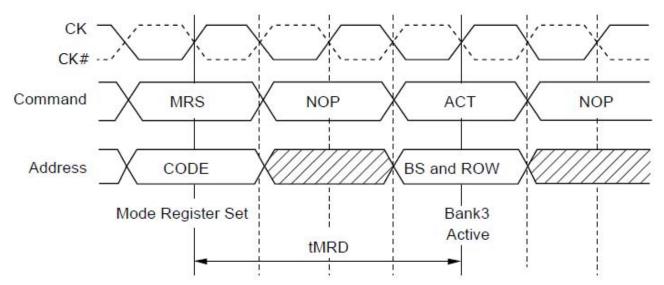

#### Mode register set to Bank-active command interval

The interval between setting the mode register and executing a bank-active command must be no less than tMRD.

#### Figure 4.26 Mode Register Set to Bank Active

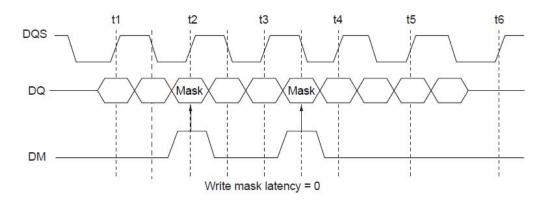

#### 4.7.10 DM Control

DM can mask input data. By setting DM to low, data can be written. UDM and LDM can mask the upper and lower byte of input data, respectively. When DM is set to high, the corresponding data is not written, and the previous data is held. The latency between DM input and enabling/disabling mask function is 0.

#### Figure 4.27 DM Control

# 5. Timing Waveforms

#### Figure 5.1 Command and Address Input Timing Definition

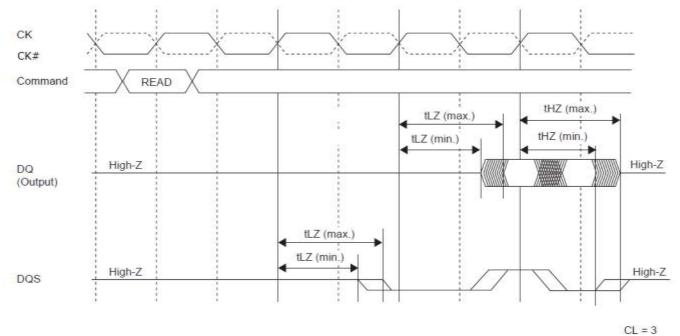

#### Figure 5.2 Read Timing Definition - 1

Figure 5.2 Read Timing Definition – 2

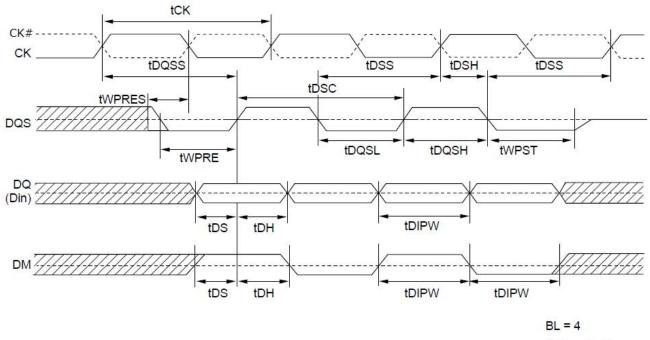

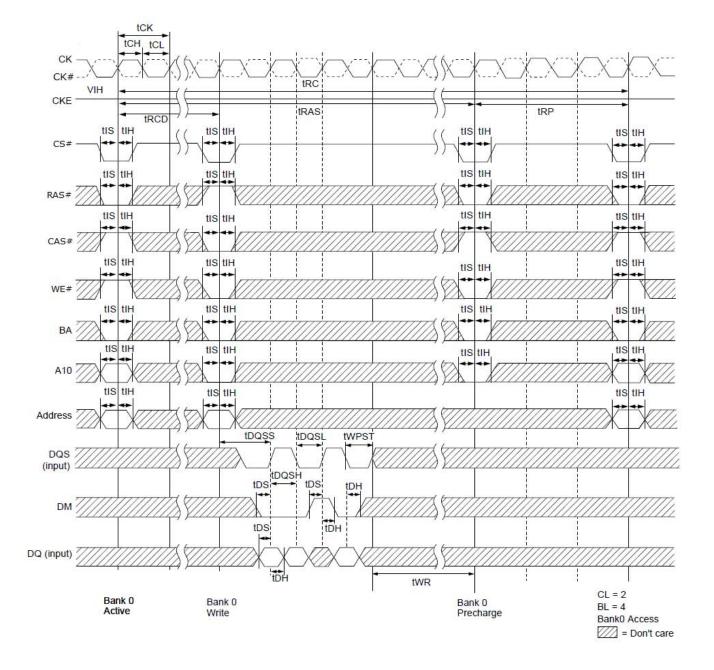

#### Figure 5.3 Write Timing Definition

= Don't care

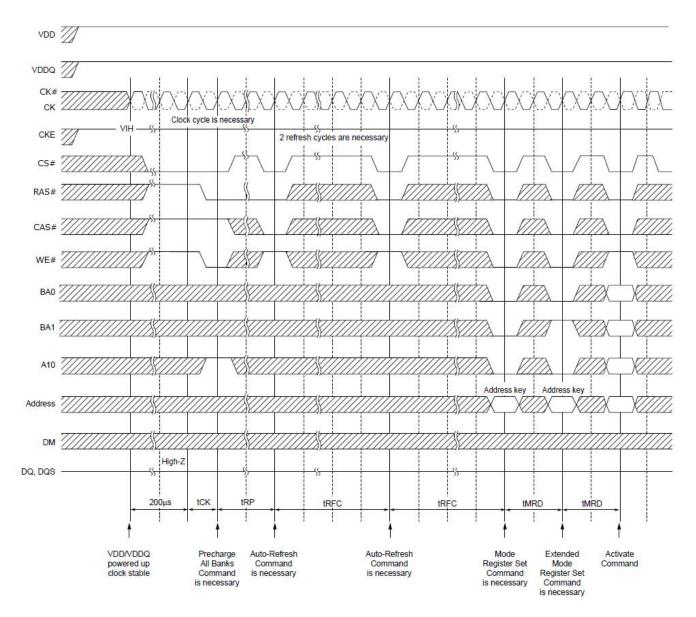

#### Figure 5.4 Initialize Sequence

= Don't care

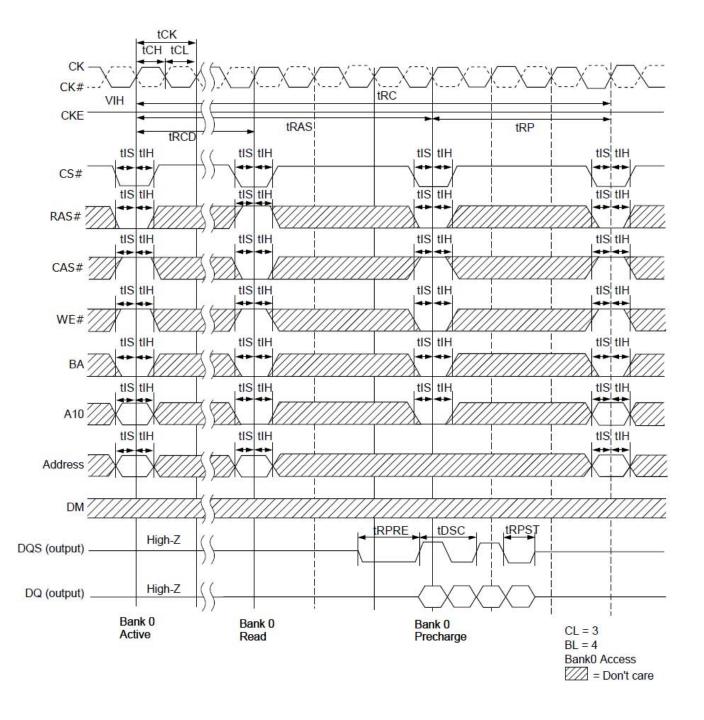

#### Figure 5.5 Read Cycle

#### Figure 5.6 Write Cycle

56

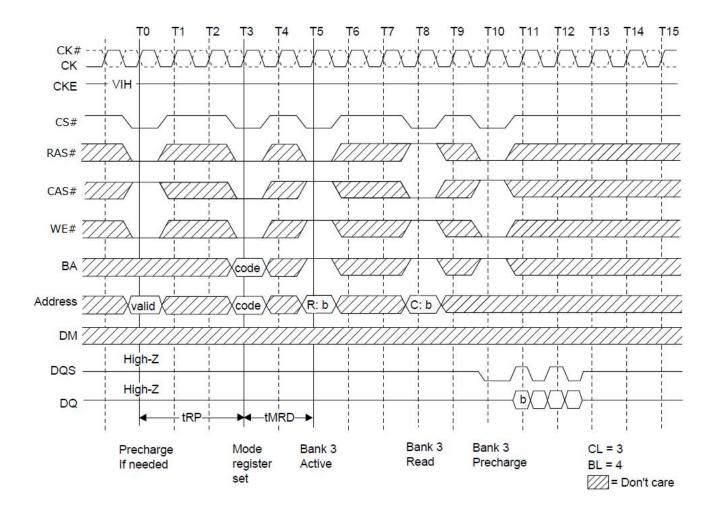

#### Figure 5.7 Mode Register Set Cycle

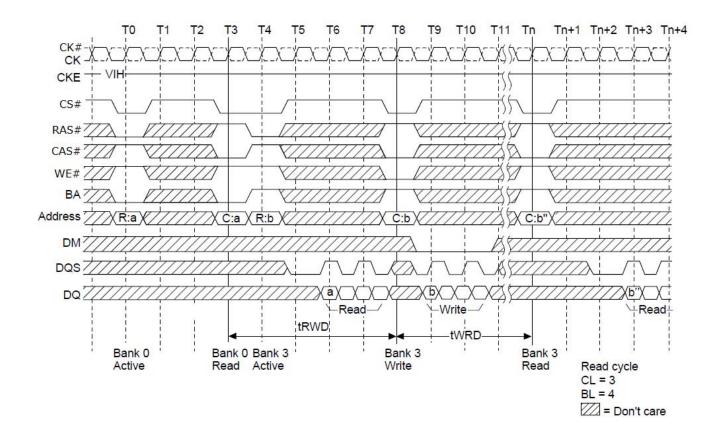

#### Figure 5.8 Read / Write Cycle

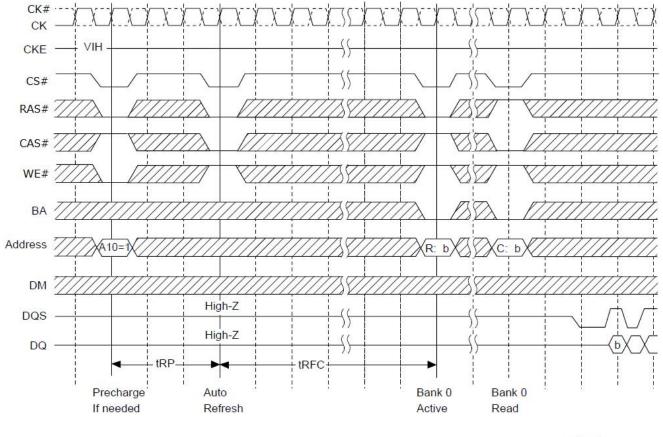

#### Figure 5.9 Auto Refresh Cycle

#### Figure 5.10 Self Refresh Cycle

Figure 5.11 Power Down Entry and Exit

#### Figure 5.12 Deep Power Down Entry

#### Figure 5.13 Deep Power Down Exit

Note: The sequence of auto-refresh, mode register programming and extended mode register programming above may be transposed.

## **6. ELECTRICAL SPECIFICATIONS**

- All voltages are referenced to VSS (GND).

- After power-up, wait more than **200µs** and then, execute power on sequence and CBR (Auto) refresh before proper device operation is achieved.

#### **6.1 Absolute Maximum Ratings**

#### Table 6.1 Absolute maximum ratings

| Parameter                          | Symbol | Rating       | Unit | Note |

|------------------------------------|--------|--------------|------|------|

| Voltage on any pin relative to VSS | VT     | -0.5 to +2.3 | V    |      |

| Supply voltage relative to VSS     | VDD    | -0.5 to +2.3 | V    |      |

| Short circuit output current       | IOS    | 50           | mA   |      |

| Power dissipation                  | PD     | 1.0          | W    |      |

| Operating junction temperature     | Tj     | -30 to +85   | °C   |      |

| Storage temperature                | Tstg   | -55 to +125  | °C   |      |

#### **Caution**:

Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

### **6.2 DC Characteristics**

#### Table 6.2 Recommended DC Operating Conditions (Tj=-30℃ to +85℃)

| Parameter                                       | Pins       | Symbol    | Min.       | Тур.       | Max.       | Unit | Note |

|-------------------------------------------------|------------|-----------|------------|------------|------------|------|------|

| Supplyveltage                                   |            | VDD, VDDQ | 1.7        | 1.8        | 1.95       | V    | 1    |

| Supply voltage                                  |            | VSS, VSSQ | 0          | 0          | 0          |      |      |

| Input high voltage                              | All other  | VIH       | 0.8 x VDDQ | -          | VDDQ + 0.3 | V    |      |

| Input low voltage                               | input pins | VIL       | -0.3       | -          | 0.2 x VDDQ | V    |      |

| DC input<br>Voltage level                       |            | VIN(DC)   | -0.3       | -          | VDDQ + 0.3 |      |      |

| AC Input<br>differential cross<br>point voltage | СК, СК#    |           |            | 0.6 x VDDQ | V          | 6    |      |

| DC input<br>differential voltage                |            | VID(DC)   | 0.4 x VDDQ | -          | VDDQ + 0.6 |      | 5    |

| AC input<br>differential voltage                |            | VID(AC)   | 0.6 x VDDQ | -          | VDDQ + 0.6 |      | 5    |

| DC input<br>high voltage                        |            | VIHD(DC)  | 0.7 x VDDQ | -          | VDDQ + 0.3 |      |      |

| DC input<br>low voltage                         | DQ, DM,    | VILD(DC)  | -0.3       | -          | 0.3 x VDDQ | V    |      |

| AC input<br>high voltage                        | DQS        | VIHD(AC)  | 0.8 x VDDQ | -          | VDDQ + 0.3 |      |      |

| AC input<br>low voltage                         |            | VILD(AC)  | -0.3       | -          | 0.2 x VDDQ |      |      |

Notes:

- 1. VDDQ must be equal to VDD.

- 2. VIH (max.) = 2.3V (pulse width  $\leq$  5ns).

- 3. VIL (min.) = -0.5V (pulse width  $\leq 5ns$ ).

- 4. All voltage referred to VSS and VSSQ must be same potential.

- 5. VID (DC) and VID (AC) are the magnitude of the difference between the input level on CK and the input level on CK#.

- 6. The value of VIX is expected to be 0.5  $\times$  VDDQ and must track variations in the DC level of the same.

Table 6.3 DC Characteristics-I(Tj=-30°C to +85°C, VDD and VDDQ = 1.7V to 1.95V, VSS and VSSQ = 0V)

| Parameter                                                      | Symbol | Max. | Unit | Test Condition                                                                                                                                                                   |

|----------------------------------------------------------------|--------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating current<br>(ACT-PRE)                                 | IDDO   | 85   | mA   | One bank active-precharge,<br>CKE = H, CS# = H between valid commands,<br>tCK = tCK (min.), tRC = tRC (min.),<br>Address bus inputs are SWITCHING;<br>Data bus inputs are STABLE |

| Standby current in power down                                  | IDD2P  | 0.8  | mA   | All banks idle, CKE=L, CS#=H, tCK=tCK (min.),<br>Address and control inputs are SWITCHING;<br>Data bus inputs are STABLE                                                         |

| Standby current in<br>power down with<br>clock stop            | IDD2PS | 0.6  | mA   | All banks idle, CKE=L, CS#=H, CK=L, CK#=H,<br>Address and control inputs are SWITCHING;<br>Data bus inputs are STABLE                                                            |

| Standby current in non-power down                              | IDD2N  | 7.0  | mA   | All banks idle, CKE=H, CS#=H, tCK=tCK (min.),<br>Address and control inputs are SWITCHING;<br>Data bus inputs are STABLE                                                         |

| Standby current in<br>non-power down with<br>clock stop        | IDD2NS | 2.0  | mA   | All banks idle, CKE=H, CS#=H, CK=L, CK#=H,<br>Address and control inputs are SWITCHING;<br>Data bus inputs are STABLE                                                            |

| Active standby current<br>in power down                        | IDD3P  | 3.0  | mA   | One bank active, CKE=L, CS#=H, tCK=tCK (min.),<br>Address and control inputs are SWITCHING;<br>Data bus inputs are STABLE                                                        |

| Active standby current<br>in power down with<br>clock stop     | IDD3PS | 2.0  | mA   | One bank active, CKE=L, CS#=H, CK=L, CK#=H;<br>Address and control inputs are SWITCHING;<br>Data bus inputs are STABLE                                                           |

| Active standby current in non-power down                       | IDD3N  | 10   | mA   | One bank active, CKE=H, CS#=H, tCK=tCK (min.),<br>Address and control inputs are SWITCHING;<br>Data bus inputs are STABLE                                                        |

| Active standby current<br>in non-power down<br>with clock stop | IDD3NS | 7.0  | mA   | One bank active, CKE=H, CS#=H, CK=L, CK#=H,<br>Address and control inputs are SWITCHING;<br>Data bus inputs are STABLE                                                           |

| Burst operating<br>current                                     | IDD4   | 135  | mA   | One bank active,<br>Continuous burst reads or writes;<br>tCK=tCK (min.), CL=3, BL=4, IOUT = 0mA,<br>Address inputs are SWITCHING,<br>50% data change each burst transfer         |

| Auto-refresh current                                           | IDD5   | 90   | mA   | CKE=H, tCK=tCK (min.), tRFC=tRFC (min.),<br>Address and control inputs are SWITCHING;<br>Data bus inputs are STABLE                                                              |

| Deep power down<br>current                                     | IDD8   | 10   | uA   | Address and control inputs are STABLE;<br>Data bus inputs are STABLE                                                                                                             |

#### Table 6.4 Advanced Data Retention Current (Tj = $-30^{\circ}$ C to $+85^{\circ}$ C,

#### VDD and VDDQ = 1.7V to 1.95V, VSS and VSSQ = 0V)

| Parameter<br>Advanced data retention current<br>(Self refresh current) | Symbol | Тур. | Max. | Unit | Condition                                                    |

|------------------------------------------------------------------------|--------|------|------|------|--------------------------------------------------------------|

| PASR="000" (Full)                                                      |        | -    | 400  |      | -30°C ≤ TJ ≤ +40°C                                           |

| PASR="001" (2BK)                                                       | IDD6   | -    | 350  |      | $-30^{\circ}$ C $\leq$ 13 $\leq$ +40 $^{\circ}$ C<br>CKE = L |