# PI7C9X3G606GP PCI EXPRESS GEN 3 PACKET SWITCH 6-Port 6-Lane PCI Express Gen 3 Switch

DATASHEET REVISION 3 February 2024

1545 Barber Lane Milpitas, CA 95035 Telephone: 1-408-232-9100 FAX: 408-434-1040 Internet: <u>http://www.diodes.com</u>

#### IMPORTANT NOTICE

1. DIODES INCORPORATED (Diodes) AND ITS SUBSIDIARIES MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes' products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes' products. Diodes' products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of Diodes' products for their intended applications, (c) ensuring their applications, which incorporate Diodes' products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

5 Diodes' products are provided subject to Diodes' Standard Terms and Conditions of Sale (https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

6. Diodes' products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes' products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

9. This Notice may be periodically updated with the most recent version available at https://www.diodes.com/about/company/terms-and-conditions/important-notice

The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries. All other trademarks are the property of their respective owners. © 2024 Diodes Incorporated. All Rights Reserved.

www.diodes.com

## **REVISION HISTORY**

| Date       | Revision Number | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03/08/2021 | 1               | Initial Datasheet Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

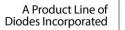

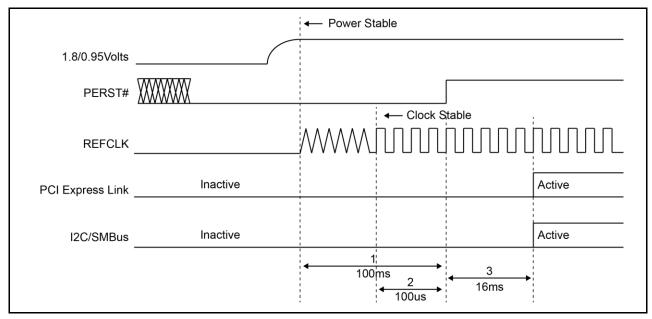

| 11/02/2023 | 2               | Add Thermal Data with HS to Table 13-1<br>Modify Section 3.5 SIDE BAND MANAGEMENT SIGNALS for EECK pin<br>Updated Figure 10-1 Initial Power-Up Sequence<br>Updated Table 12-12 Power Consumption<br>Updated 14 PACKAGE INFORMATION<br>Updated 5.4 I2C INTERFACE<br>Updated 9.3.47 LINK STATUS REGISTER – OFFSET 78h<br>Updated Section 8.3.3.3 CONTROL FILED<br>Updated Section 9.7.1 DMA CONTROL AND STATUS REGISTER 0 – OFFSET 00h<br>Updated Section 9.3.5 REVISION ID REGISTER – OFFSET 08h<br>Unified definition of host definitions for Section 7 and Section 8<br>Added Section 4.2.1 PHY CONTROL REGISTER PARALLEL INTERFACE ACCESS<br>Updated Domain ID Range<br>Removed ASPM Function<br>Updated Table 6-1 CPLD Signal Name Mapping for 8-bit IO Expander<br>Updated Table 6-3 CPLD Signal Name Mapping for 16-bit IO Expander<br>Updated Section 6.1.1 and 6.1.3<br>Updated Section 6.2 TIMING SEQUENCE FOR SURPRISED HOT PLUG<br>OPERATION<br>Updated "EEPROM/I2C-SMBUS" Columm for Section 9 |

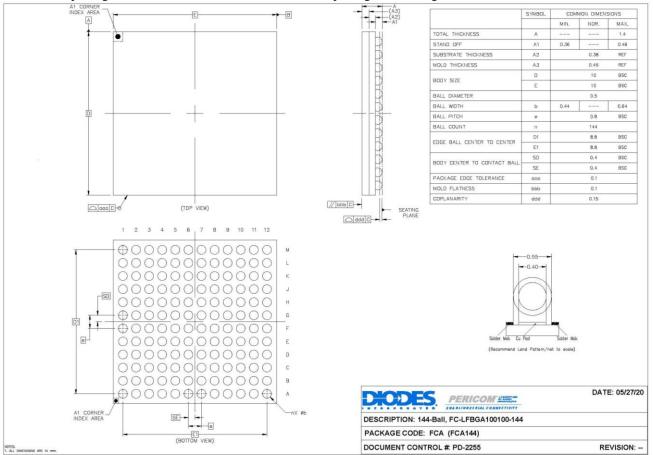

| 02/15/2024 | 3               | Updated Section 6 Hot Plug Support<br>Updated Section 9.3.48 and 9.4.38 SLOT CAPABILITIES REGISTER – OFFSET 7Ch<br>(Downstream Port Only)<br>Updated Section 9.3.138 and 9.4.110 OPERATION MODE REGISTER – OFFSET<br>348h (Port 0 Only)<br>Updated Section 9.3.188 and 9.4.160 DEVICE CONFIGURATION 2 REGISTER –<br>OFFSET 50Ch (Port 0 Only)<br>Updated Section 3.2 CONFIGURATION STRAPPING SIGNALS<br>Updated Figure Standard Devices to I2C Bus Connection Block Diagram<br>Updtaed Package Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## **TABLE OF CONTENTS**

| 1 | INT                 | RODUCTION                                           |    |

|---|---------------------|-----------------------------------------------------|----|

|   | 1.1                 | KEY FEATURES                                        |    |

| 2 | GEN                 | IERAL DESCRIPTION                                   | 26 |

| - | <b>UL</b>           |                                                     | 20 |

| 3 | PIN                 | DESCRIPTION                                         |    |

|   | 3.1                 | PCI EXPRESS INTERFACE SIGNALS                       |    |

|   | 3.2                 | CONFIGURATION STRAPPING SIGNALS                     |    |

|   | 3.3                 | HOT PLUG SIGNALS                                    |    |

|   | 3.4                 | REFERENCE CLOCK OUTPUT AND CONTROL SIGNALS          |    |

|   | 3.5                 | SIDE BAND MANAGEMENT SIGNALS                        |    |

|   | 3.6                 | MISCELLANEOUS CONTROL AND STATUS                    |    |

|   | 3.7                 | JTAG BOUNDARY SCAN SIGNALS                          |    |

|   | 3.8                 | POWER PINS                                          |    |

| 4 | FUN                 | CTIONAL OVERVIEW                                    |    |

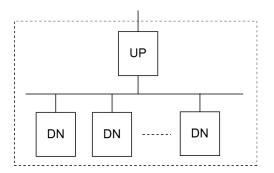

|   | 4.1                 | MODES OF OPERATIONS                                 | 33 |

|   | 4.1.                |                                                     |    |

|   | 4.1.2               |                                                     |    |

|   |                     | PHYSICAL LAYER CIRCUITS                             |    |

|   |                     | PHY CONTROL REGISTER PARALLEL INTERFACE ACCESS      |    |

|   | 4.                  | 2.1.1 Read Procedures                               |    |

|   |                     | 2.1.2 Write Procedures                              |    |

|   | 4.3                 | MEDIA ACCESS CONTROL (MAC)                          |    |

|   | 4.4                 | DATA LINK LAYER (DLL)                               |    |

|   | 4.5                 | TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION) |    |

|   | 4.6                 | ROUTING                                             |    |

|   | 4.7<br><i>4.7</i> . | QUEUE<br>I POSTED REQUEST HEADER (PH)               |    |

|   | 4.7.2               |                                                     |    |

|   | 4.7.                | $\epsilon$                                          |    |

|   | 4.7.4               |                                                     |    |

|   | 4.7.                |                                                     |    |

|   | 4.8                 | TRANSACTION ORDERING                                |    |

|   | 4.9                 | PORT ARBITRATION                                    |    |

|   | 4.10                | FLOW CONTROL                                        |    |

|   | 4.11                | TRANSATION LAYER TRANSMIT BLOCK (TLP ENCAPSULATION) |    |

|   | 4.12                | ACCESS CONTROL SERVICE (ACS)                        |    |

|   | 4.13                | MULTICAST OPERATION                                 |    |

| 5 | CHI                 | P INITIZATION                                       |    |

|   | 5.1                 | PORT-LANE CONFIGURATION                             | 41 |

|   | 5.1.                |                                                     |    |

|   | 5.1.2               | 2 LANE MAPPING                                      |    |

|   | 5.1.                | 3 PORT NUMERING                                     | 41 |

|   | 5.1.4               | 4 PORT-LANE MAPPING                                 | 41 |

|   | 5.2                 | CLOCK SCHEME                                        |    |

|   | 5.2.                |                                                     |    |

|   | 5.2.2               |                                                     |    |

|   | 5.3                 | EEPROM INTERFACE                                    |    |

|   | 5.3.                | I EERPOM ACCESS MODES                               |    |

PI7C9X3G606GP

| 5.3.2 E             | EPROM MODE AT RESET                                 | 11 |

|---------------------|-----------------------------------------------------|----|

|                     | EPROM MODE AT RESET                                 |    |

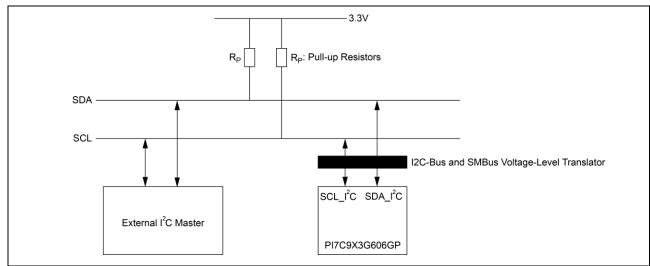

|                     | TERFACE                                             |    |

|                     | CREGISTER WRITE ACCESS                              |    |

|                     | C REGISTER READ ACCESS                              |    |

|                     | G SUPPORT                                           | 51 |

|                     |                                                     |    |

|                     | PLUG TYPES                                          |    |

|                     | URPRISED SERIAL HOT PLUG                            |    |

|                     | IANAGED SERIAL HOT PLUG                             |    |

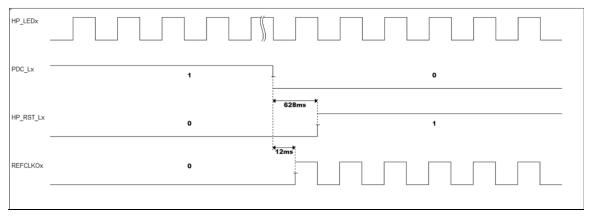

| 6.2 TIMIN           | IG SEQUENCE FOR SURPRISED HOT PLUG OPERATION        | 53 |

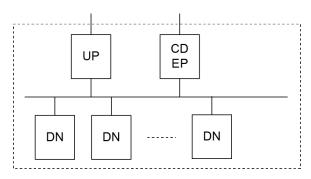

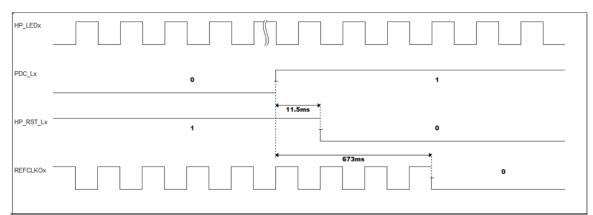

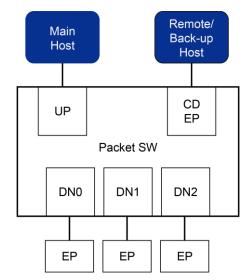

| 7 CROSS-DO          | DMAIN END-POINT                                     | 55 |

| 7.1 GENE            | RAL DESCRIPTION                                     |    |

|                     | AIL-OVER                                            |    |

|                     | O-PROCESSOR                                         |    |

| 7.2 PORT            | CONFIGURATION                                       |    |

| 7.3 BAR T           | RANSLATION FOR REMOTE HOST DOMAIN                   |    |

|                     | VIRECT ADDRESS TRANSLATION (DAT)                    |    |

|                     | DDRESS LOOK-UP TRANSLATION (ALUT)                   |    |

|                     | D TRANSLATION                                       |    |

|                     | RANSLATION FOR MAIN HOST DOMAIN                     |    |

|                     | TCHPADS AND DOORBELLS                               |    |

| 8 DIRECT M          | IEMORY ACCESS                                       | 59 |

| 8.1 GENE            | RAL DESCRIPTION                                     | 59 |

|                     | CONFIGURATION                                       |    |

|                     | MA FUNCTIONS                                        |    |

| 8.2.1.1             | DMA MODE BIT DEFINITION                             | 60 |

| 8.2.1.2             | DMA MODE AND CD MODE                                |    |

| 8.2.1.3             | ENUMERATION                                         |    |

|                     | MA CONTROL REGISTER                                 |    |

| 8.2.2.1<br>8.2.2.2  | DMA DESCRIPTOR REGISTER<br>DMA OPERATIONAL REGISTER |    |

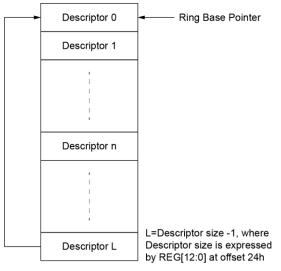

| 0                   | DESCRIPTORS AND TRANSFERS                           |    |

|                     | ESCRIPTORS                                          |    |

| 8.3.1.1             | INITIALIZATION                                      |    |

| 8.3.1.2             | OWNERSHIP                                           | 62 |

| 8.3.1.3             | PRE-FETCH                                           |    |

|                     | RANSFER                                             |    |

| 8.3.2.1<br>8.3.2.2  | LOCAL DOMAIN TRANSFER                               |    |

|                     | EXCEPTOR LAYOUT                                     |    |

| 8.3.3.1             | DOMAIN AND ADDRESS FIELD                            |    |

| 8.3.3.2             | TRANSFER COUNT FIELD                                |    |

| 8.3.3.3             | CONTROL FILED                                       | 64 |

| 8.3.3.4             | ERR FIELD                                           |    |

| 8.3.3.5             | ST FIELD                                            |    |

| 8.3.3.6<br>8.4 ERRO | CRC FIELD<br>R REPORTING AND HANDLING               |    |

|                     | RROR REPORTING                                      |    |

| 0.4.1 E.<br>8.4.1.1 | REPORTING VIA FUNCTION                              |    |

| 8.4.1.2             | REPORTING VIA CHANNEL                               |    |

| 8.4.1.3             | REPORTING VIA DESCRIPTOR                            | 66 |

|                     | RROR LOGGING                                        |    |

|                     | ATA INTEGRITY                                       |    |

| 8.4.4 E             | RROR HANDLING FOR UNCORRECTABLE ERROR DETECTED      | 67 |

| 8.4.4.           | 1 ERROR IN DATA BUFFER                                                | 67 |

|------------------|-----------------------------------------------------------------------|----|

| 8.4.4.           |                                                                       |    |

| 8.4.5            | ERROR HANDLING FOR DMA READ                                           | 67 |

| 9 REGIST         | FER DESCRIPTION                                                       | 68 |

| 9.1 RE           | GISTER TYPES                                                          | 68 |

|                  | GISTER ACCESS                                                         |    |

| 9.2.1            | PCI-COMPATIBLE CONFIGURATION MECHANISM                                |    |

| 9.2.1            | PCI EXPRESS ENHANCED CONFIGURATION ACCESS MECHANISM                   |    |

| 9.2.2            | DEVICE SPECIFIC MEMORY MAPPED CONFIGURATION ACCESS MECHANISM          |    |

|                  | ANSPARENT MODE CONFIGURATION REGISTERS                                |    |

| 9.3 TK           | VENDOR ID REGISTER – OFFSET 00h                                       |    |

| 9.3.1            | DEVICE ID REGISTER – OFFSET 00h                                       |    |

| 9.3.2<br>9.3.3   | COMMAND REGISTER – OFFSET 00h                                         |    |

| 9.3.3<br>9.3.4   | PRIMARY STATUS REGISTER – OFFSET 04h                                  |    |

| 9.3.4<br>9.3.5   | REVISION ID REGISTER – OFFSET 04h                                     |    |

| ,                | CLASS REGISTER – OFFSET 08h                                           |    |

| 9.3.6            |                                                                       |    |

| 9.3.7            | CACHE LINE REGISTER – OFFSET 0Ch                                      |    |

| 9.3.8            | PRIMARY LATENCY TIMER REGISTER – OFFSET 0Ch                           |    |

| 9.3.9            | HEADER TYPE REGISTER – OFFSET 0Ch.                                    |    |

| 9.3.10           | BASE ADDRESS 0 REGISTER – OFFSET 10h (Upstream Port Only)             |    |

| 9.3.11           | BASE ADDRESS 1 REGISTER – OFFSET 14h (Upstream Port Only)             |    |

| 9.3.12           | PRIMARY BUS NUMBER REGISTER – OFFSET 18h                              |    |

| 9.3.13           | SECONDARY BUS NUMBER REGISTER – OFFSET 18h                            |    |

| 9.3.14           | SUBORDINATE BUS NUMBER REGISTER – OFFSET 18h                          |    |

| 9.3.15           | SECONDARY LATENCY TIMER REGISTER – OFFSET 18h                         |    |

| 9.3.16           | I/O BASE ADDRESS REGISTER – OFFSET 1Ch                                |    |

| 9.3.17           | I/O LIMIT ADDRESS REGISTER – OFFSET 1Ch                               |    |

| <i>9.3.18</i>    | SECONDARY STATUS REGISTER – OFFSET 1Ch                                |    |

| 9.3.19           | MEMORY BASE ADDRESS REGISTER – OFFSET 20h                             |    |

| 9.3.20           | MEMORY LIMIT ADDRESS REGISTER – OFFSET 20h                            |    |

| 9.3.21           | PREFETCHABLE MEMORY BASE ADDRESS REGISTER – OFFSET 24h                | 78 |

| 9.3.22           | PREFETCHABLE MEMORY LIMIT ADDRESS REGISTER – OFFSET 24h               | 78 |

| 9.3.23           | PREFETCHABLE MEMORY BASE ADDRESS UPPER 32-BITS REGISTER – OFFSET 28h  | 78 |

| 9.3.24           | PREFETCHABLE MEMORY LIMIT ADDRESS UPPER 32-BITS REGISTER – OFFSET 2Ch | 79 |

| 9.3.25           | I/O BASE ADDRESS UPPER 16-BITS REGISTER – OFFSET 30h                  | 79 |

| 9.3.26           | I/O LIMIT ADDRESS UPPER 16-BITS REGISTER – OFFSET 30h                 | 79 |

| 9.3.27           | CAPABILITY POINTER REGISTER – OFFSET 34h                              | 79 |

| 9.3.28           | INTERRUPT LINE REGISTER – OFFSET 3Ch                                  | 79 |

| 9.3.29           | INTERRUPT PIN REGISTER – OFFSET 3Ch                                   | 79 |

| 9.3.30           | BRIDGE CONTROL REGISTER – OFFSET 3Ch                                  |    |

| 9.3.31           | POWER MANAGEMENT CAPABILITIES REGISTER – OFFSET 40h                   |    |

| 9.3.32           | POWER MANAGEMENT DATA REGISTER – OFFSET 44h                           |    |

| 9.3.33           | PPB SUPPORT EXTENSIONS REGISTER – OFFSET 44h                          |    |

| 9.3.34           | DATA REGISTER– OFFSET 44h                                             |    |

| 9.3.35           | MSI CAPABILITIES REGISTER – OFFSET 48h                                |    |

| 9.3.36           | MESSAGE ADDRESS REGISTER – OFFSET 4Ch                                 |    |

| 9.3.37           | MESSAGE UPPER ADDRESS REGISTER – OFFSET 50h                           |    |

| 9.3.38           | MESSAGE DATA REGISTER – OFFSET 54h                                    |    |

| 9.3.30           | MESSAGE DATA REGISTER – OFFSET 54n                                    |    |

| 9.3.39<br>9.3.40 | MESSAGE MASK REGISTER – OFFSET 500                                    |    |

| 9.3.40<br>9.3.41 | PCI EXPRESS CAPABILITIES REGISTER – OFFSET 5Ch                        |    |

| 9.3.41<br>9.3.42 | CAPABILITIES REGISTER – OFFSET 6Ch                                    |    |

|                  | DEVICE CONTROL REGISTER – OFFSET 70h                                  |    |

| 9.3.43           |                                                                       |    |

| 9.3.44           | DEVICE STATUS REGISTER – OFFSET 70h                                   | 84 |

| 9.3.45           | LINK CAPABILITIES REGISTER – OFFSET 74h                                                                                            | 84  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|

| 9.3.46           | LINK CONTROL REGISTER – OFFSET 78h                                                                                                 |     |

| 9.3.40<br>9.3.47 | LINK STATUS REGISTER – OFFSET 78h                                                                                                  |     |

| 9.3.47<br>9.3.48 | SLOT CAPABILITIES REGISTER – OFFSET 7Ch (Downstream Port Only)                                                                     |     |

| 9.3.48<br>9.3.49 |                                                                                                                                    |     |

|                  | SLOT CONTROL REGISTER – OFFSET 80h (Downstream Port Only)                                                                          |     |

| 9.3.50           | SLOT STATUS REGISTER – OFFSET 80h (Downstream Port Only)                                                                           |     |

| 9.3.51           | DEVICE CAPABILITIES REGISTER 2 – OFFSET 8Ch                                                                                        |     |

| 9.3.52           | DEVICE CONTROL REGISTER 2 – OFFSET 90h                                                                                             |     |

| 9.3.53           | DEVICE STATUS REGISTER 2 – OFFSET 90h                                                                                              |     |

| 9.3.54           | LINK CAPABILITIES REGISTER 2 – OFFSET 94h                                                                                          |     |

| 9.3.55           | LINK CONTROL REGISTER 2 – OFFSET 98h                                                                                               |     |

| 9.3.56           | LINK STATUS REGISTER 2 – OFFSET 98h                                                                                                |     |

| 9.3.57           | SLOT CAPABILITIES REGISTER 2 – OFFSET 9Ch                                                                                          | 90  |

| 9.3.58           | SLOT CONTROL REGISTER 2 – OFFSET A0h                                                                                               | 90  |

| 9.3.59           | SLOT STATUS REGISTER 2 – OFFSET A0h                                                                                                | 90  |

| 9.3.60           | SSID/SSVID CAPATILITIES REGISTER – OFFSET A4h                                                                                      |     |

| 9.3.61           | SUBSYSTEM VENDOR ID REGISTER – OFFSET A8h                                                                                          |     |

| 9.3.62           | SYSTEM ID REGISTER – OFFSET A8h                                                                                                    |     |

| 9.3.63           | MSI-X CAPATILITIES REGISTER – OFFSET B0h (Upstream Port Only)                                                                      |     |

| 9.3.64           | MSI-X TABLE OFFSET/TABLE BIR REGISTER – OFFSET B4h (Upstream Port Only)                                                            |     |

| 9.3.65           | MSI-X PBA OFFSET / PBA BIR REGISTER – OFFSET B8h (Upstream Port Only)                                                              |     |

| 9.3.66           | BAR 0 CONFIGURATION REGISTER – OFFSET E0h (Upstream Port Only)                                                                     |     |

| 9.3.67           | BAR 0 CONFIGURATION REGISTER – OFFSET Eon (Opstream Font Only)<br>BAR 0-1 CONFIGURATION REGISTER – OFFSET E4h (Upstream Port Only) |     |

| 9.3.68           |                                                                                                                                    |     |

| /10100           | PCI EXPRESS ADVANCED ERROR REPORTING ENHANCED CAPABILITY HEADER REGISTER                                                           |     |

|                  | $\Gamma 100h$                                                                                                                      |     |

| 9.3.69           | UNCORRECTABLE ERROR STATUS REGISTER – OFFSET 104h                                                                                  |     |

| 9.3.70           | UNCORRECTABLE ERROR MASK REGISTER – OFFSET 108h                                                                                    |     |

| 9.3.71           | UNCORRECTABLE ERROR SEVERITY REGISTER – OFFSET 10Ch                                                                                |     |

| 9.3.72           | CORRECTABLE ERROR STATUS REGISTER – OFFSET 110h                                                                                    |     |

| 9.3.73           | CORRECTABLE ERROR MASK REGISTER – OFFSET 114h                                                                                      |     |

| 9.3.74           | ADVANCE ERROR CAPABILITIES AND CONTROL REGISTER – OFFSET 118h                                                                      |     |

| 9.3.75           | HEADER LOG REGISTER – OFFSET From 11Ch to 128h                                                                                     |     |

| 9.3.76           | PCI EXPRESS VIRTUAL CHANNEL ENHANCED CAPABILITYHEADER REGISTER – OFFSET 1                                                          | 30h |

|                  | 96                                                                                                                                 |     |

| 9.3.77           | PORT VC CAPABILITY REGISTER 1 – OFFSET 134h                                                                                        | 96  |

| 9.3.78           | PORT VC CAPABILITY REGISTER 2 – OFFSET 138h                                                                                        | 96  |

| 9.3.79           | PORT VC CONTROL REGISTER – OFFSET 13Ch                                                                                             |     |

| 9.3.80           | PORT VC STATUS REGISTER – OFFSET 13Ch                                                                                              |     |

| 9.3.81           | VC RESOURCE CAPABILITY REGISTER (0) – OFFSET 140h                                                                                  |     |

| 9.3.82           | VC RESOURCE CONTROL REGISTER (0) – OFFSET 144h                                                                                     |     |

| 9.3.83           | VC RESOURCE STATUS REGISTER (0) – OFFSET 148h                                                                                      |     |

| 9.3.83<br>9.3.84 | DEVICE SERIAL NUMBER ENHANCED CAPABILITY HEADER REGISTER – OFFSET 1A0h                                                             | 90  |

| 9.3.84<br>9.3.85 | DEVICE SERIAL NUMBER ENHANCED CAI ABILITT HEADER REGISTER – OFFSET 1A0n<br>DEVICE SERIAL NUMBER LOWER DW REGISTER – OFFSET 1A4h    |     |

|                  | DEVICE SERIAL NUMBER LOWER DW REGISTER – OFFSET 1A4n<br>DEVICE SERIAL NUMBER HIGHER DW REGISTER – OFFSET 1A8h                      |     |

| 9.3.86           |                                                                                                                                    |     |

| 9.3.87           | PCI EXPRESS POWER BUDGETING ENHANCED CAPABILITY HEADER REGISTER – OFFSET                                                           |     |

| · · ·            | pstream Port Only)                                                                                                                 |     |

| 9.3.88           | DATA SELECT REGISTER – OFFSET 1B4h (Upstream Port Only)                                                                            |     |

| 9.3.89           | POWER BUDGETING DATA REGISTER – OFFSET 1B8h (Upstream Port Only)                                                                   |     |

| 9.3.90           | POWER BUDGET CAPABILITY REGISTER – OFFSET 1BCh (Upstream Port Only)                                                                |     |

| 9.3.91           | ACS ENHANCED CAPABILITY HEADER REGISTER – OFFSET 1C0h (Downstream Port Only)                                                       |     |

| 9.3.92           | ACS CAPABILITY REGISTER – OFFSET 1C4h (Downstream Port Only)                                                                       |     |

| 9.3.93           | EGRESS CONTROL VECTOR REGISTER – OFFSET 1C8h (Downstream Port Only)                                                                |     |

| 9.3.94           | MULTI-CAST ENHANCED CAPABILITY HEADER REGISTER – OFFSET 1D0h                                                                       | 100 |

| 9.3.95           | MULTI-CAST CAPABILITY REGISTER – OFFSET 1D4h                                                                                       | 100 |

| 9.3.96           | MULTI-CAST CONTROL REGISTER – OFFSET 1D4h                                                                                          | 100 |

|                  |                                                                                                                                    |     |

| 9.3.97             | MULTI-CAST BASE ADDRESS 0 REGISTER – OFFSET 1D8h                                                              |     |

|--------------------|---------------------------------------------------------------------------------------------------------------|-----|

| 9.3.98             | MULTI-CAST BASE ADDRESS 1 REGISTER – OFFSET 1DCh                                                              |     |

| 9.3.99             | MULTI-CAST RECEIVER REGISTER – OFFSET 1E0h                                                                    |     |

| 9.3.100            | MULTI-CAST RECEIVER UPPER 32-BITS REGISTER – OFFSET 1E4h                                                      |     |

| 9.3.101            | MULTI-CAST BLOCK ALL REGISTER – OFFSET 1E8h                                                                   |     |

| 9.3.102            | MULTI-CAST BLOCK ALL UPPER 32-BITS REGISTER – OFFSET 1ECh                                                     | 101 |

| 9.3.103            | MULTI-CAST BLOCK UNTRANSLATED REGISTER – OFFSET 1F0h                                                          |     |

| 9.3.104            | MULTI-CAST BLOCK UNTRANSLATED UPPER 32-BITS REGISTER – OFFSET 1F4h                                            |     |

| 9.3.105            | LTR EXTENDED CAPABILITY HEADER – OFFSET 200h (Upstream Port Only)                                             | 102 |

| 9.3.106            | MAX SNOOP LATENCY REGISTER – OFFSET 204h (Upstream Port Only)                                                 |     |

| 9.3.107            | MAX NO-SNOOP LATENCY REGISTER – OFFSET 204h (Upstream Port Only)                                              |     |

| 9.3.108            | SECONDARY PCI EXPRESS EXTENDED CAPABILITY HEADER – OFFSET 210h                                                |     |

| 9.3.109            | LINK CONTROL 3 REGISTER – OFFSET 214h                                                                         |     |

| 9.3.110            | LANE ERROR STATUS REGISTER – OFFSET 218h                                                                      |     |

| 9.3.111            | LANE EQUALIZATION CONTROL REGISTER – OFFSET 21Ch/22C/230h                                                     |     |

| 9.3.112            | DPC EXTENDED CAPABILITY HEADER – OFFSET 2A0h (Downstream Port Only)                                           |     |

| 9.3.112            | DPC CAPABILITY REGISTER – OFFSET 2A4h (Downstream Port Only)                                                  |     |

| 9.3.114            | DPC CONTROL REGISTER – OFFSET 2A4h (Downstream Port Only)                                                     |     |

| 9.3.115            | DPC STATUS REGISTER – OFFSET 2A8h (Downstream Port Only)                                                      |     |

| 9.3.116            | DPC ERROR SOURCE ID REGISTER – OFFSET 2A8h (Downstream Port Only)                                             |     |

| 9.3.117            | LI PM SUBSTATES ENHANCED CAPABILITY HEADER – OFFSET 2B0h                                                      |     |

| 9.3.117<br>9.3.118 | LI PM SUBSTATES ENHANCED CAFABILITT HEADER – OFFSET 2B0n<br>L1 PM SUBSTATES CAPABILITY REGISTER – OFFSET 2B4h |     |

| 9.3.118            | LI PM SUBSTATES CAPABILITI REGISTER – OFFSET 2B4n<br>L1 PM SUBSTATES CONTROL 1 REGISTER – OFFSET 2B8h         |     |

|                    |                                                                                                               |     |

| 9.3.120            | L1 PM SUBSTATES CONTROL 2 REGISTER – OFFSET 2BCh<br>VENDOR-SPECIFIC ENHANCED CAPABILITY HEADER – OFFSET 300h  |     |

| 9.3.121            |                                                                                                               |     |

| 9.3.122            | VENDOR-SPECIFIC HEADER – OFFSET 304h                                                                          |     |

| 9.3.123            | EEPROM CONTROL REGISTER – OFFSET 308h (Upstream Port Only)                                                    |     |

| 9.3.124            | EEPROM ADDRESS AND DATA REGISTER – OFFSET 30Ch (Upstream Port Only)                                           |     |

| 9.3.125            | DEBUGOUT CONTROL REGISTER – OFFSET 310h (Port 0 Only)                                                         |     |

| 9.3.126            | DEBUGOUT DATA REGISTER – OFFSET 314h (Port 0 Only)                                                            |     |

| 9.3.127            | I2C CONTROL AND STATUS REGISTER – OFFSET 318h (Port 0 Only)                                                   |     |

| 9.3.128            | GPIO 0-15 DIRECTION CONTROL REGISTER – OFFSET 31Ch (Port 0 Only)                                              |     |

| 9.3.129            | GPIO 16-31 DIRECTION CONTROL REGISTER – OFFSET 320h (Port 0 Only)                                             |     |

| 9.3.130            | GPIO INPUT DE-BOUNCE REGISTER – OFFSET 324h (Port 0 Only)                                                     |     |

| 9.3.131            | GPIO 0-15 INPUT DATA REGISTER – OFFSET 328h (Port 0 Only)                                                     |     |

| 9.3.132            | GPIO 16-31 INPUT DATA REGISTER – OFFSET 32Ch (Port 0 Only)                                                    |     |

| 9.3.133            | GPIO 0-15 OUTPUT DATA REGISTER – OFFSET 330h (Port 0 Only)                                                    |     |

| 9.3.134            | GPIO 16-31 OUTPUT DATA REGISTER – OFFSET 334h (Port 0 Only)                                                   | 113 |

| 9.3.135            | GPIO 0-31 INTERRUPT POLARITY REGISTER – OFFSET 338h (Port 0 Only)                                             | 113 |

| 9.3.136            | GPIO 0-31 INTERRUPT STATUS REGISTER – OFFSET 33Ch (Port 0 Only)                                               | 113 |

| 9.3.137            | GPIO 0-31 INTERRUPT MASK REGISTER – OFFSET 340h (Port 0 Only)                                                 | 113 |

| 9.3.138            | OPERATION MODE REGISTER – OFFSET 348h (Port 0 Only)                                                           | 114 |

| 9.3.139            | CLOCK BUFFER CONTROL REGISTER – OFFSET 34Ch (Port 0 Only)                                                     | 114 |

| 9.3.140            | LTSSM CSR 0 REGISTER – OFFSET 380h                                                                            | 115 |

| 9.3.141            | LTSSM CSR 1 REGISTER – OFFSET 384h                                                                            | 115 |

| 9.3.142            | LTSSM CSR 2 REGISTER – OFFSET 388h                                                                            | 115 |

| 9.3.143            | LTSSM CSR 3 REGISTER – OFFSET 38Ch                                                                            | 115 |

| 9.3.144            | LTSSM 0 REGISTER – OFFSET 390h                                                                                | 116 |

| 9.3.145            | LTSSM 1 REGISTER – OFFSET 394h                                                                                | 116 |

| 9.3.146            | LTSSM 2 REGISTER – OFFSET 398h                                                                                |     |

| 9.3.147            | LTSSM 3 REGISTER – OFFSET 39Ch                                                                                |     |

| 9.3.148            | LTSSM 4 REGISTER – OFFSET 3A0h                                                                                |     |

| 9.3.149            | LTSSM 5 REGISTER – OFFSET 3A4h                                                                                |     |

| 9.3.150            | LTSSM 6 REGISTER – OFFSET 3A8h                                                                                |     |

| 9.3.151            | LTSSM 7 REGISTER – OFFSET 3ACh                                                                                |     |

|                    |                                                                                                               |     |

| 9.3.152               | LTSSM 8 REGISTER – OFFSET 3B0h                                                                                                         |     |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|

| 9.3.153               | LTSSM 9 REGISTER – OFFSET 3B4h                                                                                                         |     |

| 9.3.154               | LTSSM 10 REGISTER – OFFSET 3B8h                                                                                                        |     |

| 9.3.155               | LTSSM 11 REGISTER – OFFSET 3BCh                                                                                                        |     |

| 9.3.156               | LTSSM 12 REGISTER – OFFSET 3C0h                                                                                                        |     |

| 9.3.157               | LTSSM 13 REGISTER – OFFSET 3C4h                                                                                                        |     |

| 9.3.158               | LTSSM 14 REGISTER – OFFSET 3C8h                                                                                                        |     |

| 9.3.159               | LTSSM 15 REGISTER – OFFSET 3CCh                                                                                                        |     |

| 9.3.160               | DLL CSR 0 REGISTER – OFFSET 420h                                                                                                       |     |

| 9.3.161               | DLL CSR 1 REGISTER – OFFSET 424h                                                                                                       |     |

| 9.3.162               | DLL CSR 2 REGISTER – OFFSET 428h                                                                                                       |     |

| 9.3.163               | DLL CSR 3 REGISTER – OFFSET 42Ch                                                                                                       |     |

| 9.3.164               | DLL CSR 4 REGISTER – OFFSET 430h                                                                                                       |     |

| 9.3.165               | DLL CSR 4 REGISTER – OFFSET 434h                                                                                                       |     |

| 9.3.166               | DLL CSR 6 REGISTER – OFFSET 438h                                                                                                       |     |

| 9.3.160<br>9.3.167    | DLL CSR 7 REGISTER – OFFSET 43Ch                                                                                                       |     |

| 9.3.107<br>9.3.168    | DLL CSR / REGISTER – OFFSET 43Ch<br>DLL CSR 8 REGISTER – OFFSET 440h                                                                   |     |

| 9.3.108<br>9.3.169    | DLL CSR 8 REGISTER – OFFSET 4440n<br>DLL CSR 9 REGISTER – OFFSET 444h                                                                  |     |

| 9.3.109<br>9.3.170    | DLL CSR 9 REGISTER – OFFSET 444n<br>DLL CSR 10 REGISTER – OFFSET 448h                                                                  |     |

|                       |                                                                                                                                        |     |

| 9.3.171               | DLL CSR 11 REGISTER – OFFSET 44Ch                                                                                                      |     |

| 9.3.172               | DLL CSR 12 REGISTER – OFFSET 450h                                                                                                      |     |

| 9.3.173               | DLL CSR 13 REGISTER – OFFSET 454h                                                                                                      |     |

| 9.3.174               | DLL CSR 14 REGISTER – OFFSET 458h                                                                                                      |     |

| 9.3.175               | DLL CSR 15 REGISTER – OFFSET 45Ch                                                                                                      |     |

| 9.3.176               | DLL CSR 16 REGISTER – OFFSET 460h                                                                                                      |     |

| 9.3.177               | DLL CSR 17 REGISTER – OFFSET 464h                                                                                                      |     |

| 9.3.178               | DLL CSR 18 REGISTER – OFFSET 468h                                                                                                      |     |

| 9.3.179               | DLL CSR 19 REGISTER – OFFSET 46Ch                                                                                                      |     |

| 9.3.180               | LA DEBUG REGISTER – OFFSET 470h                                                                                                        |     |

| 9.3.181               | TL CSR 0 REGISTER – OFFSET 4C0h                                                                                                        |     |

| 9.3.182               | TL CSR 1 REGISTER – OFFSET 4C4h                                                                                                        |     |

| 9.3.183               | TL CSR 2 REGISTER – OFFSET 4C8h                                                                                                        |     |

| 9.3.184               | TL CSR 3 REGISTER – OFFSET 4CCh (Port 0 Only)                                                                                          | 129 |

| 9.3.185               | TL CSR 4 REGISTER – OFFSET 4D0h                                                                                                        |     |

| 9.3.186               | DEVICE CONFIGURATION 0 REGISTER – OFFSET 504h (Port 0 Only)                                                                            | 129 |

| 9.3.187               | DEVICE CONFIGURATION 1 REGISTER – OFFSET 508h (Port 0 Only)                                                                            | 130 |

| 9.3.188               | DEVICE CONFIGURATION 2 REGISTER – OFFSET 50Ch (Port 0 Only)                                                                            | 130 |

| 9.3.189               | DEVICE CLOCK EXTERNAL CONTROL REGISTER – OFFSET 510h (Port 0 Only)                                                                     | 131 |

| 9.3.190               | DEVICE SRIS MODE EXTERNAL CONTROL REGISTER – OFFSET 514h (Port 0 Only)                                                                 |     |

| 9.3.191               | DEVICE COMM REFCLK MODE EXTERNAL CONTROL REGISTER – OFFSET 518h (Port                                                                  |     |

|                       | 131                                                                                                                                    |     |

| 9.3.192               | MBIST CFG CONTROL REGISTER – OFFSET 51Ch (Port 0 Only)                                                                                 | 132 |

| 9.3.193               | MBIST CFG STATUS REGISTER – OFFSET 520h (Port 0 Only)                                                                                  |     |

| 9.3.194               | NOC BIST CONTROL REGISTER – OFFSET 524h (Port 0 Only)                                                                                  |     |

| 9.3.194<br>9.3        | EXTERNAL LOOPBACK PRBS CONTROL REGISTER – OFFSET 528h (Port 0 Only)                                                                    |     |

| 9.3.196               | PHY SRAM PROGRAM 0 REGISER – OFFSET 52Ch (Port 0 Only)                                                                                 |     |

| 9.3.197               | PHY SRAM PROGRAM 1 REGISTER – OFFSET 530h (Port 0 Only)                                                                                |     |

| 9.3.198               | FAILOVER CONTROL REGISTER – OFFSET 534h (Port 0 Only)                                                                                  |     |

| 9.3.198<br>9.3.199    | THERMAL SENSOR INT MASK AND STATUS REGISTER – OFFSET 538h (Port 0 Only)                                                                |     |

| 9.3.199<br>9.3.200    | THERMAL SENSOR INT MASK AND STATUS REGISTER – OFFSET 536h (Fort 0 Only)<br>THERMAL SENSOR CONTROL REGISTER – OFFSET 53Ch (Port 0 Only) |     |

| 9.3.200<br>9.3.201    | DEVICE ELASTIC BUFFER EMPTY MODE EXTERNAL CONTROL REGISTER – OFFSET                                                                    |     |

|                       |                                                                                                                                        |     |

| (Port 0 0)<br>9.3.202 | ily)                                                                                                                                   |     |

|                       | DEVICE MISC REGISTER – OFFSET 544h (Port 0 Only)                                                                                       |     |

| 9.3.203<br>9.3.204    | SWITCH DOMAIN MODE CONTROL REGISTER – OFFSET 558h (Port 0 Only)<br>PORT CLOCK CONTROL REGISTER – OFFSET 55Ch (Port 0 Only)             |     |

| U 3 /11/1             | $P \cup R \cup U \cup V \cup R \cup U \cup R \cup U \cup R = U R R A F U A A A A A A A A A A A A A A A A A$                            | 111 |

| 9.3.205            | PERFORMANCE COUNTER CONTROL REGISTER – OFFSET 56Ch                                                                                                     | 135 |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 9.3.206            | PHY SOURCE SELECT REGISTER – OFFSET 570h                                                                                                               |     |

| 9.3.207            | NIC CTRL 0 REGISTER – OFFSET 5A0h (Port 0 Only)                                                                                                        |     |

| 9.3.208            | NIC CTRL 1 REGISTER – OFFSET 5A4h (Port 0 Only)                                                                                                        |     |

| 9.3.209            | NIC CTRL 2 REGISTER – OFFSET 5A8h (Port 0 Only)                                                                                                        |     |

| 9.3.210            | NIC CTRL 3 REGISTER – OFFSET 5ACh (Port 0 Only)                                                                                                        |     |

| 9.3.211            | NIC CTRL 4 REGISTER – OFFSET 5B0h (Port 0 Only)                                                                                                        |     |

| 9.3.212            | CR RW CTRL AND STATUS REGISTER – OFFSET 5C0h (Port 0 Only)                                                                                             |     |

| 9.3.212            | CR CTRL 0 REGISTER – OFFSET 5C4h (Port 0 Only)                                                                                                         |     |

| 9.3.213            | CR CTRL 1 REGISTER – OFFSET 5C8h (Port 0 Only)                                                                                                         |     |

| 9.3.214            | CR CTRL 2 REGISTER – OFFSET 5CCh (Port 0 Only)                                                                                                         |     |

| 9.3.215            | CR CTRL 3 REGISTER – OFFSET 5D0h (Port 0 Only)                                                                                                         |     |

| 9.3.210            | THERMAL SENSOR TEST REGISTER – OFFSET 5D4h (Port 0 Only)                                                                                               |     |

| 9.3.217<br>9.3.218 | THERMAL SENSOR TEST REGISTER – OFFSET 5D4n (Pon 0 Only)<br>THERMAL SENSOR CTRL 0 REGISTER – OFFSET 5D8h (Port 0 Only)                                  |     |

| 9.3.218<br>9.3.219 | THERMAL SENSOR CTRL 0 REGISTER – OFFSET 5D6n (Port 0 Only)<br>THERMAL SENSOR CTRL 1 REGISTER – OFFSET 5DCh (Port 0 Only)                               |     |

|                    |                                                                                                                                                        |     |

| 9.3.220<br>9.3.221 | THERMAL SENSOR CTRL 2 REGISTER – OFFSET 5E0h (Port 0 Only)                                                                                             |     |

|                    | INGRESS COMPLETION TLP PACKET COUNT[31:0] REGISTER – OFFSET 600h                                                                                       |     |

| 9.3.222            | INGRESS COMPLETION TLP PACKET COUNT[47:32] REGISTER – OFFSET 604h                                                                                      |     |

| 9.3.223            | INGRESS COMPLETION TLP PAYLOAD BYTE COUNT[31:0] REGISTER – OFFSET 608h                                                                                 |     |

| 9.3.224            | INGRESS COMPLETION TLP PAYLOAD BYTE COUNT[47:32] REGITER – OFFSET 60Ch                                                                                 |     |

| 9.3.225            | INGRESS POST TLP PACKET COUNT[31:0] REGISTER – OFFSET 610h                                                                                             |     |

| 9.3.226            | INGRESS POST TLP PACKET COUNT[47:32] REGISTER – OFFSET 614h                                                                                            |     |

| 9.3.227            | INGRESS POST TLP PAYLOAD BYTE COUNT[31:0] REGISTER – OFFSET 618h                                                                                       |     |

| 9.3.228            | INGRESS POST TLP PAYLOAD BYTE COUNT[47:32] REGISTER – OFFSET 61Ch                                                                                      |     |

| 9.3.229            | INGRESS BAD TLP PACKET COUNT[31:0] REGISTER – OFFSET 620h                                                                                              |     |

| 9.3.230            | INGRESS NON-POST TLP PACKET COUNT[31:0] REGISTER – OFFSET 628h                                                                                         |     |

| 9.3.231            | INGRESS NON-POST TLP PACKET COUNT[47:32] REGISTER – OFFSET 62Ch                                                                                        |     |

| 9.3.232            | EGRESS COMPLETION TLP PACKET COUNT[31:0] REGISTER - OFFSET 630h                                                                                        |     |

| 9.3.233            | EGRESS COMPLETION TLP PACKET COUNT[47:32] REGISTER – OFFSET 634h                                                                                       |     |

| 9.3.234            | EGRESS COMPLETION TLP PAYLOAD BYTE COUNT[31:0] REGISTER – OFFSET 638h                                                                                  |     |

| 9.3.235            | EGRESS COMPLETION TLP PAYLOAD BYTE COUNT[47:32] REGISTER – OFFSET 63Ch.                                                                                |     |

| 9.3.236            | EGRESS POST TLP PACKET COUNT[31:0] REGISTER – OFFSET 640h                                                                                              |     |

| 9.3.237            | EGRESS POST TLP PACKET BYTE COUNT[47:32] REGISTER – OFFSET 644h                                                                                        |     |

| 9.3.238            | EGRESS POST TLP PAYLOAD BYTE COUNT[31:0] REGISTER – OFFSET 648h                                                                                        |     |

| 9.3.239            | EGRESS POST TLP PAYLOAD BYTE COUNT[47:32] REGISTER – OFFSET 64Ch                                                                                       | 142 |

| 9.3.240            | EGRESS ERROR TLP PACKET COUNT[15:0] REGISTER – OFFSET 650h                                                                                             |     |

| 9.3.241            | EGRESS ERROR TLP PAYLOAD BYTE COUNT[47:32] REGISTER – OFFSET 654h                                                                                      | 142 |

| 9.3.242            | EGRESS NON-POST TLP PACKET COUNT[31:0] REGISTER – OFFSET 658h                                                                                          | 142 |

| 9.3.243            | EGRESS NON-POST TLP PACKET COUNT[47:32] REGISTER – OFFSET 65Ch                                                                                         | 143 |

| 9.3.244            | TL/DLL/MAC/PHY ERROR TYPE SEL REGISTER – OFFSET 660h                                                                                                   | 143 |

| 9.3.245            | TL/DLL/MAC/PHY ERROR COUNT 0 REGISTER – OFFSET 664h                                                                                                    | 145 |

| 9.3.246            | TL/DLL/MAC/PHY ERROR COUNT 1 REGISTER – OFFSET 668h                                                                                                    | 145 |

| 9.3.247            | TL/DLL/MAC/PHY ERROR COUNT 2 REGISTER – OFFSET 66Ch                                                                                                    | 145 |

| 9.3.248            | TL/DLL/MAC/PHY ERROR MASK 0 REGISTER – OFFSET 670h                                                                                                     | 145 |

| 9.3.249            | TL/DLL/MAC/PHY ERROR MASK 1 REGISTER – OFFSET 674h                                                                                                     | 145 |

| 9.3.250            | TL/DLL/MAC/PHY ERROR MASK 2 REGISTER – OFFSET 678h                                                                                                     | 145 |

| 9.3.251            | INGRESS ERROR COUNTER ENABLE REGISTER – OFFSET 67Ch                                                                                                    | 145 |

| 9.3.252            | TRIGGER 1 MASK REGISTER – OFFSET 700h (Port 0 Only)                                                                                                    |     |

| 9.3.253            | TRIGGER 2 MASK REGISTER – OFFSET 704h (Port 0 Only)                                                                                                    |     |

| 9.3.254            | PATTERN 1 SETTING REGISTER – OFFSET 708h (Port 0 Only)                                                                                                 |     |

| 9.3.255            | PATTERN 2 SETING REGISTER – OFFSET 70Ch (Port 0 Only)                                                                                                  |     |

| 9.3.256            | TRIGGER 1 DEBUG_OUT MODE SELECTION REGISTER – OFFSET 710h (Port 0 Only)                                                                                |     |

| 9.3.257            | TRIGGER 2 DEBUG_OUT MODE SELECTION REGISTER – OFFSET 714h (Port 0 Only)                                                                                |     |

|                    |                                                                                                                                                        |     |

| 9.3.259            |                                                                                                                                                        |     |

| 9.3.258            | TRIGGER 1 AND/OR CONDITION SELECTION REGISTER – OFFSET 718h (Port 0 Only)<br>TRIGGER 2 AND/OR CONDITION SELECTION REGISTER – OFFSET 71Ch (Port 0 Only) | 1   |

| 9.3.260            | TRIGGER SELECT REGISTER – OFFSET 720h (Port 0 Only)                                   | 147 |

|--------------------|---------------------------------------------------------------------------------------|-----|

| 9.3.261            | TRIGGER POSITION SELECT REGISTER – OFFSET 724h (Port 0 Only)                          |     |

| 9.3.262            | TRIGGER COUNTER SETTING REGISTER – OFFSET 72Ch (Port 0 Only)                          |     |

| 9.3.262            | TRIGGER START REGISTER – OFFSET 730h (Port 0 Only)                                    |     |

| 9.3.263            | READ WAVEFORM DATA REGISTER – OFFSET 734h (Port 0 Only)                               |     |

| 9.3.204<br>9.3.265 | SAMPLE RATE SETTING REGISTER – OFFSET 734h (Port 0 Only)                              |     |

|                    |                                                                                       |     |

| 9.3.266            | WAVEFORM OUTPUT PORT SELECT REGISTER – OFFSET 73Ch (Port 0 Only)                      |     |

| 9.3.267            | WAVEFORM READ EVENT RESET REGISTER – OFFSET 748h (Port 0 Only)                        |     |

| 9.3.268            | DUMP MEMORY TO GPIO RATE CONTROL REGISTER – OFFSET 74Ch (Port 0 Only)                 |     |

| 9.3.269            | DUMP WAVEFORM START REGISTER – OFFSET 750h (Port 0 Only)                              |     |

| 9.3.270            | FREE RUN BUTTON REGISTER – OFFSET 754h (Port 0 Only)                                  |     |

|                    | LEP CONFIGURATION REGISTERS                                                           |     |

| 9.4.1              | VENDOR ID REGISTER – OFFSET 00h                                                       |     |

| 9.4.2              | DEVICE ID REGISTER – OFFSET 00h                                                       |     |

| 9.4.3              | COMMAND REGISTER – OFFSET 04H                                                         |     |

| 9.4.4              | PRIMARY STATUS REGISTER – OFFSET 04H                                                  | 156 |

| 9.4.5              | REVISION REGISTER – OFFSET 08H                                                        | 156 |

| 9.4.6              | CLASS REGISTER – OFFEST 08H                                                           | 156 |

| 9.4.7              | CACHE LINE REGISTER – OFFSET 0Ch                                                      | 156 |

| 9.4.8              | PRIMARY LATENCY TIMER REGISTER – OFFSET 0Ch                                           | 157 |

| 9.4.9              | HEADER TYPE REGISTER – OFFSET 0Ch                                                     |     |

| 9.4.10             | BAR 0 REGISTER – OFFSET 10h                                                           |     |

| 9.4.11             | BAR 1 REGISTER – OFFSET 14h                                                           |     |

| 9.4.12             | BAR 2 REGISTER – OFFSET 18h                                                           |     |

| 9.4.13             | BAR 3 REGISTER – OFFSET 1Ch                                                           |     |

| 9.4.14             | BAR 4 REGISTER – OFFSET 20h                                                           |     |

| 9.4.14<br>9.4.15   | BAR 5 REGISTER – OFFSET 24h                                                           |     |

| 9.4.16             | SSVID REGISTER – OFFSET 2Ch                                                           |     |

| 9.4.10<br>9.4.17   | SSVID REGISTER – OFFSET 2Ch                                                           |     |

|                    |                                                                                       |     |

| 9.4.18             | CAPABILITY POINTER REGISTER – OFFSET 34h                                              |     |

| 9.4.19             | INTERRUPT LINE REGISTER – OFFSET 3Ch                                                  |     |

| 9.4.20             | INTERRUPT PIN REGISTER – OFFSET 3Ch                                                   |     |

| 9.4.21             | POWER MANAGEMENT CAPABILITIES REGISTER – OFFSET 40h                                   |     |

| 9.4.22             | POWER MANAGEMENT DATA REGISTER – OFFSET 44h                                           |     |

| 9.4.23             | PPB SUPPORT EXTENSIONS REGISTER – OFFSET 44h                                          |     |

| 9.4.24             | DATA REGISTER– OFFSET 44h                                                             |     |

| 9.4.25             | MSI CAPABILITIES REGISTER – OFFSET 48h                                                |     |

| 9.4.26             | MESSAGE ADDRESS REGISTER – OFFSET 4Ch                                                 |     |

| 9.4.27             | MESSAGE UPPER ADDRESS REGISTER – OFFSET 50h                                           |     |

| 9.4.28             | MESSAGE DATA REGISTER – OFFSET 54h                                                    | 161 |

| 9.4.29             | MESSAGE MASK REGISTER – OFFSET 58h                                                    | 162 |

| 9.4.30             | MESSAGE PENDING REGISTER – OFFSET 5Ch                                                 | 162 |

| 9.4.31             | PCI EXPRESS CAPABILITIES REGISTER – OFFSET 68h                                        | 162 |

| 9.4.32             | DEVICE CAPABILITIES REGISTER – OFFSET 6Ch                                             | 162 |

| 9.4.33             | DEVICE CONTROL REGISTER – OFFSET 70h                                                  | 163 |

| 9.4.34             | DEVICE STATUS REGISTER – OFFSET 70h                                                   |     |

| 9.4.35             | LINK CAPABILITIES REGISTER – OFFSET 74h                                               |     |

| 9.4.36             | LINK CONTROL REGISTER – OFFSET 78h                                                    |     |

| 9.4.37             | LINK STATUS REGISTER – OFFSET 78h                                                     |     |

| 9.4.38             | SLOT CAPABILITIES REGISTER – OFFSET 7Ch                                               |     |

| 9.4.39             | SLOT CONTROL REGISTER – OFFSET 80h                                                    |     |

| 9.4.39<br>9.4.40   | SLOT CONTROL REGISTER – OFFSET 80h                                                    |     |

| 9.4.40<br>9.4.41   | DEVICE CAPABILITIES REGISTER 2 – OFFSET 8Ch                                           |     |

| 9.4.41<br>9.4.42   | DEVICE CAFABILITIES REGISTER 2 – OFFSET 8Ch<br>DEVICE CONTROL REGISTER 2 – OFFSET 90h |     |

| 9.4.42<br>9.4.43   | DEVICE CONTROL REGISTER 2 – OFFSET 90n<br>DEVICE STATUS REGISTER 2 – OFFSET 90h       |     |

| 9.4.43             | DEVICE STATUS REGISTER 2 = OFFSET 90%                                                 |     |

| 9.4.44                                                                                                                                                                                                                                                                                       | LINK CAPABILITIES REGISTER 2 – OFFSET 94h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 166                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|