Datasheet January 2018 Revision 3

A Product Line of Diodes Incorporated

1545 Barber Lane Milpitas, CA 95035 Telephone: 408-232-9100 FAX: 408-434-1040 Internet: <u>http://www.diodes.com</u>

A Product Line of Diodes Incorporated

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

A. Life support devices or systems are devices or systems which:

1. are intended to implant into the body, or

2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the

failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devicesor systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated

www.diodes.com

# **REVISION HISTORY**

| DATE       | <b>REVISION #</b> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05/27/2009 | 0.1               | Preliminary Datasheet                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 09/15/2009 | 0.2               | Updated Section 6.3 (I/O Limit Register – Offset 1Ch, Interrupt Line Register – Offset 3Ch,<br>Arbiter Enable Register – Offset 48h, Memory ReadSmart Range Control Register – Offset<br>58h, Upstream Memory Read/Write Control Register – Offset 68h, XPIP Configuration<br>Register 1 – Offset D0h)                                                                                                                                           |

|            |                   | Updated Section 12 IEEE 1149.1 Compatible JTAG Controller (Removed TRST_L)<br>Updated Table 14-2 DC Electrical Characteristics (VDDA)                                                                                                                                                                                                                                                                                                            |

| 07/26/2010 | 0.3               | Updated Section 2 Pin Definitions (Pin 22 to NC)<br>Updated Section 6.3 PCI Configuration Registers (Offset 40h, 44h, 6Ch, A4h, D0h, D4h)<br>Updated VDDC and VDDA voltage to 1.1V (Section 2.7, Table 14-2)<br>Updated Temperature Support Range from Extended Commercial to Industrial                                                                                                                                                         |

| 01/14/2011 | 0.3g              | Updated DC Spec Parameters                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 08/19/2011 | 1.0               | Updated Figure 15-1 Package outline drawing<br>Datasheet Released                                                                                                                                                                                                                                                                                                                                                                                |

| 09/7/2011  | 1.1               | Updated VDDC and VDDA voltage to 1.0V (Section 2.7, Table 14-2)                                                                                                                                                                                                                                                                                                                                                                                  |

| 05/27/2013 | 1.2               | Remove Figure 8-2 Topology of internal clock generator and internal clock buffering –<br>external feedback mode<br>Remove Figure 8-4 Topology of external clock generator and internal clock buffering –<br>external feedback mode<br>Updated VDDC and VDDA voltage to 1.15V (retroactive notice in January 2016)                                                                                                                                |

| 07/24/2014 | 1.3               | Remove NC and pin 22 from Section 2.6 and added pin 22 to Section 2.7 under pin name VSS                                                                                                                                                                                                                                                                                                                                                         |

| 04/21/2016 | 1.4               | Updated Section 2.5 JTAG Boundary Scan Signals                                                                                                                                                                                                                                                                                                                                                                                                   |

| 01/23/2017 | 1.5               | Updated Logo<br>Updated Section 2.7 Power and Ground Pins<br>Updated Section 2.8 Pin Assignments<br>Updated Section 14.1 Absolute Maximum Ratings<br>Updated Section 14.2 DC Specifications<br>Added Section 14.4 Operating Ambient Temperature<br>Added Table 14-4 PCI Express Interface - Differential Transmitter (TX) Output<br>Characteristics<br>Added Table 14-5 PCI Express Interface - Differential Receiver (RX) Input Characteristics |

| 09/27/2017 | 2                 | Added Section 14 Power Sequencing<br>Updated Section 17 Ordering Information<br>Revision numbering system changed to whole number                                                                                                                                                                                                                                                                                                                |

| 01/18/2018 | 3                 | Fix converted PDF file<br>Added Figure 16-2 Part Marking<br>Updated Section 17 Ordering Information<br>Updated Table 15-1 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                               |

# PREFACE

The datasheet of PI7C9X113SL will be enhanced periodically when updated information is available. The technical information in this datasheet is subject to change without notice. This document describes the functionalities of PI7C9X113SL (PCI Express Bridge) and provides technical information for designers to design their hardware using PI7C9X113SL.

# **TABLE OF CONTENTS**

| 1 | INT             | RODUCTION                                                                                             | 10 |

|---|-----------------|-------------------------------------------------------------------------------------------------------|----|

|   | 1.2             | INDUSTRY SPECIFICATION COMPLIANCE<br>GENERAL FEATURES<br>PCI EXPRESS FEATURES                         | 11 |

|   |                 | PCI FEATURES                                                                                          |    |

| 2 |                 | DEFINITIONS                                                                                           |    |

| - |                 |                                                                                                       |    |

|   |                 | SIGNAL TYPES<br>PCI EXPRESS SIGNALS                                                                   |    |

|   |                 | PCI EXPRESS SIGNALS                                                                                   |    |

|   |                 | MODE SELECT AND STRAPPING SIGNALS                                                                     |    |

|   |                 | JTAG BOUNDARY SCAN SIGNALS                                                                            |    |

|   |                 | MISCELLANEOUS SIGNALS                                                                                 |    |

|   |                 | POWER AND GROUND PINS                                                                                 |    |

|   |                 | PIN ASSIGNMENTS                                                                                       |    |

|   |                 |                                                                                                       |    |

| 3 | MOI             | DE SELECTION AND PIN STRAPPING                                                                        | 17 |

|   | 3.1             | FUNCTIONAL MODE SELECTION                                                                             | 17 |

|   | 3.2             | PIN STRAPPING                                                                                         | 17 |

| 4 | TRA             | NSPARENT AND FORWARD BRIDGING                                                                         | 18 |

|   | 4.1             | TRANSPARENT MODE                                                                                      | 18 |

|   |                 | FORWARD BRDIGE                                                                                        |    |

| 5 |                 | EXPRESS FUNCTIONAL OVERVIEW                                                                           |    |

| • |                 |                                                                                                       |    |

|   |                 | TLP STRUCTURE                                                                                         |    |

|   |                 | VIRTUAL ISOCHRONOUS OPERATION                                                                         |    |

| 6 | CON             | NFIGURATION REGISTER ACCESS                                                                           | 21 |

|   |                 | CONFIGURATION REGISTER MAP                                                                            |    |

|   | 6.2             | PCI EXPRESS EXTENDED CAPABILITY REGISTER MAP                                                          | 23 |

|   |                 | PCI CONFIGURATION REGISTERS                                                                           |    |

|   | 6.3.1           | VENDOR ID – OFFSET 00h                                                                                |    |

|   | 6.3.2           | DEVICE ID – OFFSET 00h<br>COMMAND REGISTER – OFFSET 04h                                               |    |

|   | 6.3.3<br>6.3.4  | PRIMARY STATUS REGISTER – OFFSET 04h                                                                  |    |

|   | 6.3.5           | REVISION ID REGISTER – OFFSET 08h                                                                     |    |

|   | 6.3.6           | CLASS CODE REGISTER – OFFSET 08h                                                                      | 26 |

|   | 6.3.7           | CACHE LINE SIZE REGISTER – OFFSET 0Ch                                                                 |    |

|   | 6.3.8           | PRIMARY LATENCY TIMER REGISTER – OFFSET 0Ch                                                           |    |

|   | 6.3.9<br>6.3.10 | <ul> <li>HEADER TYPE REGISTER – OFFSET 0Ch</li> <li>RESERVED REGISTERS – OFFSET 10h TO 17h</li> </ul> |    |

|   | 6.3.11          |                                                                                                       |    |

|   | 6.3.12          |                                                                                                       |    |

| 6.3.13           | SUBORDINATE BUS NUMBER REGISTER – OFFSET 18h                                                                             |    |

|------------------|--------------------------------------------------------------------------------------------------------------------------|----|

| 6.3.14           | SECONDARY LATENCY TIME REGISTER – OFFSET 18h                                                                             |    |

| 6.3.15           | I/O BASE REGISTER – OFFSET 1Ch                                                                                           |    |

| 6.3.16           | I/O LIMIT REGISTER – OFFSET 1Ch                                                                                          |    |

| 6.3.17           | SECONDARY STATUS REGISTER – OFFSET 1Ch                                                                                   |    |

| 6.3.18           | MEMORY BASE REGISTER – OFFSET 20h                                                                                        |    |

| 6.3.19           | MEMORY LIMIT REGISTER – OFFSET 20h                                                                                       |    |

| 6.3.20           | PREFETCHABLE MEMORY BASE REGISTER – OFFSET 24h                                                                           |    |

| 6.3.21           | PREFETCHABLE MEMORY LIMIT REGISTER – OFFSET 24h                                                                          |    |

| 6.3.22           | PREFETCHABLE BASE UPPER 32-BIT REGISTER – OFFSET 28h                                                                     |    |

| 6.3.23           | PREFETCHABLE LIMIT UPPER 32-BIT REGISTER – OFFSET 2Ch                                                                    |    |

| 6.3.24           | I/O BASE UPPER 16-BIT REGISTER – OFFSET 30h                                                                              |    |

| 6.3.25           | I/O LIMIT UPPER 16-BIT REGISTER – OFFSET 30h                                                                             |    |

| 6.3.26           | CAPABILITY POINTER – OFFSET 34h                                                                                          |    |

| 6.3.27           | EXPANSION ROM BASE ADDRESS REGISTER – OFFSET 38h                                                                         |    |

| 6.3.28           | INTERRUPT LINE REGISTER – OFFSET 3Ch                                                                                     |    |

| 6.3.29           | INTERRUPT PIN REGISTER – OFFSET 3Ch                                                                                      |    |

| 6.3.30           | BRIDGE CONTROL REGISTER – OFFSET 3Ch                                                                                     |    |

| 6.3.31           | PCI DATA PREFETCHING CONTROL REGISTER – OFFSET 40h                                                                       |    |

| 6.3.32           | CHIP CONTROL 0 REGISTER – OFFSET 40h                                                                                     |    |

| 6.3.33           | RESERVED REGISTER – OFFSET 44h                                                                                           |    |

| 6.3.34           | ARBITER ENABLE REGISTER – OFFSET 44n                                                                                     |    |

| 6.3.34<br>6.3.35 | ARBITER MODE REGISTER – OFFSET 48h                                                                                       |    |

| 6.3.36           | ARBITER PRIORITY REGISTER – OFFSET 48h                                                                                   |    |

|                  | RESERVED REGISTERS – OFFSET 46n                                                                                          |    |

| 6.3.37           | MEMORY READSMART BASE LOWER 32-Bit REGISTER 1 – OFFSET 50h                                                               |    |

| 6.3.38           | MEMORY READSMART BASE LOWER 52-Bit REGISTER 1 – OFFSET 50n<br>MEMORY READSMART BASE UPPER 32-Bit REGISTER 1 – OFFSET 54h |    |

| 6.3.39           | MEMORY READSMART BASE UPPER 52-Bit REGISTER 1 – OFFSET 54n<br>MEMORY READSMART RANGE CONTROL REGISTER 1 – OFFSET 58h     |    |

| 6.3.40           | MEMORY READSMART RANGE CONTROL REGISTER 1 – OFFSET 58n<br>MEMORY READSMART BASE LOWER 32-Bit REGISTER 2 – OFFSET 5Ch     |    |

| 6.3.41           |                                                                                                                          |    |

| 6.3.42           | MEMORY READSMART BASE UPPER 32-Bit REGISTER 2 – OFFSET 60h                                                               |    |

| 6.3.43           | MEMORY READSMART RANGE SIZE REGISTER 2 – OFFSET 64h                                                                      |    |

| 6.3.44           | UPSTREAM MEMORY READ/WRITE CONTROL REGISTER – OFFSET 68h                                                                 |    |

| 6.3.45           | PHY TRANSMIT/RECEIVE CONTROL REGISTER – OFFSET 6Ch                                                                       |    |

| 6.3.46           | EEPROM AUTOLOAD CONTROL/STATUS REGISTER – OFFSET 70h                                                                     |    |

| 6.3.47           | RESERVED REGISTER – OFFSET 74h                                                                                           |    |

| 6.3.48           | GPIO DATA AND CONTROL REGISTER – OFFSET 78h                                                                              |    |

| 6.3.49           | RESERVED REGISTER – OFFSET 7Ch                                                                                           |    |

| 6.3.50           | PCI-X CAPABILITY ID REGISTER – OFFSET 80h                                                                                |    |

| 6.3.51           | NEXT CAPABILITY POINTER REGISTER – OFFSET 80h                                                                            |    |

| 6.3.52           | PCI-X SECONDARY STATUS REGISTER – OFFSET 80h                                                                             |    |

| 6.3.53           | PCI-X BRIDGE STATUS REGISTER – OFFSET 84h                                                                                |    |

| 6.3.54           | UPSTREAM SPLIT TRANSACTION REGISTER – OFFSET 88h                                                                         |    |

| 6.3.55           | DOWNSTREAM SPLIT TRANSACTION REGISTER – OFFSET 8Ch                                                                       |    |

| 6.3.56           | POWER MANAGEMENT ID REGISTER – OFFSET 90h                                                                                |    |

| 6.3.57           | NEXT CAPABILITY POINTER REGISTER – OFFSET 90h                                                                            |    |

| 6.3.58           | POWER MANAGEMENT CAPABILITY REGISTER – OFFSET 90h                                                                        |    |

| 6.3.59           | POWER MANAGEMENT CONTROL AND STATUS REGISTER – OFFSET 94h                                                                |    |

| 6.3.60           | PCI-TO-PCI SUPPORT EXTENSION REGISTER – OFFSET 94h                                                                       |    |

| 6.3.61           | SUBTRACTIVE DECODING PCI-TO-PCI BRIDGE ENABLE – OFFSET 98h                                                               |    |

| 6.3.62           | RESERVED REGISTERS – OFFSET 9Ch                                                                                          |    |

| 6.3.63           | CAPABILITY ID REGISTER – OFFSET A0h                                                                                      |    |

| 6.3.64           | NEXT POINTER REGISTER – OFFSET A0h                                                                                       | 44 |

| 6.3.65           | SLOT NUMBER REGISTER – OFFSET A0h                                                                                        |    |

| 6.3.66           | CHASSIS NUMBER REGISTER – OFFSET A0h                                                                                     |    |

|                  |                                                                                                                          |    |

| 6.3.67             | SECONDARY CLOCK AND CLKRUN CONTROL REGISTER – OFFSET A4h                    |    |

|--------------------|-----------------------------------------------------------------------------|----|

| 6.3.68             | XPIP CONFIGURATION REGISTER 3 – OFFSET A4h                                  |    |

| 6.3.69             | CAPABILITY ID REGISTER – OFFSET A8h                                         |    |

| 6.3.70             | NEXT POINTER REGISTER – OFFSET A8h                                          |    |

| 6.3.71             | RESERVED REGISTER – OFFSET A8h                                              |    |

| 6.3.72             | SUBSYSTEM VENDOR ID REGISTER – OFFSET ACh                                   |    |

| 6.3.73             | SUBSYSTEM ID REGISTER – OFFSET ACh                                          |    |

| 6.3.74             | PCI EXPRESS CAPABILITY ID REGISTER – OFFSET B0h                             |    |

| 6.3.75             | NEXT CAPABILITY POINTER REGISTER – OFFSET B0h                               |    |

| 6.3.76             | PCI EXPRESS CAPABILITY REGISTER – OFFSET B0h                                |    |

| 6.3.77             | DEVICE CAPABILITY REGISTER – OFFSET B4h                                     |    |

| 6.3.78             | DEVICE CONTROL REGISTER – OFFSET B8h                                        |    |

| 6.3.79             | DEVICE STATUS REGISTER – OFFSET B8h                                         |    |

| 6.3.80             | LINK CAPABILITY REGISTER – OFFSET BOM                                       |    |

| 6.3.81             | LINK CATABILITT REGISTER – OFFSET BCh<br>LINK CONTROL REGISTER – OFFSET COh |    |

| 6.3.81<br>6.3      | LINK CONTROL REGISTER – OFFSET CON<br>LINK STATUS REGISTER – OFFSET CON     |    |

|                    | RESERVED REGISTER – OFFSET C4 – C8h                                         |    |

| 6.3.83             | XPIP CONFIGURATION REGISTER 0 – OFFSET CCh                                  |    |

| 6.3.84             |                                                                             |    |

| 6.3.85             | XPIP CONFIGURATION REGISTER 1 – OFFSET D0h                                  |    |

| 6.3.86             | XPIP CONFIGURATION REGISTER 2 – OFFSET D4h                                  |    |

| 6.3.87             | CAPABILITY ID REGISTER – OFFSET D8h                                         |    |

| 6.3.88             | NEXT POINTER REGISTER – OFFSET D8h                                          |    |

| 6.3.89             | VPD REGISTER – OFFSET D8h                                                   |    |

| 6.3.90             | VPD DATA REGISTER – OFFSET DCh                                              |    |

| 6.3.91             | EXTENDED CONFIGURATION ACCESS ADDRESS REGISTER – OFFSET E0h                 | 52 |

| 6.3.92             | EXTENDED CONFIGURATION ACCESS DATA REGISTER – OFFSET E4h                    | 52 |

| 6.3.93             | RESERVED REGISTERS – OFFSET E8h – ECh                                       | 52 |

| 6.3.94             | MESSAGE SIGNALED INTERRUPTS ID REGISTER – F0h                               | 52 |

| 6.3.95             | NEXT CAPABILITIES POINTER REGISTER – F0h                                    | 53 |

| 6.3.96             | MESSAGE CONTROL REGISTER – OFFSET F0h                                       | 53 |

| 6.3.97             | MESSAGE ADDRESS REGISTER – OFFSET F4h                                       | 53 |

| 6.3.98             | MESSAGE UPPER ADDRESS REGISTER – OFFSET F8h                                 | 53 |

| 6.3.99             | MESSAGE DATA REGISTER – OFFSET FCh                                          |    |

| 6.3.100            | ADVANCE ERROR REPORTING CAPABILITY ID REGISTER – OFFSET 100h                |    |

| 6.3.101            | ADVANCE ERROR REPORTING CAPABILITY VERSION REGISTER – OFFSET 100h           |    |

| 6.3.102            | NEXT CAPABILITY OFFSET REGISTER – OFFSET 100h                               |    |

| 6.3.102            | UNCORRECTABLE ERROR STATUS REGISTER – OFFSET 104h                           |    |

| 6.3.104            | UNCORRECTABLE ERROR MASK REGISTER – OFFSET 108h                             |    |

| 6.3.105            | UNCORRECTABLE ERROR SEVERITY REGISTER – OFFSET 100h                         |    |

| 6.3.105            | CORRECTABLE ERROR SEVERITI REGISTER – OFFSET TOCK                           |    |

| 6.3.100<br>6.3.107 | CORRECTABLE ERROR MASK REGISTER – OFFSET 110h                               |    |

| 6.3.107<br>6.3.108 | ADVANCED ERROR CAPABILITIES AND CONTROL REGISTER – OFFSET 114n              |    |

|                    |                                                                             |    |

| 6.3.109            | HEADER LOG REGISTER 1 – OFFSET 11Ch                                         |    |

| 6.3.110            | HEADER LOG REGISTER 2 – OFFSET 120h                                         |    |

| 6.3.111            | HEADER LOG REGISTER 3 – OFFSET 124h                                         |    |

| 6.3.112            | HEADER LOG REGISTER 4 – OFFSET 128h                                         |    |

| 6.3.113            | SECONDARY UNCORRECTABLE ERROR STATUS REGISTER – OFFSET 12Ch                 |    |

| 6.3.114            | SECONDARY UNCORRECTABLE ERROR MASK REGISTER – OFFSET 130h                   |    |

| 6.3.115            | SECONDARY UNCORRECTABLE ERROR SEVERITY REGISTER – OFFSET 134h               |    |

| 6.3.116            | SECONDARY ERROR CAPABILITY AND CONTROL REGISTER – OFFSET 138h               |    |

| 6.3.117            | SECONDARY HEADER LOG REGISTER – OFFSET 13Ch – 148h                          |    |

| 6.3.118            | RESERVED REGISTER – OFFSET 14Ch                                             |    |

| 6.3.119            | VC CAPABILITY ID REGISTER – OFFSET 150h                                     |    |

| 6.3.120            | VC CAPABILITY VERSION REGISTER – OFFSET 150h                                | 58 |

|                    |                                                                             |    |

|               | 3.121 NEXT CAPABILITY OFFSET REGISTER – OFFSET 150h                                                                         |    |

|---------------|-----------------------------------------------------------------------------------------------------------------------------|----|

|               | 3.122 PORT VC CAPABILITY REGISTER 1 – OFFSET 154h                                                                           |    |

|               | 3.123 PORT VC CAPABILITY REGISTER 2 – OFFSET 158h                                                                           |    |

|               | 3.124 PORT VC CONTROL REGISTER – OFFSET 15Ch<br>3.125 PORT VC STATUS REGISTER – OFFSET 15Ch                                 |    |

|               | 3.126 VC0 RESOURCE CAPABILITY REGISTER – OFFSET 160h                                                                        |    |

|               | 3.127 VC0 RESOURCE CONTROL REGISTER – OFFSET 164h                                                                           |    |

|               | 3.128 VC0 RESOURCE STATUS REGISTER – OFFSET 168h                                                                            |    |

| 6.3           | 3.129 RESERVED REGISTERS – OFFSET 16Ch – 2FCh                                                                               |    |

|               | 3.130 EXTENDED GPIO DATA AND CONTROL REGISTER – OFFSET 300h                                                                 |    |

|               | 3.131 EXTENDED GPI/GPO DATA AND CONTROL REGISTER – OFFSET 304h                                                              |    |

|               | 3.132RESERVED REGISTERS – OFFSET 308h – 30Ch3.133REPLAY AND ACKNOWLEDGE LATENCY TIMERS – OFFSET 310h                        |    |

|               | 3.133       REPLAY AND ACKNOWLEDGE LATENCY TIMERS – OFFSET 310h         3.134       RESERVED REGISTERS – OFFSET 314h – FFCh |    |

|               |                                                                                                                             |    |

|               | PIO PINS AND SM BUS ADDRESS                                                                                                 |    |

| 8 C           | LOCK SCHEME                                                                                                                 |    |

| 9 IN          | NTERRUPTS                                                                                                                   | 67 |

| 10 El         | EPROM (I2C) INTERFACE AND SYSTEM MANAGEMENT BUS                                                                             | 68 |

| 10.1          | EEPROM (I2C) INTERFACE                                                                                                      |    |

| 10.2          |                                                                                                                             |    |

| 10.3          | EEPROM AUTOLOAD CONFIGURATION                                                                                               |    |

| 11 R          | ESET SCHEME                                                                                                                 |    |

|               | CEE 1149.1 COMPATIBLE JTAG CONTROLLER                                                                                       |    |

| 12.1          | INSTRUCTION REGISTER                                                                                                        |    |

| 12.1          | BYPASS REGISTER                                                                                                             |    |

| 12.2          | DEVICE ID REGISTER                                                                                                          |    |

| 12.3          | BOUNDARY SCAN REGISTER                                                                                                      |    |

| 12.4          | JTAG BOUNDARY SCAN REGISTER ORDER                                                                                           |    |

|               |                                                                                                                             |    |

|               | OWER MANAGEMENT                                                                                                             |    |

| 14 PC         | OWER SEQUENCING                                                                                                             |    |

| 14.1          | INITIAL POWER-UP (G3 TO L0)                                                                                                 | 75 |

| 15 El         | LECTRICAL AND TIMING SPECIFICATIONS                                                                                         | 77 |

| 15.1          | ABSOLUTE MAXIMUM RATINGS                                                                                                    | 77 |

| 15.2          | DC SPECIFICATIONS                                                                                                           | 77 |

| 15.3          |                                                                                                                             |    |

| 15.4          | OPERATING AMBIENT TEMPERATURE                                                                                               | 79 |

| <b>16 P</b> A | ACKAGE INFORMATION                                                                                                          |    |

| 17 0          | RDERING INFORMATION                                                                                                         |    |

|               |                                                                                                                             |    |

# TABLE OF FIGURES

| FIGURE 1-1 PI7C9X113SL TOPOLOGY                                                | 10 |

|--------------------------------------------------------------------------------|----|

| FIGURE 4-1 FORWARD BRIDGE MODE                                                 | 19 |

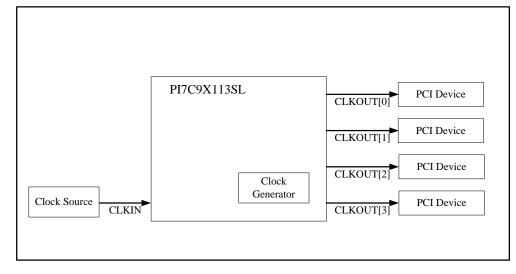

| FIGURE 8-1 TOPOLOGY OF INTERNAL CLOCK GENERATOR AND INTERNAL CLOCK BUFFERING – |    |

| Internal Feedback Mode                                                         | 64 |

| FIGURE 8-2 TOPOLOGY OF INTERNAL CLOCK GENERATOR AND INTERNAL CLOCK BUFFERING – |    |

| External Feedback Mode                                                         | 64 |

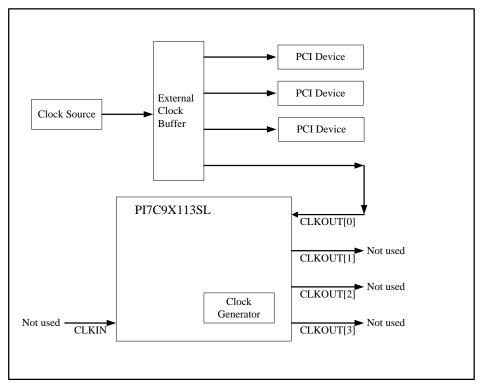

| FIGURE 8-3 TOPOLOGY OF EXTERNAL CLOCK GENERATOR AND INTERNAL CLOCK BUFFERING – |    |

| Internal Feedback Mode                                                         | 65 |

| FIGURE 8-4 TOPOLOGY OF EXTERNAL CLOCK GENERATOR AND INTERNAL CLOCK BUFFERING – |    |

| External Feedback Mode                                                         | 65 |

| FIGURE 8-5 TOPOLOGY OF EXTERNAL CLOCK GENERATOR AND EXTERNAL CLOCK BUFFERING   | 66 |

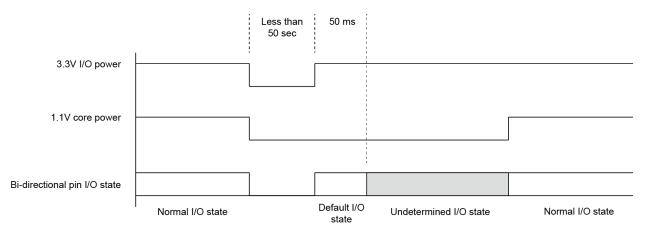

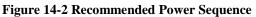

| FIGURE 14-1 TIMING SEQUENCE WITH UNDETERMINED I/O STATE                        | 74 |

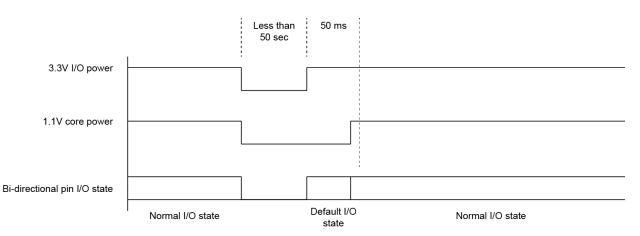

| FIGURE 14-2 RECOMMENDED POWER SEQUENCE                                         |    |

| FIGURE 14-3 INITIAL POWER-UP                                                   |    |

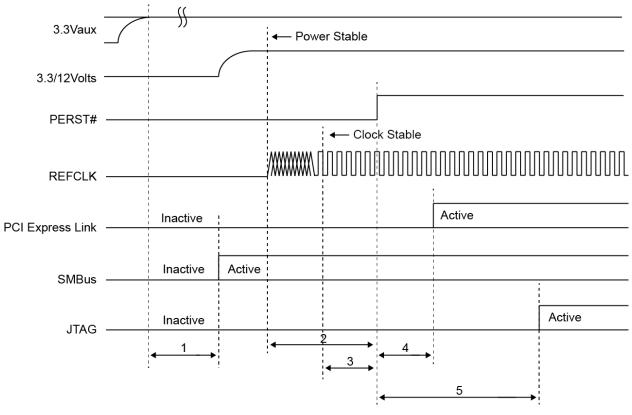

| FIGURE 15-1 PCI SIGNAL TIMING CONDITIONS                                       |    |

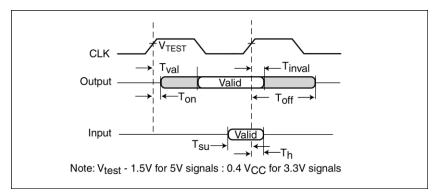

| FIGURE 16-1 PACKAGE OUTLINE DRAWING                                            | 80 |

| FIGURE 16-2 PART MARKING                                                       | 80 |

# LIST OF TABLES

| TABLE 2-1 PIN ASSIGNMENTS                                                               | . 16 |

|-----------------------------------------------------------------------------------------|------|

| TABLE 3-1 MODE SELECTION                                                                | . 17 |

| TABLE 3-2 PIN STRAPPING FOR CLOCK POWER MANAGEMENT                                      | . 17 |

| TABLE 5-1 TLP FORMAT                                                                    | . 20 |

| TABLE 6-1 CONFIGURATION REGISTER MAP (00H – FFH)                                        | . 21 |

| TABLE 6-2 PCI EXPRESS EXTENDED CAPABILITY REGISTER MAP (100H – FFFH)                    | . 24 |

| TABLE 7-1 SM BUS DEVICE ID STRAPPING                                                    | . 62 |

| TABLE 8-1 FREQUENCY OF PCI CLKOUT WITH INTERNAL CLOCK SOURCE:                           | . 63 |

| TABLE 9-1 PCI INTERRUPT TO PCIE INTERRUPT MESSAGE MAPPING IN FORWARD BRIDGE MODE        | . 67 |

| TABLE 12-1 INSTRUCTION REGISTER CODES                                                   | .71  |

| TABLE 12-2 JTAG DEVICE ID REGISTER                                                      | .71  |

| TABLE 14-1 POWER SEQUENCING AND RESET SIGNAL TIMINGS                                    |      |

| TABLE 15-1 ABSOLUTE MAXIMUM RATINGS                                                     | .77  |

| TABLE 15-2 DC ELECTRICAL CHARACTERISTICS                                                | .77  |

| TABLE 15-3 PCI BUS TIMING PARAMETERS                                                    | . 78 |

| TABLE 15-4 PCI EXPRESS INTERFACE - DIFFERENTIAL TRANSMITTER (TX) OUTPUT CHARACTERISTICS | s78  |

| TABLE 15-5 PCI EXPRESS INTERFACE - DIFFERENTIAL RECEIVER (RX) INPUT CHARACTERISTICS     | . 79 |

| TABLE 15-6 OPERATING AMBIENT TEMPERATURE                                                | . 79 |

A Product Line of Diodes Incorporated

This page intentionally left blank.

# 1 INTRODUCTION

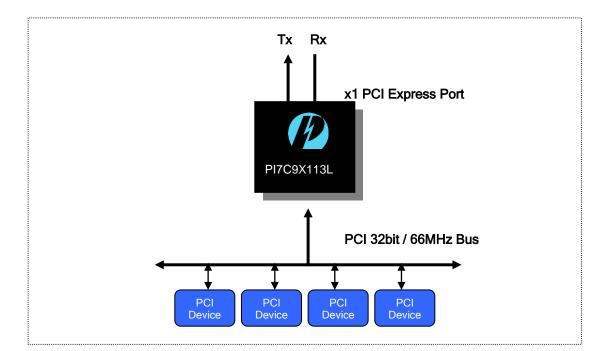

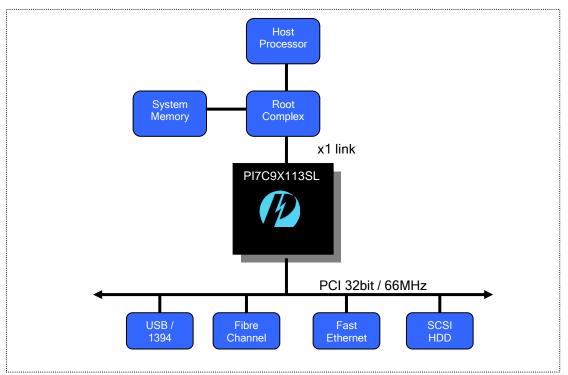

PI7C9X113SL is a PCIe-to-PCI/PCI-X bridge. PI7C9X113SL is compliant with the *PCI Express Base Specification*, Revision 1.1, the *PCI Express Card Electromechanical Specification*, Revision 1.1, the *PCI Local Bus Specification*, Revision 3.0 and *PCI Express to PCI/PCI-X Bridge Specification*, Revision 1.0. PI7C9X113SL supports transparent mode operation and forward bridging. PI7C9X113SL has an x1 PCI Express upstream port and a 32-bit PCI downstream port. The 32-bit PCI downstream port is 66MHz capable (see Figure 1-1). PI7C9X113SL configuration registers are backward compatible with existing PCI bridge software and firmware. No modification of PCI bridge software and firmware is needed for the original operation.

#### Figure 1-1 PI7C9X113SL Topology

# 1.1 INDUSTRY SPECIFICATION COMPLIANCE

- Compliant with PCI Express Base Specification, Revision 1.1

- Compliant with PCI Express to PCI/PCI-X Bridge Specification, Revision 1.0

- Compliant with PCI Express Card Electromechanical Specification, Revision 1.0a

- Compliant with PCI-to-PCI Bridge Architecture Specification, Revision 1.2

- Compliant with PCI Local Bus Specification, Revision 3.0

- Compliant with PCI SHPC and Subsystem Specification, Revision 1.0

- Compliant with PCI Mobile Design Guide, Version 1.1

- Compliant with PCI Bus PM Interface Specification, Revision 1.2

- Compliant with System Management (SM) Bus, Version 2.0

- Compliant with Advanced Configuration and Power Interface Specification (ACPI), Revision 2.0b

# 1.2 GENERAL FEATURES

- Forward bridging (PCI Express as primary bus, PCI as secondary bus)

- x1 PCI Express interface (2.5Gb/s data rate)

- 32-bit PCI interface capable of 66MHz

- GPIO support (4 bi-directional pins). When external arbiter is used, 3 additional GPI (input) and GPO (output) pins

- Power Management (including ACPI, PCI\_PM, CLKRUN\_L and CLKREQ\_L,)

- Transparent mode support

- Subtractive Decoding PCI-to-PCI bridge to support legacy device

- Masquerade support (user-defined vendor, device, revision, subsystem device, and subsystem vendor ID)

- EEPROM (I2C) Interface

- SM Bus Interface

- 10k byte buffer: 2K byte buffer for downstream memory read, 4K bytes for upstream memory read, and 2K byte buffer for memory write in both directions

- Auxiliary powers (VAUX, VDDAUX, VDDCAUX) support

- Power consumption less than 350 mW in typical condition

- Industrial temperature range (-40C to 85C)

# 1.3 PCI EXPRESS FEATURES

- Physical Layer interface (x1 link with 2.5Gb/s data rate)

- Virtual Isochronous support (upstream TC1-7 generation, downstream TC1-7 mapping)

- CRC (16-bit), LCRC (32-bit)

- ECRC and advanced error reporting

- Lane polarity toggle

- ASPM support

- WAKE\_L support

- Maximum payload size to 512 bytes

- CLKREQ\_L support to disable Refclk at L1 and L2 state

# 1.4 PCI FEATURES

- Provides two level arbitration support for four PCI Bus masters

- 3.3V PCI signaling with 5V I/O tolerance

- PME\_L support

- LOCK support

- 16-bit address decode for VGA

- Subsystem Vendor and Subsystem Device IDs support

- PCI INT interrupt or MSI Function support

- Adaptive fragmentation support for memory write

- Internal clock generator for PCI bus

- CLKRUN\_L support to stop the PCI clock

# 2 PIN DEFINITIONS

# 2.1 SIGNAL TYPES

| TYPE ( | OF SIGNAL - DESCRIPTIONS                  |

|--------|-------------------------------------------|

| В      | Bi-directional                            |

| Ι      | Input                                     |

| IU     | Input with pull-up                        |

| ID     | Input with pull-down                      |

| IOD    | Bi-directional with open drain output     |

| OD     | Open drain output                         |

| 0      | Output                                    |

| Р      | Power                                     |

| G      | Ground                                    |

| "T??:  | n signal name indicates Asting IOW signal |

"\_L" in signal name indicates Active LOW signal

# 2.2 PCI EXPRESS SIGNALS

| NAME    | PIN ASSIGNMENT | TYPE | DESCRIPTION                                                             |

|---------|----------------|------|-------------------------------------------------------------------------|

| REFCLKP | 13, 12         | Ι    | Reference Clock Inputs: Connect to external 100MHz differential clock.  |

| REFCLKN |                |      |                                                                         |

| RP      | 21, 20         | Ι    | PCI Express Data Inputs: Differential data receiver input signals       |

| RN      |                |      |                                                                         |

| TP      | 17, 16         | 0    | PCI Express Data Outputs: Differential data transmitter output signals  |

| TN      |                |      |                                                                         |

| PERST_L | 29             | Ι    | PCI Express Fundamental Reset (Active LOW): PI7C9X113SL The device uses |

|         |                |      | this signal reset to initialize the internal state machines.            |

# 2.3 PCI SIGNALS

| NAME       | PIN ASSIGNMENT                                                                                                                                                   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD [31:0]  | 125, 126, 124, 121,<br>122, 120, 119, 117,<br>113, 111, 110, 109,<br>108, 106, 103, 104,<br>90, 88, 86, 85, 83, 80,<br>79, 78, 75, 74, 71, 70,<br>68, 69, 67, 64 | В    | Address / Data: Multiplexed address and data bus. Address phase is aligned with first clock of FRAME_L assertion. Data phase is aligned with IRDY_L or TRDY_L assertion. Data is transferred on rising edges of CLKOUT[0] when both IRDY_L and TRDY_L are asserted. During bus idle (both FRAME_L and IRDY_L are de-asserted), PI7C9X113SL drives AD to a valid logic level when arbiter is parking to PI7C9X113SL on PCI bus.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CBE_L[3:0] | 116, 99, 89, 76                                                                                                                                                  | В    | <b>Command / Byte Enables (Active LOW):</b> Multiplexed command at address phase<br>and byte enable at data phase. During address phase, the initiator drives commands on<br>CBE [3:0] signals to start the transaction. If the command is a write transaction, the<br>initiator will drive the byte enables during data phase. Otherwise, the target will drive<br>the byte enables during data phase. During bus idle, PI7C9X113SL drives CBE [3:0]<br>signals to a valid logic level when arbiter is parking to PI7C9X113SL on PCI bus.                                                                                                                                                                                                                                                                                                                  |

| PAR        | 94                                                                                                                                                               | В    | <b>Parity Bit:</b> Parity bit is an even parity (i.e. even number of 1's), which generates based on the values of AD [31:0], CBE [3:0]. If PI7C9X113SL is an initiator with a write transaction, PI7C9X113SL will tri-state PAR. If PI7C9X113SL is a target and a write transaction, PI7C9X113SL will drive PAR one clock after the address or data phase. If PI7C9X113SL is a target and a read transaction, PI7C9X113SL will drive PAR one clock after the address. PAR one clock after the address or data phase. If PI7C9X113SL is a target and a read transaction, PI7C9X113SL will drive PAR one clock after the address phase and tri-state PAR during data phases. PAR is tri-stated one cycle after the AD lines are tri-stated. During bus idle, PI7C9X113SL drives PAR to a valid logic level when arbiter is parking to PI7C9X113SL on PCI bus. |

| FRAME_L    | 63                                                                                                                                                               | В    | <b>FRAME</b> (Active LOW): Driven by the initiator of a transaction to indicate the beginning and duration an access. The de-assertion of FRAME_L indicates the final data phase signaled by the initiator in burst transfers. Before being tri-stated, it is driven to a de-asserted state for one cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| IRDY_L     | 97                                                                                                                                                               | В    | <b>IRDY</b> (Active LOW): Driven by the initiator of a transaction to indicate its ability to complete current data phase on the primary side. Once asserted in a data phase, it is not de-asserted until the end of the data phase. Before tri-stated, it is driven to a de-asserted state for one cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| NAME                       | PIN ASSIGNMENT    | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------|-------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRDY_L                     | 100               | В    | <b>TRDY</b> (Active LOW): Driven by the target of a transaction to indicate its ability to complete current data phase on the primary side. Once asserted in a data phase, it is not de-asserted until the end of the data phase. Before tri-stated, it is driven to a de-                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                            |                   |      | asserted state for one cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DEVSEL_L                   | 98                | В    | <b>Device Select (Active LOW):</b> Asserted by the target indicating that the device is accepting the transaction. As a master, PI7C9X113SL waits for the assertion of this signal within 5 cycles of FRAME_L assertion; otherwise, terminate with master abort. Before tri-stated, it is driven to a de-asserted state for one cycle.                                                                                                                                                                                                                                                                                                                                                                                             |

| STOP_L                     | 96                | В    | <b>STOP</b> (Active LOW): Asserted by the target indicating that the target is requesting the initiator to stop the current transaction. Before tri-stated, it is driven to a deasserted state for one cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LOCK_L                     | 93                | В    | <b>LOCK</b> (Active LOW): Asserted by the initiator for multiple transactions to complete. PI7C9X113SL does not support any upstream LOCK transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PERR_L                     | 92                | В    | <b>Parity Error (Active LOW):</b> Asserted when a data parity error is detected for data received on the PCI bus interface. Before being tri-stated, it is driven to a de-asserted state for one cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SERR_L                     | 61                | IOD  | <ul> <li>System Error (Active LOW): Can be driven LOW by any device to indicate a system error condition. If SERR control is enabled, PI7C9X113SL will drive this pin on:</li> <li>Address parity error</li> <li>Posted write data parity error on target bus</li> <li>Master abort during posted write transaction</li> <li>Target abort during posted write transaction</li> <li>Posted write transaction discarded</li> <li>Delayed write request discarded</li> <li>Delayed transaction master timeout</li> <li>Errors reported from PCI Express port (advanced error reporting) in transparent mode.</li> <li>This signal is an open drain buffer that requires an external pull-up resistor for proper operation.</li> </ul> |

| REQ_L [3:0]                | 33, 34, 32, 31    | I    | <b>Request (Active LOW):</b> REQ_L's are asserted by bus master devices to request for transactions on the PCI bus. The master devices de-assert REQ_Ls for at least 2 PCI clock cycles before asserting them again. If external arbiter is selected, REQ_L [0] will be the bus grant input to PI7C9X113SL. Also, REQ_L [3:1] will become the GPI [2:0].<br>When powered up, if both REQ_L[2] and REQ_L[3] and pulled low (Active LOW) and stay low in normal operation, the PI7C9X113SL will change the function of CLKOUT[3] to CLKRUN_L and CLKOUT[2] to CLKREQ_L, respectively.                                                                                                                                                |

| GNT_L [3:0]                | 41, 39, 40, 37    | 0    | <b>Grant (Active LOW):</b> PI7C9X113SL asserts GNT_Ls to release PCI bus control to bus master devices. During idle and all GNT_Ls are de-asserted and arbiter is parking to PI7C9X113SL, PI7C9X113SL will drive AD, CBE, and PAR to valid logic levels. If external arbiter is selected, GNT_L [0] will be the bus request from PI7C9X113SL to external arbiter. Also, GNT_L [3:1] will become the GPO [2:0].                                                                                                                                                                                                                                                                                                                     |

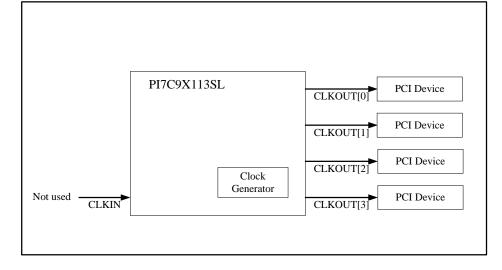

| CLKOUT [3:0]               | 49, 54, 56, 59    | В    | PCI Clock Outputs: PCI clock outputs are derived from the CLKIN and provide clocking signals to external PCI Devices. In external feedback mode, CLKOUT[0] becomes an input for feedback clock and CLKOUT[1:3] remain as clock outputs to provide clock signals to external PCI Devices. Please see Chapter 8 for further information.                                                                                                                                                                                                                                                                                                                                                                                             |

| M66EN                      | 102               | I    | <b>66MHz Enable:</b> This input is used to specify if Bridge is capable of running at 66MHz. For 66MHz operation on the PCI bus, this signal should be pulled "HIGH". For 33MHz operation on the PCI bus, this signal should be pulled LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RESET_L                    | 46                | 0    | <b>RESET_L</b> (Active LOW): When RESET_L active, all PCI signals should be asynchronously tri-stated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| INTA_L<br>INTB_L<br>INTC_L | 36,<br>43,<br>57, | I    | <b>Interrupt:</b> Signals are asserted to request an interrupt. After asserted, it can be cleared by the device driver. INTA_L, INTB_L, INTC_L, INTD_L signals are inputs and asynchronous to the clock in the forward mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| INTD_L<br>CLKIN            | 60<br>44          | Ι    | <b>PCI Clock Input:</b> PCI Clock Input Signal connects to an external clock source.<br>The PCI Clock Outputs CLKOUT [3:0] pins are derived from CLKIN Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### MODE SELECT AND STRAPPING SIGNALS 2.4

| NAME | PIN ASSIGNMENT | TYPE | DESCRIPTION                                                                        |

|------|----------------|------|------------------------------------------------------------------------------------|

| TM0  | 128            | ID   | Mode Select 0: Mode Selection Pin to select EEPROM or SM Bus. TM0=0 for            |

|      |                |      | EEPROM (I2C) support and TM0=1 for SM Bus support. TM0 is a strapping pin.         |

|      |                |      | See Table 3-1 mode selection and Table 3-2 for strapping control.                  |

| TM1  | 23             | ID   | Mode Select 1: Mode Selection Pin for normal operation. Set TM1=0 for normal       |

|      |                |      | operation. TM1=1 is reserved. TM1 is a strapping pin. See Table 3-1 mode selection |

|      |                |      | and Table 3-2 for strapping control.                                               |

# 2.5 JTAG BOUNDARY SCAN SIGNALS

| NAME | PIN ASSIGNMENT | TYPE | DESCRIPTION                                                                               |

|------|----------------|------|-------------------------------------------------------------------------------------------|

| TCK  | 26             | IU   | Test Clock: TCK is the test clock to synchronize the state information and data on        |

|      |                |      | the PCI bus side of PI7C9X113SL during boundary scan operation. At normal                 |

|      |                |      | operation mode, this pin should be left open(NC).                                         |

| TMS  | 24             | IU   | Test Mode Select: TMS controls the state of the Test Access Port (TAP) controller.        |

|      |                |      | At normal operation mode, this pin should be pulled low through a 1K-Ohm pull-            |

|      |                |      | down resistor.                                                                            |

| TDO  | 27             | 0    | Test Data Output: TDO is the test data output and connects to the end of the JTAG         |

|      |                |      | scan chain. At normal operation mode, this pin should be left open(NC).                   |

| TDI  | 28             | IU   | Test Data Input: TDI is the test data input and connects to the beginning of the          |

|      |                |      | JTAG scan chain. It allows the test instructions and data to be serially shifted into the |

|      |                |      | PCI side of PI7C9X113SL. At normal operation mode, this pin should be left                |

|      |                |      | open(NC).                                                                                 |

#### 2.6 MISCELLANEOUS SIGNALS

| NAME       | PIN ASSIGNMENT | TYPE  | DESCRIPTION                                                                           |

|------------|----------------|-------|---------------------------------------------------------------------------------------|

| GPIO [3:0] | 47, 48, 51, 52 | В     | General Purpose I/O Data Pins: The 4 general-purpose signals are programmable as      |

|            |                |       | either input-only or bi-directional signals by writing the GPIO output enable control |

|            |                |       | register in the configuration space.                                                  |

| SMBCLK /   | 3              | В     | SMBUS / EEPROM Clock Pin: When EEPROM (I2C) interface is selected                     |

| SCL        |                |       | (TM0=0), this pin is an output of SCL clock and connected to EEPROM clock input.      |

|            |                |       | When SMBUS interface is selected (TM0=1), this pin is an input for the clock of       |

|            |                |       | SMBUS.                                                                                |

| SMBDATA /  | 5              | B/IOD | SMBUS / EEPROM Data Pin: Data Interface Pin to EERPOM or SMBUS. When                  |

| SDA        |                |       | EEPROM (I2C) interface is selected (TM0=0), this pin is a bi-directional signal.      |

|            |                |       | When SMBUS interface is selected (TM0=1), this pin is an open drain signal.           |

| PME_L      | 1              | Ι     | Power Management Event Pin: Power Management Event Signal is asserted to              |

|            |                |       | request a change in the device or link power state.                                   |

| WAKE_L     | 4              | 0     | Wakeup Signal (Active LOW): This signal is asserted when PME_L pin is asserted        |

|            |                |       | and the link is in the L2 state                                                       |

| REXTP,     | 8,9            | Ι     | External Precision Resistor: Connect an external resistor (1.43K Ohm +/- 1%) to       |

| REXTN      |                |       | provide a reference to both the bias currents and impedance calibration circuitry.    |

# 2.7 POWER AND GROUND PINS

| NAME    | PIN ASSIGNMENT         | TYPE | DESCRIPTION                                                                    |

|---------|------------------------|------|--------------------------------------------------------------------------------|

| VDDA    | 15, 18                 | Р    | Analog Voltage Supply for PCI Express Interface: Connect to the 1.1V-1.2V      |

|         |                        |      | Power Supply.                                                                  |

| VDDA33  | 10                     |      | High Voltage Supply for PCI Express Interface: Connect to the 3.3V Power       |

|         |                        |      | Supply.                                                                        |

| VDDC    | 30, 35, 45, 53, 62,    | Р    | Core Supply Voltage: Connect to the 1.1V-1.2V Power Supply.                    |

|         | 73, 81, 95, 105,       |      |                                                                                |

|         | 114, 127               |      |                                                                                |

| VDDCAUX | 7                      | Р    | Auxiliary Core Supply Voltage: Connect to the 1.1V-1.2V Power Supply.          |

| VD33    | 25, 38, 50, 55, 58, 66 | Р    | I/O Supply Voltage for PCI Interface: Connect to the 3.3V Power Supply for PCI |

|         | 72, 77, 82, 87, 91,    |      | I/O Buffers.                                                                   |

|         | 101, 107, 112,         |      |                                                                                |

|         | 118, 123               |      |                                                                                |

| NAME | PIN ASSIGNMENT         | TYPE | DESCRIPTION                                                               |

|------|------------------------|------|---------------------------------------------------------------------------|

| VAUX | 2                      | Р    | Auxiliary I/O Supply Voltage for PCI interface: Connect to the 3.3V Power |

|      |                        |      | Supply.                                                                   |

| VSS  | 6, 11, 14, 19, 22, 42, | Р    | Ground: Connect to Ground.                                                |

|      | 65, 84, 115, 129       |      |                                                                           |

# 2.8 PIN ASSIGNMENTS

#### Table 2-1 Pin Assignments

| PIN | NAME         | PIN | NAME      | PIN | NAME     | PIN | NAME   |

|-----|--------------|-----|-----------|-----|----------|-----|--------|

| 1   | PME_L        | 34  | REQ_L[2]  | 67  | AD[1]    | 100 | TRDY_L |

| 2   | VAUX         | 35  | VDDC      | 68  | AD[3]    | 101 | VD33   |

| 3   | SMBCLK / SCL | 36  | INTA_L    | 69  | AD[2]    | 102 | M66EN  |

| 4   | WAKE_L       | 37  | GNT_L[0]  | 70  | AD[4]    | 103 | AD[17] |

| 5   | SMBDAT / SDA | 38  | VD33      | 71  | AD[5]    | 104 | AD[16] |

| 6   | VSS          | 39  | GNT_L[2]  | 72  | VD33     | 105 | VDDC   |

| 7   | VDDCAUX      | 40  | GNT_L[1]  | 73  | VDDC     | 106 | AD[18] |

| 8   | REXTP        | 41  | GNT_L[3]  | 74  | AD[6]    | 107 | VD33   |

| 9   | REXTN        | 42  | VSS       | 75  | AD[7]    | 108 | AD[19] |

| 10  | VDDA33       | 43  | INTB_L    | 76  | CBE[0]   | 109 | AD[20] |

| 11  | VSS          | 44  | CLKIN     | 77  | VD33     | 110 | AD[21] |

| 12  | REFCLKN      | 45  | VDDC      | 78  | AD[8]    | 111 | AD[22] |

| 13  | REFCLKP      | 46  | RESET_L   | 79  | AD[9]    | 112 | VD33   |

| 14  | VSS          | 47  | GPIO[3]   | 80  | AD[10]   | 113 | AD[23] |

| 15  | VDDA         | 48  | GPIO[2]   | 81  | VDDC     | 114 | VDDC   |

| 16  | TN           | 49  | CLKOUT[3] | 82  | VD33     | 115 | VSS    |

| 17  | TP           | 50  | VD33      | 83  | AD[11]   | 116 | CBE[3] |

| 18  | VDDA         | 51  | GPIO[1]   | 84  | VSS      | 117 | AD[24] |

| 19  | VSS          | 52  | GPIO[0]   | 85  | AD[12]   | 118 | VD33   |

| 20  | RN           | 53  | VDDC      | 86  | AD[13]   | 119 | AD[25] |

| 21  | RP           | 54  | CLKOUT[2] | 87  | VD33     | 120 | AD[26] |

| 22  | VSS          | 55  | VD33      | 88  | AD[14]   | 121 | AD[28] |

| 23  | TM1          | 56  | CLKOUT[1] | 89  | CBE[1]   | 122 | AD[27] |

| 24  | TMS          | 57  | INTC_L    | 90  | AD[15]   | 123 | VD33   |

| 25  | VD33         | 58  | VD33      | 91  | VD33     | 124 | AD[29] |

| 26  | TCK          | 59  | CLKOUT[0] | 92  | PERR_L   | 125 | AD[31] |

| 27  | TDO          | 60  | INTD_L    | 93  | LOCK_L   | 126 | AD[30] |

| 28  | TDI          | 61  | SERR_L    | 94  | PAR      | 127 | VDDC   |

| 29  | PERST_L      | 62  | VDDC      | 95  | VDDC     | 128 | TM0    |

| 30  | VDDC         | 63  | FRAME_L   | 96  | STOP_L   | 129 | E_PAD  |

| 31  | REQ_L[0]     | 64  | AD[0]     | 97  | IRDY_L   |     |        |

| 32  | REQ_L[1]     | 65  | VSS       | 98  | DEVSEL_L |     |        |

| 33  | REQ_L[3]     | 66  | VD33      | 99  | CBE[2]   |     |        |

# 3 MODE SELECTION AND PIN STRAPPING

## 3.1 FUNCTIONAL MODE SELECTION

PI7C9X113SL uses TM1 and TM0 pins to select different modes of operations. These input signals are required to be stable during normal operation. One of the four combinations of normal operation can be selected by setting the logic values for the three mode select pins. For example, if the logic values are low for both two (TM1 and TM0) pins, the normal operation will have EEPROM (I2C) support with internal arbiter. The designated operation with respect to the values of the TM1 and TM0 pins are defined on Table 3-1:

#### Table 3-1 Mode Selection

| TM1 Strapped | TM0 Strapped | Functional Mode      |

|--------------|--------------|----------------------|

| 0            | 0            | EEPROM (I2C) support |

| 0            | 1            | SM Bus support       |

### 3.2 PIN STRAPPING

If TM1 is strapped to low, PI7C9X113SL uses REQ\_L[3:2] as the strapping pins at the PCIe PERST\_L de-assertion to enable Clock Power Management feature.

#### Table 3-2 Pin Strapping for Clock Power Management

| TM1 Strapped | REQ_L[3:2] Strapped | Test Functions                              |

|--------------|---------------------|---------------------------------------------|

| 0            | 2'b0                | Clock Power Management is enabled, only two |

|              |                     | PCI devices supported.                      |

|              |                     | CLKOUT[2] is used as CLKREQ_L               |

|              |                     | CLKOUT[3] is used as CLKRUN_L               |

# 4 TRANSPARENT AND FORWARD BRIDGING

# 4.1 TRANSPARENT MODE