# **PI3TB212**

## **10.3Gbps Thunderbolt<sup>™</sup> and DisplayPort<sup>™</sup> Switch**

#### **Features**

- ➔ Supports 5.4Gbps for DisplayPort 1.2 and 10.3Gbps for Thunderbolt Electrical Standard

- → Supports DP and DP++ Configuration

- → Supports AUX and DDC MUX

- → V<sub>DD</sub> Operating Range for normal operation: 3.3V±10%

- ➔ Extended operation down to 2.5V min on the LSTx/LSRx to TBC-9/TBC-11 channels (performance not guaranteed, but all buffers will still operate)

- → ESD protection on all pins

- → 1.0kV HBM per JESD22 standard

- → Packaging (Pb-free & Green):

- <sup>o</sup> 3.0 mm x 3.0 mm, 24-contact TQFN

## Application

→ Thunderbolt over mini-DP connector enablement

## Description

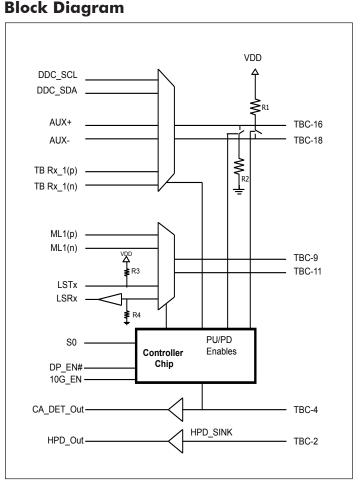

Pericom Semiconductor's PI3TB212 is a high-speed multiplexer/demultiplexer switch. PI3TB212 can switch signals up to 10.3125Gbps for DisplayPort and Thunderbolt<sup>™</sup>(TB) applications. The device supports 5.4Gbps for DisplayPort and 10.3125Gbps for Thunderbolt.

PI3TB212 is a major advance over first-generation Thunderbolt solutions. PI3TB212 integrates the 10.3125 Gbps Thunderbolt path. This eliminates external PIN diode switches, thereby reducing board space, reducing cost, and improving link performance.

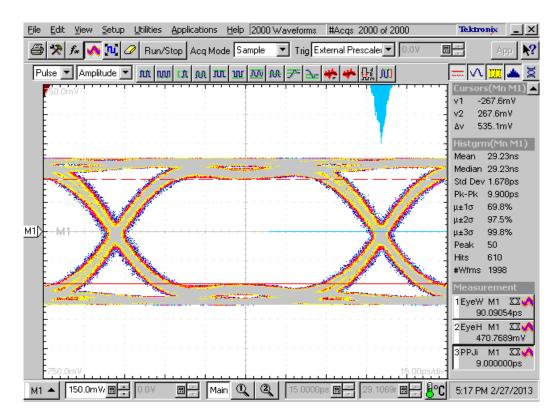

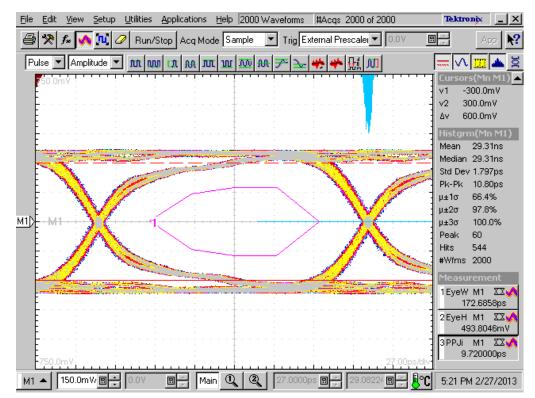

PI3TB212 achieves excellent signal integrity at 10.3125 Gbps as evidenced by measured results.

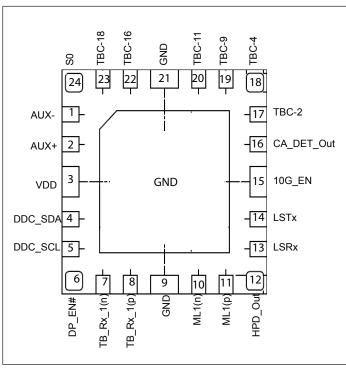

## **Pin Configuration (Top View)**

| Pin #                | Pin Name                 | Туре     | Description                                                                                                                                                                            |

|----------------------|--------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17                   | TBC-2                    | Ι        | Connector Side Hot Plug Detect Input. Connect to mini-DP connector pin2                                                                                                                |

| 11<br>10             | ML1(p)<br>ML1(n)         | I/O      | Controller Side Channel 1, DisplayPort Positive Signal (external AC coupling is required)<br>Controller Side Channel 1, DisplayPort Negative Signal (external AC coupling is required) |

| 22<br>23             | TBC-16<br>TBC-18         | I/O      | Sink Side TB Rx1(p) or AUX+ Signal or DDC_SCL. Connect to mini-DP connector pin 16.<br>Sink Side TB Rx1(n) or AUX- Signal or DDC_SDA. Connect to mini-DP connector pin 18.             |

| 19<br>20             | TBC-9<br>TBC-11          | I/O      | Sink Side DP Main Link + Signal or LSTX. Connect to mini-DP connector pin 9.<br>Sink Side DP Main Link - Signal or LSRX. Connect to mini-DP connector pin 11                           |

| 2                    | AUX+<br>AUX-             | I/O      | Controller Side AUX Positive Signal<br>Controller Side AUX Negative Signal                                                                                                             |

| 8<br>7               | TB Rx_1(p)<br>TB Rx_1(n) | I/O      | Controller Side 10Gbps Positive Signal (external AC coupling is required)<br>Controller Side 10Gbps Negative Signal (external AC coupling is required)                                 |

| 5<br>4               | DDC_SCL<br>DDC_SDA       | I/O      | Controller Side DDC Clock<br>Controller Side DDC Data                                                                                                                                  |

| 18                   | TBC-4                    | Ι        | Connector Side Cable Detect for DP++ Dongle. Connect to mini-DP connector pin 4.                                                                                                       |

| 12                   | HPD_Out                  | 0        | Controller Side Buffered Hot Plug Detect Output                                                                                                                                        |

| 14<br>13             | LSTx<br>LSRx             | I/O<br>O | Controller Side un-buffered UART TX Signal. Integrated 9K $\Omega$ pull-up<br>Controller Side buffered UART RX Signal. 1M $\Omega$ pull-down present at buffer input                   |

| 24                   | S0                       | Ι        | Control signal. See truth table for detailed functionality                                                                                                                             |

| 16                   | CA_DET_Out               | 0        | Cable detect buffered output coming from TBC-4 (pin 18)                                                                                                                                |

| 6                    | DP_EN#                   | Ι        | DisplayPort path enable. See truth table for detailed functionality.                                                                                                                   |

| 15                   | 10G_EN                   | Ι        | 10G path enable. See truth table for detailed functionality.                                                                                                                           |

| 3                    | VDD                      | Power    | 3.3V+/-10% power supply voltage                                                                                                                                                        |

| Center<br>Pad, 9, 21 | GND                      | Ground   | Ground. both pins and center pad must all be connected to GND plane.                                                                                                                   |

## **Pin Description**

## **Description of Operation**

#### **Truth Table**

|                         |                   | Control P | ins    |       | Device and PU/PD Configurations |         |                                           |                   |  |

|-------------------------|-------------------|-----------|--------|-------|---------------------------------|---------|-------------------------------------------|-------------------|--|

| Device States           | S0                | 10G_EN    | DP_EN# | TBC-4 | 2:1 Mux                         | 3:1 Mux | LSRx, HPD_Out,<br>& CA_DET_Out<br>buffers | R1, R2 status     |  |

| Thunderbolt 10G mode    | 1 (System Active) | 1         | 1      | Х     | LSTx & LSRx                     | TB Rx_1 | A                                         | $R_1 = R_2 = OFF$ |  |

| Inunderbolt 10G mode    | 0 (System Sleep)  | 1         | 1      | Х     | LSTx & LSRx                     | Hi-z    | All buffers on                            | $R_1 = R_2 = OFF$ |  |

| DisplayPort Mode        | 1 (System Active) | 0         | 0      | 0     | DP ML1 (p, n)                   | AUX     | All buffers on                            | R1 = R2 = ON      |  |

| DisplayPort Mode        | 0 (System Sleep)  | 0         | 0      | 0     | Hi-Z                            | Hi-z    | ALL BUFFERS ON                            | R1 = R2 = ON      |  |

| TMDS Mode               | 1 (System Active) | 0         | 0      | 1     | DP ML1 (p, n)                   | DDC     | All buffers on                            | R1 = R2 = ON      |  |

| T MDS Mode              | 0 (System Sleep)  | 0         | 0      | 1     | Hi-Z                            | Hi-z    | ALL BUFFERS ON                            | R1 = R2 = ON      |  |

| Detect Mode             | X - don't care    | 0         | 1      | Х     | LSTx & LSRx                     | Hi-z    | All buffers on                            | R1 = R2 = ON      |  |

| Chip Disable mode       | X - don't care    | 1         | 0      | х     | hi-z                            | hi-z    | All buffers on                            | R1 = ON, R2 = ON  |  |

| Power off (VDD = $0$ V) | X - don't care    | х         | х      | x     | hi-z                            | hi-z    | All buffers oFF                           | R1 = OFF, R2 = ON |  |

| ThunderBolt Connector Pins | Controller Pin Names             |

|----------------------------|----------------------------------|

| TBC-16                     | DDC_SCL or AUX(p) or TB RX_1 (p) |

| TBC-18                     | DDC_SDA or AUX(n) or TB Rx_1 (n) |

| TBC-9                      | ML1 (p) or LSTx                  |

| TBC-11                     | ML1 (n) or LSRx                  |

| TBC-4                      | CA_DET_Out                       |

| TBC-2                      | HPD_Out                          |

# PERICOM<sup>®</sup>

#### **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.) Note: Stresses greater than those listed under MAXIMUM

| Storage Temperature                | $-65^{\circ}C \text{ to } +150^{\circ}C$ |

|------------------------------------|------------------------------------------|

| Supply Voltage to Ground Potential | -0.5V to +4.6V                           |

| I/O (Pin7 and 8) DC Input Voltage  | –0.5V to 1.5V                            |

| I/O (pin 1, 2, 4, and 5)           | -0.5V to 4.0V                            |

| I/O (pin 10 and 11)                | -0.5V to 2.6V                            |

| I/O (pin 19 and 20)                | –0.5V to 4.0V                            |

| DC Output Current                  |                                          |

| Power Dissipation                  | 0.5W                                     |

| Control Logic DC Input Voltage     | VDD + 0.5V                               |

|                                    |                                          |

**Note:** Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### Electrical Characteristics Recommended Operating Conditions

| Symbol                 | Parameter                                     | Conditions                                                                  | Min | Тур | Max  | Units |

|------------------------|-----------------------------------------------|-----------------------------------------------------------------------------|-----|-----|------|-------|

| VDD                    | 3.3V Power Supply                             |                                                                             | 3.0 | 3.3 | 3.6  | V     |

| I <sub>DD</sub>        | current consumption in normal op-<br>peration | Control pins = GND or VDD, LSTx = VDD                                       |     | 300 | 780  |       |

| IDDQ (Sys-<br>tem off) | Current consumption when $S0 = 0$             | S0 = 0, TBC-2 and TBC-4 = GND or VDD,<br>LSTx = VDD, all I/Os are floating  |     | 100 | 300  | uA    |

| I <sub>DD_detect</sub> | Current consumption during detect             | $S0 = VDD, 10G_EN = 0, DP_EN\# = VDD,$<br>LSTx = VDD, all I/Os are floating |     | 120 | 300  |       |

| P <sub>DD</sub>        | Total Power from V <sub>DD</sub> 3.3V supply  | Control pins = GND or VDD, LSTx = VDD                                       |     | 1   | 2.8  | mW    |

| PDDQ (Sys-<br>tem off) | Power consumption when $S0 = 0$               | S0 = 0, TBC-2 and TBC-4 = GND or VDD,<br>LSTx = VDD                         |     | 330 | 1080 | uW    |

| P <sub>DD_Detect</sub> | Power consumption during detect               | S0 = VDD, $10G_EN = 0$ , $DP_EN\# = VDD$ ,<br>LSTx = VDD                    |     | 400 | 1080 | uW    |

| T <sub>CASE</sub>      | Case operating temperature range              |                                                                             | 0   |     | 105  | С     |

#### DC Electrical Characteristics for Switching over Operating Range

| Parameters      | Description                                                        | Test Conditions <sup>(1)</sup>                                | Min | Typ <sup>(1)</sup> | Max  |      |

|-----------------|--------------------------------------------------------------------|---------------------------------------------------------------|-----|--------------------|------|------|

| V <sub>IH</sub> | Input HIGH Voltage for S0, DP_EN#,<br>10G_EN, TBC-4, TBC-2, TBC-11 | VDD = 3.3V                                                    | 1.8 |                    |      |      |

| V <sub>IL</sub> | Input LOW Voltage for S0, DP_EN#,<br>10G_EN, TBC-4, TBC-2, TBC-11  | VDD = 3.3V                                                    |     |                    | 0.8  | V    |

| V <sub>IK</sub> | Clamp Diode Voltage                                                | VDD= Max., $I_{IN} = -18mA$                                   |     | -0.7               | -1.2 |      |

| IIH             | Input HIGH Current for S0, DP_<br>EN#, 10G_EN, TBC-4. TBC-2        | $VDD = Max., V_{IN} = V_{DD}$                                 | -1  |                    | 1    |      |

| IIL             | Input LOW Current for S0, DP_EN#,<br>10G_EN, TBC-4, TBC-2          | $VDD = Max., V_{IN} = 0V$                                     | -1  |                    | 1    | - μΑ |

|                 | leakage from TBC-16                                                | VDD = 0V, 1.5V present on TBC-16<br>TB Rx_1 (p/n) is floating | -60 |                    | +60  |      |

| IOFF (TBC pins) | leakage from TBC-18                                                | VDD = 0V, 1.5V present on TBC-18<br>TB Rx_1 (p/n) is floating | -20 |                    | +20  | μΑ   |

|                 | leakage from TBC-9, TBC-11, TBC-<br>4, & TBC-2                     | VDD = 0V, 3.3V present on TBC<br>pins<br>ML1(p/n) is floating | -20 |                    | +20  |      |

| Parameters           | Description                                    | Test Conditions <sup>(1)</sup>                                                                                 | Min  | Typ <sup>(1)</sup> | Max  | Units |

|----------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|--------------------|------|-------|

| I <sub>Leakage</sub> | Leakage on TB-16/TB-18<br>Thunderbolt 10G Mode | $VDD = 3.6V. TB path on. Vin = 1.0V, TBRx_1 (p/n) is floating$                                                 |      | 20                 | 50   |       |

|                      | I/O leakage for DDC/AUX                        | VDD = 3.6V. Vin = 0V                                                                                           |      | 10                 | 15   |       |

|                      | I/O leakage for TB Rx1(p/n)                    | VDD = 3.6V. Vin = 0V; TBC16, 18 = 0.2V                                                                         |      | 20                 | 50   |       |

|                      | I/O leakage for ML1                            | VDD = 3.6V. Vin = 0V; TBC9, 11 = 0.5V                                                                          |      | 10                 | 15   |       |

| I <sub>OZL</sub>     | I/O leakage for LSTx                           | VDD = 3.6V. Vin = 0V                                                                                           | -600 | -400               | -300 |       |

| 022                  | I/O leakage for TBC9 and 11                    | VDD = 3.6V, Vin = 0V, ML1 (p/n) is float-<br>ing                                                               |      | 10                 | 15   |       |

|                      | I/O leakage for TBC16 and 18                   | VDD = 3.6V, Vin = 0V, S0=low, 10G_EN<br>= high, DP_EN# = high, TBRx_1 (p/n) is<br>floating, Thunderbolt Mode   |      | 40                 | 78   | μΑ    |

|                      | I/O leakage for DDC/AUX                        | VDD = 3.6V. Vin = VDD                                                                                          |      | 10                 | 15   |       |

|                      | I/O leakage for TB Rx1(p/n)                    | VDD = 3.6V. Vin = 0.5V                                                                                         |      | 20                 | 50   |       |

|                      | I/O leakage for ML1                            | VDD = 3.6V. Vin = 2.6V                                                                                         |      | 10                 | 15   |       |

| IOZH                 | I/O leakage for LSTx                           | VDD = 3.6V. Vin = VDD                                                                                          |      | 10                 | 15   |       |

| 02m                  | I/O leakage for TBC9 and 11                    | VDD = 3.6V, Vin = VDD, ML1(p/n) is floating                                                                    |      | 10                 | 15   |       |

|                      | I/O leakage for TBC16 and 18                   | VDD = 3.6V, Vin = VDD, S0=low, 10G_<br>EN = high, DP_EN# = high, TBRx_1<br>(p/n) is floating, Thunderbolt mode |      | 80                 | 150  |       |

## DC Electrical Characteristics for Switching over Operating Range

#### **R**on **Table**

| Parameters   | Description              | Test Conditions                          | Min. | Тур. | Max. | Units |

|--------------|--------------------------|------------------------------------------|------|------|------|-------|

| RON AUX/LSTx | AUX & LSTx On Resistance | VDD = 3.3V Vinput = 3.3V, Iinput = -40mA |      | 9    | 15   |       |

| Ron TB       | TB On Resistance         | VDD = 3.3V Vinput = 0V, Iinput = -40mA   |      | 5    | 8    | Ohme  |

| RON DP       | DP On Resistance         | VDD = 3.3V Vinput = 0V, Iinput = -40mA   |      | 5    | 8    | Ohms  |

| RON DDC      | DDC On Resistance        | VDD = 3.3V Vinput = 3.3V, Iinput = -40mA |      | 5    | 25   |       |

| Parameter                  | Description                                         | Test Conditions  | Min. | Typ. <sup>(1)</sup> | Max. | Units |

|----------------------------|-----------------------------------------------------|------------------|------|---------------------|------|-------|

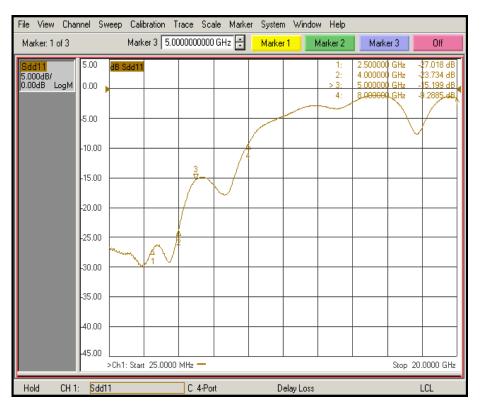

| DDIL <sup>(2)</sup>        | Insertion Loss on TB Rx_1 (p, n) to TBC-            | f=4.0GHz         |      | -1.2                |      |       |

| (TB RX_1)                  | 16 and TBC-18 path                                  | f=5.0GHz         |      | -1.5                |      | dB    |

| (ID KA_I)                  | $(V_{IN} = -10 dBm, DC = 0V)$                       | f=8.0GHz         |      | -3.0                |      |       |

| DDU                        | Insertion Loss on ML1 (p, n) to TBC-9 and           | f=810MHz (RBR)   |      | -0.5                |      |       |

| DDIL                       | TBC-11 path                                         | f=1.35GHz (HBR1) |      | -0.7                |      | dB    |

| (ML1)                      | $(V_{IN} = -10 dBm, DC = 0V)$                       | f=2.7GHz (HBR2)  |      | -1.1                |      |       |

| DDRL <sup>(2)</sup>        | Differential Return Loss on<br>10G thunderbolt path | f= 4.0GHz        |      | -24                 |      |       |

|                            |                                                     | f= 5.0GHz        |      | -16                 |      | dB    |

| (TB Rx_1)                  |                                                     | f= 8.0GHz        |      | -9                  |      |       |

| DDDI                       |                                                     | f= 1.35GHz       |      | -31                 |      |       |

| DDRL                       | Differential Return Loss on                         | f= 2.7GHz        |      | -27                 |      | dB    |

| (ML1)                      | DP path                                             | f= 6.0GHz        |      | -17                 |      |       |

|                            |                                                     | f = 810MHz       |      | -27                 |      |       |

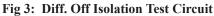

|                            | Off-isolation for DP path                           | f = 1.35GHz      |      | -22                 |      | dB    |

| Off-Isolation <sup>3</sup> |                                                     | f = 2.7GHz       |      | -16                 |      |       |

|                            |                                                     | f = 4.0GHz       |      | -16                 |      | 10    |

|                            | Off-isolatoin for TB path                           | f = 5.0GHz       |      | -15                 |      | dB    |

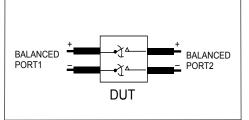

#### **Dynamic Electrical Characteristics**

Notes:

1. Guaranteed by design. Typical values are at  $V_{DD} = 3.3V$ ,  $T_A = 25^{\circ}C$  ambient and maximum loading.

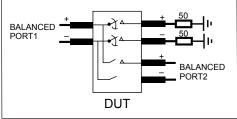

2. Refer to figure 1 for test setup

3. Refer to figure 3 for test setup

#### Buffers (HPD\_Out, CA\_DET\_Out, TBC-2, TBC-4 and LSRx)

| Parameters | Description                                      | Test Conditions              | Min. | Тур. | Max. | Units |

|------------|--------------------------------------------------|------------------------------|------|------|------|-------|

| VIH        | Input high for TBC-2, TBC-4<br>and TBC-11        | VDD = 3.6V                   | 1.8  |      |      |       |

| VIL        | Input Low for TBC-2, TBC-4<br>and TBC-11         | VDD = 3.6V                   |      |      | 0.8  | 17    |

| VOH        | Output high for HPD_Out,<br>CA_DET_Out, and LSRx | VDD = 3.3V+/-10%, Ioh = -2mA | 2.4  |      | VDD  | V     |

| VOL        | Output Low for HPD_Out,<br>CA_DET_Out and LSRx   | VDD = 3.6V, Iol = 2mA        |      |      | 0.8  |       |

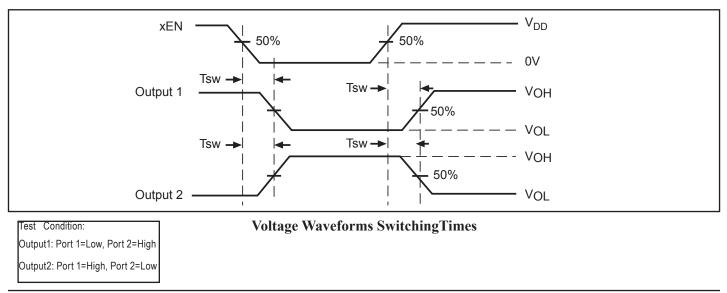

Timing

| Parameter | Description                                          | Test Conditions             |                       | Min. | Typ. <sup>(1)</sup> | Max. | Units |

|-----------|------------------------------------------------------|-----------------------------|-----------------------|------|---------------------|------|-------|

| Tsw       | Switching time between paths                         | VDD = 3.0                   | )V                    |      |                     | 2    | us    |

| Tstartup  | VDD valid to channel enable                          | VDD valio                   | d = 2.7 V             |      |                     | 10   |       |

|           | v DD vand to channel enable                          | VDD ramp is from 0V to 3.3V |                       |      |                     | 10   | us    |

| Twakeup   | From sleep mode to on mode (tog-<br>gling S0)        | VDD = 3.0V                  |                       |      |                     | 2    | us    |

| Ть-ь      | Bit-to-bit skew within the same<br>differential pair | VDD =                       | (between pin 22 & 23) |      | 2                   | 5    |       |

|           |                                                      | 3.0V (between pin 19 & 20)  |                       |      | 2                   | 5    | ps    |

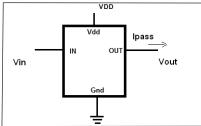

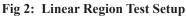

#### Linear region for Analog switches (non-buffered paths)

| Parameter  | Description                                        | Test Conditions             | Min. | Тур | Max. | Units |

|------------|----------------------------------------------------|-----------------------------|------|-----|------|-------|

| Vp_TBT     | TB Rx_1(p) and TB Rx_1(n) path $^{(2)}$            | VDD = 3.3V, Ipass =<br>10mA | 1.0  | 1.3 |      | V     |

| Vp_AUX/DDC | AUX+, AUX-, DDC_SCL, & DDC_SDA path <sup>(2)</sup> | VDD = 3.3V, Ipass = 10mA    | 3.6  | 4.2 |      | V     |

| Vp_ML      | ML1(p) and ML1(n) path <sup>(2)</sup>              | VDD = 3.3V, Ipass =<br>10mA | 2.2  | 2.5 |      | V     |

| Vp_LSTx    | LSTx signal path <sup>(2)</sup>                    | VDD = 3.3V, Ipass =<br>10mA | 3.6  | 4.2 |      | V     |

## Pull-up/Pull-downs

| Parameter | Description                     | Test Conditions                                                                       | Min. | Typ. <sup>(1)</sup> | Max.       | Units |

|-----------|---------------------------------|---------------------------------------------------------------------------------------|------|---------------------|------------|-------|

| R2        | Pull-down value on AUX+<br>path | S0 = 10G_EN = DP_EN#=TBC-4 = 0V<br>VDD=3.3V, TBC-16 = 3.3V<br>VDD = 0V, TBC-16 = 3.3V |      | 88<br>88            | 105<br>105 | Kohm  |

| R1        | Pull-up value on AUX- path      | S0 = 10G_EN = DP_EN#=TBC-4 = 0V<br>VDD = 3.3V, TBC-18 = 0V                            |      | 88                  | 105        | Kohm  |

| R4        | Pull-down value on LSRx<br>path | S0 = 10G_EN = 0V;<br>DP_EN#=TBC-11=3.3V;<br>VDD = 3.3V                                | 1    | 1.5                 |            | Mohm  |

| R3        | Pull-up value on LSTx path      | S0 = 10G_EN = 0V;<br>DP_EN# = VDD; LSTx=0V<br>VDD = 3.3V                              |      | 8.8                 | 10.5       | Kohm  |

#### Notes:

1. Typical values are at  $V_{DD} = 3.3V$ ,  $T_A = 25^{\circ}C$  ambient and maximum loading.

13-0026

2. See figure 2 for test setup

Fig 1: Diff. Insertion Loss and Return Test Circuit

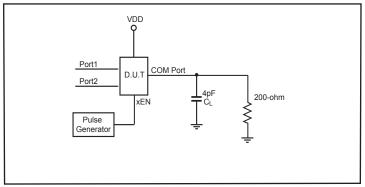

## **Test Circuit for Electrical Characteristics**<sup>(1-5)</sup>

#### Notes:

- 1.  $C_L$  = Load capacitance: includes jig and probe capacitance.

- 2.  $R_T$  = Termination resistance: should be equal to  $Z_{OUT}$  of the Pulse Generator

- 3. Output 1 is for an output with internal conditions such that the output is low except when disabled by the output control. output 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- 4. All input impulses are supplied by generators having the following characteristics: PRR  $\leq$  MHz, Z<sub>0</sub> = 50 $\Omega$ , t<sub>R</sub>  $\leq$  2.5ns, t<sub>F</sub>  $\leq$  2.5ns.

- 5. The outputs are measured one at a time with one transition per measurement.

#### **Switching Waveforms**

## Measured Insertion loss for 10Gbps Thunderbolt Path at $V_{DD}$ = 3.3V , $T_A$ = 25°C

Measured Return loss for 10Gbps Thunderbolt Path at  $V_{DD}$  = 3.3V ,  $T_{A}$  = 25°C

## Measured Data Eye for 10.3125 Gbps Thunderbolt Path at $V_{DD} = 3.0V$ , $T_A = 25^{\circ}C$ , PRBS2^7-1

Measured Data Eye for 5.4 Gbps Display Port Path at  $V_{DD}$  = 3.0V ,  $T_A$  = 25°C, PRBS2^7-1

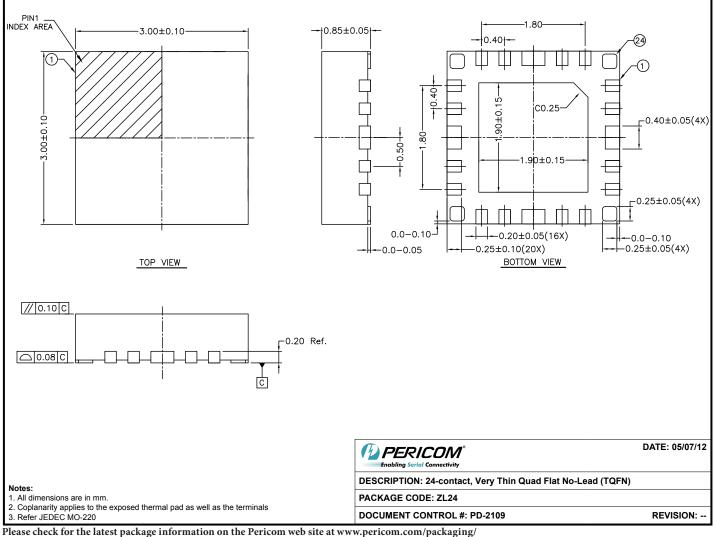

## Packaging Mechanical: 24-Contact TQFN

rease check for the fatest package information on the Pericom web site at www.pericom.com/pack

## **Ordering Information**

| Ordering Number | Package Code | Package Description             |

|-----------------|--------------|---------------------------------|

| PI3TB212ZLE     | ZL           | Pb-free & Green 24-Contact TQFN |

• Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

13-0026

• E = Pb-free and Green

• X suffix = Tape/Reel

Pericom Semiconductor Corporation • 1-800-435-2336

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Diodes Incorporated: <u>PI3TB212ZLEX</u>