I<sup>2</sup>C-bus/SPI to Quad Port Expander

### Features

- $\rightarrow$  Support Low-speed signals management and I<sup>2</sup>C aggregation across four ports

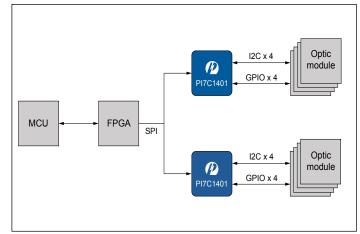

- → Support multiple PI7C1401s to control high-port-count through a single host interface

- → Selectable  $I^2C(up \text{ to } 1Mhz)$  or SPI(up to 33Mhz) host control interface

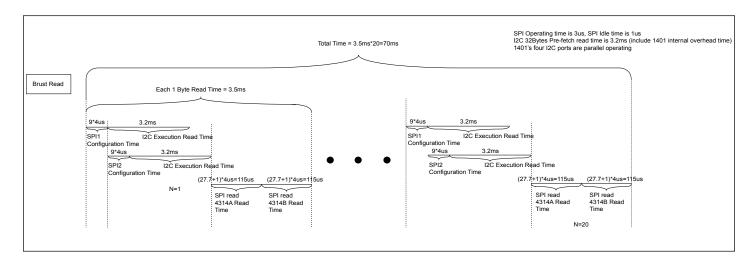

- → Automatic pre-fetching of critical, user-specified data from the modules and stored into internal 32 Byte FIFO

- → Advanced LED features for port status indication, including programmable blinking and dimming

- → Support standard SFF-8431, SFF-8472, SFF-8436, SFF-8679, INF-8074 and other such low-speed electrical interfaces, including a dedicated 100/400Khz I<sup>2</sup>C interface to each port

- → Customizable events which trigger an interrupt to the host

- → Broadcast Mode allows writes to all ports simultaneously

- → Separate host-side I/O voltage: 1.8V to 3.3V

- → Industrial Temperature Range: -40°C to 85°C

- → ESD: (HBM) 4KV, (CDM) 2KV

- → Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- → Halogen and Antimony Free. "Green" Device (Note 3)

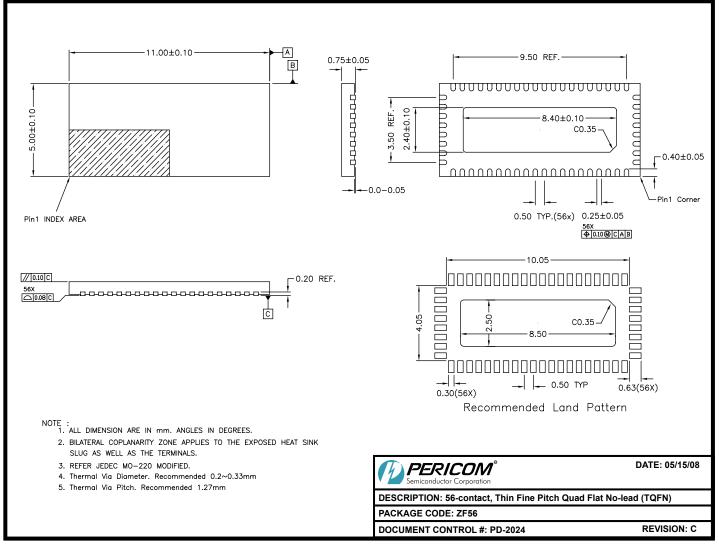

- → Packaging (Pb-free & Green):

- 56-ZF (TQFN) 5x11mm, 0.5mm pin pitch

## Software Support

- → PI7C1401 Programming Guide

- → PI7C1401 Sample Code

- → PI7C1401 Implementation Guide

## Application

- → Telecom for Wireless Base Station

- → Enterprise Switch/Router

- → Embedded System for Video

- → Storage for Data Center

Notes:

# Description

The PI7C1401 is a SPI/I<sup>2</sup>C Quad Port Expander, it's specifically designed to manage common port types such as SFP+ and QSFP+. The PI7C1401 provides an I<sup>2</sup>C/SPI interface, an interrupt output to host and four I<sup>2</sup>C interfaces, general purpose pins for low-speed control signals to the modules. The PI7C1401 can be used a wide range of applications such as Networking, Telecom, Storage, Embedded. The typical usage for this device is high volume applications requiring an "expander" to aggregate all low-speed control and I<sup>2</sup>C signals across four ports and presents a single I<sup>2</sup>C or SPI interface to host. Multiple PI7C1401s can be used in high-port-count applications with one I<sup>2</sup>C or SPI to host. The system BOM cost can be cut by using smaller IO count control devices(FPGAs, CPLDs, MCUs) and by reducing routing layer congestion.

### **Application Diagram**

<sup>1.</sup> No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

<sup>2.</sup> See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free. 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

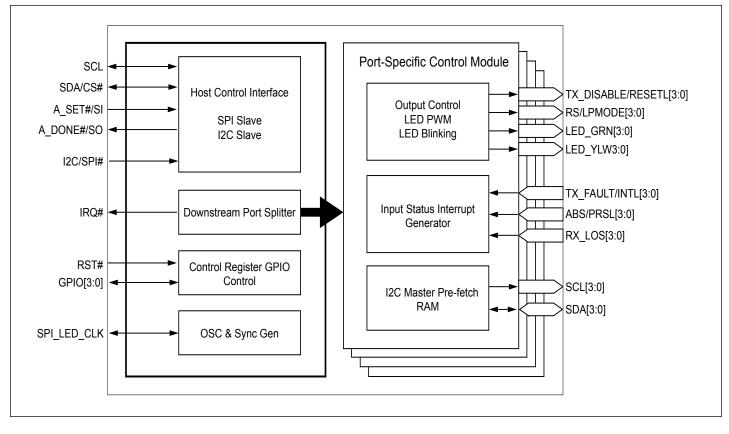

# **Block Diagram**

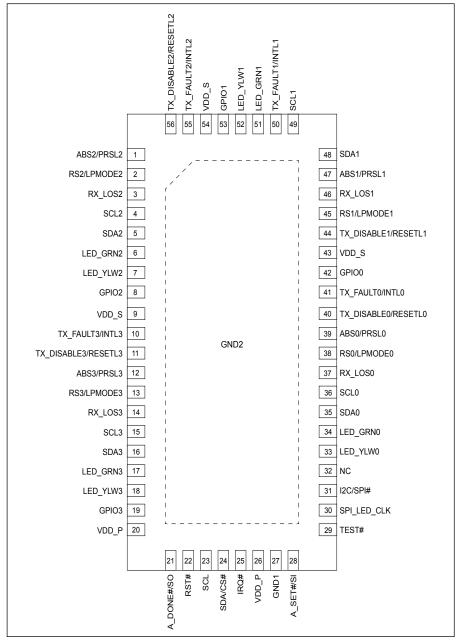

# **Pin Configuration**

# **Pin Description**

| Pin Name              | Pin# | Туре | Description                                                                                                                                                                                                     |

|-----------------------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQ#                  | 25   | OD   | Interrupt output, active low, the events which trigger an interrupt are configurable                                                                                                                            |

| SCL                   | 23   | IOD  | Primary I <sup>2</sup> C-bus or SPI serial input clock                                                                                                                                                          |

| SDA/CS#               | 24   | IOD  | Primary I <sup>2</sup> C-bus data input/output(open-drain) if I <sup>2</sup> C bus configuration is selected by I <sup>2</sup> C/SPI# pin. Chip select pin, active low if SPI configuration is selected         |

| A_SET#/SI             | 28   | IU   | Primary I <sup>2</sup> C-bus salve address assignment enable pin if I <sup>2</sup> C bus configuration is selected by I <sup>2</sup> C/SPI# pin. SPI data input pin if SPI configuration is selected            |

| A_DONE#/SO            | 21   | О    | Primary I <sup>2</sup> C-bus slave address assignment complete pin if I <sup>2</sup> C bus configura-<br>tion is selected by I <sup>2</sup> C/SPI# pin. SPI data output pin if SPI configuration is<br>selected |

| RST#                  | 22   | IU   | When set to low, PI7C1401 is held in reset state                                                                                                                                                                |

| GPIO0                 | 42   | В    | Programmable I/O pin, general purpose IO                                                                                                                                                                        |

| GPIO1                 | 53   | В    | Programmable I/O pin, general purpose IO                                                                                                                                                                        |

| GPIO2                 | 8    | В    | Programmable I/O pin, general purpose IO                                                                                                                                                                        |

| GPIO3                 | 19   | В    | Programmable I/O pin, general purpose IO                                                                                                                                                                        |

| I <sup>2</sup> C/SPI# | 31   | IU   | $I^2C$ bus or SPI interface select. $I^2C$ bus interface is selected if this pin is at logic high, SPI interface is selected if this pin is at logic low                                                        |

| SPI_LED_CLK           | 30   | BU   | LED sync pin for primary SPI mode only, connect all PI7C1401's SPI_LED_<br>CLK pins together in order to ensure LED sync for all PI7C1401 devices                                                               |

| TEST#                 | 29   | IU   | Test pin is for internal test purpose, high: normal operation, low: test mode                                                                                                                                   |

| SCL0                  | 36   | IOD  | Secondary I <sup>2</sup> C-bus output clock for port0                                                                                                                                                           |

| SCL1                  | 49   | IOD  | Secondary I <sup>2</sup> C-bus output clock for port1                                                                                                                                                           |

| SCL2                  | 4    | IOD  | Secondary I <sup>2</sup> C-bus output clock for port2                                                                                                                                                           |

| SCL3                  | 15   | IOD  | Secondary I <sup>2</sup> C-bus output clock for port3                                                                                                                                                           |

| SDA0                  | 35   | IOD  | Secondary I <sup>2</sup> C-bus data input/output, open-drain for port0                                                                                                                                          |

| SDA1                  | 48   | IOD  | Secondary I <sup>2</sup> C-bus data input/output, open-drain for port1                                                                                                                                          |

| SDA2                  | 5    | IOD  | Secondary I <sup>2</sup> C-bus data input/output, open-drain for port2                                                                                                                                          |

| SDA3                  | 16   | IOD  | Secondary I <sup>2</sup> C-bus data input/output, open-drain for port3                                                                                                                                          |

| TX_FAULT0/INTL0       | 41   | IU   | TX_FAULT0 if secondary I <sup>2</sup> C bus is connected to SFP+ optic module, INTL0 if secondary I <sup>2</sup> C bus is connected to QSFP+ optic module                                                       |

| TX_FAULT1/INTL1       | 50   | IU   | TX_FAULT1 if secondary $I^2C$ bus is connected to SFP+ optic module, INTL1 if secondary $I^2C$ bus is connected to QSFP+ optic module                                                                           |

| TX_FAULT2/INTL2       | 55   | IU   | TX_FAULT2 if secondary $I^2C$ bus is connected to SFP+ optic module, INTL2 if secondary $I^2C$ bus is connected to QSFP+ optic module                                                                           |

| TX_FAULT3/INTL3       | 10   | IU   | TX_FAULT3 if secondary $I^2C$ bus is connected to SFP+ optic module, INTL3 if secondary $I^2C$ bus is connected to QSFP+ optic module                                                                           |

# **Pin Description Cont.**

| Pin Name            | Pin# | Туре | Description                                                                                                                                               |

|---------------------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABS0/PRSL0          | 39   | IU   | ABS0 if secondary $I^2C$ bus is connected to SFP+ optic module, PRSL0 if secondary $I^2C$ bus is connected to QSFP+ optic module                          |

| ABS1/PRSL1          | 47   | IU   | ABS1 if secondary $I^2C$ bus is connected to SFP+ optic module, PRSL1 if secondary $I^2C$ bus is connected to QSFP+ optic module                          |

| ABS2/PRSL2          | 1    | IU   | ABS2 if secondary $I^2C$ bus is connected to SFP+ optic module, PRSL2 if secondary $I^2C$ bus is connected to QSFP+ optic module                          |

| ABS3/PRSL3          | 12   | IU   | ABS3 if secondary $I^2C$ bus is connected to SFP+ optic module, PRSL3 if secondary $I^2C$ bus is connected to QSFP+ optic module                          |

| RX_LOS0             | 37   | IU   | $RX\_LOS0$ if secondary $I^2C$ bus is connected to SFP+ optic module, NC if secondary $I^2C$ bus is connected to QSFP+ optic module                       |

| RX_LOS1             | 46   | IU   | RX_LOS1 if secondary I <sup>2</sup> C bus is connected to SFP+ optic module, NC if sec-<br>ondary I <sup>2</sup> C bus is connected to QSFP+ optic module |

| RX_LOS2             | 3    | IU   | RX_LOS2 if secondary I <sup>2</sup> C bus is connected to SFP+ optic module, NC if sec-<br>ondary I <sup>2</sup> C bus is connected to QSFP+ optic module |

| RX_LOS3             | 14   | IU   | $RX\_LOS3$ if secondary $I^2C$ bus is connected to SFP+ optic module, NC if secondary $I^2C$ bus is connected to QSFP+ optic module                       |

| TX_DISABLE0/RESETL0 | 40   | 0    | TX_DISABLE0 if secondary $I^2C$ bus is connected to SFP+ optic module, RE-SETL0 if secondary $I^2C$ bus is connected to QSFP+ optic module                |

| TX_DISABLE1/RESETL1 | 44   | 0    | TX_DISABLE1 if secondary $I^2C$ bus is connected to SFP+ optic module, RE-SETL1 if secondary $I^2C$ bus is connected to QSFP+ optic module                |

| TX_DISABLE2/RESETL2 | 56   | 0    | TX_DISABLE2 if secondary $I^2C$ bus is connected to SFP+ optic module, RE-SETL2 if secondary $I^2C$ bus is connected to QSFP+ optic module                |

| TX_DISABLE3/RESETL3 | 11   | 0    | TX_DISABLE3 if secondary $I^2C$ bus is connected to SFP+ optic module, RE-SETL3 if secondary $I^2C$ bus is connected to QSFP+ optic module                |

| RS0/LPMODE0         | 38   | 0    | RS0 if secondary I <sup>2</sup> C bus is connected to SFP+ optic module, LPMODE0 if secondary I <sup>2</sup> C bus is connected to QSFP+ optic module     |

| RS1/LPMODE1         | 45   | 0    | RS1 if secondary I <sup>2</sup> C bus is connected to SFP+ optic module, LPMODE1 if secondary I <sup>2</sup> C bus is connected to QSFP+ optic module     |

| RS2/LPMODE2         | 2    | 0    | RS2 if secondary I <sup>2</sup> C bus is connected to SFP+ optic module, LPMODE2 if secondary I <sup>2</sup> C bus is connected to QSFP+ optic module     |

| RS3/LPMODE3         | 13   | 0    | RS3 if secondary I <sup>2</sup> C bus is connected to SFP+ optic module, LPMODE3 if secondary I <sup>2</sup> C bus is connected to QSFP+ optic module     |

| LED_GRN0            | 34   | 0    | Green LED output for port0                                                                                                                                |

| LED_GRN1            | 51   | 0    | Green LED output for port1                                                                                                                                |

| LED_GRN2            | 6    | 0    | Green LED output for port2                                                                                                                                |

| LED_GRN3            | 17   | 0    | Green LED output for port3                                                                                                                                |

| LED_YLW0            | 33   | 0    | Yellow LED output for port0                                                                                                                               |

| LED_YLW1            | 52   | 0    | Yellow LED output for port1                                                                                                                               |

| LED_YLW2            | 7    | 0    | Yellow LED output for port2                                                                                                                               |

# **Pin Description Cont.**

| Pin Name | Pin#       | Туре | Description                                                          |

|----------|------------|------|----------------------------------------------------------------------|

| LED_YLW3 | 18         | О    | Yellow LED output for port3                                          |

| VDD_S    | 9, 43, 54  | Р    | 3.3V Power supply for down stream interface                          |

| VDD_P    | 20, 26     | Р    | 1.8V to 3.3V Power supply for primary interface I/Os (pin 21-25, 28) |

| GND1     | 27         | G    | Connect to ground                                                    |

| GND2     | Center Pad | G    | Connect to ground                                                    |

| NC       | 32         | _    | Not Connection                                                       |

Pin type: B=Bi-directional, I=Input, IU=Input with pull-up, ID=Input with pull-down, IOD=Bi-directional with open drain output, OD=Open drain output, O=Output, P=Power, G=Ground.

# **Functional Description**

The PI7C1401 can interface with four ports and aggregate the I<sup>2</sup>C and low-speed control and status signals associated with these ports into a single host-side interface (SPI or  $I^2C$ ). Multiple PI7C1401s can be combined to support up to 56 total ports, all of which are controlled via the same host-side interface. This greatly reduces the number of signals which route to the host controller.

Functionally, the PI7C1401 is organized as shown in Block Diagram on page 2. Two types of host-side control interfaces are supported (SPI or I<sup>2</sup>C) for controlling and monitoring the downstream ports. The PI7C1401 has two special outputs per downstream port

(LED\_GRN,LED\_YLW) which can be used to drive port status LEDs.

# 1. Host Interface

PI7C1401 host interface can be set as either  $I^2C$  or SPI bus depending on the strap value of the pin  $I^2C$ /SPI#.

# 1.1 I<sup>2</sup>C

When pin  $I^2C$ /SPI# is set high,  $I^2C$  is selected. PI7C1401 can support up to 1Mhz Fast-mode. The maximum number of PI7C1401 devices which can share the bus is 14. PI7C1401 does not need dedicated address pins for unique addressing since it has an autoaddressing scheme which is accomplished by connecting one PI7C1401's A\_DONE# pin to the subsequent PI7C1401's A\_SET# pin.

The first PI7C1401 will connect A\_SET# to GND, and the last PI7C1401 will connect A\_DONE# to GND. A\_SET# pin has internal pullup resistor, PI7C1401 will not respond to any I<sup>2</sup>C transaction until this pin is low. A\_DONE# pin is high-Z at default and Host controller should first configure each PI7C1401 devices to have a unique address using the default I<sup>2</sup>C address(0x1E), once the device is programmed to a new address, PI7C1401 will drive low to A\_DONE# and it will not respond to  $I^2C$  transaction using default address. After address programming is done. Pin A\_SET# and A\_DONE# are used to transfer the LED clock for blinking synchronization. Power cycling the device or toggling the RST# pin will restore the device to the default address. Each PI7C1401, each port behind the device and each logical device address within each port is accessible to the Host controller via a unique  $I^2C$  address.

Below is an example of  $I^2C$  address map:

|                       |                          | Port0          |                | Port1          |                | Po             | rt2            | Ро             | rt3            |

|-----------------------|--------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| PI7C1401<br>Instance# | PI7C1401<br>Self-Address | Device<br>0xA0 | Device<br>0xA2 | Device<br>0xA0 | Device<br>0xA2 | Device<br>0xA0 | Device<br>0xA2 | Device<br>0xA0 | Device<br>0xA2 |

| ALL                   | 0x02                     | _              | _              | _              | _              | -              | _              | _              | _              |

| 0                     | 0x04                     | 0x20           | 0x22           | 0x24           | 0x26           | 0x28           | 0x2A           | 0x2C           | 0x2E           |

| 1                     | 0x06                     | 0x30           | 0x32           | 0x34           | 0x36           | 0x38           | 0x3A           | 0x3C           | 0x3E           |

| 2                     | 0x08                     | 0x40           | 0x42           | 0x44           | 0x46           | 0x48           | 0x4A           | 0x4C           | 0x4E           |

| 3                     | 0x0A                     | 0x50           | 0x52           | 0x54           | 0x56           | 0x58           | 0x5A           | 0x5C           | 0x5E           |

| 4                     | 0x0C                     | 0x60           | 0x62           | 0x64           | 0x66           | 0x68           | 0x6A           | 0x6C           | 0x6E           |

| 5                     | 0x0E                     | 0x70           | 0x72           | 0x74           | 0x76           | 0x78           | 0x7A           | 0x7C           | 0x7E           |

| 6                     | 0x10                     | 0x80           | 0x82           | 0x84           | 0x86           | 0x88           | 0x8A           | 0x8C           | 0x8E           |

| 7                     | 0x12                     | 0x90           | 0x92           | 0x94           | 0x96           | 0x98           | 0x9A           | 0x9C           | 0x9E           |

| 8                     | 0x14                     | 0xA0           | 0xA2           | 0xA4           | 0xA6           | 0xA8           | 0xAA           | 0xAC           | 0xAE           |

| 9                     | 0x16                     | 0xB0           | 0xB2           | 0xB4           | 0xB6           | 0xB8           | 0xBA           | 0xBC           | 0xBE           |

| 10                    | 0x18                     | 0xC0           | 0xC2           | 0xC4           | 0xC6           | 0xC8           | 0xCA           | 0xCC           | 0xCE           |

| 11                    | 0x1A                     | 0xD0           | 0xD2           | 0xD4           | 0xD6           | 0xD8           | 0xDA           | 0xDC           | 0xDE           |

| 12                    | 0x1C                     | 0xE0           | 0xE2           | 0xE4           | 0xE6           | 0xE8           | 0xEA           | 0xEC           | 0xEE           |

| 13                    | 0x1E                     | 0xF0           | 0xF2           | 0xF4           | 0xF6           | 0xF8           | 0xFA           | 0xFC           | 0xFE           |

### Table 1. I<sup>2</sup>C 8-Bit Address Map

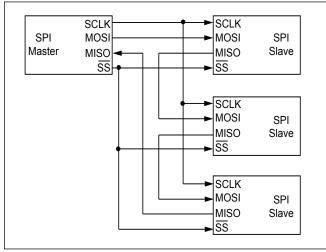

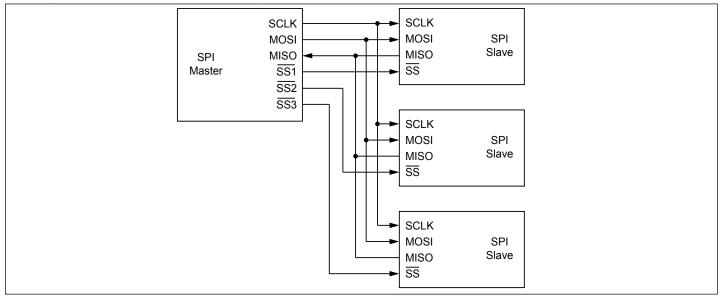

### 1.2 SPI

If I<sup>2</sup>C/SPI# is low, SPI is selected. PI7C1401 can support up to 33Mhz of SPI speed. The maximum number of PI7C1401 devices which can share a single SPI bus is unlimited. All PI7C1401 devices are connected in a daisy-chain fashion, the first PI7C1401 will connect SI to the host controller's MOSI pin, and SO of the first PI7C1401 will connect to the subsequent PI7C1401's SI pin and so on until the last PI7C1401's SO pin connects back to the host controller's MISO pin. All PI7C1401 will connect SCL and CS# to the same pin on the host controller. SI input is ignored and SO output is high-Z whenever CS# is high to synchronize LED blinking across multiple PI7C1401 devices, the SPI\_LED\_CLK pin should be connected across all PI7C1401 devices in SPI mode.

The SPI address is 12 bit and it is unique for each port and each logical devices. Refer to below table:

#### Table 2. SPI Address Map

|                       |                   | Address Range  |                |                   |                   |                   |                   |                   |                   |

|-----------------------|-------------------|----------------|----------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

|                       | Port0             |                | Port1          |                   | Port2             |                   | Port3             |                   |                   |

| PI7C1401<br>Instance# | Device<br>0xA0    | Device<br>0xA2 | Device<br>0xA0 | Device<br>0xA2    | Device<br>0xA0    | Device<br>0xA2    | Device<br>0xA0    | Device<br>0xA2    | PI7C1401<br>Regs  |

| 0                     |                   |                |                |                   |                   |                   |                   |                   |                   |

| 1                     |                   |                |                |                   |                   |                   |                   |                   |                   |

| 2                     | 0x000 to<br>0x0FF |                |                | 0x300 to<br>0x3FF | 0x400 to<br>0x4FF | 0x500 to<br>0x5FF | 0x600 to<br>0x6FF | 0x700 to<br>0x7FF | 0x800 to<br>0x8FF |

| _                     |                   |                | 0,511          | 01411             | UX311             | UX0111            | 0x/11             | 01011             |                   |

| N                     |                   |                |                |                   |                   |                   |                   |                   |                   |

## 1.2.1 SPI Frame Structure for Daisy Chain

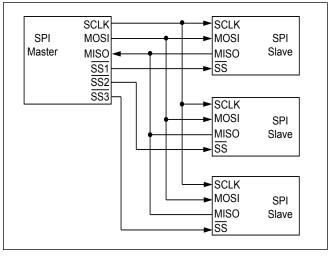

#### Figure 1. Daisy Chained SPI Bus

By default, daisy chain is used for SPI operation.

Each SPI transaction to a single PI7C1401 device is 29 bits long, please see below table:

#### **Table 3. SPI Frame Structure**

| Bit | Field | Description                                         |

|-----|-------|-----------------------------------------------------|

|     |       | 0: Write command                                    |

| 28  | R/W   | 1: Read Command                                     |

|     |       | This is the first bit shifted in on the MOSI input. |

| Bit   | Field         | Description                                                                                                              |

|-------|---------------|--------------------------------------------------------------------------------------------------------------------------|

| 27:16 | ADDR[11:0]    | 12-bit address field. See Table 2.                                                                                       |

| 15    | DATA[15]      | Busy flag. For read operations, a '1' means the downstream port is buys. For write operations, DATA[15] is a don't care. |

| 14    | DATA[14]      | Don't care.                                                                                                              |

| 13    | DATA[13]      | NACK received flag. A '1' means the PI7C1401 has received a NACK from the downstream port.                               |

| 12    | DATA[12]      | Reject flag. A '1' means the PI7C1401 has rejected the previous command because it is busy servicing a prior command.    |

| 11:8  | DATA[11:8]    | Don't care.                                                                                                              |

| 7.0   | DATA [7.0]    | 8-bit data field.                                                                                                        |

| /:0   | 7:0 DATA[7:0] | DATA[0] is the last bit shifted in on the MOSI input.                                                                    |

When daisy-chain N PI7C1401 devices, there are 29 x N bit in one SPI transaction (one CS# assertion), When CS# transit from low to high, each PI7C1401 device in the SPI chain will capture the command in its 29 bits shift registers.

The previous SPI command, address, and data are shifted out on SO as the current SPI command, address, and data are shifted in on SI. SPI read operation requires two SPI transactions, in between these two transactions, PI7C1401 fetches the requested data from wither local PI7C1401 registers or from the downstream port. And PI7C1401 shifted the data on SO in the 2nd SPI transaction. The 2nd SPI transaction can be dummy frame composed of all ones. SPI write operation requires only one SPI transaction.

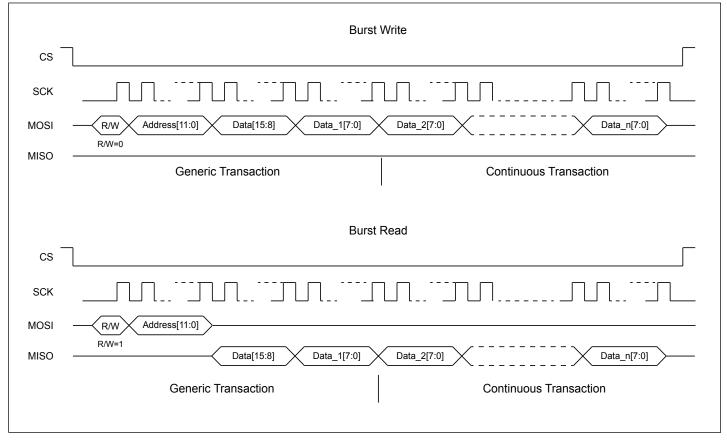

### **1.2.2 SPI Burst Transaction**

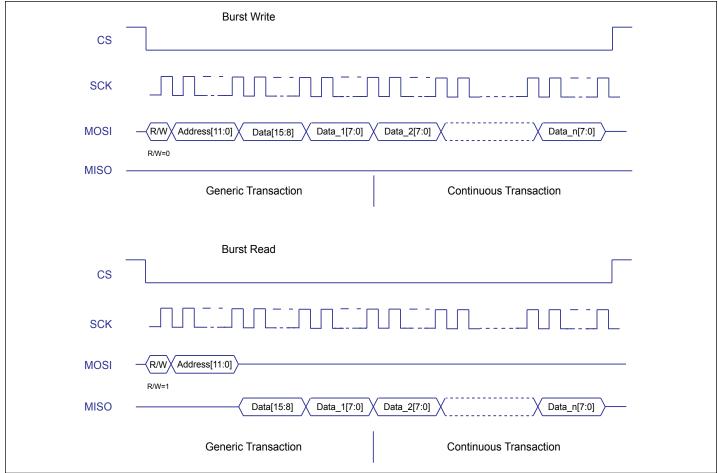

#### Figure 2. Independent Configuration SPI Bus

If SPI devices are connected in independent configuration mode, that is, each PI7C1401 has separated connection to host controller for CS#, but only share SI, SO(wired-or) and SCL. Host controller can burst read to local PI7C1401 registers (including prefetch Data registers) after set a burst read enable register.

For frame of burst read, it requires only one SPI transaction and more data byte can be read out after the first 29 bits in one SPI transaction. Host controller can stop the burst read by de-assert CS#.

Table 4. SPI Burst read/write frame structure at independent configuration

| Bit   | Field    | Description      |

|-------|----------|------------------|

| 28    | R/W      | 0: Write, 1:Read |

| 27:16 | ADDR     | 12-bit Address   |

| 15    | DATA[15] | Busyflag         |

| Bit  | Field      | Description                          |

|------|------------|--------------------------------------|

| 14   | DATA[14]   | Don't care                           |

| 13   | DATA[13]   | NACK flag                            |

| 12   | DATA[12]   | Reject flag                          |

| 11:8 | DATA[11:8] | Don't care                           |

| 7:0  | DATA[7:0]  | The first byte 8-bit data            |

| 7:0  | DATA[7:0]  | Second byte 8-bit data (continuer/w) |

| :    | :          | :                                    |

| 7:0  | DATA[7:0]  | The end of byte 8-bit data           |

#### Figure 3. SPI Burst Transaction Waveform

#### Typical SPI Bus Burst read/write Configuration

- 1. Connect PI7C1401 SPI bus in independent configuration.

- 2. Set SPI Burst Enable Register -- B1h[0] = 1 (default value 0)

- 3. Follow generic transaction continuous read (or write) local register 8-bit data.

- 4. Or follow generic transaction continuous read pre-fetch RAM's 8-bit data.

### 1.2.3 SPI Read Latency

# 2. LED Control

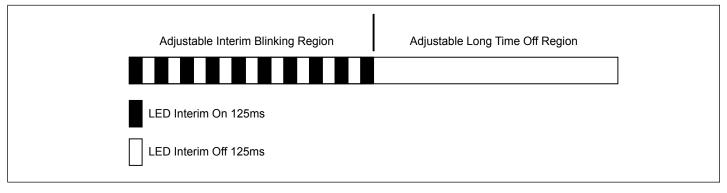

The PI7C1401 uses two sets of outputs, LED\_GRN[3:0] and LED\_YLW[3:0], to drive LEDs associated with the ports under its control. Most SFP+ and QSFP+ applications use one yellow and one green LED per port to indicate different link status such as link up, link down, and other link states.

LEDs should be connected to the PI7C1401 in an active-low fashion. When the LED\_GRN or LED\_YLW pin drives a low voltage (V<sub>OL</sub>), the LED is illuminated. When drives a high voltage (V<sub>OH</sub>), the LED is off. Bi-color LEDs can be connected in a similar fashion, and each LED should have its own current-limiting resistor. The current-limiting resistor value is selected by choosing the desired maximum current through the LED and the corresponding voltage drop from the LED's current vs. voltage plot. The sum of forward voltage drop of the LED, the voltage drop across the series resistor, and the maximum Vol. (0.5V maximum for currents between 2 and 18mA) is equal to the LED supply voltage. Note that LED\_GRN and LED\_YLW are tri-stated while the device is held in reset (during POR or while the RST# pin is low), and are enabled during normal operation and drive a high voltage by default.

Each port under the PI7C1401's control has a set of registers that allow the user to configure each LED into one of the following states:

- ♦ ON

- ♦ OFF

- PWM (ON with programmable intensity)

- BLINK (with programmable blink duty cycle, frequency, and ON intensity)

- LED blinking is configured by setting an on and an off time using control registers (see programming guide)

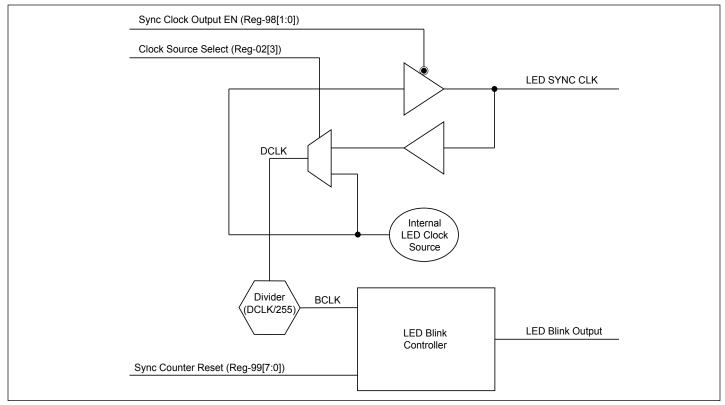

LED blinking can be synchronized across all four ports under the PI7C1401's control, and it can be synchronized across all ports in the system which are under the control of an PI7C1401. For SPI, cross-device synchronization utilizes the SPI\_LED\_CLK pin. One device is configured to forward its internal LED clock to this pin, and all other devices are configured to receive an external LED clock on this pin. For  $I^2C$ , the first device in the A DONE# to A SET# pin daisy chain is configured to output its internal LED clock to the A\_DONE# pin. All other devices are configured to receive an external LED clock from the A\_SET# pin and to output the clock to the A\_DONE# pin.

#### I2C mode daisy chain LED synchronization sequence

- 1. Set LED counter registers for each devices (same value recommend)

- 2. Set forward LED clock enable for each devices

- 3. Configure all device to receive external LED clock

- 4. All of device's LED blinking counter reset

- 5. Set the first device (nearest the host) in the daisy chain to use internal LED clock

- (LED sync clock will output from A DONE# pin)

#### SPI mode daisy chain LED synchronization sequence

- 1. Set LED counter registers for each devices (same value recommend)

- 2. Configure all device to receive external LED clock

- 3. All of device's LED blinking counter reset

- 4. Set any one device to enable LED clock output (only one device acceptable)

- 5. Set above device to use internal LED clock

- (LED sync clock will output from SPI\_LED\_CLK pin)

# 3. Low Speed downstream Outputs Control

The PI7C1401 has two general-purpose outputs per port (TX\_DISABLE/RESETL and RS/LPMODE) which can be used to drive the low-speed inputs to the module. The host controller can change the state of these outputs for each port individually, for all ports connected to a given PI7C1401 device simultaneously, or for all ports in the system simultaneously.

There are two configuration registers for these output pins (see detail in programming guide). A 10-k $\Omega$  pull-up or pull-down resis-

tor is recommended (note that SFP+ and QSFP+ modules have internal pull-up and pull-downs on certain inputs). Note that if the VDD S rail does not have power and there is an externally powered pull-up resistor connected to an output pin, the output pin will be pulled low until VDD\_S is supplied.

# 4. Low Speed Input Status and Interrupt

The PI7C1401 has three general-purpose inputs per port which can be used to monitor the low-speed outputs from the module. The host controller can monitor the status of these signals for each port by reading the appropriate registers in the PI7C1401. In addition, the PI7C1401 can be configured to generate an interrupt to the host via the IRQ# signal whenever one or more of the low-speed input signals change state. Multiple PI7C1401s' IRQ# pins can be connected together in a wired-or fashion.

The interrupt can be configured to trigger on the falling edge, the rising edge, or both the falling and rising edges. A single register stores flags for which inputs and edges are responsible for the trigger (detail see programming guide)

The PI7C1401 is also able to generate an interrupt based on pre-fetched data. This is known as a data-driven interrupt. The PI7C1401 monitors up to four bytes within the pre-fetched range for each port. For each of the bytes, the register offset address is programmed to a local PI7C1401 register as well as the enable bit fields which will trigger the interrupt. When one of the enabled bits of the four monitored bytes changes state from a '0' to a '1' and stays a '1' for two consecutive periodic pre-fetch cycles  $(0 \rightarrow 1 \rightarrow 1)$ , the interrupt is generated and the periodic pre-fetch operation is halted. The PI7C1401 has four port-specific registers which contain the sampled data from the bytes being monitored after the interrupt is triggered. To clear the interrupt, the trigger source byte's sampled data register is read. The periodic pre-fetch must be restarted after the interrupt is cleared with an  $I^2C$  command. Because it takes two periodic prefetch cycles to trigger this interrupt, it may take up to 10ms for the host to see the trigger after the downstream module's monitored bit field changes for the fastest periodic pre-fetch setting.

The PI7C1401 also has the ability to generate an interrupt if there is a abnormal behavior in the downstream I<sup>2</sup>C bus. The SDA bus and the SCL bus each have timers that will trigger an interrupt if they are held in a low state too long due to excessive clock stretching or a port error. Once the interrupt is triggered, it is cleared by issuing a port reset on the relevant port. These interrupts are known as SCL Stuck and SDA Stuck interrupts and can be configured individually for each port. By default, the SCL Stuck interrupt will trigger after the SCL bus is held low for 35ms (typical). This value is configurable individually by port. The SDA Stuck interrupt will trigger after the SDA is held low for 1 s (typical). The user may issue a port reset sequence (9 consecutive SCL clock cycles with the last being an I<sup>2</sup>C stop condition) or module reset to restore the module to a known state.

When a host-side interrupt is triggered, the host must determine the source and cause of the interrupt. The recommended procedure for identifying the source and cause of an interrupt is as follows:

1. Read the PI7C1401 aggregated port interrupt flags of the first PI7C1401 instance to see which, if any, downstream port triggered the interrupt.

2. If this instance of the PI7C1401 has any aggregated port interrupts flagged, read all of the status registers to determine the source of the interrupt and clear it. If an SCL Stuck or SDA Stuck interrupt is triggered, a port reset must be issued and the periodic pre-fetch must be restarted. The host may also perform other housekeeping activities based on the interrupt, such as change the state of the LEDs after a module is no longer present.

3. Repeat steps 1 and 2 for the next PI7C1401 instance, until the IRQ# bus is cleared.

This procedure applies to every PI7C1401 device which is wire-or'ed to the host-side interrupt signal. The total time required for the host to identify the source and cause of the interrupt for an implementation consisting of N total PI7C1401's, where all N IRQ# outputs are wire-or'ed together, is as follows:

T<sub>interrupt</sub> = Delay between the input pin changing state and the corresponding PI7C1401 device triggering an interrupt (50µs max).

T<sub>read</sub> = Time required to read a single register from N PI7C1401 devices.

For I<sup>2</sup>C mode,  $T_{read} = (9*4*N)/F_{I2C}$ , where  $F_{I2C}$  is the SCL clock frequency.

For SPI mode,  $T_{read} = (29*2*N)/F_{SPI} + T_{OFF-CSN}$ , where  $F_{SPI}$  is the SCK clock frequency, and  $T_{OFF-CSN}$  is the CS#

off time.

$T_{total} = T_{interrupt} + 4^*T_{read}$

See the Programming Guide for more details on how to configure the interrupts.

# 5. Downstream I<sup>2</sup>C Master

The PI7C1401 has four master I<sup>2</sup>C interfaces for managing up to four ports, referred to as "downstream" ports. Each downstream  $I^2C$  interface can be configured to operate with an SCL clock frequency between 100kHz and 400kHz. The downstream  $I^2C$  master supports clock stretching.

The SFF-8472 and SFF-8431 specifications define up to two logical device addresses per SFP+ port: 0xA0 and 0xA2. The SFF-8436 specification defines one logical device address per QSFP+ port: 0xA0. Both 0xA0 and 0xA2 are directly addressable by the upstream host controller. Refer to Table 1 (I<sup>2</sup>C) and Table 2 (SPI). The PI7C1401 uses this address mapping scheme to decode the port and device address and perform a downstream  $I^2C$  read or write operation. This is known as a direct access. Direct accesses have the highest priority when accessing the downstream module. If there is an on-going periodic pre-fetch or indirect write, these operations will be stopped at the next byte boundary and the direct access will be executed. The periodic pre-fetch or schedule write operation will be resumed after the direct access finishes. Note that the periodic pre-fetch will begin from the starting register offset of the pre-fetch range rather than where it left off during the interruption. If a direct access is attempted during an interrupt-driven pre-fetch, the interrupt-driven pre-fetch will finish and the direct access will be executed afterwards. If an autonomous access (pre-fetch or indirect write) occurs during a direct access, the autonomous access will be executed after the direct access is completed.

# 6. Pre-Fetch Read From Downstream Modules

The PI7C1401 can be configured to pre-fetch data from each downstream port's module. The pre-fetched data is stored locally in the PI7C1401's memory, allowing any downstream read operations in the pre-fetch range to be directly read from the PI7C1401 rather than waiting for the PI7C1401 to read from the downstream device through I<sup>2</sup>C. The PI7C1401 can pre-fetch data from the ports on a one-time basis, a regular basis (periodic pre-fetch), or upon the occurrence of certain events (interrupt-driven pre-fetch).

For periodic pre-fetching, the pre-fetched range is determined by two settings, the pre-fetch length and the pre-fetch offset address. The PI7C1401 will pre-fetch beginning at the offset address for a length of bytes between 1 and 32. The target device address is set to either 0xA0 or 0xA2. Once configured, the start bit is set to begin periodic pre-fetching and the stop bit is set to stop pre-fetching. After a pre-fetch is completed, the gate bit is reset to '0', and any attempted read operation in the pre-fetched range will return data from the PI7C1401's memory containing the last pre-fetched data. To modify the pre-fetched range or to stop the PI7C1401 from returning the data from memory, the gate bit must be set to '1'. If the PI7C1401 receives a NACK during a pre-fetch attempt, the gate bit will automatically be set to '1'. Each port has its own gate bit and separate memory and settings.

For interrupt-driven pre-fetch, the interrupt event can be configured for either the rising- or falling-edge of one of the low speed input signals of a port. The pre-fetch range and target device address is configured similarly but independently of the periodic pre-fetch settings. Interrupt-driven pre-fetch also has a gate bit and memory independent of the periodic pre-fetch. Once an interrupt-driven pre-fetch occurs successfully, an interrupt is triggered on the IRQ# pin and the aggregated interrupt flag for that port will be set. For the interrupt to be cleared and for another interrupt pre-fetch to occur, it must be re-armed with a register write. If the pre-fetch attempt is NACK'd, the gate bit will not be set, the interrupt will not be generated, and the interrupt-driven pre-fetch does not need to be re-armed. Note that the pre-fetched data from the interrupt-driven pre-fetch has precedence over the data from a periodic pre-fetch if they have overlapping pre-fetch ranges. The PI7C1401 will return data from the interrupt-driven pre-fetch even if the periodic prefetch data is more recent. When an interrupt-driven pre-fetch occurs, it is recommended that it is dealt with immediately by reading the pre-fetched data and re-arming it.

See the Programming Guide for more details on how to configure data pre-fetch.

# 7. Indirect Write

The PI7C1401 has the ability to schedule a write operation on one or more downstream modules simultaneously by writing to local PI7C1401 registers. This operation, known as a indirect write, allows for quicker writing by utilizing the faster host-side  $I^2C$  rate. The host-side I<sup>2</sup>C bus is not held while the write occurs in the downstream I<sup>2</sup>C. This command may be broadcasted to all PI7C1401 to write to any combination of ports concurrently.

indirect writes can be directed to an individual port (port Indirect Write) or to a group of two or more ports simultaneously (common indirect write). The status of the port indirect write or common indirect write may be checked in a local PI7C1401 register. This register will reflect if the operation completed successfully, or if it was NACKed by the downstream module.

indirect write operations have a higher priority than periodic pre-fetch operations. This means that if a schedule write is sent while a

periodic pre-fetch is on-going, the periodic pre-fetch will be stopped at the next byte boundary and the indirect write will be executed. The periodic pre-fetch will resume on the next period. Note that it will begin reading at the start of the pre-fetch range rather than where the indirect write occurred.

See the Programming Guide for more details on how to configure indirect write.

# 8. I<sup>2</sup>C Bus Timeouts

The PI7C1401 has a watchdog timer to ensure that the  $I^2C$  buses do not become permanently stuck. For example, if the host is performing a direct access on a downstream module, the PI7C1401 will clock stretch the host-side  $I^2C$  while the downstream  $I^2C$  transaction occurs. If the downstream module clock stretches for a very long time or any other error occurs that prevents the transaction from finishing, the host-side  $I^2C$  will not become stuck. The watchdog timer is what prevents this from happening by setting a maximum time for the downstream transaction to complete; and if it does not complete, the timer expires and the PI7C1401 will NACK the host to terminate the transaction. By default, the timer is set to 3ms and is programmable in steps of 1ms up to 127ms. This timer may also be disabled, but this is not recommended as the  $I^2C$  bus may become permanently stuck and a device reset will be necessary. Each port's  $I^2C$  master also has a programmable watchdog timer which operates similarly to the host-side  $I^2C$  watchdog timer.

When the host attempts a direct access transaction through I<sup>2</sup>C, after the I<sup>2</sup>C device ID has been ACKed, the PI7C1401 waits for the host to send a register offset address or a read/write command before downplaying it on the downstream port I<sup>2</sup>C. If the host becomes busy with something else and does not finish the I<sup>2</sup>C transaction, the PI7C1401 state machine will be stuck. There is a I<sup>2</sup>C Bus Timeout timer for each port to prevent this from happening. If the host does not finish the I<sup>2</sup>C transaction within this timer, the PI7C1401 will timeout and return to the idle state. This counter is 10ms (typical) by default and is configurable in steps of 1ms up to 255ms.

See the Programming Guide for more details on how to configure I<sup>2</sup>C Bus Timeouts.

# 9. General-Purpose Inputs/Outputs

The PI7C1401 has multiple general purpose input/output pins which can be used to control auxiliary functions on the board through the same host-side control interface which is used to manage the ports. The GPIO pins can be configured as inputs or outputs through the PI7C1401 registers.

If ringing is a concern a series resistor may be placed near the GPIO pin. A good rule of thumb for sizing the resistor is the difference of the transmission line characteristic impedance minus the driver impedance. For example in the case of a  $60\Omega$  transmission line impedance a 50 $\Omega$  series resistor may be used to minimize ringing. Cases such as these may be simulated using the provided PI7C1401 IBIS model.

## 10. Register Map

| Register Type | Definition                  |

|---------------|-----------------------------|

| RO            | Read Only                   |

| RW            | Read/Write                  |

| RWS           | Read/Write and Self-clear   |

| ROC           | Read only and Clear at read |

### Offset 00H(default=00)-Reset Register

| Bit   | Туре | Description                                                    |

|-------|------|----------------------------------------------------------------|

| [7]   | RW   | Reset local register when set                                  |

| [6:4] | RO   | Reserved                                                       |

| [3:0] | RW   | Reset port3-0 when set, it clear port logic including prefetch |

#### Offset 01H(default=3F)-I2C Device ID Register

| Bit   | Туре | Description                                                                                         |

|-------|------|-----------------------------------------------------------------------------------------------------|

| [7:1] | RW   | When bit[0] is set, Device ID can be programmed by host at I2C mode                                 |

| [0]   | RW   | This bit must be cleared when bit[7:1] is programmed<br>This bit can't be set except hardware reset |

#### Offset 02H(default=00)-External LED Clock Enable Register

| Bit   | Туре | Description                                                        |

|-------|------|--------------------------------------------------------------------|

| [7:4] | RO   | Reserved                                                           |

| [3]   | RW   | When set to 1, the external LED clock will be used for LED counter |

| [2:0] | RO   | Reserved                                                           |

#### Offset 03H(default=00)-Reserved

| Bit   | Туре | Description |

|-------|------|-------------|

| [7:0] | RO   | Reserved    |

#### Offset 04H(default=46)-I2C Slave Watchdog Timer Register

| Bit   | Туре | Description                                                                                                                                                                                                                  |

|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:1] | RW   | Host side I2C watchdog timer[6:0], the unit is ms and default is 35ms<br>The counter is armed when receives Start, disarmed when receives Stop, and cleared when see ACK. When it<br>timeout, I2C slave is set to idle state |

| [0]   | RW   | When set, disable the I2C slave watchdog timer                                                                                                                                                                               |

#### Offset 05H(default=00)-Reserved

| Bit   | Туре | Description |

|-------|------|-------------|

| [7:0] | RO   | Reserved    |

#### Offset 06H(default=00)-TX\_FAULT/INTL Inputs Status and Aggregated Interrupt Status Register

| Bit   | Туре | Description                                                                                         |

|-------|------|-----------------------------------------------------------------------------------------------------|

| [7:4] | RO   | Input status of TX_FAULT/INTL for port 3~0                                                          |

| [3:0] | RO   | Aggregated interrupt status for port 3~0. It will be cleared once all of the interrupts are cleared |

#### Offset 07H(default=00)-ABS/PRSL and RX\_LOS Inputs Status Register

| Bit   | Туре | Description                               |

|-------|------|-------------------------------------------|

| [7:4] | RO   | Input status of pin RX_LOS for port 3~0   |

| [3:0] | RO   | Input status of pin ABS/PRSL for port 3~0 |

#### Offset 08H(default=00)-TX\_DISABLE/RESET and RS/LPMODE Output Enable Register

| Bit   | Туре | Description                                            |

|-------|------|--------------------------------------------------------|

| [7:4] | RW   | Output enable for outputs RS/LPMODE of port 3~0        |

| [3:0] | RW   | Output enable for outputs TX_DISABLE/RESET of port 3~0 |

#### Offset 09H(default=FF)-LED\_YLW and LED\_GRN Output Enable Register

| Bit   | Туре | Description                                   |

|-------|------|-----------------------------------------------|

| [7:4] | RW   | Output enable for outputs LED_YLW of port 3~0 |

| [3:0] | RW   | Output enable for outputs LED_GRN of port 3~0 |

#### Offset 0AH(default=0F)-TX\_DISABLE/RESET and RS/LPMODE Output Value Register

| Bit   | Туре | Description                                           |

|-------|------|-------------------------------------------------------|

| [7:4] | RW   | Output value for outputs RS/LPMODE of port 3~0        |

| [3:0] | RW   | Output value for outputs TX_DISABLE/RESET of port 3~0 |

### Offset 0BH(default=FF)-Prefetch Gate Register

| Bit   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:4] | RO   | Interrupt driven prefetch gate register of port 3~0.When this bit is 1, host cannot access the interrupt driven prefetching range and any access falling into this range is directed to downstream port. this bit is reset to 0 when interrupt driven prefetching has completed successfully. and host can directly access the memory if it fall into the range. This bit is set to 1 when interrupt driven prefetching is re-armed or disabled. if the interrupt driven prefetching is overlaps the periodic prefetch range,host will get data from the interrupt driven prefetching memory. |

| [3:0] | RW   | Periodic prefetch gate register of port 3~0. When this bit is 1, host cannot access the periodic prefetching range and any access falling into this range is directed to downstream port. This bit is reset to 0 when prefetching has completed successfully. and host can directly access the memory if it fall into the range. This bit should be set to 1 when pre-fetching range is modified or periodic prefetch is stopped.                                                                                                                                                             |

#### Offset 0CH(default=00)-Interrupt Driven Prefetch Source Register

| Bit   | Туре | Description                                                                                                                                                                                                             |

|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6] | RW   | Interrupt driven prefetch source register of port 3<br>0h = interrupt driven prefetch is disabled<br>1h = input pin TX_FAULT3 is selected<br>2h = input pin ABS/PRSL3 is selected<br>3h = input pin RX_LOS3 is selected |

| [5:4] | RW   | Interrupt driven prefetch source register of port 2<br>0h = interrupt driven prefetch is disabled<br>1h = input pin TX_FAULT2 is selected<br>2h = input pin ABS/PRSL2 is selected<br>3h = input pin RX_LOS2 is selected |

| [3:2] | RW | Interrupt driven prefetch source register of port 1<br>0h = interrupt driven prefetch is disabled<br>1h = input pin TX_FAULT1 is selected<br>2h = input pin ABS/PRSL1 is selected<br>3h = input pin RX_LOS1 is selected |

|-------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1:0] | RW | Interrupt driven prefetch source register of port 0<br>0h = interrupt driven prefetch is disabled<br>1h = input pin TX_FAULT0 is selected<br>2h = input pin ABS/PRSL0 is selected<br>3h = input pin RX_LOS0 is selected |

#### Offset 0DH(default=00)-Downstream Address 0xA2 Absence Register

| Bit   | Туре | Description                                                                                                                                                                                               |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:4] | RO   | Reserved                                                                                                                                                                                                  |

| [3:0] |      | Downstream address 0xA2 absence control for port 3~0. When this bit is set to 1, the device address 0xA2 is absent and access to 0xA2 from host will be Nacked without being sent to the downstream port. |

### Offset 0EH(default=00)-I2C LED Clock Output Enable Register

| Bit   | Туре | Description                                                                                     |

|-------|------|-------------------------------------------------------------------------------------------------|

| [7:5] | RW   | 3'b000 : pin A_DONE# is set to default functionality<br>3'b001 : pin A_DONE# outputs LED clock. |

| [4:0] | RO   | Reserved                                                                                        |

#### Offset 0FH(default=--)-GPIO and Pin Status Register

| Bit | Туре | Description                |

|-----|------|----------------------------|

| [7] | RO   | status of pin I2C/SPI#     |

| [6] | RO   | status of pin SPI_LED_SYNC |

| [5] | RO   | status of pin A_DONE#      |

| [4] | RO   | status of pin A_SET#       |

| [3] | RO   | status of pin GPIO3        |

| [2] | RO   | status of pin GPIO2        |

| [1] | RO   | status of pin GPIO1        |

| [0] | RO   | status of pin GPIO0        |

### Offset 10H/30H/50H/70H(default=00)-Reserved

| Bit   | Туре | Description |

|-------|------|-------------|

| [7:0] | RO   | Reserved    |

#### Offset 11H/31H/51H/71H(default=98)-Port 0~3 SCL High Time Register

| Bit   | Туре | Description                                                                                                                                                                                              |

|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | RW   | Port I2C SCL high time in number of main clock(27Mhz +/- 10%) together with SCL Low Time register to define the port I2C bit rate.<br>set to 0x98 gives 100K at most.<br>set to 0x26 gives 400K at most. |

#### Offset 12H/32H/52H/72H(default=98)-Port 0~3 SCL Low Time Register

| Bit   | Туре | Description                                                                                                                                                                                                                                                               |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | RW   | Port I2C SCL low time in number of main clock(27Mhz +/- 10%) together with SCL High Time register to<br>define the port I2C bit rate.<br>set to 0x98 gives 100K at most.<br>set to 0x26 gives 400K at most.<br>This register can only be programmed to be laess than 0xAA |

#### Offset 13H/33H/53H/73H(default=A0)-Port 0~3 Downstream I2C Device ID Modifier Register

| Bit   | Туре | Description                                                             |

|-------|------|-------------------------------------------------------------------------|

| [7:3] | RW   | Upper five bit of I2C Device ID.                                        |

| [2]   | RW   | When set to 1, it disable the port I2C watchdog timer(A9H/AAH/ABH/ACH). |

| [1]   | RW   | Downstream I2C Device ID bit 2                                          |

| [0]   | RO   | Reserved                                                                |

### Offset 14H/34H/54H/74H(default=00)-Port 0~3 LED\_GRN PWM Control Register

| Bit   | Туре | Description                                                                                                                                                                                                                                 |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | RW   | Control the PWM on time of LED_GRN output for LED brightness.<br>FFh is the brightnest setting, and 01h is the dimmest setting, 00h is completely off.<br>On time value = This register value x 10 us<br>Off time value = 2.55ms - On time. |

#### Offset 15H/35H/55H/75H(default=00)-Port 0~3 LED\_YLW PWM Control Register

|   | Bit   | Туре | Description                                                                                                                                                                                                                                 |

|---|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [ | [7:0] | RW   | Control the PWM on time of LED_YLW output for LED brightness.<br>FFh is the brightnest setting, and 01h is the dimmest setting, 00h is completely off.<br>On time value = This register value x 10 us<br>Off time value = 2.55ms - On time. |

#### Offset 16H/36H/56H/76H(default=00)-Port 0~3 LED\_GRN Blink On Control Register

| Bit   | Туре | Description                                                                                                                                                                                |

|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] |      | When Blinking mode is set, control the BLINKING on time of LED_GRN output, the unit is 2.5ms.<br>When 4x long on/off time blink mode is set, the unit is 10ms setting to 0 is not allowed. |

#### Offset 17H/37H/57H/77H(default=00)-Port 0~3 LED\_GRN Blink Off Control Register

| Bit   | Туре | Description                                                                                                                                                                             |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] |      | Control the BLINKING off time of LED_GRN output When Blinking mode is set, the unit is 2.5ms. When 4x long on/off time blink mode is set, the unit is 10ms setting to 0 is not allowed. |

#### Offset 18H/38H/58H/78H(default=00)-Port 0~3 LED\_YLW Blink On Control Register

| Bit   | Туре | Description                                                                                                                                                                                |

|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] |      | When Blinking mode is set, control the BLINKING on time of LED_YLW output, the unit is 2.5ms.<br>When 4x long on/off time blink mode is set, the unit is 10ms setting to 0 is not allowed. |

#### Offset 19H/39H/59H/79H(default=00)-Port 0~3 LED\_YLW Blink Off Control Register

| Bit   | Туре | Description                                                                                                                                                                                |

|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] |      | Control the BLINKING off time of LED_YLW output When Blinking mode is set, the unit is 2.5ms.<br>When 4x long on/off time blink mode is set, the unit is 10ms setting to 0 is not allowed. |

#### Offset 1AH/3AH/5AH/7AH(default=30)-Port 0~3 LED Mode Select Register

| Bit   | Туре | Description                                                                                                                                                                    |

|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6] | RW   | LED long time blink mode select:<br>0h = OFF<br>1h = LED_GRN/YLW 4x long on/off time mode enable<br>2h = Reserved<br>3h = LED_GRN/YLW 125ms interminttent blinking mode enable |

| [5]   | RW   | When set, inverts the LED_YLW output for active low LED                                                                                                                        |

| [4]   | RW   | When set, inverts the LED_GRN output for active low LED                                                                                                                        |

| [3:2] | RW   | LED mode select for LED_YLW:<br>0h = OFF<br>1h = ON(no PWM)<br>2h = PWM(for dimming)<br>3h = BLINK                                                                             |

| [1:0] | RW   | LED mode select for LED_GRN:<br>0h = OFF<br>1h = ON(no PWM)<br>2h = PWM(for dimming)<br>3h = BLINK                                                                             |

#### Offset 1BH/3BH/5BH/7BH(default=00)-Port 0~3 Interrupt Driven Prefetch Control Register

| Bit   | Туре | Description                                                                                                             |

|-------|------|-------------------------------------------------------------------------------------------------------------------------|

| [7:3] | RW   | Number of bytes of interrupt driven prefetch range is equal to this register plus one. between single byte to 32 bytes. |

| [2]   | RW   | When set, enable modified down port ID of device full features                                                          |

| [1]   | RW   | Define which edge of the input pin will trigger the prefetch<br>0h = falling edge<br>1h = rising edge                   |

| [0] | RW | Define the I2C device address for interrup driven prefetching:<br>0h = 0xA0<br>1h = 0xA2 |

|-----|----|------------------------------------------------------------------------------------------|

|     |    | 1h = 0xA2                                                                                |

#### Offset 1CH/3CH/5CH/7CH(default=00)-Port 0~3 Interrupt Driven Prefetch Offset Address Register

| Bit   | Туре | Description                                                  |

|-------|------|--------------------------------------------------------------|

| [7:0] | RW   | Define the starting address of interrupt driven prefetching. |

#### Offset 1DH/3DH/5DH/7DH(default=00)-Port 0~3 Periodic Prefetch Control Register

| Bit   | Туре | Description                                                                                                                                                  |

|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:3] | RW   | Number of bytes of periodic prefetch range is equal to this register plus one. between single byte to 32 bytes.                                              |

| [2]   | RWS  | Set to 1 will stop the ongoing periodic prefetch.<br>This bit is self cleared when the prefetching is stopped on the port.                                   |

| [1]   | RW   | Set to 1 will start the periodic prefetch.<br>This bit is cleared when bit 2(Stop) is set to 1 or self cleared if the prefetch period is set to 0(one-time). |

| [0]   | RW   | Define the I2C device address for periodic prefetching:<br>0h = 0xA0<br>1h = 0xA2                                                                            |

#### Offset 1EH/3EH/5EH/7EH(default=00)-Port 0~3 Periodic Prefetch Offset Address Register

| Bit   | Туре | Description                                          |

|-------|------|------------------------------------------------------|

| [7:0] | RW   | Define the starting address of periodic prefetching. |

#### Offset 1FH/3FH/5FH/7FH(default=00)-Port 0~3 Periodic Prefetch Period Register

| Bit   | Туре | Description                                                                     |

|-------|------|---------------------------------------------------------------------------------|

| [7:0] |      | Define the period of periodic prefetching in unit of 5ms                        |

| [,.0] | 1000 | Maximum of 1.3 seconds can be set. Setting to 0 will trigger one-time prefetch. |

#### Offset 20H/40H/60H/80H(default=00)-Port 0~3 Input Pin Interrupt Enable Register

| Bit | Туре | Description                                                     |

|-----|------|-----------------------------------------------------------------|

| [7] | RW   | When set, ABS/PRSL 2s hot-plug interrupt delay enable           |

| [6] | RW   | When set, TX_FAULT/INTL 300ms input window gate enable          |

| [5] | RW   | Setting 1 enable interrupt at falling edge of pin ABS/PRSL      |

| [4] | RW   | Setting 1 enable interrupt at rising edge of pin ABS/PRSL       |

| [3] | RW   | Setting 1 enable interrupt at falling edge of pin RXLOS         |

| [2] | RW   | Setting 1 enable interrupt at rising edge of pin RXLOS          |

| [1] | RW   | Setting 1 enable interrupt at falling edge of pin TX_FAULT/INTL |

| [0] | RW   | SSetting 1 enable interrupt at rising edge of pin TX_FAULT/INTL |

#### Offset 21H/41H/61H/81H(default=80)-Port 0~3 Interrupt Status and Interrupt Driven Prefetch Re-Arm Register

| Bit | Туре | Description                                                                                                                                                                                                                                       |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7] | RW   | This bit is cleared when an interrupt-driven prefetching is completed successfully on the port.<br>Setting to 1 will clear the interrupt on IRQ# caused by interrupt-driven prefetching completeness and re-arm the interrupt driven prefetching. |

| [6] | RO   | Data driven interrupt status from periodic prefetch.<br>It is cleared when sampled data register from the triggered byte is cleared.                                                                                                              |

| [5] | ROC  | Interrupt status of falling edge of input ABS/PRSL. It is cleared when read.                                                                                                                                                                      |

| [4] | ROC  | Interrupt status of rising edge of input ABS/PRSL. It is cleared when read.                                                                                                                                                                       |

| [3] | ROC  | Interrupt status of falling edge of input RXLOS. It is cleared when read.                                                                                                                                                                         |

| [2] | ROC  | Interrupt status of rising edge of input RXLOS. It is cleared when read.                                                                                                                                                                          |

| [1] | ROC  | Interrupt status of falling edge of input TX_FAULT/INTL It is cleared when read.                                                                                                                                                                  |

| [0] | ROC  | Interrupt status of rising edge of input TX_FAULT/INTL It is cleared when read.                                                                                                                                                                   |

#### Offset 22H/42H/62H/82H(default=00)-Port 0~3 Data Driven Interrupt Index 0 Offset Address Register

| Bit   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | RW   | Offset register for data-driven interrupt byte(Index 0)<br>This offset must be within the periodic prefetch range. When specific bits(defined in Data Driven Interrupt<br>Index 0 Bit Enable Register) in the prefetched data of this specific offset changes from 0 to 1 and stay at 1 for<br>two prefetch cycles, the data driven interrupt will be triggered and periodic prefetch will be halted. |

#### Offset 23H/43H/63H/83H(default=00)-Port 0~3 Data Driven Interrupt Index 1 Offset Address Register

| Bi   | it | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|------|----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0 | 0] | RW   | Offset register for data-driven interrupt byte(Index 1)<br>This offset must be within the periodic prefetch range.<br>When specific bits(defined in Data Driven Interrupt Index 1 Bit Enable Register) in the prefetched data of this<br>specific offset changes from 0 to 1 and stay at 1 for two prefetch cycles, the data driven interrupt will be trig-<br>gered and periodic prefetch will be halted. |

#### Offset 24H/44H/64H/84H(default=00)-Port 0~3 Data Driven Interrupt Index 2 Offset Address Register

| Bit   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | RW   | Offset register for data-driven interrupt byte(Index 2)<br>This offset must be within the periodic prefetch range. When specific bits(defined in Data Driven Interrupt<br>Index 2 Bit Enable Register) in the prefetched data of this specific offset changes from 0 to 1 and stay at 1 for<br>two prefetch cycles, the data driven interrupt will be triggered and periodic prefetch will be halted. |

#### Offset 25H/45H/65H/85H(default=00)-Port 0~3 Data Driven Interrupt Index 3 Offset Address Register

|   | Bit  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                             |