AP7179D

### 3A, ULTRA LOW NOISE, HIGH ACCURACY, LDO VOLTAGE REGULATOR

### **Description**

The DIODES<sup>TM</sup> AP7179D is a high output current (3A), low-dropout regulator capable of sourcing 3A with 180mV maximum dropout, low-noise (4.4 $\mu$ V<sub>RMS</sub>), high output voltage accuracy (1%). The device output voltage is pin-programmable from 0.8V to 3.95V using a PCB layout and adjustable from 0.8V to 5.0V using an external resistor divider. The device supports a lower input voltage of 1.1V, which makes it flexible to use and requires a lower component count.

The device's low noise  $(4.4 \mu V_{RMS})$ , high PSRR, and high output current capability makes it ideal to power noise-sensitive devices such as high-performance serializers and deserializers (SerDes), analog-to-digital converters (ADCs), digital-to-analog converters (DACs), and RF components.

High output accuracy, remote sensing, excellent transient performance, and soft-start capabilities also make the AP7179D ideal to power digital loads such as field-programmable gate arrays (FPGAs), digital signal processors (DSPs), and application-specific integrated circuits (ASICs).

The enable control and a power-good indicator provide easy and accessible power-sequence control. Output noise immunity is enhanced by adding a bypass capacitor on NR/SS pin.

The AP7179D is packaged in the W-QFN3535-20 (Type A1) package.

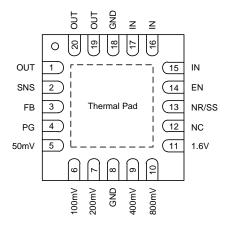

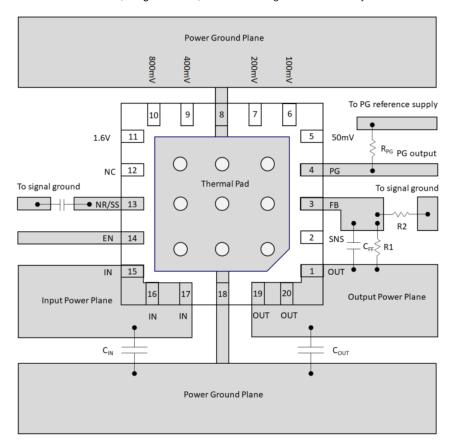

### **Pin Assignments**

(Top View)

W-QFN3535-20 (Type A1)

### **Features**

- Low V<sub>IN</sub> and Wide V<sub>IN</sub> Range: 1.1V to 6.5V

- Low Dropout Voltage: 180mV at 3A

- V<sub>OUT</sub> Accuracy ±1% Over Line, Load, and Temperature

- Pin-Strapped Output Voltage

- Output Voltage Range: 0.8V to 3.95V

- Adjustable Output Voltage

- Output Voltage Range: 0.8V to 5.5V

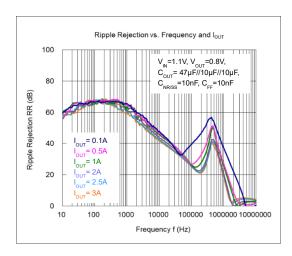

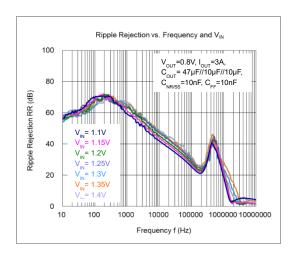

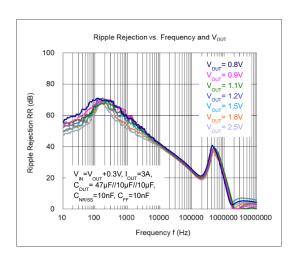

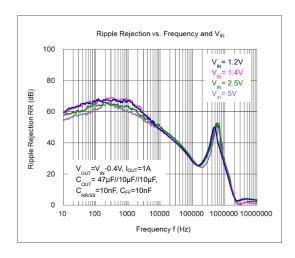

- Ultra-High PSRR: 40dB at 500kHz

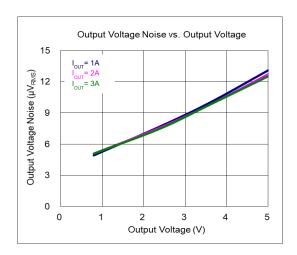

- Output Voltage Noise:

- 4.4µVRMS at 0.8V Output

- 7.7µVRMS at 5.0V Output

- Adjustable Soft-Start Output

- Open-Drain Power-Good Indicator Function

- Stable with a 47µF or Larger Ceramic Output Capacitor

- Excellent Load Transient Response

- Enable Control

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

- For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/104/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please contact us or your local Diodes representative. https://www.diodes.com/quality/product-definitions/

### **Applications**

- Portable electronic devices

- Digital loads: SerDes, FPGAs, and DSPs

- Analog circuits applications: VCO, ADC, DAC, and LVDS

- Test and measurement equipment

Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- 2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

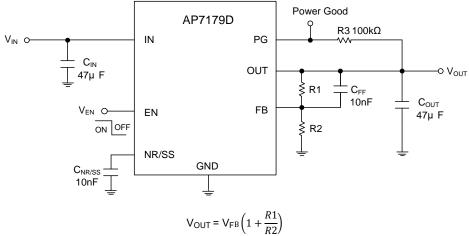

## **Typical Applications Circuit**

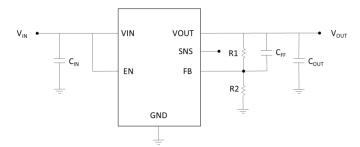

Figure 1. Configuration Circuit for V<sub>OUT</sub> Adjusted by a Resistive Divider

Table 1. Recommended Feedback-Resistor Values

| Output Voltage(V) | <b>External Restive Divider Combinations</b> |        |  |  |  |

|-------------------|----------------------------------------------|--------|--|--|--|

| Output Voltage(V) | R1(KΩ)                                       | R2(KΩ) |  |  |  |

| 0.9               | 12.4                                         | 100    |  |  |  |

| 1                 | 12.4                                         | 49.9   |  |  |  |

| 1.2               | 12.4                                         | 24.9   |  |  |  |

| 1.5               | 12.4                                         | 14.3   |  |  |  |

| 1.8               | 12.4                                         | 10     |  |  |  |

| 2.5               | 12.4                                         | 5.9    |  |  |  |

| 3.3               | 11.8                                         | 3.74   |  |  |  |

| 4.5               | 11.8                                         | 2.55   |  |  |  |

| 5                 | 12.4                                         | 2.37   |  |  |  |

$V_{OUT} = V_{REF} + 50mV + 400mV = 0.8V + 50mV + 400mV = 1.25V$

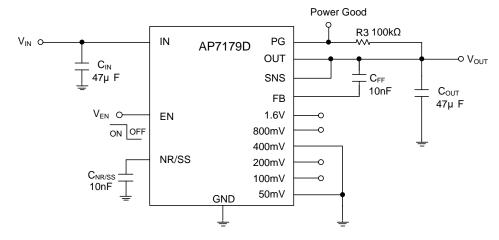

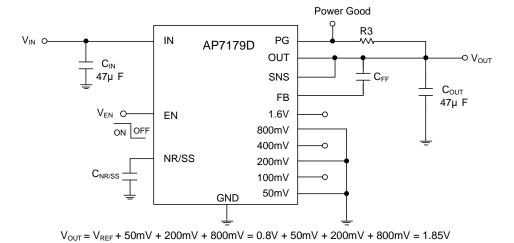

Figure 2. Configuration Circuit for  $V_{\text{OUT}}$  Adjusted via PCB layout

## Typical Applications Circuit (continued)

Table 2. Programming VOUT Target by Output Voltage Setting Pin

| V <sub>OUT</sub> (V) | 50mV | 100mV | 200mV | 400mV | 800mV | 1.6V | V <sub>OUT</sub> (V) | 50mV | 100mV | 200mV | 400mV | 800mV | 1.6V |

|----------------------|------|-------|-------|-------|-------|------|----------------------|------|-------|-------|-------|-------|------|

| 0.80                 | Open | Open  | Open  | Open  | Open  | Open | 2.40                 | Open | Open  | Open  | Open  | Open  | GND  |

| 0.85                 | GND  | Open  | Open  | Open  | Open  | Open | 2.45                 | GND  | Open  | Open  | Open  | Open  | GND  |

| 0.90                 | Open | GND   | Open  | Open  | Open  | Open | 2.50                 | Open | GND   | Open  | Open  | Open  | GND  |

| 0.95                 | GND  | GND   | Open  | Open  | Open  | Open | 2.55                 | GND  | GND   | Open  | Open  | Open  | GND  |

| 1.00                 | Open | Open  | GND   | Open  | Open  | Open | 2.60                 | Open | Open  | GND   | Open  | Open  | GND  |

| 1.05                 | GND  | Open  | GND   | Open  | Open  | Open | 2.65                 | GND  | Open  | GND   | Open  | Open  | GND  |

| 1.10                 | Open | GND   | GND   | Open  | Open  | Open | 2.70                 | Open | GND   | GND   | Open  | Open  | GND  |

| 1.15                 | GND  | GND   | GND   | Open  | Open  | Open | 2.75                 | GND  | GND   | GND   | Open  | Open  | GND  |

| 1.20                 | Open | Open  | Open  | GND   | Open  | Open | 2.80                 | Open | Open  | Open  | GND   | Open  | GND  |

| 1.25                 | GND  | Open  | Open  | GND   | Open  | Open | 2.85                 | GND  | Open  | Open  | GND   | Open  | GND  |

| 1.30                 | Open | GND   | Open  | GND   | Open  | Open | 2.90                 | Open | GND   | Open  | GND   | Open  | GND  |

| 1.35                 | GND  | GND   | Open  | GND   | Open  | Open | 2.95                 | GND  | GND   | Open  | GND   | Open  | GND  |

| 1.40                 | Open | Open  | GND   | GND   | Open  | Open | 3.00                 | Open | Open  | GND   | GND   | Open  | GND  |

| 1.45                 | GND  | Open  | GND   | GND   | Open  | Open | 3.05                 | GND  | Open  | GND   | GND   | Open  | GND  |

| 1.50                 | Open | GND   | GND   | GND   | Open  | Open | 3.10                 | Open | GND   | GND   | GND   | Open  | GND  |

| 1.55                 | GND  | GND   | GND   | GND   | Open  | Open | 3.15                 | GND  | GND   | GND   | GND   | Open  | GND  |

| 1.60                 | Open | Open  | Open  | Open  | GND   | Open | 3.20                 | Open | Open  | Open  | Open  | GND   | GND  |

| 1.65                 | GND  | Open  | Open  | Open  | GND   | Open | 3.25                 | GND  | Open  | Open  | Open  | GND   | GND  |

| 1.70                 | Open | GND   | Open  | Open  | GND   | Open | 3.30                 | Open | GND   | Open  | Open  | GND   | GND  |

| 1.75                 | GND  | GND   | Open  | Open  | GND   | Open | 3.35                 | GND  | GND   | Open  | Open  | GND   | GND  |

| 1.80                 | Open | Open  | GND   | Open  | GND   | Open | 3.40                 | Open | Open  | GND   | Open  | GND   | GND  |

| 1.85                 | GND  | Open  | GND   | Open  | GND   | Open | 3.45                 | GND  | Open  | GND   | Open  | GND   | GND  |

| 1.90                 | Open | GND   | GND   | Open  | GND   | Open | 3.50                 | Open | GND   | GND   | Open  | GND   | GND  |

| 1.95                 | GND  | GND   | GND   | Open  | GND   | Open | 3.55                 | GND  | GND   | GND   | Open  | GND   | GND  |

| 2.00                 | Open | Open  | Open  | GND   | GND   | Open | 3.60                 | Open | Open  | Open  | GND   | GND   | GND  |

| 2.05                 | GND  | Open  | Open  | GND   | GND   | Open | 3.65                 | GND  | Open  | Open  | GND   | GND   | GND  |

| 2.10                 | Open | GND   | Open  | GND   | GND   | Open | 3.70                 | Open | GND   | Open  | GND   | GND   | GND  |

| 2.15                 | GND  | GND   | Open  | GND   | GND   | Open | 3.75                 | GND  | GND   | Open  | GND   | GND   | GND  |

| 2.20                 | Open | Open  | GND   | GND   | GND   | Open | 3.80                 | Open | Open  | GND   | GND   | GND   | GND  |

| 2.25                 | GND  | Open  | GND   | GND   | GND   | Open | 3.85                 | GND  | Open  | GND   | GND   | GND   | GND  |

| 2.30                 | Open | GND   | GND   | GND   | GND   | Open | 3.90                 | Open | GND   | GND   | GND   | GND   | GND  |

| 2.35                 | GND  | GND   | GND   | GND   | GND   | Open | 3.95                 | GND  | GND   | GND   | GND   | GND   | GND  |

### **Pin Descriptions**

| Pin Number             | Pin Name | Function                                                                                                                                                                                                                                                                                                            |

|------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 19, 20              | OUT      | LDO output pin. Connect a 47µF or larger ceramic capacitor (22µF or greater of capacitance) is required for stability and the output capacitor as close to the device as possible to minimize the impedance between OUT pin to load.                                                                                |

| 2                      |          | Output voltage sense input pin. Connect this pin to OUT only if using the programmed output voltage function (set the output voltage via PCB layout). If the OUT voltage is set by external resistor, leave this pin floating.                                                                                      |

| 3                      | FB       | Feedback voltage pin connected to the error amplifier. This pin is used to set the output voltage by an external resistive divider. The typically reference voltage is 0.8V.                                                                                                                                        |

| 4                      | PG       | Output voltage power good indicator pin. Active-high with open-drain outputs when output voltage reaches 88% of the target. The pin is pulled to ground when the output voltage is lower than threshold, EN pulled down, OCP and OTP.                                                                               |

| 5, 6, 7, 9, 10, 11     |          | Output voltage setting pins. Connect these pins to ground or leave floating. Connecting theses pins to ground increases the output voltage; multiple pins can be simultaneously connected to GND to select the desired output voltage. Leaves these pins floating (open) when not in use.                           |

| 8,18, 21 (Exposed Pad) | GND      | Ground pin. These pins must be connected to ground. The exposed pad solders to ground with large PCB to enhance the power dissipation.                                                                                                                                                                              |

| 12                     | NC       | No internal connection. Leave this pin floating doesn't affect the chip functionality.                                                                                                                                                                                                                              |

| 13                     | NR/SS    | Noise-reduction and soft-start pin. This pin Connect an external capacitor to ground reduce the reference voltage noise and slow down the output voltage rise as a soft-start. A 10nF or larger capacitor connects between NR/SS to ground for low noise applications.                                              |

| 14                     | EN       | Enable pin. Connecting this pin to logic high enables the device or connecting this pin to logic low disables the device. If enable functionality is required; connecting high with EN pin after $V_{IN}$ voltage is established. Connecting EN pin to $V_{IN}$ always, if the enable functionality is not required |

| 15, 16, 17             | IN       | Input supply voltage pin. Connecting a $47\mu F$ or large ceramic capacitor from IN to ground as close as possible to get better noise rejection performance.                                                                                                                                                       |

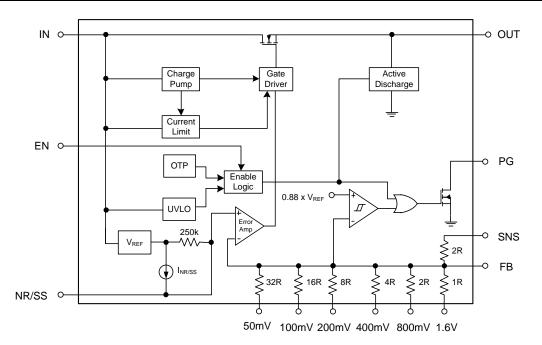

## **Functional Block Diagram**

### **Feature Descriptions**

#### Operation

The AP7179D operates with single supply input range from 1.1V to 6.5V and is capable of delivering 3A current to output. The device has a high PSRR, and its low noise provides a clean supply to the application.

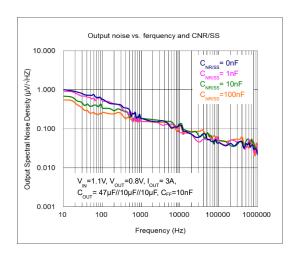

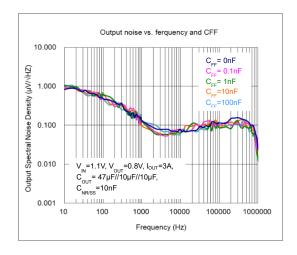

A low-noise reference and error amplifier are included to reduce device noise. The  $C_{NR/SS}$  capacitor filters the noise from the reference and the  $C_{FF}$  feed-forward capacitor filters the noise from the error amplifier. The power-supply rejection ratio (PSRR) of the AP7179D minimizes the coupling of input supply noise to the output. The combination of a low noise-floor and high PSRR ensure that the device provides a clean supply to the application.

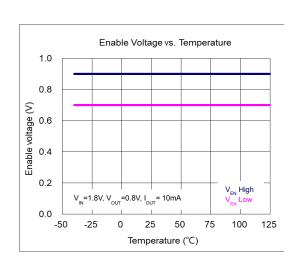

#### **Enable and Shutdown**

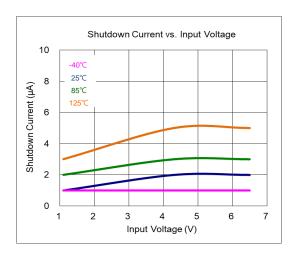

The AP7179D provides an EN pin, as an external chip enable control, to enable or disable the device. A  $V_{EN}$  below 0.5V turns the regulator off and enters shutdown mode. When the  $V_{EN}$  is above 1.1V, it turns the regulator on. When the regulator is shut down, the ground current is reduced to a maximum of 25 $\mu$ A. The enable circuitry has hysteresis (typically 50mV) with relatively slow, ramping analog signals. When the enable function is not desired, the EN must be tied as close as possible to the VIN \ to prevent voltage drops on the VIN line from triggering the enable circuit.

#### **VOUT Programming Pins**

The AP7179D's built-in matched feedback resistor network sets the output voltage. The output voltage can be programmed from 0.8V to 3.95V, with 50mV steps by tying programming pins 5 to 11 to the ground. Tying any of the VOUT programming pins to SNS can lower the value of the upper resistor divider and increase programming resolution.

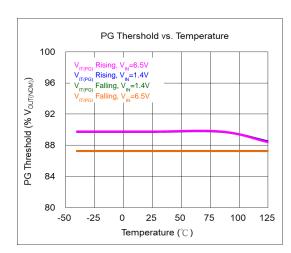

#### **Power Good**

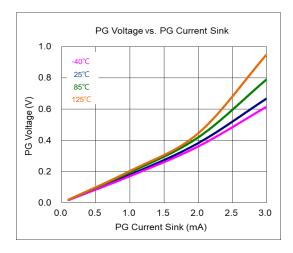

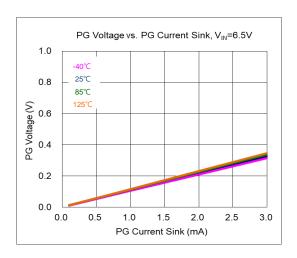

The power-good circuit monitors the feedback pin voltage to indicate the status of the output voltage. The open-drain PGOOD pin requires an external pull-up resistor to an external supply, any downstream device can receive power-good as a logic signal for sequencing. A pull-up resistor from  $10k\Omega$  to  $100k\Omega$  is recommended. Make sure that the external pull-up supply voltage results in a valid logic signal for the receiving device.

After start-up, the PGOOD pin has a high impedance when the feedback voltage exceeds  $V_{PGOOD\_HYS}$  (typically 88.3% of 0.8V reference voltage level). The PGOOD is pulled to GND when the feedback pin voltage falls below the  $V_{IT\_PGOOD}$ .

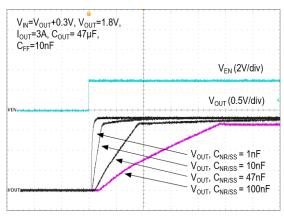

#### **Programmable Soft-Start**

Soft-start refers to the ramp-up time of the output voltage during LDO turn-on after EN and  $V_{UVLO}$  exceed the respective threshold voltage. The AP7179D activates a quick-start circuit to charge the noise reduction capacitor ( $C_{NR/SS}$ ) and then the output voltage ramps up. The noise reduction capacitor ( $C_{NR/SS}$ ) accomplishes both noise-reduction and the soft-start ramp-time programming during turn-on.

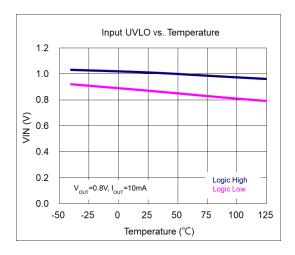

#### **Undervoltage Lockout (UVLO)**

The UVLO circuit monitors the input voltage to prevent the device from turning on before the VIN rises above the  $V_{UVLO}$  threshold. The UVLO circuit also disables the output of the device when VIN falls below the lockout voltage ( $V_{UVLO} - V_{HYS}$ ). The UVLO circuit responds quickly to glitches on the VIN and will attempt to disable the output of the device if the VIN collapses.

#### Internal Current Limit (I<sub>LIM</sub>)

The AP7179D continuously monitors the output current to protect the pass transistor against high-load current faults or shorting events. When encountering an abnormal condition, the LDO sources constant current to limit the output within the predefined range. Thermal shutdown can activate during a current-limit event because of the high power dissipation typically found in these conditions. To ensure proper operation of the current limit, minimize the inductances to the input and load. Continuous operation in current limit is not recommended.

By reason of the built-in body diode, the pass transistor conducts current when the output voltage exceeds input voltage. Since the current is not limited here, external current protection should be added if the device may work in a reverse voltage state.

#### **Overtemperature Protection (OTP)**

The AP7179D implements thermal shutdown protection. The device is disabled when the junction temperature (T<sub>J</sub>) exceeds 160°C (typical). Thermal shutdown hysteresis ensures that the LDO resets again (turns on) when the temperature falls to 140°C (typical). Continuously running the AP7179D into thermal shutdown or above a junction temperature of 125°C reduces long-term reliability.

#### **Output Active Discharge**

When the device is disabled, the AP7179D discharges the LDO output (via VOUT pins) through an internal pulldown MOSFET that connects a resistance of several hundred ohms to ground.

Do not rely on the active discharge circuit for discharging a large amount of output capacitance after the input supply has collapsed because reverse current can possibly flow from the output to the input. External current protection should be added if the device may work at a reverse voltage state.

### Absolute Maximum Ratings (Note 4) (@TA = +25°C, unless otherwise specified.)

| Symbol             | Parameter                                                 | Ratings                       | Unit |

|--------------------|-----------------------------------------------------------|-------------------------------|------|

| ESD HBM            | Human Body Mode ESD Protection                            | 2                             | kV   |

| CDM                | Charged Device Model                                      | 500                           | V    |

| V <sub>IN</sub>    | Input Voltage                                             | -0.3 to 7                     | V    |

| V <sub>EN</sub>    | Input Voltage for EN Pin                                  | -0.3 to 7                     | V    |

| $V_{PG}$           | Power Good Indictor Voltage                               | -0.3 to 7                     | V    |

| V <sub>OUT</sub>   | Output Voltage                                            | -0.3 to V <sub>IN</sub> + 0.3 | V    |

| V <sub>NR/SS</sub> | V <sub>NR/SS</sub> Pin Voltage                            | -0.3 to 2                     | V    |

| $V_{FB}$           | Feedback Pin Voltage                                      | -0.3 to 2                     | V    |

| $T_J$              | Operating Junction Temperature                            | 150                           | °C   |

| T <sub>STG</sub>   | Storage Temperature                                       | -55 to +150                   | °C   |

| $\theta_{JA}$      | Thermal Resistance Junction to Ambient (θ <sub>JA</sub> ) | 65.4                          | °C/W |

Notes:

- 4. a). Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to absolute-maximum-rated conditions for extended period may affect device reliability.

- b). Ratings apply to ambient temperature at +25°C. The JEDEC High-K board design used to derive this data was a 3 inch x 3 inch multilayer board with 1oz. internal power and ground planes and 2oz. copper traces on the top and bottom of the board.

### Recommended Operating Conditions (@T<sub>A</sub> = +25°C, unless otherwise specified.)

| Symbol          | Parameter                      | Min | Max  | Unit |

|-----------------|--------------------------------|-----|------|------|

| V <sub>IN</sub> | Input Voltage                  | 1.1 | 6.5  | V    |

| Іоит            | Each Channel Output Current    | 0   | 3    | А    |

| TJ              | Operating Junction Temperature | -40 | +125 | °C   |

### **Electrical Characteristics**

Over operating temperature range (T<sub>J</sub> =  $-40^{\circ}$ C to 125°C), (1.1V  $\leq$  V<sub>IN</sub> < 6.5V and V<sub>IN</sub>  $\geq$  V<sub>OUT(TARGET)</sub> + 0.3 V, V<sub>OUT(TARGET)</sub> = 0.8V, V<sub>OUT</sub> connected to 50 $\Omega$  to GND, V<sub>EN</sub> = 1.1 V, C<sub>IN</sub> = 10 $\mu$ F, COUT = 47 $\mu$ F, C<sub>NR/SS</sub> = 0nF, C<sub>FF</sub> = 0nF, and PG pin pulled up to V<sub>IN</sub> with 100 k $\Omega$ , unless otherwise noted. (Note 5)

| Parameter                           | Symbol                                    | Test Conditions                                                                        | Min      | Тур  | Max      | Unit |

|-------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------|----------|------|----------|------|

| Input Voltage Range                 | V <sub>IN</sub>                           |                                                                                        | 1.1      |      | 6.5      | V    |

| Feedback Reference Voltage          | $V_{FB}$                                  |                                                                                        |          | 0.8  |          | V    |

| NR/SS Pin Voltage                   | V <sub>NR/SS</sub>                        |                                                                                        |          | 0.8  |          | V    |

| Undervoltage Look Out               | V <sub>UVLO</sub>                         | V <sub>IN</sub> increasing                                                             |          | 1.02 | 1.085    | V    |

| Undervoltage Lock-Out               | V <sub>HYS</sub>                          | Hysteresis                                                                             |          | 150  |          | mV   |

| Output Voltage Range                |                                           | Using voltage setting pins (50mV, 100mV, 200mV, 400mV, 800mV, and 1.6V)                | 0.8 -1%  |      | 3.95+ 1% | V    |

|                                     |                                           | Using external resistors                                                               | 0.8 - 1% |      | 5 + 1%   | ٧    |

| Output Voltage Accuracy<br>(Note 6) | V <sub>OUT</sub>                          | $V_{IN} = V_{OUT} + 0.3V, 0.8V \le V_{OUT} \le 5V,$<br>$5\text{mA} \le I_{OUT} \le 3A$ | -1       |      | 1        | %    |

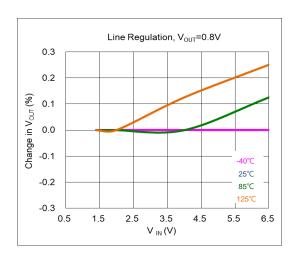

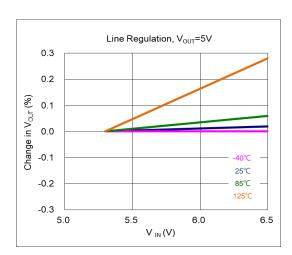

| Line Regulation                     | ΔV <sub>OUT</sub> /<br>ΔV <sub>IN</sub>   | I <sub>OUT</sub> = 5mA, 1.4V ≤ V <sub>IN</sub> ≤ 6.5 V                                 |          | 0.05 |          | %/V  |

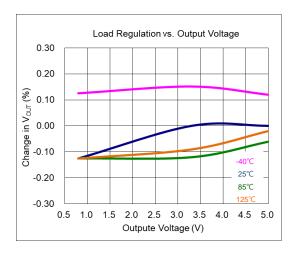

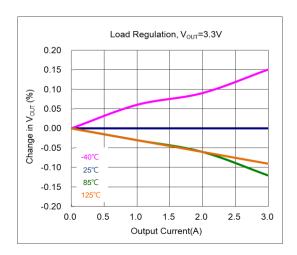

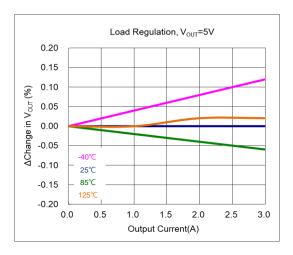

| Load Regulation                     | ΔV <sub>OUT</sub> /<br>Δ I <sub>OUT</sub> | 5mA ≤ I <sub>OUT</sub> ≤ 3A                                                            |          | 0.08 |          | %/A  |

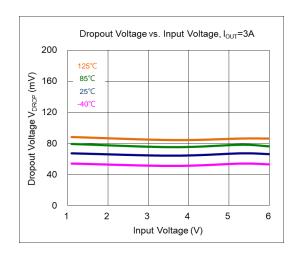

| Dropout Voltage                     | $V_{DROP}$                                | $V_{IN} = 1.1 V$ to 6.5 V, $I_{OUT} = 3 A$ , $V_{FB} = 0.8 V - 3 \%$                   |          | 110  | 180      | mV   |

| Output Current Limit                | I <sub>LIM</sub>                          | Vout = 90% Vout(target), Vin = Vout(target) + 0.4V                                     | 3.7      | 4.2  | 4.7      | А    |

### **Electrical Characteristics** (continued)

Over operating temperature range (T $_J$  = -40°C to 125°C), (1.1V  $\leq$  V $_{IN}$  < 6.5V and V $_{IN}$   $\geq$  V $_{OUT(TARGET)}$  + 0.3 V, V $_{OUT(TARGET)}$  = 0.8V, V $_{OUT}$  connected to 50 $\Omega$  to GND, V $_{EN}$  = 1.1 V, C $_{IN}$  = 10 $\mu$ F, COUT = 47 $\mu$ F, C $_{NR/SS}$  = 0nF, C $_{FF}$  = 0nF, and PG pin pulled up to V $_{IN}$  with 100 k $\Omega$ , unless otherwise noted. (Note 5)

| Parameter                                                       | Symbol              | Test Condition                                                                                                                        | ıs                                               | Min                     | Тур                      | Max                     | Unit          |  |

|-----------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------|--------------------------|-------------------------|---------------|--|

| Short-circuit Current Limit                                     | I <sub>SC</sub>     | $R_{LOAD} = 20 \text{ m}\Omega$                                                                                                       |                                                  |                         | 1.0                      |                         | Α             |  |

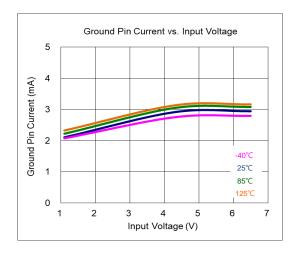

|                                                                 |                     | Minimum load, V <sub>IN</sub> = 6.5V, I <sub>OUT</sub> = 5mA                                                                          |                                                  |                         | 2.8                      | 4                       |               |  |

| Ground Pin Current                                              | 1                   | Maximum load, V <sub>IN</sub> = 1.4V, I <sub>OU</sub>                                                                                 | T = 3A                                           |                         | 4.2                      | 5.5                     | mA            |  |

| Ground Fill Current                                             | I <sub>GND</sub>    | Shutdown, PG = Open, V <sub>IN</sub> = V <sub>EN</sub> = 0.5V                                                                         | 6.5V,                                            |                         |                          | 25                      | μA            |  |

| EN Pin Current                                                  | I <sub>EN</sub>     | $V_{IN} = 6.5V$ , $V_{EN} = 0V$ and $6.5V$                                                                                            |                                                  | -0.1                    |                          | 0.7                     | μΑ            |  |

| EN Pin High-Level Input Voltage                                 | V <sub>EN_H</sub>   | Enable device                                                                                                                         |                                                  | 1.1                     |                          | 6.5                     |               |  |

| EN Pin Low-Level Input Voltage                                  | V <sub>EN_L</sub>   | Disable device                                                                                                                        |                                                  | 0                       |                          | 0.5                     | V             |  |

| PG Pin Threshold                                                | V <sub>IT_PG</sub>  | For the direction PG signal falli decreasing V <sub>OUT</sub>                                                                         | ng with                                          | 0.82 x V <sub>OUT</sub> | 0.883 x V <sub>OUT</sub> | 0.93 x V <sub>OUT</sub> | ٧             |  |

| PG Pin Hysteresis                                               | V <sub>PG_HYS</sub> | For PG signal rising                                                                                                                  |                                                  |                         | 0.01 x V <sub>OUT</sub>  |                         | V             |  |

| PG Pin Low- Level Output<br>Voltage                             | $V_{PG\_L}$         | $V_{OUT} < V_{IT\_PG}$ , $I_{PG} = -1$ mA (cur                                                                                        |                                                  |                         | 0.4                      | ٧                       |               |  |

| PG Pin Leakage Current                                          | I <sub>PG_LK</sub>  | V <sub>OUT</sub> > V <sub>IT_PG</sub> , V <sub>PG</sub> = 6.5V                                                                        |                                                  |                         |                          | 1                       | μΑ            |  |

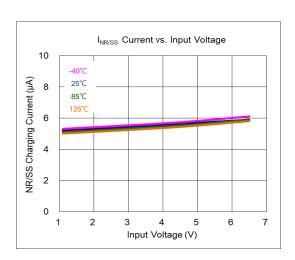

| NR/SS Pin Charging Current                                      | I <sub>NR/SS</sub>  | $V_{NR/SS} = GND, V_{IN} = 6.5V$                                                                                                      | V <sub>NR/SS</sub> = GND, V <sub>IN</sub> = 6.5V |                         | 6.2                      | 9                       | μΑ            |  |

| FB Pin Leakage Current                                          | I <sub>FB</sub>     | V <sub>IN</sub> = 6.5V                                                                                                                |                                                  | -100                    |                          | 100                     | nA            |  |

|                                                                 |                     |                                                                                                                                       | f = 10kHz,<br>$V_{OUT} = 0.8V$                   |                         | 42                       |                         |               |  |

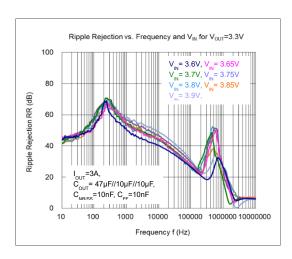

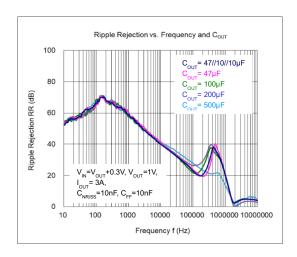

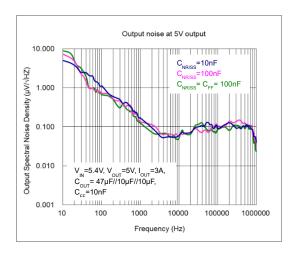

| Dower Supply Pointing Potio                                     | PSRR                | $V_{IN}$ - $V_{OUT}$ = 0.4V, $I_{OUT}$ = 3A, $C_{NR/SS}$ = 100nF, $C_{FF}$ = 10nF, $C_{OUT}$ = 47 $\mu$ F    10 $\mu$ F    10 $\mu$ F | f = 500kHz,<br>$V_{OUT} = 0.8V$                  |                         | 39                       |                         | - dB          |  |

| Power Supply Rejection Ratio                                    |                     |                                                                                                                                       | f = 10kHz,<br>$V_{OUT} = 5V$                     |                         | 40                       | 1                       |               |  |

|                                                                 |                     |                                                                                                                                       | f = 500kHz,<br>$V_{OUT} = 5V$                    |                         | 25                       |                         |               |  |

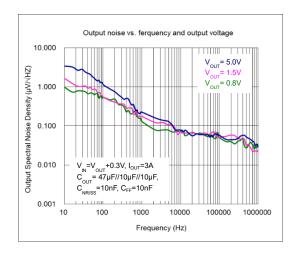

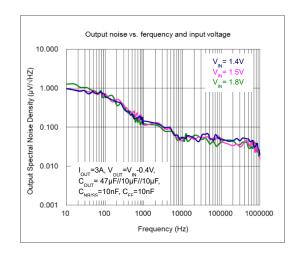

| Output Noise Voltage                                            | BW = 10Hz to 100k   |                                                                                                                                       | $V_{IN} = 1.1V$ , $V_{OUT} = 0.8V$               |                         | 4.4                      | 1                       | /             |  |

|                                                                 | V <sub>n</sub>      | $C_{NR/SS} = 100nF, C_{FF} = 10nF,$<br>$C_{OUT} = 47\mu F    10\mu F    10\mu F$                                                      | V <sub>OUT</sub> = 5 V                           |                         | 7.7                      |                         | $\mu V_{RMS}$ |  |

| Thermal Shutdown Threshold                                      | Т                   | Temperature increasing                                                                                                                |                                                  |                         | 160                      |                         | °C            |  |

| Thermal Shuldown Threshold                                      | T <sub>SD</sub>     | Temperature decreasing                                                                                                                |                                                  |                         | 140                      |                         |               |  |

| Thermal Resistance Junction to Case (θ <sub>JC</sub> ) (Note 4) | $\theta_{JC}$       |                                                                                                                                       |                                                  |                         | 3.68                     |                         | °C/W          |  |

Notes:

<sup>5.</sup>  $V_{OUT(TARGET)}$  is the expected VOUT value set by the external feedback resistors. The  $50\Omega$  load is disconnected when the test conditions specify an IOUT value.

6. External resistor tolerance is not taken into account.

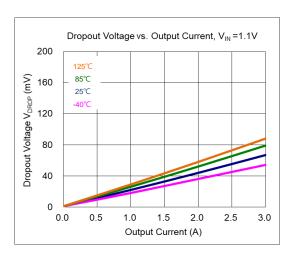

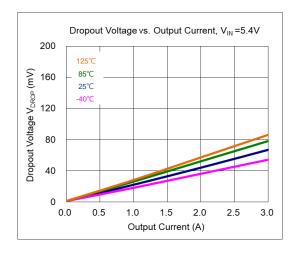

### **Typical Performance Characteristics**

At TA = 25°C, VIN = 1.1 V or VIN = VOUT(NOM) + 0.3 V (whichever is greater), VOUT(NOM) = 0.8 V, VEN = 1V,  $C_{IN}$  = 10 $\mu$ F,  $C_{OUT}$  = 47 $\mu$ F,  $C_{NR/SS}$  = 0nF,  $C_{FF}$  = 0nF, and PG pin pulled up to VIN with 100k $\Omega$  (unless otherwise noted)

At Ta = 25°C, Vin = 1.1 V or Vin = Vout(Nom) + 0.3 V (whichever is greater), Vout(Nom) = 0.8 V, Ven = 1V,  $C_{IN}$  = 10 $\mu$ F,  $C_{OUT}$  = 47 $\mu$ F,  $C_{NR/SS}$  = 0nF,  $C_{FF}$  = 0nF, and PG pin pulled up to Vin with 100k $\Omega$  (unless otherwise noted)

At Ta = 25°C, Vin = 1.1 V or Vin = Vout(NOM) + 0.3 V (whichever is greater), Vout(NOM) = 0.8 V, Ven = 1V,  $C_{IN}$  = 10 $\mu$ F,  $C_{OUT}$  = 47 $\mu$ F, CNR/ss = 0nF, CFF = 0nF, and PG pin pulled up to Vin with 100k $\Omega$  (unless otherwise noted)

#### Power up response

Time (4ms/div)

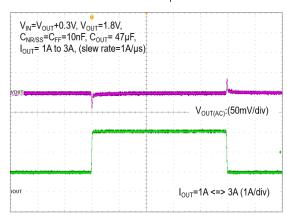

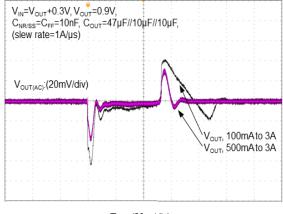

#### Load transient response

Time (100µs/div)

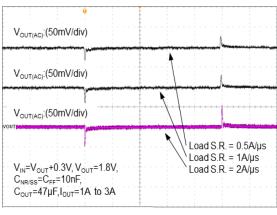

Load transient response vs. load slew rate

Time (100µs/div)

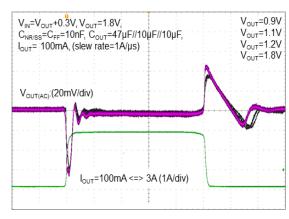

Load transient response vs. Vout

Time (20µs/div)

#### Load transient response vs. DC load

Time (20µs/div)

At Ta = 25°C, Vin = 1.1 V or Vin = Vout(Nom) + 0.3 V (whichever is greater), Vout(Nom) = 0.8 V, Ven = 1V,  $C_{IN}$  = 10 $\mu$ F,  $C_{OUT}$  = 47 $\mu$ F,  $C_{NR/SS}$  = 0nF,  $C_{FF}$  = 0nF, and PG pin pulled up to Vin with 100 $k\Omega$  (unless otherwise noted)

At Ta = 25°C, Vin = 1.1 V or Vin = Vout(Nom) + 0.3 V (whichever is greater), Vout(Nom) = 0.8 V, Ven = 1V,  $C_{IN}$  = 10 $\mu$ F,  $C_{OUT}$  = 47 $\mu$ F,  $C_{NR/SS}$  = 0nF,  $C_{FF}$  = 0nF, and PG pin pulled up to Vin with 100k $\Omega$  (unless otherwise noted)

At Ta = 25°C, Vin = 1.1 V or Vin = Vout(NOM) + 0.3 V (whichever is greater), Vout(NOM) = 0.8 V, Ven = 1V,  $C_{IN}$  = 10 $\mu$ F,  $C_{OUT}$  = 47 $\mu$ F,  $C_{NR/SS}$  = 0nF,  $C_{FF}$  = 0nF, and PG pin pulled up to Vin with 100k $\Omega$  (unless otherwise noted)

### **Application Information**

#### Overview

The AP7179D is a high-current, low-noise, high-accuracy, low-dropout linear regulator with a 3A maximum output current. The device features an input-voltage operating range from 1.1V to 6.5V, and an adjustable output voltage (0.8V to 5.5V via external resistor setting or 0.8V to 3.95V from the PCB layout) to short specific pins and maintain the required output voltage.

#### **Output Voltage Setting**

The output voltage of the AP7179D can be set by external resistors or by output voltage setting pins (50mV, 100mV, 200mV, 400mV, 800mV, and 1.6V) to achieve different output targets. Using external resistors, the values of R1 and R2 use the equation below:

$$V_{OUT} = 0.8 \times (1 + \frac{R1}{R2})$$

The application circuit is determined by the values of R1 and R2, seen in Figure 3.

Figure 3. Output voltage set by external resistors

The AP7179D can program the regulated output voltage by shorting pins 5, 6, 7, 8, 9, 10, and 11 to ground without external resistors, while the SNS pin connects with VOUT pin. Pins 5, 6, 7, 9, 10, and 11 are connected with internal resistor pairs, where each pin is either connected to the ground (active) or left open (floating).

Voltage programming is set as the sum of the internal reference voltage ( $V_{REF} = 0.8V$ ) and the accumulated sum of the respective voltages assigned to each active pin, seen in Figure 4.

Figure 4. Output voltage set by programing pins

Table 2 summarizes these voltage values associated with each active pin setting. The output minimum voltage is equal to  $V_{REF}$  (0.8V) when all program pins are open. The maximum output can be up to 3.95V after all pins short to ground.

#### **Dropout Voltage**

The dropout voltage refers to the minimum voltage difference between the input and output voltage (V<sub>DO</sub> = V<sub>IN</sub> - V<sub>OUT</sub>) required for regulation.

For normal operation, the suggested LDO operating range is  $(V_{IN} > V_{DROP})$  to maintain good transient response and PSRR ability. When VIN drops below the required  $V_{DO}$  for the given load current, the device functions as a resistive switch and does not regulate output voltage.

### **Application Information** (continued)

### $\textbf{C}_{\text{IN}}$ and $\textbf{C}_{\text{OUT}}$ Selection

The AP7179D is designed to support low ESR (equivalent series resistance) ceramic capacitors. The X7R, X5R, and COG-rated ceramic capacitors are recommended due to their good capacitive stability across temperatures. The Y5V-rated capacitor is discouraged because of its large variations in capacitance.

However, ceramic capacitance varies with operating voltage and temperature. Ceramic capacitors are usually recommended to have a voltage derating of 50%. A 47µF or greater ceramic capacitor (or 22µF effective capacitance) for the output is suggested to ensure stability. Input capacitance is selected to minimize transient input droop during load current steps. An input capacitor of at least 47µF is highly recommended for minimal input impedance. If the trace inductance between the AP7179D input supply is high, an available option is to add more input capacitors to restrict ringing and prevent the device from exceeding absolute maximum ratings.

It is generally recommended to use a 47µF 0805-sized ceramic capacitor in parallel with two 10µF 0805-sized ceramic capacitors that meet the minimum effective capacitance at high input-voltage and high output-voltage requirements. Place these capacitors as close as possible to the pins for optimum performance and stability.

#### Feed-Forward Capacitor (CFF)

The AP7179D is designed to be stable without the external feed-forward capacitor ( $C_{FF}$ ). A 10nF external feed-forward capacitor optimizes the transient, noise, and PSRR performance. A higher capacitance  $C_{FF}$  can be also used, but the start-up time is longer and the power-good signal can incorrectly indicate that the output voltage is settled.

#### Soft-Start and Noise Reduction (CNR/SS)

The AP7179D features a programmable, monotonic soft-start time for output rising, which can be achieved via an external capacitor ( $C_{NR/SS}$ ) on the NR/SS pin. Using an external  $C_{NR/SS}$  is recommended for general application. Minimizing in-rush current into the output capacitors also helps reduce the noise component from internal reference. The error amplifier of the AP7179D tracks the voltage ramp of the external soft-start capacitor ( $C_{NR/SS}$ ) until the voltage approaches the internal reference 0.8V. The soft-start ramp time can be calculated with Equation 1 and depends on the soft-start charging current ( $I_{NR/SS}$ ), the soft-start capacitance ( $C_{NR/SS}$ ), and the internal reference ( $V_{REF}$ ).

$$t_{SS} = \frac{(V_{REF} \times C_{NR/SS})}{I_{NR/SS}} \tag{1}$$

For noise-reduction consideration, the  $C_{NR/SS}$  in conjunction with an internal noise-reduction resistor forms a low-pass filter (LPF) that filters out noise from the internal bandgap reference, before being gained up via the error amplifier. This reduces the total device noise floor. For low-noise applications, a 10nF to 1µF  $C_{NR/SS}$  is recommended.

#### **Input Inrush Current**

In-rush current is defined as the current into the LDO at the IN pin during start-up and consists of the sum of the load current and the charging current of the output capacitor. Because the input capacitor must be removed to measure inrush current, this method is not recommended. Generally, the soft-start inrush current can be estimated by Equation 2 below.

$$I_{OUT}(t) = \frac{\left(C_{OUT} \times dV_{OUT}(t)\right)}{dt} + \left(\frac{V_{OUT}(t)}{R_{LOAD}}\right) \tag{2}$$

#### Where:

- V<sub>OUT</sub>(t) is the instantaneous output voltage of the turn-on ramp

- dV<sub>OUT</sub>(t) / dt is the slope of the V<sub>OUT</sub> ramp

- R<sub>LOAD</sub> is the resistive load impedance.

#### **Undervoltage Lockout (UVLO)**

The undervoltage lockout (UVLO) threshold is the minimum input operational voltage range that ensures the device stays disabled and shut down when input voltage collapses. Three input voltage events may occur in the application; assuming  $V_{EN} \ge V_{EN,H}$  in all situations.

- (1) Input power starts rising and V<sub>IN</sub> over the V<sub>UVLO</sub> rising threshold, the V<sub>OUT</sub> powers on then reaches the target level and is under-regulated.

- (2) Assuming the  $V_{IN}$  instant power line is unstable and droops severely, the  $V_{IN}$  droop level is not lower than the  $V_{UVLO}$  falling threshold, the device maintains normal work status, and the  $V_{OUT}$  still under-regulated.

- (3)  $V_{IN}$  droop level is lower than UVLO falling threshold, the control loop of the device is disabled and does not have regulation ability, the  $V_{OUT}$  drops in the meantime.

For general applications, instant power line transient with a long power trace between VIN pin may maintain the  $V_{IN}$  level under UVLO threshold, making the output voltage collapse. In this case, use a larger input capacitor to limit the fall-time of the input supply when operating near the minimum  $V_{IN}$ .

AP7179D 15 of 20 January 2023

Document number: DS42129 Rev. 2 - 2 www.diodes.com © 2023 Copyright Diodes Incorporated. All Rights Reserved.

### **Application Information** (continued)

#### Power-Good (PGOOD) Function

Power-Good function monitors the feedback pin voltage and checks if the output voltage is functional or nonfunctional. This feature enables other devices to receive the AP7179D Power-Good signal as a logic signal that can be used for sequence-design application.

The PGOOD pin is an open-drain structure, thus an external pull-up resistor connecting to an external supply is necessary. The pulled-up resistor value between  $10k\Omega$  to  $100k\Omega$  is recommended for proper operation. The lower limit of  $10k\Omega$  results from the maximum pulled-down strength of the power-good transistor, and the upper limit of the  $100k\Omega$  results from the maximum leakage current at the power-good node. If the pullup resistor is outside of this range, then the power-good signal may not read a valid digital logic level. The  $C_{FF}$  time constant must be greater than the  $C_{NR/SS}$  soft-start time constant to ensure proper operation of the PG during start-up.

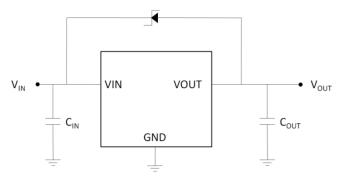

#### **Reverse Current Protection**

If the maximum VOUT exceeds VIN + 0.3V, this may induce reverse current from VOUT to VIN that flows through the body diode of the pass element and cause possible damage. When the output is biased above the input supply voltage level, this makes the VIN < VOUT. An external Schottky diode may be added to prevent the pass element from being damaged by the reverse current, as seen in Figure 5.

Figure 5. Application circuit for reverse current protection

#### **Thermal Considerations**

Thermal protection limits power dissipation in the AP7179D. When power dissipation on the pass element ( $P_D = (V_{IN} - V_{OUT}) \times I_{OUT}$ ) that raises the operating junction temperature exceeds 160°C, the OTP circuit starts the thermal shutdown function and turns the pass element off. The pass element turns on again after the junction temperature drop by 20°C. When the output short circuit occurs, the output voltage will be closed to zero. Overtemperature protection can reduce chip temperature and provide maximum safety to end users when output short circuit occurs.

To avoid permanent damage to the device, the junction temperature should never exceed the absolute maximum junction temperature  $T_{J(MAX)}$ , listed under Absolute Maximum Ratings. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the sizing of the thermal plane, and the rate of surrounding airflow. The primary heat conduction path for the package is through the thermal pad to the PCB. Solder the thermal pad to a copper pad area under the device.

#### **Power Dissipation**

The device power dissipation and proper sizing of the thermal plane connected to the thermal pad is critical to avoid thermal shutdown and ensure reliable operation. Power dissipation of the device depends on input voltage and load conditions, and can be calculated by:

$$P_D = (V_{IN} - V_{OUT}) \times I_{OUT}$$

The maximum power dissipation is handled by the device and depends on the maximum junction to ambient thermal resistance, maximum ambient temperature, and maximum device junction temperature, which can be calculated by the following equation:

$$P_{D(max@T_A)} = \frac{(125^{\circ}\text{C} - T_A)}{R_{\theta JA}}$$

AP7179D Document number: DS42129 Rev. 2 - 2

### Application Information (continued)

### **Layout Consideration**

For best performance of the AP7179D, the recommended PCB layout suggestions are below. All circuit components are placed on the same side of the circuit board and as close as possible to the LDO pins. Place the ground return path connection to the input and output capacitor, with the ground plane connected by a wide copper surface for improved thermal dissipation. It is discouraged to use vias and long power traces for the input and output capacitors connection as this negatively impacts performance. Figure 6 shows an example layout reference that minimizes inductive parasitic, reduces load-current transients, mitigates noise, and maintains good circuit stability.

Figure 6. PCB Layout Guide

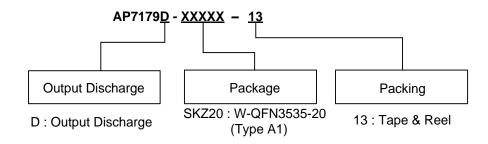

### **Ordering Information** (Note 7)

| Part Number     | rt Number Part Number Suffix Package Packag |                        | Package Code | Pac   | king            |

|-----------------|---------------------------------------------|------------------------|--------------|-------|-----------------|

| Fait Number     | Fait Number Sumx                            | Fackage                | Fackage Code | Qty.  | Carrier         |

| AP7179DSKZ20-13 | -13                                         | W-QFN3535-20 (Type A1) | SKZ20        | 5,000 | 13" Tape & Reel |

Note: 7. For packaging details, go to our website at https://www.diodes.com/design/support/packaging/diodes-packaging/.

### **Marking Information**

(1) W-QFN3535-20 (Type A1)

### (Top View)

$\underline{\mathsf{X}\mathsf{X}}$ YWX XX: Identification Code

Y: Year: 0~9

<u>W</u>: Week: A~Z: 1~26 week; a~z: 27~52 week; z represents

52 and 53 week X: Internal Code

| Part Number     | Package                | Identification Code |

|-----------------|------------------------|---------------------|

| AP7179DSKZ20-13 | W-QFN3535-20 (Type A1) | 9D                  |

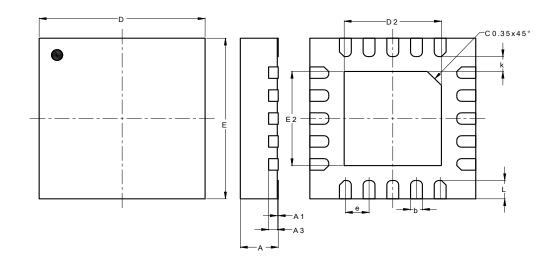

### **Package Outline Dimensions**

Please see http://www.diodes.com/package-outlines.html for the latest version.

### W-QFN3535-20 (Type A1)

| W-QFN3535-20 |           |           |      |  |  |  |  |

|--------------|-----------|-----------|------|--|--|--|--|

|              | (Type A1) |           |      |  |  |  |  |

| Dim          | Min       | Max       | Тур  |  |  |  |  |

| Α            | 0.70      | 0.80      | 0.75 |  |  |  |  |

| A1           | 0.00      | 0.05      | 0.02 |  |  |  |  |

| А3           | C         | 0.203 REF |      |  |  |  |  |

| b            | 0.18      | 0.30      | 0.25 |  |  |  |  |

| D            | 3.50 BSC  |           |      |  |  |  |  |

| D2           | 2.00      | 2.10      | 2.05 |  |  |  |  |

| Е            | ;         | 3.50 B    | SC   |  |  |  |  |

| E2           | 2.00      | 2.10      | 2.05 |  |  |  |  |

| е            |           | 0.50 B    | SC   |  |  |  |  |

| k            | 0.20      |           | -    |  |  |  |  |

| L            | 0.35      | 0.45      | 0.40 |  |  |  |  |

| All D        | imens     | ions ir   | mm   |  |  |  |  |

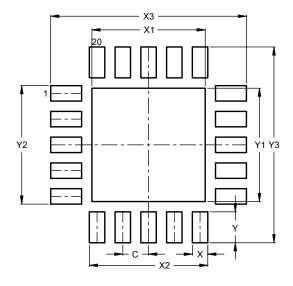

## **Suggested Pad Layout**

Please see http://www.diodes.com/package-outlines.html for the latest version.

### W-QFN3535-20 (Type A1

| Dimensions | Value<br>(in mm) |

|------------|------------------|

| С          | 0.500            |

| Х          | 0.300            |

| X1         | 2.200            |

| X2         | 2.300            |

| Х3         | 3.800            |

| Y          | 0.600            |

| Y1         | 2.200            |

| Y2         | 2.300            |

| Y3         | 3.800            |

### **Mechanical Data**

- Moisture Sensitivity: Level 1 Per J-STD-020

- Terminals: Finish Matte Tin Plated Leads, Solderable per MIL-STD-202, Method 208 @3

- Weight: 0.03 grams (Approximate)

#### **IMPORTANT NOTICE**

- DIODES INCORPORATED (Diodes) AND ITS SUBSIDIARIES MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

- The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes' products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes' products. Diodes' products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of Diodes' products for their intended applications, (c) ensuring their applications, which incorporate Diodes' products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, guality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their

- Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and

- Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

- provided Diodes' products subject to Diodes' Standard Terms (https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

- Diodes' products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes' products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

- While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

- Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

- 9. This Notice may be periodically updated with the most recent version available at https://www.diodes.com/about/company/terms-andconditions/important-notice

The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries.

DIODES is a trademark of Diodes Incorporated in the United States and other countries.

All other trademarks are the property of their respective owners.

© 2023 Diodes Incorporated. All Rights Reserved.

www.diodes.com

January 2023 www.diodes.com © 2023 Copyright Diodes Incorporated. All Rights Reserved.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Diodes Incorporated:

AP7179DSKZ20-13