### FEATURES AND BENEFITS

- Low (90 m $\Omega$ ) R<sub>DS(on)</sub> outputs

- Integrated current limit circuit (OCL)

- Configurable for industry-standard input formats

A4959 Phase, Enable, Mode

A4958 IN1, IN2

- Low-power standby mode

- Fault output

- Adjustable current limit

- · Scaled current output

- Synchronous rectification

- Internal UVLO

- Crossover-current protection

#### PACKAGE: 24-Lead TSSOP (suffix "LP")

Not to scale

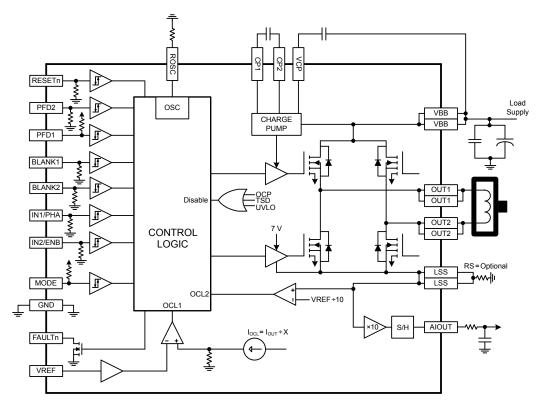

### DESCRIPTION

Designed for pulse-width-modulated (PWM) control of DC motors, the A4958 and A4959 are capable of peak output currents to  $\pm 5$  A and operating voltages to 50 V.

Input terminals are provided for use in controlling the speed and direction of a DC motor with externally applied PWM control signals. Internal synchronous rectification control circuitry is provided to lower power dissipation during PWM operation.

Internal circuit protection includes overcurrent limit, thermal shutdown with hysteresis, undervoltage monitoring of VBB, and crossover-current protection.

The A4958 and A4959 are supplied in a low-profile 24-lead TSSOP package (suffix "LP") with exposed power tab.

#### **Typical Application**

A4958-9-DS, Rev. 1 MCO-0001123

### SPECIFICATIONS

#### **SELECTION GUIDE**

| Part Number  | Temperature Range | Packing                      |

|--------------|-------------------|------------------------------|

| A4958GLPTR-T | –40°C to 105°C    | 4000 pieces per 13 inch reel |

| A4959GLPTR-T | –40°C to 105°C    | 4000 pieces per 13 inch reel |

#### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic              | Symbol           | Notes                     | Rating     | Unit |

|-----------------------------|------------------|---------------------------|------------|------|

| Load Supply Voltage         | V <sub>BB</sub>  |                           | 50         | V    |

| Motor Outputs               | V <sub>OUT</sub> |                           | –2 to 52   | V    |

| LSS                         | N                |                           | ±0.5       | V    |

| 133                         | V <sub>LSS</sub> | t <sub>W</sub> < 500 ns   | ±2.5       | V    |

| Output Current              |                  | Continuous <sup>[1]</sup> | 6          | A    |

|                             | IOUT             | t <sub>W</sub> < 500 ns   | 12         | A    |

| VREF                        | V <sub>REF</sub> |                           | –0.3 to 6  | V    |

| Logic Input Voltage Range   | V <sub>IN</sub>  |                           | –0.3 to 6  | V    |

| Junction Temperature        | TJ               |                           | 150        | °C   |

| Storage Temperature Range   | T <sub>stg</sub> |                           | –55 to 150 | °C   |

| Operating Temperature Range | T <sub>A</sub>   | Range G                   | -40 to 105 | °C   |

<sup>[1]</sup> Power dissipation and thermal limits must be observed.

#### THERMAL CHARACTERISTICS

| Characteristic             | Symbol           | Test Conditions                                                      | Value | Unit |

|----------------------------|------------------|----------------------------------------------------------------------|-------|------|

| Package Thermal Resistance | Р                | 24-lead TSSOP (package LP), on JEDEC High-K board                    | 28    | °C/W |

|                            | κ <sub>θJA</sub> | 24-lead TSSOP (package LP), on 2-sided PCB 1-in. <sup>2</sup> copper | 38    | °C/W |

## A4958 and A4959

# 50 Volt, 5 Amp DC Motor Driver

## PINOUT DIAGRAM AND TERMINAL LIST TABLE

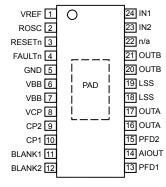

#### A4958LP Package Pinouts

#### A4958 Terminal List Table

| Terminal<br>Number | Name   | Function                                     |  |  |

|--------------------|--------|----------------------------------------------|--|--|

| 1                  | VREF   | Set current limit                            |  |  |

| 2                  | ROSC   | Set fixed off-time                           |  |  |

| 3                  | RESETn | Standby mode when low                        |  |  |

| 4                  | FAULTn | Fault condition when low                     |  |  |

| 5                  | GND    | Ground                                       |  |  |

| 6                  | VBB    | Power supply                                 |  |  |

| 7                  | VBB    | Power supply                                 |  |  |

| 8                  | VCP    | Charge pump capacitor                        |  |  |

| 9                  | CP2    | Charge pump capacitor                        |  |  |

| 10                 | CP1    | Charge pump capacitor                        |  |  |

| 11                 | BLANK1 | Set BLANK time                               |  |  |

| 12                 | BLANK2 | Set BLANK time                               |  |  |

| 13                 | PFD1   | Set decay mode for fixed off-time            |  |  |

| 14                 | AIOUT  | Current monitor output                       |  |  |

| 15                 | PFD2   | Set decay mode for fixed off-time            |  |  |

| 16                 | OUTA   | Motor output                                 |  |  |

| 17                 | OUTA   | Motor output                                 |  |  |

| 18                 | LSS    | Low-side source connection                   |  |  |

| 19                 | LSS    | Low-side source connection                   |  |  |

| 20                 | OUTB   | Motor output                                 |  |  |

| 21                 | OUTB   | Motor output                                 |  |  |

| 22                 | n/a    | Unused                                       |  |  |

| 23                 | IN2    | Control input                                |  |  |

| 24                 | IN1    | Control input                                |  |  |

| PAD                | PAD    | Exposed pad for enhanced thermal dissipation |  |  |

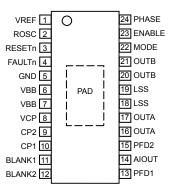

#### A4959LP Package Pinouts

#### A4959 Terminal List Table

| Terminal<br>Number | Name   | Function                                     |  |  |  |

|--------------------|--------|----------------------------------------------|--|--|--|

| 1                  | VREF   | Set current limit                            |  |  |  |

| 2                  | ROSC   | Set fixed off-time                           |  |  |  |

| 3                  | RESETn | Standby mode when low                        |  |  |  |

| 4                  | FAULTn | Fault condition when low                     |  |  |  |

| 5                  | GND    | Ground                                       |  |  |  |

| 6                  | VBB    | Power supply                                 |  |  |  |

| 7                  | VBB    | Power supply                                 |  |  |  |

| 8                  | VCP    | Charge pump capacitor                        |  |  |  |

| 9                  | CP2    | Charge pump capacitor                        |  |  |  |

| 10                 | CP1    | Charge pump capacitor                        |  |  |  |

| 11                 | BLANK1 | Set BLANK time                               |  |  |  |

| 12                 | BLANK2 | Set BLANK time                               |  |  |  |

| 13                 | PFD1   | Set decay mode for fixed off-time            |  |  |  |

| 14                 | AIOUT  | Current monitor output                       |  |  |  |

| 15                 | PFD2   | Set decay mode for fixed off-time            |  |  |  |

| 16                 | OUTA   | Motor output                                 |  |  |  |

| 17                 | OUTA   | Motor output                                 |  |  |  |

| 18                 | LSS    | Low-side source connection                   |  |  |  |

| 19                 | LSS    | Low-side source connection                   |  |  |  |

| 20                 | OUTB   | Motor output                                 |  |  |  |

| 21                 | OUTB   | Motor output                                 |  |  |  |

| 22                 | MODE   | Control input                                |  |  |  |

| 23                 | ENABLE | Control input                                |  |  |  |

| 24                 | PHASE  | Control input                                |  |  |  |

| PAD                | PAD    | Exposed pad for enhanced thermal dissipation |  |  |  |

### ELECTRICAL CHARACTERISTICS <sup>[1]</sup>: Valid at T<sub>A</sub> = 25°C, V<sub>BB</sub> = 5.5 to 50 V, unless otherwise noted

| Characteristics                    | Symbol                   | Test Conditions                                          | Min. | Тур. | Max. | Unit  |

|------------------------------------|--------------------------|----------------------------------------------------------|------|------|------|-------|

| GENERAL                            |                          |                                                          |      |      |      |       |

|                                    |                          | Outputs off                                              | _    | 10   | 15   | mA    |

| VBB Supply Current I <sub>BB</sub> |                          | Standby mode                                             | _    | _    | 15   | μA    |

| VREF Input Current                 | I <sub>VREF</sub>        |                                                          | -5   | <1   | 5    | μA    |

|                                    |                          | External sense resistor                                  | 0    | _    | 4    | V     |

| VREF Input Range                   | V <sub>REF</sub>         | Internal mode (R <sub>SENSE</sub> = 0)                   | 0    | _    | 2    | V     |

| Current Sense Accuracy Internal    |                          | V <sub>REF</sub> = 2 V                                   | 4.25 | 5    | 5.75 | A     |

| Current Sense Accuracy – Internal  | I <sub>OCL</sub>         | V <sub>REF</sub> = 200 mV, T <sub>A</sub> = 25°C         | 300  | 500  | 625  | mA    |

| Current Sense Accuracy External    | A <sub>V</sub>           | $V_{REF}$ / $V_{LSS}$ , $V_{REF}$ = 200 mV to 4 V        | 9.5  | 10   | 10.5 | V/V   |

| Current Sense Accuracy – External  | V <sub>OS</sub>          | Offset                                                   | 1    | 4.5  | 9    | mV    |

| AIOUT Gain                         | A <sub>V</sub>           | I = 200 μA, V <sub>LSS</sub> = 50 to 400 mV              | 8.5  | 10   | 11.5 | V/V   |

| Sample/Hold Droop Rate             | V <sub>DR</sub>          |                                                          | _    | _    | 1    | mV/µs |

| AIOUT Output Impedance             | R <sub>AIOUT</sub>       |                                                          | _    | 1    | _    | kΩ    |

| Power-Up Delay                     | t <sub>PU</sub>          |                                                          | _    | 200  | 400  | μs    |

| OUTPUT DRIVERS                     |                          |                                                          |      |      |      |       |

|                                    |                          | I = 4 A, T <sub>J</sub> = 25°C, V <sub>BB</sub> = 8 V    | _    | 180  | 220  | mΩ    |

| Total Driver On-Resistance         |                          | I = 4 A, T <sub>J</sub> = 125°C, V <sub>BB</sub> = 8 V   | _    | 280  | 350  | mΩ    |

| (Sink + Source)                    | R <sub>DS(ON)</sub>      | I = 4 A, T <sub>J</sub> = 25°C, V <sub>BB</sub> = 5.5 V  | _    | 200  | -    | mΩ    |

|                                    |                          | I = 4 A, T <sub>J</sub> = 125°C, V <sub>BB</sub> = 5.5 V | _    | 300  | _    | mΩ    |

| Output Leakage Current             | I <sub>LK</sub>          |                                                          | -10  | _    | 10   | μA    |

| Rise Time                          | t <sub>r</sub>           | V <sub>BB</sub> = 12 V                                   | 40   | 80   | 200  | ns    |

| Fall Time                          | t <sub>f</sub>           | V <sub>BB</sub> = 12 V                                   | 40   | 100  | 200  | ns    |

| LOGIC INPUT AND OUTPUT             |                          |                                                          |      |      |      | ·     |

| Logic Output Voltage               | Vo                       | I = 2 mA, fault asserted                                 | _    | 0.2  | 0.5  | V     |

| Output Leakage                     | I <sub>FLTn</sub>        | V = 5 V                                                  | _    | -    | 5    | μA    |

| Logic Input Voltage High           | V <sub>IH</sub>          |                                                          | 2.0  | _    | -    | V     |

| Logic Input Voltage Low            | V <sub>IL</sub>          |                                                          | _    | _    | 0.8  | V     |

| Logic Input Voltage Standby Mode   | V <sub>IN(STANDBY)</sub> | Standby mode                                             | _    | _    | 0.4  | V     |

| Input Hysteresis                   | V <sub>HYS</sub>         |                                                          | _    | 250  | 550  | mV    |

| Input Pull-Up Resistor             | R <sub>PU</sub>          | PFD1, MODE (to 5 V <sub>INT</sub> )                      | 30   | 50   | 70   | kΩ    |

| Input Pull-Down Resistor           | R <sub>PD</sub>          | RESETn, PFD2, BLANK1, BLANK2, ENB, IN1, IN2, PHA         | 30   | 50   | 70   | kΩ    |

| PWM TIMING                         |                          |                                                          |      |      |      |       |

| Diank Time                         | 4                        | BLANKx = 00 and 11, relative to target                   | -20  | 0    | 20   | %     |

| Blank Time                         | t <sub>BLK</sub>         | BLANKx = 01 and 10, relative to target                   | -30  | 0    | 30   | %     |

| Fixed Off-Time                     | t <sub>OFF</sub>         | Relative to target, $R_{OSC}$ = 8 to 80 k $\Omega$       | -20  | 0    | 20   | %     |

| PROTECTION CIRCUITS                |                          |                                                          |      |      |      |       |

| UVLO Enable Threshold              | V <sub>UVLO</sub>        | V <sub>BB</sub> rising                                   | 5.1  | _    | 5.4  | V     |

| UVLO Hysteresis                    | V <sub>UVLOHYS</sub>     |                                                          | 200  | 275  | 350  | mV    |

| Thermal Shutdown Temperature       | T <sub>JTSD</sub>        | Temperature increasing                                   | 155  | 170  | 185  | °C    |

| Thermal Shutdown Hysteresis        | ΔTJ                      | Recovery = $T_{JTSD} - \Delta T_J$                       | _    | 30   | _    | °C    |

<sup>[1]</sup> Specified limits are tested at a single temperature and assured over operating temperature range by design and characterization.

### FUNCTIONAL DESCRIPTION

### **Device Operation**

The A4958/9 is designed to operate DC motors. The output drivers are capable of 50 V and 5 A peak operating currents. Actual 100% steady-state DC current capability depends on thermal capability of the package, PCB, and ambient temperature. N-channel DMOS drivers feature internal synchronous rectification to reduce power dissipation. Peak current can be regulated by fixed off-time pulse-width-modulated (PWM) control circuitry.

Protection circuitry includes thermal shutdown, and protection against shorted loads, or against output shorts to ground or supply. Undervoltage lockout prevents damage by keeping the outputs off until the driver has enough power supply voltage to operate normally.

#### Internal PWM Current Control

Peak current is set by sensing the current through the high-side MOSFET or by monitoring the voltage on an external sense resistor.

Using high side monitor:

$$I_{OCL} = V_{REF} \times (2.5 \text{ A/V})$$

Using external sense resistor:

$$I_{OCL} = V_{REF} / (A_V \times R_{SENSE}) + V_{OS} / R_{SENSE}$$

When the peak current is exceeded, the source driver turns off to chop the current according to mode selected by PFD pin.

The high-side monitor is always active. If using external sense resistor, make sure the resistor value is chosen so that the  $I_{PEAK}$  trip level is below that of high-side monitor.

### **Blank Function**

The internal current sense circuit is ignored at the beginning of PWM transitions so as not to falsely sense overcurrent events due to motor capacitance. The blank time can be adjusted as follows, allowing high or low capacitive loads to be optimized. This blanking time sets the minimum on-time of the PWM.

| BLANK2 | BLANK1 | T (us) |

|--------|--------|--------|

| 0      | 0      | 3      |

| 0      | 1      | 1      |

| 1      | 0      | 2      |

| 1      | 1      | 6      |

## R<sub>osc</sub>

Resistor tied to ground will set the fixed off-time that occurs during current limit operation. Off-Time is set by the following equation:

$t_{off} = R_{OSC} / 825$  (where  $t_{off}$  is in microseconds)

$R_{OSC}$  is allowed in the range 8 to 80 k $\Omega.$

If  $R_{OSC}$  is connected to GND or >3.5 V then  $t_{OFF}$  will default to 25  $\mu s.$

## **PFD Function**

Percent Fast Decay is determined by the state of PFD logic inputs as shown below. After a current limit event, load current will recirculate in slow decay, fast decay, or mixed decay mode.

| PFD2 | PFD1 | PFD  |

|------|------|------|

| 0    | 0    | 0%   |

| 0    | 1    | 15%  |

| 1    | 0    | 50%  |

| 1    | 1    | 100% |

#### **Standby Mode**

Low-power standby mode is activated when RESETn input is set low. Low-power standby mode disables most of the internal circuitry, including the charge pump and the regulator. When the A4958/9 is coming out of standby mode, the charge pump should be allowed to reach its regulated voltage (a maximum delay of 200  $\mu$ s) before any PWM commands are issued to the device.

#### TSD

If the die temperature increases to approximately  $T_{TSD}$ , the full bridge outputs will be disabled until the internal temperature falls below a hysteresis level of  $T_{HYS}$ .

## FAULTn Output

The fault pin is driven low to indicate overtemperature (TSD) status. The fault pin is not used for normal current limit or supply undervoltage.

### **Control Logic**

#### A4958

| RESETn | IN1 | IN2 | I > IOCL | OUT1 | OUT2 | Function                                    |

|--------|-----|-----|----------|------|------|---------------------------------------------|

| 1      | 0   | 0   | 0        | Z    | Z    | Coast                                       |

| 1      | 0   | 1   | 0        | L    | Н    | Reverse                                     |

| 1      | 1   | 0   | 0        | Н    | L    | Forward                                     |

| 1      | 1   | 1   | 0        | L    | L    | Brake (slow decay)                          |

| 1      | 1   | 1   | 1        | L    | L    | Brake (slow decay)                          |

| 1      | 0   | 1   | 1        | H/L  | L    | Chop (decay set by PFD pins) <sup>[1]</sup> |

| 1      | 1   | 0   | 1        | L    | H/L  | Chop (decay set by PFD pins) <sup>[1]</sup> |

| 0      | Х   | Х   | Х        | Z    | Z    | Standby Mode                                |

<sup>[1]</sup> Outputs change to High-Z state when load current approaches zero.

#### A4959

| RESETn | PHASE | ENABLE | MODE | I > IOCL | OUT1 | OUT2 | Function                                    |

|--------|-------|--------|------|----------|------|------|---------------------------------------------|

| 1      | 1     | 1      | Х    | 0        | Н    | L    | Forward                                     |

| 1      | 0     | 1      | Х    | 0        | L    | Н    | Reverse                                     |

| 1      | Х     | 0      | 1    | 0        | L    | L    | Brake (slow decay)                          |

| 1      | 1     | 0      | 0    | 0        | L    | Н    | Fast Decay SR <sup>[1]</sup>                |

| 1      | 0     | 0      | 0    | 0        | Н    | L    | Fast Decay SR <sup>[1]</sup>                |

| 1      | 1     | 1      | Х    | 1        | L    | H/L  | Chop (decay set by PFD pins) <sup>[1]</sup> |

| 1      | 0     | 1      | Х    | 1        | H/L  | L    | Chop (decay set by PFD pins) <sup>[1]</sup> |

| 0      | Х     | Х      | Х    | Х        | Z    | Z    | Standby Mode                                |

<sup>[1]</sup> Outputs change to High-Z state when load current approaches zero.

#### AIOUT

An analog output can be used to monitor peak current through an external sense resistor (if used). The voltage on the sense resistor is amplified by 10. The circuit uses a tracking sample/hold to allow AIOUT to represent peak load current. Representation of load current depends on the operational mode as described in below table.

| Operational MODE                                   | AIOUT Function                                                                  |

|----------------------------------------------------|---------------------------------------------------------------------------------|

| PWM via ENABLE; Mode = SLOW decay                  | Track during on-time after blank, hold during off-time                          |

| PWM via ENABLE; Mode = FAST decay                  | Track after blank; AIOUT proportional to load current only when $V_{SENSE} > 0$ |

| PWM via PHASE (ENB = 1)                            | Track after blank; AIOUT proportional to load current only when $V_{SENSE} > 0$ |

| Chopping by internal current control (VREF and RS) | Track after blank; Hold during off-time                                         |

Note: If ENABLE held low for 250 µs, AIOUT will be discharged to GND.

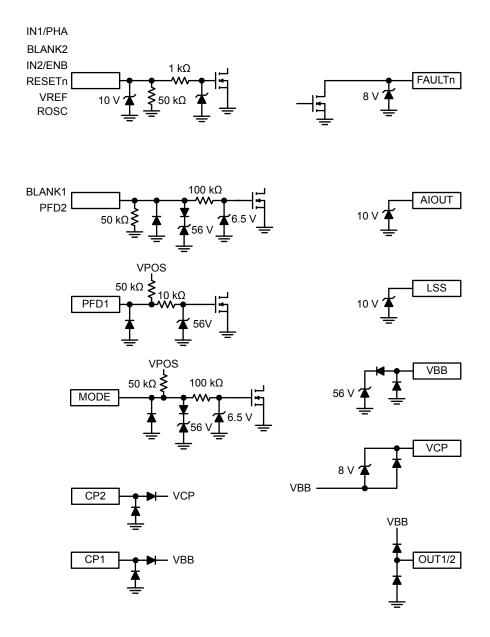

**PIN DIAGRAMS**

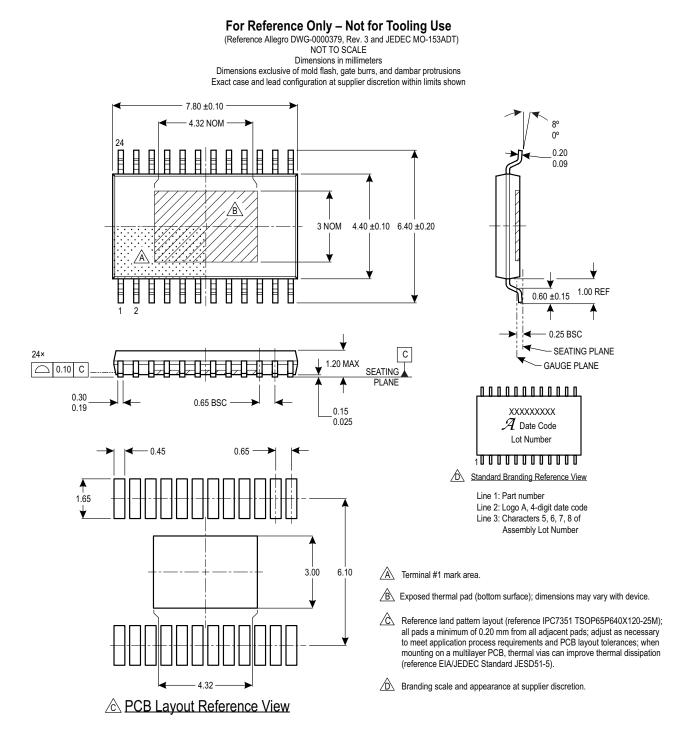

## PACKAGE OUTLINE DRAWING

#### LP Package, 24-Pin TSSOP with Exposed Thermal Pad

#### **Revision History**

| Number | Date          | Description                      |  |  |  |

|--------|---------------|----------------------------------|--|--|--|

| -      | July 13, 2021 | Initial release                  |  |  |  |

| 1      | July 27, 2022 | Updated package drawing (page 8) |  |  |  |

Copyright 2022, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website:

www.allegromicro.com

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Allegro MicroSystems: A4959GLPTR-T