# **User Manual**

# Using Allegro ASEK-20 and ASEK71240 Daughterboard with ACS71240 Samples Programmer

By Ryan Dunn, Allegro MicroSystems

#### Introduction

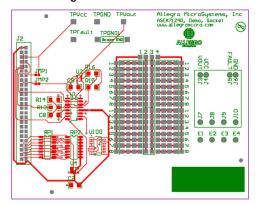

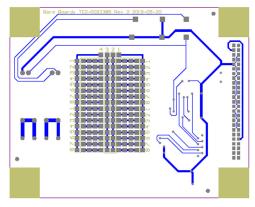

This quick guide documents the use of the ACS71240 daughterboard (TED-0002385) and the ASEK-20 (Part #85-0540-004) with the Allegro ACS71240 samples programmer. The ASEK-20 chassis can be seen in Figure 1, and the top and bottom layers of the ASEK-20 ACS1240 daughterboard can be seen in Figure 2. See the Appendix section for the ASEK71240 Daughterboard Schematic.

Figure 1: ASEK-20 Chassis

Figure 2: Top and Bottom Layers for ASEK-20 ACS71240 Daughterboard

### **Downloading the Programmer**

- 1. Register for software on the Allegro Software Portal: https://registration.allegromicro.com/login.

- 2. Ensure that the ASEK-20 being used has the most recent firmware downloaded. Refer to the ASEK-20 firmware webpage (https://registration.allegromicro.com/parts/ASEK-20) and the ASEK-20 quick guide under "Support Files" on the ASEK-20 firmware webpage.

- 3. After registering and logging in to the software portal, the dashboard page will be shown. Choose the "Find a Part" button highlighted in Figure 3.

Figure 3: "Find a Part" button allowing the user to register specific devices

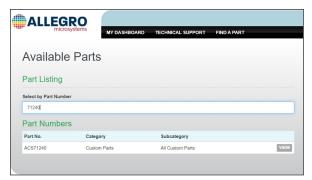

- 4. Click "Find a Part" to go to the "Available Parts & Software" page.

- 5. Search for "ACS71240" in the "Select by Part Number" search bar shown in Figure 4.

Figure 4: "Select by Part Number" on the Available Parts & Software page

6. Click "View" next to the ACS71240 search result as shown highlighted in Figure 5.

Figure 5: "View" next to "ACS71240" search result

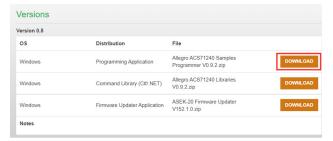

7. Click "Download" next to the first result to open the Programming Application ZIP file as highlighted in red in Figure 6.

Figure 6: "Download" to open the Programming Application

- 8. Open and extract the downloaded ZIP file and save to a known location.

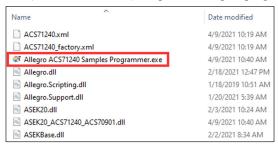

- 9. Open the extracted ZIP file and open the folder "Allegro ACS71240 Samples Programmer V#".

- 10. Open the "Allegro ACS71240 Samples Programmer" application file (EXE file extension) to open the samples programmer.

Figure 7: Application file

# Connecting ASEK-20 to PC and ASEK71240 Daughterboard

- 1. Connect one end of the USB communications cable to the USB port of a personal computer.

- 2. Connect the other end of the USB communications cable to the "USB" port on the ASEK-20 chassis.

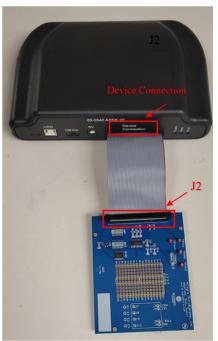

- 3. Connect a ribbon cable to the "J2" connector on the left-hand side of the ACS71240 daughterboard.

- 4. Connect the other end of the ribbon cable to the "Device Connection" port on the ASEK-20 chassis as shown in Figure 8.

Figure 8: Connection between ASEK-20 and ASEK71240 Daughterboard

- 5. Connect the DC Power Supply/Cable to the 5 V port on the ASEK-20 chassis.

- 6. Plug in the DC Power Supply to a 110/220 AC 60/50 Hz outlet with the appropriate power adapter.

#### **Using the Programmer**

## Connecting to the ASEK-20

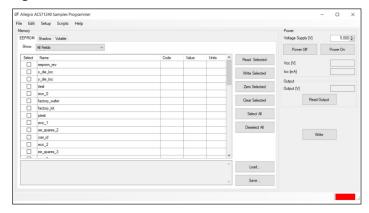

Opening the programmer will result in a window identical to Figure 9 below.

Figure 9: ACS71240 Programmer Application

To connect the ASEK-20, click "Setup" → "Communication Setup". The dialog box in Figure 10 will appear. Click the correct COM# in the pulldown menu next to COM Port. If the COM port is unknown, do the following:

- 1. Unplug the USB cable to the ASEK-20.

- Click "Refresh" in the "Communication Setup" dialog window as highlighted in blue in Figure 10.

- 3. Click on the "COM Port" pulldown menu.

- 4. Note which ports are in the menu.

- 5. Plug the USB cable back into the ASEK-20.

- 6. Click "Refresh".

- 7. Click the "COM Port" popup menu again.

- 8. Note the COM port not previously listed in the menu; this is the port connected to the ASEK-20.

- 9. Select this COM port to use.

Once the correct COM port is selected and the ASEK-20 is connected to the PC, verify next to "Communication" the status of the ASEK-20.

If the status is "Active", the ASEK-20 is powered and responding. If the status is "Inactive", the ASEK-20 is not responding or powered on. If this is the case, click "Refresh" and ensure the ASEK-20 chassis is plugged into the PC and the chassis is powered on.

Click "OK" to exit the dialog box.

Figure 10: Communication Setup dialog box

#### Status Bar

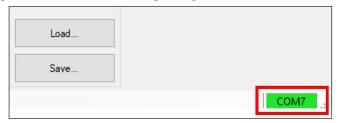

The green or red colored rectangle on the right side of the status bar shown highlighted in red in Figure 11 indicates the status of the communication with the ASEK. If the status bar is red, the communication is not active and if green, the application is communicating with the ASEK. The COM port that is currently set is overlaid on the colored rectangle. Clicking on the rectangle will open the Communication setup dialog window.

Figure 11: Status bar on the bottom right-hand side of GUI

# Turning the Part ON and OFF

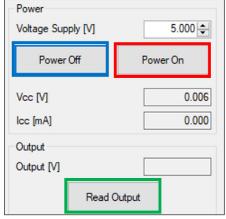

To power-on the part using the ASEK-20, click "Power On" on the right-hand side of the programmer as show in red in Figure 12.

Figure 12: "Power On", "Power Off", and "Read Output"

Once the part is powered on, values for " $V_{CC}$  [V]" and " $I_{CC}$  [mA]" will populate with the measured values. Verify that the voltage is what is desired and that the device is consuming approximately 10 mA (maximum of 12 mA).

To read the output of the ACS71240, select "Read Output" highlighted green in Figure 12. Verify the Output [V] is a reasonable number, around 2.5 volts with zero external field applied if testing a bidirectional part with 5 volts typical  $V_{\rm CC}$  (0.5 volts with zero external field applied for a unidirectional device).

To turn the part off, select "Power Off" to the left of "Power On", highlighted in blue in Figure 14 above. Clicking "Power Off" will cause ICC to fall to  $\approx 0$  mA.

#### Reading from and Writing to the Part

Note before reading and writing to the part, the part must be connected and powered on using the programmer GUI.

It is recommended that the user save the memory to a tabular file before experimenting with programming so the user can return the device to its original factory programmed state if necessary. See the Saving and Loading Memory Files section below.

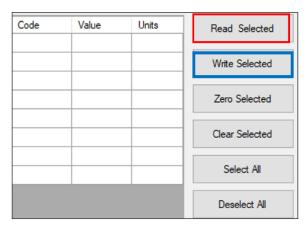

To read a field, select the desired field by checking the box under "Select" to the left of the register name and click the "Read Selected" button highlighted in red in Figure 15.

To write to a field, select the desired field by checking the box under "Select" to the left of the name. Change the value under "Code" to the desired value and press Enter. Click "Write Selected" button highlighted in blue in Figure 15.

To verify that field was written to the device, do the following: click "Clear Selected" causing the values in the "Code" and "Value" cells to disappear. Then click "Read Selected". The values that were written will reappear in the "Code" and "Value" cells verifying the user correctly wrote to the part.

Figure 13: "Read Selected" and "Write Selected" buttons

Below, each option on the programmer menu has been briefly defined:

- · Read Selected: reads value of the selected field.

- Write Selected: writes entered value to the part.

- **Zero Selected**: this option will zero the selected field but will not write zero to the device unless "Write Selected" is clicked.

- Clear Selected: this option will hide and clear the value of the selected field but will not change the value.

- Select All: selects all fields.

- Deselect All: deselects any and all selected fields.

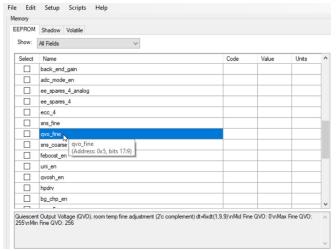

Note that clicking on the name of a selected field will define the field to the user. Hovering over a field with the PC cursor will tell the user the address of that field (see Figure 13).

Figure 14: Hovering over a field shows the address

# **Accessing the Register Diagram**

To access the register diagram, hover over "Help" on the menu bar. Select "ACS71240 Register Diagram". This will open a dialog window identical to the window in Figure 18 below. See the appendix section below for a larger register diagram.

|         |                   |  |  |     |  |       |                                |                   |        |                                 |       |       |     |       |                   | Bi     | it Nu       | mber |                   |       |               |             |           |               |    |    |    |             |            |    |      |    |  |  |  |

|---------|-------------------|--|--|-----|--|-------|--------------------------------|-------------------|--------|---------------------------------|-------|-------|-----|-------|-------------------|--------|-------------|------|-------------------|-------|---------------|-------------|-----------|---------------|----|----|----|-------------|------------|----|------|----|--|--|--|

| Address | 31 30 29 28 27 26 |  |  |     |  | 25    | 24                             | 23                | 22     | 21                              | 20    | 19    | 18  | Т     | 17                | 16     | 15          | 14   | 13                | 12    | 11            | 10          | 09        | 08            | 07 | 06 | 05 | 04          | 03         | 02 | 01   | 00 |  |  |  |

| 0xx00   | ecc_0             |  |  |     |  |       | itest y_di                     |                   |        |                                 |       |       |     |       | lie_j             | ie_loc |             |      |                   |       |               |             | x_die_loc |               |    |    |    |             | eeprom_rev |    |      |    |  |  |  |

| 0x01    | ecc_1             |  |  |     |  |       |                                | ptest factory_lot |        |                                 |       |       |     |       |                   |        |             |      |                   |       | factory_wafer |             |           |               |    |    |    |             |            |    |      |    |  |  |  |

| 0x02    | ecc_2             |  |  |     |  |       | г                              | cas_id            |        |                                 |       |       |     |       |                   |        |             |      |                   |       |               | ee_spares_2 |           |               |    |    |    |             |            |    |      |    |  |  |  |

| 0x03    | ecc_3             |  |  |     |  |       | ee_spares_3                    |                   |        |                                 |       |       |     |       |                   |        |             |      |                   |       |               |             |           |               |    |    |    |             |            |    |      |    |  |  |  |

| 0x04    | ecc_4             |  |  |     |  | ee_sp |                                | ee_sp             | ares_4 | analog adc_nback_end_mpol_c pol |       |       |     |       |                   |        |             | - 1  | vepi_tcd vepi_tcn |       |               |             |           | cn vcc3v ibia |    |    |    | _trim clk   |            |    | trim |    |  |  |  |

| 0x06    |                   |  |  | c_5 |  |       | bg_ch                          |                   | drv    | qvos                            | uni_e | feboo | sns | coars | •                 |        | _           |      | 9                 | vo_fi | se se         |             |           |               |    |    |    |             | ns_f       | ne |      |    |  |  |  |

| 0x06    | ecc_6             |  |  |     |  |       | ee_spare_6 tm_ck_freq tm_st to |                   |        |                                 |       |       |     | mp.   | mp_offset qvo_coe |        |             |      |                   |       |               | o_coef      | coeff_1   |               |    |    |    | qvo_coeff_0 |            |    |      |    |  |  |  |

| 0x07    | ecc 7             |  |  |     |  |       | dev_l fault_mode ftrim fprog   |                   |        |                                 |       |       |     |       |                   | in     | ans coeff 1 |      |                   |       |               | sns coeff 0 |           |               |    |    |    |             |            |    |      |    |  |  |  |

Figure 15: ACS71240 Register Diagram

# Manchester Programming Protocol

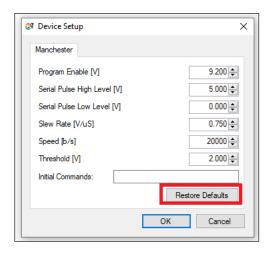

Under "Setup" → "Device Setup...", the dialog menu in Figure 16 below will appear. In this menu, the user can change various characteristics of the Manchester programming protocol used by the ASEK-20. To restore these settings to their default settings, click "Restore Defaults" as highlighted in red in Figure 16.

Figure 16: "Device Setup" menu defaults

Below, each Manchester option has been briefly defined:

- **Program Enable [V]**: used to set the voltage for the Program Enable.

- Serial Pulse High Level [V]: used to set the voltage for the high level of the Manchester signal.

- Serial Pulse Low Level [V]: used to set the voltage for the low level of the Manchester signal.

- Slew Rate [V/μs]: used to set the speed at which the Manchester signal will take to get from one voltage to another.

- **Speed [kb/s]**: used to set the bit rate for communication with the ASEK.

- Threshold [V]: used to set the threshold for determining the difference between a 1 and a 0 when performing register read.

- Initial Commands: used for commands that must be sent to the ASEK-20 when it is being initialized.

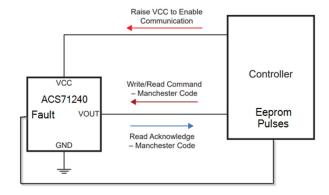

The ACS71240 uses a bidirectional communication on VOUT. When the voltage on the VCC pin is increased beyond the programming threshold, the device will enter programming mode

(see Figure 17). Note the ACS71240 does not initiate communication; it responds to commands from the external controller. If the command is a write, there is no acknowledging from the ACS71240. If the command is a read, the ACS71240 responds by transmitting the requested data. To initialize any communication,  $V_{CC}$  should be increased to a level above  $V_{prgL}$  (6.5 V) without exceeding  $V_{prgH}$  (9.2 V). At this time, VOUT is disabled and acts as an input.

Figure 17: ACS71240 Programming Diagram

Figure 18: Oscilloscope capture showing the Manchester programming protocol on the output of the part

### **Saving and Loading Memory Files**

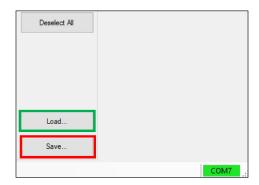

To save the memory as a tabular data file or text file, click "Save..." in the bottom right side of the GUI as highlighted in red in Figure 19. Clicking "Save..." will open a file explorer where the user can save the memory information as a CSV file or TXT file. Saving the memory is recommended before experimenting with programming so the user can return the device to its original factory-programmed state if necessary. The user can also save the memory by clicking "File" → "Save Memory...".

To load a previously saved file containing memory information, click "Load..." as highlighted in green in Figure 19 below. Clicking "Load..." will open a file explorer where the user can navigate to a previously saved CSV or TXT file. The user can also load a memory file by clicking "File" → "Load Memory".

Figure 19: "Load" and "Save" the memory to a tabular file

# **Appendix**

|         |                   |  |  |  |  |  |       |             |      |         |           |                          |       |      |       | Bit N | umber |    |                  |             |    |             |            |        |    |             |             |          |    |          |          | П |  |  |

|---------|-------------------|--|--|--|--|--|-------|-------------|------|---------|-----------|--------------------------|-------|------|-------|-------|-------|----|------------------|-------------|----|-------------|------------|--------|----|-------------|-------------|----------|----|----------|----------|---|--|--|

| Address | 31 30 29 28 27 26 |  |  |  |  |  |       | 24          | 23   | 22      | 21        | 20                       | 19    | 18   | 17    | 16    | 15    | 14 | 13               | 12          | 11 | 10          | 09         | 08     | 07 | 06          | 05          | 04       | 03 | 02       | 01 0     | 0 |  |  |

| 0x00    | ecc_0             |  |  |  |  |  |       | i           | test |         | y_die_loc |                          |       |      |       |       |       |    |                  | x_die_loc   |    |             |            |        |    |             | eeprom_rev  |          |    |          |          |   |  |  |

| 0x01    | ecc_1             |  |  |  |  |  |       | F           | test |         |           | factory_lot              |       |      |       |       |       |    |                  |             |    |             |            | factor |    |             |             |          |    |          | ry_wafer |   |  |  |

| 0x02    | ecc_2             |  |  |  |  |  |       | cas_id      |      |         |           |                          |       |      |       |       |       |    |                  |             |    | ee_spares_2 |            |        |    |             |             |          |    |          |          |   |  |  |

| 0x03    | ecc_3             |  |  |  |  |  |       | ee_spares_3 |      |         |           |                          |       |      |       |       |       |    |                  |             |    |             |            |        |    |             |             |          |    |          |          |   |  |  |

| 0x04    | ecc_4             |  |  |  |  |  | ee_sp |             | ee_s | pares_4 | _analo    | g                        | adc_1 | back | end_g | pol_c | pol   | 7  | vepi_tcd vepi_tc |             |    |             | en vec3v i |        |    |             | bias_trim   |          |    | clk_trim |          |   |  |  |

| 0x05    | ecc_5             |  |  |  |  |  | bg_ch | h           | pdrv | qvos    | huni_e    | uni_erfeboo sns_coarse ( |       |      |       |       |       |    |                  | qvo_fine    |    |             |            |        |    |             | S           | sns_fine |    |          |          |   |  |  |

| 0x06    | ecc_6             |  |  |  |  |  | ee_sp | are_(       | 5 tm | ck_free | tm_sl     | tm_sl temp_offset        |       |      |       |       |       |    |                  | qvo_coeff_1 |    |             |            |        |    |             | qvo_coeff_0 |          |    |          |          |   |  |  |

| 0x07    | ecc_7             |  |  |  |  |  |       |             | _mod |         |           | ftrim fprog              |       |      |       |       |       |    | sns_coeff_1      |             |    |             |            |        |    | sns_coeff_0 |             |          |    |          |          |   |  |  |

Figure 20: ACS71240 Register Diagram

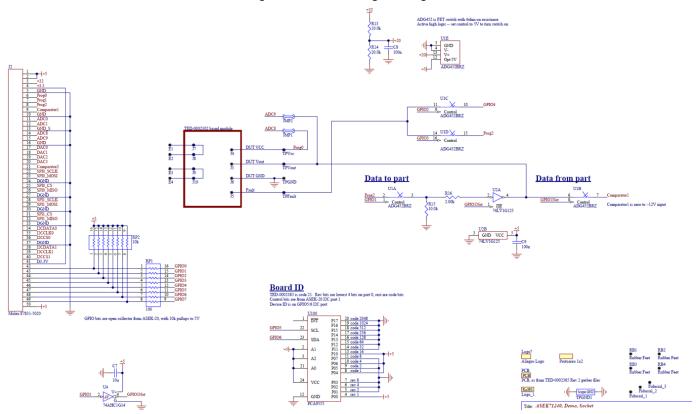

Figure 21: ASEK71240 Daughterboard Schematic

#### **Revision History**

| Number | Date            | Description     |  |  |  |  |  |  |  |  |

|--------|-----------------|-----------------|--|--|--|--|--|--|--|--|

| _      | August 16, 2021 | Initial release |  |  |  |  |  |  |  |  |

Copyright 2021, Allegro MicroSystems.

The information contained in this document does not constitute any representation, warranty, assurance, guaranty, or inducement by Allegro to the customer with respect to the subject matter of this document. The information being provided does not guarantee that a process based on this information will be reliable, or that Allegro has explored all of the possible failure modes. It is the customer's responsibility to do sufficient qualification testing of the final product to ensure that it is reliable and meets all design requirements.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website:

www.allegromicro.com

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Allegro MicroSystems:

ASEK71240LLC-30B3