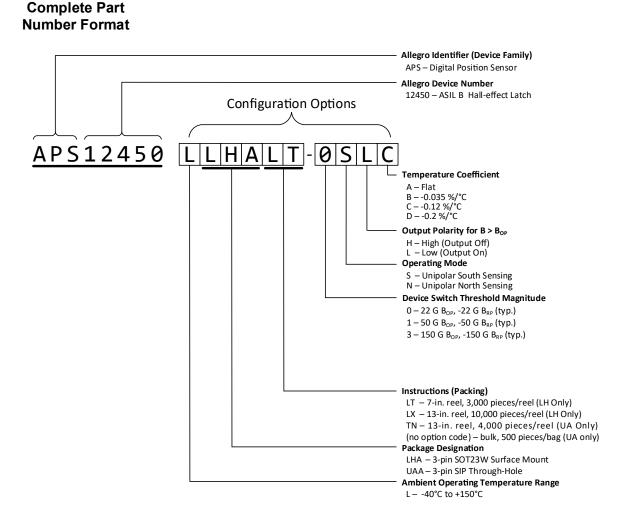

### **Three-Wire Hall-Effect Latch with Advanced Diagnostics**

### FEATURES AND BENEFITS

- Functional safety

- □ Developed in accordance with ISO 26262 to meet ASIL B requirements

- □ Integrated background diagnostics for:

- Signal path

- Regulator

- Hall plate and bias

- Overtemperature detection

- Nonvolatile memory

- □ Defined fault state

- Multiple product options

- □ Magnetic polarity, switchpoints, and hysteresis

- Temperature coefficient

- □ Output polarity

- Reduces module bill-of-materials (BOM) and assembly cost

ASIL B sensor can replace redundant sensors

- □ Integrated overvoltage clamp and reverse-battery diode

Continued on the next page ...

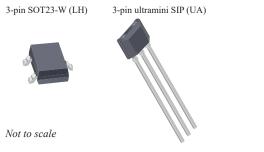

### PACKAGES

### DESCRIPTION

The APS12450 three-wire planar Hall-effect sensor integrated circuits (ICs) were developed in accordance with ISO 26262 as a hardware safety element out of context with ASIL B capability for use in automotive safety-related systems when integrated and used in the manner prescribed in the applicable safety manual and datasheet. The enhanced three-wire interface provides interconnect open/short diagnostics and a fault state to communicate diagnostic data while maintaining compatibility with legacy three-wire systems. The continuous background diagnostics are transparent to the host system and result in a reduced fault-tolerant time.

The APS12450 product options include magnetic switchpoints, temperature coefficient, and output polarity. The response can be matched to SmCo, NdFeB, or low-cost ferrite magnets. For situations where a functionally equivalent three-wire switch device is preferred, refer to the APS11450.

Continued on the next page ...

### **TYPICAL APPLICATIONS**

- · Automotive and industrial safety systems

- Seat/window motors

- Sun roof/convertible top/tailgate/liftgate actuation

- Brake and clutch by wire actuators

- Engine management actuators

- Electric power steering (EPS)

- Transmission shift actuator

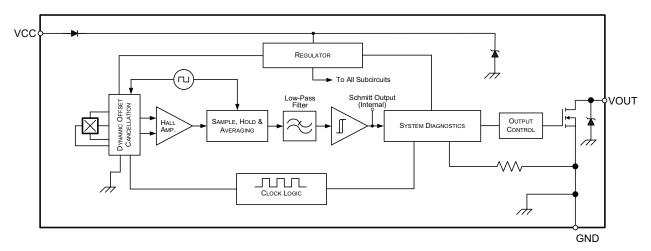

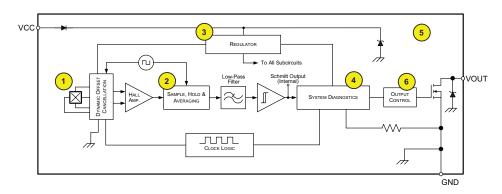

#### Functional Block Diagram

### FEATURES AND BENEFITS (continued)

- Automotive-grade ruggedness and fault tolerance

- $\hfill\square$  Extended AEC-Q100 Grade 0 qualification

- $\circ$  Operation to 175°C junction temperature

- $\square$  3 to 30 V operating voltage range

- $\Box \pm 8$  kV human body model (HBM) electrostatic discharge (ESD)

- $\hfill\square$  Overtemperature indication

### **DESCRIPTION** (continued)

APS12450 sensors are engineered to operate in the harshest environments with minimal external components. They are qualified beyond the requirements of AEC-Q100 Grade 0 and survive extended operation at 175°C junction temperature.

These monolithic ICs include on-chip reverse-battery protection, overvoltage protection (e.g., 40 V load dump), ESD protection, overtemperature detection, and an internal voltage regulator for operation directly from an automotive battery bus. These integrated features reduce the end-product bill-of-materials (BOM) and assembly cost.

Package options include an industry-standard surface-mount smalloutline transistor (SOT) (suffix LH) package and a through-hole single-inline package (SIP) (suffix UA). Both packages are RoHScompliant and lead (Pb) free with 100% matte tin-plated leadframes.

### SELECTION GUIDE [1]

| Part Number         | Package                    | Packing                         | Output Polarity<br>(B > B <sub>OP</sub> ) | Temperature<br>Coefficient | Magnetic<br>Operate Point,<br>B <sub>OP</sub> (typ) |

|---------------------|----------------------------|---------------------------------|-------------------------------------------|----------------------------|-----------------------------------------------------|

| APS12450LLHALX-0SLA | 3-pin SOT23W surface mount | 13-in. reel, 10,000 pieces/reel |                                           |                            |                                                     |

| APS12450LLHALT-0SLA | 3-pin SOT23W surface mount | 7-in. reel, 3000 pieces/reel    | Low                                       | 0%/°C                      | 22 G                                                |

| APS12450LUAA-0SLA   | 3-pin SIP through-hole     | bulk, 500 pieces/bag            |                                           |                            |                                                     |

| APS12450LLHALX-1SLA | 3-pin SOT23W surface mount | 13-in. reel, 10,000 pieces/reel |                                           |                            |                                                     |

| APS12450LLHALT-1SLA | 3-pin SOT23W surface mount | 7-in. reel, 3000 pieces/reel    | Low                                       | 0%/°C                      | 50 G                                                |

| APS12450LUAA-1SLA   | 3-pin SIP through-hole     | bulk, 500 pieces/bag            |                                           |                            |                                                     |

| APS12450LLHALX-3SLA | 3-pin SOT23W surface mount | 13-in. reel, 10,000 pieces/reel |                                           |                            |                                                     |

| APS12450LLHALT-3SLA | 3-pin SOT23W surface mount | 7-in. reel, 3000 pieces/reel    | Low                                       | 0%/°C                      | 150 G                                               |

| APS12450LUAA-3SLA   | 3-pin SIP through-hole     | bulk, 500 pieces/bag            |                                           |                            |                                                     |

<sup>[1]</sup> Contact Allegro MicroSystems for options not listed in the selection guide.

### Three-Wire Hall-Effect Latch with Advanced Diagnostics

#### ABSOLUTE MAXIMUM RATINGS

| Characteristic               | Symbol                 | Notes         | Rating     | Unit |

|------------------------------|------------------------|---------------|------------|------|

| Supply Voltage [1]           | V <sub>CC</sub>        |               | 35         | V    |

| Reverse Supply Voltage       | V <sub>RCC</sub>       |               | -30        | V    |

| Forward Output Voltage       | V <sub>OUT</sub>       |               | 30         | V    |

| Reverse Output Voltage       | V <sub>ROUT</sub>      |               | -0.3       | V    |

| Output Current Sink          | I <sub>OUT(SINK)</sub> | VCC to VOUT   | 12         | mA   |

| Movimum Junction Tomporature | т                      |               | 165        | °C   |

| Maximum Junction Temperature | I J(MAX)               | For 500 hours | 175        | °C   |

| Storage Temperature          | T <sub>stg</sub>       |               | -65 to 170 | °C   |

[1] This rating does not apply to extremely short voltage transients such as load dump and/or ESD. Those events have individual ratings specific to the respective transient voltage event. For information about electromagnetic-compatibility (EMC) test results, contact your local field applications engineer.

# APS12450 Three-Wire Hall-Effect Latch with Advanced Diagnostics

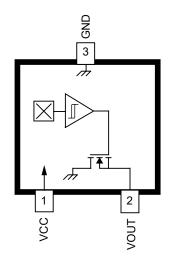

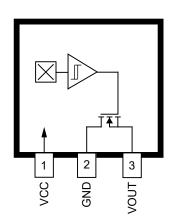

### **PINOUT DIAGRAMS AND TERMINAL LIST**

LH Package, 3-Pin SOT23W Pinout

UA Package, 3-Pin SIP Pinout

|  | Terminal | List | Table |

|--|----------|------|-------|

|--|----------|------|-------|

| Name | Pin N | umber | Function       |

|------|-------|-------|----------------|

| Name | LH    | UA    | Function       |

| VCC  | 1     | 1     | Supply voltage |

| VOUT | 2     | 3     | Output         |

| GND  | 3     | 2     | Ground         |

#### **OPERATING CHARACTERISTICS:** Valid over full operating voltage and ambient temperature ranges for T<sub>J</sub> < T<sub>J</sub>(max),

unless otherwise specified

| Characteristics                            | Symbol                     | Test Conditions                                                                                                                                                 | Min.                            | Typ. [1]                | Max. | Unit |

|--------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------|------|------|

| SUPPLY AND STARTUP                         |                            |                                                                                                                                                                 |                                 |                         |      |      |

| Supply Voltage [2]                         | V <sub>CC</sub>            | Operating, T <sub>J</sub> < 165°C                                                                                                                               | 3                               | _                       | 30   | V    |

| Supply Current                             | I <sub>CC</sub>            |                                                                                                                                                                 | -                               | -                       | 4.5  | mA   |

| Power-On Time <sup>[3]</sup>               | t <sub>on</sub>            | $V_{CC} > V_{CC}(min), B < B_{RP}(min) - 10 G,$<br>B > B <sub>OP</sub> (max) + 10 G                                                                             | -                               | -                       | 150  | μs   |

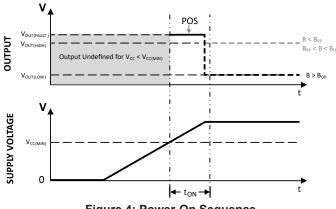

| Power-On State                             | POS                        | t < t <sub>on(max)</sub>                                                                                                                                        | ,                               | V <sub>OUT(FAULT)</sub> |      | _    |

| Output Rise Time                           | t <sub>RISE</sub>          | See Applications Circuit, Figure 9;                                                                                                                             | 2                               | 4                       | 15   | μs   |

| Output Fall Time                           | t <sub>FALL</sub>          | $V_{PU} = V_{CC}$ , $R_{PU} = 3 \text{ k}\Omega$ , $C_{OUT} = 1 \text{ nF}$ , $I_{OUT} < 12 \text{ mA}$                                                         | 2                               | 4                       | 15   | μs   |

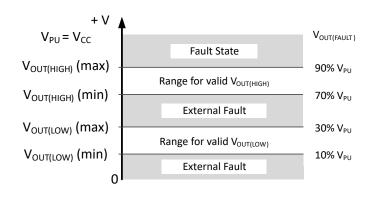

| Output On Voltage                          | V <sub>OUT(LOW)</sub>      | Output ratiometric to V <sub>PU</sub> ;                                                                                                                         | 10                              | 20                      | 30   | %    |

| Output Off Voltage                         | V <sub>OUT(HIGH)</sub>     | $V_{PU} = V_{CC}, \tau < 3 \ \mu s^{[5]}, I_{OUT} < 12 \ mA$                                                                                                    | 70                              | 80                      | 90   | %    |

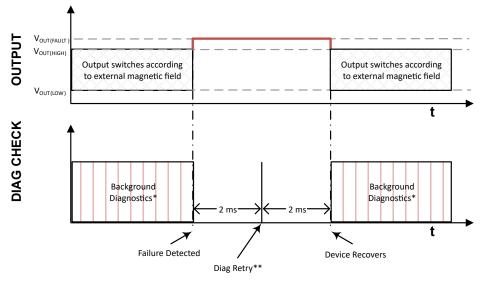

| Output Off Voltage Overshoot [4]           | V <sub>OUT(HIGH)OVER</sub> | Overshoot percentage relative to V <sub>PU</sub> (see Figure 8);<br>V <sub>PU</sub> = V <sub>CC</sub> , $\tau$ < 3 µs <sup>[5]</sup> , I <sub>OUT</sub> < 12 mA | -                               | 2                       | _    | %    |

|                                            | t <sub>VOUT(H)OVER</sub>   | Duration of output voltage overshoot (V <sub>OUT(HIGH)OVER</sub> )                                                                                              | -                               | -                       | 5    | μs   |

| ON-BOARD PROTECTION                        |                            |                                                                                                                                                                 |                                 |                         |      |      |

| Fault Reaction Time                        | t <sub>DIAG</sub>          |                                                                                                                                                                 | _                               | 25                      | 60   | μs   |

| Diagnostics Fault Retry Time [6]           | t <sub>DIAGF</sub>         |                                                                                                                                                                 | -                               | 2                       | _    | ms   |

| Fault Mode Output Voltage<br>(Fault State) | V <sub>OUT(FAULT)</sub>    | V <sub>PU</sub> = V <sub>CC</sub> , τ < 3 μs, I <sub>OUT</sub> < 12 mA                                                                                          | > V <sub>OUT(HIGH)</sub><br>MAX | V <sub>PU</sub>         | _    | V    |

| Overtemperature Shutdown                   | T <sub>SD</sub>            | Temperature increasing                                                                                                                                          | _                               | 205                     | _    | °C   |

| Overtemperature Hysteresis                 | T <sub>JHYS</sub>          |                                                                                                                                                                 | _                               | 25                      | _    | °C   |

<sup>[1]</sup> Typical data is at  $T_A$  = 25°C and  $V_{CC}$  = 12 V and is for design information only.

$^{[2]}V_{CC}$  represents the voltage between the VCC pin and the GND pin.

[3] Power-on time (t<sub>ON</sub>) is measured from V<sub>CC</sub> = V<sub>CC</sub>(min) to 50% of the output transition from V<sub>PU</sub> to final value. Adding a bypass capacitor increases power-on time.

<sup>[4]</sup> The overshoot specification pertains only to conditions where the overshoot is greater than the V<sub>OUT(HIGH)MAX</sub> specification.

<sup>[5]</sup>  $\tau$  is the time constant of the RC circuit;  $\tau = R_{PU} \times C_{OUT}$ .

<sup>[6]</sup> The diagnostics fault retry repeats continuously until a fault condition is no longer observed. For details, see the Diagnostics Mode Operation section.

#### TRANSIENT PROTECTION CHARACTERISTICS: Valid for T<sub>A</sub> = 25°C and C<sub>BYP</sub> = 0.1 µF, unless otherwise specified

| Characteristics                       | Symbol           | Test Conditions              | Min. | Тур. | Max. | Unit |

|---------------------------------------|------------------|------------------------------|------|------|------|------|

| PROTECTION                            |                  |                              |      |      |      |      |

| Forward Supply Zener<br>Clamp Voltage | Vz               | I <sub>CC</sub> (max) + 3 mA | 35   | _    | -    | V    |

| Reverse Supply Zener<br>Clamp Voltage | V <sub>RCC</sub> | $I_{CC} = -1 \text{ mA}$     | _    | _    | -30  | V    |

| Reverse Supply Current                | I <sub>RCC</sub> | $V_{RCC} = -30 V$            | _    | _    | -5   | mA   |

### **MAGNETIC CHARACTERISTICS:** Valid over full operating voltage and ambient temperature ranges for $T_J < T_J(max)$ ,

unless otherwise specified

| Characteristics             | Symbol              | Test C                            | onditions                  | Min.            | Typ. [1] | Max. | Unit <sup>[2]</sup> |   |

|-----------------------------|---------------------|-----------------------------------|----------------------------|-----------------|----------|------|---------------------|---|

|                             |                     |                                   | (A) Flat                   | -               | 0        | _    | %/°C                |   |

| Sensitivity Temperature     | то                  | Relative to sensitivity           | (B) SmCo                   | -               | -0.035   | _    | %/°C                |   |

| Coefficient                 | TC <sub>SENS</sub>  | at 25°C                           | (C) NdFeB                  | -               | -0.12    | _    | %/°C                |   |

|                             |                     |                                   | (D) Ferrite                | -               | -0.2     | _    | %/°C                |   |

| Analog Signal Bandwidth     | f <sub>(-3dB)</sub> |                                   |                            | -               | 10       | _    | kHz                 |   |

|                             |                     | APS12450-0SxA                     |                            | 5               | 22       | 40   | G                   |   |

| Operate Point               | B <sub>OP</sub>     | APS12450–1SxA                     |                            | 15              | 50       | 90   | G                   |   |

|                             |                     | APS12450–3SxA                     |                            | APS12450–3SxA 1 | 100      | 150  | 180                 | G |

|                             |                     | APS12450-0SxA                     |                            | -40             | -22      | -5   | G                   |   |

| Release Point               | B <sub>RP</sub>     | APS12450-1SxA                     |                            | -90             | -50      | -15  | G                   |   |

|                             |                     | APS12450–3SxA                     |                            | -180            | -150     | -100 | G                   |   |

|                             |                     | APS12450-0SxA                     |                            | 10              | 45       | 80   | G                   |   |

| Hysteresis B <sub>HYS</sub> | B <sub>HYS</sub>    | APS12450–1SxA                     |                            | 30              | 100      | 180  | G                   |   |

|                             |                     | APS12450–3SxA                     |                            | 200             | 300      | 360  | G                   |   |

| Symmetry                    | B <sub>SYM</sub>    | B <sub>OP</sub> + B <sub>RP</sub> |                            | -30             | _        | 30   | G                   |   |

| Jitter <sup>[3]</sup>       | _                   | B <sub>OP</sub> = 22 G, B = 100 G | <sub>РК-РК</sub> , 1000 Hz | -               | 0.25     | _    | %                   |   |

<sup>[1]</sup> Typical data is at  $T_A = 25^{\circ}C$  and  $V_{CC} = 12$  V, unless otherwise noted; for design information only.

$^{[2]}$  1 G (gauss) = 0.1 mT (millitesla).

<sup>[3]</sup> Output edge repeatability as a percentage of the period.

### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Symbol          | Test Conditions <sup>[1]</sup>                                                  | Value | Unit |

|----------------------------|-----------------|---------------------------------------------------------------------------------|-------|------|

|                            |                 | Package LH, on 1-layer PCB based on JEDEC standard                              | 228   | °C/W |

| Package Thermal Resistance | $R_{\theta JA}$ | Package LH, on 2-layer PCB with 0.463 in. <sup>2</sup> of copper area each side | 110   | °C/W |

|                            |                 | Package UA, on 1-layer PCB with copper limited to solder pads                   | 165   | °C/W |

[1] Additional thermal information available on the Allegro website.

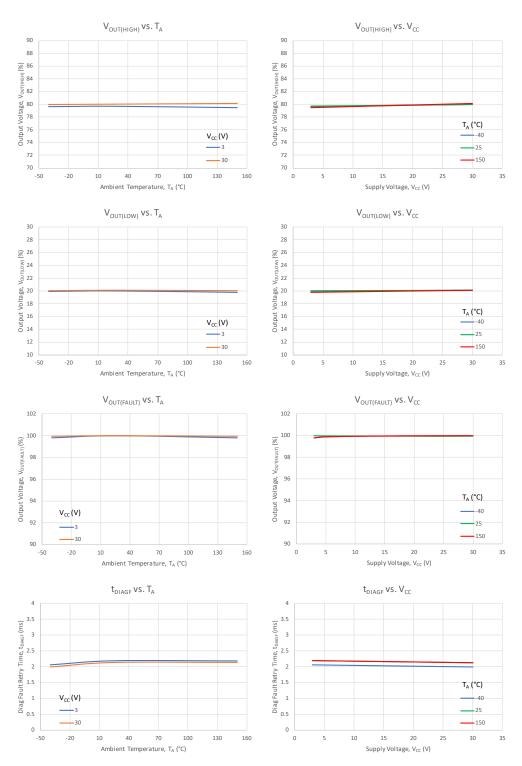

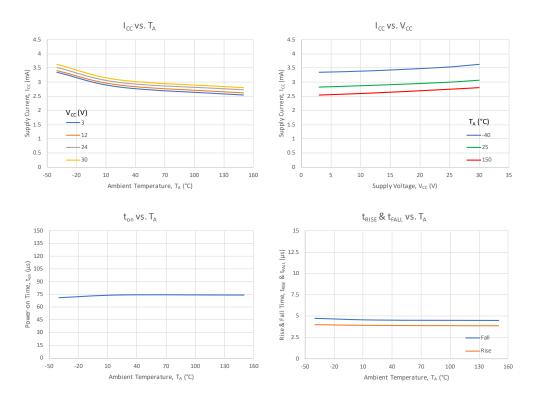

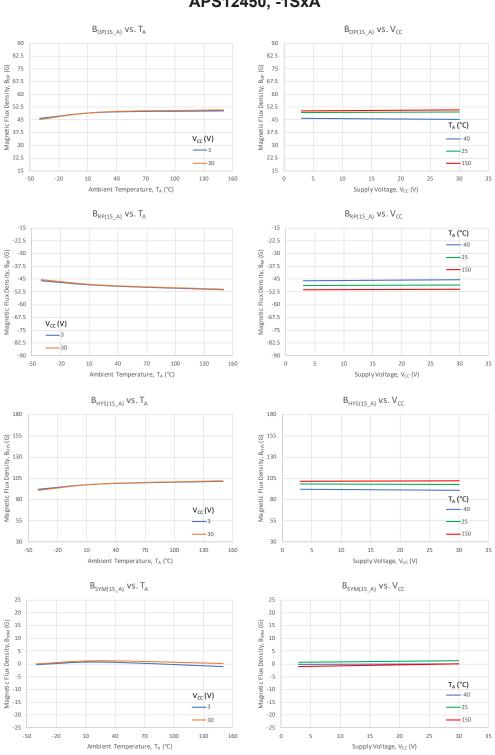

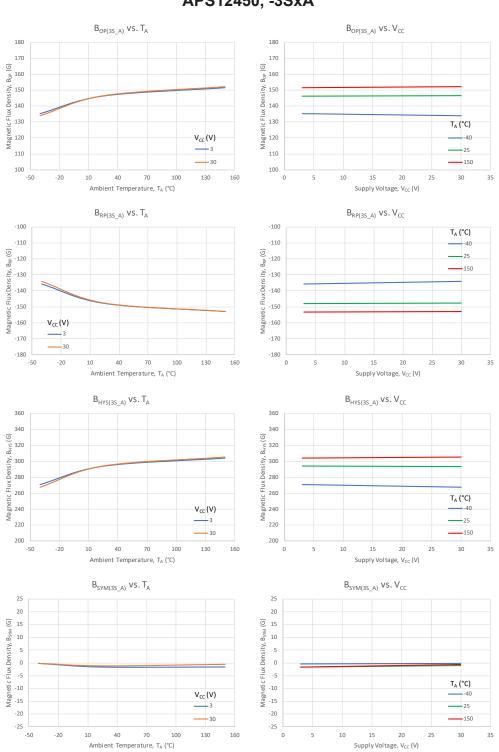

### CHARACTERISTIC PERFORMANCE DATA

### CHARACTERISTIC PERFORMANCE DATA (continued)

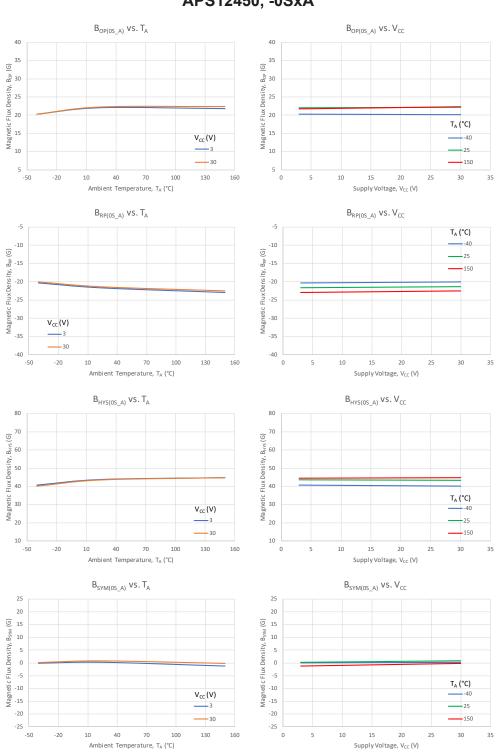

### CHARACTERISTIC PERFORMANCE DATA APS12450, -0SxA

### CHARACTERISTIC PERFORMANCE DATA APS12450, -1SxA

### CHARACTERISTIC PERFORMANCE DATA APS12450, -3SxA

### **FUNCTIONAL DESCRIPTION**

### Operation

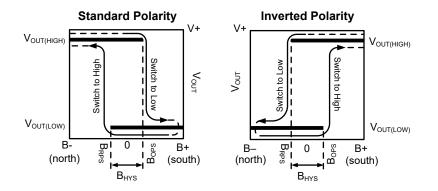

The output of these devices switches when a magnetic field perpendicular to the Hall-effect sensor exceeds the operate-point threshold  $(B_{OP})$ . When the magnetic field is reduced below the release point  $(B_{RP})$ , the device output switches to the alternate state. The output state (polarity) and magnetic-field polarity depend on the selected device options. The device is a latch; therefore,  $B_{OP}$  and  $B_{RP}$  are in opposite magnetic-field polarities.

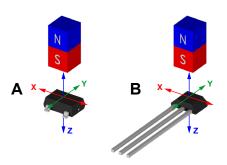

The difference between operate  $(B_{OP})$  and release  $(B_{RP})$  points is the hysteresis  $(B_{HYS})$ . Hysteresis allows clean switching of the output, even in the presence of external mechanical vibration and electrical noise. The hysteresis is set to double the programmed operating point. The output switching behavior relative to increasing and decreasing magnetic field is shown in Figure 1. On the horizontal axis, the B+ direction indicates increasing south-polarity magneticfield strength. The sensing orientation of the magnetic field relative to the device package is shown in Figure 2.

NOTE: This device *latches*; that is, a south pole of sufficient strength toward the branded face of the device turns the device on, and the device remains on with removal of the south pole.

The potential unipolar and omnipolar options and output polarity options that can be configured with the APS12450 are shown in Figure 1. The direction of the applied magnetic field is perpendicular to the branded face of the APS12450 (see Figure 2).

Figure 1: Hall latch magnetic and output polarity options B– indicates increasing north-polarity magnetic-field strength, and B+ indicates increasing south-polarity magnetic-field strength.

Figure 2: Magnetic Sensing Orientations APS12450 LH (Panel A), APS12450 UA (Panel B)

### **Three-Wire Hall-Effect Latch with Advanced Diagnostics**

### FUNCTIONAL SAFETY

The APS12450 was developed in accordance with ISO 26262as a hardware safety element out of context with ASIL B capability for use in automotive safety-related systems when integrated and used in the manner prescribed in the applicable safety manual and datasheet.

### **Diagnostics Mode Operation**

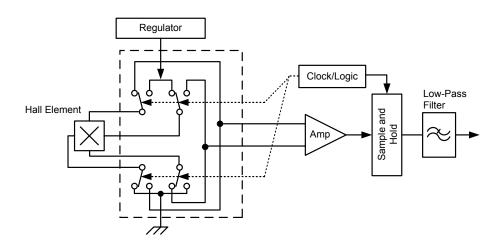

The APS12450 features a proprietary diagnostics routine that meets ASIL B safety requirements. This internal diagnostics routine continuously runs in the background, monitoring all key subsystems of the IC. These subsystems are shown in Table 1 and Figure 3. The diagnostic scheme runs at high speed and provides minimal impact on device performance. Signal-path diagnostics are injected and measured in less than 2  $\mu$ s, while all other diagnostics are run in real time in the background. The Hall element biasing circuit and voltage regulator are checked for valid operation, and the digital and nonvolatile memory blocks are checked for valid device configuration.

The signal-path monitoring system verifies two internal state transitions ( $B_{OP}$  and  $B_{RP}$  within limits) under typical operation. If these output transitions do not occur, or if another internal fault is detected, the output enters the fault state (see the Three-Wire Diagnostic Output section).

In the event of an internal fault, the device runs the diagnostics routine every 2 ms ( $t_{DIAGF}$ ). The periodic recovery-attempt sequence allows the device to continually check for the presence of a fault and return to typical operation if the fault condition clears.

If the fault is no longer present, the output resumes typical operation. However, if the fault is persistent, the device does not exit fault mode and the output voltage continues to be  $V_{OUT(FAULT)}$ .

When a system rating higher than ASIL B is required, additional external safety measures may be employed (e.g., sensor redundancy and rationality checks, etc.). Refer to the device safety manual for additional details about the diagnostics.

|   |                                                              | Feature           | Coverage                                                           |

|---|--------------------------------------------------------------|-------------------|--------------------------------------------------------------------|

| Γ | 1                                                            | Hall plate        | Connectivity and biasing of Hall plate                             |

| ſ | 2 Signal path Signal path and Schmitt trigger                |                   | Signal path and Schmitt trigger                                    |

|   | 3                                                            | Voltage regulator | Regulator voltage for typical operation                            |

|   | 4 Digital subsystem Digital subsystem and nonvolatile memory |                   | Digital subsystem and nonvolatile memory                           |

|   | 5                                                            | Entire system     | Overtemperature and redundancies for single-point failures         |

|   | 6                                                            | Output            | Output verified through valid regulation states (external monitor) |

#### Table 1: Diagnostics Coverage

Figure 3: Diagnostics Coverage Block Diagram

### **Power-On Behavior**

During power-on, the output voltage is in the fault state  $(V_{OUT(FAULT)})$ , which is the pull-up voltage  $(V_{PU})$ , until the device is ready to respond appropriately to the input magnetic field (t > t<sub>ON</sub>). If the device powers on with the field within the hysteresis band, the output switches from VOUT(FAULT) to the off state (V<sub>OUT(HIGH)</sub>) with standard output polarity as shown in Figure 4. For inverted output polarity operation, the output switches from V<sub>OUT(FAULT)</sub> to V<sub>OUT(LOW)</sub> (not shown).

#### Figure 4: Power-On Sequence

### **Temperature Coefficient and Magnet Selection**

The APS12450 allows the user to select the magnetic temperature coefficient to compensate for drifts of SmCo, NdFeB, and ferrite magnets over temperature, as indicated in the Magnetic Characteristics specifications table. This compensation improves the magnetic system performance over the entire temperature range. For example, the magnetic field strength from NdFeB decreases as the temperature increases from 25°C to 150°C. This lower magnetic field strength means that a lower switching threshold is required to maintain switching at the same distance from the magnet to the sensor. Correspondingly, higher switching thresholds are required at cold temperatures, as low as -40°C, due to the higher magnetic field strength from the NdFeB magnet. The APS12450 compensates the switching thresholds over temperature as described above. It is recommended that system designers evaluate their magnetic circuit over the expected operating temperature range to ensure the magnetic switching requirements are met.

A sample calculation is provided in the Applications Information section.

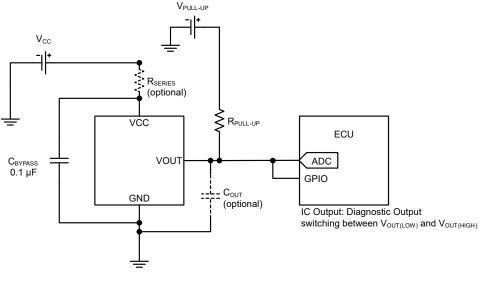

### **Three-Wire Diagnostic Output**

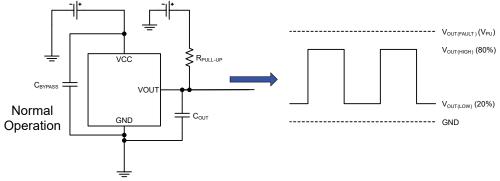

Three-wire diagnostic output enables the user to identify various fault conditions external to the IC, in addition to the internal fault detection. The output low ( $V_{OUT(LOW)}$ ) and high ( $V_{OUT(HIGH)}$ ) states are ratiometric to the pull-up voltage, with low and high states being 20% and 80% respectively. For example, for a  $V_{CC}$

and  $V_{PULL-UP}$  of 5 V, the output-state levels are 1 V and 4 V, ±0.5 V. The output RC time constant ( $\tau$ ) must be less than 3 µs (e.g.,  $R_{PU} = 3 \text{ k}\Omega$  and  $C_{OUT} = 1 \text{ nF}$ ), and  $V_{PU}$  must be equal to  $V_{CC}$  (recommend pulling up  $V_{OUT}$  directly to  $V_{CC}$ ).

During typical operation (Figure 5), the output switches between the  $V_{OUT(LOW)}$  (20%) and  $V_{OUT(HIGH)}$  (80%) states.

Figure 5: The APS12450 diagnostic output during typical operation (no fault detected)

With various opens and shorts on any of the IC pins, the output is no longer controlled by the IC. The output itself may continue to switch, depending on the external connectivity fault; however, the output level(s) observed deviate from the 20% and 80% (of  $V_{PU}$ ) output levels.

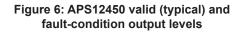

If an internal fault is detected via diagnostics monitoring, the output becomes set to the fault state,  $V_{OUT(FAULT)}$ , which is equal to the pull-up voltage,  $V_{PU}$ .

Any output voltage level beyond the valid  $V_{OUT(HIGH)}$  and  $V_{OUT(LOW)}$  range indicates a fault as shown in Figure 6. The observed voltage on VOUT relative to potential fault conditions are summarized in Table 2.

| Table 2: Fault Conditions and Resulting | J Output |

|-----------------------------------------|----------|

| Level                                   |          |

| Fault           | Output Level                                    |

|-----------------|-------------------------------------------------|

| No Fault        | 20% or 80% of V <sub>PU</sub> ,<br>respectively |

| Short, VCC-VOUT | V <sub>CC</sub>                                 |

| Short, VOUT-GND | GND                                             |

| Short, VCC-GND  | V <sub>PU</sub>                                 |

| Open, VCC       | V <sub>PU</sub>                                 |

| Open, VOUT      | V <sub>PU</sub>                                 |

| Open, GND       | V <sub>PU</sub>                                 |

| Internal Fault  | V <sub>PU</sub>                                 |

Note:  $V_{OUT(FAULT)} \le V_{PULL-UP}$  and  $V_{PULL-UP} = V_{CC}$ .

APS12450 Three-Wire Hall-Effect Latch with Advanced Diagnostics

### **Fault Detection and Retry**

The fault detection diagnostics run continuously in the background during typical operation after the device has powered-on. If a fault is detected, the output immediately changes to the  $V_{OUT(FAULT)}$

state. The diagnostics continue to be retried approximately every 2 ms. If the fault recovers, the output returns to typical operation. See Figure 7.

\* 4x Diagnostic Cycles completed every 0.025 ms (nom.)

\*\* Diagnostic Fault Retry Time interval is 2 ms (nom.)

### **Output Overshoot**

When the output switches from  $V_{OUT(LOW)}$  to  $V_{OUT(HIGH)}$ , depending on the RC circuit, a small overshoot can occur  $(V_{OUT(H)OVER})$ .  $V_{OUT(H)OVER}$  is specified as a percentage of  $V_{PULL-UP}$  (and/or  $V_{CC}$ , which needs to be the same). Therefore with an RC time constant ( $\tau$ ) of 3 µs (see the Applications Information section), a nominal overshoot of 2% is possible. With  $V_{PULL-UP}$  at 5 V, the output may overshoot by 0.1 V, for less than 5 µs ( $t_{VOUT(H)OVER}$ ). The output edge profile is shown in Figure 7.

For example, with a 5 V pull-up, if  $V_{OUT(HIGH)}$  is at the upper limit (90%),  $V_{OUT(HIGH)}$  is 4.5 V. With a  $\tau$  of 3 µs at room temperature, the output can briefly reach 4.6 V until it settles to 4.5 V. Because  $V_{OUT(HIGH)}$  is valid between 70% and 90%, or 3.5 and 4.5 V, this

condition is not out of specification. The specification for the output-off voltage overshoot pertains only to conditions where the overshoot is greater than the  $V_{OUT(HIGH)MAX}$  specification.

Figure 8: Output Overshoot

### **Three-Wire Hall-Effect Latch with Advanced Diagnostics**

### APPLICATIONS INFORMATION

### **Typical Applications**

For the LH and UA packages, an external bypass capacitor,  $C_{BYP}$ , should be connected (in close proximity to the Hall sensor) between the supply and ground of the device to reduce both external noise and noise generated by the chopper stabilization technique. As shown in Figure 9, a 0.1 µF bypass capacitor is typical, with an optional output capacitor,  $C_{OUT}$  (recommended 1 nF).

The time constant of the RC circuit ( $\tau$ ) on output must be less than 3  $\mu$ s, where:

$$\begin{aligned} \tau &= R_{PULLUP} \times C_{OUT} \\ &= 3 \ k\Omega \times 1 \ nF \\ &= 3 \ \mu s \end{aligned}$$

The resistor,  $R_{PULLUP}$ , must be between 2 and 30 k $\Omega$ .

#### **Temperature Compensation**

To calculate the typical effect of the TC<sub>SENS</sub> on B<sub>OP</sub> (or B<sub>RP</sub>), multiply B<sub>OP</sub> at the starting temperature by TC<sub>SENS</sub> and the change in temperature.

Example  $B_{OP}$  calculation for TC<sub>SENS</sub> compensation from 25°C to 150°C, for TC<sub>SENS</sub> = -0.12%/°C, and  $B_{OP(25C)}$  = 180 G:

$$\begin{split} \Delta T_{A} &= 150^{\circ}C - 25^{\circ}C = 125^{\circ}C \\ B_{OP(150C)} &= B_{OP(25C)} + (B_{OP(25C)} \times TC \times \Delta T_{A}) \\ &= 180 \text{ G} + (180 \text{ G} \times -0.12\% / ^{\circ}C \times 125^{\circ}C) \\ &= 180 \text{ G} + (-27 \text{ G}) \\ &= 153 \text{ G} \end{split}$$

Figure 9: Typical Applications Circuits Diagnostic Output

|                  | Diagnostic Output [1]                                                  |

|------------------|------------------------------------------------------------------------|

| V <sub>CC</sub>  | 3 to 30 V                                                              |

| V <sub>PU</sub>  | V <sub>CC</sub>                                                        |

| C <sub>BYP</sub> | 0.1 µF                                                                 |

| C <sub>OUT</sub> | τ <sub>RC</sub> < 3 μs                                                 |

| R <sub>PU</sub>  | l <sub>OUT</sub> < 12 mA<br>τ <sub>RC</sub> < 3 μs<br>2 kΩ < R < 30 kΩ |

| R <sub>S</sub>   | 100 Ω*                                                                 |

[1] The following application circuit conditions are required:

• The  $\tau$  of the RC on output must be < 3  $\mu$ s.

• 2 k $\Omega$  < R<sub>PU</sub> < 30 k $\Omega$ .

•  $V_{PU} = V_{CC}$  (recommend pulling VOUT up to VCC).

# APS12450 Three-Wire Hall-Effect Latch with Advanced Diagnostics

Extensive application information about magnets and Hall-effect sensors is available in:

- Hall-Effect IC Applications Guide, AN27701 (https://www.allegromicro.com/-/media/files/applicationnotes/an27701-hall-effect-ic-application-guide.pdf)

- Guidelines For Designing Subassemblies Using Hall-Effect Devices, AN27703.1 (<u>https://www.allegromicro.com/-/media/files/application-notes/an277031-guidelines-for-designing-subassemblies-using-hall-effect-devices.pdf</u>)

- Soldering Methods for Allegro's Products SMT and Through-Hole, AN26009 (<u>https://www.allegromicro.com/-/media/files/application-</u> notes/an26009-soldering-methods-for-allegro-products.pdf)

- Functional Safety Challenges to the Automotive Supply Chain (https://www.allegromicro.com/en/insights-and-innovations/ technical-documents/general-semiconductor-information/ functional-safety-challenges-automotive-supply-chain)

All are provided on the Allegro website:

www.allegromicro.com

#### **Chopper Stabilization Technique**

A limiting factor for switch-point accuracy when using Halleffect technology is the small-signal voltage developed across the Hall plate. This voltage is proportionally small relative to the offset that can be produced at the output of the Hall sensor. This makes it difficult to process the signal and maintain an accurate, reliable output over the specified temperature and voltage range. Chopper stabilization is a proven approach used to minimize Hall offset.

The technique, dynamic quadrature offset cancellation, removes key sources of the output drift induced by temperature and package stress. This offset reduction technique is based on a signal modulation-demodulation process. "Figure 10: Model of Chopper Stabilization Circuit (Dynamic Offset Cancellation)" illustrates how it is implemented.

The undesired offset signal is separated from the magnetically induced signal in the frequency domain through modulation. The subsequent demodulation acts as a modulation process for the offset causing the magnetically induced signal to recover its original spectrum at baseband while the DC offset becomes a high-frequency signal. Then, using a low-pass filter, the signal passes while the modulated DC offset is suppressed. The innovative Allegro chopper-stabilization technique uses a high-frequency clock.

The high-frequency operation allows a greater sampling rate that produces higher accuracy, reduced jitter, and faster signal processing. Additionally, filtering is more effective and results in a lower-noise analog signal at the sensor output. Devices such as the APS12450 that use this approach have an extremely stable quiescent Hall output voltage, are immune to thermal stress, and have precise recoverability after temperature cycling. This technique is made possible through the use of a BiCMOS process that allows the use of low-offset and low-noise amplifiers in combination with high-density logic and sample-and-hold circuits.

Figure 10: Model of Chopper Stabilization Circuit (Dynamic Offset Cancellation)

### POWER DERATING

The device must be operated below the maximum junction temperature,  $T_J$  (max). Reliable operation may require derating supplied power and/or improving the heat dissipation properties of the application.

Thermal resistance (junction to ambient),  $R_{\theta JA}$ , is a figure of merit summarizing the ability of the application and the device to dissipate heat from the junction (die), through all paths to ambient air.  $R_{\theta JA}$  is dominated by the effective thermal conductivity, K, of the printed circuit board, which includes adjacent devices and board layout. Thermal resistance from the die junction to case,  $R_{\theta JC}$ , is a relatively small component of  $R_{\theta JA}$ . Ambient air temperature,  $T_A$ , and air motion are significant external factors in determining a reliable thermal operating point.

The following three equations can be used to determine operation points for given power and thermal conditions.

$$P_D = V_{IN} \times I_{IN} \tag{1}$$

$$\Delta T = P_D \times R_{\theta JA} \tag{2}$$

$$T_J = T_A + \Delta T \tag{3}$$

For example, given common conditions:  $T_A = 25^{\circ}C$ ,  $V_{CC} = 12$  V,  $I_{CC} = 4$  mA, and  $R_{\theta JA} = 110^{\circ}C/W$  for the LH package, then:

$$P_D = V_{CC} \times I_{CC} = 12 \ V \times 4 \ mA = 48 \ mW$$

$$\Delta T = P_D \times R_{\theta JA} = 48 \ mW \times 110^{\circ}C/W = 5.28^{\circ}C$$

$$T_J = T_A + \Delta T = 25^{\circ}C + 5.28^{\circ}C = 31.28^{\circ}C$$

### Determining Maximum V<sub>CC</sub>

For a given ambient temperature,  $T_A$ , the maximum allowable power dissipation as a function of  $V_{CC}$  can be calculated.  $P_D$  (max) represents the maximum allowable power level without exceeding  $T_J$  (max) at a selected  $R_{\theta JA}$  and  $T_A$ .

Example:  $V_{CC}$  at  $T_A = 150^{\circ}$ C, package UA, using low-K PCB. Using the worst-case ratings for the device, specifically:  $R_{0JA} = 165^{\circ}$ C/W,  $T_J$  (max) = 165°C,  $V_{CC}$  (max) = 24 V, and  $I_{CC}$  (max) = 4 mA, calculate the maximum allowable power level,  $P_D$  (max). First, using Equation 3:

$$\Delta T (max) = T_J (max) - T_A = 165^{\circ}C - 150^{\circ}C = 15^{\circ}C$$

This provides the allowable increase to  $T_J$  resulting from internal power dissipation. Then, from Equation 2:

$$P_D(max) = \Delta T(max) \div R_{\theta,IA} = 15^{\circ}C \div 165^{\circ}C/W = 91 \text{ mW}$$

Finally, using Equation 1, solve for the maximum allowable  $V_{CC}$  for the given conditions:

$$V_{CC}(est) = P_D(max) \div I_{CC}(max) = 91 \ mW \div 4 \ mA = 22.8 \ V$$

The result indicates that, at  $T_A$ , the application and device can dissipate adequate amounts of heat at voltages  $\leq V_{CC}$  (est).

If the application requires  $V_{CC} > V_{CC(est)}$ ,  $R_{\theta JA}$  must be improved. This can be accomplished by adjusting the layout or PCB materials, or by controlling the ambient temperature.

### Determining Maximum T<sub>A</sub>

If the V<sub>CC</sub> (max) level is known, and the system designer would like to determine the maximum allowable ambient temperature  $T_A$  (max)—for example, in a worst-case scenario with conditions  $V_{CC}$  (max) = 40 V,  $I_{CC}$  (max) = 4 mA, and  $R_{\theta JA}$  = 228°C/W for the LH package—using Equation 1, the largest possible amount of dissipated power is:

$$P_D = V_{IN} \times I_{IN}$$

$$P_D = 40 \ V \times 4 \ mA = 160 \ mW$$

Then, by rearranging Equation 3 and substituting with Equation 2:

$$T_A (max) = T_J (max) - \Delta T$$

$$T_A (max) = 165^{\circ}C - (160 \text{ mW} \times 228^{\circ}C/W)$$

$$T_A (max) = 165^{\circ}C - 36.5^{\circ}C = 128.5^{\circ}C$$

In another example, the maximum supply voltage is equal to  $V_{CC}$  (min). Therefore,  $V_{CC}$  (max) = 3 V and  $I_{CC}$  (max) = 4 mA. By using Equation 1, the largest possible amount of dissipated power is:

$$P_D = V_{IN} \times I_{IN}$$

$$P_D = 3 \ V \times 4 \ mA = 12 \ mW$$

Then, by rearranging Equation 3 and substituting with Equation 2:

$$T_A (max) = T_J (max) - \Delta T$$

$T_A (max) = 165^{\circ}C - (12 \text{ mW} \times 228^{\circ}C/W)$

$T_A (max) = 165^{\circ}C - 11.6^{\circ}C = 162.3^{\circ}C$

The example above indicates that, at  $V_{CC} = 3$  V and  $I_{CC} = 4$  mA, the  $T_A$  (max) can be as high as 162.3°C without exceeding

the  $T_A$  (max) can be as high as 162.3°C without exceeding  $T_J$  (max). However, the  $T_A$  (max) rating of the device is 150°C; the device performance is not guaranteed above  $T_A = 150$ °C.

### **Three-Wire Hall-Effect Latch with Advanced Diagnostics**

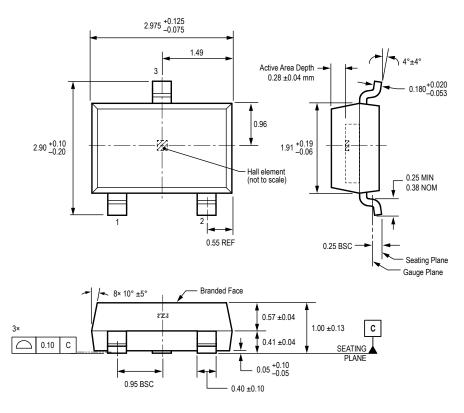

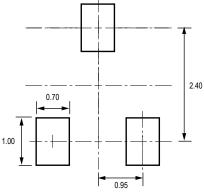

### Package LH, 3-Pin SOT23W

For Reference Only – Not for Tooling Use (Reference Allegro DWG-0000628, Rev. 1) NOT TO SCALE Dimensions in millimeters Dimensions exclusive of mold flash, gate burrs, and dambar protrusions Exact case and lead configuration at supplier discretion within limits shown

#### PCB Layout Reference View

All pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary to meet application process requirements and PCB layout tolerances

Standard Branding Reference View 1

Line 1 = Three digit assigned brand number

Branding scale and appearance at supplier discretion

# APS12450 Three-Wire Hall-Effect Latch with Advanced Diagnostics

### Package UA, 3-Pin SIP, Matrix HD Style

### **Three-Wire Hall-Effect Latch with Advanced Diagnostics**

#### **REVISION HISTORY**

| Number | Date              | Description                                                                                                                                                                                                                 |

|--------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -      | January 31, 2019  | Initial release                                                                                                                                                                                                             |

| 1      | April 23, 2019    | Updated ASIL status                                                                                                                                                                                                         |

| 2      | April 28, 2022    | Updated package drawings (pages 21-22)                                                                                                                                                                                      |

| 3      | February 13, 2024 | Removed year from ISO 2626 references and "pending assessment" from ASIL references (pages 1 and 13), and made minor editorial corrections throughout including minimization of capitalization and use of the future tense. |

Copyright 2024, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

<u>Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of</u> <u>Allegro's product can reasonably be expected to cause bodily harm.</u>

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website:

www.allegromicro.com

### **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Allegro MicroSystems:

APS12450LLHALT-0SLAAPS12450LLHALT-1SLAAPS12450LLHALT-3SLAAPS12450LLHALX-0SLAAPS12450LLHALX-1SLAAPS12450LLHALX-3SLAAPS12450LUAA-0SLAAPS12450LUAA-1SLAAPS12450LUAA-1SLA3SLA