## FEATURES AND BENEFITS

- **GMR technology** integrates high sensitivity MR (magnetoresistive) sensor elements and high precision BiCMOS circuits on a single silicon integrated circuit, offering high accuracy, low magnetic field operation

- Integrated capacitor in a single overmolded miniature package provides greater EMC robustness

- SolidSpeed Digital Architecture supports advanced algorithms, maintaining performance in the presence of extreme system-level disturbances, including vibration immunity capability over the full target pitch

- Flexible orientation for xMR or Hall replacement

- ASIL B(D) rating based on integrated diagnostics and certified safety design process

- **Two-wire current source output** pulse-width protocol supporting speed, direction, and ASIL

- **EEPROM** offers device traceability throughout the production process

## DESCRIPTION

The A19350 is a giant magnetoresistance (GMR) integrated circuit (IC) that provides a user-friendly two-wire solution for applications where speed and direction information is required. The small integrated package includes an integrated capacitor and GMR IC in a single overmold design with an additional molded lead-stabilizing bar for robust shipping and ease of assembly.

The GMR-based IC is designed for use in conjunction with front-biased ring magnet encoders. State-of-the-art GMR technology with industry-leading signal processing algorithms accurately switch in response to low-level differential magnetic signals. The high sensitivity of GMR combined with differential sensing offers inherent rejection of interfering common-mode magnetic fields and valid speed and direction over larger air gaps, commonly required in wheel speed sensing applications.

Patented GMR technology allows the same orientation as Hall-effect for a drop-in solution in the application.

Integrated diagnostics are used to detect an IC failure which impacts the output protocol's accuracy, providing coverage compatible with ASIL B(D) compliance. Built-in EEPROM scratch memory offers traceability of the device throughout the IC's production process.

The IC is offered in the UB package, which integrates the IC and a high-temperature ceramic capacitor in a single overmold SIP package for enhanced EMC performance. The 2-pin SIP package is lead (Pb) free, with tin leadframe plating.

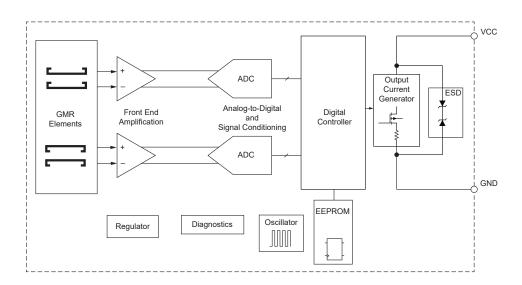

#### Figure 1: Functional Block Diagram

#### **SELECTION GUIDE\***

| Part Number      | Packing                             |

|------------------|-------------------------------------|

| A19350LUBATN-FBE | Topo and Book 4000 pieces per real  |

| A19350LUBATN-RBE | Tape and Reel, 4000 pieces per reel |

\* Not all combinations are available. Contact Allegro sales for availability and pricing of custom programming options.

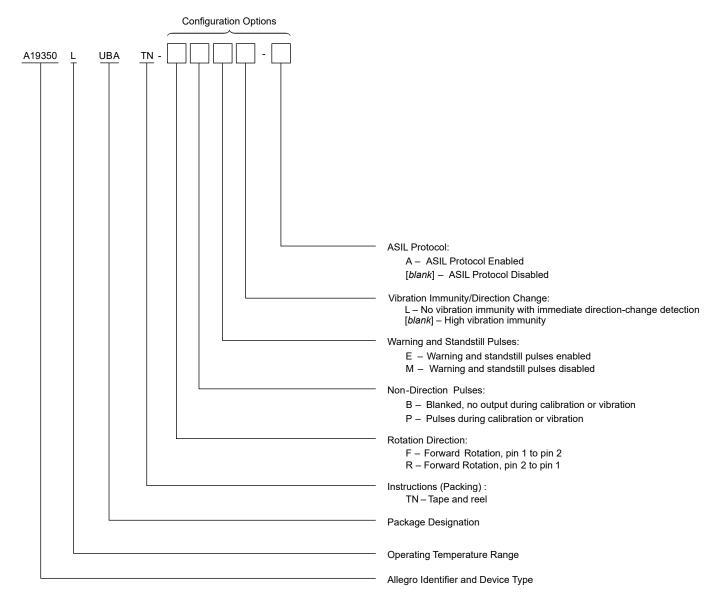

### **Complete Part Number Format**

## SPECIFICATIONS

#### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic                | Symbol              | Notes                                                              | Rating     | Unit |

|-------------------------------|---------------------|--------------------------------------------------------------------|------------|------|

| Supply Voltage                | V <sub>cc</sub>     | Refer to Power Derating section; potential between pin 1 and pin 2 | 28         | V    |

| Reverse Supply Voltage        | V <sub>RCC</sub>    |                                                                    | -18        | V    |

| Operating Ambient Temperature | T <sub>A</sub>      |                                                                    | -40 to 150 | °C   |

| Maximum Junction Temperature  | T <sub>J(max)</sub> |                                                                    | 165        | °C   |

| Storage Temperature           | T <sub>stg</sub>    |                                                                    | -65 to 170 | °C   |

| Applied Magnetic Flux Density | В                   | In any direction                                                   | 500        | G    |

#### INTERNAL DISCRETE CAPACITOR RATINGS

| Characteristic      | Characteristic Symbol Test Conditions                                         |  | Value | Unit |

|---------------------|-------------------------------------------------------------------------------|--|-------|------|

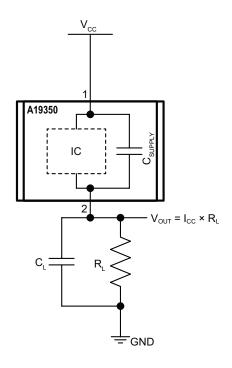

| Nominal Capacitance | nce C <sub>SUPPLY</sub> Connected between pin 1 and pin 2 (refer to Figure 2) |  | 2.2   | nF   |

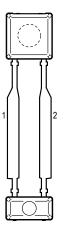

### PINOUT DIAGRAM AND TERMINAL LIST

Package UB, 2-Pin SIP Pinout Diagram

#### **Terminal List Table**

| Pin Name | Pin Number | Function       |

|----------|------------|----------------|

| VCC      | 1          | Supply Voltage |

| GND      | 2          | Ground         |

Figure 2: Application Circuit

Allegro MicroSystems 955 Perimeter Road Manchester, NH 03103-3353 U.S.A. www.allegromicro.com

#### OPERATING CHARACTERISTICS: Valid throughout full operating voltage and temperature ranges, unless otherwise specified

| Characteristic                        | Symbol                                          | Test Conditions                                                                                                                                  | Min.                 | Typ. [1] | Max. | Unit |

|---------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------|------|------|

| ELECTRICAL CHARACTERISTICS            |                                                 |                                                                                                                                                  |                      |          |      |      |

| Supply Voltage <sup>[2]</sup>         | V <sub>CC</sub>                                 | Potential between pin 1 and pin 2                                                                                                                | 4                    | -        | 24   | V    |

| Reverse Supply Current <sup>[3]</sup> | I <sub>RCC</sub>                                | $V_{CC} = V_{RCC(MAX)}$                                                                                                                          | -10                  | _        | -    | mA   |

| Supply Zener Clamp Voltage            | V <sub>Zsupply</sub>                            | $I_{CC} = I_{CC(MAX)} + 3 \text{ mA}, T_A = 25^{\circ}\text{C}$                                                                                  | 28                   | _        | -    | V    |

| Supply Current                        | I <sub>CC(LOW)</sub>                            | Low-current state                                                                                                                                | 5.9                  | 7        | 8.4  | mA   |

|                                       | I <sub>CC(HIGH)</sub>                           | High-current state                                                                                                                               | 12                   | 14       | 16   | mA   |

| Supply Current Ratio [4]              | I <sub>CC(HIGH)</sub> /<br>I <sub>CC(LOW)</sub> | Measured as a ratio of high current to low current (isothermal)                                                                                  | 1.9                  | -        | _    | -    |

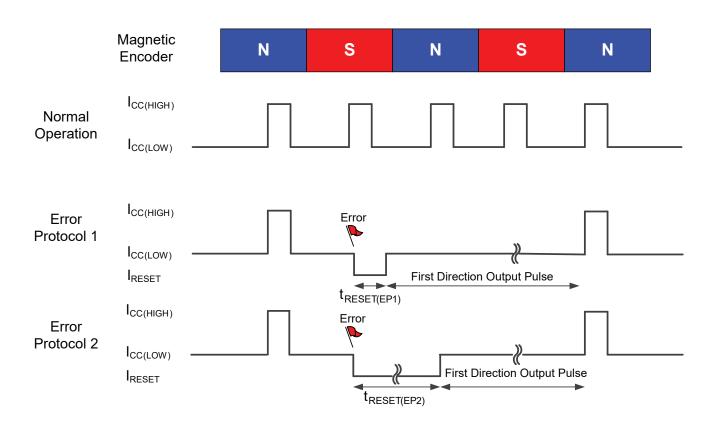

| ASIL Safety Current                   | I <sub>RESET</sub>                              | Refer to Figure 11                                                                                                                               | 1.5                  | 3.5      | 3.9  | mA   |

| ASIL Safety Current Time              | t <sub>RESET(EP1)</sub>                         | Refer to Figure 11 (Error Protocol 1)                                                                                                            | -                    | 90       | -    | μs   |

| ASIL Salety Current Time              | t <sub>RESET(EP2)</sub>                         | Refer to Figure 11 (Error Protocol 2)                                                                                                            | 3                    | -        | 6    | ms   |

| Output Rise/Fall Time                 | t <sub>r</sub> , t <sub>f</sub>                 | Voltage measured at terminal 2 in Figure 2;<br>R <sub>L</sub> = 100 $\Omega$ , C <sub>L</sub> = 10 pF, measured between<br>10% and 90% of signal | _                    | 2        | 4    | μs   |

| POWER-ON CHARACTERISTICS              |                                                 |                                                                                                                                                  |                      |          |      |      |

| Power-On State                        | POS                                             | $V_{CC} > V_{CC(min)}$ as connected in Figure 1                                                                                                  | I <sub>CC(LOW)</sub> |          | mA   |      |

| Power-On Time                         | t <sub>PO</sub>                                 | $V_{CC} > V_{CC(min)}$ as connected in Figure 1 <sup>[5]</sup>                                                                                   | -                    | _        | 1    | ms   |

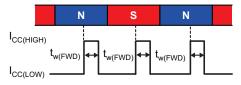

| OUTPUT PULSE-WIDTH PROTOCO            | L [6]                                           |                                                                                                                                                  |                      |          |      |      |

| Pulse-Width Off Time                  | t <sub>W(PRE)</sub>                             |                                                                                                                                                  | 38                   | 45       | 52   | μs   |

| Forward Pulse Width                   | t <sub>W(FWD)</sub>                             |                                                                                                                                                  | 76                   | 90       | 104  | μs   |

| Reverse Pulse Width                   | t <sub>W(REV)</sub>                             |                                                                                                                                                  | 153                  | 180      | 207  | μs   |

| Warning Pulse Width                   | t <sub>W(WARN)</sub>                            | -xxE variant                                                                                                                                     | 38                   | 45       | 52   | μs   |

| Standstill Pulse Width                | t <sub>W(STILL)</sub>                           | -xxE variant                                                                                                                                     | 1232                 | 1440     | 1656 | μs   |

| Standstill Period <sup>[7]</sup>      | t <sub>STOP</sub>                               | -xxE variant                                                                                                                                     | 590                  | 737      | 848  | ms   |

| Non-Direction Pulse Width             | t <sub>W(ND)</sub>                              | -xxE variant                                                                                                                                     | 306                  | 360      | 414  | μs   |

[1] Typical values are at T<sub>A</sub> = 25°C and V<sub>CC</sub> = 12 V. Performance may vary for individual units, within the specified maximum and minimum limits.

<sup>[2]</sup> Maximum voltage must be adjusted for power dissipation and junction temperature; see representative Power Derating section.

<sup>[3]</sup> Negative current is defined as conventional current coming out of (sourced from) the specified device terminal.

<sup>[4]</sup> Supply current ratio is taken as a mean value of  $I_{CC(HIGH)} / I_{CC(LOW)}$ . <sup>[5]</sup> Time between power-on to  $I_{CC}$  stabilizing. Output transients prior to  $t_{PO}$  should be ignored.

<sup>[6]</sup> Pulse width measured at threshold of  $(I_{CC(HIGH)} + I_{CC(LOW)})/2$ . <sup>[7]</sup> At operating frequencies less than 2 Hz, -xxM variant must be used in order to output forward/reverse/warning direction pulses.

Continued on the next page ...

#### **OPERATING CHARACTERISTICS (continued):** Valid throughout full operating voltage and temperature ranges,

unless otherwise specified

| Characteristic                                          | Symbol                                         | Test Conditions                                                                                                                                     | Min. | Typ. <sup>[1]</sup> | Max. | Unit               |

|---------------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|------|--------------------|

| INPUT CHARACTERISTICS AND PE                            | RFORMANC                                       | E                                                                                                                                                   |      |                     |      |                    |

| Operating Frequency,<br>Forward Rotation <sup>[8]</sup> | f <sub>FWD</sub>                               |                                                                                                                                                     | 0    | _                   | 3.9  | kHz                |

| Operating Frequency,<br>Reverse Rotation <sup>[8]</sup> | f <sub>REV</sub>                               |                                                                                                                                                     | 0    | _                   | 2.4  | kHz                |

| Operating Frequency,<br>Warning Pulses <sup>[8]</sup>   | f <sub>WARN</sub>                              |                                                                                                                                                     | 0    | -                   | 6.4  | kHz                |

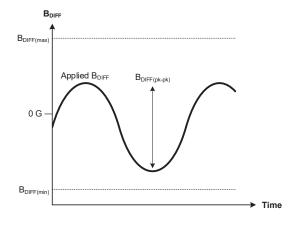

| Operating Differential Magnetic Input <sup>[9]</sup>    | D                                              | Peak-to-peak of differential magnetic input (refer to Figure 6)                                                                                     | 5    | _                   | -    | G                  |

| Operating Differential Magnetic Input (9)               | B <sub>DIFF(pk-pk)</sub>                       | Peak-to-peak allowable for repeatability (refer to Figure 6)                                                                                        | 20   | _                   | -    | G                  |

| Operating Differential Magnetic Range <sup>[8]</sup>    | B <sub>DIFF</sub>                              | Refer to Figure 6                                                                                                                                   | -300 | -                   | 300  | G                  |

| Operating Differential Magnetic Offset                  | B <sub>DIFFEXT</sub>                           | Differential magnetic offset; see Figure 6                                                                                                          | -40  | -                   | 40   | G                  |

| Operating Single-Ended Bx Field<br>Magnitude            | Bx                                             | Refer to Figure 7 for field orientations                                                                                                            | -50  | -                   | 50   | G                  |

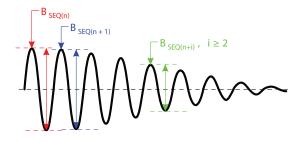

| Allowable Differential Sequential<br>Signal Variation   | B <sub>SEQ(n+1)</sub> /<br>B <sub>SEQ(n)</sub> | Signal period-to-period variation (refer to Figure 3)                                                                                               | 60   | -                   | 200  | %                  |

|                                                         | B <sub>SEQ(n+i)</sub> /<br>B <sub>SEQ(n)</sub> | Overall signal variation (e.g. run-out) (refer to Figure 3)                                                                                         | 40   | -                   | 200  | %                  |

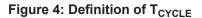

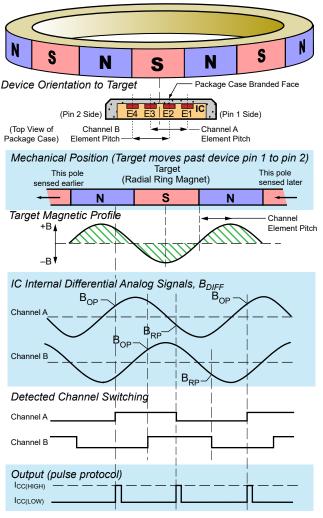

| Operate Point                                           | B <sub>OP</sub>                                | % of peak-to-peak IC-processed signal                                                                                                               | _    | 60                  | _    | %                  |

| Release Point                                           | B <sub>RP</sub>                                | % of peak-to-peak IC-processed signal                                                                                                               | _    | 40                  | _    | %                  |

| Air Gap Warning Level                                   | B <sub>WARN</sub>                              | Warning pulses output when B <sub>DIFF(pk-pk)</sub> < B <sub>WARN</sub>                                                                             | _    | 10                  | _    | G <sub>pk-pk</sub> |

| Repeatability <sup>[10]</sup>                           | Err <sub>θE</sub>                              | Constant air gap (greater than 20 G(pk-pk)),<br>temperature, and target speed. Sinusoidal input<br>signal. Greater than 1000 output edges captured. | _    | -                   | 0.3  | %                  |

| Target Pitch                                            | T <sub>PITCH</sub>                             | Arc length of each pole-pair (at 0 mm air gap)                                                                                                      | 1.4  | -                   | 8    | mm                 |

| Switch Point Separation                                 | B <sub>DIFF(SP-SEP)</sub>                      | Required amount of amplitude separated between channels at each $B_{OP}$ and $B_{RP}$ occurrence. (refer to Figure 5)                               | 20   | _                   | -    | %pk-pk             |

| THERMAL CHARACTERISTICS                                 |                                                |                                                                                                                                                     |      |                     |      |                    |

| Magnetic Temperature Coefficient <sup>[11]</sup>        | TC                                             | Valid for full temperature range based on ferrite                                                                                                   | _    | 0.2                 | _    | %/°C               |

| Package Thermal Resistance                              | R <sub>θJA</sub>                               | Single-layer PCB with copper limited to solder pads                                                                                                 | _    | 213                 | _    | °C/W               |

<sup>[8]</sup> If a higher frequency operation is required, an option is available.

[9] Differential magnetic field is measured for the Channel A (E1-E3) and Channel B (E2-E4). Each channel's differential magnetic field is measured between two GMR elements spaced by 1.4 mm. Magnetic field is measured to the GMR element spacing orientation in the By direction (Refer to Figure 7).

[<sup>10</sup>] Repeatability (i.e. jitter) is tested to 6 sigma and is guaranteed by design and characterization only.

[<sup>11</sup>] Ring magnet decreases in magnetic strength with rising temperature, and the device compensates. Note that B<sub>DIFF(pk-pk)</sub> requirement is not influenced by this.

# **OPERATING CHARACTERISTICS (continued):** Valid throughout full operating voltage and temperature ranges, unless otherwise specified

| Characteristic                    | Symbol                                  | Test Conditions                 | Min. | Typ. [1]    | Max. | Unit               |  |

|-----------------------------------|-----------------------------------------|---------------------------------|------|-------------|------|--------------------|--|

| PERFORMANCE CHARACTERISTI         | PERFORMANCE CHARACTERISTICS (-B OPTION) |                                 |      |             |      |                    |  |

| Calibration Period                |                                         | No Vibration Immunity Mode      | _    | -           | 3.5  | T <sub>CYCLE</sub> |  |

| Calibration Period                | _                                       | High Vibration Immunity Mode    | -    | -           | 3.5  | T <sub>CYCLE</sub> |  |

| Calibration Period First Correct  |                                         | No Vibration Immunity Mode      | _    | -           | 3.5  | T <sub>CYCLE</sub> |  |

| Direction Output                  | _                                       | High Vibration Immunity Mode    | _    | -           | 3.5  | T <sub>CYCLE</sub> |  |

| Vibratian Immunity                |                                         | No Vibration Immunity Mode [12] | _    | -           | _    | T <sub>CYCLE</sub> |  |

| Vibration Immunity                | _                                       | High Vibration Immunity Mode    | 2    | -           | _    | T <sub>CYCLE</sub> |  |

|                                   |                                         | No Vibration Immunity Mode      | _    | -           | 1.5  | T <sub>CYCLE</sub> |  |

| Vibration Recovery, First Output  | _                                       | High Vibration Immunity Mode    | _    | -           | 4    | T <sub>CYCLE</sub> |  |

| Vibration Recovery, First Correct | -                                       | No Vibration Immunity Mode      | _    | _           | 3    | T <sub>CYCLE</sub> |  |

| Direction Output                  |                                         | High Vibration Immunity Mode    | _    | _           | 4    | T <sub>CYCLE</sub> |  |

| PERFORMANCE CHARACTERISTI         | CS (-P OPTIC                            | DN)                             |      | · · · · · · |      |                    |  |

| Calibration Period                | _                                       | No Vibration Immunity Mode      | _    | _           | 1.5  | T <sub>CYCLE</sub> |  |

|                                   |                                         | High Vibration Immunity Mode    | _    | -           | 1.5  | T <sub>CYCLE</sub> |  |

| Calibration Period First Correct  | -                                       | No Vibration Immunity Mode      | _    | -           | 3.5  | T <sub>CYCLE</sub> |  |

| Direction Output                  |                                         | High Vibration Immunity Mode    | _    | -           | 3.5  | T <sub>CYCLE</sub> |  |

|                                   | -                                       | No Vibration Immunity Mode [12] | _    | _           | _    | T <sub>CYCLE</sub> |  |

| Vibration Immunity                |                                         | High Vibration Immunity Mode    | 2    | _           | _    | T <sub>CYCLE</sub> |  |

|                                   | _                                       | No Vibration Immunity Mode      | _    | _           | 1.5  | T <sub>CYCLE</sub> |  |

| Vibration Recovery, First Output  |                                         | High Vibration Immunity Mode    | _    | _           | 1.5  | T <sub>CYCLE</sub> |  |

| Vibration Recovery, First Correct |                                         | No Vibration Immunity Mode      | _    | _           | 3    | T <sub>CYCLE</sub> |  |

| Direction Output                  | _                                       | High Vibration Immunity Mode    | _    | _           | 4    | T <sub>CYCLE</sub> |  |

<sup>[12]</sup> Device has small inherent vibration immunity based on switch point locations.

**Figure 3: Differential Signal Variation**

B<sub>DIFF</sub> = Differential Input Signal; the differential magnetic flux sensed by the sensor

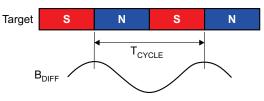

T<sub>CYCLE</sub> = Target Cycle; the amount of rotation that moves one north pole and one south pole across the sensor

Figure 5: Definition of Switch Point Separation

Figure 6: Input Signal Definition

## FUNCTIONAL DESCRIPTION

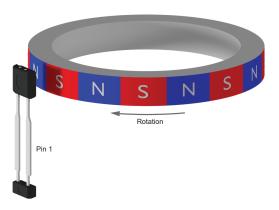

The A19350 sensor IC contains a single-chip GMR circuit that uses spaced elements. These elements are used in differential pairs to provide electrical signals containing information regarding edge position and direction of rotation. The A19350 is intended for use with ring magnet targets as shown in Figure 8. The IC detects the peaks of the magnetic signals and sets dynamic thresholds based on these detected signals.

Figure 7: Package Orientation

Figure 8: Parallel Orientation

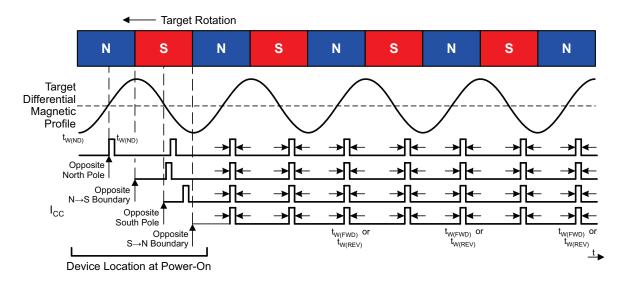

## **Data Protocol Description**

When a target passes in front of the device (opposite the branded face of the package case), the A19350 generates an output pulse for each magnetic pole-pair of the target. Speed information is provided by the output pulse rate, while direction of target rotation is provided by the duration of the output pulses. The sensor IC can sense target movement in both the forward and reverse directions.

Figure 9: Basic Operation

**Forward Rotation.** For the -Fxx variant, when the target is rotating such that a target feature passes from pin 1 to pin 2, this is referred to as forward rotation. This direction of rotation is indicated on the output by a  $t_{W(FWD)}$  pulse width. For the -Rxx variant, forward direction is indicated for target rotation from pin 2 to 1.

**Reverse Rotation.** For the -Fxx variant, when the target is rotating such that a target feature passes from pin 2 to pin 1, this is referred to as reverse rotation. This direction of rotation is indicated on the output by a  $t_{W(REV)}$  pulse width. For the -Rxx variant, reverse direction is indicated for target rotation from pin 1 to 2.

Output edges are triggered by  $B_{DIFF}$  transitions through the switch points. On a crossing, the output pulse of  $I_{CC(HIGH)}$  is present for  $t_{w(FWD)}$  or  $t_{w(REV)}$ .

The IC is always capable of properly detecting input signals up to the defined operating frequency. At frequencies beyond the operational frequencies specifications (refer to Operational Frequency specifications noted on page 5), the  $I_{CC(HIGH)}$  pulse duration will collide with subsequent pulses.

Figure 10: Output Timing Example

## **ASIL Safe State Output Protocol**

The A19350 sensor IC contains diagnostic circuitry that will continuously monitor occurrences of failure defects within the IC. Refer to Figure 11 for the output protocol of the ASIL safe state after an internal defect has been detected. Error Protocol 1 will result from faults due to over frequency conditions from the input signal. Error Protocol 2 will result from hard failures detected within the A19350 such as a regulator and front end fault.

Note: If a fault exists continuously, the device will stay in permanent safe state. Refer to the A19350 Safety Manual for additional details on the ASIL Safe State Output Protocol.

Figure 11: Output Protocol of the -xBx Variant (ASIL Safe State)

## **Calibration and Direction Validation**

When power is applied to the A19350, the built-in algorithm performs an initialization routine. For a short period after power-on, the device calibrates itself and determines the direction of target rotation. For the -xPx variant, the output transmits non-direction pulses during calibration (Figure 12). For the -xBx variant, the output does not transmit any pulses during calibration.

Once the calibration routine is complete, the A19350 will transmit accurate speed and direction information.

Figure 12: Calibration Behavior of the -xPx Variant

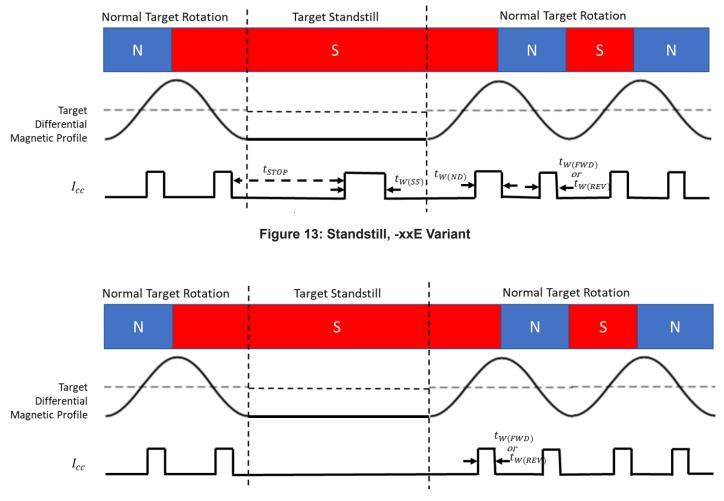

## Standstill

For the -xxE variant, if no output switching is detected for the length of the standstill period, the A19350 will output a standstill pulse. The first speed pulse following a standstill pulse will always be a non-direction pulse. For the -xxM variant, the output does not transmit any pulses during standstill.

In cases of pulse collisions, non-direction pulse will indicate previous pulse was a standstill pulse to allow for differentiating standstill and speed information.

Figure 14: Standstill, -xxM Variant

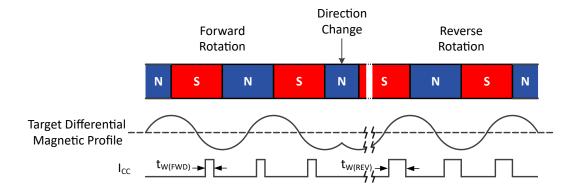

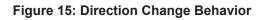

# Direction Changes, Vibrations, and Anomalous Events

During normal operation, the A19350 will be exposed to changes in the direction of target rotation (Figure 15), vibrations of the target (Figure 16), and anomalous events such as sudden air gap changes. These events cause temporary uncertainty in the A19350's internal direction detection algorithm. The -xPx variant may transmit non-direction pulses during vibrations, while the -xBx variant will not transmit any pulses during vibrations.

Figure 16: Vibration Behavior, -xPx, -xBx, and -xxxL variants

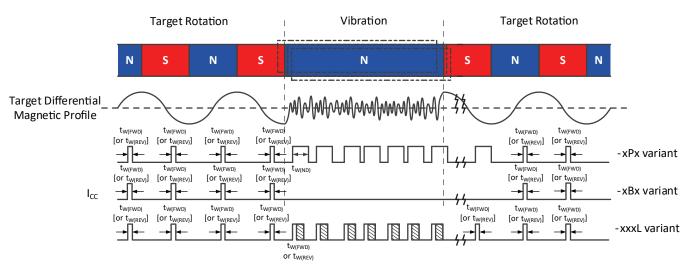

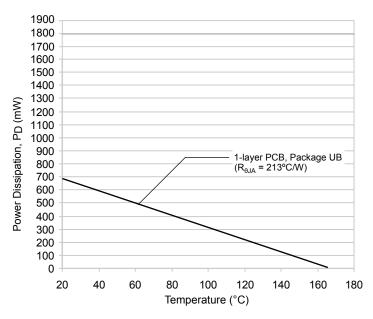

#### POWER DERATING

The device must be operated below the maximum junction temperature of the device,  $T_{J(max)}$ . Under certain combinations of peak conditions, reliable operation may require derating supplied power or improving the heat dissipation properties of the application. This section presents a procedure for correlating factors affecting operating  $T_J$ . (Thermal data is also available on the Allegro MicroSystems website.)

The Package Thermal Resistance,  $R_{\theta JA}$ , is a figure of merit summarizing the ability of the application and the device to dissipate heat from the junction (die), through all paths to the ambient air. Its primary component is the Effective Thermal Conductivity, K, of the printed circuit board, including adjacent devices and traces. Radiation from the die through the device case,  $R_{\theta JC}$ , is a relatively small component of  $R_{\theta JA}$ . Ambient air temperature,  $T_A$ , and air motion are significant external factors, damped by overmolding.

The effect of varying power levels (Power Dissipation,  $P_D$ ) can be estimated. The following formulas represent the fundamental relationships used to estimate  $T_J$ , at  $P_D$ .

$$P_D = V_{IN} \times I_{IN} \tag{1}$$

$\Delta T = P_D \times R_{\theta JA} \tag{2}$

$T_J = T_A + \Delta T \tag{3}$

For example, given common conditions such as:

$T_A{=}~25^{\circ}C,~V_{CC}{=}~12$  V,  $I_{CC}{=}~7.15$  mA, and  $R_{\theta JA}{=}~213^{\circ}C/W,$  then:

$$\begin{split} P_D &= V_{CC} \times I_{CC} = 12 \ V \times \ 7.15 \ mA = 85.8 \ mW \\ & \Delta T = P_D \times R_{\theta JA} = 85.8 \ mW \times 213^{\circ} C/W = 18.3^{\circ} C \\ & T_J = T_A + \Delta T = 25^{\circ} C + 18.3^{\circ} C = 43.3^{\circ} C \end{split}$$

A worst-case estimate,  $P_{D(max)}$ , represents the maximum allowable power level ( $V_{CC(max)}$ ,  $I_{CC(max)}$ ), without exceeding  $T_{J(max)}$ , at a selected  $R_{\theta JA}$  and  $T_A$ .

Example: Reliability for  $V_{CC}$  at  $T_A = 150^{\circ}C$ .

Observe the worst-case ratings for the device, specifically:

$R_{\theta JA} = 213 \,^{\circ}\text{C/W}$  (subject to change),  $T_{J(max)} = 165 \,^{\circ}\text{C}$ ,  $V_{CC(max)} = 24 \,$  V, and  $I_{CC(AVG)} = 14.8 \,$  mA.  $I_{CC(AVG)}$  is computed using  $I_{CC(HIGH)(max)}$  and  $I_{CC(LOW)(max)}$ , with a duty cycle of 84% computed from  $t_{w(REV)(max)}$  on-time and  $t_{w(PRE)(min)}$  off-time (pulse-width protocol).

Calculate the maximum allowable power level,  $P_{D(max)}$ . First, invert equation 3:

$$\Delta T_{max} = T_{J(max)} - T_A = 165^{\circ}C - 150^{\circ}C = 15^{\circ}C$$

This provides the allowable increase to  $T_J$  resulting from internal power dissipation. Then, invert equation 2:

$$P_{D(max)} = \varDelta T_{max} \div R_{\theta JA} = 15^{\circ}C \div 213^{\circ}C/W = 70.4 \ mW$$

Finally, invert equation 1 with respect to voltage:

$$V_{CC(est)} = P_{D(max)} \div I_{CC(max)} = 70.4 \text{ mW} \div 14.8 \text{ mA} = 4.8 \text{ V}$$

The result indicates that, at  $T_A$ , the application and device can dissipate adequate amounts of heat at voltages  $\leq V_{CC(est)}$ .

Compare  $V_{CC(est)}$  to  $V_{CC(max)}$ . If  $V_{CC(est)} \leq V_{CC(max)}$ , then reliable operation between  $V_{CC(est)}$  and  $V_{CC(max)}$  requires enhanced  $R_{\theta JA}$ . If  $V_{CC(est)} \geq V_{CC(max)}$ , then operation between  $V_{CC(est)}$  and  $V_{CC(max)}$  is reliable under these conditions.

#### Power Derating Curve

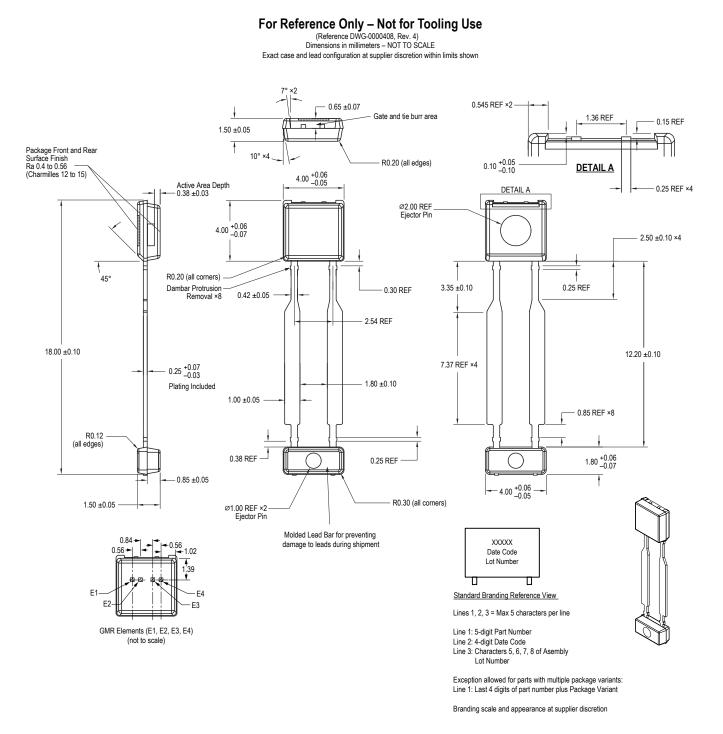

#### PACKAGE OUTLINE DRAWING

Figure 17: Package UB, 2-Pin SIP

#### **Revision History**

| Number              | Date                                                                                                                                   | Description                                                                                                                                                            |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| -                   | November 16, 2018                                                                                                                      | Initial release                                                                                                                                                        |  |  |

| 1                   | March 25, 2021                                                                                                                         | Minor editorial updates (page 1)                                                                                                                                       |  |  |

| 2                   | April 11, 2022                                                                                                                         | Updated package drawing (page 13)                                                                                                                                      |  |  |

|                     | August 10, 2022                                                                                                                        | Updated Operating Characteristics and footnote 9 (page 5).                                                                                                             |  |  |

| 3 February 23, 2023 |                                                                                                                                        | Updated Complete Part Number Format schematic (page 2), Operating Characteristics (page 4), Figure 12 (page 9), Standstill section (page 10), and Figure 16 (page 11). |  |  |

| 4                   | December 15, 2023 Updated available device configurations (page 2), Operating Characteristics (page 6), and figures 15 and 16 (page 12 |                                                                                                                                                                        |  |  |

Copyright 2023, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website:

www.allegromicro.com

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Allegro MicroSystems:

A19350LUBATN-FBE-A A19350LUBATN-RBE-A A19350LUBBTN-RBE