### A1335

### Precision Hall-Effect Angle Sensor IC with I<sup>2</sup>C, SPI, and SENT Interfaces

### FEATURES AND BENEFITS

- 360° contactless high-resolution angle position sensor

- Circular vertical Hall (CVH) technology

- Available with either a single die or dual independent die housed within a single package

- Digital output format selectable among serial port interface (SPI), inter-integrated circuit (I<sup>2</sup>C), and singleedge nibble transmission (SENT)

- SENT output is SAEJ2716 JAN2010-compliant, with Allegro-proprietary, enhanced, programmable features

- Customer-programmable SENT tick times, ranging from 0.5 to 7.9 µs

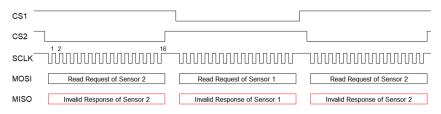

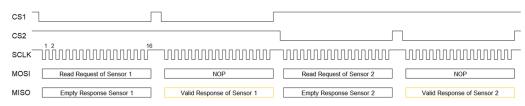

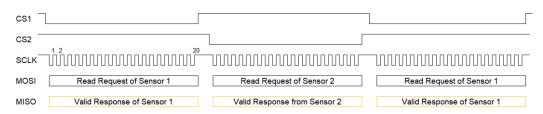

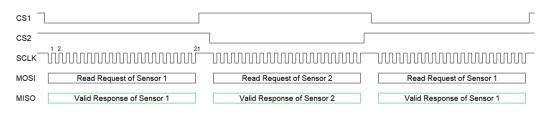

- SPI interface allows use of multiple independent sensor ICs for applications requiring redundancy

- Refresh rate: 32 µs, 12-bit resolution

- Programmable via Manchester encoding on the VCC • line, reducing external wiring

- Automotive temperature range: -40°C to 150°C

- AEC-Q100 automotive qualified

Continued on the next page ....

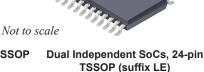

# PACKAGES:

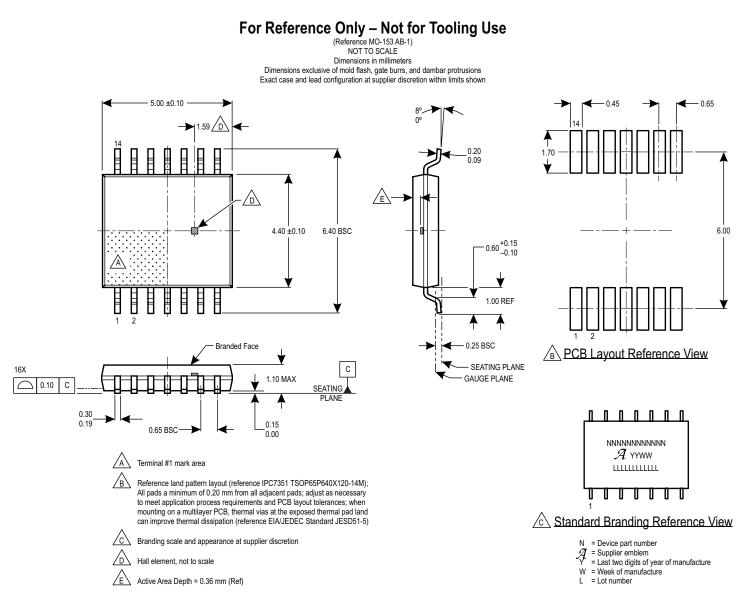

Single SoC, 14-pin TSSOP (suffix LE)

### DESCRIPTION

The A1335 is a 360° contactless high-resolution programmable magnetic angle position sensor IC. It is designed for digital systems and is capable of communicating via an I<sup>2</sup>C, SPI, or SENT interface.

This system-on-chip (SoC) architecture includes a front end based on circular vertical Hall (CVH) technology, programmable microprocessor-based signal processing, and an interface capable of supporting I<sup>2</sup>C, SPI, and SENT. In addition to providing full-turn angular measurement, the A1335 also provides scaling for angle measurement applications of less than 360°. It includes on-chip EEPROM technology, capable of supporting up to 100 read/write cycles, for flexible programming of calibration parameters.

Digital signal processing functions, including temperature compensation and gain/offset trim, as well as advanced output linearization algorithms, provide an extremely accurate and linear output for both end-of-shaft applications and off-axis applications.

The A1335 is ideal for automotive applications requiring highspeed 360° angle measurements, such as: electronic power steering (EPS), transmission, torsion bar, and other systems that require accurate measurement of angles. The A1335 linearization schemes were designed with challenging off-axis applications in mind.

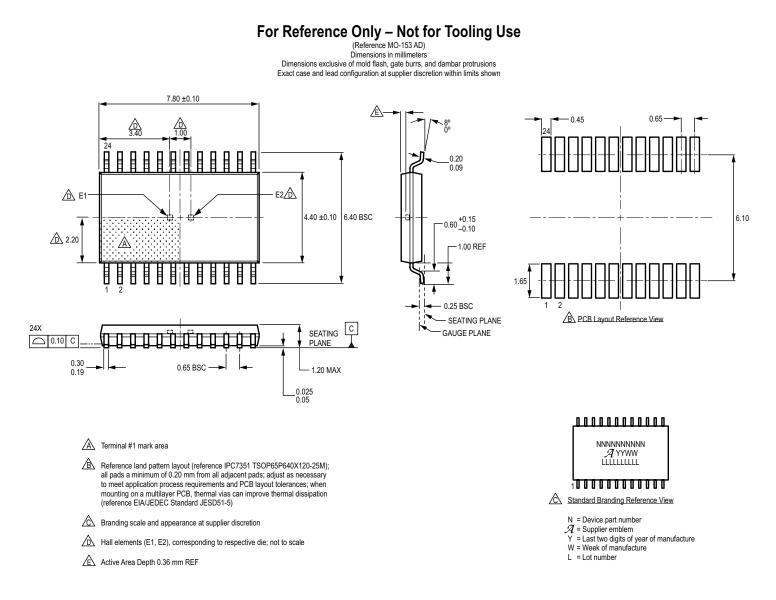

The A1335 is available as a single die in a 14-pin TSSOP, or dual die in a 24-pin TSSOP. Both packages are lead (Pb) free with 100% matte tin leadframe plating.

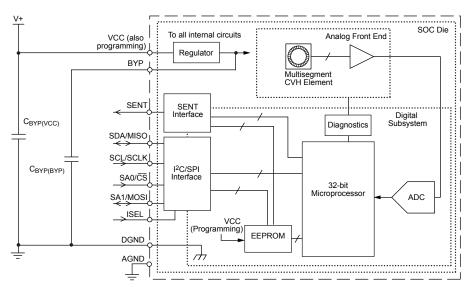

**Functional Block Diagram**

Industry-leading linearization enables off-axis (side-shaft) operation

#### FEATURES AND BENEFITS (continued)

- Two types of linearization algorithms offered: harmonic linearization and segmented linearization

Enables off-axis operation

- Programmable range—can scale 22.5° to full-scale digital output

- · Microprocessor-based output linearization

**SELECTION GUIDE**

## EEPROM with error correction control (ECC) for trimming calibration 1 mm-thin (TSSOP) package

• Improved air gap performance, based on continuous background calibration

| Part Number   | Part Number System Die Package |              | Packing <sup>[1]</sup>      |

|---------------|--------------------------------|--------------|-----------------------------|

| A1335LLETR-1  | Single                         | 14-pin TSSOP | 4000 pieces per 13-in. reel |

| A1335LLETR-DE | )-T Dual                       | 24-pin TSSOP | 4000 pieces per 13-in. reel |

[1] Contact Allegro for additional packing options

#### ABSOLUTE MAXIMUM RATINGS

| Characteristic                | Symbol               | Notes               | Rating      | Unit |

|-------------------------------|----------------------|---------------------|-------------|------|

| Forward Supply Voltage        | V <sub>CC</sub>      |                     | 24          | V    |

| Reverse Supply Voltage        | V <sub>RCC</sub>     |                     | -18         | V    |

| All Other Pins                | V <sub>IN</sub>      |                     | -0.5 to 5.5 | V    |

| Operating Ambient Temperature | T <sub>A</sub>       | L temperature range | -40 to 150  | °C   |

| Maximum Junction Temperature  | T <sub>J</sub> (max) |                     | 165         | °C   |

| Storage Temperature           | T <sub>stg</sub>     |                     | -65 to 170  | °C   |

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Symbol           | Test Conditions <sup>[1]</sup> | Value | Unit |

|----------------------------|------------------|--------------------------------|-------|------|

| Package Thermal Resistance | R <sub>θJA</sub> | LE-14 package                  | 82    | °C/W |

|                            |                  | LE-24 package                  | 117   | °C/W |

[1] Additional thermal information available on the Allegro website.

#### **Table of Contents**

| Features and Benefits              |     |

|------------------------------------|-----|

| Description<br>Packages            |     |

| Functional Block Diagram           |     |

| Selection Guide                    | . 2 |

| Absolute Maximum Ratings           | . 2 |

| Thermal Characteristics            | . 2 |

| Pinout Diagrams and Terminal Lists | . 3 |

| Operating Characteristics          |     |

| Functional Description             |     |

| Overview                           |     |

| Operation                          | . 7 |

| Diagnostic Features1               |     |

| Programming Mode                   | 11  |

| Manchester Serial Interface 1      |     |

|                                    |     |

| Entering Manchester Communication Mode           | 12 |

|--------------------------------------------------|----|

| Transaction Types                                | 12 |

| Writing to EEPROM                                | 12 |

| Manchester Interface Reference                   | 13 |

| SENT Output Mode                                 | 14 |

| Application Information                          | 16 |

| Serial Interface Description                     | 16 |

| Magnetic Target Requirements                     | 17 |

| Calculating Target Zero Degree Angle             |    |

| Bypass Pin Usage                                 |    |

| Effect of Orientation on Signal                  |    |

| Linearization                                    |    |

| Typical Performance Characteristics              | 25 |

| Package Outline Drawings                         |    |

| APPENDIX A: SPI Interface Error Flag Description |    |

|                                                  |    |

DGND 1 BYP 2

DGND 3 NC 4 VCC 5 NC 6

AGND 7

DGND 1 1

BYP\_1 2

VCC 1 5 ISEL 2 6

SENT\_2 7 SDA\_2/MISO\_2 8 SCL\_2/SCLK\_2 9

SA1\_2/MOSI\_2 10

SA0\_2/CS\_2 11 DGND\_2 12

AGND\_1 3 NC 4

### **Precision Hall-Effect Angle Sensor IC** with I<sup>2</sup>C, SPI, and SENT Interfaces

|                                                   |            |                                                                                     | D: No. 141              | Pin Nu   | umber |                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------|------------|-------------------------------------------------------------------------------------|-------------------------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D 1                                               | 0          | 14 DGND                                                                             | Pin Name <sup>[1]</sup> | LE-14    | LE-24 | Function                                                                                                                                                                                                                                                                                                                                                          |

| Р 2                                               | •          | 13 SA0/CS                                                                           | VCC_1                   | 5        | 5     | Device power supply and input for EEPROM writing pulses. Used to enter/exit                                                                                                                                                                                                                                                                                       |

| D 3                                               |            | 12 SA1/MOSI                                                                         | VCC_2                   | -        | 17    | Manchester serial communication mode; serves as programming data input once mode has been entered.                                                                                                                                                                                                                                                                |

| C 4                                               |            | 11 SCL/SCLK                                                                         | AGND_1                  | 7        | 3     | Device evolve ground terminal                                                                                                                                                                                                                                                                                                                                     |

| C 5                                               |            | 10 SDA/MISO                                                                         | AGND_2                  | -        | 15    | Device analog ground terminal.                                                                                                                                                                                                                                                                                                                                    |

| C 6<br>D 7                                        |            | 9 SENT<br>8 ISEL                                                                    | BYP_1                   | 2        | 2     | Internal bypass node, connect with bypass capacitor to DGND (die 1).                                                                                                                                                                                                                                                                                              |

|                                                   |            |                                                                                     | BYP_2                   | -        | 14    | Internal bypass node, connect with bypass capacitor to DGND (die 2).                                                                                                                                                                                                                                                                                              |

| I E                                               | -14 Packa  | 00                                                                                  | DGND_1                  | 1, 3, 14 | 1, 24 |                                                                                                                                                                                                                                                                                                                                                                   |

|                                                   |            | -                                                                                   | DGND_2                  | -        | 12,13 | Device digital ground terminal.                                                                                                                                                                                                                                                                                                                                   |

| (S                                                | Single SoC | ;)                                                                                  | ISEL_1                  | 8        | 18    | Selects between I <sup>2</sup> C operation (set to logic low)<br>or SPI operation (set to logic high) (for SENT/Manchester operation set low) (die 1).                                                                                                                                                                                                            |

|                                                   |            | <b></b>                                                                             | ISEL_2                  | -        | 6     | Selects between I <sup>2</sup> C operation (set to logic low)<br>or SPI operation (set to logic high) (for SENT/Manchester operation set low) (die 2).                                                                                                                                                                                                            |

|                                                   | 0          | 24 DGND_1                                                                           | NC                      | 4, 6     | 4, 16 | Not Connected; connect to GND for optimal ESD performance.                                                                                                                                                                                                                                                                                                        |

| P_1 2<br>p_1 3<br>NC 4<br>p_1 5<br>p_1 5<br>p_2 6 |            | 23 SA0_1/CS_1<br>22 SA1_1/MOSI_1<br>21 SCL_1/SCLK_1<br>20 SDA_1/MISO_1<br>19 SENT_1 | SA0_1/CS_1              | 13       | 23    | <ul> <li>I<sup>2</sup>C: SA0 digital input. Sets peripheral address bit 0 (LSB) <sup>[2]</sup>; tie to BYP for 1, tie to DGND for 0.</li> <li>SPI: Chip-select input, active low (die 1).</li> <li>Manchester: LSB of the ID value for die 1. tie to BYP for 1, to DGND for 0. Must be in I<sup>2</sup>C operation (ISEL set to a logic low).</li> </ul>          |

| _2 7<br>_2 7<br>_2 8<br>_2 9<br>_2 9              |            | 18 ISEL_1<br>17 VCC_2<br>16 NC<br>15 AGND_2                                         | SA0_2/CS_2              | _        | 11    | <ul> <li>I<sup>2</sup>C: SA0 digital input. Sets peripheral address bit 0 (LSB) <sup>[2]</sup>; tie to BYP for 1, tie to DGND for 0.</li> <li>SPI: Chip-select input, active low (die 2).</li> <li>Manchester: LSB of the ID value for die 2. tie to BYP for 1, to DGND for 0. Must be in I<sup>2</sup>C operation (ISEL set to a logic low).</li> </ul>          |

| 2 <u>11</u><br>2 <u>12</u>                        | -24 Packa  | 14 BYP_2<br>13 DGND_2<br><b>QE</b>                                                  | SA1_1/<br>MOSI_1        | 12       | 22    | <ul> <li>I<sup>2</sup>C: SA1 digital input: Sets peripheral address bit 1 (LSB) <sup>[2]</sup>; tie to BYP for 1, tie to DGND for 0.</li> <li>SPI: Controller output/slave input terminal (die 1).</li> <li>Manchester: MSB of the ID value for Die 1. tie to BYP for 1, to DGND for 0. Must be in I<sup>2</sup>C operation (ISEL set to a logic low).</li> </ul> |

|                                                   | Dual SoC   | •                                                                                   | SA1_2/<br>MOSI_2        | _        | 10    | <ul> <li>I<sup>2</sup>C: SA1 digital input: Sets peripheral address bit 1 (LSB) I<sup>2</sup>; tie to BYP for 1, tie to DGND for 0.</li> <li>SPI: Controller output/slave input terminal (die 2).</li> <li>Manchester: MSB of the ID value for Die 2. tie to BYP for 1, to DGND for 0. Must be in I<sup>2</sup>C operation (ISEL set to a logic low).</li> </ul>  |

|                                                   |            |                                                                                     | SCL_1/<br>SCLK_1        | 11       | 21    | Digital input: Serial clock (I <sup>2</sup> C: SCL, SPI: SCLK); open drain, pull up externally to 3.3 V (die 1).                                                                                                                                                                                                                                                  |

|                                                   |            |                                                                                     | SCL_2/<br>SCLK_2        | -        | 9     | Digital input: Serial clock (I <sup>2</sup> C: SCL, SPI: SCLK); open drain, pull up externally to 3.3 V (die 2).                                                                                                                                                                                                                                                  |

|                                                   |            |                                                                                     | SDA_1/<br>MISO_1        | 10       | 20    | I <sup>2</sup> C: Digital data terminal: digital output of evaluated target angle, also<br>programming data input; open drain, pull up externally to 3.3 V (die 1).<br>SPI: Master Input/Slave Output terminal (die 1).                                                                                                                                           |

|                                                   |            |                                                                                     | SDA_2/<br>MISO_2        | _        | 8     | <sup>12</sup> C: Digital data terminal: digital output of evaluated target angle, also<br>programming data input; open drain, pull up externally to 3.3 V (die 2).<br>SPI: Master Input/Slave Output terminal (die 2).                                                                                                                                            |

|                                                   |            |                                                                                     | SENT_1                  | 9        | 19    | SENT transmission output terminal (die 1); Manchester output in Manchester mode; open drain, pull-up to external supply.                                                                                                                                                                                                                                          |

### PINOUT DIAGRAMS AND TERMINAL LIST

**Terminal List Table**

7

SENT\_2

<sup>[1]</sup> The number following the underscore refers to the die number in a dual SOC variant <sup>[2]</sup> For additional information regarding the INTF register, I2CM field, refer to the Programming Reference addendum, EEPROM Description and Programming section.

mode; open drain, pull-up to external supply.

SENT transmission output terminal (die 2); Manchester output in Manchester

### OPERATING CHARACTERISTICS: Valid throughout full operating voltage and ambient temperature ranges,

unless otherwise specified

| Characteristic                                            | Symbol                     | Test Conditions                                              | Min. | Typ. [1] | Max. | Unit <sup>[2]</sup> |

|-----------------------------------------------------------|----------------------------|--------------------------------------------------------------|------|----------|------|---------------------|

| ELECTRICAL CHARACTERISTICS                                | 3                          |                                                              |      |          |      |                     |

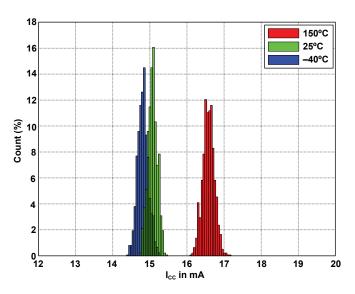

| Supply Voltage                                            | V <sub>CC</sub>            |                                                              | 4.5  | 5        | 5.5  | V                   |

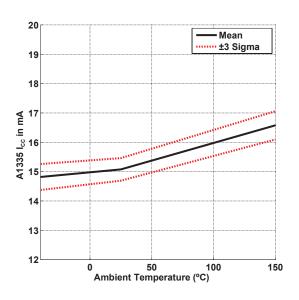

| Supply Current                                            | I <sub>CC</sub>            |                                                              | _    | 15       | 20   | mA                  |

| VCC Low Flag Threshold                                    | V <sub>CCLOW(TH)</sub>     |                                                              | 4.4  | 4.55     | 4.75 | V                   |

| Supply Zener Clamp Voltage                                | V <sub>ZSUP</sub>          | $I_{ZCC} = I_{CC} + 3 \text{ mA}, T_A = 25^{\circ}\text{C}$  | 26.5 | -        | _    | V                   |

| Reverse Battery Voltage                                   | V <sub>RCC</sub>           | $I_{RCC} = -3 \text{ mA}, T_A = 25^{\circ}C$                 | _    | -        | -18  | V                   |

| Power-On Time [3][4]                                      | t <sub>PO</sub>            | T <sub>A</sub> = 25°C                                        | 2    | -        | 40   | ms                  |

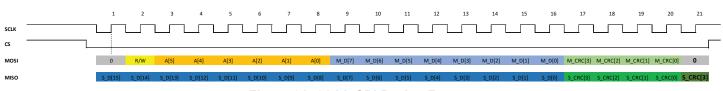

| SPI INTERFACE SPECIFICATION                               | S <sup>[5]</sup>           |                                                              |      |          |      |                     |

| Digital Input High Voltage [3]                            | V <sub>IH</sub>            | MOSI, SCLK, CS pins                                          | 2.8  | _        | 3.63 | V                   |

| Digital Input Low Voltage [3]                             | V <sub>IL</sub>            | MOSI, SCLK, $\overline{CS}$ pins                             | _    | _        | 0.5  | V                   |

| SPI Output High Voltage                                   | V <sub>OH</sub>            | MISO pins, T <sub>A</sub> = 25°C                             | 2.93 | 3.3      | 3.69 | V                   |

| SPI Output Low Voltage                                    | V <sub>OL</sub>            | MISO pins                                                    | _    | 0.3      | _    | V                   |

| SPI Clock Frequency [3]                                   | f <sub>SCLK</sub>          | MISO pins, C <sub>L</sub> = 50 pF                            | 0.1  | _        | 10   | MHz                 |

| SPI Clock Duty Cycle [3]                                  | D <sub>fSCLK</sub>         |                                                              | 40   | _        | 60   | %                   |

| Chip Select to First SCLK Edge [3]                        | t <sub>cs</sub>            | Time from CS going low to SCLK falling edge                  | 50   | -        | _    | ns                  |

| Chip Select Idle Time [3]                                 | t <sub>CS_IDLE</sub>       | Time $\overline{CS}$ must be high between SPI message frames | 200  | _        | _    | ns                  |

| Data Output Valid Time [3]                                | t <sub>DAV</sub>           | Data output valid after SCLK falling edge                    | _    | 45       | _    | ns                  |

| MOSI Setup Time [3]                                       | t <sub>SU</sub>            | Input setup time before SCLK rising edge                     | 10   | _        | _    | ns                  |

| MOSI Hold Time <sup>[3]</sup>                             | t <sub>HD</sub>            | Input hold time after SCLK rising edge                       | 50   | _        | _    | ns                  |

| SCLK to CS Hold Time [3]                                  | t <sub>CHD</sub>           | Hold SCLK high time before CS rising edge                    | 5    | _        | _    | ns                  |

| Load Capacitance [3]                                      | CL                         | Loading on digital output (MISO) pin                         | _    | _        | 50   | pF                  |

| I <sup>2</sup> C INTERFACE SPECIFICATIONS                 | 6 (V <sub>PU</sub> = 3.3 V | on SDA and SCL pins)                                         |      |          |      |                     |

| Bus Free Time Between Stop<br>and Start [3]               | t <sub>BUF</sub>           |                                                              | 1.3  | _        | _    | μs                  |

| Hold Time Start Condition [3]                             | t <sub>HD(STA)</sub>       |                                                              | 0.6  | _        | _    | μs                  |

| Setup Time for Repeated Start<br>Condition <sup>[3]</sup> | t <sub>SU(STA)</sub>       |                                                              | 0.6  | -        | _    | μs                  |

| SCL Low Time <sup>[3]</sup>                               | t <sub>LOW</sub>           |                                                              | 1.3  | _        | _    | μs                  |

| SCL High Time <sup>[3]</sup>                              | t <sub>HIGH</sub>          |                                                              | 0.6  | _        | _    | μs                  |

| Data Setup Time [3]                                       | t <sub>SU(DAT)</sub>       |                                                              | 100  | _        | _    | ns                  |

| Data Hold Time <sup>[3]</sup>                             | t <sub>HD(DAT)</sub>       |                                                              | 0    | _        | 900  | ns                  |

| Setup Time for Stop Condition [3]                         | t <sub>SU(STO)</sub>       |                                                              | 0.6  | -        | _    | μs                  |

| Logic Input Low Level (SDA and SCL pins) <sup>[6]</sup>   | V <sub>IL(I2C)</sub>       |                                                              | _    | _        | 0.9  | V                   |

| Logic Input High Level (SDA and SCL pins) $^{[6]}$        | V <sub>IH(I2C)</sub>       |                                                              | 2.1  | _        | 3.63 | V                   |

Continued on the next page ...

### **OPERATING CHARACTERISTICS** (continued): Valid throughout full operating voltage and ambient temperature ranges, unless otherwise specified

| Characteristic                                          | Symbol                   | Test Conditions                                                                                         | Min.             | Typ. [1] | Max. | Unit <sup>[2]</sup> |

|---------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------|------------------|----------|------|---------------------|

| I <sup>2</sup> C INTERFACE SPECIFICATIONS               | (V <sub>PU</sub> = 3.3 V | on SDA and SCL pins) (continued)                                                                        |                  |          |      |                     |

| Logic Input Current [3]                                 | I <sub>IN</sub>          | $V_{IN} = 0 V$ to $V_{CC}$                                                                              | -1               | -        | 1    | μA                  |

| Output Voltage (SDA pin)                                | V <sub>OL(I2C)</sub>     | $R_{PU}$ = 1 kΩ, $C_B$ = 100 pF, $T_A$ = 25°C                                                           | -                | -        | 0.6  | V                   |

| Logic Input Rise Time (SDA and SCL pins) <sup>[3]</sup> | t <sub>r(IN)</sub>       |                                                                                                         | -                | _        | 300  | ns                  |

| Logic Input Fall Time (SDA and SCL pins) [3]            | t <sub>f(IN)</sub>       |                                                                                                         | -                | _        | 300  | ns                  |

| SDA Output Rise Time [3]                                | t <sub>r(OUT)</sub>      | R <sub>PU</sub> = 1 kΩ, C <sub>B</sub> = 100 pF                                                         | -                | _        | 300  | ns                  |

| SDA Output Fall Time [3]                                | t <sub>F(OUT)</sub>      | R <sub>PU</sub> = 1 kΩ, C <sub>B</sub> = 100 pF                                                         | -                | -        | 300  | ns                  |

| SCL Clock Frequency [6]                                 | f <sub>CLK</sub>         |                                                                                                         | -                | -        | 400  | kHz                 |

| SDA and SCL Bus Pull-Up Resistor                        | R <sub>PU</sub>          |                                                                                                         | -                | 1        | _    | kΩ                  |

| Total Capacitive Load on SDA Line [3]                   | CB                       |                                                                                                         | -                | -        | 100  | pF                  |

| Pull-Up Voltage <sup>[3]</sup>                          | V <sub>PU</sub>          | R <sub>PU</sub> = 1 kΩ, C <sub>B</sub> = 100 pF                                                         | 2.97             | 3.3      | 3.63 | V                   |

| SENT Interface Specifications [3]                       |                          |                                                                                                         |                  |          |      |                     |

| SENT Message Duration                                   | t <sub>SENT</sub>        | Tick time = 3 μs                                                                                        | -                | -        | 1    | ms                  |

| Minimum Programmable SENT<br>Message Duration           | t <sub>SENTMIN</sub>     | Tick time = 0.5 $\mu$ s, 3 data nibbles, SCN, and CRC, nibble length = 27 ticks                         | -                | 96       | -    | μs                  |

|                                                         | V <sub>SENT(L)</sub>     | $5 \text{ k}\Omega \leq \text{R}_{\text{pullup}} \leq 50 \text{ k}\Omega$                               | -                | -        | 0.10 | V                   |

| SENT Output Signal                                      | V                        | Minimum R <sub>pullup</sub> = 5 kΩ                                                                      | $0.9 \times V_S$ | -        | _    | V                   |

|                                                         | V <sub>SENT(H)</sub>     | Maximum $R_{pullup} = 50 \text{ k}\Omega$                                                               | $0.7 \times V_S$ | -        | -    | V                   |

| SENT Trigger Signal                                     | V <sub>SENTtrig(L)</sub> |                                                                                                         | -                | _        | 1.4  | V                   |

|                                                         | V <sub>SENTtrig(H)</sub> |                                                                                                         | 2.8              | -        | _    | V                   |

| Minimum Time Frame for SENT<br>Trigger Signal           | T <sub>trig(MIN)</sub>   |                                                                                                         | 2                | -        | -    | μs                  |

| Triggered Delay Time                                    | t <sub>dSENT</sub>       | From end of trigger pulse to beginning of SENT<br>message frame.<br>TSENT (SENT_MODE 3 and SENT_MODE 4) | -                | 7        | _    | tick                |

| Maximum Sink Current                                    | I <sub>LIMIT</sub>       | Output FET on, T <sub>A</sub> = 25°C                                                                    | -                | 30       | _    | mA                  |

| Magnetic Characteristics                                |                          |                                                                                                         |                  |          |      |                     |

| Magnetic Field [7]                                      | В                        | Range of input field                                                                                    | _                | _        | 1500 | G                   |

Continued on the next page ...

### **OPERATING CHARACTERISTICS** (continued): Valid throughout full operating voltage and ambient temperature ranges, unless otherwise specified

| Characteristic                            | Symbol                          | Test Conditions                                                                                                      | Min.     | Typ. [1] | Max. | Unit <sup>[2]</sup> |

|-------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------|----------|----------|------|---------------------|

| ANGLE CHARACTERISTICS                     |                                 |                                                                                                                      | <u>`</u> |          |      |                     |

| Output <sup>[8]</sup>                     | RES <sub>ANGLE</sub>            |                                                                                                                      | _        | 12       | _    | bit                 |

| Effective resolution <sup>[9]</sup>       |                                 | B = 300 G, T <sub>A</sub> = 25°C, ORATE = 0                                                                          | _        | 10.8     | _    | bits                |

|                                           |                                 | B ≥ 700 G, T <sub>A</sub> = 25°C, ORATE = 0                                                                          | _        | 12       | -    | bits                |

| Angle Refresh Rate [10]                   | t <sub>ANG</sub>                | ORATE = 0                                                                                                            | -        | 32       | _    | μs                  |

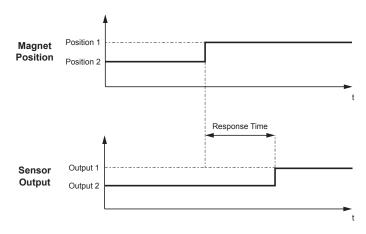

| Response Time [11]                        | t <sub>RESPONSE</sub>           | All linearization and computations disabled, see Figure 1                                                            | _        | 60       | _    | μs                  |

|                                           |                                 | $T_A = 25^{\circ}C$ , ideal magnet alignment, B = 300 G, target rpm = 0, no linearization                            | _        | ±0.5     | _    | degrees             |

| An ele Free [12]                          | 500                             | $T_A = 25^{\circ}C$ , ideal magnet alignment, B = 900 G, target rpm = 0, no linearization                            | _        | ±0.2     | _    | degrees             |

| Angle Error <sup>[12]</sup>               | ERR <sub>ANG</sub>              | $T_A = 150$ °C, ideal magnet alignment, B = 300 G, target rpm = 0, no linearization                                  | -1.3     | -        | +1.3 | degrees             |

|                                           |                                 | $T_A = 150$ °C, ideal magnet alignment, B = 900 G, target rpm = 0, no linearization                                  | _        | ±0.3     | _    | degrees             |

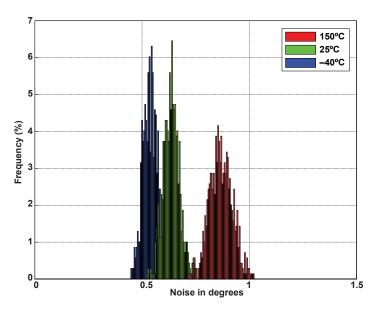

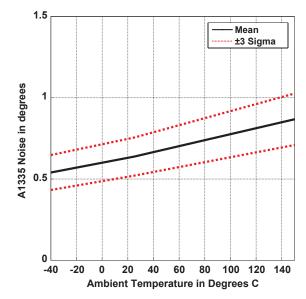

| America Marica [12][12]                   | N                               | T <sub>A</sub> = 25°C, B = 300 G, no internal filtering,<br>3 sigma value                                            | _        | 0.6      | _    | degrees             |

| Angle Noise <sup>[12][13]</sup>           | N <sub>ANG</sub>                | $T_A = 150$ °C, B = 300 G, no internal filtering,<br>3 sigma value                                                   | _        | 0.8      | _    | degrees             |

| Turning Duiff                             |                                 | T <sub>A</sub> = 150°C, B = 300 G                                                                                    | -1.4     |          | 1.4  | degrees             |

| Temperature Drift                         | ANGLEDRIFT                      | T <sub>A</sub> = -40°C, B = 300 G                                                                                    | _        | ±1.2     | _    | degrees             |

| Angle Drift Over Lifetime <sup>[14]</sup> | ANGLE <sub>DRIFT-</sub><br>LIFE | B = 300 G, typical maximum drift observed of<br>peak angle error following AEC-Q100 Grade 0<br>qualification testing | _        | ±0.7     | _    | degrees             |

<sup>[1]</sup> Typical data is at  $T_A = 25^{\circ}$ C and  $V_{CC} = 5$  V and it is for design information only.

$^{[2]}$  1 G (gauss) = 0.1 mT (millitesla).

[3] Parameters for this characteristic are determined by design. They are not measured at final test.

<sup>[4]</sup> Power-on time may be reduced by disabling CVH self-test at power-on.

<sup>[5]</sup> During the power-on phase, the A1335 SPI transactions are not guaranteed.

<sup>[6]</sup> Parameter is tested at wafer probe only.

[7] The A1335 operates in Magnetic fields lower than 300 G, but with reduced accuracy and resolution. CVH self-test operation is not guaranteed at field levels above 300 G.

[8] RES<sub>ANGLE</sub> represents the number of bits of data available for reading from the die registers.

<sup>[9]</sup> Effective Resolution is calculated using the formula below:

$$\log_2(360) - \log_2\left(\frac{1}{n}\sum_{i=1}^n \sigma_i\right)$$

where  $\sigma$  is the Standard Deviation based on thirty measurements taken at each of the 32 angular positions, I = 11.25, 22.5, ... 360.

- [10] The rate at which a new angle reading is ready. This value varies with the ORATE selection.

- [11] This value assumes no post-processing and is the response time to read the magnetic position with no further computations. Actual response time is dependent on EEPROM settings. Settings related to filter design, signal path computations, and linearization will increase the response time.

- [12] Error and noise values are with no further signal processing. Angle Error can be corrected with linearization algorithm, and Angle Noise can be reduced with internal filtering and slower Angle Refresh Rate value.

- <sup>[13]</sup> 3 sigma value at 300 G. Operation with a larger magnetic field results in improved noise performance. For 600 G operation, noise reduced by 40-50% vs. 300 G.

- [14] Maximum observed drift in angle error parameter following AEC-Q100 Grade 0 stress was 1.7 degrees following temperature cycle stress.

#### **Definition of Response Time**

### FUNCTIONAL DESCRIPTION

### Overview

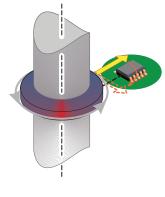

The A1335 incorporates a Hall sensor IC that measures the direction of the magnetic field vector through 360° in the X-Y plane (parallel to the branded face of the device). The A1335 computes the angle based on the actual physical reading, as well as any internal parameters that have been set by the user. The end user can configure the output dynamic range, output scaling, and filtering.

This device is an advanced, programmable internal microprocessor-driven system-on-chip (SoC). It includes a Circular vertical Hall (CVH) analog front end, a high-speed sampling analog-todigital converter, digital filtering, a 32-bit custom microprocessor, a digital control interface capable of supporting I<sup>2</sup>C, SPI and SENT, and digital output of processed angle data.

Advanced linearization, offset, and gain adjustment options are available in the A1335. These options can be configured in onboard EEPROM providing a wide range of sensing solutions in the same device. Device performance can be optimized by enabling individual functions or disabling them in EEPROM to minimize latency.

### Operation

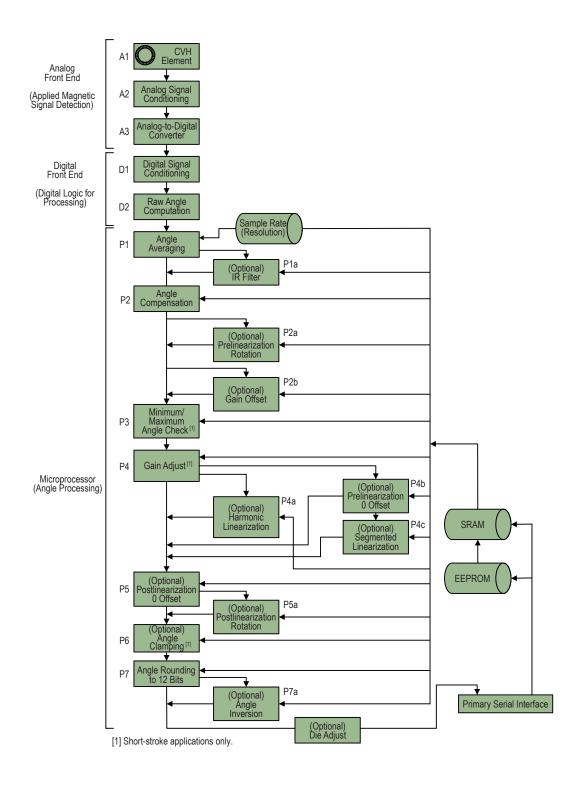

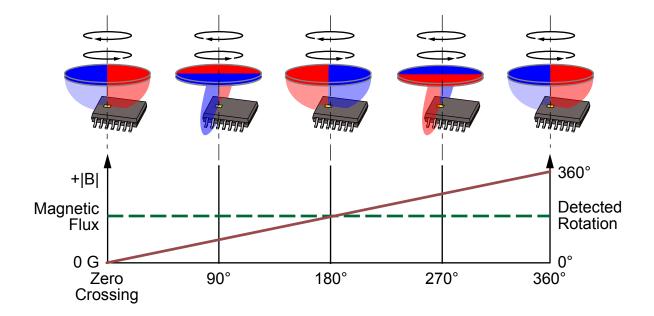

The device is designed to acquire angular position data by sampling a rotating bipolar magnetic target using a multisegmented circular vertical Hall-effect (CVH) detector. The analog output is processed, then digitized and compensated before being loaded into the output register. For a depiction of the signal process flow described here, refer to Figure 1.

• *Analog Front End.* In this stage, the applied magnetic signal is detected and digitized for more-advanced processing.

A1 CVH Element. The CVH is the actual magnetic-sensing element that measures the direction of the applied magnetic vector.

**A2 Analog Signal Conditioning.** The signal acquired by the CVH is sampled.

A3 Analog-to-Digital Converter. The analog signal is digitized and handed off to the digital-front-end stage.

• *Digital Front End.* In this preprocessing stage, the digitized signal is conditioned for analysis.

**D1 Digital Signal Conditioning**. The digitized signal is decimated and bandpass filtered.

**D2 Raw Angle Computation**. For each sample, the raw angle value is calculated.

• *Microprocessor.* The preprocess signal is subjected to various user-selected computations. The type and selection of computations used involves a trade-off between precision and increased response time in producing the final output.

**P1 Angle Averaging**. The raw angle data is received in a periodic stream, and several samples are accumulated and averaged based on the user-selected output rate. This feature increases the effective resolution of the system. The amount of averaging is determined by the user-programmable output rate (ORATE) field. The user can configure the quantity of averaged samples by powers of two to determine the *refresh rate*, the rate at which successive averaged angle values are fed into the post-processing stages. The available rates are set as shown in Table 1.

| Table 1. Refresh Rates of Averaged Dampies |                                 |                      |  |  |  |  |  |

|--------------------------------------------|---------------------------------|----------------------|--|--|--|--|--|

| ORATE<br>[2:0]                             | Quantity of Samples<br>Averaged | Refresh Rate<br>(µs) |  |  |  |  |  |

| 000                                        | 1                               | 32                   |  |  |  |  |  |

| 001                                        | 2                               | 64                   |  |  |  |  |  |

| 010                                        | 4                               | 128                  |  |  |  |  |  |

| 011                                        | 8                               | 256                  |  |  |  |  |  |

| 100                                        | 16                              | 512                  |  |  |  |  |  |

| 101                                        | 32                              | 1024                 |  |  |  |  |  |

| 110                                        | 64                              | 2048                 |  |  |  |  |  |

| 111                                        | 128                             | 4096                 |  |  |  |  |  |

Table 1: Refresh Rates of Averaged Samples

**P1a IIR Filter (Optional).** The optional infinite impulse response (IIR) filter can provide more-advanced multiorder filtering of the input signal. Filter coefficients can be user-programmed, and the filter (FI) bit can be programmed by the user to enable or disable this feature.

**P2 Angle Compensation.** The A1335 is capable of compensating for drift in angle readings that result from changes in the device temperature through the operating ambient temperature range. The device comes from the factory preprogrammed with coefficient settings to allow compensation of linear shifts of angle with temperature.

**P2a Prelinearization Rotation (Optional, but required if linearization is used).** The linearization algorithms require input functions that are both continuous and monotonically increasing. The LR bit sets which relative direction of target rotation results in an increasing angle value. The bit must be set such that the input to the linearization algorithm is increasing.

### A1335

# Precision Hall-Effect Angle Sensor IC with I<sup>2</sup>C, SPI, and SENT Interfaces

**P2b Gain Offset (Optional).** Allows zeroing out of the angle prior to applying gain. Set via the GAIN\_OFFSET field.

Angle = Angle – GAIN\_OFFSET.

**P3 Minimum/Maximum Angle Check (Short-Stroke Applications Only)**. The device compares the raw angle value to the angle-value boundaries set by user-programming of the MIN\_ANGLE\_S or MAX\_ANGLE\_S fields. If the angle is excessive, an error flag is set at ERR[AH] (high boundary violation) or ERR[AL] (low boundary violation). This feature is useful for applications that use angle strokes less than 360 degrees (short stroke). (Note: This feature is only active if the shortstroke bit has been set.)

**P4 Gain Adjust (Short-Stroke Applications Only).** This bit adjusts the output dynamic range of the device. For example, if the application only requires 45 degrees of stroke, the user can set this field such that a 45-degree angular change would be distributed across the entire  $4095 \rightarrow 0$  code range. Set using the GAIN field. (Note: This feature is only active if the short-stroke bit has been set.)

**P4a Harmonic Linearization (Optional).** Applies user-programmed error correction coefficients (set in the LINC registers) to the raw angle measurements. Use the HL bit to enable harmonic linearization.

P4b Prelinearization 0 Offset (optional but required if segmented linearization is used). The expected angle values should be distributed throughout the input dynamic range to optimize angle post-processing. This is mostly needed for applications that use full 360-degree rotations. This value establishes the position that corresponds to zero error. This value should be set such that the 360  $\geq$  degree range corresponds to the 4095  $\geq$  0 code range. Setting this point is critical if segmented linearization is used. This is required prior to going through linearization, as the compensation requires a continuous input function to operate correctly. Set using the LIN\_OFFSET field. **P4c Segmented Linearization (Optional).** Applies user-programmed error correction coefficients (set in the LINC registers) to the raw angle measurements. Use the SL bit to enable segmented linearization.

**P5 Postlinearization 0 Offset (Optional)**. This computation assigns the final angle offset value, to set the low expected angle value to code 0 in the output dynamic range, after all linearization and processing has been completed. Set using the ZERO\_OFFSET field.

**P5a Postlinearization Rotation (Optional)**. This feature allows the user to chose the polarity of the final angle output, relative to the result of the prelinearization rotation direction setting (LR bit, previously described). Set using the RO bit.

**P6 Angle Clamping (Short-Stroke Applications Only).** The A1335 has the ability to apply digital clamps to the output signal. This feature is most useful for applications that use angle strokes less than 360 degrees. If the output signal exceeds the upper clamp, the output stays at the clamped value. If the output signal is lower than the lower clamp, the output stays at the low clamp value. Set using the CLAMP\_HI and CLAMP\_LO fields. (Note: This feature is only active if the short-stroke bit has been set.)

**P7 Angle Rounding to 12 Bits**. All internal calculations for angle processing in the A1335 are performed with 16-bit precision. This step rounds the data into a 12-bit word for output through the primary serial interface.

**P7a Angle Inversion (Short-Stroke Applications Only).** Rotation within the high and low clamp values:

(Note: This feature is only active if the short-stroke bit has been set.)

**P8 Die Adjust (Optional)**. Rotates final angle 180 degrees. Used to compensate for the 180-degree offset between die in dual SoC packages.

#### **Diagnostic Features**

The A1335 was designed with diagnostic requirements in mind and supports many on-chip diagnostics as well as error/status flags, enabling the host microcontroller to assess the operational status of each die.

In addition, the A1335 supports three different on-chip userinitiated diagnostics.

#### **USER-INITIATED DIAGNOSTICS**

The following three internal self-tests may be configured to run at power-on, and may also be initiated at any time by the system microcontroller via extended access commands through the SPI/ I<sup>2</sup>C interface. A failure of any one of the three self-tests asserts the self-test (ST) failure flag within the extended error register. The specific failing test can be identified by performing an extended address read (address 0xFFFC).

#### • CVH Self-Test

Table 2: Status and Error Flags

The CVH self-test is a signal-path diagnostic used to verify both analog and digital system integrity. Test execution requires approximately 36 ms, during which time no new angle measurements are generated by the sensor. The test is implemented by changing the transducer switch configuration from typical mode into a test configuration, allowing a test current to drive the CVHD in place of the magnetic field. By changing the direction of the test current and sequencing different elements within the CVH, the self-test emulates a changing magnetic-field angle. The measured angle is monitored to determine a passing or failing device. A failure of the CVH self-test asserts the ST flag. If the self-test was initiated via the extended access command, test results for the individual Hall elements are stored in the SRAM CMDSTATUS field (0x00) and the primary serial interface ERD register (0x0E through 0x11).

Due to the sensitivity of the self-test, test results are only valid at field levels equal to or less than 300 G and temperatures at or above 25°C.

#### • SRAM BIST

The SRAM built-in self-test (BIST) verifies proper functionality of the SRAM. The test may be run in either long or short mode, and can be configured to halt on error. A failure of the SRAM BIST asserts the ST flag. When enabled to run on power-up, the short-test mode is used, requiring approximately 100  $\mu$ s to complete. For more information on SRAM BIST options, consult the A1335 programming guide.

| Fault Condition                               | Description                                                                                                                                                                                                         | Sensor Response                     |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| V <sub>CC</sub> < V <sub>CCLOW(TH)(min)</sub> | Indicates potential for reduced angle accuracy                                                                                                                                                                      | UV error flag is set                |

| V <sub>CC</sub> > 8.8 V                       | Indicates possible system-level power supply failure                                                                                                                                                                | OV error flag is set <sup>[1]</sup> |

| Field > MAG_HIGH                              | MAG_HIGH programmable from 0 to1240 G in 40 G steps. Monitors level of MAG field in case of mechanical failure                                                                                                      | MH flag is set                      |

| Field < MAG_LOW                               | MAG_LOW programmable from 0-620 G in 20 G steps. Monitors level of MAG field in case of mechanical failure                                                                                                          | ML flag is set                      |

| −60°C > T <sub>A</sub> > 180°C                | Ambient temperature beyond maximum rating detected                                                                                                                                                                  | TR flag is set                      |

| Processor Halt                                | Monitors digital logic for proper functionality                                                                                                                                                                     | WT and WC flags are set             |

| Single-Bit EEPROM Error (correctable)         | Detects and corrects a single-bit EEPROM Error                                                                                                                                                                      | ES error flag is set                |

| Multi-Bit EEPROM Error (uncorrectable)        | Detects a multi-bit uncorrectable EEPROM ERROR                                                                                                                                                                      | EU error flag is set                |

| Single-Bit SRAM Error (correctable)           | Detects and corrects a single-bit SRAM Error                                                                                                                                                                        | SS error flag is set                |

| Multi-Bit SRAM Error (uncorrectable)          | Detects a multi-bit uncorrectable SRAM ERROR                                                                                                                                                                        | SU error flag is set                |

| Angle-Processing Errors                       | New angle measurement did not occur within the maximum time allotted.                                                                                                                                               | AT flag is set                      |

| Angle Out of Range                            | Angle value (prior to scaling by gain) is outside the range set by MIN_ANGLE<br>and MAX_ANGLE. Short-stroke only.                                                                                                   | AL or AH flag is set                |

| Loss of $V_{CC}$                              | Determines if system power was lost. Also detects a reset of the internal microprocessor                                                                                                                            | POR and RC flags are set            |

| Self-Test Failure                             | Indicates a failure of one of the three internal self-tests: SRAM BIST, ROM<br>checksum verification, and CVH self-test. Tests can be individually configured<br>to run at power-up and may also be user initiated. | ST flag is set                      |

[1] EEPROM programming pulses result in OV flag assertion.

#### ROM Checksum

Verification of the ROM checksum may be configured to occur at power-on. In addition, the checksum is continuously recalculated in the background during typical operation (independent of power-on configuration). This test may be initiated at any time by the system microcontroller via an extended access command (0xFFE0). If the self-test was initiated via the extended access command, the failing checksum is stored in the CMDSTATUS SRAM register (0x00). A bad ROM checksum asserts the self-test (ST) failure flag.

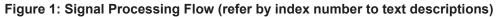

#### LOW VOLTAGE DETECTION

In addition to setting the undervoltage (UV) flag, a  $V_{CC}$  ramp also changes the state of the output pins (SDA/MISO and SENT) as the part enters and exits the reset condition. This is shown in Figure 2.

For more information about diagnostic features and flags, refer to the more-complete description of the available flags and settings in the <u>A1335 Programming Manual</u>.<sup>[1]</sup>

Figure 2: Relationship of V<sub>CC</sub> and Output

### **Programming Modes**

The EEPROM can be written through the dedicated I<sup>2</sup>C or SPI interface pins or via Manchester encoding on the VCC pin, allowing process coefficients to be entered and options selected. (Note: programming EEPROM also requires the VCC line to be pulsed, which could adversely affect other devices if powered from the same line). Certain operating commands also are available by writing directly to SRAM. The EEPROM and SRAM provide parallel data structures for operating parameters. The SRAM provides a rapid test and measurement environment for application

development and bench-testing. The EEPROM provides persistent storage at the end of line for final parameters. At power-on initialization, the EEPROM contents are read into the corresponding SRAM. Provided the lock microprocessor (LM) bit within EEPROM is not set, SRAM can be overwritten during operation (use caution). The EEPROM is permanently locked by setting the lock EEPROM (LE) bit in the EEPROM.

The A1335 EEPROM is programmed via either the I<sup>2</sup>C, the SPI, or the VCC pin serial interface, with additional power provided by pulses on the VCC pin to set the EEPROM bit fields.

<sup>[1]</sup> https://www.allegromicro.com/-/media/files/application-notes/an296127-a1335-advanced-on-chip-linearization.pdf?sc\_lang=en

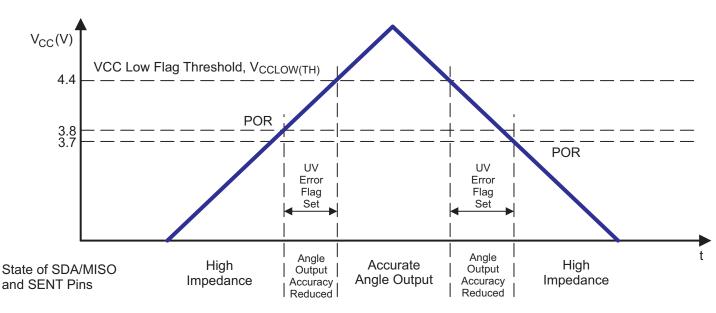

### MANCHESTER SERIAL INTERFACE

To facilitate addressable device programming when using the unidirectional SENT output mode with no need for additional wiring, the A1335 incorporates a serial interface on the VCC line. (Note: The A1335 may be programmed via the SPI or I<sup>2</sup>C interfaces, with additional wiring connections. For detailed information about part programming, refer to the A1335 Programming Manual). This interface allows an external controller to read and write registers in the A1335 EEPROM and volatile memory. The device uses a point-to-point communication protocol, based on Manchester encoding per G.E. Thomas (a rising edge indicates a 0, and a falling edge indicates a 1), with address and data transmitted MSB first. The addressable Manchester code implementation uses the logic states of the SA0/SA1 pins to set address values for each die. In this way, individual communication with up to four A1335 die is possible.

To prevent any undesired programming of the A1335, the serial interface can be disabled by setting the disable Manchester bit. With this bit set, the A1335 ignores any Manchester input on VCC.

### **Entering Manchester Communication Mode**

Provided the disable Manchester bit is not set in EEPROM, the A1335 continuously monitors the VCC line for valid Manchester commands. The part takes no action until a valid Manchester access code is received.

There are two special Manchester code commands used to activate or deactivate the serial interface and specify the output format used during read operations:

- 1. Manchester Access Code: Enters Manchester communication mode; Manchester code is output on the SENT pin.

- 2. Manchester Exit Code; returns the SENT pin to typical (angle data) output format.

Once the Manchester communication mode is entered, the SENT output pin ceases to provide angle data, interrupting any data transmission in progress.

### **Transaction Types**

The A1335 receives all commands via the VCC pin, and responds to read commands via the SENT pin, as shown in Figure 3. This implementation of Manchester encoding requires the communication pulses to be within a high ( $V_{MAN(H)}$ ) and low ( $V_{MAN(L)}$ ) range of voltages on the VCC line. Writing to EEPROM is supported by two high-voltage pulses on the VCC line.

Each transaction is initiated by a command from the controller; the A1335 does not initiate any transactions. Two commands are recognized by the A1335: write and read.

### Writing to EEPROM

When a write command requires writing to nonvolatile EEPROM, after the write command, the controller must also send two *programming pulses*, high-voltage strobes via the VCC pin. These strobes are detected internally, allowing the A1335 to boost the voltage on the EEPROM gates. For specific details about sensor programming and protocols, refer to the <u>A1335 Programming Manual</u>.

Figure 3: Top-Level Programming Interface

#### Manchester Interface Reference

#### Table 3: Manchester Interface Protocol Characteristics [1]

| Characteristics Symbol                 |                         | Note                                                                                                                      |                            | Тур. | Max.                                  | Unit |

|----------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------|------|---------------------------------------|------|

| INPUT/OUTPUT SIGNAL TIMING             |                         |                                                                                                                           | 1                          |      | · · · ·                               |      |

| Bit Rate                               |                         | Defined by the input message bit rate sent from the external controller                                                   | 4                          | _    | 100                                   | kbps |

| Bit Time                               |                         | Data bit pulse width at 4 kbps                                                                                            | 243                        | 250  | 257                                   | μs   |

| Bit Time                               | t <sub>BIT</sub>        | Data bit pulse width at 100 kbps                                                                                          | 9.5                        | 10   | 10.5                                  | μs   |

| Bit Time Error                         | err <sub>TBIT</sub>     | Deviation in t <sub>BIT</sub> during one command frame                                                                    | -11                        | _    | +11                                   | %    |

| Write Delay                            | t <sub>WRITE(E)</sub>   | Required delay from the end of the second<br>EEPROM programming pulse to the leading<br>edge of a following command frame | V <sub>CC</sub> <<br>6.0 V | -    | -                                     | -    |

| Read Delay                             | t <sub>start_read</sub> | Delay from the trailing edge of a read<br>command frame to the leading edge of the read<br>acknowledge frame              | ¹∕₄ × t <sub>bit</sub>     | -    | ³∕₄ × t <sub>bit</sub>                | μs   |

| EEPROM PROGRAMMING PULS                | E                       |                                                                                                                           |                            |      |                                       |      |

| EEPROM Programming Pulse<br>Setup Time | t <sub>sPULSE(E)</sub>  | Delay from last bit cell of write command to start<br>of EEPROM programming pulse                                         | 40                         | _    | -                                     | μs   |

| INPUT SIGNAL VOLTAGE                   |                         |                                                                                                                           |                            |      | · · · · · · · · · · · · · · · · · · · |      |

| Manchester Code High Voltage           | V <sub>MAN(H)</sub>     | Applied to VCC line                                                                                                       | 7.8                        | -    | -                                     | V    |

| Manchester Code Low Voltage            | V <sub>MAN(L)</sub>     | Applied to VCC line                                                                                                       | -                          | _    | 5.7                                   | V    |

| OUTPUT SIGNAL VOLTAGE (App             | lied on SENT            | Line)                                                                                                                     |                            |      |                                       |      |

| Manchester Code High Voltage           |                         | Minimum R <sub>pullup</sub> = 5 kΩ                                                                                        | $0.9 \times V_S$           | -    | _                                     | V    |

| Manchester Code Fight voltage          | V <sub>MAN(H)</sub>     | Maximum R <sub>pullup</sub> = 50 k $\Omega$                                                                               | 0.7 × V <sub>S</sub>       | -    | -                                     | V    |

| Manchester Code Low Voltage            | V <sub>MAN(L)</sub>     | 5 kΩ ≤ R <sub>pullup</sub> ≤ 50 kΩ                                                                                        | -                          | _    | 0.1                                   | V    |

<sup>[1]</sup> Determined by design.

### **SENT Output Mode**

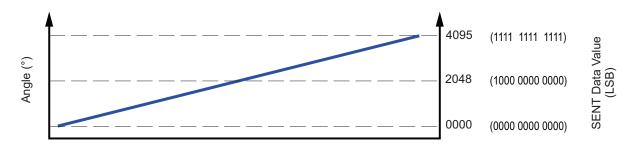

The SENT output converts the measured magnetic field angle into a binary value mapped to the full-scale output (FSO) range of 0 to 4095, shown in Figure 4. This data is inserted into a binary pulse message, referred to as a frame, that conforms to the SENT data transmission specification (SAEJ2716 JAN2010).

The SENT frame may be configured via EEPROM. The A1335 may operate in one of three broadly defined SENT modes. (For details about SENT modes and settings, refer to the A1335 Programming Manual.)

- SAE J2716 SENT: Free-streaming SENT frame in accordance with industry specification. Additional programmability allows tick time adjustment from 0.5 μs to 7.9 μs.

- Triggered SENT (TSENT): User-defined sampling and retrieval.

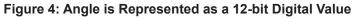

- Shared SENT: Allows multiple devices to share a common SENT line. Devices may either be directly addressed (addressable SENT or ASENT) or sequentially polled (sequential SENT or SSENT).

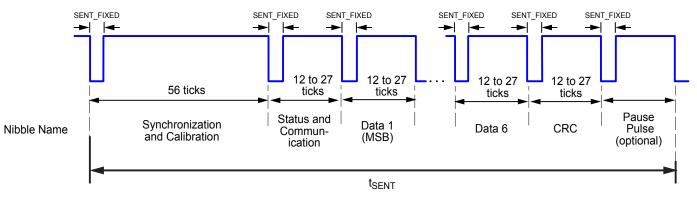

#### SENT MESSAGE STRUCTURE

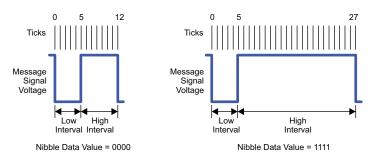

Data within a SENT message frame is represented as a series of nibbles, with the following characteristics:

- Each nibble is an ordered pair of a low-voltage interval followed by a high-voltage interval.

- The low-voltage interval acts as the delimiting state, which acts as a boundary between each nibble. The length of this low-voltage interval is fixed at 5 ticks.

- The high-voltage interval performs the job of the information state and is variable in duration in order to contain the data payload of the nibble.

- The slew rate of the falling edge may be adjusted using the SENT\_DRIVER parameter.

#### Figure 6: General Value Formation for SENT

0000 (left), 1111 (right)

The duration of a nibble is denominated in ticks. The period of a tick is set by the SENT\_TICK parameter. The duration of the nibble is the sum of the low-voltage interval plus the high-voltage interval.

The parts of a SENT message are arranged in the following required sequence (see Figure 7):

- **1. Synchronization and Calibration:** Flags the start of the SENT message.

- **2. Status and Communication Nibble:** Provides A1335 status and the optional serial data determined by the setting of the SENT\_SERIAL parameter.

- 3. Data: Angle information and optional data.

- 4. CRC: Error checking.

- **5. Pause Pulse (optional):** Fill pulse between SENT message frames.

#### Table 4: Nibble Composition and Value

| Q                           | uantity of Tick              | s      | Pinon                      | Decimal             |  |  |

|-----------------------------|------------------------------|--------|----------------------------|---------------------|--|--|

| Low-<br>Voltage<br>Interval | High-<br>Voltage<br>Interval | Total  | Binary<br>(4-bit)<br>Value | Equivalent<br>Value |  |  |

| 5                           | 7                            | 12     | 0000                       | 0                   |  |  |

| 5                           | 8                            | 13     | 0001                       | 1                   |  |  |

| 5                           | 9                            | 14     | 0002                       | 2                   |  |  |

| ÷                           | •<br>•                       | •<br>• | •<br>•                     | •                   |  |  |

| 5                           | 21                           | 26     | 1110                       | 14                  |  |  |

| 5                           | 22                           | 27     | 1111                       | 15                  |  |  |

Figure 7: General Format for SENT Message Frame

### **APPLICATION INFORMATION**

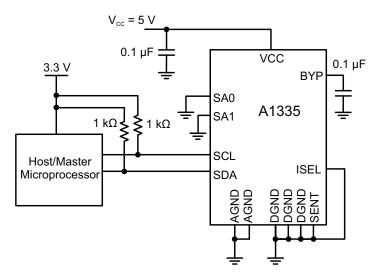

### **Serial Interface Description**

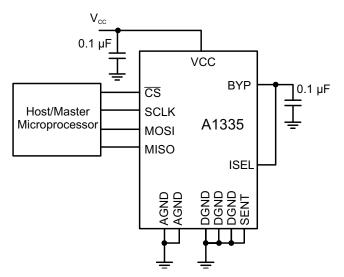

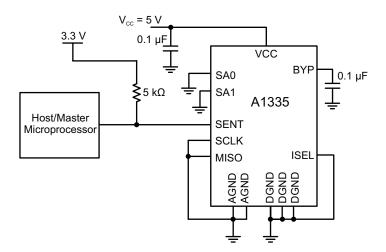

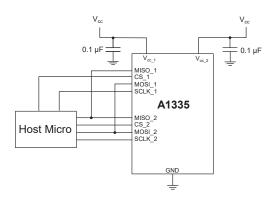

The A1335 features I<sup>2</sup>C-, SPI-, and SENT-compliant interfaces for communication with a host microcontroller or other controller. A basic circuit for configuring the A1335 package is shown

in Figure 8. When not in use, the SENT pin should be grounded (as shown in A and B of Figure 8) and SENT disabled (SENT\_MODE = 0 within EEPROM address 0x317).

(B) Typical A1335 configuration using SPI interface

(C) Typical A1335 configuration using SENT interface (SA0/SA1 may be brought to BYP or GND to configure Manchester/Shared SENT address)

Figure 8: Typical A1335 configuration

**Table 5: Target Magnet Parameters**

### **Magnetic Target Requirements**

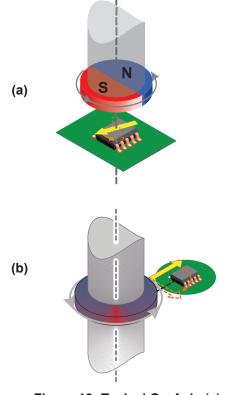

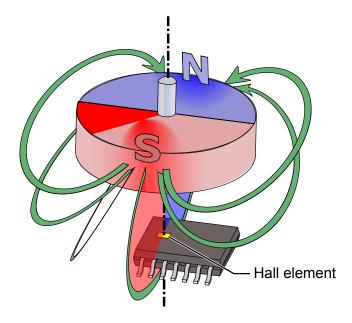

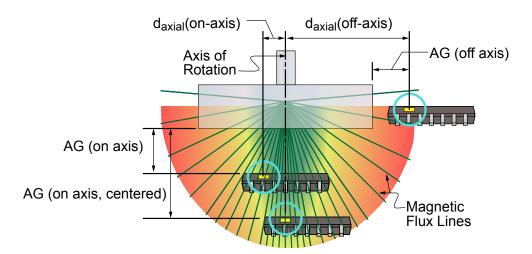

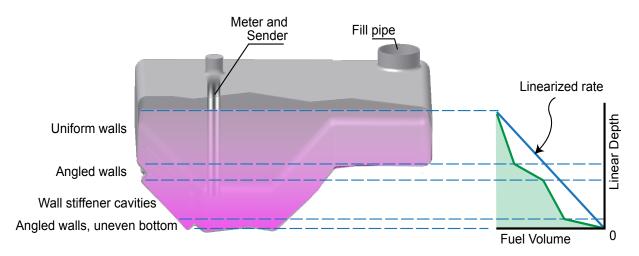

There are two main sensing configurations for magnetic angle sensing: on-axis and off-axis. On-axis (end of shaft) refers to when the center axis of a magnet lines up with the center of the sensing element. Off-axis (side shaft) refers to when the angle sensor is mounted along the edge of a magnet. On- and off-axis sensing configurations are illustrated in the Effect of Orientation on Signal section.

### FIELD STRENGTH

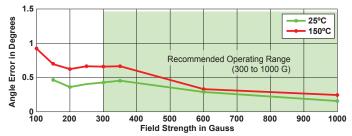

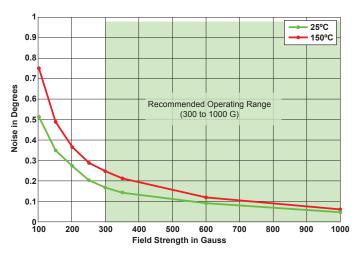

The A1335 actively measures and adapts to its magnetic environment. This allows operation throughout a large range of field strengths (recommended range is 300 to 1000 G; operation beyond this range is allowed with no long-term impact). Due to the greater signal-to-noise ratio provided at higher field strengths, performance inherently increases with increasing field strength. Typical angle performance over applied field strength is shown in Figure 9 and Figure 10.

Figure 9: Typical Maximum Angle Error Over Field Strength

Figure 10: Typical One-Sigma Angle Noise Over Field Strength

| Magnetic Material                   | Diameter<br>(mm) | Thickness<br>(mm) |  |  |

|-------------------------------------|------------------|-------------------|--|--|

| Neodymium (bonded)                  | 15               | 4                 |  |  |

| Neodymium (sintered) <sup>[1]</sup> | 10               | 4                 |  |  |

| Neodymium (sintered)                | 8                | 3                 |  |  |

| Neodymium/SmCo                      | 6                | 2.5               |  |  |

| Thickness                           | Diameter         |                   |  |  |

[1] A sintered neodymium magnet with 10 mm (or greater) diameter and 4 mm thickness is the recommended magnet for redundant applications.

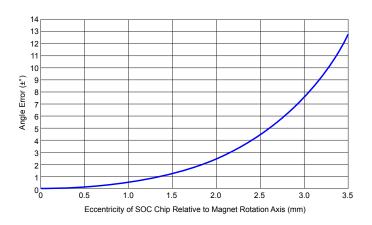

## Figure 11: Simulated Error versus Eccentricity for a 10 mm × 4 mm Neodymium Magnet at a 2.7 mm Air Gap

Typical systemic error versus magnet to sensor eccentricity (d<sub>axial</sub>), Note: "Systemic error" refers to application errors in alignment and system timing. It does not refer to sensor IC device errors. The data in this graph is simulated with ideal magnetization.

### **Calculating Target Zero-Degree Angle**

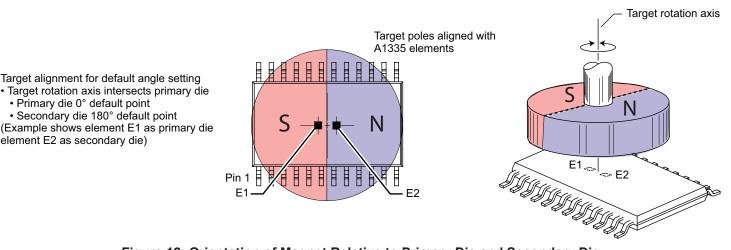

When shipped from the factory, the default angle value when oriented as shown in Figure 12, is approximately 0° (180° on secondary die). In some cases, the end user may want to program an angle offset in the A1335 to compensate for variation in magnetic assemblies, or for applications where absolute system-level readings are required.

The internal algorithm for computing the output angle is:

$Angle_{OUT} = Angle_{postLin} - Zero \ Offset \ . \tag{1}$

The procedure to "zero out" the A1335 follows.

During final application calibration, position the magnet above the sensor in the required zero-degree position and record the angle reading from the device. Program the Zero Offset field in EEPROM (0x306 bits 12:0) with this value (for additional details, refer to the <u>A1335 Programming Manual</u>).

It is important to keep in mind that the zero offset adjustment occurs after linearization within the A1335 signal path (see Figure 1). As a result, the zero offset adjustment should be performed following end-of-line linearization.

### **Bypass Pin Usage**

The bypass pin is required for proper device operation and is intended to bypass internal IC nodes of the A1335. A 0.1  $\mu$ F capacitor must be placed in close proximity to the bypass pin. It is not intended to be used to source external components.

Figure 12: Orientation of Magnet Relative to Primary Die and Secondary Die

#### **ON-AXIS APPLICATIONS**

Some common on-axis applications for the device include digital potentiometer, motor sensing, power steering, and throttle sensing. The A1335 is designed to operate with magnets constructed with a variety of magnetic materials, cylindrical geometries, and field strengths, as shown in Table 5. The device has two internal linearization algorithms that can compensate for much of the error due to alignment. For more-detailed information about magnet selection and theoretical error, contact Allegro.

#### **OFF-AXIS APPLICATIONS**

There are two major challenges with off-axis angle-sensing applications. The first is field strength. All efforts should be conducted to maximize magnetic signal strength obsrved by the device. The goal is a minimum of 300 G. Field strength can be maximized by using high-quality magnetic material, and by minimizing the distance between the sensor and the magnet. Another challenge is overcoming the inherent nonlinearity of the magnetic-field vector generated at the edge of a magnet. The device has two linearization algorithms that can compensate for much of the geometric error. Harmonic linearization is recommended for off-axis applications.

Figure 13: Typical On-Axis (a) and Off-Axis (b) Orientation

### Effect of Orientation on Signal

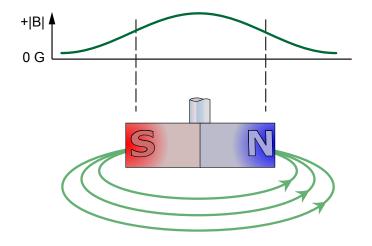

Figure 14: The magnetic field flux lines run between the north pole and south pole of the magnet. The peak flux densities are between the poles.

Figure 15: As the magnet rotates, the Hall element detects the rotating relative polarity of the magnetic field (solid line). When the center of rotation is centered on the Hall element, the magnetic flux amplitude is constant (dashed line).

Figure 16: Centering the axis of magnet rotation on the Hall element provides the strongest signal in all degrees of rotation.

Figure 17: The magnetic flux density degenerates rapidly away from the plane of peak north-south polarity. When the axis of rotation is placed away from the Hall element, the device must be placed closer to the magnetic poles to maintain an adequate level of flux at the Hall element.

### Linearization

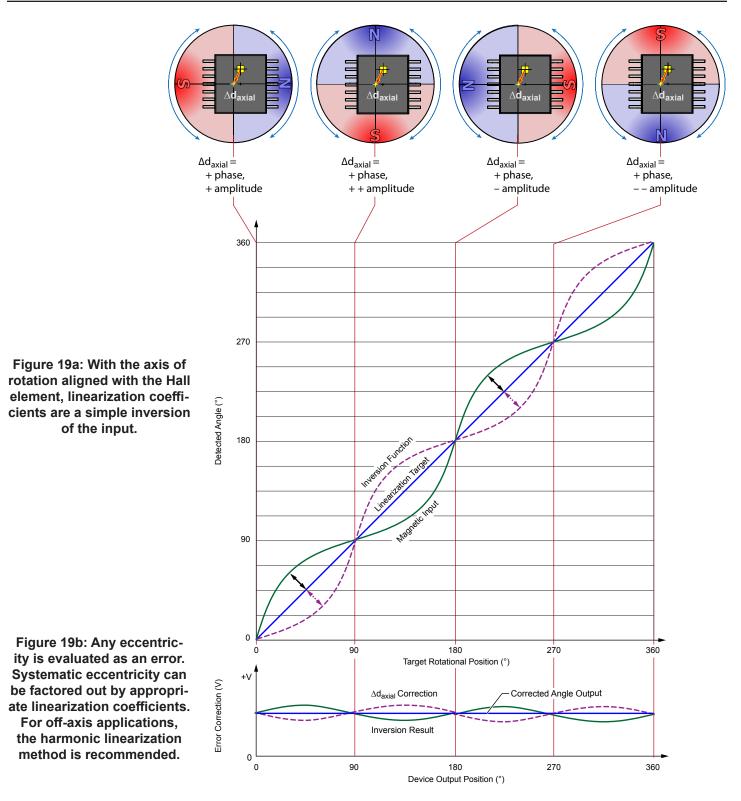

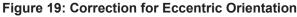

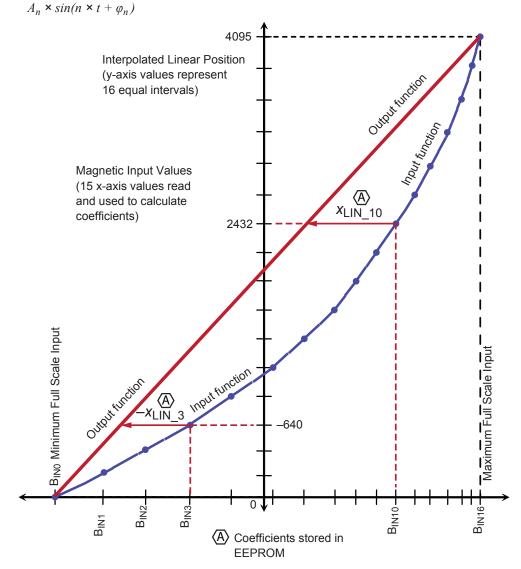

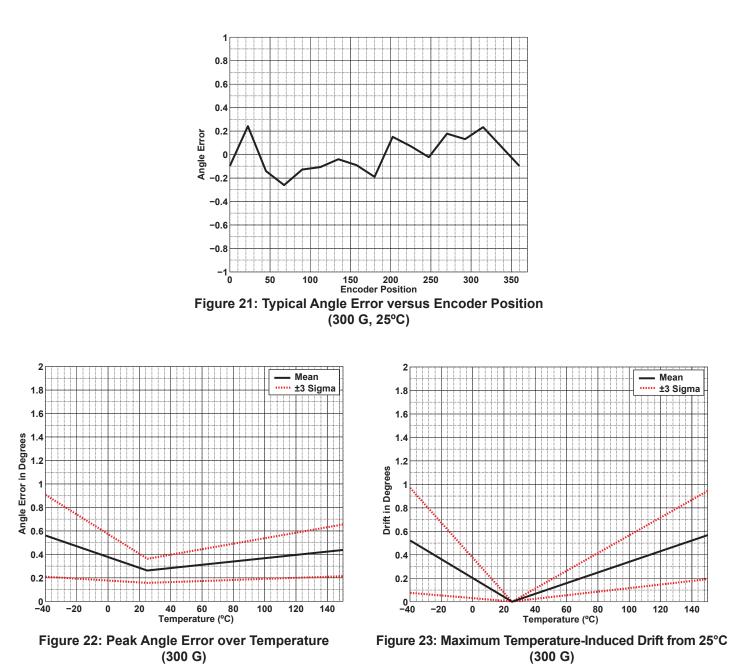

Magnetic fields are generally not completely linear throughout the full range of target positions. This can be the result of nonuniformities in mechanical motion or of material composition. In some applications, it may be required to apply a mathematical transfer function to the angle that is reported by the A1335.