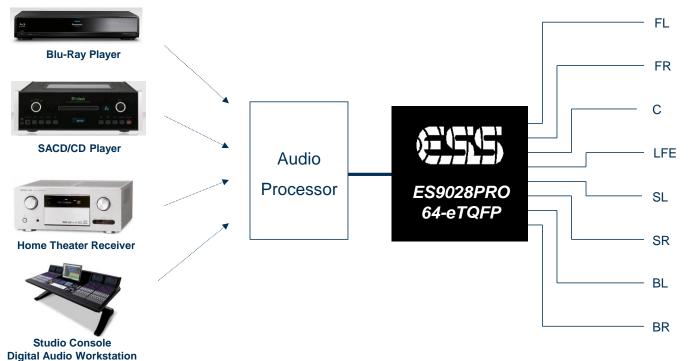

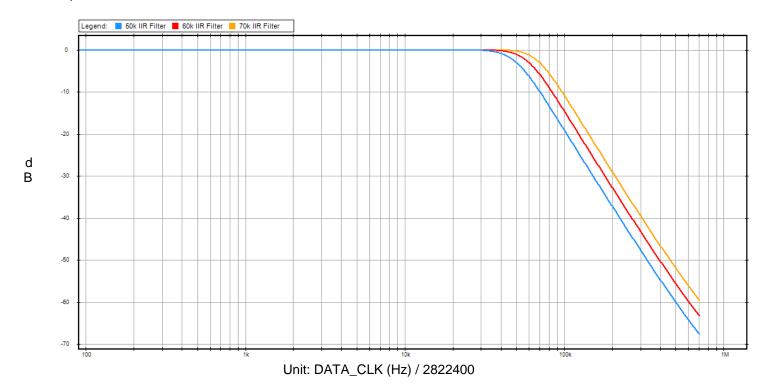

The **SABRE® ES9028PRO HyperStream® II** 8-channel audio DAC is a high performance 32-bit solution designed for Audiophile and Studio equipment applications such as SACD players, Blu-ray players, digital preamplifier, A/V receivers, studio consoles and digital audio workstations.

| Part<br>Number | Description                                         | Package     | DNR<br>(dB)              | THD+N<br>(dB) | 32-bit<br>DAC | I <sup>2</sup> S / DoP / DSD<br>/ SPDIF Input | Jitter<br>Reduction |

|----------------|-----------------------------------------------------|-------------|--------------------------|---------------|---------------|-----------------------------------------------|---------------------|

|                | SABRE® PRO 32-bit 8-ch<br>HypersStream II Audio DAC | 64<br>eTQFP | 135 (mono)<br>129 (8-Ch) | -120          | Yes           | Yes                                           | Yes                 |

Using the critically acclaimed ESS' patented **HyperStream® II** architecture and Time Domain Jitter Eliminator, the ES9028PRO 32-Bit Audio DAC delivers an unprecedented DNR of up to 135dB in mono mode and THD+N of –120dB, the industry's highest performance level that will satisfy the needs of the most demanding audio applications.

The **ES9028PRO** handles up to 32-bit 768kHz PCM, DSD256 via DoP and native DSD1024 data in master or slave timing modes. Custom sound signature is supported via a fully programmable FIR filter with 7 presets. Residual distortion from suboptimal PCB components and layout can be minimized using **ES9028PRO's** unique THD compensation circuit, while chip-to-chip gain variation is minimized via a built-in auto gain calibration circuit.

The **SABRE**® **ES9028PRO** sets the standard for HD audio performance, **SABRE SOUND**®, in a cost-effective, easy-to-use 64-eTQFP package for today's most demanding digital-audio applications.

| FEATURES                                        | BENEFITS                                                                                          |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Patented 32-bit HyperStream® II DAC             | <ul> <li>Industry's highest performance 32-bit audio DAC with unprecedented</li> </ul>            |

| <ul> <li>Up to 135dB DNR (mono mode)</li> </ul> | dynamic range and ultra-low distortion                                                            |

| ○ −120dB THD+N                                  | <ul> <li>Supports both synchronous and asynchronous sampling modes</li> </ul>                     |

| Patented Time Domain Jitter Eliminator          | <ul> <li>Unmatched audio clarity free from input clock jitter</li> </ul>                          |

| 64-bit accumulator and 32-bit processing        | <ul> <li>Distortion-free signal processing</li> </ul>                                             |

|                                                 | <ul> <li>Supports SPDIF, PCM (I<sup>2</sup>S, LJ, RJ 16-32-bit), DoP or DSD input</li> </ul>      |

| Versatile Digital Input                         | <ul> <li>Supports up to 768kHz PCM, DSD256 via DoP and native DSD1024</li> </ul>                  |

| Versatile Digital Input                         | <ul> <li>Supports up to 1.536MHz external oversampling filter</li> </ul>                          |

|                                                 | <ul> <li>Supports master and slave timing modes</li> </ul>                                        |

|                                                 | <ul> <li>Click-free, soft mute and output volume changes</li> </ul>                               |

| Integrated DSP functions                        | <ul> <li>Programmable Zero detection</li> </ul>                                                   |

|                                                 | <ul> <li>De-emphasis for 32kHz, 44.1kHz, and 48kHz sampling</li> </ul>                            |

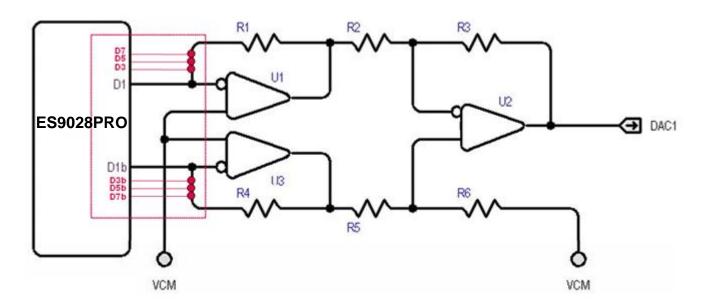

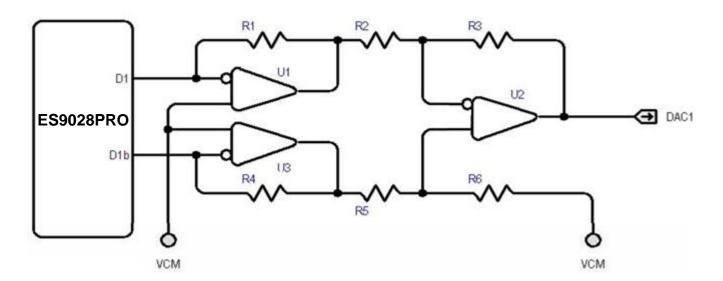

| Customizable output configuration               | <ul> <li>Mono, stereo, or 8-channel output with either current-mode or voltage-mode</li> </ul>    |

| Customizable output comiguration                | operation (current-mode gives lower THD)                                                          |

|                                                 | <ul> <li>7 ready-to-use preset filters with linear/minimum phase and low-delay options</li> </ul> |

| User Programmable Oversampling Filter           | <ul> <li>Supports custom coefficients for unique sound signature</li> </ul>                       |

|                                                 | Supports external oversampling filter                                                             |

| Clock Gearing                                   | <ul> <li>Reduces operating frequency for lower power consumption</li> </ul>                       |

| Gain Calibration ADC                            | <ul> <li>Enables uniform output level across all chips</li> </ul>                                 |

| THD compensation                                | <ul> <li>Minimizes distortion from external PCB components and layout</li> </ul>                  |

| Full 8-to-8 channel mapping                     | <ul> <li>Allows channels to be remapped for optimized PCB routing</li> </ul>                      |

### **APPLICATIONS**

Digital-Audio Workstations Blu-ray / SACD players

Professional Audio Equipment A/V Receivers

# ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

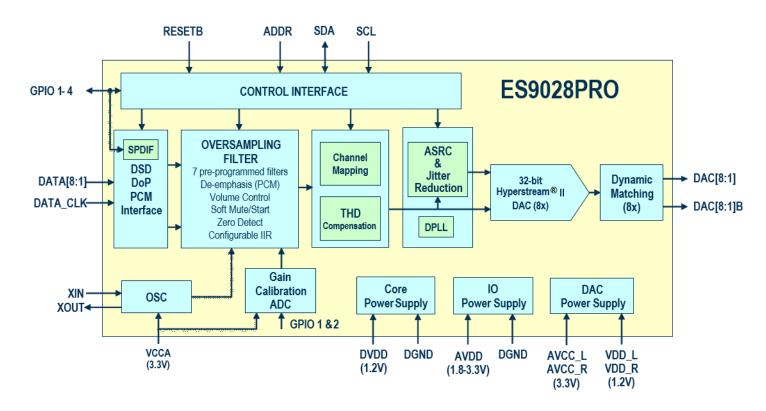

#### **FUNCTIONAL BLOCK DIAGRAM**

### TYPICAL APPLICATION BLOCK DIAGRAM

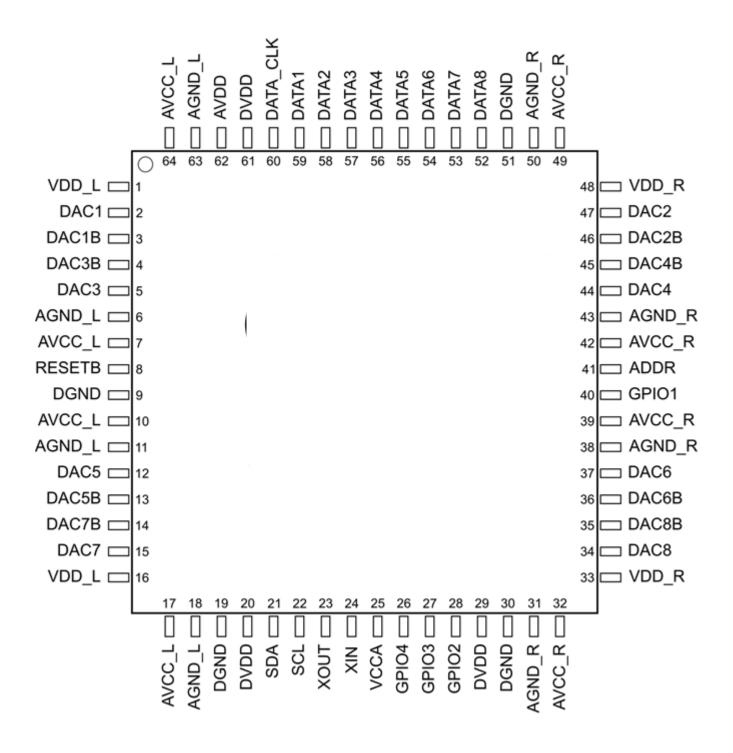

#### **PIN LAYOUT**

# ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

### **PIN DESCRIPTIONS**

| Pin | Name   | Pin Type | Reset State               | Pin Description                                                 |

|-----|--------|----------|---------------------------|-----------------------------------------------------------------|

| 1   | VDD_L  | Power    | Power                     | Analog Power (+1.2V) for Left channels                          |

| 2   | DAC1   | AO       | Driven to ground via RDAC | Differential Positive Analog Output 1                           |

| 3   | DAC1B  | AO       | Driven to ground via RDAC | Differential Negative Analog Output 1                           |

| 4   | DAC3B  | AO       | Driven to ground via RDAC | Differential Negative Analog Output 3                           |

| 5   | DAC3   | AO       | Driven to ground via RDAC | Differential Positive Analog Output 3                           |

| 6   | AGND_L | Ground   | Ground                    | Analog Ground for Left channels                                 |

| 7   | AVCC_L | Power    | Power                     | Low-Noise Analog Power (+3.3V) for Left channels                |

| 8   | RESETB | I        | Tri-stated                | Global Reset Input, Active Low                                  |

| 9   | DGND   | Ground   | Ground                    | Digital Ground                                                  |

| 10  | AVCC_L | Power    | Power                     | Low-Noise Analog Power (+3.3V) for Left channels                |

| 11  | AGND_L | Ground   | Ground                    | Analog Ground for Left channels                                 |

| 12  | DAC5   | AO       | Driven to ground via RDAC | Differential Positive Analog Output 5                           |

| 13  | DAC5B  | AO       | Driven to ground via RDAC | Differential Negative Analog Output 5                           |

| 14  | DAC7B  | AO       | Driven to ground via RDAC | Differential Negative Analog Output 7                           |

| 15  | DAC7   | AO       | Driven to ground via RDAC | Differential Positive Analog Output 7                           |

| 16  | VDD_L  | Power    | Power                     | Analog Power (+1.2V) for Left channels                          |

| 17  | AVCC_L | Power    | Power                     | Low-Noise Analog Power (+3.3V) for Left channels                |

| 18  | AGND_L | Ground   | Ground                    | Analog Ground for Left channels                                 |

| 19  | DGND   | Ground   | Ground                    | Digital Ground                                                  |

| 20  | DVDD   | Power    | Power                     | Digital Power (+1.2V) for core logic                            |

| 21  | SDA    | I/O      | Tri-stated                | I <sup>2</sup> C Serial Data Input / Output                     |

| 22  | SCL    | I        | Tri-stated                | I <sup>2</sup> C Serial Clock Input                             |

| 23  | XOUT   | AO       | Floating                  | Crystal oscillator output                                       |

| 24  | XIN    | Al       | Floating                  | Crystal oscillator input (Note: can also just be a clock input) |

| 25  | VCCA   | Power    | Power                     | Power (+3.3V) for oscillator / Gain Calibration                 |

| 26  | GPIO4  | I/O      | Tri-stated                | GPIO 4                                                          |

| 27  | GPIO3  | I/O      | Tri-stated                | GPIO 3                                                          |

| 28  | GPIO2  | I/O      | Tri-stated                | GPIO 2                                                          |

| 29  | DVDD   | Power    | Power                     | Digital Power (+1.2V) for core of chip                          |

| 30  | DGND   | Ground   | Ground                    | Digital Ground                                                  |

| 31  | AGND_R | Ground   | Ground                    | Analog Ground for Right channels                                |

| 32  | AVCC_R | Power    | Power                     | Low-Noise Analog Power (+3.3V) for Right channels               |

| 33  | VDD_R  | Power    | Power                     | Analog Power (+1.2V) for Right channels                         |

| 34  | DAC8   | AO       | Driven to ground via RDAC | Differential Positive Analog Output 8                           |

| 35  | DAC8B  | AO       | Driven to ground via RDAC | Differential Negative Analog Output 8                           |

| 36  | DAC6B  | AO       | Driven to ground via RDAC | Differential Negative Analog Output 6                           |

| 37  | DAC6   | AO       | Driven to ground via RDAC | Differential Positive Analog Output 6                           |

| 38  | AGND_R | Ground   | Ground                    | Analog Ground for Right channels                                |

| 39  | AVCC_R | Power    | Power                     | Low-Noise Analog Power (+3.3V) for Right channels               |

August 19, 2022 v3.7

# ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

### PIN DESCRIPTIONS (continued)

| Pin         | Name     | Pin Type | Reset State               | Pin Description                                                                                                   |

|-------------|----------|----------|---------------------------|-------------------------------------------------------------------------------------------------------------------|

| 40          | GPIO1    | I/O      | Tri-stated                | GPIO 1                                                                                                            |

| 41          | ADDR     | I        | Tri-stated                | Chip Address Select                                                                                               |

| 42          | AVCC_R   | Power    | Power                     | Low-Noise Analog Power (+3.3V) for Right channels                                                                 |

| 43          | AGND_R   | Ground   | Ground                    | Analog Ground for Right channels                                                                                  |

| 44          | DAC4     | AO       | Driven to ground via RDAC | Differential Positive Analog Output 4                                                                             |

| 45          | DAC4B    | AO       | Driven to ground via RDAC | Differential Negative Analog Output 4                                                                             |

| 46          | DAC2B    | AO       | Driven to ground via RDAC | Differential Negative Analog Output 2                                                                             |

| 47          | DAC2     | AO       | Driven to ground via RDAC | Differential Positive Analog Output 2                                                                             |

| 48          | VDD_R    | Power    | Power                     | Analog Power (+1.2V) for Right channels                                                                           |

| 49          | AVCC_R   | Power    | Power                     | Low-Noise Analog Power (+3.3V) for Right channels                                                                 |

| 50          | AGND_R   | Ground   | Ground                    | Analog Ground for Right channels                                                                                  |

| 51          | DGND     | Ground   | Ground                    | Digital Ground                                                                                                    |

| 52          | DATA8    | I/O      | Tri-stated                | DSD Data8 or SPDIF Input 9                                                                                        |

| 53          | DATA7    | I/O      | Tri-stated                | DSD Data7 or SPDIF Input 8                                                                                        |

| 54          | DATA6    | I/O      | Tri-stated                | DSD Data6 or SPDIF Input 7                                                                                        |

| 55          | DATA5    | I/O      | Tri-stated                | DSD Data5 or PCM Data CH7 / CH8 or SPDIF Input 6                                                                  |

| 56          | DATA4    | I/O      | Tri-stated                | DSD Data4 or PCM Data CH5 / CH6 or SPDIF Input 5                                                                  |

| 57          | DATA3    | I/O      | Tri-stated                | DSD Data3 or PCM Data CH3 / CH4 or SPDIF Input 4                                                                  |

| 58          | DATA2    | I/O      | Tri-stated                | DSD Data2 or PCM Data CH1 / CH2 or SPDIF Input 3                                                                  |

| 59          | DATA1    | I/O      | Tri-stated                | DSD Data1 or PCM Frame Clock or SPDIF Input 2                                                                     |

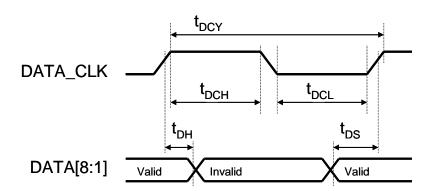

| 60          | DATA_CLK | I/O      | Tri-stated                | PCM Bit Clock or DSD Bit Clock or SPDIF Input 1                                                                   |

| 61          | DVDD     | Power    | Power                     | Digital Power (+1.2V) for core of chip                                                                            |

| 62          | AVDD     | Power    | Power                     | Digital Power (+1.8V / +3.3V) for top pad ring of chip                                                            |

| 63          | AGND_L   | Ground   | Ground                    | Analog Ground for Left channels                                                                                   |

| 64          | AVCC_L   | Power    | Power                     | Low-Noise Analog Power (+3.3V) for Left channels                                                                  |

| Exposed Pad |          |          |                           | Can be left open, connected to digital or analog ground. Internally connected to substrate via a conductive epoxy |

#### Notes:

VDD\_L, VDD\_R and DVDD are internally connected.

I = Digital Input I/O = Input / Output AI = Analog Input AO = Analog Output

All unused digital inputs should be connected to ground directly, or via a pull-down resistor of  $4.7k\Omega$  to  $47k\Omega$

## **5V Tolerant Pins (3.3V AVDD Supply Only)**

The following pins are 5V tolerant:

- RESETB

- SDA and SCL

- GPIO1-4

- ADDR

- DATA1-8

- DATA\_CLK

## **System Clock and Audio Inputs**

**Sampling Rate Notations**

| Mode                         | FSR<br>raw sample rate at<br>audio interface | fs<br>sample rate for filter<br>specification |

|------------------------------|----------------------------------------------|-----------------------------------------------|

| DSD                          | DATA_CLK                                     | FSR / 64                                      |

| DoP                          | Frame Clock Rate                             | FSR / 4                                       |

| Serial (PCM) Normal Mode     | Frame Clock Rate                             | FSR                                           |

| Serial (PCM) OSF Bypass Mode | Frame Clock Rate                             | FSR/8                                         |

| SPDIF                        | SPDIF Audio Rate                             | FSR                                           |

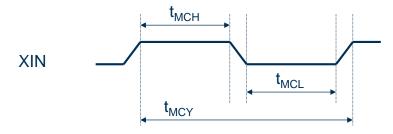

### System Clock (XIN) and Audio Master Clock (MCLK)

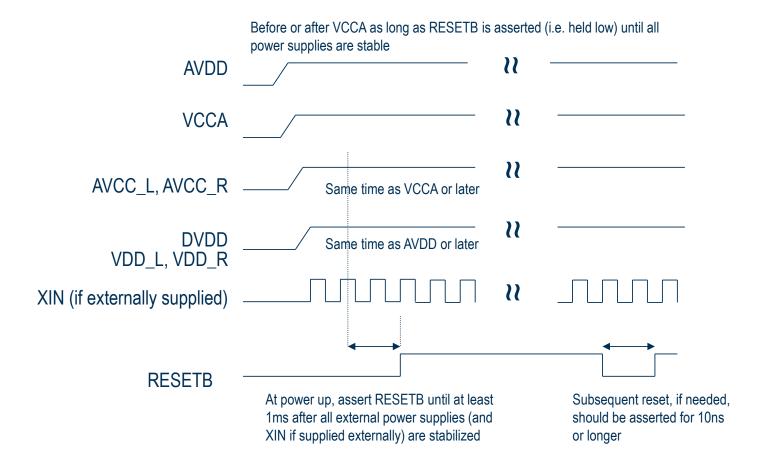

The system clock (XIN) can be generated with a crystal using the built-in oscillator or supplied externally.

- o The maximum XIN frequency is 100MHz as specified in <u>ANALOG PERFORMANCE</u> and <u>XIN Timing</u>.

- o The audio master clock (MCLK) is divided down from XIN via clock\_gear in Register 0: System Registers.

- The minimum MCLK frequency for a given raw sample rate FSR is specified in ANALOG PERFORMANCE.

- o The minimum MCLK frequency for a given I2C clock is specified in the table under I2C Timing Table.

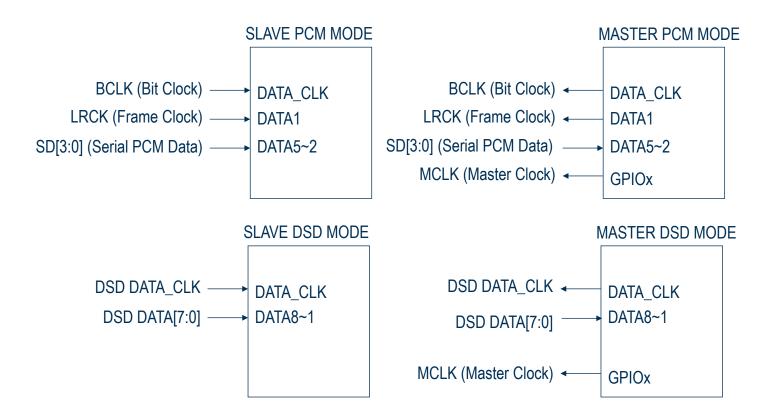

#### **PCM Pin Connections**

| Pin Name | Description                    |

|----------|--------------------------------|

| DATA1    | Frame clock                    |

| DATA5~2  | 8-channel PCM serial data      |

| DATA_CLK | Bit clock for PCM audio format |

Note: DATA\_CLK frequency must be (2 x serial\_length) x FSR.

serial\_length can be set in Register 2: Serial Data Configuration and Automute Enable

#### SPDIF Pin Connections

| Pin Name | Description       |

|----------|-------------------|

| GPIO4~1  | SPDIF input 13~10 |

| DATA8~1  | SPDIF input 9~2   |

| DATA_CLK | SPDIF input 1     |

An SPDIF source multiplexer allows for up to 13 SPDIF sources to be connected to the data and GPIO pins selectable via Register 11: SPDIF Mux and GPIO Inversion. SPDIF input mode can be manually selected by *input\_select* in Register 1: Input selection or automatically selected if *auto\_select* in Register 1: Input selection is set to a mode allowing automatic SPDIF selection.

#### **DSD Pin Connections**

| Pin Name | Description                  |

|----------|------------------------------|

| DATA8~1  | 8-channel DSD data input     |

| DATA_CLK | Bit clock for DSD data input |

Note: DATA\_CLK frequency must be FSR.

August 19, 2022 v3.7

### ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

#### **Master Mode**

The DAC can become an audio timing master via master\_mode in Register 10: Master Mode and Sync Configuration.

o The 'input select' bits in Register 1: Input selection must be set correctly to select either DSD or serial master mode.

The Bit Clock frequency can be configured using one of the following two methods:

- o Set the desired master\_div in Register 10: Master Mode and Sync Configuration, or

- Use NCO mode to set FSR using <u>Register 42-45: Programmable NCO</u>. When in NCO mode the <u>master\_div</u> setting will be ignored.

An available GPIO pin can be configured to output MCLK using Register 8: GPIO1-2 Configuration and Register 9: GPIO3-4 Configuration.

### ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

### **Function Description**

#### Soft Mute

When Mute is asserted the output signal will ramp to the -∞ level. When Mute is reset the attenuation level will ramp back up to the previous level set by the volume control register. Asserting Mute will not change the value of the volume control register. The ramp rate is set by Register 6: De-emphasis Filter & Volume Ramp Rate according to the following relationship:

$$rate = \frac{2^{\text{vol\_rate}} * FSR}{512} dB/s$$

#### **Automute (PCM and SPDIF modes only)**

Automute is disabled by default and can be enabled by setting *automute\_time* to a non-zero value. Automute is triggered when the following conditions are met:

| Mode  | Detection Condition               | Time                |

|-------|-----------------------------------|---------------------|

|       | Data is lower than automute_level | 2096896             |

| SPDIF | for the specified time            | automute_time * FSR |

Automute\_time can be set using Register 4: Automute Time. Automute\_level can be set using Register 5: Automute Level.

The automute status can be read using *automute\_status* in <u>Register 64: Chip ID and Status</u> or via a GPIO pin programmed as *Automute Status* using Register 8: GPIO1-2 Configuration or Register 9: GPIO3-4 Configuration.

The triggered automute behavior can be configured using Register 2: Serial Data Configuration and Automute Enable to one of the followings:

- No action

- Soft Mute

- Ramp all channels to ground to reduce power consumption

- Soft Mute then ramp all channels to ground

The ramp-to-ground rate can be configured to  $4096 * \frac{2^{(\text{soft\_start\_time+1})}}{\text{MCLK}}$  using Register 14: Soft-Start Configuration.

#### **Volume Control**

Each channel has an independently controlled digital attenuation circuit which can be set to attenuate from 0dB to -127dB in 0.5dB steps. When a new volume level is set, the digital attenuation circuit will ramp softly to the new level. To ensure silent digital volume transitions each 0.5dB step can take as many as 64 intermediate steps depending on the *volume\_rate* setting in Register 6: De-emphasis Filter & Volume Ramp Rate.

#### **Master Trim**

The master trim sets the 0dB reference level for the digital volume control of each DAC. The master trim is programmable via Register 24-27: Master Trim. The master trim registers store a 32bit signed number and should never exceed the full scale signed value 32'h7FFFFFFF.

#### 18dB Channel Gain (PCM mode only)

A +18dB gain can be applied on a per-channel based using Register 62: +18dB Channel Gain, in addition to volume control and master trim. Note that the output will be clipped if the +18dB gain results in larger than full scale output.

August 19, 2022 v3.7

### ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

#### **De-emphasis**

The de-emphasis feature is included for audio data that has utilized the 50/15µs pre-emphasis for noise reduction. There are three de-emphasis filters, one for 32kHz, one for 44.1kHz, and one for 48kHz selectable via *deemph\_sel* and bypassed via *deemph\_bypass* in Register 6: De-emphasis Filter & Volume Ramp Rate.

The de-emphasis filter can automatically be applied when an SPDIF stream sets the de-emphasis flag. It will auto detect the sample rate (32k, 44.1k, 48k) in either consumer or professional formats and then apply the correct de-emphasis filter. The automatic enabling of the de-emphasis filter can be enabled via *auto\_deemph* in Register 6: De-emphasis Filter & Volume Ramp Rate.

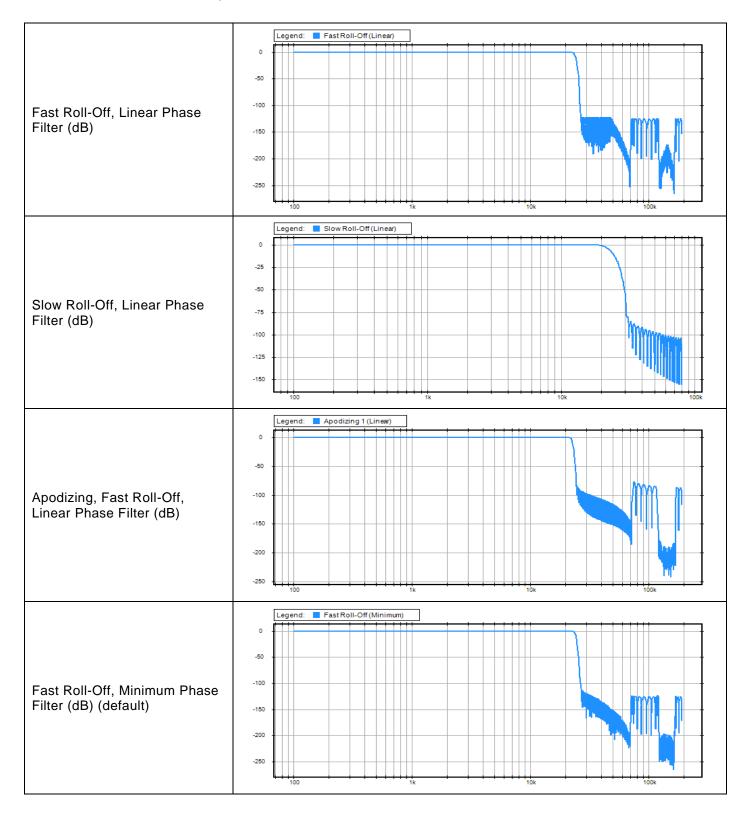

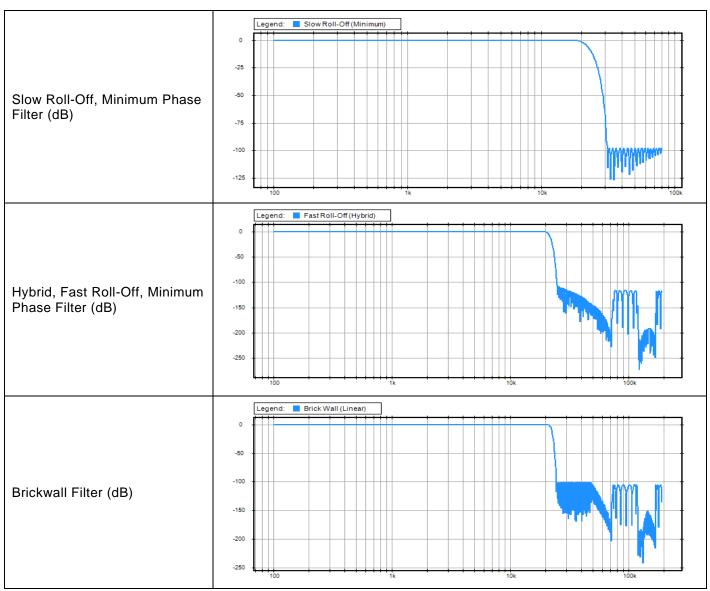

#### **Preset Oversampling FIR Filters**

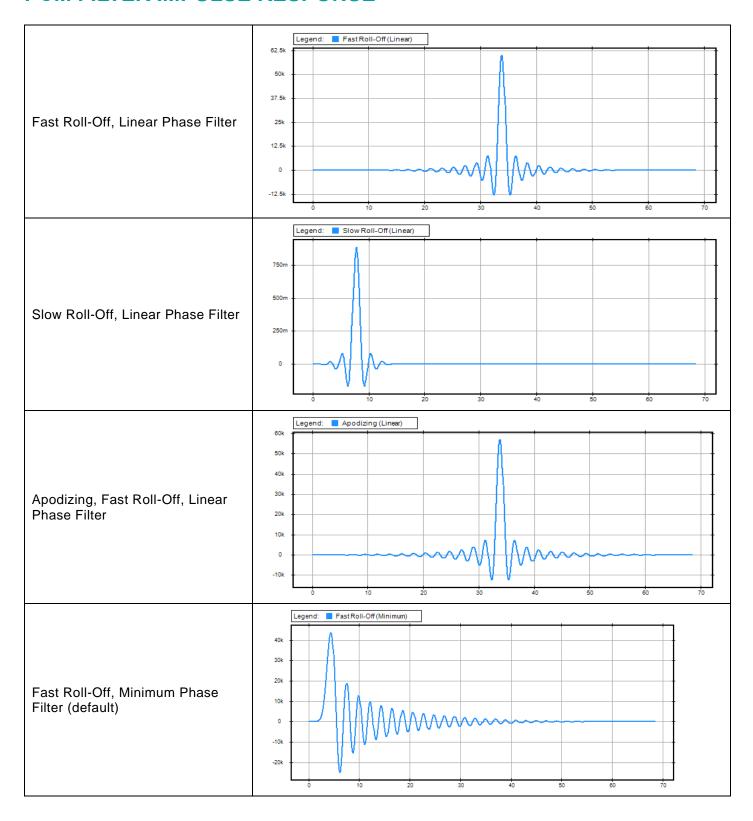

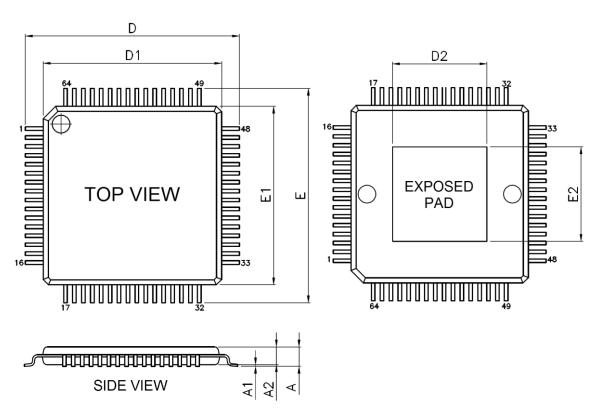

Seven pre-programmed digital filters are selectable for SPDIF and PCM serial mode via *filter\_shape* in <u>Register 7: Filter Bandwidth and System Mute</u>. See <u>ANALOG PERFORMANCE</u>, <u>PCM FILTER FREQUENCY RESPONSE</u> and <u>PCM FILTER IMPULSE RESPONSE</u> for more information.

#### **Custom Oversampling FIR Filter**

The FIR filter can also be programmed as a two-staged interpolation filter with custom coefficients to achieve unique sound signature. Custom coefficients can be generated using MATLAB and then downloaded using a custom C code.

#### Example Source Code for Loading a Filter

```

// only accept 128, 64 or 16 coefficients

// Note: The coefficients must be quantized to 32 bits for this method!

// Note: Stage 1 consists of 128 or 64 values (0-127 being the coefficients)

// Note: Stage 2 consists of 16 values (0-13 being the coefficients, 14-15 are zeros)

Stage 2 is symmetric about coefficient 13. See the example filters for more information.

byte fir_badr = 32;

byte coeff_stage = (byte)(coeffs.Count == 64 ? 0 : 1);

for (int i = 0; i < coeffs.Count; i++)</pre>

{

// stage 1 contains 128 or 64 coefficients, while stage 2 contains 16 coefficients

registers.WriteRegister(fir_badr, (byte)((coeff_stage << 7) + i));</pre>

// write the coefficient data

registers.WriteRegister(fir_badr+1, (byte)(coeffs[i] & 0xff));

registers.WriteRegister(fir_badr+2, (byte)((coeffs[i] >> 8) & 0xff));

registers.WriteRegister(fir_badr+3, (byte)((coeffs[i] >> 16) & 0xff));

registers.WriteRegister(fir_badr+5, 0x02); // set the write enable bit

// disable the write enable bit when we're done

registers.WriteRegister(fir_badr+5, (byte)(setEvenBit ? 0x04 : 0x00));

```

#### Oversampling Filter (OSF) Bypass

The oversampling FIR filter can be bypassed using *bypass\_osf* in Register 37: Programmable FIR Configuration, sourcing data directly into the IIR filter. The audio input should be oversampled at 8 x fs rate when OSF is bypassed to have the same IIR filter bandwidth as PCM audio sampled at fs rate. For example, a signal with 44.1kHz sample rate can be oversampled externally to 8 x 44.1kHz = 352.8kHz and then applied to the serial decoder in either I<sup>2</sup>S, LJ, or RJ format. The maximum sample rate that can be applied is 1.536MHz (8 x 192kHz).

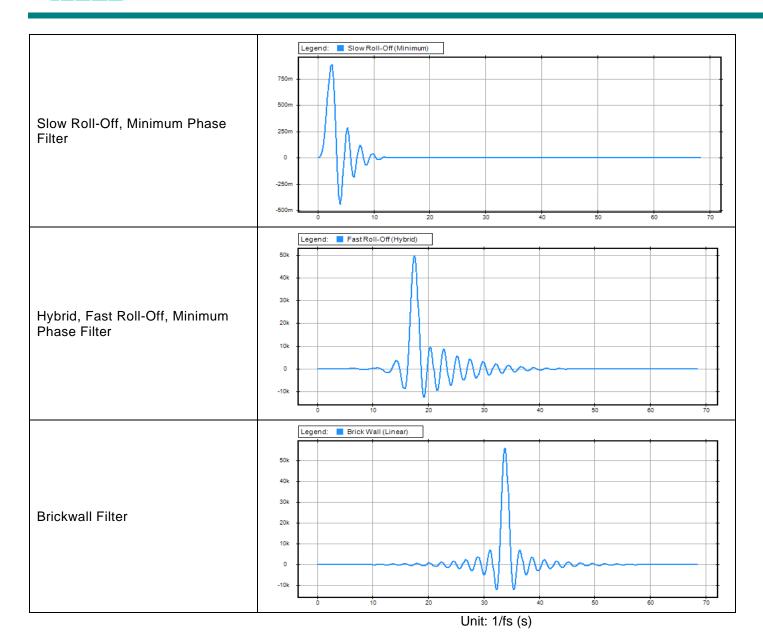

#### IIR Filter

Four filters with cutoffs at 47kHz, 50kHz, 60kHz, and 70kHz scaled by fs/44100 are selectable via *iir\_bw* in Register 7: Filter Bandwidth and System Mute. See ANALOG PERFORMANCE and IIR FILTER RESPONSE for more information.

## ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

#### Time Domain Jitter Eliminator and DPLL

By default, the DAC works in Jitter Eliminator mode allowing the audio interface timing to be asynchronous to MCLK. A DPLL constantly updates the FSR/MCLK ratio to calculate the true 32-bit timing of the incoming audio samples allowing the ESS patented Time Domain Jitter Eliminator to remove any distortion caused by jitter.

- The DPLL acquisition speed can be set by lock speed in Register 10: Master Mode and Sync Configuration.

- The PCM/SPDIF DPLL bandwidth can be set via dpll\_bw\_serial in Register 12: Jitter Eliminator / DPLL Bandwidth

- The DSD DPLL bandwidth can be set via dpll bw dsd in Register 12: Jitter Eliminator / DPLL Bandwidth

For best performance, the DPLL bandwidth should be set to the minimum setting that will keep the DPLL reliably in lock.

#### **Sample Rate Calculation**

The raw sample rate (FSR) can be calculated from Register 66-69: DPLL Number using the following formula:

$$FSR = \frac{(dpll\_num * MCLK)}{2^{32}}$$

#### Synchronous Mode (PCM mode only)

The DPLL can be bypassed if the incoming PCM audio is synchronous to MCLK with the relationship MCLK=128FSR. This can be enabled via 128fs\_mode in Register 10: Master Mode and Sync Configuration.

#### **DAC Full-Scale Gain Calibration**

DAC gain calibration enables uniform output level across multiple chips by compensating for chip-to-chip gain variations.

The DAC full-scale gain-calibration system works by comparing an internal resistor to an external precision resistor of known value. The two resistors are set up as a voltage divider that is connected between power and ground. The value of the internal resistor changes with semiconductor process variations so by measuring the divider's voltage output, using an ADC, the process variation from nominal can be measured and this is used to correct the DAC gain. As all the DAC channels are on the same monolithic chip, the channel-to-channel gain variation is very small and does not need to be trimmed.

There are two ADCs and either of the ADC inputs can be used to drive the auto-calibration circuit. The circuit uses the ADC value, as decimated by the internal programmable decimation filters, to scale the master\_trim value. Master\_trim can be programmed as normal but will be scaled by the ADC value when in automatic-calibration mode. In this mode, master\_trim can be set once by enabling automatic calibration, and the DAC output levels will be consistent across all DAC devices.

- Full-scale gain-calibration is enabled using calib\_en in Register 63: Auto Calibration.

- calib\_sel in Register 63: Auto Calibration selects which ADC to use

- calib\_latch in Register 63: Auto Calibration determines whether to use the new ADC correction value or ignore it.

- ADC values update at the ADC\_CLK rate which is also programmable in Register 46: ADC Configuration.

The ADC decimation filters may also be programmed to a lower bandwidth to help smooth out any voltage transients on the divider output.

August 19, 2022 v3.7

### ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

#### **THD Compensation**

THD Compensation can be used to minimize distortion from external PCB components and layout through the generation of inverse second and third harmonic components matching the target system distortion profile.

THD compensation can be enabled via *thd\_enb* in <u>Register 13: Jitter Eliminator / DPLL Configuration & THD Bypass</u>. The coefficient for manipulating second harmonic distortion is stored in <u>Register 28-29: THD Compensation C2</u>. The coefficient for manipulating third harmonic distortion is stored in <u>Register 30-31: THD Compensation C3</u>.

All channels use the same compensation coefficients.

#### Full Channel Mapping, Mono Mode and Stereo Mode

Channel mapping allows output channels to be remapped to arbitrary input channels for optimized PCB routing

Clearing stereo\_mode in Register 15: GPIO Input Selection & Volume Configuration allows the data for each DAC to be sourced from any input channel using Registers 38-41: DAC Channel Mapping.

Mono mode can be implemented by channel mapping all output DAC sources to the same input channel

Setting stereo\_mode in Register 15: GPIO Input Selection & Volume Configuration will source DAC channels 1/3/5/7 and channels 2/4/6/8 from input channel 1 and 2.

In SPDIF mode, DAC channels 1/3/5/7 and channels 2/4/6/8 are sourced from SPDIF input left and right channels.

#### **Power Supplies**

To minimize THD+N, AVCC\_L and AVCC\_R must be powered by low-noise +3.3V supplies. Although AVCC\_L and AVCC\_R could be powered from a single low-noise supply, crosstalk would be compromised and so separate +3.3V supplies are highly recommended. The ES9311Q dual ultra-low noise regulator is designed to power AVCC\_L and AVCC\_R and minimize THD+N and crosstalk on all SABRE PRO DACs.

# ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

#### **Audio Interface Formats**

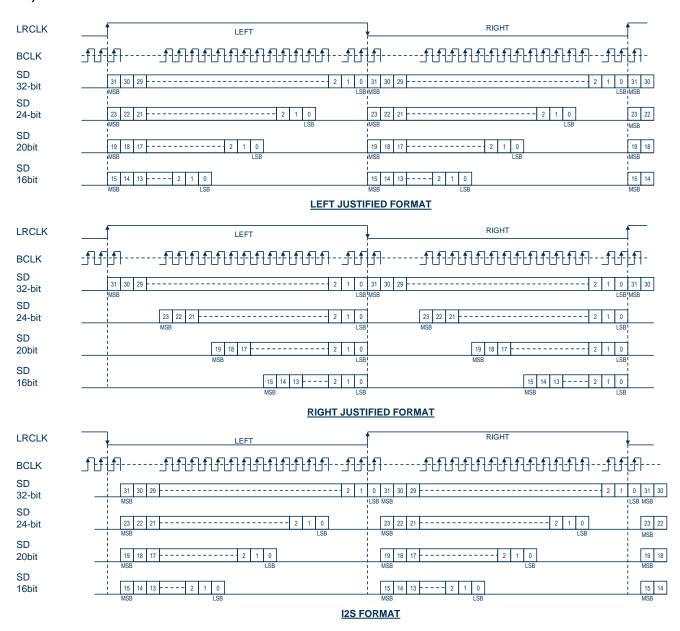

Several digital audio transport formats are supported to allow direct connection to common audio processors. Auto detection circuitry is enabled by default to detect the input format. The input mode can be explicitly set using <a href="Register 1: Input selection">Register 1: Input selection</a>. The following diagrams outline the supported formats (using stereo 2-channel inputs as an example).

#### PCM LJ, RJ and I2S Formats

The following number of BCLK edges are present per frame (left plus right):

16-bit mode: 32 BCLKs 24-bit mode: 48 BCLKs 32-bit mode: 64 BCLKs

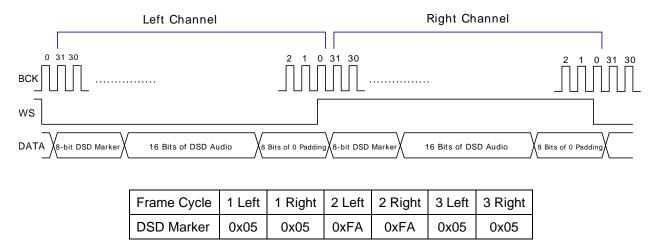

#### **DoP (DSD over PCM) Audio Format**

The DoP format packs DSD data into PCM frames. The incoming data is identified as DoP if the DSD Markers 0x05 and 0xFA alternating each frame clock cycle are present as illustrated below.

Note: DoP requires 24-bit or 32-bit PCM mode and cannot be handled by 16-bit PCM mode.

- 24-bit mode: DoP data consists of 8-bit marker in the MSB followed by 16-bit DSD data

- 32-bit mode: DoP data consists of 8-bit marker in the MSB followed by 16-bit DSD data and 8-bit padding

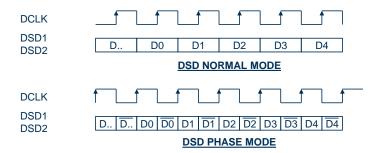

#### **Native DSD Format**

# ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

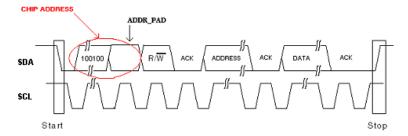

### **Serial Control Interface**

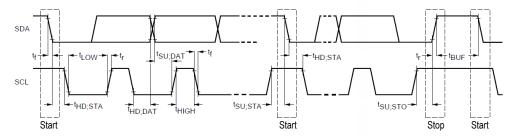

The registers inside the chip are programmed via an I<sup>2</sup>C interface. The diagram below shows the timing for this interface. The chip address can be set to 2 different settings via the "ADDR" pin.

| ADDR | CHIP ADDRESS |

|------|--------------|

| 0    | 0x90         |

| 1    | 0x92         |

#### Notes:

- 1. The "ADDR" pin is used to create the CHIP ADDRESS. (0x90, 0x92)

- 2. The first byte after the CHIP ADDRESS ("ADDRESS") is the register address.

- 3. The second byte after the CHIP ADDRESS ("DATA") is the data to be programmed into the register.

- 4. Multi-byte reads are NOT supported and will cause the I2C decoder to become unresponsive until a reset occurs.

### **I2C Timing Table**

| Parameter                           | Symbol              | MCLK       | Standard-Mode |      | Fast-Mode |     | Unit |

|-------------------------------------|---------------------|------------|---------------|------|-----------|-----|------|

|                                     |                     | Constraint | MIN           | MAX  | MIN       | MAX |      |

| SCL Clock Frequency                 | f <sub>SCL</sub>    | < MCLK/20  | 0             | 100  | 0         | 400 | kHz  |

| START condition hold time           | t <sub>HD,STA</sub> |            | 4.0           | -    | 0.6       | -   | μS   |

| LOW period of SCL                   | t <sub>LOW</sub>    | >10/MCLK   | 4.7           | -    | 1.3       | -   | μs   |

| HIGH period of SCL (>10/MCLK)       | t <sub>HIGH</sub>   | >10/MCLK   | 4.0           | -    | 0.6       | -   | μS   |

| START condition setup time (repeat) | <b>t</b> su,sta     |            | 4.7           | -    | 0.6       | -   | μs   |

| SDA hold time from SCL falling      | t <sub>HD,DAT</sub> |            | 0             | -    | 0         | -   | μS   |

| SDA setup time from SCL rising      | tsu,dat             |            | 250           | -    | 100       | -   | ns   |

| Rise time of SDA and SCL            | tr                  |            | -             | 1000 |           | 300 | ns   |

| Fall time of SDA and SCL            | t <sub>f</sub>      |            | -             | 300  |           | 300 | ns   |

| STOP condition setup time           | tsu,sto             |            | 4             | -    | 0.6       | -   | μS   |

| Bus free time between transmissions | t <sub>BUF</sub>    |            | 4.7           | -    | 1.3       | -   | μS   |

| Capacitive load for each bus line   | Сь                  |            | -             | 400  | -         | 400 | pF   |

### **REGISTER SETTINGS**

Note: Multi-byte registers use little-endian byte ordering scheme with the least significant byte stored at the lowest register address and most significant byte stored at the highest register address.

### **Register 0: System Registers**

| Bits     | [7:4]   | [3:2]    | [1]      | [0]        |

|----------|---------|----------|----------|------------|

| Mnemonic | osc_drv | clk_gear | reserved | soft_reset |

| Default  | 4'b0000 | 2'b00    | 1'b0     | 1'b0       |

| Bit   | Mnemonic   | Description                                                                    |

|-------|------------|--------------------------------------------------------------------------------|

|       |            | Oscillator drive specifies the bias current to the oscillator pad.             |

|       |            | 4'b1111: shut down the oscillator                                              |

| [7:4] | osc_drv    | • 4'b1110: ¼ bias                                                              |

| [7.4] | 030_01     | • 4'b1100: ½ bias                                                              |

|       |            | • 4'b1000: ¾ bias                                                              |

|       |            | 4'b0000: full bias (default)                                                   |

|       |            | Configures a clock divider network that can reduce the power                   |

|       |            | consumption of the chip by reducing the clock frequency supplied to            |

|       |            | both the digital core and analog stages.                                       |

| [3:2] | clk_gear   | • 2'b00: MCLK = XIN (default)                                                  |

|       |            | • 2'b01: MCLK = XIN / 2                                                        |

|       |            | • 2'b10: MCLK = XIN / 4                                                        |

|       |            | • 2'b11: MCLK = XIN / 8                                                        |

| [1]   | reserved   |                                                                                |

|       |            | Software configurable hardware reset with the ability to reset the design      |

|       |            | to its initial power-on configuration.                                         |

|       |            | <ul> <li>1'b1: resets the SABRE DAC to its power-on defaults</li> </ul>        |

| [0]   | soft_reset | 1'b0: normal operation (default)                                               |

|       |            | <b>Note</b> : This register will always read as "1'b0" as the power-on default |

|       |            | for this register is "1'b0". A reset can be verified by checking the status    |

|       |            | of other modified registers.                                                   |

# ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

## **Register 1: Input selection**

| Bits     | [7]       | [6]           | [5]            | [4]      | [3:2]       | [1:0]        |

|----------|-----------|---------------|----------------|----------|-------------|--------------|

| Mnemonic | user_bits | spdif_ig_data | spdif_ig_valid | reserved | auto_select | input_select |

| Default  | 1'b0      | 1'b0          | 1'b0           | 1'b0     | 2'b11       | 2'b00        |

| Bit   | Mnemonic       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]   | user_bits      | Both SPDIF channel status bits and SPDIF user bits are available for readback via the I2C interface. To reduce register count, the channel status bits and user bits occupy the same register space. Setting user_bits will present the SPDIF user bits on the read-only register interface instead of the default channel status bits.  • 1'b1: presents the SPDIF user bits on the read-only register interface • 1'b0: presents the SPDIF channel status bits on the read-only register interface (default) |

| [6]   | spdif_ig_data  | Configures the SPDIF decoder to ignore the 'data' flag in the channel status bits.  1'b1: ignore the data flag in the channel status bits and continue to process the decoded SPDIF data  1'b0: mute the SPDIF data when the data flag is set (default)  Note: Enabling the SPDIF output when data is present could cause undesirable noise if the SPDIF data is compressed audio or a non-standard format.                                                                                                    |

| [5]   | spdif_ig_valid | Configures the SPDIF decoder to ignore the 'valid' flag in the SPDIF stream.  1'b1: ignore the valid flag and continue to process the decoded SPDIF data  1'b0: mute the SPDIF data when the valid flag is invalid (default)                                                                                                                                                                                                                                                                                   |

| [4]   | reserved       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| [3:2] | auto_select    | Allows the SABRE DAC to automatically select between either serial, SPDIF or DSD input formats.  • 2'b11: automatically select between DSD, SPDIF or serial data (default)  • 2'b10: automatically select between SPDIF or serial data  • 2'b01: automatically select between DSD or serial data  • 2'b00: disable automatic input decoder and instead use the information provided by register 1[1:0]                                                                                                         |

| [1:0] | input_select   | Configures the SABRE DAC to use a particular input decoder if auto_select is disabled.  • 2'b11: DSD  • 2'b10: reserved  • 2'b01: SPDIF  • 2'b00: serial (default)  Note: Register 1[3:2] must be set to 2'b00 for input_select to function.                                                                                                                                                                                                                                                                   |

## Register 2: Serial Data Configuration and Automute Enable

| Bits     | [7:6]           | [5:4]       | [3:2]         | [1:0]       |

|----------|-----------------|-------------|---------------|-------------|

| Mnemonic | automute_config | serial_bits | serial_length | serial_mode |

| Default  | 2'b00           | 2'b11       | 2'b11         | 2'b00       |

| Bit   | Mnemonic           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6] | automute<br>config | Configures the automute state machine, which allows the SABRE DAC to perform different power saving and sound optimizations.  • 2'b11: perform a mute and then ramp all channels to ground when an automute condition is asserted  • 2'b10: ramp all channels to ground when an automute condition is asserted  • 2'b01: perform a mute when an automute condition is asserted  • 2'b00: normal operation (default)  Note: Ramping DAC outputs to ground can reduce the power consumption of the SABRE DAC in some situations.  Note: This process can be sped up by using the automute_time, volume_rate and soft_start_time registers. |

| [5:4] | serial_bits        | Selects how many bits consist of a data word in the serial data stream.  • 2'b11: 32-bit data words (default)  • 2'b10: 32-bit data words  • 2'b01: 24-bit data words  • 2'b00: 16-bit data words                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| [3:2] | serial_length      | Selects how many DATA_CLK pulses exist per data word.  • 2'b11: 32-bit data words (default)  • 2'b10: 32-bit data words  • 2'b01: 24-bit data words  • 2'b00: 16-bit data words                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| [1:0] | serial_mode        | Configures the type of serial data.  • 2'b11 or 2'b10: right-justified mode  • 2'b01: left-justified mode  • 2'b00: I2S mode (default)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

## **Register 3: Reserved**

| Bits     | [7:0]       |

|----------|-------------|

| Mnemonic | reserved    |

| Default  | 8'b00000000 |

## **Register 4: Automute Time**

| Bits     | [7:0]         |

|----------|---------------|

| Mnemonic | automute_time |

| Default  | 8'd0          |

| Bit   | Mnemonic      | Description                                                                                                                                                       |

|-------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | automute_time | Configures the amount of time the audio data must remain below the automute_level before an automute condition is flagged. Defaults to 0 which disables automute. |

| [7:0] |               | Time in seconds = $\frac{2096896}{\text{automute\_time} * FSR}$                                                                                                   |

## Register 5: Automute Level

| Bits     | [7]      | [6:0]          |

|----------|----------|----------------|

| Mnemonic | reserved | automute_level |

| Default  | 1'b0     | 7'd104         |

| Bit   | Mnemonic       | Description                                                                                                                                                                                                                                              |

|-------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]   | reserved       |                                                                                                                                                                                                                                                          |

| [6:0] | automute_level | Configures the threshold which the audio must be below before an automute condition is flagged. The level is measured in decibels (dB) and defaults to -104dB.  Note: This register works in tandem with automute_time to create the automute condition. |

## Register 6: De-emphasis Filter & Volume Ramp Rate

| Bits     | [7]         | [6]           | [5:4]      | [3]      | [2:0]       |

|----------|-------------|---------------|------------|----------|-------------|

| Mnemonic | auto_deemph | deemph_bypass | deemph_sel | reserved | volume_rate |

| Default  | 1'b0        | 1'b1          | 2'b00      | 1'b1     | 2'b010      |

| Bit   | Mnemonic      | Description                                                                                                                                                                                                                               |  |

|-------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [7]   | auto_deemph   | Automatically engages the de-emphasis filters when SPDIF data is provides and the SPDIF channel status bits contains valid de-emphasis settings.  • 1'b1: enables automatic de-emphasis  • 1'b0: disables automatic de-emphasis (default) |  |

| [6]   | deemph_bypass | <ul> <li>Enables or disables the built-in de-emphasis filters.</li> <li>1'b1 disabled de-emphasis filters (default)</li> <li>1'b0 enables de-emphasis filters</li> </ul>                                                                  |  |

| [5:4] | deemph_sel    | Selects which de-emphasis filter is used.  • 2'b11: reserved  • 2'b10: 48kHz  • 2'b01: 44.1kHz  • 2'b00: 32kHz (default)                                                                                                                  |  |

| [3]   | reserved      | Must be set to 1'b1 (default) for normal operation                                                                                                                                                                                        |  |

| [2:0] | volume_rate   | Selects a volume ramp rate to use when transitioning between different volume levels. The volume ramp rate is measured in decibels per second (dB/s). Volume rate is in the range 0-7. $ rate = \frac{2^{vol\_rate} * FSR}{512} \; dB/s $ |  |

# ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

## Register 7: Filter Bandwidth and System Mute

| Bits     | [7:5]        | [4:3]    | [2:1]  | [0]  |

|----------|--------------|----------|--------|------|

| Mnemonic | filter_shape | reserved | iir_bw | mute |

| Default  | 3'b010       | 2'b00    | 2'b00  | 1'b0 |

| Bit   | Mnemonic     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| [7:5] | filter_shape | Selects the type of filter to use during the 8x FIR interpolation phase.  3'b111: brickwall filter 3'b110: hybrid, fast roll-off, minimum phase filter 3'b100: apodizing, fast roll-off, linear phase filter 3'b101: reserved 3'b011: slow roll-off, minimum phase filter 3'b010: fast roll-off, minimum phase filter 3'b001: slow roll-off, linear phase filter 3'b000: fast roll-off, linear phase filter The FIR filter is only applied to PCM data, DSD bypasses this phase |  |  |

| [4:3] | reserved     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| [2:1] | iir_bw       | Selects the type of filter to use during the 8x IIR interpolation phase.  • 2'b11: 1.5873fs (70k @ 44.1kHz)  • 2'b10: 1.3605fs (60k @ 44.1kHz)  • 2'b01: 1.1338fs (50k @ 44.1kHz)  • 2'b00: 1.0757fs (47.44k @ 44.1kHz) (default)  Note: 47.44k filter should only be used for PCM data. Recommended settings for DSD data are 50k, 60k or 70k.                                                                                                                                 |  |  |

| [0]   | mute         | Mutes all 8 channels of the SABRE DAC.  1'b1: mute all eight channels 1'b0: normal operation (default)                                                                                                                                                                                                                                                                                                                                                                          |  |  |

August 19, 2022 v3.7

# ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

### **Register 8: GPIO1-2 Configuration**

| Bits     | [7:4]     | [3:0]     |

|----------|-----------|-----------|

| Mnemonic | gpio2_cfg | gpio1_cfg |

| Default  | 4'd8      | 4'd8      |

### **Register 9: GPIO3-4 Configuration**

| Bits     | [7:4]     | [3:0]     |

|----------|-----------|-----------|

| Mnemonic | gpio4_cfg | gpio3_cfg |

| Default  | 4'd8      | 4'd8      |

#### **GPIO Table**

The GPIO can each be configured in one of several ways.

The table below is for programming each independent GPIO configuration value.

| gpioX_cfg | Name                    | I/O       | Details                                                                                                                                                                                                              |

|-----------|-------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |                         | Direction |                                                                                                                                                                                                                      |

| 4'd 0     | Automute Status         | Output    | Output is high when an automute has been triggered. This signal is analogous to the automute_status register (register 64).                                                                                          |

| 4'd 1     | Lock Status             | Output    | Output is high when lock is triggered. This signal is analogous to the lock_status register (register 64).                                                                                                           |

| 4'd 2     | Volume Min              | Output    | Output is high when all digital volume controls have been ramped to minus full scale. This can occur, for example, if automute is enabled and set to mute the volume.                                                |

| 4'd 3     | CLK                     | Output    | Output is a buffered MCLK signal which can be used to synchronize other devices.                                                                                                                                     |

| 4'd 4     | Automute/Lock Interrupt | Output    | Output is high when the contents of register 64 have been modified (meaning that the lock_status or automute_status register have been changed). Reading register 64 will clear this interrupt.                      |

| 4'd 5     | ADC_CLK                 | Output    | Output is a buffered ADC clock signal. The ADC clock signal is defined by the adc_clk_sel register.                                                                                                                  |

| 4'd6      | Reserved                |           | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                |

| 4'd 7     | Output 1'b0             | Output    | Output is forced low                                                                                                                                                                                                 |

| 4'd 8     | Standard Input          | Input     | Places the GPIO into a high impedance state, allowing the customer to provide a digital signal and then read that signal back via the I2C register 65.                                                               |

| 4'd 9     | Input Select            | Input     | Places the GPIO into a high impedance state and allows the customer to toggle the input selection between two modes using the GPIO. See register 15 for more information.                                            |

| 4'd 10    | Mute All                | Input     | Places the GPIO into a high impedance state and allows the customer to force a mute condition by applying a logic high signal to the GPIO. When a logic low signal is applied the DAC will exhibit normal operation. |

| 4'd11     | Reserved                |           |                                                                                                                                                                                                                      |

| 4'd12     | Reserved                |           |                                                                                                                                                                                                                      |

# ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

| 4'd 13 | gpio1_cfg and gpio2_cfg | Input  | <ul> <li>gpio1_cfg: GPIO1 becomes ADC2 input</li> <li>gpio2_cfg: GPIO2 becomes ADC1 input</li> </ul>                                                                 |

|--------|-------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4'd 14 | Soft Start Complete     | Output | Output is high when the DAC output is ramped to ground. The DAC can be ramped to ground via an automute condition when appropriately programmed, or via register 14. |

| 4'd 15 | Output 1'b1             | Output | Output is forced high                                                                                                                                                |

# ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

## Register 10: Master Mode and Sync Configuration

| Bits     | [7]         | [6:5] [4]  |            | [3:0]      |

|----------|-------------|------------|------------|------------|

| Mnemonic | master_mode | master_div | 128fs_mode | lock_speed |

| Default  | 1'b0        | 2'b00      | 1'b0       | 4'd0       |

| Mnemonic    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| master_mode | Enables master mode which causes the SABRE DAC to derive the DATA_CLK and DATA1 signals when in I2S mode. Can also be enabled when in DSD mode to enable DATA_CLK only.  • 1'b1: enables master mode  • 1'b0: disables master mode (default)                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| master_div  | Sets the frame clock (DATA1) and DATA_CLK frequencies when in master mode. This register is used when in normal synchronous operation.  • 2'b00: DATA_CLK frequency = MCLK/2 (default)  • 2'b01: DATA_CLK frequency = MCLK/4  • 2'b10: DATA_CLK frequency = MCLK/8  • 2'b11: DATA_CLK frequency = MCLK/16                                                                                                                                                                                                                                                                                                                                                |  |

| 128fs_mode  | Enables operation of the DAC while in synchronous mode with a 128*FSR MCLK in PCM normal or OSF bypass mode only.  • 1'b1: enables MCLK = 128*FSR mode  • 1'b0: disables MCLK = 128*FSR mode (default)                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| lock_speed  | Sets the number of audio samples required before the DPLL and jitter eliminator lock to the incoming signal. More audio samples give a better initial estimate of the MCLK/FSR ratio at the expense of a longer locking interval.  • 4'd0: 16384 FSL edges (default) • 4'd1: 8192 FSL edges • 4'd2: 5461 FSL edges • 4'd3: 4096 FSL edges • 4'd4: 3276 FSL edges • 4'd5: 2730 FSL edges • 4'd6: 2340 FSL edges • 4'd6: 2340 FSL edges • 4'd7: 2048 FSL edges • 4'd8: 1820 FSL edges • 4'd1: 1365 FSL edges • 4'd1: 1365 FSL edges • 4'd1: 1260 FSL edges • 4'd12: 1260 FSL edges • 4'd13: 1170 FSL edges • 4'd14: 1092 FSL edges • 4'd15: 1024 FSL edges |  |

|             | master_div  128fs_mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

# ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

## Register 11: SPDIF Mux and GPIO Inversion

| Bits     | [7:4]     | [3:0]       |

|----------|-----------|-------------|

| Mnemonic | spdif_sel | invert_gpio |

| Default  | 4'd0      | 4'b0000     |

| Bit   | Mnemonic    | Description                                                                                                                                                                                                                                                                                                                                |  |  |

|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| [7:4] | spdif_sel   | Selects which input to use when decoding SPDIF data. Note: If using a GPIO the GPIO configuration must be set to an input.  4'd0: DATA_CLK (default)  4'd1: DATA1  4'd2: DATA2  4'd3: DATA3  4'd4: DATA4  4'd5: DATA5  4'd6: DATA6  4'd7: DATA7  4'd8: DATA8  4'd9: GPIO1  4'd10: GPIO2  4'd11: GPIO3  4'd12: GPIO4  4'd13-4'd15: Reserved |  |  |

| [3:0] | invert_gpio | Inverts each of the GPIO outputs when set. For example, to invert GPIO1 set invert_gpio[0] to 1'b1. GPIOs are non-inverted by default.                                                                                                                                                                                                     |  |  |

August 19, 2022 v3.7

# ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

## Register 12: Jitter Eliminator / DPLL Bandwidth

| Bits     | [7:4]          | [3:0]       |

|----------|----------------|-------------|

| Mnemonic | dpll_bw_serial | dpll_bw_dsd |

| Default  | 4'd5           | 4'd10       |

| Bit   | Mnemonic       | Description                                                      |

|-------|----------------|------------------------------------------------------------------|

|       |                | Sets the bandwidth of the DPLL when operating in I2S/SPDIF mode. |

|       |                | 4'd0: DPLL Off                                                   |

|       |                | 4'd1: Lowest Bandwidth                                           |

|       |                | • 4'd2:                                                          |

|       |                | • 4'd3:                                                          |

|       |                | • 4'd4:                                                          |

|       |                | • 4'd5: (default)                                                |

|       |                | • 4'd6:                                                          |

| [7:4] | dpll_bw_serial | • 4'd7:                                                          |

|       |                | • 4'd8:                                                          |

|       |                | • 4'd9:                                                          |

|       |                | • 4'd10:                                                         |

|       |                | • 4'd11:                                                         |

|       |                | • 4'd12:                                                         |

|       |                | • 4'd13:                                                         |

|       |                | • 4'd14:                                                         |

|       |                | 4'd15: Highest Bandwidth                                         |

|       |                | Sets the bandwidth of the DPLL when operating in DSD mode.       |

|       |                | <ul><li>4'd0: DPLL Off</li><li>4'd1: Lowest Bandwidth</li></ul>  |

|       |                | <ul><li>4'd1: Lowest Bandwidth</li><li>4'd2:</li></ul>           |

|       |                | • 4 d2.<br>• 4'd3:                                               |

|       |                | • 4'd4:                                                          |

|       |                | • 4'd5:                                                          |

|       |                | • 4'd6:                                                          |

| [3:0] | dpll_bw_dsd    | • 4'd7:                                                          |

| [0.0] | apii_bw_asa    | • 4'd8:                                                          |

|       |                | • 4'd9:                                                          |

|       |                | 4'd10: (default)                                                 |

|       |                | • 4'd11:                                                         |

|       |                | • 4'd12:                                                         |

|       |                | • 4'd13:                                                         |

|       |                | • 4'd14:                                                         |

|       |                | 4'd15: Highest Bandwidth                                         |

# ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

## Register 13: Jitter Eliminator / DPLL Configuration & THD Bypass

| Bits     | [7]           | [6]     | [5]           | [4:0]    |

|----------|---------------|---------|---------------|----------|

| Mnemonic | ns_dither_enb | thd_enb | jitterelim_en | reserved |

| Default  | 1'b0          | 1'b0    | 1'b1          | 4'd0     |

| Bit   | Mnemonic      | Description                                                                                                                                                                                                                                           |  |

|-------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [7]   | ns_dither_enb | Selects whether to enable dither in the noise shaped modulators. Dither is enabled by default and helps with maintaining the best possible performance of the modulators.                                                                             |  |

|       |               | <ul><li>1'b0: enable dither (default)</li><li>1'b1: disable dither</li></ul>                                                                                                                                                                          |  |

| [6]   | thd_enb       | Selects whether to disable the THD compensation logic. THD compensation is enabled by default and can be configured to correct for second and third harmonic distortion.  • 1'b0: enable THD compensation (default)  • 1'b1: disable THD compensation |  |

| [5]   | jitterelim_en | Enables the jitter eliminator and DPLL circuitry.  1'b0: disable jitter eliminator  1'b1: enable jitter eliminator (default)                                                                                                                          |  |

| [4:0] | reserved      |                                                                                                                                                                                                                                                       |  |

# **Register 14: Soft-Start Configuration**

| Bits     | [7]        | [6]                 | [5]      | [4:0]           |

|----------|------------|---------------------|----------|-----------------|

| Mnemonic | soft_start | soft_stop_on_unlock | reserved | soft_start_time |

| Default  | 1'b1       | 1'b0                | 1'b0     | 5'd10           |

| Bit   | Mnemonic                | Description                                                                                                                                                                                                                                                                                                                                         |

|-------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]   | soft_start              | The Sabre DAC initializes both DAC and DACB to GND, and then ramps up the signal to AVCC/2. DAC and DACB remain in phase until the ramp is complete.  Soft_start controls the ramp operation and defaults to 1'b1 (ramp to AVCC/2)  1'b0: ramps the output stream to ground  1'b1: normal operation (default) will ramp the output stream to AVCC/2 |

| [6]   | soft_stop_on<br>_unlock | Automatically ramps the output low when lock is lost  1'b0: do not force the output low on loss of lock (default)  1'b1: force output to ground on loss of lock                                                                                                                                                                                     |

| [5]   | reserved                |                                                                                                                                                                                                                                                                                                                                                     |

| [4:0] | Soft_start<br>_time     | Sets the amount of time it takes to perform a soft-start ramp. This time affects ramp to ground & ramp to AVCC/2. The value is valid from 0 to 20 (inclusive). $time (s) = 4096 * \frac{2^{(soft\_start\_time+1)}}{MCLK (Hz)}$                                                                                                                      |

# ES9028PRO 32-Bit HyperStream® II 8-Channel Audio DAC

## Register 15: GPIO Input Selection & Volume Configuration

| Bits     | [7:6]     | [5:4]     | [3]      | [2]         | [1]     | [0]       |

|----------|-----------|-----------|----------|-------------|---------|-----------|

| Mnemonic | gpio_sel2 | gpio_sel1 | reserved | stereo_mode | ch1_vol | latch_vol |

| Default  | 2'b00     | 2'b00     | 1'b1     | 1'b0        | 1'b0    | 1'b1      |

| Bit   | Mnemonic    | Description                                                                                                                                                                                                                                                                                                                                                        |

|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|