# 32-bit Stereo Low Power Audio DAC

**Datasheet**

The **ES9018K2M SABRE**<sup>32</sup> **Reference DAC** is a high-performance 32-bit, 2-channel audio D/A converter targeted for audiophile-grade portable power sensitive applications such as digital music players, consumer applications such as Blu-ray players, audio pre-amplifiers and A/V receivers, as well as professional applications such as recording systems, mixer consoles and digital audio workstations.

Using the critically acclaimed ESS patented 32-bit HyperStream™ DAC architecture, SABRE SOUND® technology, and Time Domain Jitter Eliminator, the *ES9018K2M SABRE*<sup>32</sup> *Reference DAC* delivers a DNR of up to 127dB and THD+N of –120dB, a performance level that will satisfy the most demanding audio enthusiasts.

The **ES9018K2M SABRE**<sup>32</sup> **Reference DAC**'s 32-bit HyperStream™ architecture can handle up to 32-bit, 384kHz PCM data via I<sup>2</sup>S, DSD-11.2MHz data as well as mono mode for highest performance applications. Both synchronous and ASRC (asynchronous sample rate conversion) modes are supported.

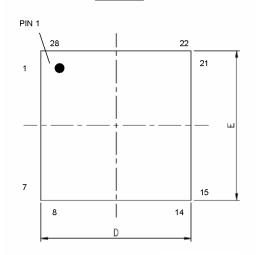

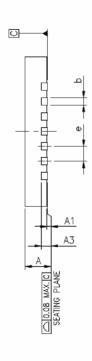

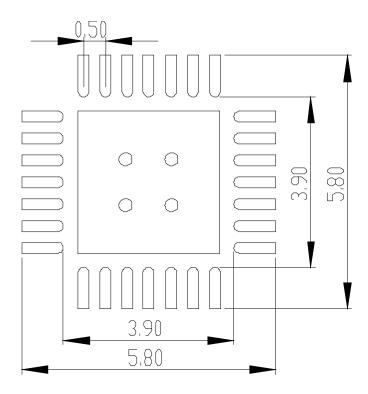

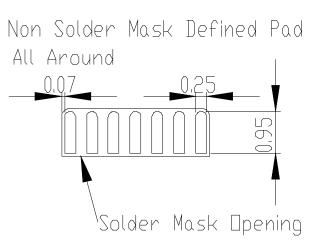

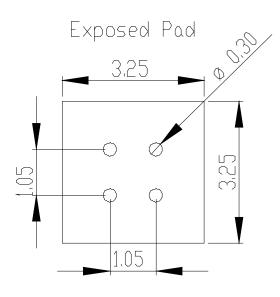

The **ES9018K2M SABRE**<sup>32</sup> **Reference DAC** comes in 28-QFN package and typically consumes 52mW in normal operating mode (< 1mW in standby mode).

The **ES9018K2M SABRE**<sup>32</sup> **Reference DAC** sets the standard for HD audio performance, in an easy-to-use form factor for today's most demanding digital-audio applications.

| FEATURE                                                        | DESCRIPTION                                                                                                                                                                                                                 |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Patented 32-bit HyperStream™ DAC                               | <ul> <li>Industry's highest performance 32-bit mobile audio DAC with unprecedented dynamic range and ultra-low distortion</li> <li>Supports both synchronous and ASRC (asynchronous sample rate converter) modes</li> </ul> |

| Patented Time Domain Jitter Eliminator SABRE SOUND® technology | <ul><li>Unmatched audio clarity free from input clock jitter</li><li>HD Audio Performance</li></ul>                                                                                                                         |

| 64-bit accumulator and 32-bit processing                       | <ul> <li>Distortion free signal processing</li> </ul>                                                                                                                                                                       |

| Integrated DSP Functions                                       | <ul> <li>Click-free soft mute and volume control</li> <li>Programmable Zero detect</li> <li>De-emphasis for 32kHz, 44.1kHz, and 48kHz sampling</li> </ul>                                                                   |

| Customizable output configuration                              | <ul> <li>Mono or stereo output in current or voltage mode based on<br/>performance criterion</li> </ul>                                                                                                                     |

| I <sup>2</sup> C control                                       | <ul> <li>Allows software control of DAC features</li> </ul>                                                                                                                                                                 |

| 28-QFN (5mm x 5mm) package                                     | o Minimizes PCB footprint                                                                                                                                                                                                   |

| 52mW typical operating power < 1mW standby power               | Maximizes battery life                                                                                                                                                                                                      |

| Versatile digital input                                        | <ul> <li>Supports SPDIF, PCM (I<sup>2</sup>S, LJ 16-32-bit) or DSD input</li> </ul>                                                                                                                                         |

| Customizable filter characteristics                            | <ul><li>User-programmable filter allowing custom roll-off response</li><li>By-passable oversampling filter</li></ul>                                                                                                        |

#### **APPLICATIONS**

- Mobile phones / Tablets / Digital music players / Portable multimedia players

- Blu-ray / SACD / DVD-Audio player

- Audio preamplifier and A/V receiver

- Professional audio recording systems / Mixing consoles / Digital audio workstation

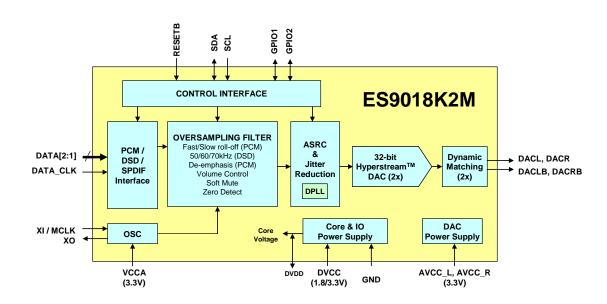

#### **FUNCTIONAL BLOCK DIAGRAM**

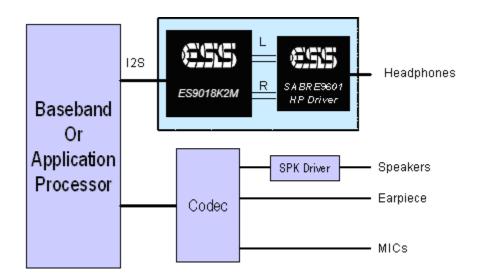

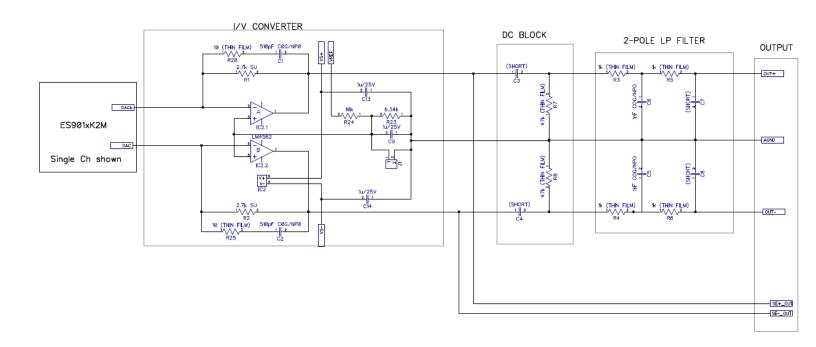

## TYPICAL APPLICATION DIAGRAM

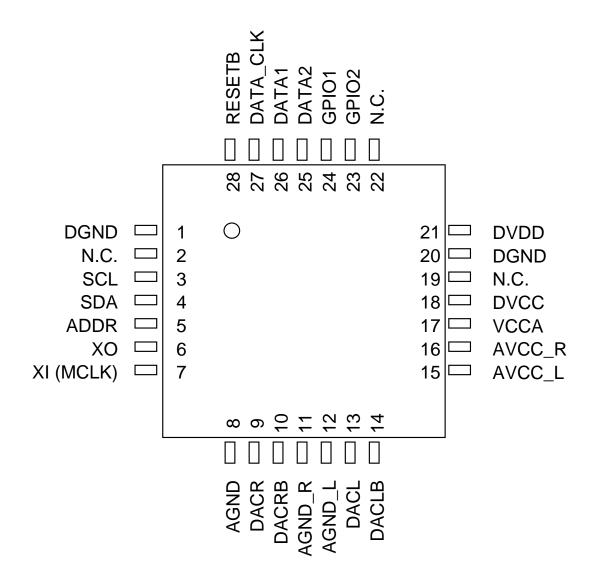

#### **PIN LAYOUT**

#### **PIN DESCRIPTIONS**

| Pin            | Name      | Pin Type                          | Reset<br>State   | Pin Description                                                                                                                                                                                                                                                                                        |  |  |

|----------------|-----------|-----------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1              | DGND      | Ground                            | Ground           | Digital Ground                                                                                                                                                                                                                                                                                         |  |  |

| 2              | N.C.      | -                                 | -                | No internal connection. Pin may be grounded if desired.                                                                                                                                                                                                                                                |  |  |

| 3              | SCL       | I                                 | Tri-stated       | I <sup>2</sup> C Serial Clock Input                                                                                                                                                                                                                                                                    |  |  |

| 4              | SDA       | I/O                               | Tri-stated       | I <sup>2</sup> C Serial Data Input / Output                                                                                                                                                                                                                                                            |  |  |

| 5              | ADDR      | I                                 | Tri-stated       | I <sup>2</sup> C Address Select                                                                                                                                                                                                                                                                        |  |  |

| 6              | XO        | AO                                | Floating         | XTAL Output                                                                                                                                                                                                                                                                                            |  |  |

| 7              | XI (MCLK) | Al                                | Floating         | XTAL / MCLK Input                                                                                                                                                                                                                                                                                      |  |  |

| 8              | AGND      | Ground                            | Ground           | Analog Ground                                                                                                                                                                                                                                                                                          |  |  |

| 9              | DACR      | AO                                | Driven to ground | Differential Positive Analog Output Right                                                                                                                                                                                                                                                              |  |  |

| 10             | DACRB     | AO                                | Driven to ground | Differential Negative Analog Output Right                                                                                                                                                                                                                                                              |  |  |

| 11             | AGND_R    | Ground                            | Ground           | Analog Ground                                                                                                                                                                                                                                                                                          |  |  |

| 12             | AGND_L    | Ground                            | Ground           | Analog Ground                                                                                                                                                                                                                                                                                          |  |  |

| 13             | DACL      | AO                                | Driven to ground | Differential Positive Analog Output Left                                                                                                                                                                                                                                                               |  |  |

| 14             | DACLB     | AO                                | Driven to ground | Differential Negative Analog Output Left                                                                                                                                                                                                                                                               |  |  |

| 15             | AVCC_L    | Power                             | Power            | Analog AVCC for Left Channel                                                                                                                                                                                                                                                                           |  |  |

| 16             | AVCC_R    | Power                             | Power            | Analog AVCC for Right Channel                                                                                                                                                                                                                                                                          |  |  |

| 17             | VCCA      | Power                             | Power            | Analog +3.3V for OSC                                                                                                                                                                                                                                                                                   |  |  |

| 18             | DVCC      | Power                             | Power            | Digital +1.8V to +3.3V                                                                                                                                                                                                                                                                                 |  |  |

| 19             | N.C.      | -                                 | -                | No internal connection. Pin may be grounded if desired.                                                                                                                                                                                                                                                |  |  |

| 20             | DGND      | Ground                            | Ground           | Digital Ground. Internally connected to the Exposed Pad.                                                                                                                                                                                                                                               |  |  |

| 21             | DVDD      | Power<br>(Internal /<br>External) | Power            | Digital Core Voltage, nominally +1.2V, is supplied by a regulator from DVCC. DVDD must be decoupled with a minimum 2.2μF capacitor to DGND. DVDD needs to be externally supplied for high XI / MCLK frequency. Please refer to the section about the DVDD supply on page 7 for additional information. |  |  |

| 22             | N.C.      | -                                 | -                | No internal connection. Pin may be grounded if desired.                                                                                                                                                                                                                                                |  |  |

| 23             | GPIO2     | I/O                               | Tri-stated       | GPIO 2                                                                                                                                                                                                                                                                                                 |  |  |

| 24             | GPIO1     | I/O                               | Tri-stated       | GPIO 1                                                                                                                                                                                                                                                                                                 |  |  |

| 25             | DATA2     | 1                                 | Tri-stated       | DSD Data2 I or PCM Data CH1/CH2 or SPDIF Input 2                                                                                                                                                                                                                                                       |  |  |

| 26             | DATA1     | I/O                               | Tri-stated       | Master mode off: Input for DSD Data1 (L) or PCM Frame Clock or SPDIF Input 3 Master mode on: Output for PCM Frame Clock                                                                                                                                                                                |  |  |

| 27             | DATA_CLK  | I/O                               | Tri-stated       | Master mode off: Input for PCM Bit Clock OR DSD Bit Clock OR SPDIF Input 1 Master mode on: Output for PCM Bit Clock                                                                                                                                                                                    |  |  |

| 28             | RESETB    | I                                 | Tri-stated       | Master Reset / Power Down (active low)                                                                                                                                                                                                                                                                 |  |  |

| Exposed<br>Pad | DGND      | Ground                            | Ground           | The exposed pad must be connected to Digital Ground                                                                                                                                                                                                                                                    |  |  |

#### Notes:

- There are 3 N.C. (No Connect) pins. If desired, these pins can be connected to ground on the PCB to strengthen the otherwise isolated pin pads. Alternatively the N.C. pins can be used to route signals to simplify PCB layout.

- The exposed pad must be connected to digital ground.

#### **FUNCTIONAL DESCRIPTION**

#### **NOTATATIONS for Sampling Rates**

| Mode                         | fs (target sample rate) | FSR (raw sample rate) |  |  |

|------------------------------|-------------------------|-----------------------|--|--|

| DSD                          | DATA_CLK / 64           | DSD data rate         |  |  |

| Serial (PCM) Normal Mode     | Frame Clock Rate        | Frame Clock Rate      |  |  |

| Serial (PCM) OSF Bypass Mode | Frame Clock Rate / 8    | Frame Clock Rate      |  |  |

| SPDIF                        | SPDIF Sampling Rate     | SPDIF Sampling Rate   |  |  |

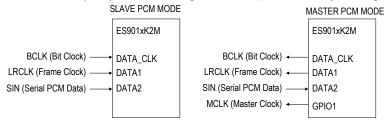

#### PCM, SPDIF and DSD Pin Connections

#### **PCM Audio Format**

**Notes:**

XI clock (MCLK) must be > 192 x FSR when using PCM input (normal mode), or 128 x FSR (synchronous MCLK). XI clock (MCLK) must be > 24 x FSR when using PCM input (OSF bypass mode).

| Pin Name | Description                    |

|----------|--------------------------------|

| DATA1    | Frame clock                    |

| DATA2    | 2-channel PCM serial data      |

| DATA CLK | Bit clock for PCM audio format |

#### Master Mode (32-bit data only)

When Register #1 'input\_select' is set to 2'd0 (I<sup>2</sup>S) and 'i2s\_length' is set to 2'd2 (32-bit), the DAC can become a master for Bit Clock and Frame Clock by setting Register #9 'master clock enable' to 1'b1. The Bit Clock frequency can be configured to MCLK / 4, MCLK / 8 or MCLK / 16 by setting Register #9 'clock divider select' to 2'b00, 2'b01 or 2'b10. GPIO 1 (or 2) can be configured to output MCLK by setting Register #8 gpio1\_cfg (or gpio2\_cfg) to 4'd3.

#### **SPDIF Audio Formant**

Note: XI clock (MCLK) must be > 386 x FSR when using SPDIF input.

Up to 5 SPDIF inputs can be connected to the 5-to-1 mux, selectable via register "spdif\_sel".

| Pin Name | Description   |

|----------|---------------|

| GPIO2    | SPDIF input 5 |

| GPIO1    | SPDIF input 4 |

| DATA1    | SPDIF input 3 |

| DATA2    | SPDIF input 2 |

| DATA CLK | SPDIF input 1 |

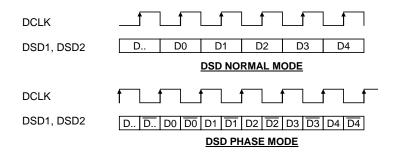

#### **DSD Audio Format**

Note: XI clock (MCLK) must be > 3 x FSR when using DSD input.

| Pin Name  | Description                  |

|-----------|------------------------------|

| DATA[1:2] | 2-channel DSD data input     |

| DATA CLK  | Bit clock for DSD data input |

#### FEATURE DESCRIPTIONS

#### Soft Mute

When Mute is asserted the output signal will ramp to the  $-\infty$  level. When Mute is reset the attenuation level will ramp back up to the previous level set by the volume control register. Asserting Mute will not change the value of the volume control register. The ramp rate is  $0.0078125 \text{ x fs} / 2^{(\text{vol\_rate-5})} \text{ dB/s}$ .

#### **Automute**

During an automute condition the ramping of the volume of each DAC to  $-\infty$  can now be programmatically enabled or disabled.

- In PCM serial mode, "AUTOMUTE" will become active once the audio data is continuously below the threshold set by

Register Automute lev>, for a length of time defined by 2096896 / (<Register#4> x 64 x fs) Seconds.

- o In SPDIF mode, "AUTOMUTE" will become active once the audio data is continuously below the threshold set by <Register Automute lev>, for a length of time defined by 2096896 / (<Register#4> x 64 x fs Seconds.

- o In the DSD Mode, "AUTOMUTE" will become active when any 8 consecutive values in the DSD stream have as many 1's and 0's for a length of time defined by 2096896 / (<Register Automute\_time> x DATA\_CLK) seconds. The following table summarizes the conditions.

| Mode  | Detection Condition                                                      | Time                                                            |

|-------|--------------------------------------------------------------------------|-----------------------------------------------------------------|

| PCM   | Data is continuously lower than<br><register automute_lev=""></register> | 2096896 / ( <register automute_time=""> x 64 x fs)</register>   |

| SPDIF | Data is continuously lower than<br><register automute_lev=""></register> | 2096896 / ( <register automute_time=""> x (64 x fs))</register> |

| DSD   | Equal number of 1s and 0s in every 8 bits of data                        | 2096896 / ( <register automute_time=""> x DATA_CLK)</register>  |

#### **Volume Control**

Each output channel has its own attenuation circuit. The attenuation for each channel is controlled independently. Each channel can be attenuated from 0dB to -127dB in 0.5dB steps.

Each 0.5dB step transition takes up to 64 intermediate levels, depending on the vol\_rate register setting. The result being that the level changes are done using small enough steps so that no switching noise occurs during the transition of the volume control. When a new volume level is set, the attenuation circuit will ramp softly to the new level.

#### **Master Trim**

The master trim sets the 0dB reference level for the volume control of each DAC. The master trim is programmable via registers 17-20 and is a 32bit signed number. Therefore it should never exceed 32'h7FFFFFFF (as this is full-scale signed).

#### All Mono Mode

An all mono mode is supported where all DACs are driven from the same source. This can be useful for high-end audio applications. The source data for all DACs can be programmatically configured to be either CH1 or CH2.

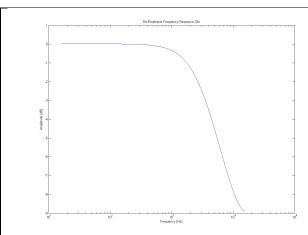

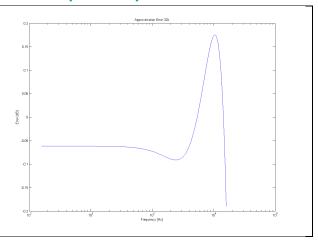

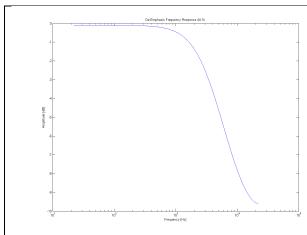

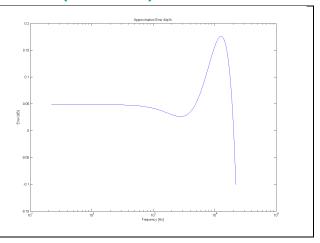

#### **De-emphasis**

The de-emphasis feature is included for audio data that has utilized the  $50/15\mu s$  pre-emphasis for noise reduction. There are three de-emphasis filters, one for 32kHz, one for 44.1kHz, and one for 48kHz.

#### **SPDIF Data Select**

An SPDIF source multiplexer allows for up to five SPDIF sources to be connected to the data pins. An internal programmable register (spdif\_sel) is used to select the appropriate data pin to decode.

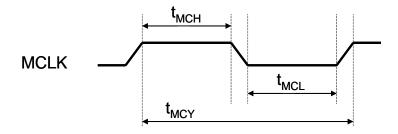

#### System Clock (XI / MCLK)

A system clock is required for proper operation of the digital filters and modulation circuitry. See p.30, Note 2 for the maximum MCLK frequencies supported. The minimum system clock frequency must also satisfy:

| Data Type                                              | Minimum MCLK Frequency                                | Note                     |  |  |

|--------------------------------------------------------|-------------------------------------------------------|--------------------------|--|--|

| DSD Data                                               | MCLK > 3 x FSR , FSR = 2.8224MHz (x 1, 2 or 4)        | The maximum FSR          |  |  |

|                                                        | MCLK > 192 x FSR, FSR ≤ 384kHz                        | frequency is further     |  |  |

| Serial Normal Mode                                     | or                                                    | limited by the maximum   |  |  |

|                                                        | MCLK = 128 x FSR (synchronous MCLK) with FSR ≤ 384kHz | MCLK frequencies         |  |  |

| Serial OSF Bypass Mode MCLK > 24 x FSR, FSR ≤ 1.536MHz |                                                       | supported as shown p.30, |  |  |

| SPDIF Data                                             | MCLK > 386 x FSR, FSR ≤ 200kHz                        | Note 2.                  |  |  |

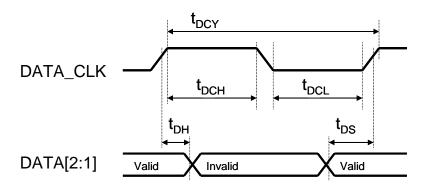

#### Data Clock

DATA\_CLOCK must be (2 x i2s\_length) x FSR for SERIAL, and FSR for DSD modes. For SPDIF mode, this pin is used for SPDIF input. This pin should be pulled low if not used.

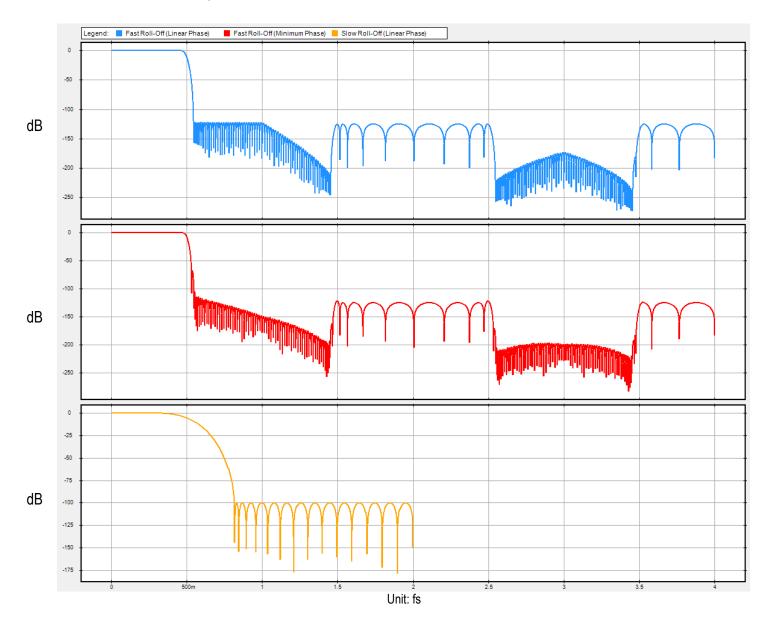

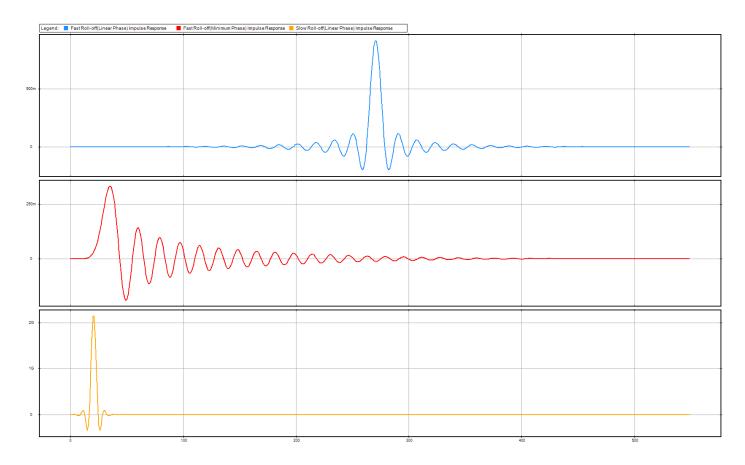

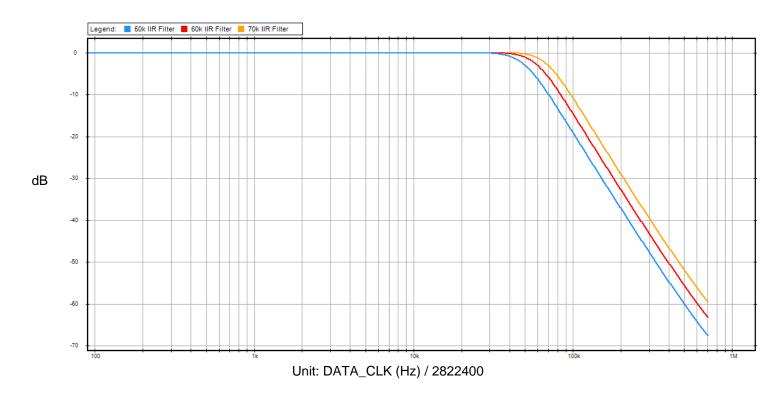

#### **Built-in Digital Filters**

Three digital filters (fast roll-off, slow roll-off filters and minimum phase filter) are included for PCM data. See 'PCM Filter Characteristics' for more information.

#### **Standby Mode**

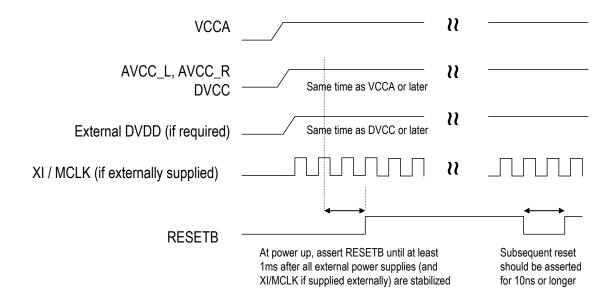

For lowest power consumption the followings should be performed to enter stand-by mode:

- Set the soft\_start bit in register 14 to 1'b0 to ramp the DAC outputs (DACL, DACLB, DACR, DACRB) to ground.

- RESETB pin should be brought to low digital level to:

- Shut off the DACs, Oscillator and internal regulator.

- Force digital I/O pins (DATA\_CLK, DATA1, GPIO1, GPIO2, SDA) into tri-state mode

- Reset all registers to default states

- If XI/MCLK is supplied externally, it should be stopped at logic low level

- If DVDD is supplied by an external regulator, it should be shut down during standby.

To resume from standby mode, bring RESETB to high digital level and reinitialize all registers.

#### **DVDD Supply**

The ES9018K2M is equipped with a regulated DVDD supply powered from DVCC. The internal DVDD regulator must be decoupled to DGND with a capacitor that maintains a minimum value of  $1\mu F$  at 1.2V over the target operating temperature range. The recommended capacitor for decoupling DVDD is a 2.2 $\mu F$  ±20%, X5R 6.3V 0402, e.g. TDK part number C1005X5R0J225M050BC or similar.

- The internal DVDD should be used except under the following conditions: PCM (SPDIF, I<sup>2</sup>S with OSF Bypass off or on): MCLK > 50MHz or FSR > 192kHz DSD: MCLK > 50MHz or FSR > 11.2MHz

- Internal DVDD may be used up to the maximum supported MCLK frequencies specified on p.29, Note 2. An External DVDD (+1.3V) supply must be used above those frequencies. The external supply voltage must be greater than the internal supply of +1.2V so the internal supply is disabled.

#### Programmable FIR filter

A two stage interpolating FIR design is used. The interpolating FIR filter is generated using MATLAB, and can then be downloaded using a custom C code.

Example Source Code for Loading a Filter

```

// only accept 128 or 16 coefficients

// Note: The coefficients must be quantized to 24 bits for this method!

Stage 1 consists of 128 values (0-127 being the coefficients)

Stage 2 consists of 16 values (0-13 being the coefficients, 14-15 are zeros)

// Note: Stage 2 is symmetric about coefficient 13. See the example filters for more information.

byte reg26 = (byte)(coeffs.Count == 128 ? 0 : 128);

for (int i = 0; i < coeffs.Count; i++)</pre>

{

// stage 1 contains 128 coefficients, while stage 2 contains 16 coefficients

registers.WriteRegister(26, (byte)(reg26 + i));

// write the coefficient data

registers.WriteRegister(27, (byte)(coeffs[i] & 0xff));

registers.WriteRegister(28, (byte)((coeffs[i] >> 8) & 0xff));

registers.WriteRegister(29, (byte)((coeffs[i] >> 16) & 0xff));

registers.WriteRegister(30, 0x02); // set the write enable bit

// disable the write enable bit when'we're done

registers.WriteRegister(30, (byte)(setEvenBit ? 0x04 : 0x00));

```

#### **OSF Bypass**

The oversampling FIR filter can be bypassed, sourcing data directly into the IIR filter. ESS recommends using 8 x FSR as the input. For example, an external signal at 44.1kHz can be oversampled externally to 8 x 44.1kHz = 352.8kHz and then applied to the serial decoder in either I<sup>2</sup>S or LJ format. The maximum sample rate that can be applied is 1.536MHz (8 x 192kHz).

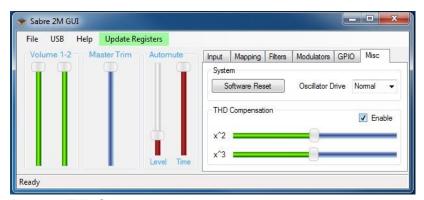

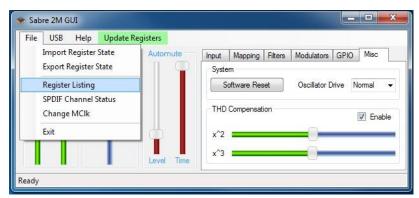

#### **THD Compensation**

THD Compensation removes the non-linearity of the DAC resistors and to a lesser degree the non-linearity of passive components in the output stage. Taking the I-V characteristic curve of a real resistor you will notice that it as a slight downward curvature. As more current flows, more power dissipates the resistor heats and the resistance rises.

Non-linearity of the DAC output resistors can lead to output distortion in two ways:

- Amplitude modulation of the output current from the DAC

- Gain modulation of the output stage as the output impedance of the DAC swings with the audio signal

The ES9018K2M includes models for its output resistors and can compensate for their characteristic curve by finely adjusting the DAC codes for large and small signal amplitudes.

THD Compensation is effective if the base THD+N measurement with no compensation is less than approximately 70dBr. If your system performs worse than this, check for other errors with the circuit before applying the THD Compensation.

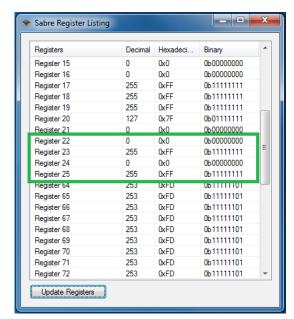

Registers #13, and #22 to #25 are used for THD Compensation.

## **Audio Interface Formats**

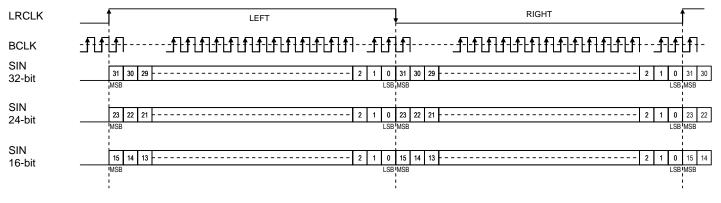

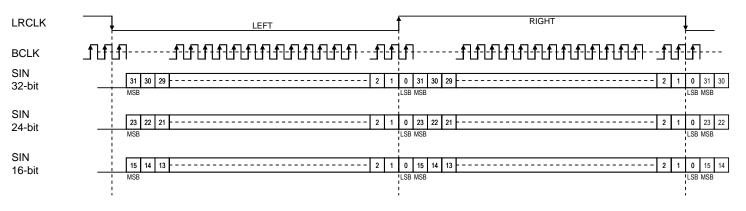

Several interface formats are provided so that direct connection to common audio processors is possible. The available formats are shown in the following diagrams. The audio interface format can be set by programming the registers.

#### **LEFT JUSTIFIED FORMAT**

**12S FORMAT**

Notes: for Left-Justified and I<sup>2</sup>S formats, the following number of BCLKs is present per (left plus right) frame:

16-bit mode: 32 BCLKs24-bit mode: 48 BCLKs

32-bit mode: 64 BCLKs

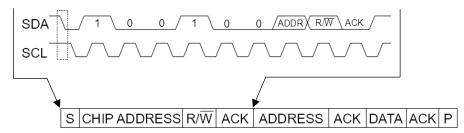

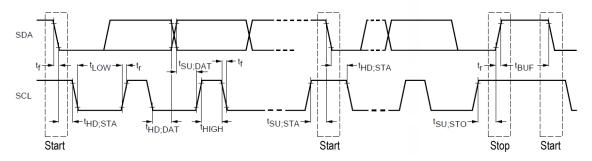

## **SERIAL CONTROL INTERFACE**

The registers inside the chip are programmed via an I<sup>2</sup>C interface. The diagram below shows the timing for this interface. The chip address can be set to 2 different settings via the "ADDR" pin. The table below summarizes this.

| ADDR | CHIP ADDRESS |  |  |  |  |  |

|------|--------------|--|--|--|--|--|

| 0    | 0x90         |  |  |  |  |  |

| 1    | 0x92         |  |  |  |  |  |

#### Notes:

- 1. The "ADDR" pin is used to create the CHIP ADDRESS. (0x90, 0x92)

- 2. The first byte after the chip address is the "ADDRESS" this is the register address.

- 3. The second byte after the CHIP ADDRESS is the "DATA" this is the data to be programmed into the register at the previous "ADDRESS".

| Parameter                           | Symbol              | Standard-Mode |      | Fast-Mode |     | Unit |

|-------------------------------------|---------------------|---------------|------|-----------|-----|------|

|                                     |                     | MIN           | MAX  | MIN       | MAX |      |

| SCL Clock Frequency                 | fscL                | 0             | 100  | 0         | 400 | kHz  |

| START condition hold time           | t <sub>HD,STA</sub> | 4.0           | -    | 0.6       | -   | μS   |

| LOW period of SCL                   | t <sub>LOW</sub>    | 4.7           | -    | 1.3       | -   | μS   |

| HIGH period of SCL                  | t <sub>HIGH</sub>   | 4.0           | -    | 0.6       | -   | μS   |

| START condition setup time (repeat) | tsu,sta             | 4.7           | -    | 0.6       | -   | μS   |

| SDA hold time from SCL falling      | t <sub>HD,DAT</sub> | 0.3           | -    | 0.3       | -   | μs   |

| SDA setup time from SCL rising      | t <sub>SU,DAT</sub> | 250           | -    | 100       | -   | ns   |

| Rise time of SDA and SCL            | t <sub>r</sub>      | -             | 1000 |           | 300 | ns   |

| Fall time of SDA and SCL            | t <sub>f</sub>      | -             | 300  |           | 300 | ns   |

| STOP condition setup time           | t <sub>su,sto</sub> | 4             | -    | 0.6       | -   | μs   |

| Bus free time between transmissions | t <sub>BUF</sub>    | 4.7           | -    | 1.3       | -   | μS   |

| Capacitive load for each bus line   | Сь                  | -             | 400  | -         | 400 | pF   |

April 22, 2021

# **ES9018K2M Datasheet**

## **REGISTER MAP**

| Address    | Register                                  | D7 (MSB)                                | D6                         | D5                      | D4        | D3                 | D2                   | D1                 | D0 (LSB)          |  |

|------------|-------------------------------------------|-----------------------------------------|----------------------------|-------------------------|-----------|--------------------|----------------------|--------------------|-------------------|--|

| (Dec/Hex)  |                                           | ()                                      |                            |                         |           |                    |                      |                    | ()                |  |

| Read/Write | OVOTEM OFTTIMO                            | OSC DRV                                 |                            |                         |           |                    |                      |                    |                   |  |

| 0 / 0x00   | SYSTEM SETTINGS<br>INPUT                  |                                         | OSC_DRV RESERVED SOFT_RESE |                         |           |                    |                      |                    |                   |  |

| 1 / 0x01   | CONFIGURATION                             | I2S_LE                                  | NGTH                       |                         |           |                    |                      |                    |                   |  |

| 2 / 0x02   | RESERVED                                  |                                         |                            |                         |           | SERVED             |                      |                    |                   |  |

| 3 / 0x03   | RESERVED                                  |                                         |                            |                         |           | SERVED             |                      |                    |                   |  |

| 4 / 0x04   | AUTOMUTE _TIME                            |                                         |                            |                         | AUTO      | MUTE_TIME          |                      |                    |                   |  |

| 5 / 0x05   | AUTOMUTE<br>_LEVEL                        | AUTOMUTE_<br>LOOPBACK                   |                            |                         |           | AUTOMUTE_LEV       | EL                   |                    |                   |  |

| 6 / 0x06   | SOFT VOLUME<br>CONTROL 3 &<br>DE-EMPHASIS | SPDIF_AUTO<br>_DEEMPH                   | DEEMPH<br>_BYPASS          | DEEMF                   | PH_SEL    | RESERVED           |                      | VOL_RATE           |                   |  |

| 7 / 0x07   | GENERAL<br>SETTINGS                       | RESERVED                                | FILTER_                    | SHAPE                   | RESERVED  | IIR_               | WR                   | N                  | IUTE              |  |

| 8 / 0x08   | GPIO<br>CONFIGURATION                     |                                         | GPI02_0                    | CFG                     |           |                    | GPIO1_               | _CFG               |                   |  |

| 9 / 0x09   | RESERVED                                  |                                         |                            |                         | RESERVED  | FOR REVISION V     |                      |                    |                   |  |

|            | MASTER MODE                               | MASTER CLK                              | 01 0 01 ( B)) ((B          |                         | SYNC_     | 1                  | 0700                 | D0.4               |                   |  |

| 10 / 0x0A  | CONTROL                                   | _ENABLE                                 | CLOCK_DIVID                | EK_SELECT               | MODE      | <u> </u>           | STOP_                | _טוע               |                   |  |

| 11 / 0x0B  | CHANNEL<br>MAPPING                        | RESERVED                                |                            | SPDIF_SEL               |           | CH2_ANALOG<br>SWAP | CH1_ANALOG<br>SWAP   | CH2_SEL            | CH1_SEL           |  |

| 12 / 0x0C  | DPLL/ASRC<br>SETTINGS                     |                                         | DPLL_BW                    |                         |           |                    |                      |                    |                   |  |

| 13 / 0x0D  | THD<br>COMPENSATION                       | RESERVED                                | BYPASS_THD                 | RESERVED                |           |                    |                      |                    |                   |  |

| 14 / 0x0E  | SOFT START<br>SETTINGS                    | SOFT_START                              | SOFT_START<br>ON LOCK      | MUTE_ON SOFT_START_TIME |           |                    |                      |                    |                   |  |

| 15 / 0x0F  | VOLUME 1                                  |                                         |                            | _                       | VO        | LUME 1             |                      |                    |                   |  |

| 16 / 0x10  | VOLUME 2                                  |                                         |                            |                         | VO        | LUME 2             |                      |                    |                   |  |

| 17 / 0x11  |                                           |                                         |                            |                         |           |                    |                      |                    |                   |  |

| 18 / 0x12  | MACTED TOIM                               |                                         |                            |                         | MAC       | TED TOIM           |                      |                    |                   |  |

| 19 / 0x13  | MASTER TRIM                               |                                         |                            |                         | IVIAS     | TER_TRIM           |                      |                    |                   |  |

| 20 / 0x14  |                                           |                                         |                            |                         |           |                    |                      |                    |                   |  |

| 21 / 0x15  | GPIO INPUT<br>SELECTION & OSF<br>BYPASS   | GPIO_INP                                | UT_SEL2                    | GPIO_INF                | PUT_SEL1  | RESERVED           | BYPASS_IIR           | RESERVED           | BYPASS_OSF        |  |

| 22 / 0x16  | 2ND HARMONIC                              |                                         |                            |                         |           |                    |                      |                    |                   |  |

| 23 / 0x17  | COMPENSATION<br>COEFFICIENTS              |                                         |                            |                         | THD_      | _COMP_C2           |                      |                    |                   |  |

| 24 / 0x18  | 3RD HARMONIC                              |                                         |                            |                         |           |                    |                      | _                  |                   |  |

| 25 / 0x19  | COMPENSATION COEFFICIENTS                 |                                         |                            |                         | THD_      | COMP_C3            |                      |                    |                   |  |

| 26 / 0x1A  | PROGRAMMABLE<br>FILTER ADDRESS            | PROG_COEFF<br>_STAGE                    |                            |                         |           | PROG_COEFF_AD      | DDR                  |                    |                   |  |

| 27 / 0x1B  | PROGRAMMABLE                              |                                         |                            |                         |           |                    |                      | _                  |                   |  |

| 28 / 0x1C  | FILTER                                    |                                         |                            |                         | PRO       | G_COEFF            |                      |                    |                   |  |

| 29 / 0x1D  | COEFFICIENT                               |                                         |                            |                         |           |                    |                      |                    |                   |  |

| 30 / 0x1E  | PROGRAMMABLE<br>FILTER CONTROL            |                                         |                            | RESERVED                |           |                    | EVEN_STAGE2<br>COEFF | PROG_<br>COEFF WE  | PROG_<br>COEFF EN |  |

| Read Only  |                                           |                                         |                            |                         |           |                    |                      | _                  | _                 |  |

| 64 / 0x40  | CHIP STATUS                               | RESER                                   | RVED                       | REVISION                |           | CHIP_ID            |                      | AUTOMUTE<br>STATUS | LOCK_STATUS       |  |

| 65 / 0x41  | GPIO STATUS                               |                                         |                            | RESE                    | ERVED     |                    |                      |                    | O_I[1:0]          |  |

| 66 / 0x42  | 55 51/1100                                |                                         |                            | i i i                   |           |                    |                      | , 311              |                   |  |

| 67 / 0x43  |                                           |                                         |                            |                         |           |                    |                      |                    |                   |  |

| 68 / 0x44  | DPLL RATIO                                |                                         |                            | DPLL_NUM                |           |                    |                      |                    |                   |  |

| 69 / 0x45  |                                           |                                         |                            |                         |           |                    |                      |                    |                   |  |

| 70-93 /    | 011441151 0747:::                         | 00015 011111111111111111111111111111111 |                            |                         |           |                    |                      |                    |                   |  |

| 0x46-0x5D  | CHANNEL STATUS                            |                                         |                            |                         | SPDIF CHA | ANNEL STATUS       |                      |                    |                   |  |

|            |                                           |                                         |                            |                         |           |                    |                      |                    |                   |  |

#### **REGISTER SETTINGS**

## Register #0: System Settings

8 bit, Read-Write Register, Default = 0x00

| Bits     | [7] [6] [5] [4] |  |  | [3] [2] [1] |   |   | [0]        |   |

|----------|-----------------|--|--|-------------|---|---|------------|---|

| Mnemonic | osc_drv         |  |  | reserved *  |   |   | soft_reset |   |

| Default  | 0 0 0 0         |  |  | 0           | 0 | 0 | 0          | 0 |

| Bit   | Mnemonic   | Description                                                                                                                                                                                                                                                           |

|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:4] | osc_drv    | Oscillator drive specifies the bias current to the oscillator pad.  4'b0000: full bias (default)  4'b1000: 3/4 bias  4'b1100: 1/2 bias  4'b1110: 1/4 bias  4'b1111: shut down the oscillator  Other settings: reserved  It is recommended to use the default setting. |

| [3:1] | reserved * |                                                                                                                                                                                                                                                                       |

| [0]   | soft_reset | 1'b1 resets chip<br>1'b0 is normal operation (default)                                                                                                                                                                                                                |

<sup>\*</sup> All Reserved Bits in Register #0 must be set to the indicated logic level to ensure correct device operation.

## **Register #1: Input Configuration**

8 bit, Read-Write Register, Default = 0x8C

| Bits     | [7]    | [6]   | [5]   | [4]  | [3]      | [2]       | [1]    | [0]    |

|----------|--------|-------|-------|------|----------|-----------|--------|--------|

| Mnemonic | i2s_le | ength | i2s_r | node | auto_inp | ut_select | input_ | select |

| Default  | 1      | 0     | 0     | 0    | 1        | 1         | 0      | 0      |

| Bit   | Mnemonic          | Description                                     |

|-------|-------------------|-------------------------------------------------|

|       |                   | 2'd0 = 16bit                                    |

| [7:6] | i2s_length        | 2'd1 = 24bit                                    |

|       |                   | 2'd2 or 2'd3 = 32bit (default)                  |

|       |                   | 2'd0 = I <sup>2</sup> S (default)               |

| [5:4] |                   | 2'd1 = LJ mode                                  |

|       |                   | 2'd2 = I <sup>2</sup> S                         |

|       |                   | 2'd3 = LJ mode                                  |

|       |                   | 2'd0 = input select                             |

| [3:2] | auto input coloct | $2'd1 = I^2S$ or DSD                            |

| [3.2] | auto_input_select | 2'd2 = I <sup>2</sup> S or SPDIF                |

|       |                   | 2'd3 = I <sup>2</sup> S, SPDIF or DSD (default) |

|       |                   | 2'd0 = I <sup>2</sup> S (default)               |

| [1:0] | input coloct      | 2'd1 = SPDIF                                    |

| [1.0] | input_select      | 2'd2 = reserved                                 |

|       |                   | 2'd3 = DSD                                      |

# Register #2: Reserved

8 bit, Read-Write Register, Default = 0x18

| Bits     | [7] | [6] | [5] | [4]  | [3]   | [2] | [1] | [0] |

|----------|-----|-----|-----|------|-------|-----|-----|-----|

| Mnemonic |     |     |     | Rese | erved |     |     |     |

| Default  | 0   | 0   | 0   | 1    | 1     | 0   | 0   | 0   |

## Register #3: Reserved

8 bit, Read-Write Register, Default = 0x10

| o bit, rtoda vvi | 110 11 | ogiot | 01, 0 | oraar | - 07  |     |     |     |

|------------------|--------|-------|-------|-------|-------|-----|-----|-----|

| Bits             | [7]    | [6]   | [5]   | [4]   | [3]   | [2] | [1] | [0] |

| Mnemonic         |        |       |       | Rese  | erved |     |     |     |

| Default          | 0      | 0     | 0     | 1     | 0     | 0   | 0   | 0   |

## Register #4: Soft Volume Control 1 (Automute Time)

8 bit, Read-Write Register, Default = 0x00

| Bits     | [7] | [6] | [5] | [4]   | [3]    | [2] | [1] | [0] |

|----------|-----|-----|-----|-------|--------|-----|-----|-----|

| Mnemonic |     |     | aı  | ıtomu | te_tin | ne  |     |     |

| Default  | 0   | 0   | 0   | 0     | 0      | 0   | 0   | 0   |

| Bit   | Mnemonic      | Description                                                                                                    |

|-------|---------------|----------------------------------------------------------------------------------------------------------------|

| [7:0] | automute_time | Default o' 8'd0 (Automute Disabled) Time in Seconds = 2096896 / (automute_time x DATA_CLK) with DATA_CLK in Hz |

## Register #5: Soft Volume Control 2 (Automute Level)

8 bit, Read-Write Register, Default = 0x68

| Bits     | [7]               | [6] [5] [4] [3] [2] [1] [ |   |       |       | [0]   |   |   |

|----------|-------------------|---------------------------|---|-------|-------|-------|---|---|

| Mnemonic | automute_loopback |                           |   | autor | mute_ | level |   |   |

| Default  | 0                 | 1                         | 1 | 0     | 1     | 0     | 0 | 0 |

| Bit   | Mnemonic          | Description                                                                   |

|-------|-------------------|-------------------------------------------------------------------------------|

| [7]   | automute_loopback | 1'b0 disables automute_loopback (default) 1'b1 ramps to -infinity on automute |

| [6:0] | automute_level    | The level (in 1dB increments) of the automute, default of 7'd104              |

#### Register #6: Soft Volume Control 3 and De-emphasis

8 bit, Read-Write Register, Default = 0x4A

| Bits     | [7]               | [6]           | [5]  | [4]    | [3]        | [2] | [1]    | [0] |

|----------|-------------------|---------------|------|--------|------------|-----|--------|-----|

| Mnemonic | spdif_auto_deemph | deemph_bypass | deem | oh_sel | reserved * | V   | ol_rat | te  |

| Default  | 0                 | 1             | 0    | 0      | 1          | 0   | 1      | 0   |

| Bit   | Mnemonic          | Description                                                                                                                |

|-------|-------------------|----------------------------------------------------------------------------------------------------------------------------|

| [7]   | spdif_auto_deemph | 1'b0 disables automatic de-emphasis select in SPDIF mode (default) 1'b1 enables automatic de-emphasis select in SPDIF mode |

| [6]   | deemph_bypass     | 1'b0 enables de-emphasis filters<br>1'b1 disabled de-emphasis filters (default)                                            |

| [5:4] | deemph_sel        | 2'b00 = 32kHz (default)<br>2'b01 = 44.1kHz<br>2'b10 = 48kHz<br>2'b11 = RESERVED                                            |

| [3]   | reserved          | Must be left as 1'b1 for normal operation                                                                                  |

| [2:0] | vol_rate          | 3'd2 by default<br>Sets the volume ramp rate to 0.0078125 x fs / 2 <sup>(vol_rate-5)</sup> dB/s                            |

<sup>\*</sup> All Reserved Bits in Register #6 must be set to the indicated logic level to ensure correct device operation.

#### **Register #7: General Settings**

8 bit, Read-Write Register, Default = 0x80

| Bits     | [7]        | [6]      | [5]   | [4]        | [3]  | [2] | [1] | [0] |

|----------|------------|----------|-------|------------|------|-----|-----|-----|

| Mnemonic | reserved * | filter_s | shape | reserved * | iir_ | bw  | mı  | ute |

| Default  | 1          | 0 0      |       | 0          | 0    | 0   | 0   | 0   |

| Bit   | Mnemonic     | Description                                                                                                                                                                                                                                                                                               |

|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]   | reserved *   |                                                                                                                                                                                                                                                                                                           |

| [6:5] | filter_shape | 2'd0 = fast rolloff (default) 2'd1 = slow rolloff 2'd2 = minimum phase 2'd3 = reserved                                                                                                                                                                                                                    |

| [4]   | reserved *   |                                                                                                                                                                                                                                                                                                           |

| [3:2] | iir_bw       | 2'd0 = 1.0757 x fs or 47.44kHz (fs = 44.1kHz) – Normal mode (default)<br>2'd1 = 1.1338 x fs or 50kHz (fs = 44.1kHz)<br>2'd2 = 1.3605 x fs or 60kHz (fs = 44.1kHz)<br>2'd3 = 1.5873 x fs or 70kHz (fs = 44.1kHz)                                                                                           |

| [1:0] | mute         | This is a soft mute, which uses the ramping volume control. mute[0]  1'b0: Channel 1 (default of left channel) unmuted (default)  1'b1: Channel 1 (default of left channel) muted mute[1]  1'b0: Channel 2 (default of right channel) unmuted (default)  1'b1: Channel 2 (default of right channel) muted |

<sup>\*</sup> All Reserved Bits in Register #7 must be set to the indicated logic level to ensure correct device operation.

## **Register #8: GPIO Configuration**

8 bit, Read-Write Register, Default = 0x10

| Bits     | [7] | [6]   | [5]   | [4] | [3] | [2]   | [1]   | [0] |

|----------|-----|-------|-------|-----|-----|-------|-------|-----|

| Mnemonic |     | gpio2 | 2_cfg |     |     | gpio′ | 1_cfg |     |

| Default  | 0   | 0     | 0     | 1   | 0   | 0     | 0     | 0   |

| Bit   | Mnemonic  | Description                                                     |

|-------|-----------|-----------------------------------------------------------------|

|       |           | Set GPIO 2 configuration.                                       |

| [7:4] | gpio2_cfg | Default to 4'd1 (DPLL Lock Status).                             |

|       |           | See GPIO Configuration Table below for meaning of all settings. |

|       |           | Set GPIO 1 configuration                                        |

| [3:0] | gpio1_cfg | Default to 4'd0 (Automute Status).                              |

|       |           | See GPIO Configuration Table below for meaning of all settings. |

#### **GPIO Configuration Table**

| Setting          | Direction | GPIO Function                                                                                       |

|------------------|-----------|-----------------------------------------------------------------------------------------------------|

| 4'd0             | Output    | Automute status (active high)                                                                       |

| <del>-</del> 400 | Output    | - asserted when Automute condition is met                                                           |

| 4'd1             | Output    | DPLL Lock status (active high)                                                                      |

|                  | Саграс    | – asserted when DPLL is in lock                                                                     |

| 41.10            |           | Minimum Volume (active high)                                                                        |

| 4'd2             | Output    | - asserted when volume of both the left & right channels has ramped to its minimum value (–127.5dB) |

| 4'd3             | Output    | MCLK                                                                                                |

|                  | · ·       | DPLL Lock interrupt (active high)                                                                   |

| 4'd4             | Output    | - asserted when DPLL Lock status changes state                                                      |

|                  | •         | - reading register 64 clears the interrupt                                                          |

|                  |           | Automute Interrupt (active high)                                                                    |

| 4'd5             | Output    | - asserted when Automute status changes state                                                       |

|                  |           | - reading register 64 clears the interrupt                                                          |

|                  |           | DPLL Lock or Automute interrupt (active high)                                                       |

| 4'd6             | Output    | - asserted when DPLL Lock or Automute status changes state                                          |

|                  |           | - reading register 64 clears the interrupt                                                          |

| 4'd7             | Output    | Output low                                                                                          |

| 4'd8             | Input     | Used as input pin – pin status can be read from register 65.                                        |

| 4'd9             | Input     | Input Selection – uses the GPIO as an input select based on register 21                             |

| 4'd15            | Output    | Output high                                                                                         |

## Register #9: Reserved

8 bit, Read-Write Register, Default = 0x22

| Bits     | [7]                     | [6] | [5] | [4] | [3] | [2] | [1] | [0] |  |

|----------|-------------------------|-----|-----|-----|-----|-----|-----|-----|--|

| Mnemonic | Reserved for Revision V |     |     |     |     |     |     |     |  |

| Default  | 0                       | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

#### Register #10: Master Mode Control

8 bit, Read-Write Register, Default = 0x5

| Bits     | [7]                 | [6]                  | [5] | [5] [4]   |   | [2]  | [1]  | [0] |

|----------|---------------------|----------------------|-----|-----------|---|------|------|-----|

| Mnemonic | master_clock_enable | clock_divider_select |     | sync_mode |   | stop | _div |     |

| Default  | 0                   | 0                    | 0   | 0         | 0 | 1    | 0    | 1   |

| Bit   | Mnemonic             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]   | master_clock_enable  | 1'b0 disables master mode (default) 1'b1 enables master mode (driving Bit clock and Frame Clock)                                                                                                                                                                                                                                                                                                                                                                                                 |

| [6:5] | clock_divider_select | 2'b00: Bit Clock frequency = MCLK / 4 (default) 2'b01: Bit Clock frequency = MCLK / 8 2b10: Bit Clock frequency = MCLK / 16 2'b11: Bit Clock frequency = MCLK / 16 Frame Clock frequency = Bit Clock frequency / 64                                                                                                                                                                                                                                                                              |

| [4]   | sync_mode            | 1'b0 for normal operation of the DPLL and ASRC. 1'b1 to enable quick lock if the fs and MCLK are synchronous and MCLK is 128 x FSR  Note: quick lock can only be used in PCM normal mode.                                                                                                                                                                                                                                                                                                        |

| [3:0] | stop_div             | Sets the number of FSR edges that must occur before the DPLL and ASRC can lock on to the incoming signal.  4'd0 = 16384 FSR edges  4'd1 = 8192 FSR edges  4'd2 = 5461 FSR edges  4'd3 = 4096 FSR edges  4'd4 = 3276 FSR edges  4'd5 = 2730 FSR edges  4'd6 = 2340 FSR edges  4'd7 = 2048 FSR edges  4'd8 = 1820 FSR edges  4'd9 = 1638 FSR edges  4'd10 = 1489 FSR edges  4'd11 = 1365 FSR edges  4'd12 = 1260 FSR edges  4'd13 = 1170 FSR edges  4'd14 = 1092 FSR edges  4'd15 = 1024 FSR edges |

For correct operation, master mode should only be enabled when the DAC's input mode is set to  $I^2S$ , and when  $i^2S$  in register 1.

When master mode is enabled, the DATA\_CLK pin will output Bit Clock and the DATA1 pin will output Frame Clock at frequencies specified by clock divider select.

For compatibility with Rev. W, or when PCM data with FSR > 96kHz is used, stop\_div should be set to 4'd0 (16384 FSR edges).

## Register #11: Channel Mapping

8 bit, Read-Write Register, Default = 0x02

| Bits     | [7]        | [6] [5] [4] |       |  | [3]             | [2]             | [1]     | [0]     |

|----------|------------|-------------|-------|--|-----------------|-----------------|---------|---------|

| Mnemonic | reserved * | spdif_sel   |       |  | ch2_analog_swap | ch1_analog_swap | ch2_sel | ch1_sel |

| Default  | 0          | 0           | 0 0 0 |  | 0               | 0               | 1       | 0       |

| Bit   | Mnemonic        | Description                                                                                                                 |

|-------|-----------------|-----------------------------------------------------------------------------------------------------------------------------|

| [7]   | reserved *      |                                                                                                                             |

| [6:4] | spdif_sel       | select the spdif data source 3'd0 = DATA_CLK (default) 3'd1 = DATA2 3'd2 = DATA1 3'd3 = GPIO1 3'd4 = GPIO2 3'd5-7: reserved |

| [3]   | ch2_analog_swap | 1'b0 = normal operation (default)<br>1'b1 = swap dac and dacb                                                               |

| [2]   | ch1_analog_swap | 1'b0 = normal operation (default)<br>1'b1 = swap dac and dacb                                                               |

| [1]   | ch2_sel         | 1'b0 = left<br>1'b1 = right (default)                                                                                       |

| [0]   | ch1_sel         | 1'b0 = left (default)<br>1'b1 = right                                                                                       |

<sup>\*</sup> All Reserved Bits in Register #11 must be set to the indicated logic level to ensure correct device operation.

Left and Right channels can be reversed using Register #11.

#### Register #12: DPLL/ASRC Settings

8 bit, Read-Write Register, Default = 0x5A

| Bits     | [7] | [6]    | [5]  | [4] | [3] | [2]   | [1]  | [0] |

|----------|-----|--------|------|-----|-----|-------|------|-----|

| Mnemonic | С   | lpll_b | w_i2 | S   | d   | pll_b | w_ds | d   |

| Default  | 0   | 1      | 0    | 1   | 1   | 0     | 1    | 0   |

| Bit   | Mnemonic    | Description                                                                                                        |

|-------|-------------|--------------------------------------------------------------------------------------------------------------------|

|       |             | DPLL bandwidth setting for I <sup>2</sup> S and SPDIF modes (16 settings) 4'b0000 : OFF 4'b0001 : Lowest Bandwidth |

| [7:4] | dpll_bw_i2s | 4'b0101 : (default)                                                                                                |

|       |             | 4'b1010 :                                                                                                          |

|       |             | variable 4'b1111 : Highest Bandwidth                                                                               |

|       |             | DPLL bandwidth setting for DSD mode (16 settings)                                                                  |

|       |             | 4'b0000 : OFF                                                                                                      |

|       |             | 4'b0001 : Lowest Bandwidth                                                                                         |

| [3:0] | dpll_bw_dsd | 4'b0101 :                                                                                                          |

|       |             | 4'b1010 : (default) ▼                                                                                              |

|       |             | 4'b1111 : Highest Bandwidth                                                                                        |

#### **Register #13: THD Compensation**

8 bit, Read-Write Register, Default = 0x40

| Bits     | [7]        | [6]        | [5] [4] [3] [2] [1] |   |   | [0] |   |   |

|----------|------------|------------|---------------------|---|---|-----|---|---|

| Mnemonic | reserved * | bypass_thd | reserved *          |   |   |     |   |   |

| Default  | 0          | 1          | 0                   | 0 | 0 | 0   | 0 | 0 |

| Bit   | Mnemonic   | Description                                                                                                                                                                                                                                                                                                                                                                |

|-------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]   | reserved * |                                                                                                                                                                                                                                                                                                                                                                            |

| [6]   | bypass_thd | 1'b0: enable THD compensation  output = input + (input²) x thd_comp_c2 + (input³) x thd_comp_c3  thd_comp_c2 is stored in registers 23-22 (16 bits signed) (register 23 stores MSBs) thd_comp_c3 is stored in registers 25-24 (16 bits signed) (register 25 stores MSBs)  1'b1: disable THD compensation (default)  PCM mode: output = input; DSD mode: output = input / 2 |

| [5:0] | reserved * |                                                                                                                                                                                                                                                                                                                                                                            |

<sup>\*</sup> All Reserved Bits in Register #13 must be set to the indicated logic level to ensure correct device operation. THD compensation can be used to reduce the 2<sup>nd</sup> and 3<sup>rd</sup> harmonic distortion introduced by external output drivers. A system level tuning is required to arrive at the optimum coefficients for thd\_comp\_c2 and thd\_comp\_c3.

#### Notes:

- To get the same gain (output = input) for PCM and DSD modes without THD compensation, bypass\_thd should be set to 1'b0 with thd\_comp\_c2 and thd\_comp\_c3 set to 16'd0 (default)

- Erroneous compensation can lead to higher distortion than the one without compensation. If accurate tuning cannot be performed, thd\_comp\_c2 and thd\_comp\_c3 should be set to 16'd0 (default) if bypass thd is set to 1'b0.

#### **Register #14: Soft Start Settings**

8 bit, Read-Write Register, Default = 0x8A

| Bits     | [7]        | [6]                | [5]          | [4] | [3]   | [2]    | [1]   | [0] |

|----------|------------|--------------------|--------------|-----|-------|--------|-------|-----|

| Mnemonic | soft_start | soft_start_on_lock | mute_on_lock |     | soft_ | start_ | _time |     |

| Default  | 1          | 0                  | 0            | 0   | 1     | 0      | 1     | 0   |

| Bit   | Mnemonic            | Description                                                                              |

|-------|---------------------|------------------------------------------------------------------------------------------|

| [7]   | soft start          | 1'b0: Ramp the output stream to ground                                                   |

| [,]   | sort_start          | 1'b1: Normal operation (default) – ramp the output stream to ½ x AVCC_L/R                |

| [6]   | soft_start_on_lock  | 1'b0: Do not force output low when lock is lost (default)                                |

| [6]   | SUIT_STAIT_UIT_TOCK | 1'b1: Force output low when lock is lost                                                 |

| [5]   | muta an laak        | 1'b0: Do not force a mute when lock is lost (default)                                    |

| [5]   | mute_on_lock        | 1'b1: Force a mute when lock is lost                                                     |

|       |                     | Time for soft start ramp                                                                 |

| [4:0] | aoft start time     | = 4096 x 2 <sup>(soft_start_time+1)</sup> / MCLK seconds (where MCLK is measured in Hz). |

| [4:0] | soft_start_time     |                                                                                          |

|       |                     | The valid range of soft-start_time is from 0 to 20.                                      |

#### Register #15: Volume 1 (usually selected for the Left Channel, but can be reversed using Register #11)

8 bit, Read-Write Register, Default = 0x00

| Bits     | [7] | [6] | [5] | [4]  | [3] | [2] | [1] | [0] |

|----------|-----|-----|-----|------|-----|-----|-----|-----|

| Mnemonic |     |     |     | volu | me1 |     |     |     |

| Default  | 0   | 0   | 0   | 0    | 0   | 0   | 0   | 0   |

| Bit   | Mnemonic | Description                                       |

|-------|----------|---------------------------------------------------|

| [7:0] | volume1  | Default to 8'd0<br>0dB to -127.5dB in 0.5dB steps |

#### Register #16: Volume 2 (usually selected for the Right Channel, but can be reversed using Register #11)

8 bit Read-Write Register Default = 0x00

| o bit, itoua i | • • • • • |     | ,,,,, | 90146 | <i>,</i> ,,, | ,,,, |     |     |

|----------------|-----------|-----|-------|-------|--------------|------|-----|-----|

| Bits           | [7]       | [6] | [5]   | [4]   | [3]          | [2]  | [1] | [0] |

| Mnemonic       |           |     |       | volu  | me2          |      |     |     |

| Default        | 0         | 0   | 0     | 0     | 0            | 0    | 0   | 0   |

| Bit          | Mnemonic | Description                    |

|--------------|----------|--------------------------------|

| [7:0]        | volumo?  | Default to 8'd0                |

| [7.0]   VOIC | volume2  | 0dB to -127.5dB in 0.5dB steps |

#### Register #20-17: Master Trim

32 bit, Read-Write Register, Default = 32'h7ffffff. Reg 20 are the MSB's, Reg 17 are the LSBs.

| Bits     | [31:0]       |

|----------|--------------|

| Mnemonic | master_trim  |

| Default  | 32'h7fffffff |

This is a 32 bit value that sets the 0dB level for all volume controls. This is a signed number, so it should never exceed 32'h7fffffff (which is  $2^{31} - 1$ ).

#### Register #21: GPIO Input Selection and OSF Bypass

8 bit, Read-Write Register, Default = 0x00

| Bits     | [7      | :6]      | [5:4]           |   | [3]        | [2]        | [1]        | [0]        |

|----------|---------|----------|-----------------|---|------------|------------|------------|------------|

| Mnemonic | gpio_in | put_sel2 | gpio_input_sel1 |   | reserved * | bypass_iir | reserved * | bypass_osf |

| Default  | 0       | 0        | 0               | 0 | 0          | 0          | 0          | 0          |

| Bit   | Mnemonic        | Description                                                                                                                                                                                                                            |

|-------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6] | gpio_input_sel2 | Selects which input will be selected when GPIOX = 1'b1 2'd0 = I <sup>2</sup> S data (default) 2'd1 = SPDIF data 2'd2 = reserved 2'd3 = DSD data                                                                                        |

| [5:4] | gpio_input_sel1 | Selects which input will be selected when GPIOX = 1'b0 2'd0 = I <sup>2</sup> S data (default) 2'd1 = SPDIF data 2'd2 = reserved 2'd3 = DSD data                                                                                        |

| [3]   | reserved *      |                                                                                                                                                                                                                                        |

| [2]   | bypass_iir      | 1'b0 = Use the IIR filter (default)<br>1'b1 = Bypass the IIR filter.                                                                                                                                                                   |

| [1]   | reserved *      |                                                                                                                                                                                                                                        |