# TFT LCD Module Product Specification

#### DT028BTFT-PTS2

2.8" (240RGB x 320 DOTS) TFT Module with Projected Capacitive Touch Screen

November 3, 2020

#### Remark:

Contents in this document are subject to change without notice. No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, for any purpose, without the express written permission of Displaytech.

#### **Displaytech**

Email: <a href="mailto:sales@displaytech.com.hk">sales@displaytech.com.hk</a>

Website: <a href="mailto:http://www.displaytech.com.hk">http://www.displaytech.com.hk</a>

## **Revision Record**

| REV | CHANGES                                                         | DATE         |

|-----|-----------------------------------------------------------------|--------------|

| 1.1 | First release                                                   | Jul 5, 2019  |

| 2.0 | Changed the P/N from DT028BTFT-PTS1 to DT028BTFT-PTS2           | Apr 28, 2020 |

|     | Updated CTP driver IC from FT5346 to FT5446 in section 3 and 4. |              |

| 2.1 | Updated the drawing details;                                    | Nov 3, 2020  |

|     | Corrected CTP signal description.                               |              |

|     |                                                                 |              |

|     |                                                                 |              |

|     |                                                                 |              |

|     |                                                                 |              |

|     |                                                                 |              |

|     |                                                                 |              |

|     |                                                                 |              |

|     |                                                                 |              |

# **Table of Content**

| Re | visior  | n Record                               | 1  |

|----|---------|----------------------------------------|----|

| 1. | Sco     | pe                                     | 3  |

| 2. | App     | olication                              | 3  |

| 3. | Ger     | neral Information                      | 3  |

| 4. | Out     | line Drawing                           | 4  |

| 5. | Inte    | rface signals                          | 5  |

| 6. | Abs     | solute maximum Ratings                 | 6  |

|    | 6.1 Ele | ectrical Absolute max. ratings         | 6  |

|    | 6.2 En  | vironment Conditions                   | 6  |

| 7. | Elec    | ctrical Specifications                 | 7  |

|    | 7.1 Ele | ectrical characteristics               | 7  |

|    | 7.2 LE  | D Backlight                            | 7  |

| 8. | Cor     | nmand/AC Timing                        | 8  |

|    |         | Characteristics                        |    |

|    | 8.2 I   | Reset Timing                           | 13 |

| 9. | Opt     | ical Specification                     | 15 |

| 10 | . Env   | rironmental / Reliability Tests        | 17 |

| 11 | . Pre   | cautions for Use of LCD Modules        | 18 |

|    | 11.1    | Safety                                 | 18 |

|    | 11.2    | Handling                               | 18 |

|    | 11.3    | Static Electricity                     |    |

|    | 11.4    | Storage                                | 18 |

|    | 11.5    | Cleaning                               | 18 |

|    | 11.6    | Cautions for installing and assembling | 19 |

#### 1. Scope

This data sheet is to introduce the specification of DT028BTFT-PTS2 active matrix TFT module. It is composed of a color TFT-LCD panel, driver ICs, FPC, CTP and a backlight unit. The 2.8" display area contains 240(RGB) x 320 pixels.

#### 2. Application

Digital equipments which need color display, mobile navigator/video systems.

#### 3. General Information

| Item                          | Contents              | Unit |

|-------------------------------|-----------------------|------|

| Size                          | 2.8                   | inch |

| Resolution                    | 240(RGB)*320          | I    |

| Interface                     | RGB/MCU               | I    |

| Technology type               | a-Si TFT              | 1    |

| Pixel Configuration           | R.G.B Vertical Stripe |      |

| Outline Dimension (W x H x D) | 50.0 x 69.2 x 4.32    | mm   |

| Active Area                   | 43.2 x 57.60          | mm   |

| Display Mode                  | Transmissive          | 1    |

| Backlight Type                | LED                   | 1    |

| TFT Driver IC                 | ILI9341               | I    |

| CTP Driver IC                 | FT5446                | 1    |

| Viewing direction             | U/L/D/R 55/65/65      | I    |

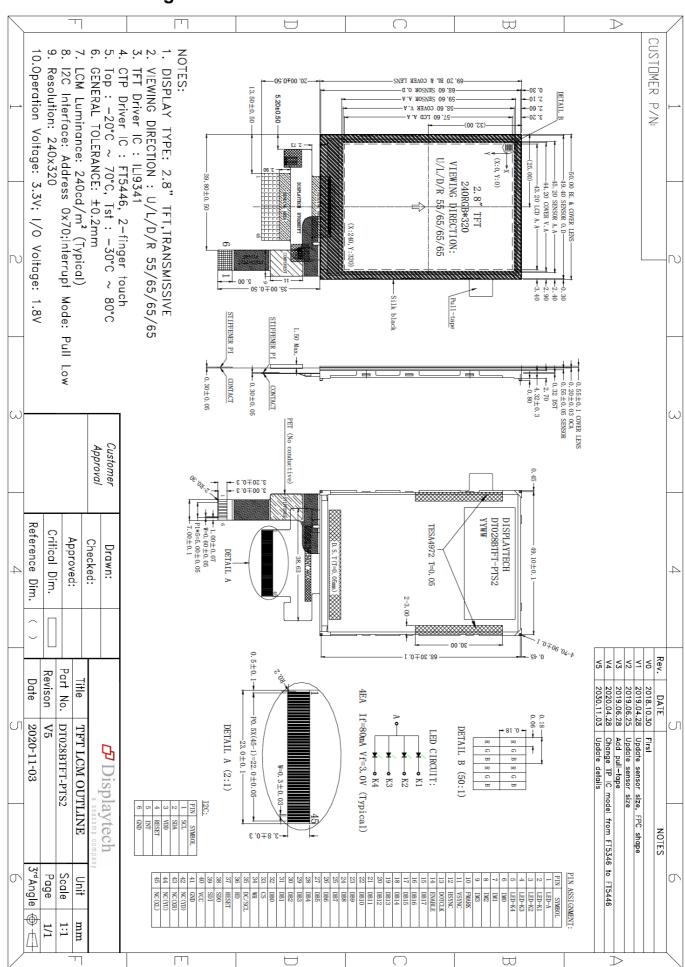

#### 4. Outline Drawing

# 5. Interface signals

Recommended mating connector: FH12S-45S-0.5SH (or equivalent)

| Pin No. | Symbol        | I/O | Function                                                                                                                                                                                      |

|---------|---------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

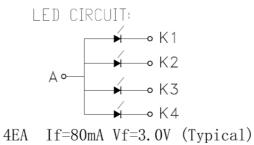

| 1       | LED-A         | Р   | LED back light(Anode)                                                                                                                                                                         |

| 2-5     | LED-K1-LED-K4 | Р   | LED back light(Cathode)                                                                                                                                                                       |

| 6-9     | IM0-IM3       | I   | System interface select. Note1                                                                                                                                                                |

| 10      | FMARK         | 0   | Tearing effect output pin to synchronize MPU to frame writing, activate by S/W command. Normally Low. Leave open when not in use.                                                             |

| 11      | VSYNC         | I   | Frame sync signal For RGB interface operation. Fix to VDD or VSS when not in use.                                                                                                             |

| 12      | HSYNC         | I   | Line sync signal For RGB interface operation. Fix to VDD or VSS when not in use.                                                                                                              |

| 13      | DOTCLK        | I   | Data clock For RGB interface operation. Fix to VDD or VSS when not in use.                                                                                                                    |

| 14      | ENABLE        | I   | Data enable pin For RGB interface operation. Fix to VDD or VSS when not in use.                                                                                                               |

| 15-32   | DB17-DBO      | I   | 18-bit parallel data bus for MCU system and RGB interface modes. Fix to VSS when not in use. Refer to Note1 for interface selection.                                                          |

| 33      | CS            | I   | Chip select signal: Active low                                                                                                                                                                |

| 34      | WR            | I   | 8080-I/8080-II Parallel interface: write signal. 4-wire serial interface: Command/Parameter select. Fix to VDD when not in use.                                                               |

| 35      | DC/SCL        | I   | 8080-I/8080-II Parallel interface: Data/Command select (DCX=1→Data select. DCX=0→Command select.) 3-wire9-bit/4-wire 8-bit serial interface: Serial clock. Fix to VDD or VSS when not in use. |

| 36      | RD            | I   | 8080-I/8080-II Parallel interface: Read signal. Fix to VDD when not in use.                                                                                                                   |

| 37      | RESET         | I   | System Reset Active Low                                                                                                                                                                       |

| 38      | SDO           | 0   | Serial data output in serial bus system interface. Leave open when not in use.                                                                                                                |

| 39      | SDI           | I   | Serial input signal IM[3] Low: Serial in/out, IM[3] High: Serial input. Fix to VDD or VSS when not in use.                                                                                    |

| 40      | VCC           | Р   | Power supply                                                                                                                                                                                  |

| 41      | GND           | Р   | Ground.                                                                                                                                                                                       |

| 42      | YD(NC)        | 0   |                                                                                                                                                                                               |

| 43      | XR(NC)        | 0   | Taurah aantuul min                                                                                                                                                                            |

| 44      | YU(NC)        | 0   | Touch control pin                                                                                                                                                                             |

| 45      | XL(NC)        | 0   |                                                                                                                                                                                               |

Note 1:

| IM3   | IM2   | IM1    | IMO   | Interface                            | DB Pi              | n in use          |  |

|-------|-------|--------|-------|--------------------------------------|--------------------|-------------------|--|

| IIVIS | IIVIZ | IIVI I | 11010 | interrace                            | Register/Content   | GRAM              |  |

| 0     | 0     | 0      | 0     | 80 MCU 8-bit bus interface I         | DB[7:0]            | DB[7:0]           |  |

| 0     | 0     | 0      | 1     | 80 MCU 16-bit bus interface I        | DB[7:0]            | DB[15:0]          |  |

| 0     | 0     | 1      | 0     | 80 MCU 9-bit bus interface I         | DB[7:0]            | DB[8:0]           |  |

| 0     | 0     | 1      | 1     | 80 MCU 18-bit bus interface I        | DB[7:0] DB[17:0]   |                   |  |

| 0     | 1     | 0      | 1     | 3-line 9-bit data serial interface I | SDA: In/Out        |                   |  |

| 0     | 1     | 1      | 0     | 4-line 8-bit data serial interface I | SDA                | : In/Out          |  |

| 1     | 0     | 0      | 0     | 80 MCU 16-bit bus interface II       | DB[8:1]            | DB[17:10] DB[8:1] |  |

| 1     | 0     | 0      | 1     | 80 MCU 8-bit bus interface Ⅱ         | DB[17:10]          | DB[17:10]         |  |

| 1     | 0     | 1      | 0     | 80 MCU 18-bit bus interface II       | DB[8:1] DB[17:0]   |                   |  |

| 1     | 0     | 1      | 1     | 80 MCU 9-bit bus interface Ⅱ         | DB[17:10] DB[17:9] |                   |  |

| 1     | 1     | 0      | 1     | 3-line 9-bit data serial interface Ⅱ | SDI: In, SDO: Out  |                   |  |

| 1     | 1     | 1      | 0     | 4-line 8-bit data serial interface Ⅱ | SDI: In,           | SDO: Out          |  |

Must select Serial MCU(system) interface to use RGB data interface.

#### CTP Interface Signal:

| Pin No. | Symbol | Function                         |

|---------|--------|----------------------------------|

| 1       | SCL    | I <sup>2</sup> C clock signal    |

| 2       | SDA    | I <sup>2</sup> C data signal     |

| 3       | VDD    | Power supply for TP              |

| 4       | RESET  | External Reset/Wake. Active low. |

| 5       | INT    | Interrupt output pin. Active low |

| 6       | GND    | Power ground                     |

Recommended mating connector: FH12-6S-1SH(55) (or equivalent)

# 6. Absolute maximum Ratings

#### 6.1 Electrical Absolute max. ratings

| Parameter            | Symbol | MIN  | MAX | Unit | Remark |

|----------------------|--------|------|-----|------|--------|

| Power Supply Voltage | VCC    | -0.3 | 4.6 | V    |        |

| Logic Supply Voltage | VDD    | -0.3 | 4.6 | V    |        |

| PCAP Supply Voltage  | VPCAP  | -0.3 | 3.6 | V    |        |

#### **6.2 Environment Conditions**

| Item                  | Symbol | MIN | MAX | Unit         | Remark |

|-----------------------|--------|-----|-----|--------------|--------|

| Operating Temperature | TOPR   | -20 | 70  | $^{\circ}$ C |        |

| Storage Temperature   | TSTG   | -30 | 80  | $^{\circ}$ C |        |

### 7. Electrical Specifications

#### 7.1 Electrical characteristics

GND=0V, Ta=25℃

| Item                  | Symbol | MIN     | TYP | MAX     | Unit | Remark |

|-----------------------|--------|---------|-----|---------|------|--------|

| Power Supply          | VCC    | 2.5     | 2.8 | 3.3     | V    |        |

| Input Cianal Valtage  | VIL    | 0       |     | 0.3*VCC | V    |        |

| Input Signal Voltage  | VIH    | 0.7*VCC |     | VCC     | V    |        |

| Output Signal Voltage | VOL    | 0       |     | 0.2*VCC | V    |        |

| Output Signal Voltage | VOH    | 0.8*VCC | -   | VCC     | V    |        |

#### 7.2 LED Backlight

Ta=25°C

| Item            | Symbol | MIN | TYP   | MAX | Unit | Remark |

|-----------------|--------|-----|-------|-----|------|--------|

| Forward Current | IF     | -   | 80    | -   | mA   |        |

| Forward Voltage | VF     | -   | 3.0   | -   | V    |        |

| LED life time   |        | -   | 30000 | -   | Hr   | Note   |

#### Notes:

1: The "LED life time" is defined as the module brightness decrease to 50% original brightness at Ta=25 $^{\circ}$ C and IL =80mA. The LED lifetime could be decreased if operating IL is larger than 80mA.

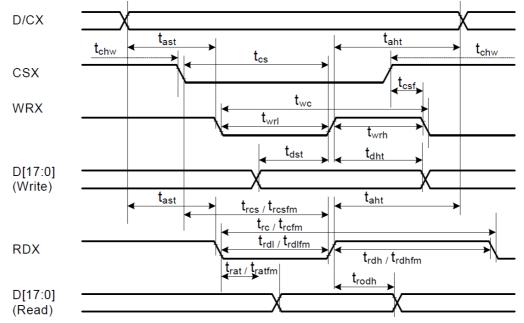

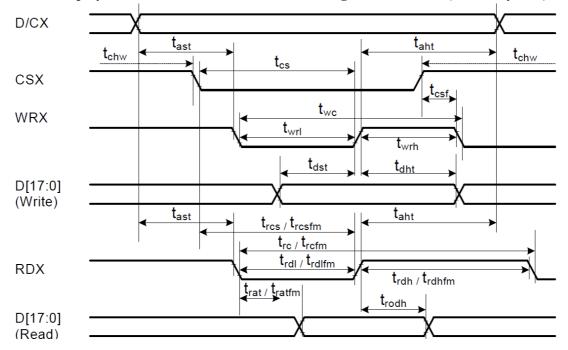

#### 8. Command/AC Timing

#### 8.1 AC Characteristics

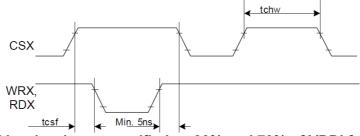

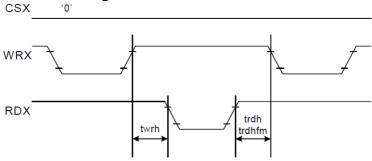

#### 8.1.1 Display Parallel 18/16/9/8-bit Interface Timing Characteristics (8080-I system)

| Signal   | Symbol | Parameter                          | min | max | Unit | Description         |

|----------|--------|------------------------------------|-----|-----|------|---------------------|

| DCV      | tast   | Address setup time                 | 0   | -   | ns   |                     |

| DCX      | taht   | Address hold time (Write/Read)     | 0   | -   | ns   |                     |

|          | tchw   | CSX "H" pulse width                | 0   | -   | ns   |                     |

|          | tcs    | Chip Select setup time (Write)     | 15  | -   | ns   |                     |

| CSX      | trcs   | Chip Select setup time (Read ID)   | 45  | -   | ns   |                     |

|          | trosfm | Chip Select setup time (Read FM)   | 355 | -   | ns   |                     |

|          | tcsf   | Chip Select Wait time (Write/Read) | 10  | -   | ns   |                     |

|          | twc    | Write cycle                        | 66  | -   | ns   |                     |

| WRX      | twrh   | Write Control pulse H duration     | 15  | -   | ns   |                     |

|          | twrl   | Write Control pulse L duration     | 15  | -   | ns   |                     |

|          | trcfm  | Read Cycle (FM)                    | 450 | -   | ns   |                     |

| RDX (FM) | trdhfm | Read Control H duration (FM)       | 90  | -   | ns   |                     |

|          | trdlfm | Read Control L duration (FM)       | 355 | -   | ns   |                     |

|          | trc    | Read cycle (ID)                    | 160 | -   | ns   |                     |

| RDX (ID) | trdh   | Read Control pulse H duration      | 90  | -   | ns   |                     |

|          | trdl   | Read Control pulse L duration      | 45  | -   | ns   |                     |

| 547.01   | tdst   | Write data setup time              | 10  | -   | ns   |                     |

| D[17:0], | tdht   | Write data hold time               | 10  | -   | ns   | 5                   |

| D[15:0], | trat   | Read access time                   | -   | 40  | ns   | For maximum CL=30pF |

| D[8:0],  | tratfm | Read access time                   | -   | 340 | ns   | For minimum CL=8pF  |

| D[7:0]   | trod   | Read output disable time           | 20  | 80  | ns   |                     |

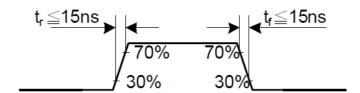

Note: Ta = -30 to 70  $^{\circ}$  C, VDDI=1.65V to 3.3V, VCI=2.5V to 3.3V, VSS=0V

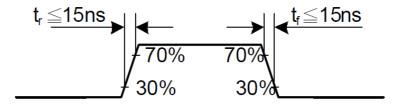

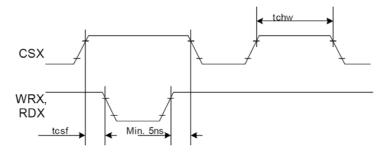

CSX timings:

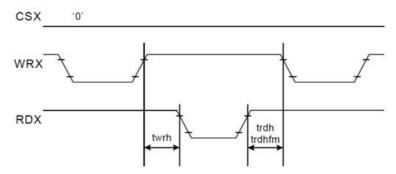

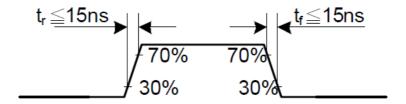

Note: Logic high and low levels are specified as 30% and 70% of VDDI for Input signals. Write to read or read to write timings:

Note: Logic high and low levels are specified as 30% and 70% of VDDI for Input signals.

#### 8.1.2 Display Parallel 18/16/9/8-bit Interface Timing Characteristics(8080- II system)

| Signal               | Symbo  | Parameter                          | min | max | Unit | Description          |

|----------------------|--------|------------------------------------|-----|-----|------|----------------------|

| DOV                  | tast   | Address setup time                 | 0   | -   | ns   |                      |

| DCX                  | taht   | Address hold time (Write/Read)     | 0   | -   | ns   |                      |

|                      | tchw   | CSX "H" pulse width                | 0   | -   | ns   |                      |

|                      | tcs    | Chip Select setup time (Write)     | 15  | -   | ns   |                      |

| CSX                  | trcs   | Chip Select setup time (Read ID)   | 45  | -   | ns   |                      |

|                      | trcsfm | Chip Select setup time (Read FM)   | 355 | -   | ns   |                      |

|                      | tcsf   | Chip Select Wait time (Write/Read) | 10  | -   | ns   |                      |

|                      | twc    | Write cycle                        | 66  | -   | ns   |                      |

| WRX                  | twrh   | Write Control pulse H duration     | 15  | -   | ns   |                      |

|                      | twrl   | Write Control pulse L duration     | 15  | -   | ns   |                      |

|                      | trcfm  | Read Cycle (FM)                    | 450 | -   | ns   |                      |

| RDX (FM)             | trdhfm | Read Control H duration (FM)       | 90  | -   | ns   |                      |

|                      | trdlfm | Read Control L duration (FM)       | 355 | -   | ns   |                      |

|                      | trc    | Read cycle (ID)                    | 160 | -   | ns   |                      |

| RDX (ID)             | trdh   | Read Control pulse H duration      | 90  | -   | ns   |                      |

|                      | trdl   | Read Control pulse L duration      | 45  | -   | ns   |                      |

| D(47.0)              | tdst   | Write data setup time              | 10  | -   | ns   |                      |

| D[17:0],             | tdht   | Write data hold time               | 10  | -   | ns   | For movimum CL =30nF |

| D[17:10]&D[8:1],     | trat   | Read access time                   | 1   | 40  | ns   | For maximum CL=30pF  |

| D[17:10],<br>D[17:9] | tratfm | Read access time                   | 1   | 340 | ns   | For minimum CL=8pF   |

| D[17.8]              | trod   | Read output disable time           | 20  | 80  | ns   |                      |

Note: Ta = -30 to 70 °C, VDDI=1.65V to 3.3V, VCI=2.5V to 3.3V, VSS=0V.

#### **CSX timings:**

Note: Logic high and low levels are specified as 30% and 70% of VDDI for Input signals.

#### Write to read or read to write timings:

Note: Logic high and low levels are specified as 30% and 70% of VDDI for Input signals.

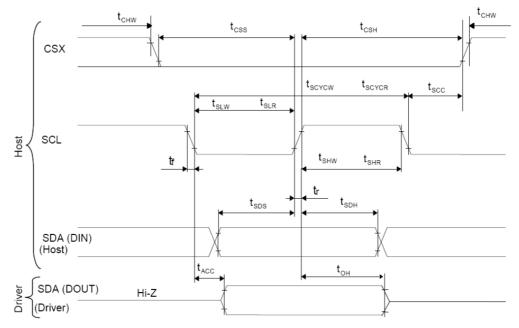

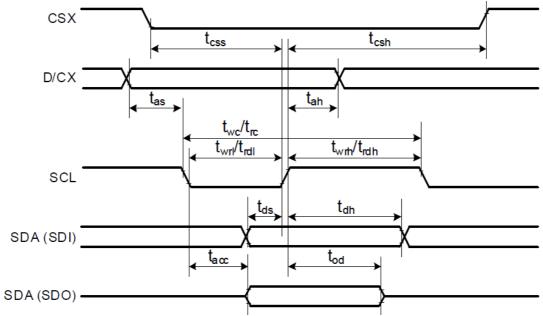

#### 8.1.3 Display Serial Interface Timing Characteristics (3-line SPI system)

| Signal    | Symbol | Parameter                   | min | max | Unit | Description |

|-----------|--------|-----------------------------|-----|-----|------|-------------|

|           | tscycw | Serial Clock Cycle (Write)  | 100 | -   | ns   |             |

|           | tshw   | SCL "H" Pulse Width (Write) | 40  | -   | ns   |             |

| SCL       | tslw   | SCL "L" Pulse Width (Write) | 40  | -   | ns   |             |

| SCL       | tscycr | Serial Clock Cycle (Read)   | 150 | -   | ns   |             |

|           | tshr   | SCL "H" Pulse Width (Read)  | 60  | -   | ns   |             |

|           | tslr   | SCL "L" Pulse Width (Read)  | 60  | -   | ns   |             |

| SDA / SDI | tsds   | Data setup time (Write)     | 30  | -   | ns   |             |

| (Input)   | tsdh   | Data hold time (Write)      | 30  | -   | ns   |             |

| SDA / SDO | tacc   | Access time (Read)          | 10  | -   | ns   |             |

| (Output)  | toh    | Output disable time (Read)  | 10  | 50  | ns   |             |

|           | tscc   | SCL-CSX                     | 20  | -   | ns   |             |

| 001/      | tchw   | CSX "H" Pulse Width         | 40  | -   | ns   |             |

| CSX       | tcss   | CSV SCI Times               | 60  | -   | ns   |             |

|           | tcsh   | CSX-SCL Time                | 65  | -   | ns   |             |

Note: Ta = 25 °C, VDDI=1.65V to 3.3V, VCI=2.5V to 3.3V, AGND=VSS=0V

#### 8.1.4 Display Serial Interface Timing Characteristics (4-line SPI system)

| Signal    | Symbol                                   | Parameter                     | min | max                 | Unit | Description        |

|-----------|------------------------------------------|-------------------------------|-----|---------------------|------|--------------------|

| CSX       | tcss                                     | Chip select time (Write)      | 40  | -                   | ns   |                    |

| CSX       | tcsh                                     | Chip select hold time (Read)  | 40  | -                   | ns   |                    |

|           | twc                                      | Serial clock cycle (Write)    | 100 | -                   | ns   |                    |

|           | twrh                                     | SCL "H" pulse width (Write)   | 40  | -                   | ns   |                    |

| SCL       | twrl                                     | SCL "L" pulse width (Write)   | 40  | -                   | ns   |                    |

| SCL       | trc                                      | Serial clock cycle (Read)     | 150 | -                   | ns   |                    |

|           | trdh                                     | SCL "H" pulse width (Read)    | 60  | -                   | ns   |                    |

| trdl      |                                          | SCL "L" pulse width (Read)    | 60  | -                   | ns   |                    |

| DIOV      | tas                                      | D/CX setup time               | 10  | -                   |      |                    |

| D/CX      | tah                                      | D/CX hold time (Write / Read) | 10  | -                   |      |                    |

| SDA / SDI | tds                                      | Data setup time (Write)       | 30  | -                   | ns   |                    |

| (Input)   | tdh                                      | Data hold time (Write)        | 30  | -                   | ns   |                    |

| SDA / SDO | DA / SDO tacc Access time (Read) 10 - ns |                               | ns  | For maximum CL=30pF |      |                    |

| (Output)  | tod                                      | Output disable time (Read)    | 10  | 50                  | ns   | For minimum CL=8pF |

Note: Ta = 25 °C, VDDI=1.65V to 3.3V, VCI=2.5V to 3.3V, AGND=VSS=0V

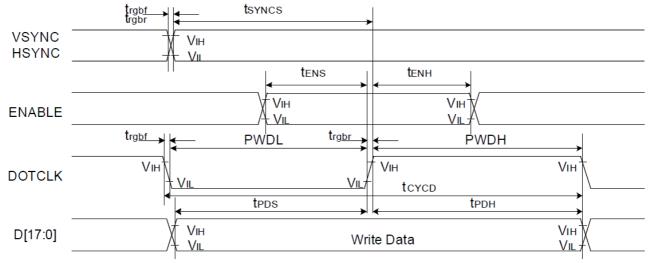

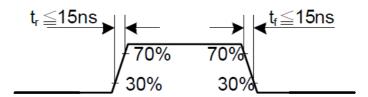

#### 8.1.5 Parallel 18/16/6-bit RGB Interface Timing Characteristics

| Signal  | Symbol                                | Parameter                         | min | max | Unit | Description       |  |

|---------|---------------------------------------|-----------------------------------|-----|-----|------|-------------------|--|

| VSYNC / | t <sub>SYNCS</sub>                    | VSYNC/HSYNC setup time            | 15  | -   | ns   |                   |  |

| HSYNC   | t <sub>SYNCH</sub>                    | VSYNC/HSYNC hold time             | 15  | -   | ns   |                   |  |

| DE      | t <sub>ENS</sub>                      | DE setup time                     | 15  | -   | ns   |                   |  |

| DE      | t <sub>ENH</sub>                      | DE hold time                      | 15  | -   | ns   |                   |  |

| D[47:0] | t <sub>POS</sub>                      | Data setup time                   | 15  | -   | ns   | 18/16-bit bus RGB |  |

| D[17:0] | t <sub>PDH</sub>                      | Data hold time                    | 15  | -   | ns   | interface mode    |  |

|         | PWDH                                  | DOTCLK high-level period          | 15  | -   | ns   |                   |  |

| DOTOLK  | PWDL                                  | DOTCLK low-level period           | 15  | -   | ns   |                   |  |

| DOTCLK  | t <sub>CYCD</sub>                     | DOTCLK cycle time                 | 100 | -   | ns   |                   |  |

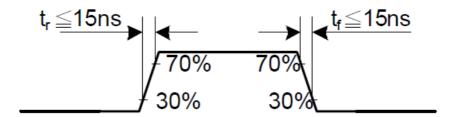

|         | t <sub>rgbr</sub> , t <sub>rgbf</sub> | DOTCLK,HSYNC,VSYNC rise/fall time | -   | 15  | ns   |                   |  |

| VSYNC / | tsyncs                                | VSYNC/HSYNC setup time            | 15  | -   | ns   |                   |  |

| HSYNC   | tsynch                                | VSYNC/HSYNC hold time             | 15  | -   | ns   |                   |  |

| DE      | t <sub>ENS</sub>                      | DE setup time                     | 15  | -   | ns   |                   |  |

| DE      | t <sub>ENH</sub>                      | DE hold time                      | 15  | -   | ns   |                   |  |

| D[47.0] | t <sub>POS</sub>                      | Data setup time                   | 15  | -   | ns   | 6-bit bus RGB     |  |

| D[17:0] | t <sub>PDH</sub>                      | Data hold time                    | 15  | -   | ns   | interface mode    |  |

|         | PWDH                                  | DOTCLK high-level pulse period    | 15  | -   | ns   |                   |  |

| DOTCLK  | PWDL                                  | DOTCLK low-level pulse period     | 15  | -   | ns   |                   |  |

| DOTCLK  | tcycD                                 | DOTCLK cycle time                 | 50  | -   | ns   |                   |  |

|         | t <sub>rgbr</sub> , t <sub>rgbf</sub> | DOTCLK,HSYNC,VSYNC rise/fall time | -   | 15  | ns   |                   |  |

Note: Ta = -30 to 70 °C, VDDI=1.65V to 3.3V, VCI=2.5V to 3.3V, AGND=VSS=0V

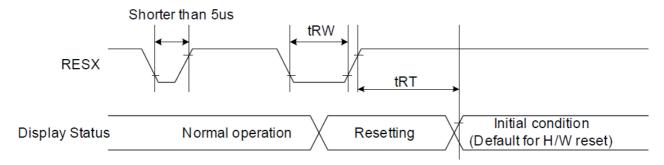

#### 8.2 Reset Timing

| Signal | Symbol             | Parameter            | Min             | Max                 | Unit |

|--------|--------------------|----------------------|-----------------|---------------------|------|

| RESX   | tRW                | Reset pulse duration | 10              |                     | uS   |

| 4DT    | tDT Depart connect |                      | 5<br>(note 1,5) | mS                  |      |

|        | tRT                | Reset cancel         |                 | 120<br>(note 1,6,7) | mS   |

Note 1: The reset cancel includes also required time for loading ID bytes, VCOM setting and other settings from NV memory to registers. This loading is done every time when there is HW reset cancel time (tRT) within 5 ms after a rising edge of RESX.

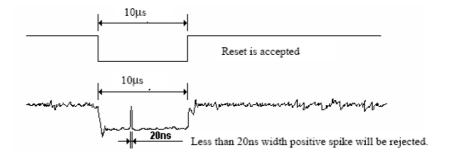

Note 2: Spike due to an electrostatic discharge on RESX line does not cause irregular system reset according to the table below:

| RESX Pulse           | Action         |

|----------------------|----------------|

| Shorter than 5us     | Reset Rejected |

| Longer than 10us     | Reset          |

| Between 5us and 10us | Reset starts   |

Note 3: During the Resetting period, the display will be blanked (The display is entering blanking sequence, which maximum time is 120 ms, when Reset Starts in Sleep Out –mode. The display remains the blank state in Sleep In -mode.) And then return to Default condition for Hardware Reset.

Note 4: Spike Rejection also applies during a valid reset pulse as shown below:

Note 5: When Reset applied during Sleep In Mode.

Note 6: When Reset applied during Sleep Out Mode.

Note 7: It is necessary to wait 5msec after releasing RESX before sending commands. Also Sleep Out command cannot be sent for 120msec.

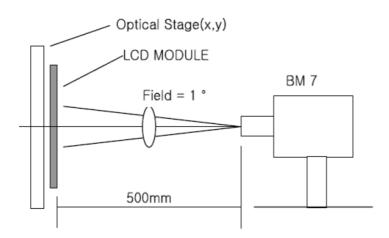

# 9. Optical Specification

Ta=25℃

| Item             |                 | Symbol | Condition           | Min | Тур. | Max.    | Unit   | Remark         |

|------------------|-----------------|--------|---------------------|-----|------|---------|--------|----------------|

| Contrast Ratio   |                 | CR     | Θ=00                | 300 | 500  | _       |        | Note1          |

| - Contract Ratio | Contrast realio |        | 0 0                 | 000 |      |         |        | Note2          |

| Response Tir     | nα              | Tr     | 25℃                 | -   | 10   | -       | ms     | Note1          |

| ixesponse iii    | 116             | Tf     | 25 0                |     | 10   | -       | ms     | Note3          |

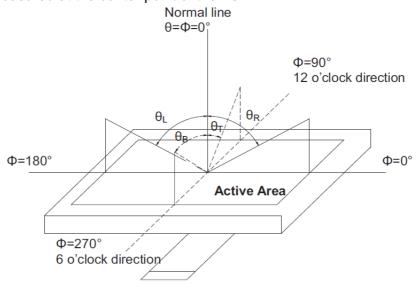

|                  |                 | ΘΤ     |                     | ı   | 55   | 1       |        |                |

| View Angles      |                 | ΘВ     | CR≧10               | -   | 65   | •       | Degree | Note4          |

| view Angles      |                 | ΘL     | CK=10               | -   | 65   | -       |        |                |

|                  |                 | ΘR     |                     | -   | 65   | -       |        |                |

|                  | White           | X      |                     |     | 0.28 | -       |        |                |

|                  |                 | Υ      |                     |     | 0.33 | -       |        |                |

|                  | Red             | Х      | Brightness<br>is on |     | 0.51 | -       | C      | Note5<br>Note1 |

| Chromoticity     |                 | Υ      |                     |     | 0.34 | -       |        |                |

| Chromaticity     | Green           | Х      |                     |     | 0.31 | -       |        |                |

|                  |                 | Υ      |                     |     | 0.56 | -       |        |                |

|                  |                 | Х      |                     |     | 0.15 | -       |        |                |

|                  | Blue            | Υ      |                     |     | 0.14 | -       |        |                |

| NTSC             |                 | S      |                     | 50  | 60   | -       | %      | Note5          |

| Luminanaa        |                 |        |                     |     | 240  |         | ad/m2  | Note1          |

| Luminance        |                 | L      |                     |     | 210  |         | cd/m2  | Note6          |

| Uniformity       |                 | U      |                     |     | 80   |         | %      | Note1          |

| Uniformity       |                 | U      |                     | -   | 60   | <b></b> | 7/0    | Note7          |

Note 1: Definition of optical measurement system.

Temperature =  $25^{\circ}$ C( $\pm 3^{\circ}$ C); LED back-light: ON, Environment brightness < 150 lx

Note 2: Contrast ratio is defined as follow:

Contrast Ratio= Surface Luminance with all white pixels

Surface Luminance with all black pixels

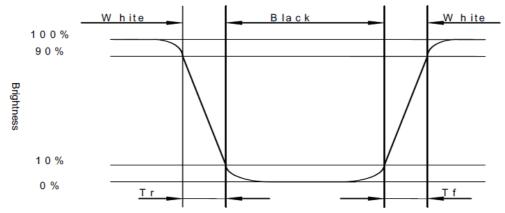

Note 3: Response time is defined as follow:

Response time is the time required for the display to transition from black to white (Rise Time, Tr) and from white to black(Decay Time, Tf).

Note 4: Viewing angle range is defined as follow: Viewing angle is measured at the center point of the LCD.

Note 5: Color chromaticity is defined as follow: (CIE1931)

Color coordinates measured at center point of LCD.

S= <u>area of RGB triangle</u> X 100%

#### Note 6: Luminance is defined as follow:

Luminance is defined as the brightness of all pixels "White" at the center of display area on optimum contrast.

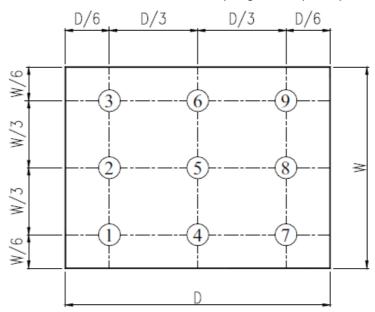

# Note 7: Luminance Uniformity is defined as follow: Active area is divided into 9 measuring areas (Refer Fig. 2). Every measuring point is placed at the center of each measuring area.

Uniformity (U) = Minimum Luminance( brightness ) in 9 points

Maximum Luminance( brightness ) in 9 points

Fig. 2 Definition of uniformity

#### 10. Environmental / Reliability Tests

| No | Test Item                            | Condition                                                                      | Judgment criteria                                        |

|----|--------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------|

| 1  | High Temp Operation                  | Ta=+70℃, 120hrs                                                                | Per table in below                                       |

| 2  | Low Temp Operation                   | Ta=-20℃, 120hrs                                                                | Per table in below                                       |

| 3  | High Temp Storage                    | Ts=+80℃, 120hrs                                                                | Per table in below                                       |

| 4  | Low Temp Storage                     | Ts=-30℃, 120hrs                                                                | Per table in below                                       |

| 5  | High Temp & High<br>Humidity Storage | Ts=+60℃, 90% RH ,120 hours                                                     | Per table in below (polarizer discoloration is excluded) |

| 6  | Thermal Shock<br>(Non-operation)     | -30°C 30 min~+80°C 30 min,<br>Change time:5min, 5 Cycles                       | Per table in below                                       |

| 7  | ESD (Operation)                      | C=150pF, R=330Ω , 5points/panel<br>Air:±8KV, 5times;<br>Contact:±4KV, 5 times; | Per table in below                                       |

| 8  | Vibration<br>(Non-operation)         | 10Hz~150Hz, 100m/s2,120min                                                     | Per table in below                                       |

| 9  | Shock<br>(Non-operation)             | Half-sine wave,300m/s2,11ms                                                    | Per table in below                                       |

| 10 | Package<br>Drop Test                 | Height:80 cm,<br>1 corner, 3 edges, 6 surfaces                                 | Per table in below                                       |

| INSPECTION             | CRITERION(after test)                                                               |

|------------------------|-------------------------------------------------------------------------------------|

| Appearance             | No Crack on the FPC, on the LCD Panel                                               |

| Alignment of LCD Panel | No Bubbles in the LCD Panel<br>No other Defects of Alignment in Active area         |

| Electrical current     | Within device specifications                                                        |

| Function / Display     | No Broken Circuit, No Short Circuit or No Black line<br>No Other Defects of Display |

#### 11. Precautions for Use of LCD Modules

#### 11.1 Safety

The liquid crystal in the LCD is poisonous. Do not put it in your mouth. If the liquid crystal touches your skin or

clothes, wash it off immediately using soap and water.

#### 11.2 Handling

- A. The LCD and touch panel is made of plate glass. Do not subject the panel to mechanical shock or to excessive force on its surface.

- B. Do not handle the product by holding the flexible pattern portion in order to assure the reliability

- C. Transparency is an important factor for the touch panel. Please wear clear finger sacks, gloves and mask to protect the touch panel from finger print or stain and also hold the portion outside the view area when handling the touch panel.

- D. Provide a space so that the panel does not come into contact with other components.

- E. To protect the product from external force, put a covering lens (acrylic board or similar board) and keep an appropriate gap between them.

- F. Transparent electrodes may be disconnected if the panel is used under environmental conditions where dew condensation occurs.

- G. Property of semiconductor devices may be affected when they are exposed to light, possibly resulting in IC malfunctions.

- H. To prevent such IC malfunctions, your design and mounting layout shall be done in the way that the IC is not exposed to light in actual use.

#### 11.3 Static Electricity

- A. Ground soldering iron tips, tools and testers when they are in operation.

- B. Ground your body when handling the products.

- C. Power on the LCD module before applying the voltage to the input terminals.

- D. Do not apply voltage which exceeds the absolute maximum rating.

- E. Store the products in an anti-electrostatic bag or container.

#### 11.4 Storage

- A. Store the products in a dark place at +25 ℃±10 ℃ with low humidity (40% RH to 60% RH). Don't expose to sunlight or fluorescent light.

- B. Storage in a clean environment, free from dust, active gas, and solvent.

#### 11.5 Cleaning

- A. Do not wipe the touch panel with dry cloth, as it may cause scratch.

- B. Wipe off the stain on the product by using soft cloth moistened with ethanol. Do not

allow ethanol to get in between the upper film and the bottom glass. It may cause peeling issue or defective operation. Do not use any organic solvent or detergent other than ethanol.

#### 11.6 Cautions for installing and assembling

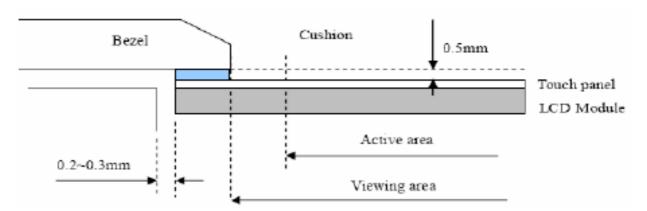

- A. Bezel edge must be positioned in the area between the Active area and View area. The bezel may press the touch screen and cause activation if the edge touches the active area. A gap of approximately 0.5mm is needed between the bezel and the top electrode. It may cause unexpected activation if the gap is too narrow. There is a tolerance of 0.2 to 0.3mm for the outside dimensions of the touch panel and tail. A gap must be made to absorb the tolerance in the case and connector.

- B. In order to make the display assembly stable and firm, Displaytech recommends to design some supporting at the display backside, especially for the display with tapeattached touch panel, such supporting is important and essential, or else, the display may drop-off from front after some period of time.

- C. Do not display the fixed pattern for a long time because it may develop image sticking due to the LCD structure. If the screen is displayed with fixed pattern, use a screen saver.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Displaytech:

DT028BTFT-PTS2