## MB15E07SL

## ASSP Single Serial Input PLL Frequency Synthesizer On-chip 2.5 GHz Prescaler

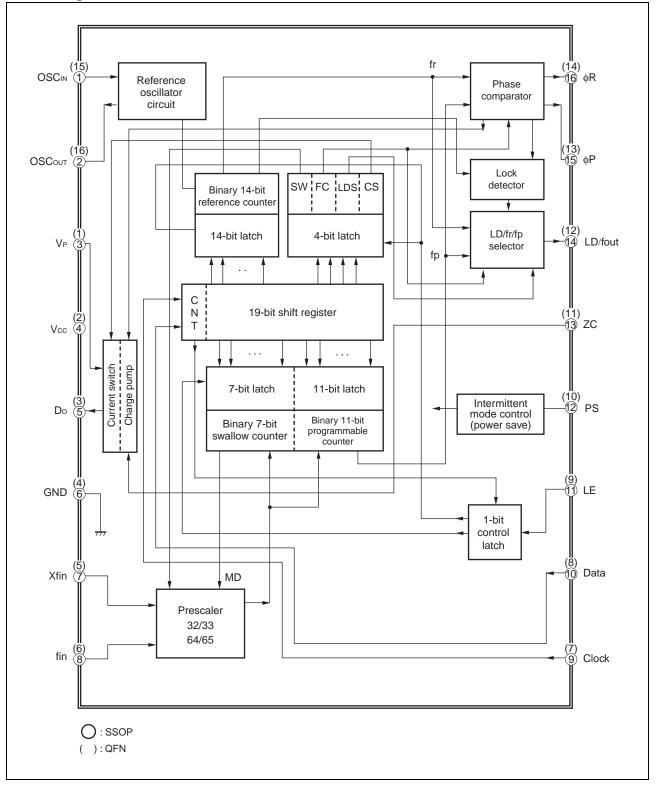

The Cypress MB15E07SL is a serial input Phase Locked Loop (PLL) frequency synthesizer with a 2.5 GHz prescaler. The 2.5 GHz prescaler has a dual modulus division ratio of 32/33 or 64/65 enabling pulse swallowing operation.

The supply voltage range is between 2.4 V and 3.6 V. The MB15E07SL uses the latest BiCMOS process, as a result the supply current is typically 3.5 mA at 2.7 V. A refined charge pump supplies well-balanced output currents of 1.5 mA and 6 mA. The charge pump current is selectable by serial data.

### Features

- High frequency operation: 2.5 GHz Max

- Low power supply voltage: Vcc = 2.4 to 3.6 V

- Ultra Low power supply current:Icc = 3.5 mA Typ (Vcc = Vp = 2.7 V, Ta = +25°C, in locking state) Icc = 4.0 mA Typ (Vcc = Vp = 3.0 V, Ta = +25°C, in locking state)

Direct power saving function: Power supply current in power saving mode Typ 0.1 μA (Vcc = Vp = 3.0 V, Ta = +25°C), Max 10 μA (Vcc = Vp = 3.0 V)

Dual modulus prescaler: 32/33 or 64/65

Serial input 14-bit programmable

- reference divider: R = 3 to 16.383

- Serial input programmable divider consisting of:

Binary 7-bit swallow counter: 0 to 127

- □ Binary 11-bit programmable counter: 3 to 2,047

- Software selectable charge pump current

- On-chip phase control for phase comparator

- Operating temperature: Ta = -40 to +85°C

- Pin compatible with MB15E07, MB15E07L

## MB15E07SL

## Contents

| Pin Assignments                             | 3  |

|---------------------------------------------|----|

| Pin Descriptions                            | 4  |

| Block Diagram                               | 5  |

| Absolute Maximum Ratings                    | 6  |

| Recommended Operating Conditions            | 6  |

| Electrical Characteristics                  | 7  |

| Functional Description                      | 9  |

| Serial Data Input Timing                    |    |

| Phase Comparator Output Waveform            | 14 |

| Measurment Circuit                          |    |

| (for Measuring Input Sensitivity fin/OSCIN) | 15 |

| Typical Characteristics                 | 16 |

|-----------------------------------------|----|

| fin input sensitivity                   | 16 |

| OSCIN input sensitivity                 | 17 |

| Do output current                       |    |

| fin input impedance                     | 19 |

| OSCIN input impedance                   | 19 |

| Reference Information                   | 20 |

| Application Example                     |    |

| Usage Precautions                       | 23 |

| Ordering Information                    | 24 |

| Package Dimensions                      | 25 |

| Document History                        |    |

| Sales, Solutions, and Legal Information |    |

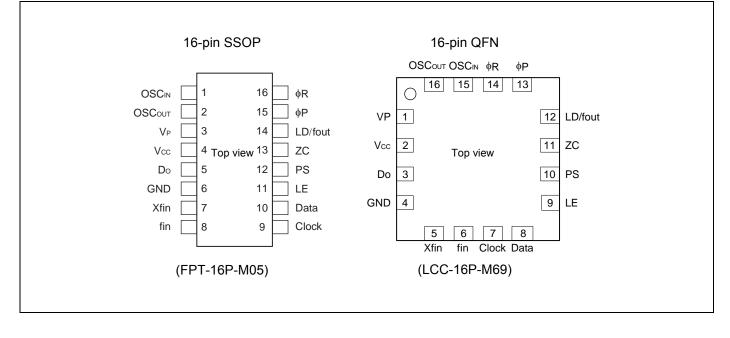

## 1. Pin Assignments

## 2. Pin Descriptions

| Pin  | no. | Diaman   | 1/0 | Descriptions                                                                                                                                                                                                                                                 |

|------|-----|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSOP | QFN | Pin name | I/O | Descriptions                                                                                                                                                                                                                                                 |

| 1    | 15  | OSCIN    | I   | Programmable reference divider input. Connection to a TCXO.                                                                                                                                                                                                  |

| 2    | 16  | OSCOUT   | 0   | Oscillator output.                                                                                                                                                                                                                                           |

| 3    | 1   | VP       | -   | Power supply voltage input for the charge pump.                                                                                                                                                                                                              |

| 4    | 2   | Vcc      | -   | Power supply voltage input.                                                                                                                                                                                                                                  |

| 5    | 3   | Do       | 0   | Charge pump output.<br>Phase of the charge pump can be selected via programming of the FC bit.                                                                                                                                                               |

| 6    | 4   | GND      | _   | Ground.                                                                                                                                                                                                                                                      |

| 7    | 5   | Xfin     | Ι   | Prescaler complementary input, which should be grounded via a capacitor.                                                                                                                                                                                     |

| 8    | 6   | fin      | I   | Prescaler input.<br>Connection to an external VCO should be done via AC coupling.                                                                                                                                                                            |

| 9    | 7   | Clock    | I   | Clock input for the 19-bit shift register.<br>Data is shifted into the shift register on the rising edge of the clock.<br>(Open is prohibited.)                                                                                                              |

| 10   | 8   | Data     | I   | Serial data input using binary code.<br>The last bit of the data is a control bit. (Open is prohibited.)                                                                                                                                                     |

| 11   | 9   | LE       | I   | Load enable signal input. (Open is prohibited.)<br>When LE is set high, the data in the shift register is transferred to a latch according to the<br>control bit in the serial data.                                                                         |

| 12   | 10  | PS       | I   | Power saving mode control. This pin must be set at "L" at Power-ON.<br>(Open is prohibited.)<br>PS = "H"; Normal mode<br>PS = "L"; Power saving mode                                                                                                         |

| 13   | 11  | ZC       | I   | Forced high-impedance control for the charge pump (with internal pull up resistor.)<br>ZC = "H"; Normal Do output.<br>ZC = "L"; Do becomes high impedance.                                                                                                   |

| 14   | 12  | LD/fout  | 0   | Lock detect signal output (LD)/phase comparator monitoring output (fout).<br>The output signal is selected via programming of the LDS bit.<br>LDS = "H"; outputs fout (fr/fp monitoring output)<br>LDS = "L"; outputs LD ("H" at locking, "L" at unlocking.) |

| 15   | 13  | φP       | 0   | Phase comparator N-channel open drain output for an external charge pump. Phase can be selected via programming of the FC bit.                                                                                                                               |

| 16   | 14  | φR       | 0   | Phase comparator CMOS output for an external charge pump. Phase can be selected via programming of the FC bit.                                                                                                                                               |

## 3. Block Diagram

## 4. Absolute Maximum Ratings

| Parameter            | Symbol | Condition | Rat  | ting      | Unit | Remark  |

|----------------------|--------|-----------|------|-----------|------|---------|

| Farameter            | Symbol | Condition | Min  | Max       | Unit | Reindik |

| Power supply voltage | Vcc    | -         | -0.5 | 4.0       | V    |         |

|                      | VP     | -         | Vcc  | 6.0       | V    |         |

| Input voltage        | Vı     | -         | -0.5 | Vcc + 0.5 | V    |         |

| Output voltage       | Vo     | Except Do | GND  | Vcc       | V    |         |

|                      | Vo     | Do        | GND  | VP        | V    |         |

| Storage temperature  | Tstg   | -         | -55  | +125      | °C   |         |

**Warning:** Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

## 5. Recommended Operating Conditions

| Parameter             | Symbol |     | Value | Unit | Remark |        |

|-----------------------|--------|-----|-------|------|--------|--------|

| Falameter             | Symbol | Min | Тур   | Мах  |        | Remark |

| Power supply voltage  | Vcc    | 2.4 | 3.0   | 3.6  | V      |        |

|                       | VP     | Vcc | _     | 5.5  | V      |        |

| Input voltage         | Vı     | GND | _     | Vcc  | V      |        |

| Operating temperature | Та     | -40 | _     | +85  | °C     |        |

Warning: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure. No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

## 6. Electrical Characteristics

|                               |                         |                            |                                                                                         |               | (VCC Z               | ,                          | 1a = -40 10 | 100 0) |

|-------------------------------|-------------------------|----------------------------|-----------------------------------------------------------------------------------------|---------------|----------------------|----------------------------|-------------|--------|

| Parameter                     |                         | Symbol                     | Condi                                                                                   | ion           |                      | Value                      |             | Unit   |

| Power supply current*1        |                         | lcc*1                      | fin = 2500<br>V <sub>CC</sub> = V <sub>P</sub> =<br>(V <sub>CC</sub> = V <sub>P</sub> = | = 2.7 V       | Min<br>–             | <b>Typ</b><br>3.5<br>(4.0) | Max<br>–    | mA     |

| Power saving current          |                         | PS                         | ZC = "H" c                                                                              | ,             | _                    | 0.1*2                      | 10          | μA     |

| Operating frequency           | fin                     | fın                        | _                                                                                       | -             | 700                  | _                          | 2500        | MHz    |

|                               | OSCIN                   | OSCIN                      | _                                                                                       |               | 3                    | _                          | 40          | MHz    |

| Input sensitivity             | fin* <sup>3</sup>       | Pfin                       | 50 <b>Ω</b> system                                                                      | SSOP          | -15                  | _                          | +2          | dBm    |

|                               |                         |                            | (Refer to the<br>measurement<br>circuit.)                                               | QFN           | -12                  | _                          | +2          |        |

|                               | OSCIN*3                 | Vosc                       | _                                                                                       |               | 0.5                  | -                          | Vcc         | Vp-p   |

| "H" level input voltage       | Data,                   | Vін                        | _                                                                                       |               | Vcc × 0.7            | -                          | -           | V      |

| "L" level input voltage       | Clock,<br>LE, PS,<br>ZC | Vil                        | _                                                                                       | -             | -                    | Vcc × 0.3                  |             |        |

| "H" level input current       | Data,                   | <b>I</b> ⊮*4               | _                                                                                       | -1.0          | _                    | +1.0                       | μA          |        |

| "L" level input current       | Clock,<br>LE, PS        | <b>I</b> ı∟*4              | -                                                                                       |               | -1.0                 | _                          | +1.0        |        |

| "H" level input current       | OSCIN                   | Ін                         | _                                                                                       |               | 0                    | _                          | +100        | μA     |

| "L" level input current       |                         | I∟* <sup>4</sup>           | _                                                                                       |               | -100                 | _                          | 0           |        |

| "H" level input current       | ZC                      | <b>I</b> ін*4              | _                                                                                       |               | -1.0                 | _                          | +1.0        | μA     |

| "L" level input current       |                         | I∟*4                       | Pull up                                                                                 | nput          | -100                 | _                          | 0           |        |

| "L" level output voltage      | фР                      | Vol                        | Open drair                                                                              | n output      | _                    | _                          | 0.4         | V      |

| "H" level output voltage      | <b>φ</b> R,             | Vон                        | $V_{CC} = V_{P} = 3.0 V$                                                                | , Іон = –1 mA | Vcc – 0.4            | _                          | -           | V      |

| "L" level output voltage      | LD/fout                 | Vol                        | $V_{CC} = V_{P} = 3.0$ V                                                                | /, Io∟ = 1 mA | _                    | _                          | 0.4         |        |

| "H" level output voltage      | Do                      | Vdoh                       | V <sub>CC</sub> = V <sub>P</sub> =<br>І <sub>DOH</sub> = –0                             | ,             | V <sub>P</sub> – 0.4 | -                          | -           | V      |

| "L" level output voltage      |                         | Vdol                       | $V_{CC} = V_{P} = I_{DOL} = 0.$                                                         | )             | -                    | -                          | 0.4         |        |

| High impedance cutoff current | Do                      | IOFF                       | $V_{CC} = V_{P} = V_{OFF} = 0.5 V to$                                                   |               | -                    | -                          | 2.5         | nA     |

| "L" level output current      | фР                      | Iol                        | Open drair                                                                              | n output      | 1.0                  | _                          | -           | mA     |

| "H" level output current      | <b>φ</b> R,             | Іон                        | _                                                                                       |               | _                    | _                          | -1.0        | mA     |

| "L" level output current      | LD/fout                 | lol                        | _                                                                                       |               | 1.0                  | -                          | _           |        |

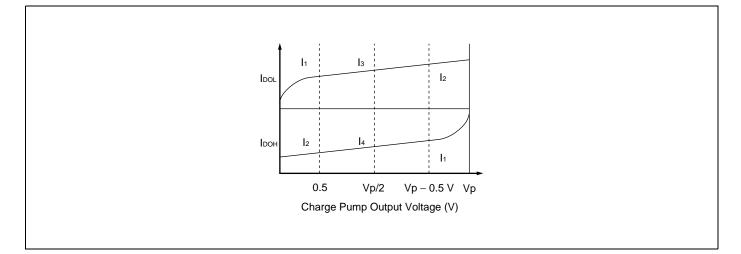

| "H" level output current      | Do                      | <b>І</b> дон <sup>*4</sup> | $V_{\rm CC} = 3 V,$                                                                     | CS bit = "H"  | -                    | -6.0                       | -           | mA     |

|                               |                         |                            | $V_P = 3 V$ ,<br>$V_{DO} = V_P/2$                                                       | CS bit = "L"  | -                    | -1.5                       | -           |        |

| "L" level output current      |                         | IDOL                       | Ta = +25°C                                                                              | CS bit = "H"  | -                    | 6.0                        | -           |        |

|                               |                         |                            |                                                                                         | CS bit = "L"  | -                    | 1.5                        | -           |        |

| Charge pump current rate      | Idol/Idoh               | DOMT*5                     | V <sub>DO</sub> = V                                                                     |               | -                    | 3                          | -           | %      |

|                               | vs V <sub>DO</sub>      | DOVD*6                     | $0.5 V \leq V_{DO} \leq$                                                                |               | -                    | 10                         | -           | %      |

|                               | vs Ta                   | DOTA*7                     | – 40°C ≤ Ta                                                                             | ≤+85°C        | -                    | 10                         | -           | %      |

(V<sub>CC</sub> = 2.4 to 3.6 V, Ta = -40 to  $+85^{\circ}$ C)

- \*1 : Conditions; fosc = 12 MHz, Ta = +25°C, in locking state.

- \*2 :  $V_{CC}$  =  $V_P$  = 3.0 V, fosc = 12.8 MHz, Ta = +25°C, in power saving mode

- \*3 : AC coupling. 1000 pF capacitor is connected under the condition of Min operating frequency.

- \*4 : The symbol "--" (minus) means direction of current flow.

- \*5 : V<sub>CC</sub> = V<sub>P</sub> = 3.0 V, Ta = +25°C ( $|I_3| |I_4|$ ) / [( $|I_3| + |I_4|$ ) /2] × 100(%)

- \*6 :  $V_{CC} = V_P = 3.0 \text{ V}$ , Ta = +25°C [(|I<sub>2</sub>| |I<sub>1</sub>|) /2] / [(|I<sub>1</sub>| + |I<sub>2</sub>|) /2] × 100(%) (Applied to each IDOL, IDOH)

- \*7 : Vcc = VP = 3.0 V, VDo = VP/2 (|IDO(85°C) IDO(-40°C)| /2) / (|IDO(85°C) + IDO(-40°C)| /2) × 100(%) (Applied to each IDOL, IDOH)

## 7. Functional Description

### 1. Pulse Swallow Function

The divide ratio can be calculated using the following equation:

$f_{VCO} = [(M \times N) + A] \times f_{OSC} \div R (A < N)$

fvco:Output frequency of external voltage controlled oscillator (VCO) N:Preset divide ratio of binary 11-bit programmable counter (3 to 2,047) A:Preset divide ratio of binary 7-bit swallow counter ( $0 \le A \le 127$ ) fosc:Output frequency of the reference frequency oscillator R:Preset divide ratio of binary 14-bit programmable reference counter (3 to 16,383) M:Preset divide ratio of modulus prescaler (32 or 64)

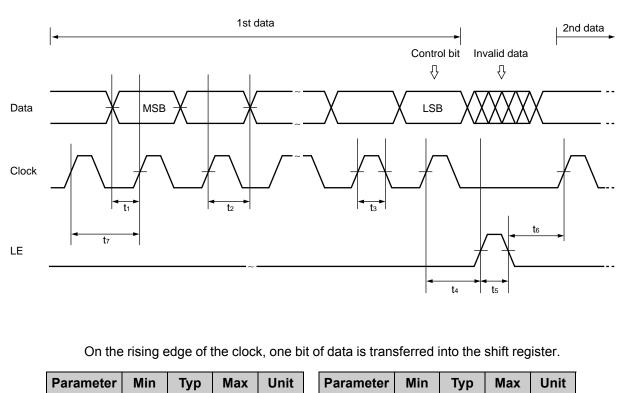

2. Serial Data Input

Serial data is processed using the Data, Clock, and LE pins. Serial data controls the programmable reference divider and the programmable divider separately.

Binary serial data is entered through the Data pin.

One bit of data is shifted into the shift register on the rising edge of the Clock. When the LE signal pin is taken high, stored data is latched according to the control bit data as follows:

#### Table 1. Control Bit

| Control bit (CNT) | Destination of serial data             |

|-------------------|----------------------------------------|

| Н                 | For the programmable reference divider |

| L                 | For the programmable divider           |

#### 1. Shift Register Configuration

| SB<br>▼                              |        |                                   |                             |                    |                              |                         |                | Data                    | a Flow | <i>ı</i> — |         |         |         |         |      |    | I                                                        | MSB<br>↓                     |

|--------------------------------------|--------|-----------------------------------|-----------------------------|--------------------|------------------------------|-------------------------|----------------|-------------------------|--------|------------|---------|---------|---------|---------|------|----|----------------------------------------------------------|------------------------------|

| 1                                    | 2      | 3                                 | 4                           | 5                  | 6                            | 7                       | 8              | 9                       | 10     | 11         | 12      | 13      | 14      | 15      | 16   | 17 | 18                                                       | 19                           |

| C<br>N<br>T                          | R<br>1 | R<br>2                            | R<br>3                      | R<br>4             | R<br>5                       | R<br>6                  | R<br>7         | R<br>8                  | R<br>9 | R<br>10    | R<br>11 | R<br>12 | R<br>13 | R<br>14 | SW   | FC | LDS                                                      | CS                           |

| CNT<br>R1 t<br>SW<br>FC<br>LDS<br>CS | o R14  | 1 : Div<br>: Div<br>: Pha<br>: LD | ride ra<br>ase с<br>/fouт s | atio se<br>atio se | tting t<br>bit for<br>select | the p<br>bit for<br>bit | the pr<br>hase | ogran<br>escale<br>comp | er (32 | /33 or     |         |         | ter (3  | to 16,  | 383) |    | [Table<br>[Table<br>[Table<br>[Table<br>[Table<br>[Table | e 2]<br>e 5]<br>e 8]<br>e 7] |

(Continued)

| SB<br>V     |                                     |        |        |         |                    |        |        | Dat    | a Flov | v —    | •      |        |        |        |           |                         |         | MSE<br>↓ |

|-------------|-------------------------------------|--------|--------|---------|--------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------|-------------------------|---------|----------|

| 1           | 2                                   | 3      | 4      | 5       | 6                  | 7      | 8      | 9      | 10     | 11     | 12     | 13     | 14     | 15     | 16        | 17                      | 18      | 19       |

| C<br>N<br>T | A<br>1                              | A<br>2 | A<br>3 | A<br>4  | A<br>5             | A<br>6 | A<br>7 | N<br>1 | N<br>2 | N<br>3 | N<br>4 | N<br>5 | N<br>6 | N<br>7 | N<br>8    | N<br>9                  | N<br>10 | N<br>11  |

| <b>N</b> 1  | NT<br>I to N<br>I to A <sup>r</sup> | 11 : D |        | ratio s | setting<br>setting |        |        |        |        |        |        |        | 2,047  | 7)     | -<br>[Tab | le 1]<br>le 3]<br>le 4] |         |          |

### Table 2. Binary 14-bit Programmable Reference Counter Data Setting

| Divide ratio<br>(R) | R14 | R13 | R12 | R11 | R10 | R9 | R8 | R7 | R6 | R5 | R4 | R3 | R2 | R1 |

|---------------------|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|

| 3                   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  |

| 4                   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| •                   | •   | •   |     | •   | •   | •  |    |    |    | •  | •  | •  |    |    |

| 16383               | 1   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

Note : Divide ratio less than 3 is prohibited.

### Table 3. Binary 11-bit Programmable Counter Data Setting

| Divide ratio (N) | N11 | N10 | N9 | N8 | N7 | N6 | N5 | N4 | N3 | N2 | N1 |

|------------------|-----|-----|----|----|----|----|----|----|----|----|----|

| 3                | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  |

| 4                | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| •                | •   | •   | •  | •  | •  | •  | •  | •  | •  | •  | •  |

| 2047             | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

Note : Divide ratio less than 3 is prohibited.

### Table 4. Binary 7-bit Swallow Counter Data Setting

| Divide ratio (A) | A7 | A6 | A5 | A4 | A3 | A2 | A1 |

|------------------|----|----|----|----|----|----|----|

| 0                | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 1                | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

| •                | •  | •  | •  | •  | •  | •  | •  |

| 127              | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

#### Table 5. Prescaler Data Setting

| SW | Prescaler divide ratio |

|----|------------------------|

| Н  | 32/33                  |

| L  | 64/65                  |

#### Table 6. Charge Pump Current Setting

| CS | Current value |

|----|---------------|

| Н  | ±6.0 mA       |

| L  | ±1.5 mA       |

#### Table 7. LD/fout Output Select Data Setting

| LDS | LD/four output signal |

|-----|-----------------------|

| Н   | fout signal           |

| L   | LD signal             |

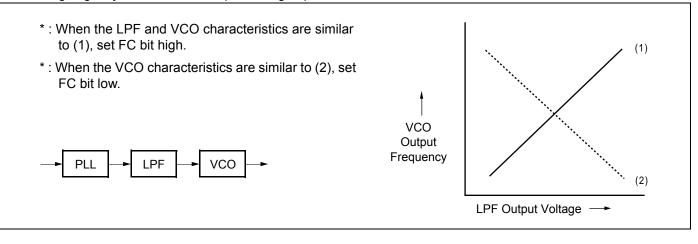

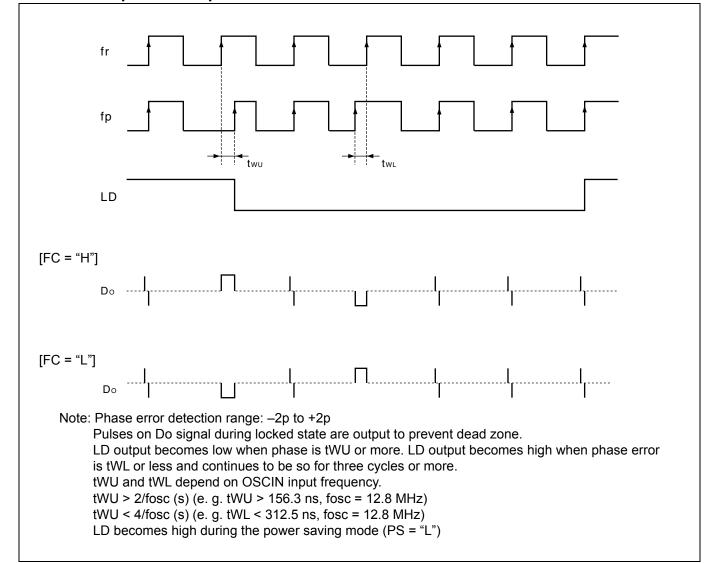

2. Relation between the FC Input and Phase Characteristics

The FC bit changes the phase characteristics of the phase comparator. Both the internal charge pump output level (Do) and the phase comparator output ( $\phi$ R,  $\phi$ P) are reversed according to the FC bit. Also, the monitor pin (four) output is controlled by the FC bit. The relationship between the FC bit and each of Do,  $\phi$ R, and  $\phi$ P is shown below.

#### Table 8. FC Bit Data Setting (LDS = "H")

|         | FC = High |            |    |           |    | FC =       | Low |           |

|---------|-----------|------------|----|-----------|----|------------|-----|-----------|

|         | Do        | φ <b>R</b> | φΡ | LD/fout   | Do | φ <b>R</b> | φΡ  | LD/fout   |

| fr > f⊦ | Н         | L          | L  | fout = fr | L  | Н          | Z*  | fout = fp |

| fr < f⊵ | L         | Н          | Z* |           | Н  | L          | L   |           |

| fr = f⊳ | Z*        | L          | Z* |           | Z* | L          | Z*  |           |

\*: High-Z

#### When designing a synthesizer, the FC pin setting depends on the VCO and LPF characteristics.

#### 3. Do Output Control

#### Table 9. ZC Pin Setting

| ZC pin | Do output      |

|--------|----------------|

| Н      | Normal output  |

| L      | High impedance |

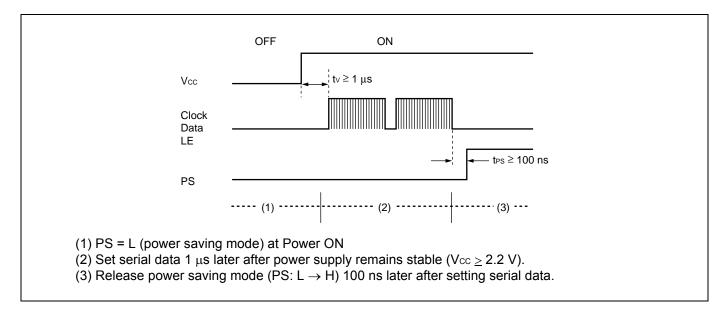

4. Power Saving Mode (Intermittent Mode Control Circuit)

#### Table 10. PS Pin Setting

| PS pin | Status            |

|--------|-------------------|

| Н      | Normal mode       |

| L      | Power saving mode |

The intermittent mode control circuit reduces the PLL power consumption.

By setting the PS pin low, the device enters into the power saving mode, reducing the current consumption. See the Electrical Characteristics chart for the specific value.

The phase detector output, Do, becomes high impedance.

For the signal PLL, the lock detector, LD, remains high, indicating a locked condition.

Setting the PS pin high, releases the power saving mode, and the device works normally.

The intermittent mode control circuit also ensures a smooth startup when the device returns to normal operation. When the PLL is returned to normal operation, the phase comparator output signal is unpredictable. This is because of the unknown relationship between the comparison frequency (fp) and the reference frequency (fr) which can cause a major change in the comparator output, resulting in a VCO frequency jump and an increase in lockup time.

To prevent a major VCO frequency jump, the intermittent mode control circuit limits the magnitude of the error signal from the phase detector when it returns to normal operation.

When power (V<sub>cc</sub>) is first applied, the device must be in standby mode, PS = Low, for at least 1  $\mu$ s.

Note : PS pin must be set "L" for Power-ON.

## 8. Serial Data Input Timing

| Parameter | Min | Тур | мах | Unit |

|-----------|-----|-----|-----|------|

| t1        | 20  | I   | Ι   | ns   |

| t2        | 20  | -   | -   | ns   |

| t₃        | 30  | -   | -   | ns   |

| t4        | 30  | -   | -   | ns   |

| Parameter      | Min | Тур | Мах | Unit |

|----------------|-----|-----|-----|------|

| t₅             | 100 | _   | _   | ns   |

| t <sub>6</sub> | 20  | _   | _   | ns   |

| t7             | 100 | -   | _   | ns   |

Note : LE should be "L" when the data is transferred into the shift register.

### 9. Phase Comparator Output Waveform

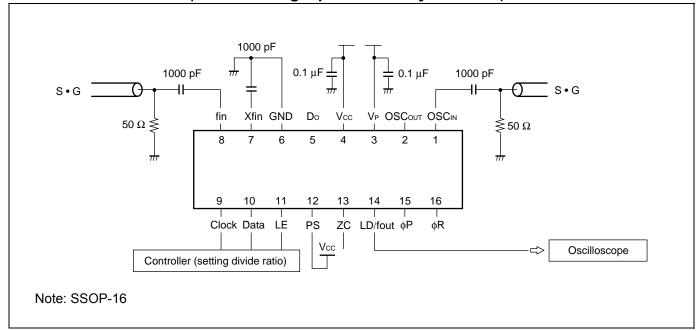

## 10. Measurment Circuit (for Measuring Input Sensitivity fin/OSCIN)

## **11. Typical Characteristics**

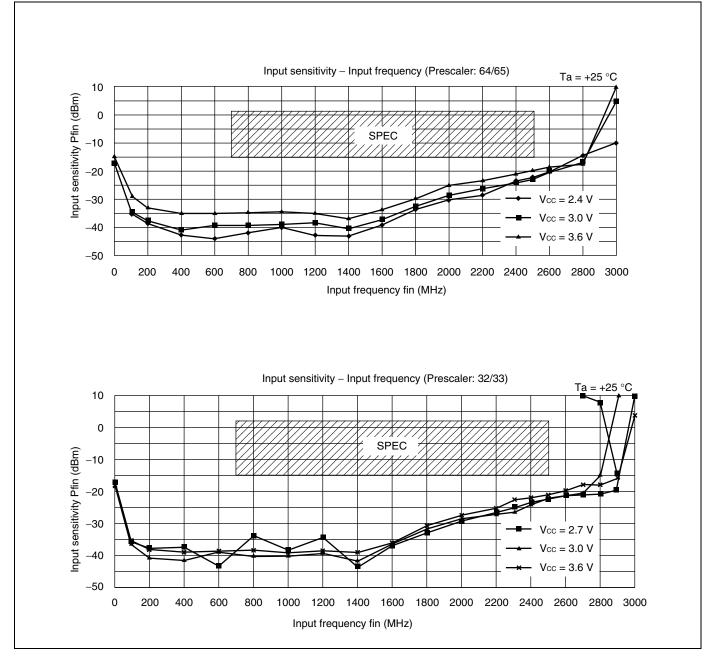

### 11.1 fin input sensitivity

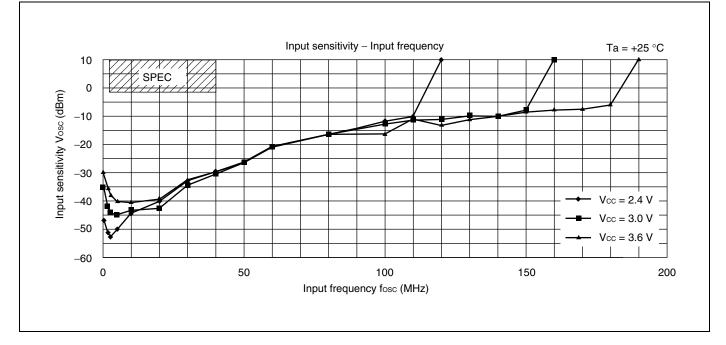

### 11.2 OSCIN input sensitivity

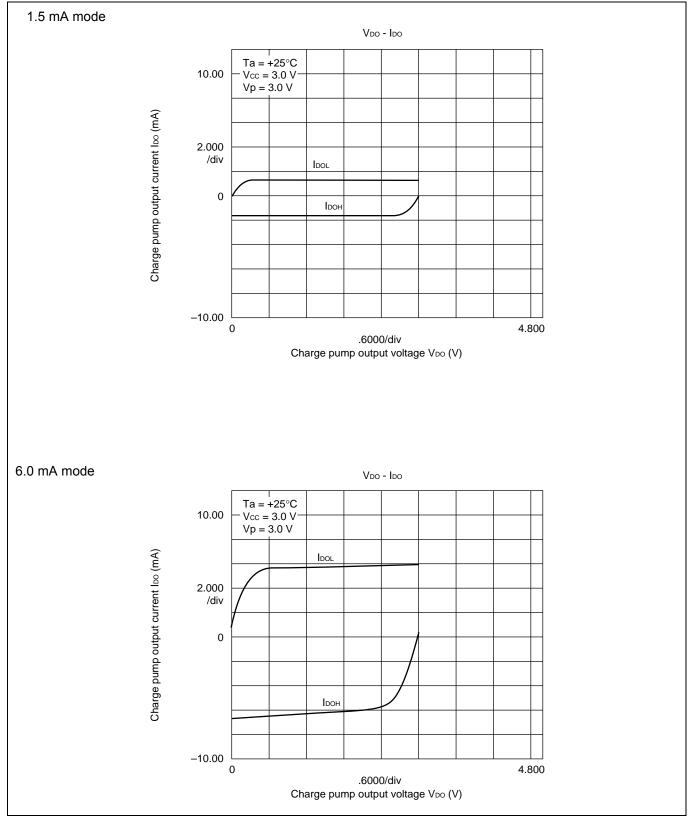

### 11.3 Do output current

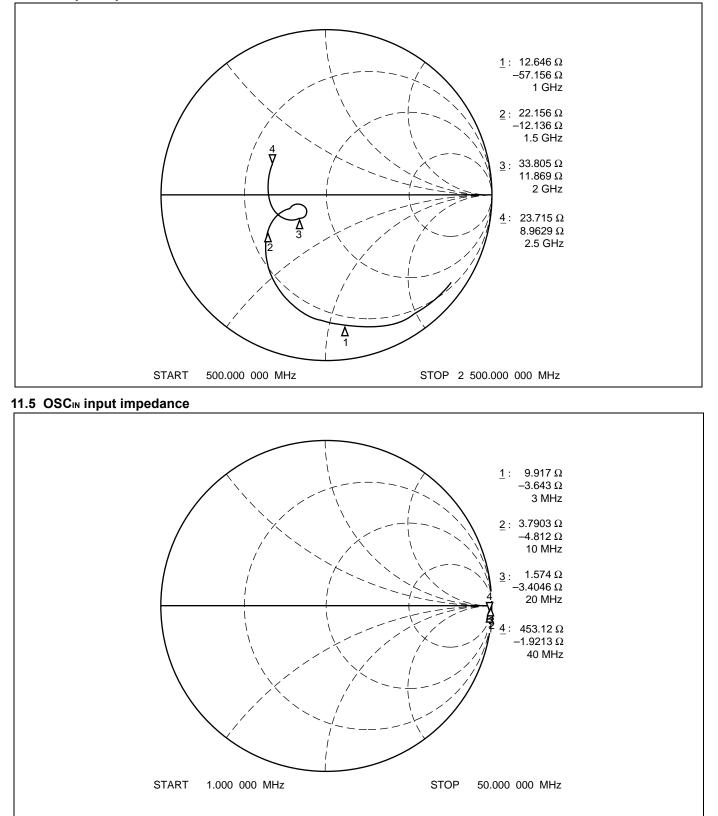

### 11.4 fin input impedance

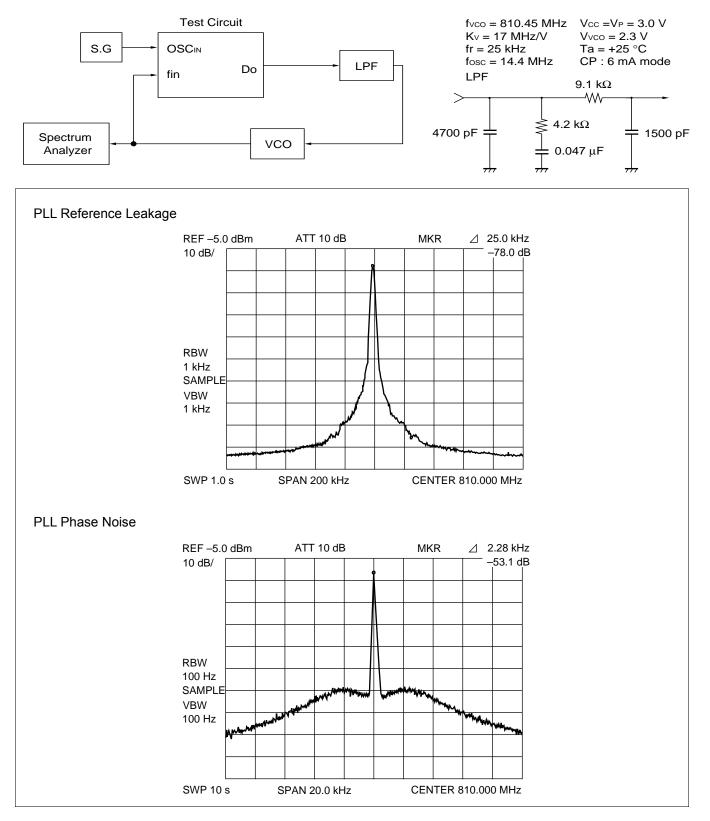

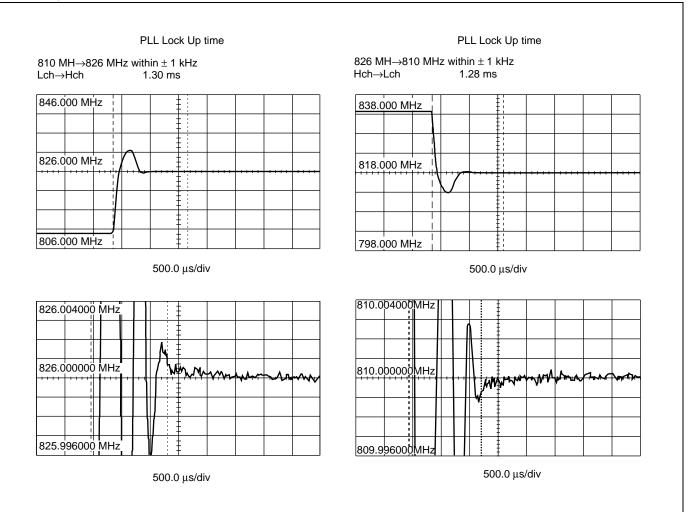

## 12. Reference Information

### (Continued)

## MB15E07SL

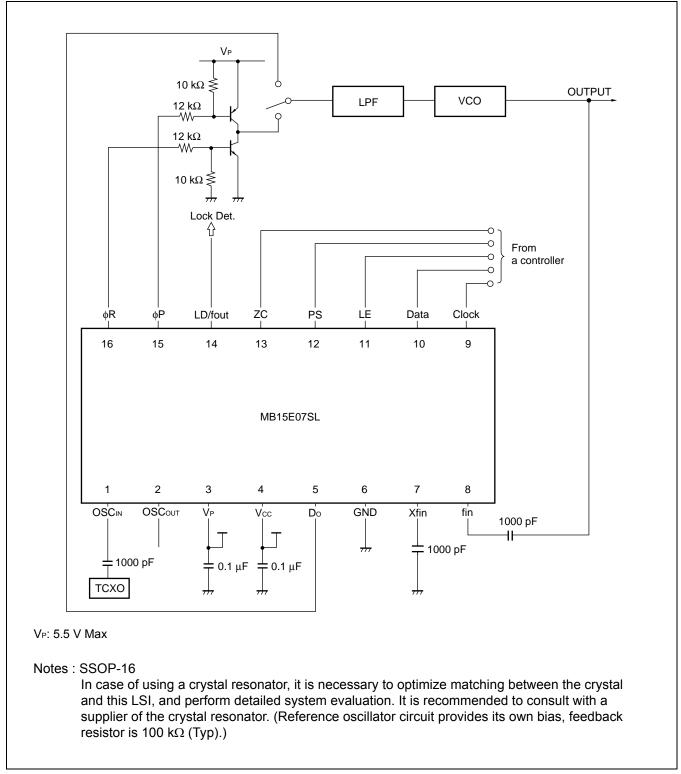

## 13. Application Example

## 14. Usage Precautions

To protect against damage by electrostatic discharge, note the following handling precautions:

Store and transport devices in conductive containers.

Use properly grounded workstations, tools, and equipment.

Turn off power before inserting device into or removing device from a socket.

Protect leads with a conductive sheet when transporting a board-mounted device.

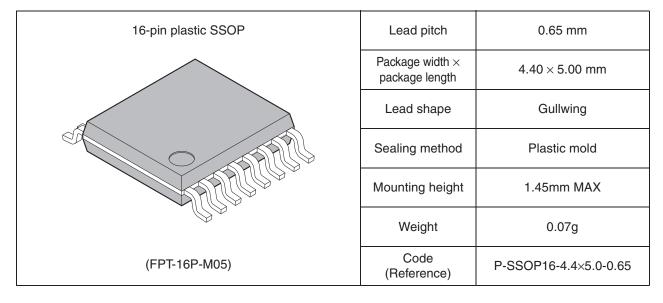

## 15. Ordering Information

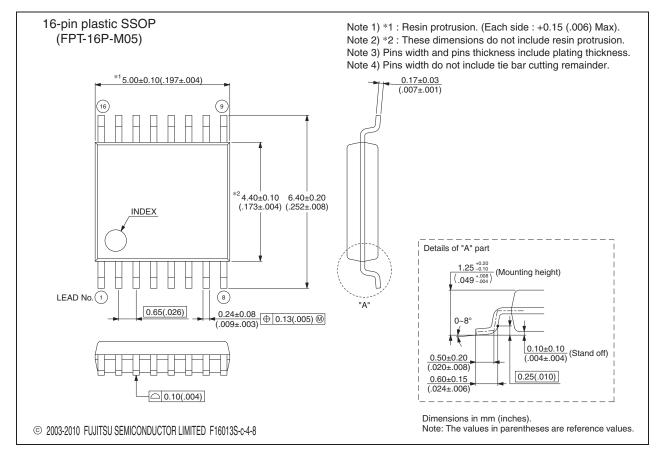

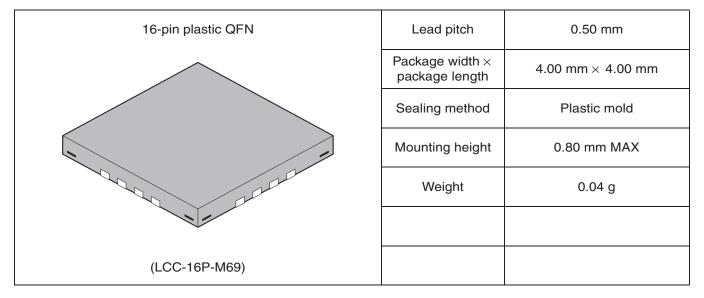

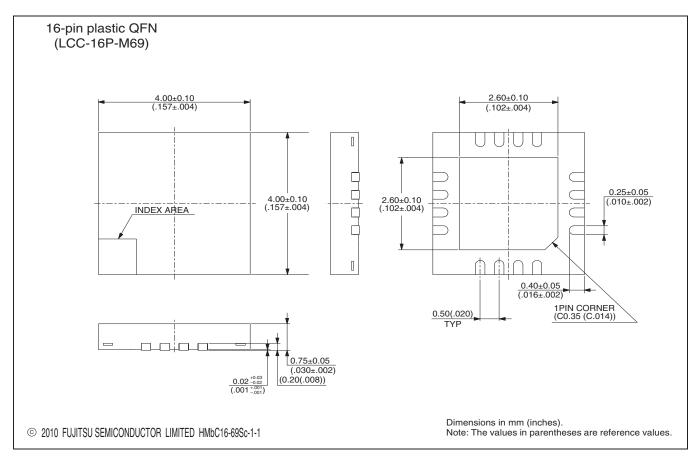

| Part number   | Package                               | Remarks |

|---------------|---------------------------------------|---------|

| MB15E07SLPFV1 | 16-pin, Plastic SSOP<br>(FPT-16P-M05) |         |

| MB15E07SLWQN  | 16-pin plastic QFN<br>(LCC-16P-M69)   |         |

## 16. Package Dimensions

## **Document History**

### Spansion Publication Number: DS04–21358–5E

| Document Title: MB15E07SL ASSP Single Serial Input PLL Frequency Synthesizer On-chip 2.5 GHz Prescaler<br>Document Number: 002-08429 |                                                        |      |            |                             |  |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------|------------|-----------------------------|--|

| Revision                                                                                                                             | evision ECN Orig. of Change Date Description of Change |      |            |                             |  |

| **                                                                                                                                   | -                                                      | TAOA | 09/06/2011 | Initial Release             |  |

| *A                                                                                                                                   | 5576747                                                | TAOA | 01/06/2017 | Updated to Cypress Template |  |

## Sales, Solutions, and Legal Information

### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products

| ARM <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Internet of Things                                    | cypress.com/iot        |

| Lighting & Power Control                              | cypress.com/powerpsoc  |

| Memory                                                | cypress.com/memory     |

| PSoC                                                  | cypress.com/psoc       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless/RF                                           | cypress.com/wireless   |

### **PSoC<sup>®</sup>Solutions**

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### **Cypress Developer Community**

Forums | WICED IoT Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2011-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hareby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or systems, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Cypress Semiconductor: <u>MB15E07SLWQN-G-JK-ERE1</u> <u>MB15E07SLPFV1-G-ER-6E1</u>