**DATA SHEET**

# SKY53510/SKY53580/SKY53540 Low-Power DC to 3.1 GHz Ultra-Low Additive Jitter Differential Clock Buffers

The SKY53510/80/40 family of fanout buffers is ideal for high-frequency, low-jitter clock distribution. These devices feature universal level format translation and ultra-low additive RMS phase jitter over a wide range of conditions, including frequency and input clock slew rate.

Separate core and output voltages are included, supporting down to 1.8 V to enable additional power savings.

Built-in LDOs deliver high PSRR performance and reduce the need for external components, simplifying low-jitter clock distribution in noisy environments.

The SKY53510/80/40 features a selectable input clock using a 3:1 input mux, one single-ended output, and either 10, 8, or 4 differential outputs in two banks, each of which is selectable as LVPECL, LVDS, HCSL, or tristate and whose voltage supply is independently sourced with either 1.8 V, 2.5 V, or 3.3 V.

Each output bank has its own dedicated 1.8 V, 2.5 V, or 3.3 V output voltage supply. This buffer family can be paired with the Skyworks NetSync™ family of network synchronizer clocks, jitter attenuators, and clock generators and oscillators to deliver ultra-low-jitter clock tree solutions.

# **Key Features**

1

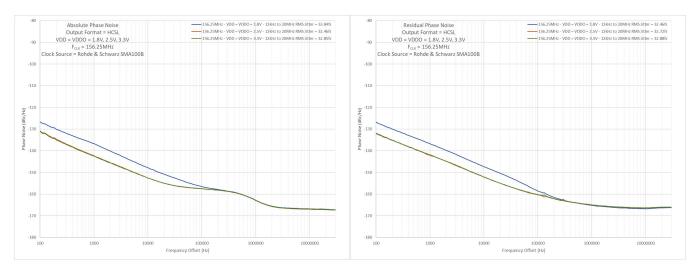

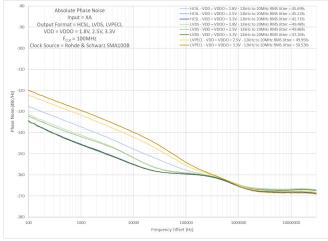

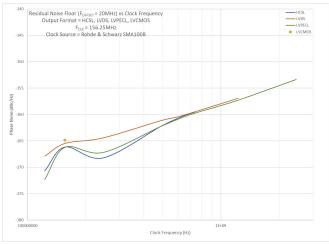

- Ultra-low additive jitter (156.25 MHz LVPECL, 12 kHz to 20 MHz):

- 35 fs RMS typical

- 47 fs RMS max

- 3:1 Input multiplexer

- Two any-format universal inputs supporting LVPECL, LVDS, S-LVDS, HCSL, CML, SSTL, and HSTL

- One crystal input (also accepts a single-ended clock)

- Two banks of differential output clocks

- 10/8/4 output ordering options

- Pin-selectable output formats (per bank):

LVPECL, LVDS, HCSL

- Frequency range:

- LVPECL: dc to 3.1 GHz

- LVDS: dc to 3 GHz

- HCSL: dc to 800 MHz

- PCIe Gen1/2/3/4/5/6/7 compliant

- Low-power operation (VDD/VDDO)

- 1.8 V/2.5 V/3.3 V

- LVCMOS output with synchronous enable/disable

- Temperature range:

- -40 to +95 °C ambient temperature

- 105 °C max board temperature

- Packages:

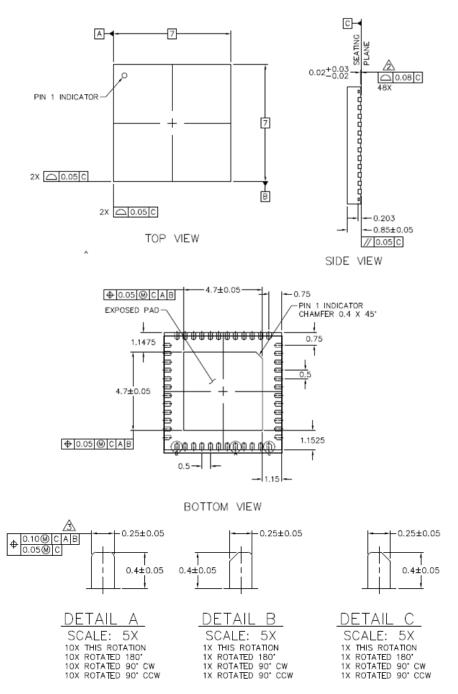

- SKY53510: 48-pin, 7 x 7 mm QFN

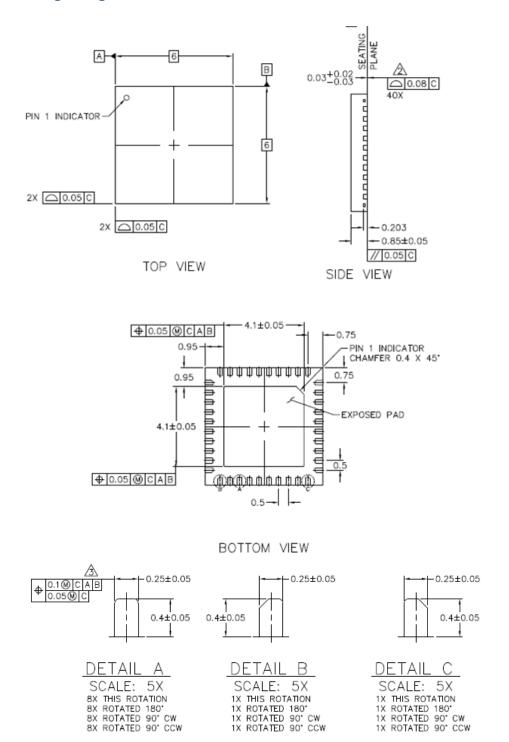

- SKY53580: 40-pin, 6 x 6 mm QFN

- SKY53540: 32-pin, 5 x 5 mm QFN

- For RoHS and other product compliance information, see the Skyworks Certificate of Conformance.

2

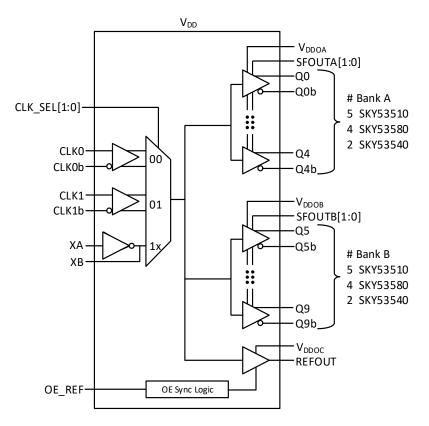

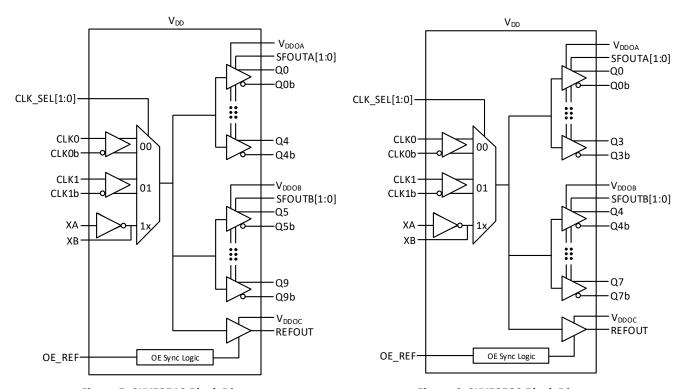

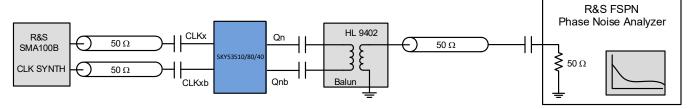

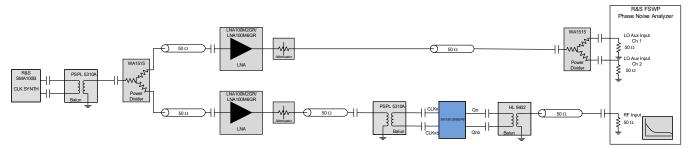

Figure 1. Functional Block Diagram

# 1. Pin Descriptions

## 1.1. SKY53510 7x7 mm 48-QFN Pin Descriptions

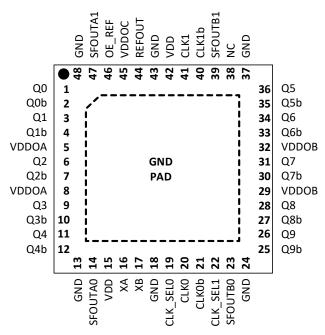

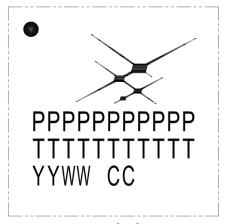

Figure 2. SKY53510 7x7 mm 48-QFN Pinout

Table 1. SKY53510 7x7mm 48-QFN Pin Descriptions

| Pin | Name  | Type <sup>1</sup> | Description                                                                                                                    |  |

|-----|-------|-------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | Q0    | 0                 | Output Clock 0                                                                                                                 |  |

| 2   | Q0b   | 0                 | Output Clock 0 (complement)                                                                                                    |  |

| 3   | Q1    | 0                 | Output Clock 1                                                                                                                 |  |

| 4   | Q1b   | 0                 | Output Clock 1 (complement)                                                                                                    |  |

| 5   | VDDOA | Р                 | Output voltage supply—Bank A (Outputs: Q0 to Q4) Bypass with 0.1 µF capacitor and place as close to the VDDOA pin as possible. |  |

| 6   | Q2    | 0                 | Output Clock 2                                                                                                                 |  |

| 7   | Q2b   | 0                 | Output Clock 2 (complement)                                                                                                    |  |

| 8   | VDDOA | Р                 | Output voltage supply—Bank A (Outputs: Q0 to Q4) Bypass with 0.1 µF capacitor and place as close to the VDDOA pin as possible. |  |

| 9   | Q3    | 0                 | Output Clock 3                                                                                                                 |  |

| 10  | Q3b   | 0                 | Output Clock 3 (complement)                                                                                                    |  |

| 11  | Q4    | 0                 | Output Clock 4                                                                                                                 |  |

| 12  | Q4b   | 0                 | Output Clock 4 (complement)                                                                                                    |  |

| 13  | GND   | GND               | Ground                                                                                                                         |  |

Table 1. SKY53510 7x7mm 48-QFN Pin Descriptions (Continued)

| Pin | Name     | Type <sup>1</sup> | Description                                                                                                                         |  |

|-----|----------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| 14  | SFOUTA0  | I                 | Output signal format control pin for Bank A SFOUTAO contains an internal pull-down resistor.                                        |  |

| 15  | VDD      | Р                 | Core voltage supply. Bypass with 0.1 μF capacitor placed as close to the VDD pin as possible.                                       |  |

| 16  | XA       | 1                 | Crystal input. Can also be driven by a XO, TCXO, or other external single-ended clock.                                              |  |

| 17  | ХВ       | 0                 | Crystal output. When a crystal is not used, and XA is used as an input, this pin should be left floating.                           |  |

| 18  | GND      | GND               | Ground                                                                                                                              |  |

| 19  | CLK_SEL0 | ı                 | Mux input select pin CLK_SELO contains an internal pull-down resistor.                                                              |  |

| 20  | CLK0     | I                 | Input Clock 0                                                                                                                       |  |

| 21  | CLK0b    | I                 | Input Clock 0 (complement).                                                                                                         |  |

| 22  | CLK_SEL1 | 1                 | Mux input select pin CLK_SEL1 contains an internal pull-down resistor.                                                              |  |

| 23  | SFOUTB0  | 1                 | Output signal format control pin for Bank B. SFOUTBO contains an internal pull-down resistor.                                       |  |

| 24  | GND      | GND               | Ground                                                                                                                              |  |

| 25  | Q9b      | 0                 | Output Clock 9 (complement)                                                                                                         |  |

| 26  | Q9       | 0                 | Output Clock 9                                                                                                                      |  |

| 27  | Q8b      | 0                 | Output Clock 8 (complement)                                                                                                         |  |

| 28  | Q8       | 0                 | Output Clock 8                                                                                                                      |  |

| 29  | VDDOB    | Р                 | Output voltage supply—Bank B (Outputs: Q5 to Q9) Bypass with 0.1 $\mu$ F capacitor and place as close to the VDDOB pin as possible. |  |

| 30  | Q7b      | 0                 | Output Clock 7 (complement)                                                                                                         |  |

| 31  | Q7       | 0                 | Output Clock 7                                                                                                                      |  |

| 32  | VDDOB    | Р                 | Output voltage supply—Bank B (Outputs: Q5 to Q9)<br>Bypass with 0.1 μF capacitor and place as close to the VDDOB pin as possible.   |  |

| 33  | Q6b      | 0                 | Output Clock 6 (complement).                                                                                                        |  |

| 34  | Q6       | 0                 | Output Clock 6.                                                                                                                     |  |

| 35  | Q5b      | 0                 | Output Clock 5 (complement)                                                                                                         |  |

| 36  | Q5       | 0                 | Output Clock 5                                                                                                                      |  |

| 37  | GND      | GND               | Ground                                                                                                                              |  |

| 38  | NC       | -                 | No connect. Leave this pin floating.                                                                                                |  |

| 39  | SFOUTB1  | I                 | Output signal format control pin for Bank B. SFOUTB1 contains an internal pull-down resistor.                                       |  |

| 40  | CLK1b    | 1                 | Input Clock 1 (complement).                                                                                                         |  |

| 41  | CLK1     | I                 | Input Clock 1.                                                                                                                      |  |

| 42  | VDD      | Р                 | Core voltage supply. Bypass with 0.1 $\mu$ F capacitor placed as close to the VDD pin as possible.                                  |  |

| 43  | GND      | GND               | Ground.                                                                                                                             |  |

| 44  | REFOUT   | 0                 | LVCMOS reference output clock. Enable this output by pulling pin 46 high.                                                           |  |

5

Table 1. SKY53510 7x7mm 48-QFN Pin Descriptions (Continued)

| Pin     | Name    | Type <sup>1</sup> | Description                                                                                      |  |

|---------|---------|-------------------|--------------------------------------------------------------------------------------------------|--|

| 45      | VDDOC   | Р                 | REFOUT buffer supply. Bypass with 0.1 µF capacitor placed as close to the VDDOC pin as possible. |  |

| 46      | OE_REF  | 1                 | Output Enable for REFOUT. OE_REF contains an internal pull-down resistor.                        |  |

| 47      | SFOUTA1 | I                 | Output signal format control pin for Bank A. SFOUTA1 contains an internal pull-down resistor.    |  |

| 48      | GND     | GND               | Ground.                                                                                          |  |

| GND Pad | GND     | GND               | Power supply ground and thermal relief.                                                          |  |

<sup>1.</sup> Pin types are: I = input, O = output, P = power, GND = ground.

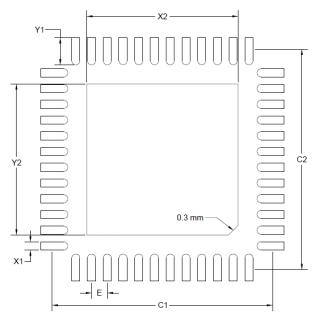

## 1.2. SKY53580 6x6 mm 40-QFN Pin Descriptions

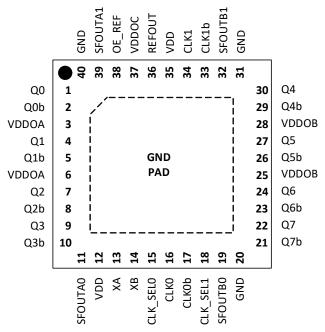

Figure 3. SKY53580 6x6 mm 40-QFN Pinout

Table 2. SKY53580 6x6 mm 40-QFN Pin Descriptions

| Pin | Name     | Type <sup>1</sup> | Description                                                                                                                          |  |

|-----|----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | Q0       | 0                 | Output Clock 0.                                                                                                                      |  |

| 2   | Q0b      | 0                 | Output Clock 0 (complement).                                                                                                         |  |

| 3   | VDDOA    | Р                 | Output voltage supply-Bank A (Outputs: Q0 to Q3). Bypass with 0.1 $\mu$ F capacitor and place as close to the VDDOA pin as possible. |  |

| 4   | Q1       | 0                 | Output Clock 1.                                                                                                                      |  |

| 5   | Q1b      | 0                 | Output Clock 1 (complement).                                                                                                         |  |

| 6   | VDDOA    | Р                 | Output voltage supply-Bank A (Outputs: Q0 to Q3). Bypass with 0.1 $\mu$ F capacitor and place as close to the VDDOA pin as possible. |  |

| 7   | Q2       | 0                 | Output Clock 2.                                                                                                                      |  |

| 8   | Q2b      | 0                 | Output Clock 2 (complement).                                                                                                         |  |

| 9   | Q3       | 0                 | Output Clock 3.                                                                                                                      |  |

| 10  | Q3b      | 0                 | Output Clock 3 (complement).                                                                                                         |  |

| 11  | SFOUTA0  | I                 | Output signal format control pin for Bank A. SFOUTAO contains an internal pull-down resistor.                                        |  |

| 12  | VDD      | Р                 | Core voltage supply. Bypass with 0.1 µF capacitor placed as close to the VDD pin as possible.                                        |  |

| 13  | XA       | 1                 | Crystal input. Can also be driven by a XO, TCXO, or other external single-ended clock.                                               |  |

| 14  | ХВ       | 0                 | Crystal output. When a crystal is not used, and XA is used as an input, this pin should be left floating.                            |  |

| 15  | CLK_SEL0 | I                 | Mux input select pin. CLK_SEL0 contains an internal pull-down resistor.                                                              |  |

Table 2. SKY53580 6x6 mm 40-QFN Pin Descriptions (Continued)

| Pin     | Name     | Type <sup>1</sup> | Description                                                                                                                        |  |

|---------|----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------|--|

| 16      | CLK0     | Ι                 | Input Clock 0.                                                                                                                     |  |

| 17      | CLK0b    | Ι                 | Input Clock 0 (complement).                                                                                                        |  |

| 18      | CLK_SEL1 | I                 | Mux input select pin. CLK_SEL1 contains an internal pull-down resistor.                                                            |  |

| 19      | SFOUTB0  | 1                 | Output signal format control pin for Bank B. SFOUTBO contains an internal pull-down resistor.                                      |  |

| 20      | GND      | GND               | Ground.                                                                                                                            |  |

| 21      | Q7b      | 0                 | Output Clock 7 (complement).                                                                                                       |  |

| 22      | Q7       | 0                 | Output Clock 7.                                                                                                                    |  |

| 23      | Q6b      | 0                 | Output Clock 6 (complement).                                                                                                       |  |

| 24      | Q6       | 0                 | Output Clock 6.                                                                                                                    |  |

| 25      | VDDOB    | Р                 | Output voltage supply-Bank B (Outputs: Q4 to Q7).<br>Bypass with 0.1 μF capacitor and place as close to the VDDOB pin as possible. |  |

| 26      | Q5b      | 0                 | Output Clock 5 (complement).                                                                                                       |  |

| 27      | Q5       | 0                 | Output Clock 5.                                                                                                                    |  |

| 28      | VDDOB    | Р                 | Output voltage supply-Bank B (Outputs: Q4 to Q7). Bypass with 0.1 µF capacitor and place as close to the VDDOB pin as possible.    |  |

| 29      | Q4b      | 0                 | Output Clock 4 (complement).                                                                                                       |  |

| 30      | Q4       | 0                 | Output Clock 4.                                                                                                                    |  |

| 31      | GND      | GND               | Ground.                                                                                                                            |  |

| 32      | SFOUTB1  | I                 | Output signal format control pin for Bank B. SFOUTB1 contains an internal pull-down resistor.                                      |  |

| 33      | CLK1b    | Ι                 | Input Clock 1 (complement).                                                                                                        |  |

| 34      | CLK1     | Ι                 | Input Clock 1.                                                                                                                     |  |

| 35      | VDD      | Р                 | Core voltage supply. Bypass with 0.1 $\mu$ F capacitor placed as close to the VDD pin as possible.                                 |  |

| 36      | REFOUT   | 0                 | LVCMOS reference output clock. Enable this output by pulling pin 38 high.                                                          |  |

| 37      | VDDOC    | Р                 | REFOUT buffer supply. Bypass with 0.1 $\mu$ F capacitor placed as close to the VDDOC pin as possible.                              |  |

| 38      | OE_REF   | I                 | Output Enable for REFOUT. OE_REF contains an internal pull-down resistor.                                                          |  |

| 39      | SFOUTA1  | I                 | Output signal format control pin for Bank A. SFOUTA1 contains an internal pull-down resistor.                                      |  |

| 40      | GND      | GND               | Ground.                                                                                                                            |  |

| GND Pad | GND      | GND               | Power supply ground and thermal relief.                                                                                            |  |

| l       | L        |                   | I                                                                                                                                  |  |

<sup>1.</sup> Pin types are: I = input, O = output, P = power, GND = ground.

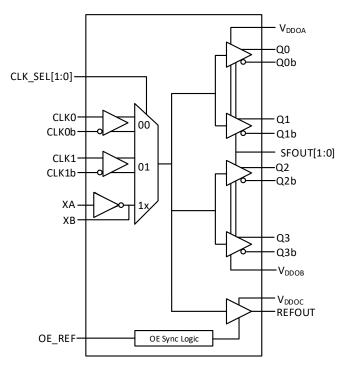

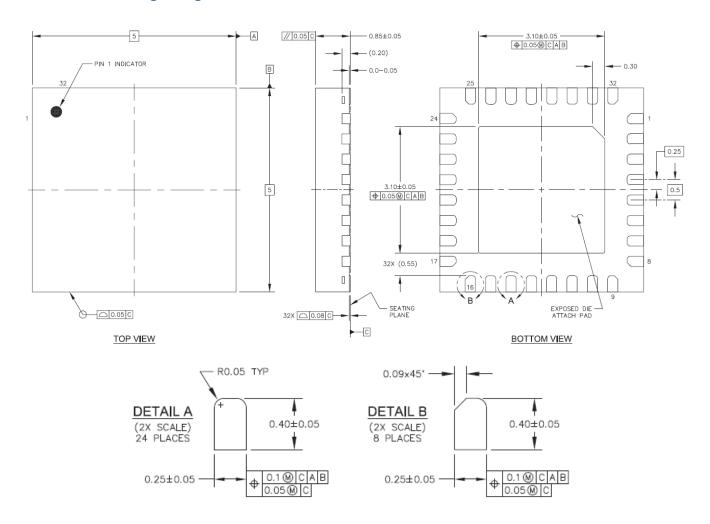

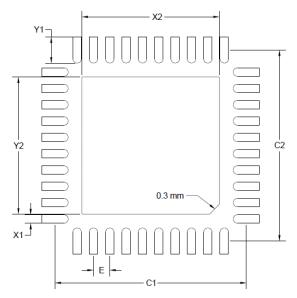

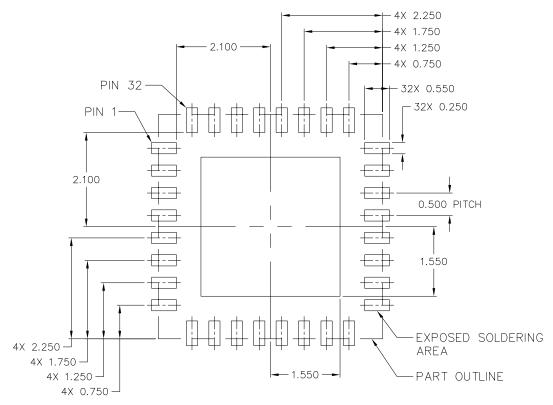

# 1.3. SKY53540 5x5 mm 32-QFN Pin Descriptions

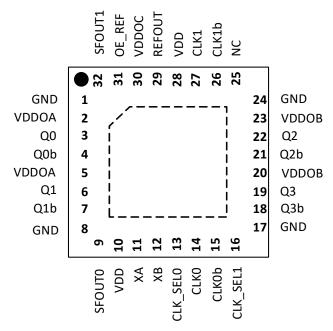

Figure 4. SKY53540 5x5 mm 32-QFN Pinout

Table 3. SKY53540 5x5 mm 32-QFN Pin Descriptions

| Pin | Name     | Type <sup>1</sup> | Description                                                                                                                                |  |

|-----|----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | GND      | GND               | Ground.                                                                                                                                    |  |

| 2   | VDDOA    | Р                 | Output voltage supply-Bank A (Outputs: Q0 to Q1). Bypass with 0.1 $\mu\text{F}$ capacitor and place as close to the VDDOA pin as possible. |  |

| 3   | Q0       | 0                 | Output clock 0.                                                                                                                            |  |

| 4   | Q0b      | 0                 | Output clock 0 (complement).                                                                                                               |  |

| 5   | VDDOA    | Р                 | Output voltage supply-Bank A (Outputs: Q0 to Q1). Bypass with 1.0 $\mu\text{F}$ capacitor and place as close to the VDDOA pin as possible. |  |

| 6   | Q1       | 0                 | Output clock 1.                                                                                                                            |  |

| 7   | Q1b      | 0                 | Output clock 1 (complement).                                                                                                               |  |

| 8   | GND      | GND               | Ground.                                                                                                                                    |  |

| 9   | SFOUT0   | I                 | Output signal format control pin for Bank A and Bank B. SFOUTO contains an internal pull-down resistor.                                    |  |

| 10  | VDD      | Р                 | Core voltage supply. Bypass with 0.1 µF capacitor placed as close to the VDD pin as possible.                                              |  |

| 11  | XA       | I                 | Crystal input. Can also be driven by a XO, TCXO, or other external single-ended clock.                                                     |  |

| 12  | ХВ       | 0                 | Crystal output. When a crystal is not used and XA is used as an input, this pin should be left floating.                                   |  |

| 13  | CLK_SEL0 | I                 | Mux input select pin. CLK_SEL0 contains an internal pull-down resistor.                                                                    |  |

| 14  | CLK0     | I                 | Input clock 0.                                                                                                                             |  |

Table 3. SKY53540 5x5 mm 32-QFN Pin Descriptions (Continued)

| Pin    | Name     | Type <sup>1</sup> | Description                                                                                                                                |  |

|--------|----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| 15     | CLK0b    | Ι                 | Input clock 0 (complement).                                                                                                                |  |

| 16     | CLK_SEL1 | I                 | Mux input select pin. CLK_SEL1 contains an internal pull-down resistor.                                                                    |  |

| 17     | GND      | GND               | Ground.                                                                                                                                    |  |

| 18     | Q3b      | 0                 | Output clock 3 (complement).                                                                                                               |  |

| 19     | Q3       | 0                 | Output clock 3.                                                                                                                            |  |

| 20     | VDDOB    | Р                 | Output voltage supply-Bank B (Outputs: Q2 to Q3). Bypass with 0.1 $\mu\text{F}$ capacitor and place as close to the VDDOB pin as possible. |  |

| 21     | Q2b      | 0                 | Output clock 2 (complement).                                                                                                               |  |

| 22     | Q2       | 0                 | Output clock 2.                                                                                                                            |  |

| 23     | VDDOB    | Р                 | Output voltage supply-Bank B (Outputs: Q2 to Q3). Bypass with 0.1 µF capacitor and place as close to the VDDOB pin as possible.            |  |

| 24     | GND      | GND               | Ground.                                                                                                                                    |  |

| 25     | NC       | _                 | No Connect.                                                                                                                                |  |

| 26     | CLK1b    | Ι                 | Input clock 1 (complement).                                                                                                                |  |

| 27     | CLK1     | Ι                 | Input clock 1.                                                                                                                             |  |

| 28     | VDD      | Р                 | Core voltage supply. Bypass with 0.1 $\mu$ F capacitor placed as close to the VDD pin as possible.                                         |  |

| 29     | REFOUT   | 0                 | LVCMOS reference output clock. Enable this output by pulling Pin 31 high.                                                                  |  |

| 30     | VDDOC    | Р                 | REFOUT buffer supply. Bypass with 0.1 $\mu$ F capacitor placed as close to the VDDOC pin as possible.                                      |  |

| 31     | OE_REF   | I                 | Output Enable for REFOUT. OE_REF contains an internal pull-down resistor.                                                                  |  |

| 32     | SFOUT1   | I                 | Output signal format control pin for Bank A and Bank B. SFOUT1 contains an internal pull-down resistor.                                    |  |

| GNDPad | GND      | GND               | Power supply ground and thermal relief.                                                                                                    |  |

<sup>1.</sup> Pin types are: I = input, O = output, P = power, GND = ground.

## 2. Detailed Description

#### 2.1. Overview

The SKY53510/80/40 is a family of ultra-low additive jitter, low-skew, universal/any-format buffers. These devices can operate up to 3.1 GHz, featuring a 3:1 input multiplexer stage that can accept the most common differential or LVCMOS input signals. The output stage includes two banks of outputs, each of which includes pin-selectable output format selection and output supply voltage, as well as an LVCMOS reference output.

# 2.2. Block Diagrams

Figure 5. SKY53510 Block Diagram

Figure 6. SKY53580 Block Diagram

Figure 7. SKY53540 Block Diagram

#### 2.3. Modes of Operation

#### 2.3.1. Input Clock Stage

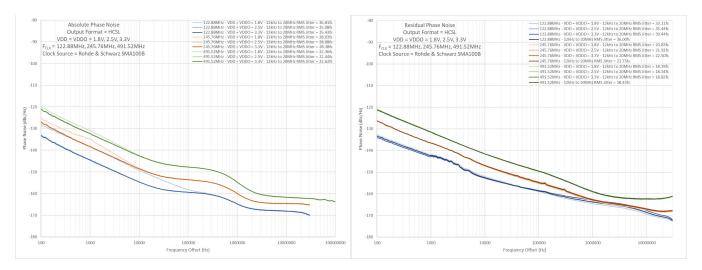

The input stage accepts a wide variety of common clock formats and voltage ranges on CLKO and CLK1, including LVPECL, LVCMOS, LVDS, HCSL, CML, SSTL, and HSTL. For ac-coupled, sine-wave clock inputs, see "AN1405: SKY535xx Applications Guide". For the best high-speed performance, differential formats are recommended. The SKY53510/80/40 exhibits excellent additive RMS phase jitter across a wide spectrum of input slew rates for both single-ended and differential input clocks.

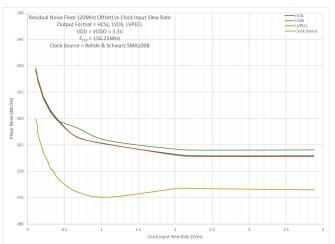

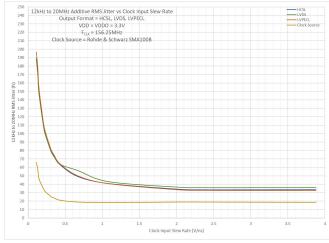

To achieve optimal performance, a differential slew rate of 3.0 V/ns is recommended for differential formats, and 1.0 V/ns for single-ended formats to meet the max RMS additive phase jitter data sheet specifications. The buffers remain fully functional with slower slew rates but will incur some degradation in jitter performance. See Figure 53 on page 39 for further information on additive RMS phase jitter performance vs.

input clock slew rate. For input frequencies below 1 MHz, dc-coupled interfaces are recommended. For more information, see "AN766: Understanding and Optimizing Clock Buffer's Additive Jitter Performance".

| Clock Format  | VDD = 1.8 V | VDD = 2.5/3.3 V |

|---------------|-------------|-----------------|

| LVPECL        | No          | Yes             |

| LVCMOS        | Yes         | Yes             |

| LVDS / S-LVDS | Yes         | Yes             |

| HCSL          | Yes         | Yes             |

Table 4. DC-Coupled Clock Input Options on CLK0/CLK1

The input clock can be selected from CLKO/CLKOb, CLK1/CLK1b, or the crystal input (XA/XB). The CLK\_SEL[1:0] pins select the active clock input and have internal pull-down resistors. The following tables summarize the input and output clock configurations based on the input multiplexer CLK\_SEL[1:0] pin settings. A single rising edge on the selected input clock is required for the output to then reflect the input source. Clock inputs should not be driven until VDD has reached the recommended minimum level.

| Table 5. Input Selection 1,2 | ,3 |

|------------------------------|----|

|------------------------------|----|

| CLK_SEL1 | CLK_SEL0 | Selected Input        |

|----------|----------|-----------------------|

| 0        | 0        | CLKO/CLK0b            |

| 0        | 1        | CLK1/CLK1b            |

| 1        | Х        | Crystal input (XA/XB) |

- 1. CLK\_SEL[1:0] have internal pull-down resistors. When left open, the pin is internally pulled to ground. To pull high, use a 4.7 k $\Omega$  resistor to VDD.

- 2. When XA is used as an AC coupled single-ended input in place of the crystal, XB should be left electrically unconnected.

- 3. Unused CLKO/1 inputs may be left floating. Unused XA should be tied to ground to prevent system noise from affecting this input.

Table 6. Clock Input vs. Output States<sup>1,2</sup>

| State of Selected Clock Input                                               | State of Enabled Clock Outputs <sup>2</sup> |

|-----------------------------------------------------------------------------|---------------------------------------------|

| CLK0/CLK0b and CLK1/CLK1b inputs shorted together via 100 $\Omega$ resistor | Logic low                                   |

| CLK0/CLK0b or CLK1/CLK1b input logic low.                                   | Logic low                                   |

| CLK0/CLK0b or CLK1/CLK1b input logic high.                                  | Logic high                                  |

- 1. Upon power up, a single rising edge at the selected input is required for the outputs to reflect the input source.

- 2. If the selected clock input is not driven, a  $100~\Omega$  resistor should be placed between CLKx/CLKxb for the state of enabled outputs to be logic low. Omission of the  $100~\Omega$  resistor may result in undesired chatter on enabled outputs.

#### 2.3.2. Clock Outputs

The highly flexible output drivers support a wide range of clock signal formats, including LVPECL, LVDS, and HCSL. The differential output format type for Bank A and Bank B outputs are independently configurable using the SFOUTA[1:0] and SFOUTB[1:0] input pins, respectively, as shown in Table 7 below. This feature enables the device to be used for format/level translation in addition to clock distribution, minimizing the number of unique buffer part numbers required in a typical application and simplifying design reuse. For applications where all differential outputs are not required, any unused Qn/Qnb output pin should be left floating with a minimal copper length to minimize capacitance, potential coupling, and power consumption. It is recommended to disable (Hi-Z) the bank to reduce power if no outputs will be used from that respective bank. See the termination diagrams in "3.3. Clock Output Termination" on page 18.

| SFOUTx[1] <sup>1</sup> | SFOUTx[0] <sup>1</sup> | V <sub>DDOx</sub> = 3.3 V    | V <sub>DDOx</sub> = 2.5 V    | V <sub>DDOx</sub> = 1.8 V    |

|------------------------|------------------------|------------------------------|------------------------------|------------------------------|

| 0                      | 0                      | LVPECL                       | LVPECL                       | N/A <sup>2</sup>             |

| 0                      | 1                      | LVDS                         | LVDS                         | S-LVDS                       |

| 1                      | 0                      | HCSL                         | HCSL                         | HCSL                         |

| 1                      | 1                      | Disabled (Hi-Z) <sup>3</sup> | Disabled (Hi-Z) <sup>3</sup> | Disabled (Hi Z) <sup>3</sup> |

**Table 7. Output Signal Format Selection**

- 1. SFOUTx[1:0] have internal pulldown resistors. When left open, the pin is internally pulled to ground. To pull high, use a 4.7 kΩ resistor to VDD.

- 2. The hardware default output format for 1.8 V is undefined. One or both of the SFOUTx pins should either be driven by the system or pulled up to VDD using a 4.7 kΩ resistor.

- 3. To power up the buffer with inactive outputs, pull both SFOUTx pins to VDD with 4.7 k $\Omega$  resistors.

The device also features an LVCMOS clock output (REFOUT) at the same frequency as the selected clock input, which can be enabled/disabled via the OE\_REF pin. The OE\_REF pin is sampled and synchronized to the falling edge of the selected input clock. This feature prevents runt pulses from being generated when REFOUT is enabled. REFOUT will be synchronously enabled within three cycles of the input clock after OE\_REF is driven high and meets setup and hold timing requirements.

When OE\_REF is low, REFOUT is disabled synchronously in a Hi-Z state. This allows the disabled state to be determined by external bias. For example, if a 1 k $\Omega$  resistor is connected from REFOUT to ground, REFOUT will be pulled low when disabled.

OE\_REFREFOUT0Disabled (Hi-Z)1Enabled

Table 8. Reference Output Enable 1

$<sup>{\</sup>bf 1.} \quad {\sf All \ unused \ outputs \ from \ Bank \ A, \ Bank \ B, \ or \ REFOUT \ should \ be \ left \ unconnected \ and \ floating.}$

## 3. Applications Information

# 3.1. Driving Clock Inputs (CLKO/CLK1)

The SKY53510/80/40 features two universal, any-format clock inputs that can accept ac-coupled LVPECL, LVDS, HCSL, CML, SSTL, HSTL, and ac-coupled, single-ended clocks, or dc-coupled LVPECL, LVDS, HCSL, or LVCMOS clock inputs. Inputs must not be driven prior to VDD reaching the recommended minimum level. The devices feature excellent additive RMS phase jitter over a wide range of clock input slew rates as shown in Figure 53 on page 39. To achieve the best additive RMS phase jitter performance on the output clocks, Skyworks recommends a differential input with a high differential slew rate of 3 V/ns or higher.

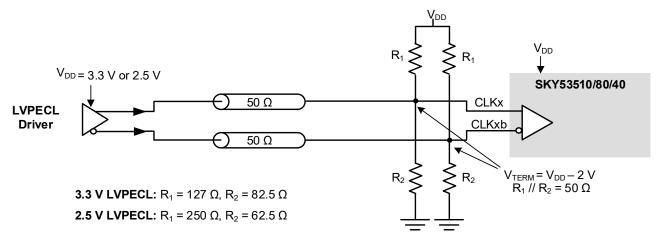

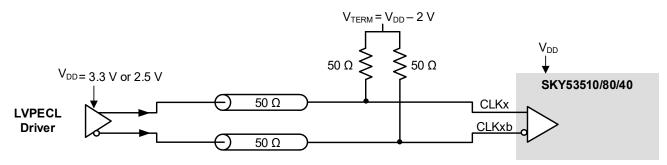

Figure 8. DC-Coupled LVPECL Input Termination Scheme 1

Figure 9. DC-Coupled LVPECL Input Termination Scheme 2

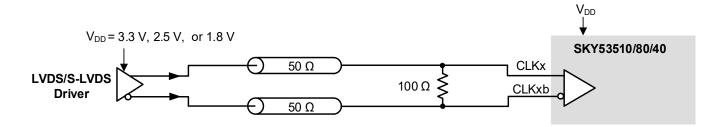

Figure 10. DC Coupled LVDS/S-LVDS Input Termination

Note: R<sub>S</sub> series termination is optional depending on the location of the receiver.

Adding Rs will reduce the amplitude of the output driver swing seen at the receiver.

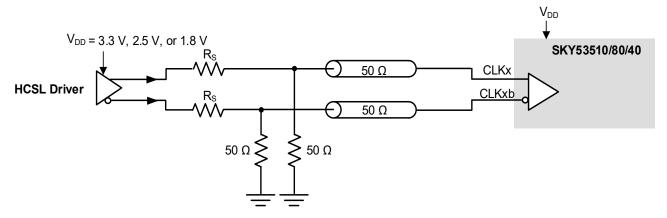

#### Figure 11. DC-Coupled HCSL Input Termination

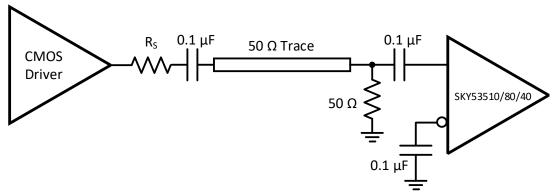

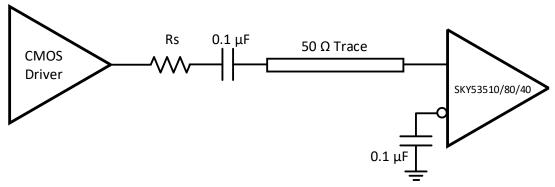

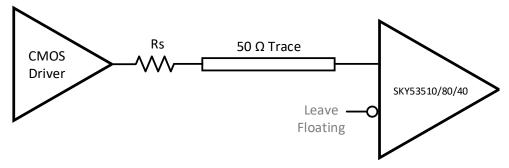

The device features internal common mode biasing to support ac-coupled differential input clocks. While it is not recommended, driving the CLKO or CLK1 input pins with a single-ended clock is possible, as long as the clock conforms to the single-ended input specifications outlined in Table 11, "Input Clock Specifications," on page 25. Single-ended input clocks can be ac-coupled, using the configurations shown in Figure 12 or Figure 13. The output impedance of the LVCMOS driver plus Rs should be close to 50  $\Omega$  to match the characteristic impedance of the transmission line and load termination.

Figure 12. Single-Ended Input Termination Scheme 1 (AC Coupling)

Figure 13. Single-Ended Input Termination Scheme 2 (AC Coupling)

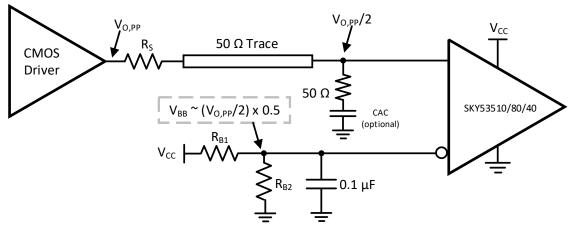

A single-ended clock may also be dc coupled to CLK0 or CLK1 as shown in Figure 14. Place a 50  $\Omega$  load resistor near the CLK0 or CLK1 input pin for signal attenuation and line termination. Half of the single-ended swing of the driver (voltage seen at the 50  $\Omega$  load will depend on the R<sub>S</sub> and CMOS source impedance) drives CLK0 or CLK1, therefore CLK0b or CLK1b should be externally biased to the midpoint voltage of the attenuated input swing ((VO,PP / 2) × 0.5). The external bias voltage should be within the specified input common-mode voltage (V<sub>CM</sub>) range specified in "5. Electrical Specifications" on page 24. This can be achieved using external biasing resistors in the k $\Omega$  range (RB1 and RB2) or another low-noise voltage reference. Doing so will ensure the input swing crosses the threshold voltage at a point where the input slew rate is the highest. If the LVCMOS driver cannot achieve sufficient swing with a dc-terminated, 50  $\Omega$  load at the CLK0 or CLK1 input as shown in Figure 14, then consider connecting the 50  $\Omega$  load termination to ground through a capacitor (CAC). This ac termination blocks the dc load current on the driver, so the voltage swing at the input is determined by the voltage divider formed by the source (Ro + Rs) and 50  $\Omega$  load resistors. The value for CAC depends on the trace delay, Td, of the 50  $\Omega$  transmission line; CAC  $\geq$  3 x Td / 50  $\Omega$ .

Figure 14. Single-Ended Input with Common-Mode Biasing Option1, DC Coupling

Figure 15. Single-Ended Input Option 2, DC Coupling

The input clock receivers on the SKY53510/80/40 do not have hysteresis; an internal biasing network prevents the receiver from switching due to board noise.

#### 3.2. Crystal Interface (XA/XB)

The SKY53510/80/40 features an integrated crystal oscillator circuit in the input stage that supports a fundamental mode, AT-cut crystal input.

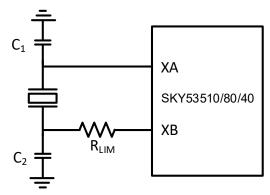

Figure 16. Crystal Interface

The external load capacitors (C1 and C2 in the figure above) are a function of capacitive parameters associated with the crystal, the input capacitance of the crystal oscillator circuit, and stray capacitance comprised of the parasitic capacitance of the board trace and bond pad capacitances. Details of how these capacitor values (C1 and C2) are calculated are provided in Application Note "AN1405: SKY535xx Applications Guide".

Table 11, "Input Clock Specifications," on page 25 provides crystal interface specifications with conditions that ensure start-up of the crystal, but it does not specify crystal power dissipation. The designer will need to ensure the crystal power dissipation does not exceed the maximum drive level specified by the crystal manufacturer. Overdriving the crystal can cause premature aging, frequency shift, and eventual failure. Drive level should be held at a sufficient level necessary to start-up and maintain steady-state operation.

The power dissipated in the crystal, Pxtal, can be computed by:

Pxtal =

$$I_{RMS} \times R_{esr} \times (1 + Co/Cl)^2$$

#### where:

- I<sub>RMS</sub> is the RMS current through the crystal.

- R<sub>esr</sub> is the maximum equivalent series resistance specified for the crystal

- Cl is the load capacitance specified for the crystal

- Co is the minimum shunt capacitance specified for the crystal

$I_{RMS}$  can be measured using a current probe (for example, Tektronix CT-6 or equivalent) placed on the leg of the crystal connected to XB with the oscillation circuit active. As shown in Figure 16, an external resistor, Rlim, can be used to limit the crystal drive level, if necessary. If the power dissipated in the selected crystal is higher than the drive level specified for the crystal with Rlim shorted, then a larger resistor value is mandatory to avoid overdriving the crystal. However, if the power dissipated in the crystal is less than the drive level with Rlim shorted, then a zero value for Rlim can be used. As a starting point, a suggested value for Rlim is 316  $\Omega$ .

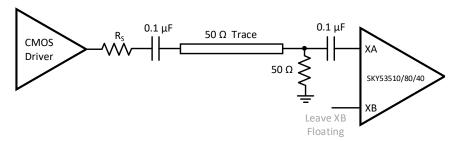

If the crystal oscillator is not used, it is possible to drive the XA input with a single-ended external clock as shown in Figure 17 below. The input clock should be ac-coupled to the XA pin, which has an internally-generated input bias voltage, and the XB pin should be left floating. While XA provides an alternative input to multiplex an external clock, it is recommended to alternatively use either universal input (CLKO/CLK1) because the inputs offer higher operating frequency, better common-mode and power supply noise rejection, and greater performance over supply voltage and temperature variations.

Figure 17. Driving XA with a Single-Ended Input Clock

## 3.3. Clock Output Termination

A single rising edge on the selected input clock is required for the output to then reflect the input source. All unused outputs should be left unconnected.

#### 3.3.1. DC-Coupled Differential Output Driver Terminations

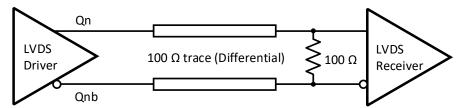

For dc-coupled operation of an LVDS driver, terminate with 100  $\Omega$  as close as possible to the LVDS receiver.

Figure 18. DC Coupled LVDS Clock Output Termination

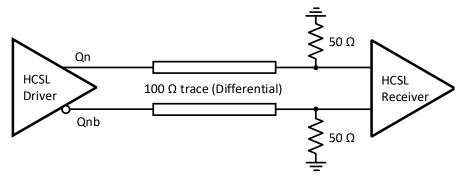

For dc-coupled operation of an HCSL driver, terminate with 50  $\Omega$  to ground near the receiver as shown in Figure 19.

Figure 19. DC Coupled HCSL Clock Output Termination (Scheme 1)

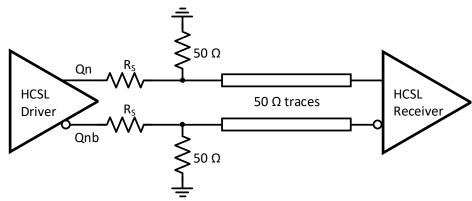

It is also possible to terminate with 50  $\Omega$  to ground near the driver output. Series resistors, Rs, may be used to limit overshoot due to the fast transient current. Because HCSL drivers require a dc path to ground, ac coupling is not allowed between the output drivers and the 50  $\Omega$  termination resistors.

Figure 20. DC Coupled HCSL Clock Output Termination (Scheme 2)

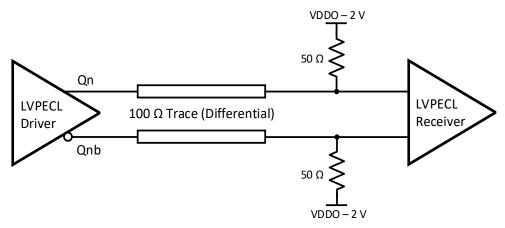

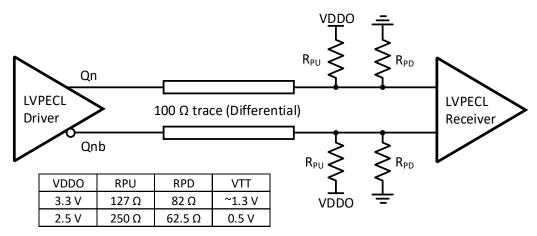

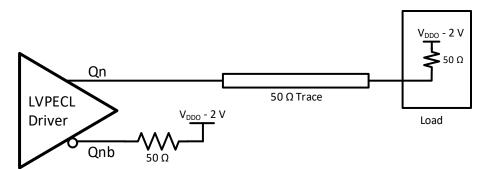

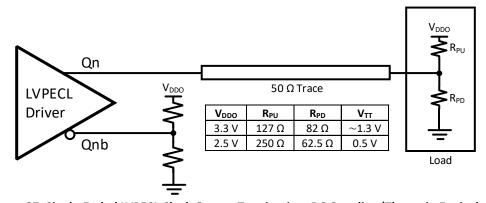

For dc-coupled operation of an LVPECL driver, terminate with 50  $\Omega$  to  $V_{DDO}$  – 2 V, as noted in Figure 21 below. Alternatively, terminate with a Thevenin equivalent circuit as shown in Figure 22 on page 19 for  $V_{DDO}$  (output driver supply voltage) = 3.3 V and 2.5 V. In the Thevenin equivalent circuit, the resistor dividers set the output termination voltage (VTT) to  $V_{DDO}$  – 2 V.

Figure 21. DC Coupled LVPECL Clock Output Termination

Figure 22. DC-Coupled LVPECL Clock Output Termination, Thevenin Equivalent

#### 3.3.2. AC-Coupled Differential Output Driver Terminations

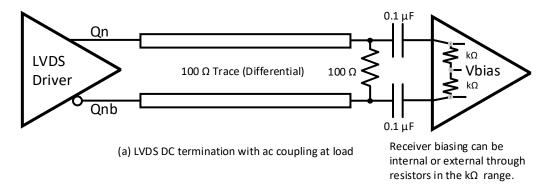

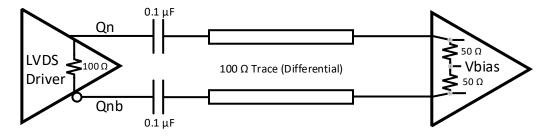

When driving differential receivers with an LVDS driver, the signal may be ac coupled by adding dc blocking capacitors; however the proper dc bias point needs to be established at both the driver side and the receiver side. The recommended termination scheme depends on whether the differential receiver has integrated termination resistors or not.

When driving a differential receiver without internal  $100~\Omega$  differential termination, the ac coupling capacitors should be placed between the load termination resistor and the receiver to allow a dc path for proper biasing of the LVDS driver. This is shown in Figure 23. The load termination resistor and ac-coupling capacitors should be placed as close as possible to the receiver inputs to minimize stub length. The receiver can be biased internally or externally to a reference voltage within the receiver's common mode input range through resistors in the kiloohm range.

When using ac coupling with LVDS outputs, there may be a start-up delay observed in the clock output due to capacitor charging. The examples in Figure 23 and Figure 24 use  $0.1~\mu F$  capacitors, but this value may be adjusted to meet the startup requirements for the particular application.

Figure 23. AC-Coupled LVDS Clock Output Coupled to Receivers without Internal 100  $\Omega$  Termination

Figure 24. AC-Coupled LVDS Clock Output Coupled to Receivers with Internal 100  $\Omega$  Termination

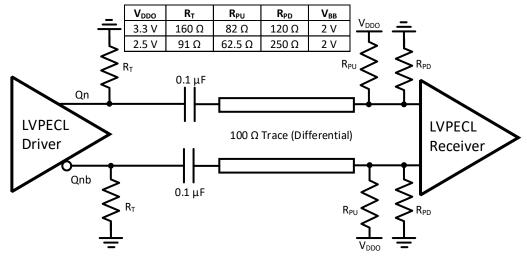

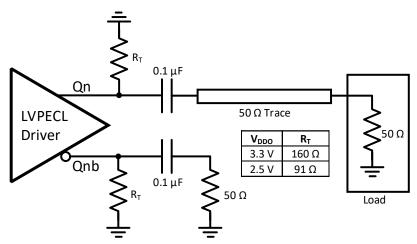

LVPECL drivers require a dc path to ground. When ac coupling an LVPECL signal, use 160  $\Omega$  emitter resistors (or 91  $\Omega$  for V<sub>DDO</sub> = 2.5 V) close to the LVPECL driver to provide a dc path to ground as shown in Figure 25. For proper receiver operation, the signal should be biased to the dc bias level (common-mode voltage) specified by the receiver. The typical dc bias voltage (common-mode voltage) for LVPECL receivers is 2 V. Alternatively, a Thevenin equivalent circuit forms a valid termination as shown in Figure 25 for V<sub>DDO</sub> = 3.3 V and 2.5 V.

**Note**: This Thevenin circuit is different from the dc-coupled example in Figure 22, since the voltage divider is setting the input common-mode voltage of the receiver.

Figure 25. AC-Coupled LVPECL Clock Output Termination (Thevenin Equivalent)

A balun can be used with either LVDS or LVPECL drivers to convert the balanced, differential signal into an unbalanced, single-ended signal. It is possible to use an LVPECL driver as one or two separate 800 mV p-p single-ended signals. When dc-coupling one of the LVPECL drivers of a Qx/Qxb pair, ensure that the unused driver is properly terminated. When dc-coupling an LVPECL driver, the termination should be 50  $\Omega$  to  $V_{DDO} = 2$  V as shown in Figure 26. The Thevenin equivalent circuit is also a valid termination as shown in Figure 27 for  $V_{DDO} = 2.5$  V or 3.3 V.

Figure 26. Single-Ended LVPECL Clock Output Termination, DC Coupling

Figure 27. Single-Ended LVPECL Clock Output Termination, DC Coupling (Thevenin Equivalent)

When ac-coupling an LVPECL driver into a single-ended load, use a 160  $\Omega$  emitter resistor (or 91  $\Omega$  for  $V_{DDO}$  = 2.5 V) to provide a dc path to ground and ensure a 50  $\Omega$  termination with the proper dc bias level for the receiver. The typical dc bias voltage for LVPECL receivers is 2 V. If the companion driver is not used, it should be terminated with either a proper ac or dc termination. This latter example of ac coupling a single-ended LVPECL signal can be used to measure single-ended LVPECL performance using a spectrum analyzer or phase noise analyzer. When using most RF test equipment, a dc voltage level of 0 Vdc is required for safe and proper operation. The internal 50  $\Omega$  termination the test equipment correctly terminates the LVPECL driver being measured, as shown in Figure 28. When using only one LVPECL driver of a Qx/Qxb pair, be sure to properly terminate the unused driver.

Figure 28. Single-Ended LVPECL Clock Output Termination (AC Coupling)

# 4. Power Supply (V<sub>DD</sub> and V<sub>DDOx</sub>)

The device includes separate core ( $V_{DD}$ ) and output driver supplies ( $V_{DDOx}$ ). This feature allows the  $V_{DDO}$  to operate at a lower voltage than the core  $V_{DD}$  reducing current consumption in mixed supply operations. The core  $V_{DD}$  supports 3.3, 2.5, or 1.8 V. Control signals, such as CLK\_SEL[1:0], SFOUTx[1:0], and OE\_REF, are in the  $V_{DD}$  domain. Each output bank has its own  $V_{DDOx}$  supply, supporting 3.3, 2.5, or 1.8 V.

# 4.1. Power Supply Sequencing

All power supplies must ramp in a monotonic, linear fashion. When powering the  $V_{DD}$  and  $V_{DDOx}$  pins from separate supply rails, it is recommended for the supplies to reach their regulation point at approximately the same time while ramping up, or reach ground potential at the same time while ramping down. Clock inputs should not be driven until  $V_{DD}$  has reached the recommended minimum levels.  $V_{DD}$  must be equal to, or greater than,  $V_{DDOx}$ .

# **5. Electrical Specifications**

Table 9. Absolute Maximum Ratings<sup>1</sup>

| Parameter                         | Symbol                                                    | Test Condition                                        | Min  | Тур | Max         | Unit |

|-----------------------------------|-----------------------------------------------------------|-------------------------------------------------------|------|-----|-------------|------|

| Storage temperature               | T <sub>S</sub>                                            |                                                       | -55  | _   | 150         | °C   |

| Supply voltage                    | $V_{\rm DD}, V_{\rm DDOA}, \\ V_{\rm DDOB}, V_{\rm DDOC}$ |                                                       | -0.5 | _   | 3.8         | V    |

| Input voltage                     | V <sub>IN</sub>                                           |                                                       | -0.5 | _   | VDD + 0.3   | V    |

| Output voltage                    | V <sub>OUT</sub>                                          |                                                       | _    | _   | VDDOx + 0.3 | V    |

| ESD sensitivity                   | НВМ                                                       | HBM, 100 pF, 1.5 kΩ                                   | _    | _   | 2000        | V    |

| ESD sensitivity                   | CDM                                                       |                                                       | _    | -   | 500         | V    |

| Peak soldering reflow temperature | T <sub>PEAK</sub>                                         | Pb-Free; Solder reflow profile per<br>JEDEC J-STD-020 | _    | _   | 260         | °C   |

| Maximum junction temperature      | T <sub>J</sub>                                            |                                                       | _    | _   | 125         | °C   |

<sup>1.</sup> Stresses beyond those listed in this table may cause permanent damage to the device. Functional operation specification compliance is not implied at these conditions. Exposure to maximum rating conditions for extended periods may affect device reliability.

ESD Handling: Industry-standard ESD handling precautions must be adhered to at all times to avoid damage to this device.

**Table 10. Recommended Operating Conditions**

| Parameter                              | Symbol                                 | Test Condition                            | Min  | Тур | Max  | Unit |

|----------------------------------------|----------------------------------------|-------------------------------------------|------|-----|------|------|

| Ambient operating temperature          | T <sub>A</sub>                         | JEDEC Board, 4-layer                      | -40  | _   | 85   | °C   |

| Ambient operating temperature          | 'A                                     | 8-layer Board                             | -40  | _   | 95   | °C   |

| Board operating temperature            | T <sub>B</sub>                         |                                           | -40  | _   | 105  | °C   |

|                                        |                                        | LVCMOS, S-LVDS, HCSL input clock(s)       | 1.71 | 1.8 | 1.89 | V    |

| Core supply voltage range <sup>1</sup> | V <sub>DD</sub>                        | LVCMOS, LVDS, LVPECL, HCSL input clock(s) | 2.37 | 2.5 | 2.63 | V    |

|                                        |                                        | LVCMOS, LVDS, LVPECL, HCSL input clock(s) | 3.13 | 3.3 | 3.47 | V    |

|                                        |                                        | S-LVDS, HCSL                              | 1.71 | 1.8 | 1.89 | V    |

| Output buffer supply voltage range     | V <sub>DDOA</sub><br>V <sub>DDOB</sub> | LVDS, LVPECL, HCSL                        | 2.37 | 2.5 | 2.63 | V    |

|                                        |                                        | LVDS, LVPECL, HCSL                        | 3.13 | 3.3 | 3.47 | V    |

|                                        |                                        |                                           | 1.71 | 1.8 | 1.89 | V    |

| Reference output supply voltage range  | $V_{DDOC}$                             | LVCMOS                                    | 2.37 | 2.5 | 2.63 | V    |

|                                        |                                        |                                           | 3.13 | 3.3 | 3.47 | V    |

<sup>1.</sup> Core supply  $V_{DD}$  and output buffer supplies  $V_{DDOx}$  are independent.  $V_{DDOx} \le V_{DD}$ .

#### **Table 11. Input Clock Specifications**

$(V_{DD} = 1.8 \text{ V} \pm 5\%, 2.5 \text{ V} \pm 5\%, \text{ or } 3.3 \text{ V} \pm 5\%, T_A = -40 \text{ to } 95 \text{ °C})$

| Parameter                               | Symbol            | Test Condition                                                                                        | Min                   | Тур | Max                   | Unit |

|-----------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|------|

| Differential input                      | V                 | V <sub>DD</sub> = 2.5 V ± 5%, 3.3 V ± 5%                                                              | 0.25                  | _   | V <sub>DD</sub> - 1.1 | V    |

| common-mode voltage                     | V <sub>CM</sub>   | V <sub>DD</sub> = 1.8 V ± 5%                                                                          | 0.25                  | _   | V <sub>DD</sub> - 0.8 | V    |

| Differential input swing (peak-to-peak) | V <sub>IN</sub>   | V <sub>DD</sub> = 1.8 V ± 5%, 2.5 V ± 5%, 3.3 V ± 5%                                                  | 0.20                  | _   | 2.2                   | V    |

| Input slew rate <sup>1</sup>            | SR                | Differential input                                                                                    | 3.0                   | _   | _                     | V/ns |

| input siew rate                         | SK .              | Single-ended input                                                                                    | 1.0                   | _   | _                     | V/ns |

| LVCMOS input high voltage               | V <sub>IH</sub>   |                                                                                                       | V <sub>DD</sub> × 0.7 | _   | _                     | V    |

| LVCMOS input low voltage                | V <sub>IL</sub>   |                                                                                                       | _                     | _   | $V_{DD} \times 0.3$   | V    |

|                                         |                   | CLKO/CLK0b and CLK1/CLK1b,<br>Differential Input                                                      | DC                    | _   | 3100                  | MHz  |

|                                         |                   | CLKO and CLK1 pins, Single Ended Input                                                                | DC                    | _   | 250                   | MHz  |

| Input frequency                         | F <sub>IN</sub>   | XA pin (driven single-ended, ac) input clock duty cycle 50%, output clock duty cycle 45% min/55% max. | 0.1                   | _   | 100                   | MHz  |

|                                         |                   | XA pin (driven single-ended, ac) input clock duty cycle 50%, output clock duty cycle 40% min/60% max. | 100                   | -   | 250                   | MHz  |

| Crystal frequency                       | F <sub>XTAL</sub> | Fundamental mode crystal <sup>2</sup>                                                                 | 24                    |     | 54                    | MHz  |

| Innut conscitones                       |                   | CLKO and CLK1 pins with respect to GND                                                                | _                     | 2.5 | _                     | pF   |

| Input capacitance                       | C <sub>IN</sub>   | XA with respect to GND                                                                                | _                     | 4   | _                     | pF   |

- 1. Required to meet prop delay and additive jitter specifications (20-80%). The device functions with a slower slew rate but may have increased jitter.

- 2. Max Crystal ESR for 24 MHz = 50 Ω, 54 MHz = 5Ω; C<sub>L</sub> = 8 pF, C<sub>0</sub> ≤ 2 pF; from Figure 16 on page 17: C<sub>1(XA)</sub> = 6.8 pF; C<sub>2(XB)</sub> = 8 pF. These values are based on the PCB layout used for characterization; equations for calculating these values for other layouts are provided in AN1405.

#### **Table 12. DC Common Characteristics**

$(V_{DD}/V_{DDOx} = 1.8 \text{ V} \pm 5\%, 2.5 \text{ V} \pm 5\%, \text{ or } 3.3 \text{ V} \pm 5\%, T_{A} = -40 \text{ to } 95 \text{ °C})$

| Parameter                                     | Symbol             | Test Condition               | Min                   | Тур | Max                   | Unit |

|-----------------------------------------------|--------------------|------------------------------|-----------------------|-----|-----------------------|------|

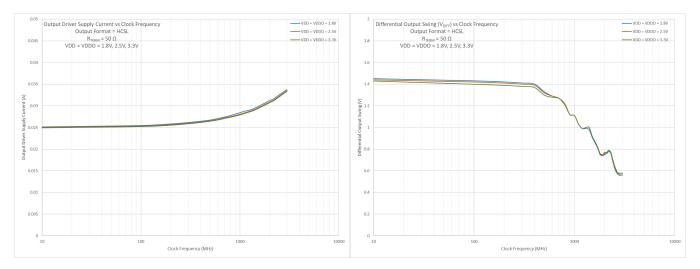

|                                               |                    | 3.3 V, HCSL, LVDS, or LVPECL | _                     | 92  | 120                   | mA   |

| Supply current                                | I <sub>DD</sub>    | 2.5 V, HCSL, LVDS, or LVPECL | _                     | 87  | 115                   | mA   |

|                                               |                    | 1.8 V, HCSL, LVDS            | _                     | 78  | 110                   | mA   |

| Output buffer supply current (per             |                    | LVPECL (3.3 V)               | _                     | 32  | _                     | mA   |

| clock output) at 156.25 MHz<br>(differential) | I <sub>DDOx</sub>  | LVDS (3.3 V)                 | _                     | 10  | _                     | mA   |

| (unierential)                                 |                    | HCSL(3.3 V)                  | _                     | 25  | _                     | mA   |

|                                               |                    | CMOS (1.8 V) <sup>1</sup>    | _                     | 8   | _                     | mA   |

| REFOUT buffer supply current at 200 MHz       | I <sub>DDREF</sub> | CMOS (2.5 V) <sup>1</sup>    | _                     | 12  | _                     | mA   |

|                                               |                    | CMOS (3.3 V) <sup>1</sup>    | _                     | 18  | _                     | mA   |

| Input high voltage                            | V <sub>IH</sub>    | SFOUTx, CLK_SELx, OE_REF     | 0.7 × V <sub>DD</sub> | _   | _                     | V    |

| Input low voltage V                           |                    | SFOUTx, CLK_SELx, OE_REF     | _                     | _   | 0.3 × V <sub>DD</sub> | V    |

| Internal pull-down resistor R <sub>PD</sub>   |                    | SFOUTX, CLK_SELX, OE_REF     | _                     | 45  | _                     | kΩ   |

<sup>1.</sup> Output capacitance load  $\leq$  5 pF for V<sub>DDOC</sub> = 1.8 V, C<sub>L</sub>  $\leq$  10 pF for V<sub>DDOC</sub> = 2.5 V, C<sub>L</sub>  $\leq$  15 pF for V<sub>DDOC</sub> = 3.3 V

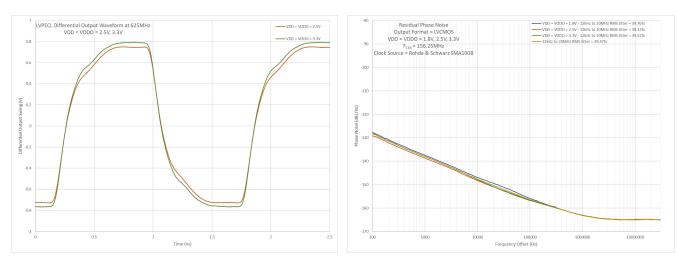

# Table 13. LVPECL Output Characteristics<sup>1</sup>

$(V_{DDOA/B} = 2.5 \text{ V} \pm 5\% \text{ or } 3.3 \text{ V} \pm 5\%, T_A = -40 \text{ to } 95 \text{ °C})$

| Parameter                                        | Symbol                              | Test Condition                                                           | Min                     | Тур                     | Max                     | Unit   |

|--------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|--------|

|                                                  |                                     | Full amplitude, $V_{OD} \ge 600 \text{ mV}$ , $V_{DDOx} = 2.5 \text{ V}$ | DC                      | _                       | 1275                    | MHz    |

| Output frequency                                 | F                                   | Full amplitude, $V_{OD} \ge 600 \text{ mV}$ , $V_{DDOx} = 3.3 \text{ V}$ | DC                      | _                       | 1325                    | MHz    |

| Touchut frequency                                | F <sub>OUT</sub>                    | 67% amplitude, $V_{OD} \ge 400 \text{ mV}$ , $V_{DDOx} = 2.5 \text{ V}$  | 1275                    | _                       | 2350                    | MHz    |

|                                                  |                                     | 67% amplitude, $V_{OD} \ge 400 \text{ mV}$ , $V_{DDOx} = 3.3 \text{ V}$  | 1325                    | _                       | 3100                    | MHz    |

| Output vice /fall time                           | + /+                                | LVPECL, 20/80%, 3.3 V                                                    | _                       | 200                     | 225                     | ps     |

| Output rise/fall time                            | t <sub>R</sub> /t <sub>F</sub>      | LVPECL, 20/80%, 2.5 V                                                    | _                       | 185                     | 220                     | ps     |

| Output dc common mode voltage                    | V <sub>CMO</sub>                    |                                                                          | V <sub>DDOx</sub> – 1.5 | V <sub>DDOx</sub> - 1.3 | V <sub>DDOx</sub> - 1.0 | V      |

| Output high voltage                              | V <sub>OH</sub>                     |                                                                          | V <sub>DDOx</sub> - 1.2 | V <sub>DDOx</sub> - 0.9 | V <sub>DDOx</sub> - 0.6 | V      |

| Output low voltage                               | V <sub>OL</sub>                     | $T_A = 25$ °C, dc measurement,<br>$R_D = 50 \Omega$ to $V_{DDOx} - 2 V$  | V <sub>DDOx</sub> - 2.0 | V <sub>DDOx</sub> - 1.7 | V <sub>DDOx</sub> - 1.4 | V      |

| Output voltage swing                             | V <sub>OD</sub>                     | _ p                                                                      | 600                     | 800                     | 1000                    | mV     |

| Output duty cycle                                | DC                                  | Input clock must have 50% duty cycle                                     | 45                      | 50                      | 55                      | %      |

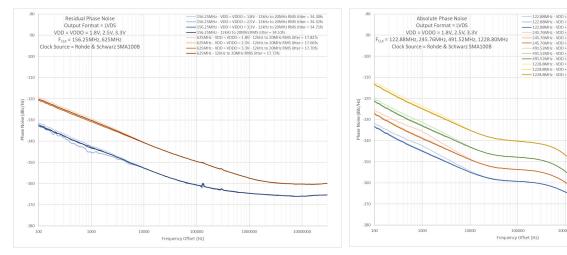

| Additive noise floor f <sub>offset</sub> ≥10 MHz | NF                                  | F <sub>OUT</sub> = 156.25 MHz                                            | _                       | -166                    | _                       | dBc/Hz |

| Propagation delay                                | T <sub>PLH</sub> , T <sub>PHL</sub> | CLKO or CLK1 input pins to output driver pins                            | 575                     | 765                     | 1070                    | ps     |

<sup>1.</sup> Unused outputs should be left floating. Do not short unused outputs to ground.

# Table 14. LVDS Output Characteristics<sup>1</sup>

$(V_{DDOA/B} = 1.8 \text{ V} \pm 5\%, 2.5 \text{ V} \pm 5\%, \text{ or } 3.3 \text{ V} \pm 5\%, T_A = -40 \text{ to } 95 \text{ °C})$

| Parameter                                              | Symbol                              | Test Condition                                                                                   | Min  | Тур  | Max  | Unit   |

|--------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------|------|------|------|--------|

| Output frequency                                       | _                                   | Full amplitude, V <sub>OD</sub> ≥ 247 mV                                                         | 0    | _    | 2200 | MHz    |

| Output frequency                                       | F <sub>OUT</sub>                    | 67% amplitude, V <sub>OD</sub> ≥ 167 mV                                                          | 2200 | _    | 3000 | MHz    |

| Delta V <sub>OD</sub>                                  | $\Delta V_{OD}$                     |                                                                                                  |      |      | 50   | mV     |

| Offset voltage<br>(V <sub>DDOx</sub> = 2.5 V or 3.3 V) | V                                   | $V_{DDOx}$ = 2.37 to 2.63 V, 3.13 to 3.47 V, $R_L$ = 100 $\Omega$ across Qn and Qnb              | 1.15 | 1.2  | 1.25 | V      |

| Offset voltage (V <sub>DDOx</sub> = 1.8 V)             | - V <sub>OS</sub>                   | $V_{DDOx}$ = 1.71 to 1.89 V,<br>R <sub>L</sub> = 100 Ω across Qn and Qnb                         | 0.85 | 0.9  | 0.95 | ٧      |

| Delta V <sub>OS</sub>                                  | $\Delta V_{OS}$                     |                                                                                                  |      |      | 50   | mV     |

| Output rise/fall time                                  | t <sub>R</sub> , t <sub>F</sub>     | LVDS, 20/80%                                                                                     | _    | 200  | 260  | ps     |

| Output voltage swing                                   | V <sub>OD</sub>                     | $R_L$ = 100 $\Omega$ across Qn and Qnb                                                           | 247  | 390  | 454  | mV     |

| Output duty cycle                                      | DC                                  | $F_{OUT} \le 3000$ MHz,<br>Input clock must have 50% duty cycle,<br>800 mV $V_{IN}$ , ac-coupled | 45   | 50   | 55   | %      |

| Additive noise floor, f <sub>offset</sub> ≥10 MHz      | NF                                  | F <sub>OUT</sub> = 156.25 MHz                                                                    | _    | -165 | _    | dBc/Hz |

| Propagation delay                                      | T <sub>PLH</sub> , T <sub>PHL</sub> | CLKO or CLK1 input pins to output driver pins                                                    | 560  | 825  | 1145 | ps     |

<sup>1.</sup> Unused outputs should be left floating. Do not short unused outputs to ground.

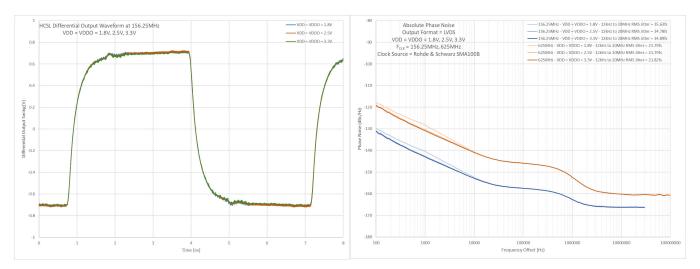

# Table 15. HCSL Output Characteristics 1,2

$(V_{DDOA/B} = 1.8 \text{ V} \pm 5\%, 2.5 \text{ V} \pm 5\%, \text{ or } 3.3 \text{ V} \pm 5\%, T_A = -40 \text{ to } 95 \text{ °C})$

| Parameter                                               | Symbol                              | Test Condition                                                                    | Min  | Тур  | Max  | Unit   |

|---------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------|------|------|------|--------|

| Output from one                                         | _                                   | Full amplitude                                                                    | 0    | _    | 650  | MHz    |

| Output frequency                                        | F <sub>OUT</sub>                    | 67% amplitude                                                                     | 650  | _    | 800  | MHz    |

| Output rise/fall time                                   | t <sub>R</sub> /t <sub>F</sub>      | 20/80%                                                                            | _    | 300  | 400  | ps     |

| Single-ended output swing                               | V <sub>SE</sub>                     | DC measurement, $R_L = 50 \Omega$ to ground                                       | 0.60 | 0.80 | 1.0  | ٧      |

| Output duty cycle                                       | DC                                  | Input clock must have 50% duty cycle                                              | 45   | 50   | 55   | %      |

| Additive noise floor, f <sub>offset</sub> >10 MHz       | N <sub>FLOOR</sub>                  | F <sub>OUT</sub> = 156.25 MHz                                                     | _    | -166 | _    | dBc/Hz |

| Propagation delay                                       | T <sub>PLH</sub> , T <sub>PHL</sub> | CLKO or CLK1 input pins to output driver pins                                     | 575  | 820  | 1110 | ps     |

| Rise-Fall matching                                      | R/F <sub>Match</sub>                |                                                                                   | _    | 10   | _    | %      |

| Variation of fall time over all falling clock edges     | T <sub>Fall_Delta</sub>             |                                                                                   | _    | 20   | _    | ps     |

| Variation of rise time over all rising clock edges      | T <sub>Rise_Delta</sub>             |                                                                                   | _    | 15   | _    | ps     |

| Absolute crossing point voltage (V)                     | V <sub>Cross</sub>                  | 100 MHz PCIe Reference Clock as source, with/without spread spectrum <sup>3</sup> | 0.33 | 0.4  | 0.48 | ٧      |

| Variation of crossing point over all rising clock edges | V <sub>Cross_Delta</sub>            | with without spread spectrum                                                      | _    | 40   | _    | mV     |

| Overshoot voltage                                       | V <sub>Ovs</sub>                    |                                                                                   | -20  | _    | 40   | mV     |

| Undershoot voltage                                      | V <sub>Uds</sub>                    | s                                                                                 |      | _    | 40   | mV     |

| Ring-back voltage                                       | $V_{Rb}$                            |                                                                                   | _    | _    | 80   | mV     |

<sup>1.</sup> Unused outputs should be left floating. Do not short unused outputs to ground.

<sup>2.</sup> DC-coupled HCSL Clock Output Termination. See Figure 19 on page 18.

<sup>3.</sup> Parameters measured with Skyworks PCI Express Clock Jitter Tool on a 100 MHz HCSL load-terminated clock waveform with/without spread spectrum, over at least 100,000 clock periods.

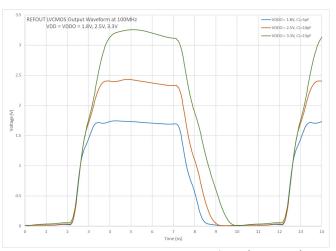

#### **Table 16. REFOUT Output Characteristics (LVCMOS)**

$(V_{DDOC} = 1.8 \text{ V} \pm 5\%, 2.5 \text{ V} \pm 5\%, \text{ or } 3.3 \text{ V} \pm 5\%, T_A = -40 \text{ to } 95 \text{ °C}).$

| Parameter                               | Symbol                              | Test Condition                                                                                                                                                                                                                                                                                               | Min                    | Тур  | Max                     | Unit            |

|-----------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------------------------|-----------------|

| Noise floor f <sub>offset</sub> ≥10 MHz | NF                                  | V <sub>DDOC</sub> = 3.3 V,<br>F <sub>out</sub> = 156.25 MHz                                                                                                                                                                                                                                                  | _                      | -164 | _                       | dBc/Hz          |

| REFOUT output enable time <sup>1</sup>  | T <sub>EN_REF</sub>                 | F ≤250 MHz                                                                                                                                                                                                                                                                                                   | _                      | 3    | 4                       | Clock<br>cycles |

| REFOUT output disable time <sup>1</sup> | T <sub>DIS_REF</sub>                | F ≤250 MHz                                                                                                                                                                                                                                                                                                   | _                      | 3    | 4                       | Clock<br>cycles |

| Output frequency                        | F <sub>OUT</sub>                    | REFOUT                                                                                                                                                                                                                                                                                                       | 0                      | _    | 250                     | MHz             |

| Output voltage high                     | V                                   | I <sub>OUT</sub> = -1 mA                                                                                                                                                                                                                                                                                     | $0.9 \times V_{DDOC}$  | _    | _                       | V               |

| Output voitage nign                     | V <sub>OH</sub>                     | I <sub>OUT</sub> = -10 mA                                                                                                                                                                                                                                                                                    | $0.75 \times V_{DDOC}$ | _    | _                       | V               |

| Output voltage low                      | V                                   | I <sub>OUT</sub> = 1 mA                                                                                                                                                                                                                                                                                      | _                      | _    | 0.1 × V <sub>DDOC</sub> | V               |

| Output voltage low                      | V <sub>OL</sub>                     | I <sub>OUT</sub> = 10 mA                                                                                                                                                                                                                                                                                     | _                      | _    | $0.25 \times V_{DDOC}$  | V               |

|                                         |                                     | 20%/80%, 1.8 V, $C_L$ = 5 pF, 50 $\Omega$ load impedance                                                                                                                                                                                                                                                     | _                      | 640  | 750                     | ps              |

| Output rise/fall time                   | t <sub>R</sub> /t <sub>F</sub>      | 20%/80%, 2.5 V, $C_L$ = 10 pF, 50 $\Omega$ load impedance                                                                                                                                                                                                                                                    | _                      | 775  | 910                     | ps              |