### Specification for 1.54 inch EPD

Model NO.: MT-DEPG0154RWS800F35

This module uses ROHS material

| CI    | USTOMER   |

|-------|-----------|

|       |           |

|       |           |

|       |           |

| APP   | PROVED BY |

|       |           |

|       |           |

|       |           |

| DATE: |           |

Tel: 1 (888) 499-8477

Fax: (407) 273-0771

E-mail: mtusainfo@microtipsusa.com

Web: www.microtipsusa.com

## **Revision History**

| Version | Content     | Date       | Producer |

|---------|-------------|------------|----------|

| 2.0     | New release | 2023/09/13 |          |

|         |             |            |          |

|         |             |            |          |

|         |             |            |          |

|         |             |            |          |

|         |             |            |          |

|         |             |            |          |

## CONTENTS

| 1. Over View                                                | 5  |

|-------------------------------------------------------------|----|

| 2. Features                                                 | 5  |

| 3. Mechanical and Optical Specification                     | 6  |

| 4.Mechanical Drawing of EPD Module                          | 7  |

| 5. Input/output Pin Assignment                              | 8  |

| 6. Electrical Characteristics                               | 9  |

| 6.1 Absolute Maximum Rating                                 | 9  |

| 6.2 Panel DC Characteristics                                | 10 |

| 6.3 Panel DC Characteristics(Driver IC Internal Regulators) | 11 |

| 6.4 Panel AC Characteristics                                | 11 |

| 6.4.1 MCU Interface Selection                               | 11 |

| 6.4.2 MCU Serial Interface (4-wire SPI)                     | 11 |

| 6.4.3 MCU Serial Interface (3-wire SPI)                     | 13 |

| 6.4.4 Interface Timing                                      | 14 |

| 7. Command Table                                            | 16 |

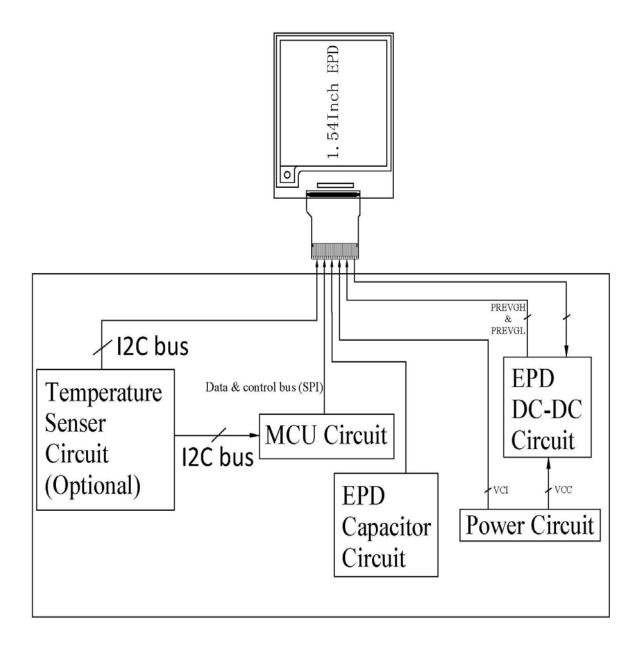

| 8. Block Diagram                                            | 24 |

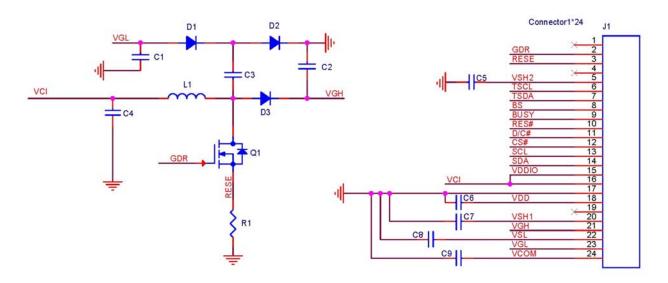

| 9. Typical Application Circuit with SPI Interface           | 25 |

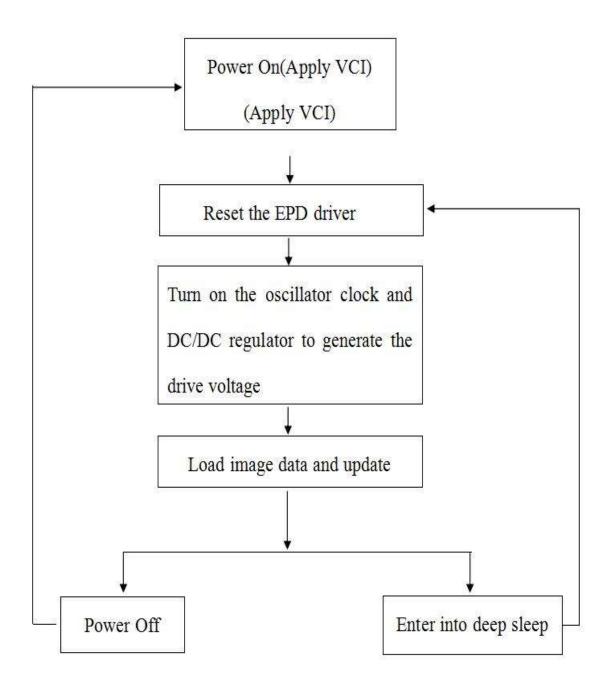

| 10 Typical Operating Sequence                               | 26 |

| 10.1 OTP Operation Flow                                     | 26 |

| 10.2 OTP Operation Reference Program Code                   | 27 |

| 11. Reliability Test                                        | 27 |

| 12.Quality Assurance                                        | 28 |

| 12.1 Environment                                            | 28 |

| 12.2 Illuminance                                            | 28 |

|                                                             |    |

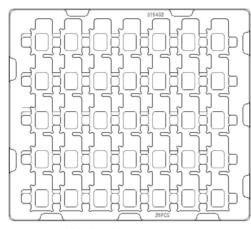

| 12.3 Inspect method                                | 28 |

|----------------------------------------------------|----|

| 12.4 Display area                                  | 28 |

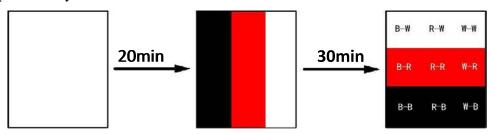

| 12.5 Ghosting test method                          | 28 |

| 12.6 Inspection standard                           | 30 |

| 12.6.1 Electric inspection standard                | 30 |

| 12.6.2 Appearance inspection standard              | 30 |

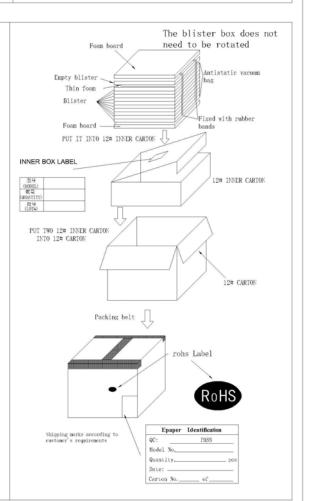

| 13.Packaging                                       | 32 |

| 14. Handling, Safety, and Environment Requirements | 33 |

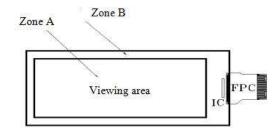

### 1. Over View

MT-DEPG0154RWS800F35 is an Active Matrix Electrophoretic Display (AM EPD), with interface and a reference system design. The display is capable to display images at 1-bit white, black and red full display capabilities. The 1.54inch active area contains 152×152 pixels. The module is a TFT-array driving electrophoresis display, with integrated circuits including gate driver, source driver, MCU interface, timing controller, oscillator, DC-DC, SRAM, LUT, VCOM. Module can be used in portable electronic devices, such as Electronic Shelf Label (ESL) System.

#### 2. Features

- ♦152×152 pixels display

- ◆ High contrast High reflectance

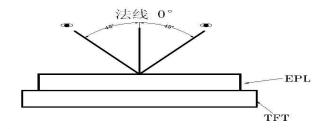

- ◆Ultra wide viewing angle Ultra low power consumption

- ◆Pure reflective mode

- ◆Bi-stable display

- ◆Commercial temperature range

- ◆Landscape portrait modes

- ◆ Hard-coat antiglare display surface

- ◆Ultra Low current deep sleep mode

- ◆On chip display RAM

- ◆ Waveform can stored in On-chip OTP or written by MCU

- ◆ Serial peripheral interface available

- ♦ On-chip oscillator

- ◆On-chip booster and regulator control for generating VCOM, Gate and Source driving voltage

- ◆I<sup>2</sup>C signal master interface to read external temperature sensor

- ◆Built-in temperature sensor

## 3. Mechanical and Optical Specification

| Parameter           | Specifications             | Unit  | Remark  |

|---------------------|----------------------------|-------|---------|

| Screen Size         | 1.54                       | Inch  |         |

| Display Resolution  | 152(H)×152(V)              | Pixel | DPI:140 |

| Active Area         | 26.98×26.98                | mm    |         |

| Pixel Pitch         | 0.1775×0.1775              | mm    |         |

| Pixel Configuration | Rectangle                  |       |         |

| Outline Dimension   | 31.8(H)×37.32 (V) ×1.0 (D) | mm    |         |

| Weight              | 2.18±0.5                   | g     |         |

| Symbol | Parameter                   | Conditions            | Min  | Тур.   | Max | Units | Notes |

|--------|-----------------------------|-----------------------|------|--------|-----|-------|-------|

|        | Black State L* value        |                       | -    | 13     | 15  |       | 3-1   |

| IZ C   | Black State A* value        |                       | -    | 4      | 6   |       | 3-1   |

| KS     | Black Ghosting $\Delta L$   |                       | -    | 1      | -   |       | 3-1   |

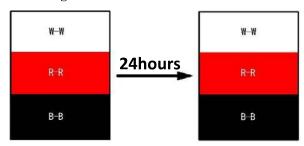

|        | After 24hour colour changed |                       | -    | 2      | -   |       | 3-4   |

|        | White State L* value        |                       | 62   | 65     | -   |       | 3-1   |

| WC     | White State A* value        |                       | -    | 0      | 1   |       | 3-1   |

| WS     | White Ghosting △ L          |                       | -    | 1      | -   |       | 3-1   |

|        | After 24hour colour changed |                       | -    | 2      | -   |       | 3-4   |

|        | Red State L* value          |                       | 27   | 28     | 32  |       | 3-1   |

| RS     | Red State A* value          |                       | 36   | 40     | 45  |       | 3-1   |

| KS     | Red Ghosting △E             |                       | _    | 3      | -   |       | 3-1   |

|        | After 24hour colour changed |                       | -    | 2      | -   |       | 3-4   |

| R      | White Reflectivity          | White                 | 30   | 34     | -   | %     | 3-1   |

| CR     | Contrast Ratio              | Indoor                | 15:1 | 20     | -   |       | 3-1   |

|        |                             |                       |      |        |     |       | 3-2   |

| GN     | 2Grey Level                 | -                     | -    | -      | -   |       |       |

|        |                             | Temp:23 $\pm$ 3°C     |      |        |     |       |       |

| Life   |                             | Humidity:55±<br>10%RH |      | 5years |     |       | 3-3   |

Notes: 3-1. Luminance meter: Eye-One Pro Spectrophotometer.

- 3-2. CR=Surface Reflectance with all white pixel/Surface Reflectance with all black pixels.

- 3-3. When the product is stored. The display screen should be kept white and face up.

- 3-4. After 24hour Colour Changed:

W: Max  $\triangle$  E(W-W)<2, K: Max  $\triangle$  E(B-B)<2, R: Max  $\triangle$  Eab(R-R)<2.

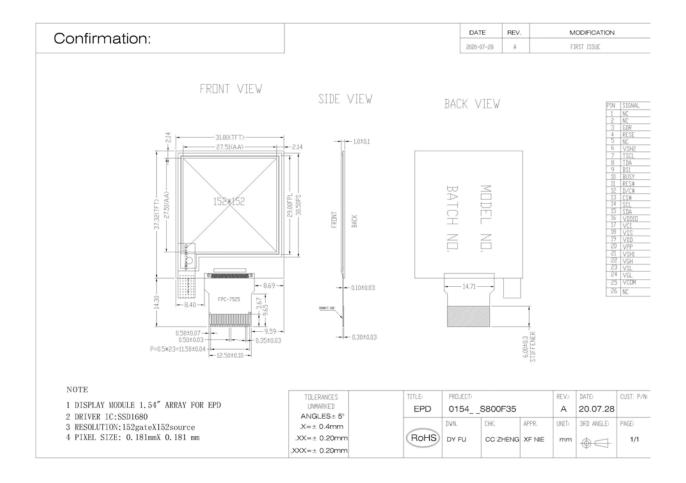

## 4.Mechanical Drawing of EPD Module

## 5. Input/output Pin Assignment

| No. | Name  | I/O | Description                                                                                                        | Remark    |

|-----|-------|-----|--------------------------------------------------------------------------------------------------------------------|-----------|

| 1   | NC    |     | Do not connect with other NC pins                                                                                  | Keep Open |

| 2   | GDR   | О   | N-Channel MOSFET Gate Drive Control                                                                                |           |

| 3   | RESE  | I   | Current Sense Input for the Control Loop                                                                           |           |

| 4   | NC    | NC  | Do not connect with other NC pins                                                                                  | Keep Open |

| 5   | VSH2  | С   | Positive Source driving voltage(Red)                                                                               |           |

| 6   | TSCL  | О   | I2C Interface to digital temperature sensor Clock pin                                                              | Note 5-6  |

| 7   | TSDA  | I/O | I2C Interface to digital temperature sensor Data pin                                                               | Note 5-6  |

| 8   | BS1   | I   | Bus Interface selection pin                                                                                        | Note 5-5  |

| 9   | BUSY  | О   | Busy state output pin                                                                                              | Note 5-4  |

| 10  | RES#  | I   | Reset signal input. Active Low.                                                                                    | Note 5-3  |

| 11  | D/C#  | I   | Data /Command control pin                                                                                          | Note 5-2  |

| 12  | CS#   | I   | Chip select input pin                                                                                              | Note 5-1  |

| 13  | SCL   | I   | Serial Clock pin (SPI)                                                                                             |           |

| 14  | SDA   | I/O | Serial Data pin (SPI)                                                                                              |           |

| 15  | VDDIO | P   | Power Supply for interface logic pins It should be connected with VCI                                              |           |

| 16  | VCI   | P   | Power Supply for the chip                                                                                          |           |

| 17  | VSS   | P   | Ground                                                                                                             |           |

| 18  | VDD   | С   | Core logic power pin VDD can be regulated internally from VCI. A capacitor should be connected between VDD and VSS |           |

| 19  | VPP   | P   | FOR TEST                                                                                                           | Keep Open |

| 20  | VSH1  | С   | Positive Source driving voltage                                                                                    |           |

| 21  | VGH   | С   | Power Supply pin for Positive Gate driving voltage and VSH1                                                        |           |

| 22  | VSL   | C   | Negative Source driving voltage                                                                                    |           |

| 23  | VGL   | С   | Power Supply pin for Negative Gate driving voltage VCOM and VSL                                                    |           |

| 24  | VCOM  | C   | VCOM driving voltage                                                                                               |           |

I = Input Pin, O = Output Pin, /O = Bi-directional Pin (Input/output), P = Power Pin, C = Capacitor Pin Note 5-1: This pin (CS#) is the chip select input connecting to the MCU. The chip is enabled for MCU

communication only when CS# is pulled LOW.

- Note 5-2: This pin is (D/C#) Data/Command control pin connecting to the MCU in 4-wire SPI mode. When the pin is pulled HIGH, the data at SDA will be interpreted as data. When the pin is pulled LOW, the data at SDA will be interpreted as command.

- Note 5-3: This pin (RES#) is reset signal input. The Reset is active low.

- Note 5-4: This pin is Busy state output pin. When Busy is High, the operation of chip should not be interrupted, command should not be sent. The chip would put Busy pin High when -Outputting display waveform -Communicating with digital temperature sensor

Note 5-5: Bus interface selection pin

Note 5-6: This pin connect to the VSS if there is no external temperature sensor.

| BS1 State | MCU Interface                                          |  |  |  |  |  |

|-----------|--------------------------------------------------------|--|--|--|--|--|

| L         | 4-lines serial peripheral interface(SPI) - 8 bits SPI  |  |  |  |  |  |

| Н         | 3- lines serial peripheral interface(SPI) - 9 bits SPI |  |  |  |  |  |

#### 6. Electrical Characteristics

6.1 Absolute Maximum Rating

| Parameter                | Symbol | Rating           | Unit |

|--------------------------|--------|------------------|------|

| Logic supply voltage     | VCI    | -0.5 to +6.0     | V    |

| Logic Input voltage      | VIN    | -0.5 to VCI +0.5 | V    |

| Logic Output voltage     | VOUT   | -0.5 to VCI +0.5 | V    |

| Operating Temp range     | TOPR   | 0 to +40         | °C.  |

| Storage Temp range       | TSTG   | -25 to+40        | °C.  |

| Optimal Storage Temp     | TSTGo  | 23±3             | °C.  |

| Optimal Storage Humidity | HSTGo  | 55±10            | %RH  |

#### Note:

- 1. Maximum ratings are those values beyond which damages to the device may occur. Functional operation should be restricted to the limits in the Panel DC Characteristics tables.

- 2. We guarantee the single pixel display quality for 0-35°C, but we only guarantee the barcode readable for 35-40°C.

- 3. The storage time is within 10 days for  $-25^{\circ}\text{C} \sim 0^{\circ}\text{C}$  or  $40^{\circ}\text{C} \sim 60^{\circ}\text{C}$ . The display screen should be kept white and face up.

### 6.2 Panel DC Characteristics

The following specifications apply for: VSS=0V, VCI=3.0V, TOPR =23°C.

| Parameter                 | Symbol    | Condition                                                 | Applicab<br>le pin | Min.    | Тур.  | Max.    | Unit |

|---------------------------|-----------|-----------------------------------------------------------|--------------------|---------|-------|---------|------|

| Single ground             | Vss       | -                                                         |                    | -       | 0     | -       | V    |

| Logic supply voltage      | Vci       | -                                                         | VCI                | 2.2     | 3.0   | 3.7     | V    |

| Core logic voltage        | Vdd       |                                                           | VDD                | 1.7     | 1.8   | 1.9     | V    |

| High level input voltage  | Vih       | -                                                         | -                  | 0.8 Vci | -     | -       | V    |

| Low level input voltage   | VIL       | -                                                         | -                  | -       | -     | 0.2 Vci | V    |

| High level output voltage | Vон       | IOH = -100uA                                              | -                  | 0.9 Vci | -     | -       | V    |

| Low level output voltage  | Vol       | IOL = 100uA                                               | -                  | -       | -     | 0.1 Vci | V    |

| Typical power             | PTYP      | V <sub>CI</sub> =3.0V                                     | -                  | -       | 8.4   | -       | mW   |

| Deep sleep mode           | PSTPY     | V <sub>CI</sub> =3.0V                                     | -                  | -       | 0.003 | _       | mW   |

| Typical operating current | Iopr_VCI  | V <sub>CI</sub> =3.0V                                     | -                  | -       | 2.8   | -       | mA   |

| Image update time         | -         | 23 °C                                                     | -                  | -       | 20    | -       | sec  |

| Typical peak current      | Iopr_VCI  | 2.2~3.7V                                                  |                    |         | 30    | 40      | mA   |

| Sleep mode current        | Islp_Vcı  | DC/DC off<br>No clock<br>No input load<br>Ram data retain | -                  | -       | 20    |         | uA   |

| Deep sleep mode current   | Idslp_Vci | DC/DC off No clock No input load Ram data not retain      | -                  | -       | 1     | 5       | uA   |

Notes: 1. The typical power is measured with following transition from horizontal 3 scale pattern to vertical 3 scale pattern.

- 2. The deep sleep power is the consumed power when the panel controller is in deep sleep mode.

- 3. The listed electrical/optical characteristics are only guaranteed under the controller & waveform provided by DKE.

- 4. Electrical measurement: Tektronix oscilloscope MDO3024,

Tektronix current probe - TCP0030A.

### 6.3 Panel DC Characteristics(Driver IC Internal Regulators)

The following specifications apply for: VSS=0V, VCI=3.0V, TOPR =23°C.

| Parameter                      | Symbol | Condition | Applicable pin | Min.  | Тур. | Max.  | Unit |

|--------------------------------|--------|-----------|----------------|-------|------|-------|------|

| VCOM output voltage            | VCOM   | -         | VCOM           | -     | TBD  | -     | V    |

| Positive Source output voltage | Vsh    | -         | S0~S151        | +14.5 | +15  | +15.5 | V    |

| Negative Source output voltage | Vsl    | -         | S0~S151        | -15.5 | -15  | -14.5 | V    |

| Positive gate output voltage   | Vgh    | -         | G0~G151        | +19   | +20  | +21   | V    |

| Negative gate output voltage   | Vgl    | -         | G0~G151        | -21   | -20  | -19   | V    |

Notes:VGH,VGL,VSH,VSL drop voltage<2V.

#### 6.4 Panel AC Characteristics

#### **6.4.1 MCU Interface Selection**

The pin assignment at different interface mode is summarized in Table 6-4-1. Different MCU mode can be set by hardware selection on BS1 pins. The display panel only supports 4-wire SPI or 3-wire SPI interface mode.

| Pin Name         | Data/Comm | and Interface | Control Signal |      |      |  |

|------------------|-----------|---------------|----------------|------|------|--|

| Bus interface    | SDA       | SCL           | CS#            | D/C# | RES# |  |

| BS1=L 4-wire SPI | SDA       | SCL           | CS#            | D/C# | RES# |  |

| BS1=H 3-wire SPI | SDA       | SCL           | CS#            | L    | RES# |  |

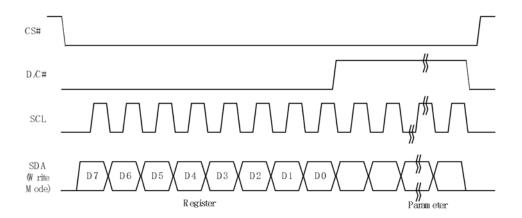

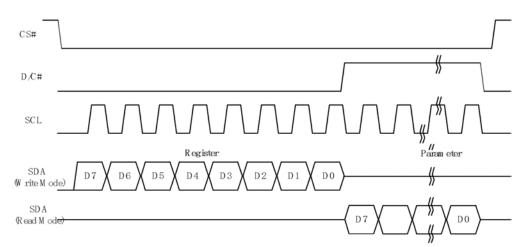

#### 6.4.2 MCU Serial Interface (4-wire SPI)

The serial interface consists of serial clock SCL, serial data SDA, D/C#, CS#. This interface supports Write mode and Read mode.

| Function      | CS# | D/C# | SCL      |

|---------------|-----|------|----------|

| Write command | L   | L    | <b>↑</b> |

| Write data    | L   | Н    | 1        |

Note: ↑ stands for rising edge of signal

In the write mode SDA is shifted into an 8-bit shift register on every rising edge of SCL in the order of D7, D6, ... D0. The level of D/C# should be kept over the whole byte. The data byte in the shift register is written to the Graphic Display Data RAM /Data Byte register or command Byte register according to D/C# pin.

Figure 6-1: Write procedure in 4-wire SPI mode

#### In the Read mode:

- 1. After driving CS# to low, MCU need to define the register to be read.

- 2. SDA is shifted into an 8-bit shift register on every rising edge of SCL in the order of D7, D6, ... D0 with D/C# keep low.

- 3. After SCL change to low for the last bit of register, D/C# need to drive to high.

- 4. SDA is shifted out an 8-bit data on every falling edge of SCL in the order of D7, D6, ... D0.

- 5. Depending on register type, more than 1 byte can be read out. After all byte are read, CS# need to drive to high to stop the read operation.

Figure 6-2: Read procedure in 4-wire SPI mode

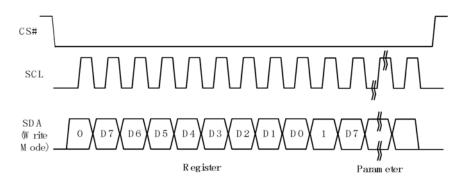

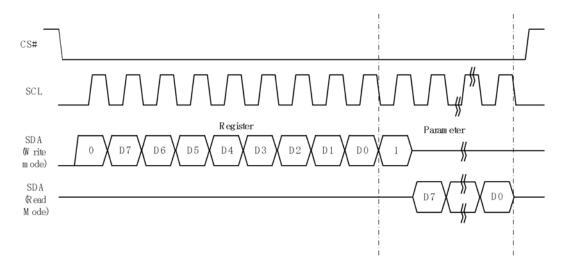

#### 6.4.3 MCU Serial Interface (3-wire SPI)

The 3-wire serial interface consists of serial clock SCL, serial data SDA and CS#. This interface also supports Write mode and Read mode.

The operation is similar to 4-wire serial interface while D/C# pin is not used. There are altogether 9-bits will be shifted into the shift register on every ninth clock in sequence: D/C# bit, D7 to D0 bit. The D/C# bit (first bit of the sequential data) will determine the following data byte in the shift register is written to the Display Data RAM (D/C# bit = 1) or the command register (D/C# bit = 0).

| Function      | CS# | D/C# | SCL      |

|---------------|-----|------|----------|

| Write command | L   | Tie  | <b>↑</b> |

| Write data    | L   | Tie  | <b>↑</b> |

Note: ↑ stands for rising edge of signal

Figure 6-3: Write procedure in 3-wire SPI mode

#### In the Read mode:

- 1. After driving CS# to low, MCU need to define the register to be read.

- 2. D/C=0 is shifted thru SDA with one rising edge of SCL

- 3. SDA is shifted into an 8-bit shift register on every rising edge of SCL in the order of D7, D6, ... D0.

- 4. D/C=1 is shifted thru SDA with one rising edge of SCL

- 5. SDA is shifted out an 8-bit data on every falling edge of SCL in the order of D7, D6, ... D0.

- 6. Depending on register type, more than 1 byte can be read out. After all byte are read, CS# need to drive to high to stop the read operation.

Figure 6-4: Read procedure in 3-wire SPI mode

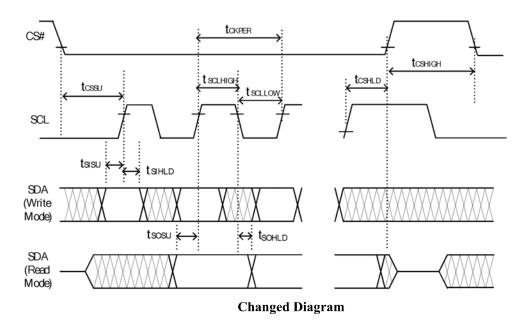

### **6.4.4 Interface Timing**

The following specifications apply for: VSS=0V, VCI=3.0V, TOPR =23°C.

### **Serial Interface Timing Characteristics**

$(VCI - VSS = 2.2V \text{ to } 3.7V, TOPR = 23^{\circ}C, CL=20pF)$

#### Write mode

| Symbol   | Parameter                                                                    | Min | Тур. | Max | Unit |

|----------|------------------------------------------------------------------------------|-----|------|-----|------|

| fSCL     | SCL frequency (Write Mode)                                                   |     |      | 20  | MHz  |

| tCSSU    | Time CS# has to be low before the first rising edge of SCLK                  | 60  |      |     | ns   |

| tCSHLD   | Time CS# has to remain low after the last falling edge of SCLK               | 65  |      |     | ns   |

| tCSHIGH  | Time CS# has to remain high between two transfers                            | 100 |      |     | ns   |

| tSCLHIGH | Part of the clock period where SCL has to remain high                        | 25  |      |     | ns   |

| tSCLLOW  | Part of the clock period where SCL has to remain low                         | 25  |      |     | ns   |

| tSISU    | Time SI (SDA Write Mode) has to be stable before the next rising edge of SCL | 10  |      |     | ns   |

| tSIHLD   | Time SI (SDA Write Mode) has to remain stable after the rising edge of SCL   | 40  |      |     | ns   |

#### Read mode

| Symbol       | Parameter                                                                | Min | Тур. | Max | Unit |

|--------------|--------------------------------------------------------------------------|-----|------|-----|------|

| fSCL         | SCL frequency (Read Mode)                                                |     |      | 2.5 | MHz  |

| tCSSU        | Time CS# has to be low before the first rising edge of SCLK              | 100 |      |     | ns   |

| tCSHLD       | Time CS# has to remain low after the last falling edge of SCLK           | 50  |      |     | ns   |

| tCSHIGH      | Time CS# has to remain high between two transfers                        | 250 |      |     | ns   |

| tSCLHIG<br>H | Part of the clock period where SCL has to remain high                    | 180 |      |     | ns   |

| tSCLLOW      | Part of the clock period where SCL has to remain low                     | 180 |      |     | ns   |

| tSOSU        | Time SO(SDA Read Mode) will be stable before the next rising edge of SCL |     | 50   |     | ns   |

| tSOHLD       | Time SO (SDA Read Mode) will remain stable after the failing edge of SCL |     | 0    |     | ns   |

### 7. Command Table

|      | /. C | VIII | IIIa | IIU | lai | JIC |    |    |            |                |                                                    |                                                                                                                                                                                                                                                                                |

|------|------|------|------|-----|-----|-----|----|----|------------|----------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/W# | D/C# | Hex  | D7   | D6  | D5  | D4  | D3 | D2 | D1         | D0             | Comman<br>d                                        | Description                                                                                                                                                                                                                                                                    |

| 0    | 0    | 01   | 0    | 0   | 0   | 0   | 0  | 0  | 0          | 1              | Driver                                             | Gate setting                                                                                                                                                                                                                                                                   |

| 0    | 1    |      | A7   | A6  | A5  | A4  | A3 | A2 | A1         | A0             | Output                                             | Set A[8:0]=0097h                                                                                                                                                                                                                                                               |

| 0    | 1    |      | 0    | 0   | 0   | 0   | 0  | 0  | 0          | A8             | control                                            | Set B[8:0]=00h                                                                                                                                                                                                                                                                 |

| 0    | 1    |      | 0    | 0   | 0   | 0   | 0  | В2 | B1         | В0             |                                                    |                                                                                                                                                                                                                                                                                |

| 0    | 0    | 03   | 0    | 0   | 0   | 0   | 0  | 0  | 1          | 1              | Gate                                               | SetGate Driving voltage                                                                                                                                                                                                                                                        |

|      |      |      | 0    | 0   | 0   |     |    |    |            |                | Driving                                            | A[4:0]=17h[POR],VGH at 20V[POR]                                                                                                                                                                                                                                                |

| 0    | 1    |      |      |     |     | A4  | A3 | A2 | A1         | A0             | voltage<br>control                                 | VGH setting from 10V to 20V                                                                                                                                                                                                                                                    |

| 0    | 0    | 04   | 0    | 0   | 0   | 0   | 0  | 1  | 0          | 0              | Source                                             | Set Source Driving voltage                                                                                                                                                                                                                                                     |

| 0    | 1    |      | A7   | A6  | A5  | A4  | A3 | A2 | <b>A</b> 1 | A0             | Driving                                            | A[7:0]= 41h[POR],VSH1 at 15V                                                                                                                                                                                                                                                   |

| 0    | 1    |      | В7   | В6  | В5  | B4  | В3 | B2 | B1         | В0             | voltage<br>control                                 | B[7:0]=A Ch[POR], VSH2 at 5.4V<br>C[7:0]= 32h[POR], VSL at -15V                                                                                                                                                                                                                |

| 0    | 1    |      | C7   | C6  | C5  | C4  | C3 | C2 | C1         | C0             | Control                                            | C[7.0]= 3211[1 OK], VSL at -13 V                                                                                                                                                                                                                                               |

| 0    | 0    | 08   | 0    | 0   | 0   | 0   | 1  | 0  | 0          | 0              | Initial<br>Code<br>Setting<br>OTP<br>Program       | Program Initial Code Setting The command required CLKEN=1. Refer to Register 0x22 for detail. BUSY pad will output high during operation                                                                                                                                       |

| 0    | 0    | 09   | 0    | 0   | 0   | 0   | 1  | 0  | 0          | 1              | Write                                              | Write Register for Initial Code Setting                                                                                                                                                                                                                                        |

| 0    | 1    |      | A7   | A6  | A5  | A4  | A3 | A2 | <b>A</b> 1 | A0             | Register                                           | Selection                                                                                                                                                                                                                                                                      |

| 0    | 1    |      | В7   | В6  | В5  | B4  | В3 | B2 | B1         | В0             | Code                                               | A[7:0] ~ D[7:0]: Reserved<br>Details refer to Application Notes of Initial                                                                                                                                                                                                     |

| 0    | 1    |      | C7   | C6  | C5  | C4  | C3 | C2 | C1         | C0             | Setting                                            | Code Setting                                                                                                                                                                                                                                                                   |

| 0    | 1    |      | D7   | D6  | D5  | D4  | D3 | D2 | D1         | D0             |                                                    |                                                                                                                                                                                                                                                                                |

| 0    | 0    | 0A   | 0    | 0   | 0   | 0   | 1  | 0  | 1          | 0              | Read<br>Register<br>for Initial<br>Code<br>Setting | Read Register for Initial Code Setting                                                                                                                                                                                                                                         |

| 0    | 0    | 10   | 0    | 0   | 0   | 1   | 0  | 0  | 0          | 0              | Deep                                               | Deep Sleep mode Control:                                                                                                                                                                                                                                                       |

| 0    | 1    |      | 0    | 0   | 0   | 0   | 0  | 0  | 0          | A <sub>0</sub> | Sleep<br>mode                                      | A[1:0]: Description 00 Normal Mode [POR] 01 Enter Deep Sleep Mode 1 11 Enter Deep Sleep Mode 2 After this command initiated, the chip will enter Deep Sleep Mode, BUSY pad will keep output high. Remark: To Exit Deep Sleep mode, User required to send HWRESET to the driver |

| 0    | 0    | 11   | 0    | 0   | 0   | 1   | 0  | 0  | 0          | 1              | Data<br>Entry<br>mode<br>setting                   | Define data entry sequence A[2:0] = 011 [POR] A [1:0] = ID[1:0] Address automatic increment / decrement setting The setting of incrementing or decrementing of the address counter can be made independently in each upper and                                                 |

| 0 | 1 |    | 0 | 0  | 0  | 0  | 0  | $A_2$ | $A_1$ | $A_0$ |         |                                                                                                   |

|---|---|----|---|----|----|----|----|-------|-------|-------|---------|---------------------------------------------------------------------------------------------------|

|   |   |    |   |    |    |    |    |       |       |       |         |                                                                                                   |

|   |   |    |   |    |    |    |    |       |       |       |         |                                                                                                   |

|   |   |    |   |    |    |    |    |       |       |       |         |                                                                                                   |

|   |   |    |   |    |    |    |    |       |       |       |         |                                                                                                   |

|   |   |    |   |    |    |    |    |       |       |       |         |                                                                                                   |

|   |   |    |   |    |    |    |    |       |       |       |         |                                                                                                   |

| 0 | 0 | 0C | 0 | 0  | 0  | 0  | 1  | 1     | 0     | 0     |         | Booster Enable with Phase 1, Phase 2 and Phase 3 for soft start current and duration setting.     |

|   |   |    |   |    |    |    |    |       |       |       | Control | A[7:0] -> Soft start setting for Phase1 = 8Bh [POR]                                               |

|   |   |    |   |    |    |    |    |       |       |       |         | B[7:0] -> Soft start setting for Phase2<br>= 9Ch [POR]<br>C[7:0] -> Soft start setting for Phase3 |

|   |   |    |   |    |    |    |    |       |       |       |         | = 96h [POR] D[7:0] -> Duration setting                                                            |

|   |   |    |   |    |    |    |    |       |       |       |         | = 0Fh [POR]                                                                                       |

|   |   |    |   |    |    |    |    |       |       |       |         | Bit Description of each byte:<br>A[6:0] / B[6:0] / C[6:0]:                                        |

|   |   |    |   |    |    |    |    |       |       |       |         | Bit[6:4] Driving Strength                                                                         |

|   |   |    |   |    |    |    |    |       |       |       |         | Selection<br>000 1(Weakest)                                                                       |

|   |   |    |   |    |    |    |    |       |       |       |         | 001 2<br>010 3                                                                                    |

|   |   |    |   |    |    |    |    |       |       |       |         | 011 4<br>100 5                                                                                    |

|   |   |    |   |    |    |    |    |       |       |       |         | 101 6<br>110 7                                                                                    |

|   |   |    |   |    |    |    |    |       |       |       |         | 111 8(Strongest)<br>Bit[3:0]                                                                      |

|   |   |    |   |    |    |    |    |       |       |       |         | Min Off Time Setting of GDR [ Time unit ]                                                         |

|   |   |    |   |    |    |    |    |       |       |       |         | 0000                                                                                              |

|   |   |    |   |    |    |    |    |       |       |       |         | 0011<br>NA                                                                                        |

|   |   |    |   |    |    |    |    |       |       |       |         | 0100 2.6<br>0101 3.2                                                                              |

| 0 | 1 |    | 1 | A6 | A5 | A4 | A3 | A2    | A1    | A0    |         | 0110 3.9<br>0111 4.6                                                                              |

| 0 | 1 |    | 1 | В6 | B5 | B4 | В3 | B2    | B1    | В0    | -       | 1000 5.4<br>1001 6.3                                                                              |

| 0 | 1 |    | 1 | C6 | C5 | C4 | C3 | C2    | C1    | C0    | -       | 1010 7.3                                                                                          |

| 0 | 1 |    | 0 | 0  | D5 | D4 | D3 | D2    | D1    | D0    |         | 1011 8.4                                                                                          |

| 0 | 0 | 12 | 0  | 0  | 0  | 1  | 0  | 0  | 1          | 0  | SWRES<br>ET                                           | It resets the commands and parameters to their S/W Reset default values except R10h-Deep Sleep Mode During operation, BUSY pad will output high. Note: RAM are unaffected by this command. |

|---|---|----|----|----|----|----|----|----|------------|----|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | 0 | 18 | 0  | 0  | 0  | 1  | 1  | 0  | 0          | 0  | _                                                     | Temperature Sensor Selection                                                                                                                                                               |

| 0 | 1 |    | A7 | A6 | A5 | A4 | A3 | A2 | Al         | A0 | ure<br>Sensor<br>Control                              | A[7:0] = 48h [POR], external temperature sensor<br>A[7:0] = 80h Internal temperature sensor                                                                                                |

| 0 | 0 | 1A | 0  | 0  | 0  | 1  | 1  | 0  | 1          | 0  | Temperat                                              | Write to temperature register.                                                                                                                                                             |

| 0 | 1 |    | A7 | A6 | A5 | A4 | A3 | A2 | A1         | A0 | ure<br>Sensor                                         | A[11:0] = 7FFh [POR]                                                                                                                                                                       |

| 0 | 1 |    | В7 | В6 | В5 | B4 | 0  | 0  | 0          | 0  | Control<br>(Write to<br>temperat<br>ure<br>register)l |                                                                                                                                                                                            |

| 0 | 0 | 20 | 0  | 0  | 1  | 0  | 0  | 0  | 0          | 0  | Master<br>Activatio<br>n                              | Activate Display Update Sequence The Display Update Sequence Option is located at R22h User should not interrupt this operation to avoid corruption of panel images.                       |

| 0 | 0 | 21 | 0  | 0  | 1  | 0  | 0  | 0  | 0          |    | Display                                               | RAM content option for Display Update                                                                                                                                                      |

| 0 | 1 |    | A7 | A6 | A5 | A4 | A3 | A2 | <b>A</b> 1 | A0 | Update                                                | A[7:0] = 00h [POR]                                                                                                                                                                         |

| 0 | 1 |    | В7  | 0   | 0    | 0  | 0    | 0  | 0  | 0    |           |                                                          |

|---|---|----|-----|-----|------|----|------|----|----|------|-----------|----------------------------------------------------------|

|   | 1 |    | , D |     |      |    |      |    |    |      |           |                                                          |

|   |   |    |     |     |      |    |      |    |    |      |           |                                                          |

|   |   |    |     |     |      |    |      |    |    |      |           |                                                          |

|   |   |    |     |     |      |    |      |    |    |      |           |                                                          |

|   |   |    |     |     |      |    |      |    |    |      |           |                                                          |

|   |   |    |     |     |      |    |      |    |    |      |           |                                                          |

|   |   |    |     |     |      |    |      |    |    |      |           |                                                          |

|   |   |    |     |     |      |    |      |    |    |      |           |                                                          |

|   |   |    |     |     |      |    |      |    |    |      |           |                                                          |

|   |   |    |     |     |      |    |      |    |    |      |           |                                                          |

| 0 | 0 | 22 | 0   | 0   | 1    | 0  | 0    | 0  | 1  | 0    | Display   | Display Update Sequence Option:                          |

|   |   |    |     |     |      |    |      |    |    |      | Update    | Enable the stage for Master Activation A[7:0]= FFh (POR) |

|   |   |    |     |     |      |    |      |    |    |      | Control 2 | Operating sequence                                       |

|   |   |    |     |     |      |    |      |    |    |      |           | Parameter (in Hex)                                       |

|   |   |    |     |     |      |    |      |    |    |      |           | Enable clock signal 80                                   |

|   |   |    |     |     |      |    |      |    |    |      |           | Disable clock signal 01<br>Enable clock signal           |

|   |   |    |     |     |      |    |      |    |    |      |           | Enable Analog                                            |

|   |   |    |     |     |      |    |      |    |    |      |           | C0<br>Disable Analog                                     |

|   |   |    |     |     |      |    |      |    |    |      |           | Disable clock signal                                     |

|   |   |    |     |     |      |    |      |    |    |      |           | 03                                                       |

|   |   |    |     |     |      |    |      |    |    |      |           | Enable clock signal Load LUT with DISPLAY Mode 1         |

|   |   |    |     |     |      |    |      |    |    |      |           | Disable clock signal                                     |

| 0 | 1 |    | A7  | A6  | A5   | A4 | A3   | A2 | A1 | A0   | -         | 91<br>Enable clock signal                                |

|   |   |    |     | 120 | 1 20 |    | 1 10 |    |    | 1.20 |           | Load LUT with DISPLAY Mode 2                             |

|   |   |    |     |     |      |    |      |    |    |      |           | Disable clock signal                                     |

|   |   |    |     |     |      |    |      |    |    |      |           | 99<br>Enable clock signal                                |

|   |   |    |     |     |      |    |      |    |    |      |           | Load temperature value                                   |

|   |   |    |     |     |      |    |      |    |    |      |           | Load LUT with DISPLAY Mode 1 Disable clock signal        |

|   |   |    |     |     |      |    |      |    |    |      |           | B1                                                       |

|   |   |    |     |     |      |    |      |    |    |      |           | Enable clock signal                                      |

|   |   |    |     |     |      |    |      |    |    |      |           | Load temperature value Load LUT with DISPLAY Mode 2      |

|   |   |    |     |     |      |    |      |    |    |      |           | Disable clock signal                                     |

|   |   |    |     |     |      |    |      |    |    |      |           | B9 Enable clock signal                                   |

|   |   |    |     |     |      |    |      |    |    |      |           | Enable Analog                                            |

|   |   |    |     |     |      |    |      |    |    |      |           | Display with DISPLAY Mode 1                              |

|   |   |    |     |     |      |    |      |    |    |      |           | Disable Analog<br>Disable OSC                            |

|   |   |    |     |     |      |    |      |    |    |      |           | C7                                                       |

|   |   |    |     |     |      |    |      |    |    |      |           | Enable clock signal Enable Analog                        |

|   |   |    |     |     |      |    |      |    |    |      |           | Display with DISPLAY Mode 2                              |

|   |   |    |     |     |      |    |      |    |    |      |           | Disable Analog                                           |

|   |   |    |     |     |      |    |      |    |    |      |           | Disable OSC<br>CF                                        |

|   |   |    |     |     |      |    |      |    |    |      |           | Enable clock signal                                      |

|   |   |    |     |     |      |    |      |    |    |      |           | Enable Analog                                            |

| 0 | 0 | 26 | 0  | 0  | 1  | 0  | 0  | 1  | 1          | 0          | Write RAM (Black White) / RAM 0x24  Write RAM (RED) / RAM 0x26) | After this command, data entries will be written into the BW RAM until another command is written. Address pointers will advance accordingly For Write pixel: Content of Write RAM(BW) = 1 For Black pixel: Content of Write RAM(BW) = 0  After this command, data entries will be written into the RED RAM until another command is written. Address pointers will advance accordingly. For Red pixel: Content of Write RAM(RED) = 1 For non-Red pixel [Black or White]: Content of Write RAM(RED) = 0 |

|---|---|----|----|----|----|----|----|----|------------|------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | 0 | 2C | 0  | 0  | 1  | 0  | 1  | 1  | 0          | 0          | Write                                                           | Write VCOM register from MCU interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0 | 1 |    | A7 | A6 | A5 | A4 | A3 | A2 | A1         | A0         | VCOM<br>register                                                | A[7:0] = 00h [POR]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0 | 0 | 2D | 0  | 0  | 1  | 0  | 1  | 1  | 0          |            | OTP                                                             | Read Register for Display Option:                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1 | 1 |    | A7 | A6 | A5 | A4 | A3 | A2 | <b>A</b> 1 | <b>A</b> 0 | Register<br>Read for                                            | A[7:0]: VCOM OTP Selection<br>(Command 0x37, Byte A)                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1 | 1 |    | В7 | В6 | В5 | B4 | В3 | B2 | B1         | В0         | Display                                                         | B[7:0]: VCOM Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1 | 1 |    | C7 | C6 | C5 | C4 | C3 | C2 | C1         |            | Option                                                          | (Command 0x2C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1 | 1 |    | D7 | D6 | D5 | D4 | D3 | D2 | D1         | D0         |                                                                 | C[7:0]~G[7:0]: Display Mode<br>(Command 0x37, Byte B to Byte F)                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1 | 1 |    | E7 | E6 | E5 | E4 | E3 | E2 | E1         | E0         |                                                                 | [5 bytes]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1 | 1 |    | F7 | F6 | F5 | F4 | F3 | F2 | F1         | F0         |                                                                 | H[7:0]~K[7:0]: Waveform Version                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1 | 1 |    | G7 | G6 | G5 | G4 | G3 | G2 | G1         | G0         |                                                                 | (Command 0x37, Byte G to Byte J) [4 bytes]                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1 | 1 |    | H7 | Н6 | H5 | H4 | Н3 | H2 | H1         | H0         |                                                                 | [4 bytes]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1 | 1 |    | I7 | I6 | I5 | I4 | I3 | I2 | I1         | 10         |                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1 | 1 |    | J7 | J6 | J5 | J4 | Ј3 | J2 | J1         | J0         |                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1 | 1 |    | K7 | K6 | K5 | K4 | K3 | K2 | K1         | K0         |                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0 | 0 | 2F | 0  | 0  | 1  | 0  | 1  | 1  | 1          | 1          | Status<br>Bit Read                                              | Read IC status Bit [POR 0x01] A[5]: HV Ready Detection flag [POR=0] 0: Ready 1: Not Ready A[4]: VCI Detection flag [POR=0] 0: Normal 1: VCI lower than the Detect level A[3]: [POR=0] A[2]: Busy flag [POR=0] 0: Normal 1: BUSY A[1:0]: Chip ID [POR=01] Remark: A[5] and A[4] status are not valid after RESET, they need to be initiated by command 0x14 and command 0x15 respectively                                                                                                                |

| 0 | 0 | 30 | 0  | 0  | 1  | 1  | 0  | 0  | 0          | 0          |                        | Program OTP of Waveform Setting The contents should be written into RAM before sending this command. The command required CLKEN=1. Refer to Register 0x22 for detail. BUSY pad will output high during operation |

|---|---|----|----|----|----|----|----|----|------------|------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | 0 | 32 | 0  | 0  | 1  | 1  | 0  | 0  | 1          | 0          | Write                  | Write LUT register from MCU interface                                                                                                                                                                            |

| 0 | 1 |    | A7 | A6 | A5 | A4 | A3 | A2 | <b>A</b> 1 | <b>A</b> 0 | LUT<br>register        | [153 bytes], which contains the content of VS[nX-LUTm], TP[nX], RP[n], SR[nXY],                                                                                                                                  |

| 0 | 1 |    | В7 | В6 | В5 | B4 | В3 | B2 | B1         | В0         | register               | FR[n] and XON[nXY]                                                                                                                                                                                               |

| 0 | 1 |    | :  | :  | :  | :  | •  | :  | :          | :          |                        | Refer to Session 6.7 WAVEFORM                                                                                                                                                                                    |

| 0 | 1 |    | :  | :  | :  | :  | :  | :  | :          | :          |                        | SETTING                                                                                                                                                                                                          |

| 0 | 1 |    | :  | :  | :  | :  | :  | :  | :          | :          |                        |                                                                                                                                                                                                                  |

| 0 | 1 |    | :  | :  | :  | :  | :  | :  | :          | :          |                        |                                                                                                                                                                                                                  |

| 0 | 0 | 39 | 0  | 0  | 1  | 1  | 1  | 0  | 0          | 1          | OTP<br>program<br>mode | OTP program mode A[1:0] = 00: Normal Mode [POR] A[1:0] = 11: Internal generated OTP programming voltage Remark: User is required to EXACTLY follow the reference code sequences                                  |

| 0 | 0 | 3C | 0  | 0  | 1  | 1  | 1  | 1  | 0          | 0          |                        | Select border waveform for VBD<br>A[7:0] = C0h [POR], set VBD as HIZ.                                                                                                                                            |

|   | 1 |    | _                     | Α     | Α              | Δ.             | 0                     | 0     | Α              | Α              |                    | A [7.6] Spleat VDD anti-                                                       |

|---|---|----|-----------------------|-------|----------------|----------------|-----------------------|-------|----------------|----------------|--------------------|--------------------------------------------------------------------------------|

| 0 | 1 |    | $A_7$                 | $A_6$ | $A_5$          | $A_4$          | 0                     | 0     | $A_1$          | $A_0$          |                    | A [7:6] :Select VBD option<br>A[7:6] Select VBD as                             |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | 00 GS Transition,                                                              |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | Defined in A[2] and                                                            |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | A[1:0]                                                                         |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | 01 Fix Level,                                                                  |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | Defined in A[5:4]                                                              |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | 10 VCOM                                                                        |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | 11[POR] HiZ                                                                    |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | A [5:4] Fix Level Setting for VBD                                              |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | A[5:4] VBD level<br>00 VSS                                                     |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | 00 VS3<br>01 VSH1                                                              |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | 10 VSL                                                                         |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | 11 VSH2                                                                        |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | A[2] GS Transition control                                                     |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | A[2] GS Transition control                                                     |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | 0 Follow LUT                                                                   |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | (Output VCOM @ RED)                                                            |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | 1 Follow LUT                                                                   |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | A [1:0] GS Transition setting for VBD<br>A[1:0] VBD Transition                 |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | 00 LUT0                                                                        |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | 01 LUT1                                                                        |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | 10 LUT2                                                                        |

|   |   |    |                       |       |                |                |                       |       |                |                |                    | 11 LUT3                                                                        |

| 0 | 0 | 44 | 0                     | 1     | 0              | 0              | 0                     | 1     | 0              | 0              |                    | Specify the start/end positions of the window                                  |

| 0 | 1 |    | 0                     | 0     | 0              | $A_4$          | $A_3$                 | $A_2$ | $\mathbf{A}_1$ | $A_0$          | X -                | address in the X direction by an address unit                                  |

| 0 | 1 |    | 0                     | 0     | 0              | $B_4$          | $B_3$                 | $B_2$ | $B_1$          | $B_0$          | address<br>Start / | A[4:0]: XSA[4:0], X Start, POR = 00h                                           |

|   |   |    |                       |       |                |                |                       |       |                |                | End                | B[4:0]: XEA[4:0], X End, POR = 12h                                             |

|   |   |    |                       |       |                |                |                       |       |                |                | position           |                                                                                |

| 0 | 0 | 45 | 0                     | 1     | 0              | 0              | 0                     | 1     | 0              | 1              | -                  | Specify the start/end positions of the window                                  |

| 0 | 1 |    | A <sub>7</sub>        | $A_6$ | $A_5$          | $A_4$          | A <sub>3</sub>        | $A_2$ | $A_1$          | $A_0$          | Y-                 | address in the Y direction by an address unit                                  |

| 0 | 1 |    | 0                     | 0     | 0              | 0              | 0                     | 0     | 0              | $A_8$          | address<br>Start / | A[8:0]: YSA[8:0], Y Start, POR = 0097h<br>B[8:0]: YEA[8:0], Y End, POR = 0000h |

| 0 | 1 |    | <b>B</b> <sub>7</sub> | $B_6$ | B <sub>5</sub> | B <sub>4</sub> | <b>B</b> <sub>3</sub> | $B_2$ | $B_1$          |                | End                | [2]. 12.1[0/0], 1 2.1d, 1 010 00001                                            |

| 0 | 1 |    | 0                     | 0     | 0              | 0              | 0                     | 0     | 0              | $\mathbf{B}_8$ | position           |                                                                                |

| 0 | 0 | 4E | 0                     | 1     | 0              | 0              | 1                     | 1     | 1              | 0              | -                  | Make initial settings for the RAM X address in                                 |

| 0 | 1 |    | 0                     | 0     | 0              | $A_4$          | $A_3$                 | $A_2$ | $\mathbf{A}_1$ | $A_0$          | X                  | the address counter (AC)                                                       |

|   |   |    |                       |       |                |                |                       |       |                |                | address<br>counter | A[4:0]: XAD[4:0], POR is 00h                                                   |

| 0 | 0 | 4F | 0                     | 1     | 0              | 0              | 1                     | 1     | 1              | 1              |                    | Make initial settings for the RAM Y address in                                 |

| 0 | 1 |    | <b>A</b> <sub>7</sub> | $A_6$ | A <sub>5</sub> | $A_4$          | A <sub>3</sub>        | $A_2$ | $A_1$          | $A_0$          | Y                  | the address counter (AC)                                                       |

| 0 | 1 |    | 0                     | 0     | 0              | 0              | 0                     | 0     | 0              | $A_8$          | address            | A[8:0]: YAD[8:0], POR is 0097h                                                 |

|   |   |    |                       |       |                |                |                       |       |                | L              | counter            |                                                                                |

## 8. Block Diagram

# 9. Typical Application Circuit with SPI Interface

| Part Name            | Value      | Reference Part                                                                        |                                                                                                    | Requirements for spare part |  |  |  |  |  |  |

|----------------------|------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------|--|--|--|--|--|--|

| C4 C6                | 1uF        | X5R/X7R;Voltage Rating:6v or 25v                                                      |                                                                                                    |                             |  |  |  |  |  |  |

| C1 C2 C3 C5<br>C7 C8 | 1uF        | 0402/0603/0805; X5R/X7R; Voltage Rating: 25v                                          |                                                                                                    |                             |  |  |  |  |  |  |

| С9                   | 0.47uF/1uF | 0603/0805; X7R;Voltage Rating:25v<br>NOTE: Effective capacitance >0.25uF @18v DC bias |                                                                                                    |                             |  |  |  |  |  |  |

| R1                   | 2.2Ohm     | 0402/0603/0805; 1% variation,≥0.05W                                                   |                                                                                                    |                             |  |  |  |  |  |  |

| D1 D2 D3             | Diode      | MBR0530                                                                               | 1)Reverse DC V<br>2)2)Io≥500mA<br>3)Forward volta                                                  | · ·                         |  |  |  |  |  |  |

| Q1                   | NMOS       | Si1304BDL/NX3008NBK                                                                   | 1)Drain-Source breakdown voltage ≥30v<br>2)Vgs(th)=0.9v(Typ), 1.3v(Max)<br>3)rds on≤2.1Ω@ Vgs=2.5v |                             |  |  |  |  |  |  |

| L1                   | 47UH       | CDRH2D18/LDNP-470NC                                                                   | 1) Io=500mA(m                                                                                      | nax)                        |  |  |  |  |  |  |

### 10 Typical Operating Sequence 10.1 OTP Operation Flow

# 10.2 OTP Operation Reference Program Code

| ACTION        | VALUE/DATA               | COMMENT                     |  |  |  |  |

|---------------|--------------------------|-----------------------------|--|--|--|--|

| POWER ON      |                          |                             |  |  |  |  |

| delay         | 10ms                     |                             |  |  |  |  |

|               | PIN CONFIG               |                             |  |  |  |  |

| RES#          | low                      | Hardware reset              |  |  |  |  |

| delay         | 200us                    |                             |  |  |  |  |

| RES#          | high                     |                             |  |  |  |  |

| delay         | 200us                    |                             |  |  |  |  |

| Read busy pin |                          | Wait for busy low           |  |  |  |  |

| Command 0x12  |                          | Software reset              |  |  |  |  |

| Read busy pin |                          | Wait for busy low           |  |  |  |  |

|               | SET VOLTAGE AND LOAD LUT |                             |  |  |  |  |

|               | LOAD IMAGE AND UPDATE    |                             |  |  |  |  |

| Command 0x24  | 2888bytes                | Load image (152/8*152)(BW)  |  |  |  |  |

| Command 0x26  | 2888bytes                | Load image (152/8*152)(RED) |  |  |  |  |

| Command 0x20  |                          |                             |  |  |  |  |

| Read busy pin |                          | Wait for busy low           |  |  |  |  |

| Command 0x10  | Data 0X01                | Enter deep sleep mode       |  |  |  |  |

|               | POWER OFF                |                             |  |  |  |  |

## 11. Reliability Test

| NO | Test items                                                                                                 | Test condition                                                                                                                             |